ARM is a family of RISC instruction set architectures (ISAs) for computer processors. Arm Ltd. develops the ISAs and licenses them to other companies, who build the physical devices that use the instruction set. It also designs and licenses cores that implement these ISAs.

SuperH is a 32-bit reduced instruction set computing (RISC) instruction set architecture (ISA) developed by Hitachi and currently produced by Renesas. It is implemented by microcontrollers and microprocessors for embedded systems.

XScale is a microarchitecture for central processing units initially designed by Intel implementing the ARM architecture instruction set. XScale comprises several distinct families: IXP, IXC, IOP, PXA and CE, with some later models designed as system-on-a-chip (SoC). Intel sold the PXA family to Marvell Technology Group in June 2006. Marvell then extended the brand to include processors with other microarchitectures, like Arm's Cortex.

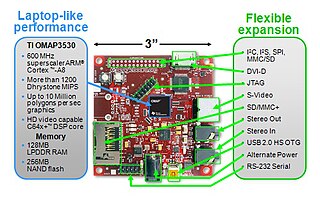

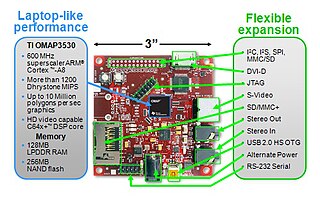

The OMAP family, developed by Texas Instruments, was a series of image/video processors. They are proprietary system on chips (SoCs) for portable and mobile multimedia applications. OMAP devices generally include a general-purpose ARM architecture processor core plus one or more specialized co-processors. Earlier OMAP variants commonly featured a variant of the Texas Instruments TMS320 series digital signal processor.

Jazelle DBX is an extension that allows some ARM processors to execute Java bytecode in hardware as a third execution state alongside the existing ARM and Thumb modes. Jazelle functionality was specified in the ARMv5TEJ architecture and the first processor with Jazelle technology was the ARM926EJ-S. Jazelle is denoted by a "J" appended to the CPU name, except for post-v5 cores where it is required for architecture conformance.

Atmel ARM-based processors are microcontrollers and microprocessors integrated circuits, by Microchip Technology, that are based on various 32-bit ARM processor cores, with in-house designed peripherals and tool support.

ARM9 is a group of 32-bit RISC ARM processor cores licensed by ARM Holdings for microcontroller use. The ARM9 core family consists of ARM9TDMI, ARM940T, ARM9E-S, ARM966E-S, ARM920T, ARM922T, ARM946E-S, ARM9EJ-S, ARM926EJ-S, ARM968E-S, ARM996HS. Since ARM9 cores were released from 1998 to 2006, they are no longer recommended for new IC designs, instead ARM Cortex-A, ARM Cortex-M, ARM Cortex-R cores are preferred.

The ARM Cortex-A9 MPCore is a 32-bit multi-core processor that provides up to 4 cache-coherent cores, each implementing the ARM v7 architecture instruction set. It was introduced in 2007.

The ARM Cortex-A15 MPCore is a 32-bit processor core licensed by ARM Holdings implementing the ARMv7-A architecture. It is a multicore processor with out-of-order superscalar pipeline running at up to 2.5 GHz.

The ARM Cortex-M is a group of 32-bit RISC ARM processor cores licensed by ARM Limited. These cores are optimized for low-cost and energy-efficient integrated circuits, which have been embedded in tens of billions of consumer devices. Though they are most often the main component of microcontroller chips, sometimes they are embedded inside other types of chips too. The Cortex-M family consists of Cortex-M0, Cortex-M0+, Cortex-M1, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23, Cortex-M33, Cortex-M35P, Cortex-M55, Cortex-M85. A floating-point unit (FPU) option is available for Cortex-M4 / M7 / M33 / M35P / M55 / M85 cores, and when included in the silicon these cores are sometimes known as "Cortex-MxF", where 'x' is the core variant.

The ARM Cortex-A is a group of 32-bit and 64-bit RISC ARM processor cores licensed by Arm Holdings. The cores are intended for application use. The group consists of 32-bit only cores: ARM Cortex-A5, ARM Cortex-A7, ARM Cortex-A8, ARM Cortex-A9, ARM Cortex-A12, ARM Cortex-A15, ARM Cortex-A17 MPCore, and ARM Cortex-A32, 32/64-bit mixed operation cores: ARM Cortex-A35, ARM Cortex-A53, ARM Cortex-A55, ARM Cortex-A57, ARM Cortex-A72, ARM Cortex-A73, ARM Cortex-A75, ARM Cortex-A76, ARM Cortex-A77, ARM Cortex-A78, ARM Cortex-A710, and ARM Cortex-A510 Refresh, and 64-bit only cores: ARM Cortex-A34, ARM Cortex-A65, ARM Cortex-A510 (2021), ARM Cortex-A715, ARM Cortex-A520, and ARM Cortex-A720.

The ARM Cortex-A5 is a 32-bit processor core licensed by ARM Holdings implementing the ARMv7-A architecture announced in 2009.

The ARM Cortex-A7 MPCore is a 32-bit microprocessor core licensed by ARM Holdings implementing the ARMv7-A architecture announced in 2011.

Scorpion is a central processing unit (CPU) core designed by Qualcomm for use in their Snapdragon mobile systems on chips (SoCs). It was released in 2008. It was designed in-house, but has many architectural similarities with the ARM Cortex-A8 and Cortex-A9 CPU cores.

Qualcomm Krait is an ARM-based central processing unit included in the Snapdragon S4 and earlier models of Snapdragon 400/600/800 series SoCs. It was introduced in 2012 as a successor to the Scorpion CPU and although it has architectural similarities, Krait is not a Cortex-A15 core, but it was designed in-house. In 2015, Krait was superseded by the 64-bit Kryo architecture, first introduced in Snapdragon 820 SoC.

The ARM Cortex-A12 is a 32-bit processor core licensed by ARM Holdings implementing the ARMv7-A architecture. It provides up to 4 cache-coherent cores. The Cortex-A12 is a successor to the Cortex-A9.

The ARM Cortex-A57 is a central processing unit implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings. The Cortex-A57 is an out-of-order superscalar pipeline. It is available as SIP core to licensees, and its design makes it suitable for integration with other SIP cores into one die constituting a system on a chip (SoC).

The ARM Cortex-A17 is a 32-bit processor core implementing the ARMv7-A architecture, licensed by ARM Holdings. Providing up to four cache-coherent cores, it serves as the successor to the Cortex-A9 and replaces the previous ARM Cortex-A12 specifications. ARM claims that the Cortex-A17 core provides 60% higher performance than the Cortex-A9 core, while reducing the power consumption by 20% under the same workload.

The ARM Cortex-A53 is one of the first two central processing units implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings' Cambridge design centre, along with the Cortex-A57. The Cortex-A53 is a 2-wide decode superscalar processor, capable of dual-issuing some instructions. It was announced October 30, 2012 and is marketed by ARM as either a stand-alone, more energy-efficient alternative to the more powerful Cortex-A57 microarchitecture, or to be used alongside a more powerful microarchitecture in a big.LITTLE configuration. It is available as an IP core to licensees, like other ARM intellectual property and processor designs.

The ARM Cortex-A72 is a central processing unit implementing the ARMv8-A 64-bit instruction set designed by ARM Holdings' Austin design centre. The Cortex-A72 is a 3-way decode out-of-order superscalar pipeline. It is available as SIP core to licensees, and its design makes it suitable for integration with other SIP cores into one die constituting a system on a chip (SoC). The Cortex-A72 was announced in 2015 to serve as the successor of the Cortex-A57, and was designed to use 20% less power or offer 90% greater performance.