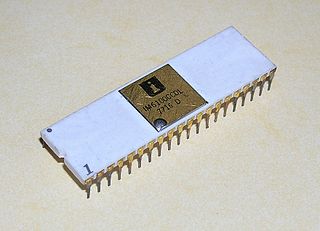

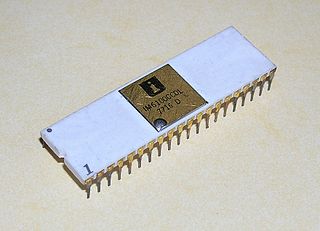

The Intel 8080 ("eighty-eighty") is the second 8-bit microprocessor designed and manufactured by Intel. It first appeared in April 1974 and is an extended and enhanced variant of the earlier 8008 design, although without binary compatibility. The initial specified clock rate or frequency limit was 2 MHz, with common instructions using 4, 5, 7, 10, or 11 clock cycles. As a result, the processor is able to execute several hundred thousand instructions per second. Two faster variants, the 8080A-1 and 8080A-2, became available later with clock frequency limits of 3.125 MHz and 2.63 MHz respectively. The 8080 needs two support chips to function in most applications: the i8224 clock generator/driver and the i8228 bus controller. The 8080 is implemented in N-type metal–oxide–semiconductor logic (NMOS) using non-saturated enhancement mode transistors as loads thus demanding a +12 V and a −5 V voltage in addition to the main transistor–transistor logic (TTL) compatible +5 V.

The Intel MCS-51 is a single chip microcontroller (MCU) series developed by Intel in 1980 for use in embedded systems. The architect of the Intel MCS-51 instruction set was John H. Wharton. Intel's original versions were popular in the 1980s and early 1990s, and enhanced binary compatible derivatives remain popular today. It is a complex instruction set computer, but also has some of the features of RISC architectures, such as a large register set and register windows, and has separate memory spaces for program instructions and data.

The Intel 8085 ("eighty-eighty-five") is an 8-bit microprocessor produced by Intel and introduced in March 1976. It is the last 8-bit microprocessor developed by Intel.

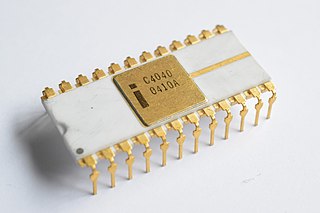

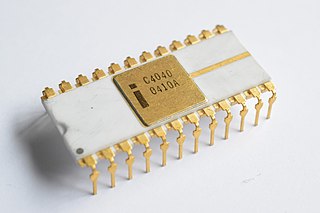

The Intel 4040 ("forty-forty") is the second 4-bit microprocessor designed and manufactured by Intel. Introduced in 1974 as a successor to the Intel 4004, the 4040 was produced with a 10 μm process and includes silicon gate enhancement-load PMOS logic technology. The 4040 contained 3,000 transistors and could execute approximately 62,000 instructions per second.

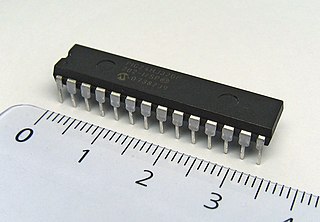

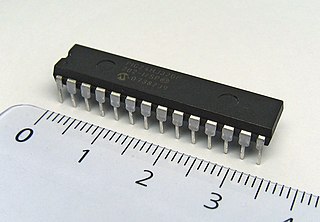

PIC is a family of microcontrollers made by Microchip Technology, derived from the PIC1640 originally developed by General Instrument's Microelectronics Division. The name PIC initially referred to Peripheral Interface Controller, and is currently expanded as Programmable Intelligent Computer. The first parts of the family were available in 1976; by 2013 the company had shipped more than twelve billion individual parts, used in a wide variety of embedded systems.

The National Semiconductor COP8 is an 8-bit CISC core microcontroller. COP8 is an enhancement to the earlier COP400 4-bit microcontroller family. COP8 main features are:

The TMS9900 was one of the first commercially available, single-chip 16-bit microprocessors. Introduced in June 1976, it implemented Texas Instruments' TI-990 minicomputer architecture in a single-chip format, and was initially used for low-end models of that lineup.

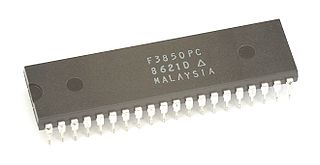

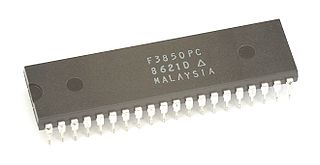

The Fairchild F8 is an 8-bit microprocessor system from Fairchild Semiconductor, announced in 1974 and shipped in 1975. The original processor family included four main 40-pin integrated circuits (ICs); the 3850 CPU which was the arithmetic logic unit, the 3851 Program Storage Unit (PSU) which contained 1 KB of program ROM and handled instruction decoding, and the optional 3852 Dynamic Memory Interface (DMI) or 3853 Static Memory Interface (SMI) to control additional RAM or ROM holding the user programs or data. The 3854 DMA was another optional system that added direct memory access into the RAM controlled by the 3852.

National Semiconductor's SC/MP for Simple Cost-effective Micro Processor, is an early 8-bit microprocessor which became available in April 1976. It was designed to allow systems to be implemented with the minimum number of additional support chips. SC/MP included a daisy-chained control pin that allowed up to three SC/MP's share a single main memory to produce a multiprocessor system, or to act as controllers in a system with another main central processing unit (CPU). Three versions were released over its lifetime, SCMP-1 through 3, the latter two also known as INS8060 and INS8070.

The Intel 8061 microcontroller is most notable for its use in the Ford EEC-IV automotive engine control unit. A close relative of the 8096, the Intel 8061 is second-sourced by Toshiba and Motorola.

The Atmel AVR instruction set is the machine language for the Atmel AVR, a modified Harvard architecture 8-bit RISC single chip microcontroller which was developed by Atmel in 1996. The AVR was one of the first microcontroller families to use on-chip flash memory for program storage.

The Signetics 2650 was an 8-bit microprocessor introduced in July 1975. According to Adam Osborne's book An Introduction to Microprocessors Vol 2: Some Real Products, it was "the most minicomputer-like" of the microprocessors available at the time. A combination of missing features and odd memory access limited its appeal, and the system saw little use in the market.

RS08 is a family of 8-bit microcontrollers by NXP Semiconductors. Originally released by Freescale in 2006, the RS08 architecture is a reduced-resource version of the Freescale MC68HCS08 central processing unit (CPU), a member of the 6800 microprocessor family. It has been implemented in several microcontroller devices for embedded systems.

TLCS is a prefix applied to microcontrollers made by Toshiba. The product line includes multiple families of CISC and RISC architectures. Individual components generally have a part number beginning with "TMP". E.g. the TMP8048AP is a member of the TLCS-48 family.

The Mitsubishi 740, also known as MELPS 740, is a series of 8-bit CMOS microcontrollers and microprocessors with an enhanced MOS Technology 6502 compatible core based on the expanded WDC 65C02. The ICs were manufactured by Mitsubishi Electric during the 1980s and 1990s.

The Intersil 6100 is a single-chip microprocessor implementation of the 12-bit PDP-8 instruction set, along with a range of peripheral support and memory ICs developed by Intersil in the mid-1970s. It was sometimes referred to as the CMOS-PDP8. Since it was also produced by Harris Corporation, it was also known as the Harris HM-6100. The Intersil 6100 was introduced in the second quarter of 1975, and the Harris version in 1976.

The 9S08 is an 8-bit microcontroller (μC) family originally produced by Motorola, later by Freescale Semiconductor, and currently by NXP, descended from the Motorola 6800 microprocessor. It is a CISC microcontroller. A slightly extended variant of the 68HC08, it shares upward compatibility with the aging 68HC05 microcontrollers, and is found in almost any type of embedded systems. The larger members offer up to 128 KiB of flash, and 8 KiB of RAM via a simple memory management unit (MMU) which allows bank-switching 16 KiB of the address space and an address/data register pair which allows data fetches from any address. The paging scheme used allows for a theoretical maximum of 4 MB of flash.

The ST6 and ST7 are 8-bit microcontroller product lines from STMicroelectronics. They are commonly used in small embedded applications like washing machines.

The STM8 is an 8-bit microcontroller family by STMicroelectronics. The STM8 microcontrollers use an extended variant of the ST7 microcontroller architecture. STM8 microcontrollers are particularly low cost for a full-featured 8-bit microcontroller.

The Mostek MK5065 was an 8-bit microprocessor introduced by Mostek in early 1974. The design was originally developed by Motorola for use in an Olivetti electronic calculator, and was licensed to Mostek for use in non-calculator roles. It featured three sets of processor registers, allowing it to switch to an interrupt handler in a single cycle, and a wait-for-data mode that aided direct memory access.