Semiconductor device fabrication is the process used to manufacture semiconductor devices, typically integrated circuits (ICs) such as computer processors, microcontrollers, and memory chips. It is a multiple-step photolithographic and physico-chemical process during which electronic circuits are gradually created on a wafer, typically made of pure single-crystal semiconducting material. Silicon is almost always used, but various compound semiconductors are used for specialized applications.

Moore's law is the observation that the number of transistors in an integrated circuit (IC) doubles about every two years. Moore's law is an observation and projection of a historical trend. Rather than a law of physics, it is an empirical relationship. It is an experience-curve law, a type of law quantifying efficiency gains from experience in production.

Taiwan Semiconductor Manufacturing Company Limited is a Taiwanese multinational semiconductor contract manufacturing and design company. It is the world's second-most valuable semiconductor company, the world's largest dedicated independent ("pure-play") semiconductor foundry, and its country's largest company, with headquarters and main operations located in the Hsinchu Science Park in Hsinchu, Taiwan. Although the central government of Taiwan is the largest individual shareholder, the majority of TSMC is owned by foreign investors. In 2023, the company was ranked 44th in the Forbes Global 2000.

The 90 nm process refers to the technology used in semiconductor manufacturing to create integrated circuits with a minimum feature size of 90 nanometers. It was an advancement over the previous 130 nm process. Eventually, it was succeeded by smaller process nodes, such as the 65 nm, 45 nm, and 32 nm processes.

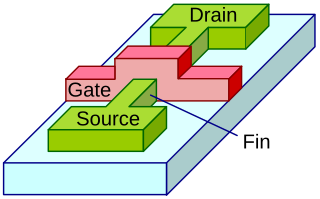

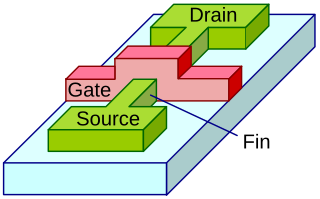

A fin field-effect transistor (FinFET) is a multigate device, a MOSFET built on a substrate where the gate is placed on two, three, or four sides of the channel or wrapped around the channel, forming a double or even multi gate structure. These devices have been given the generic name "FinFETs" because the source/drain region forms fins on the silicon surface. The FinFET devices have significantly faster switching times and higher current density than planar CMOS technology.

The "32 nm" node is the step following the "45 nm" process in CMOS (MOSFET) semiconductor device fabrication. "32-nanometre" refers to the average half-pitch of a memory cell at this technology level.

The transistor count is the number of transistors in an electronic device. It is the most common measure of integrated circuit complexity. The rate at which MOS transistor counts have increased generally follows Moore's law, which observes that transistor count doubles approximately every two years. However, being directly proportional to the area of a die, transistor count does not represent how advanced the corresponding manufacturing technology is. A better indication of this is transistor density which is the ratio of a semiconductor's transistor count to its die area.

The "22 nm" node is the process step following 32 nm in CMOS MOSFET semiconductor device fabrication. The typical half-pitch for a memory cell using the process is around 22 nm. It was first demonstrated by semiconductor companies for use in RAM memory in 2008. In 2010, Toshiba began shipping 24 nm flash memory chips, and Samsung Electronics began mass-producing 20 nm flash memory chips. The first consumer-level CPU deliveries using a 22 nm process started in April 2012 with the Intel Ivy Bridge processors.

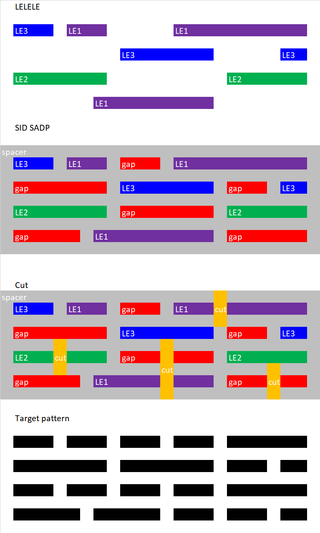

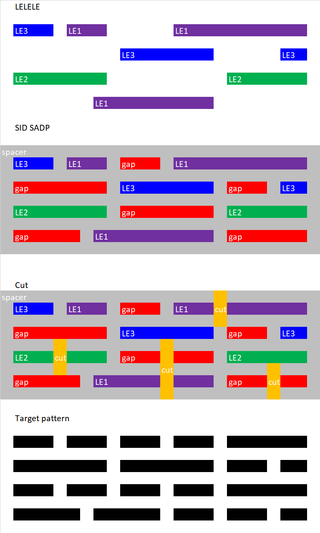

Multiple patterning is a class of technologies for manufacturing integrated circuits (ICs), developed for photolithography to enhance the feature density. It is expected to be necessary for the 10 nm and 7 nm node semiconductor processes and beyond. The premise is that a single lithographic exposure may not be enough to provide sufficient resolution. Hence additional exposures would be needed, or else positioning patterns using etched feature sidewalls would be necessary.

The "14 nanometer process" refers to a marketing term for the MOSFET technology node that is the successor to the "22 nm" node. The "14 nm" was so named by the International Technology Roadmap for Semiconductors (ITRS). Until about 2011, the node following "22 nm" was expected to be "16 nm". All "14 nm" nodes use FinFET technology, a type of multi-gate MOSFET technology that is a non-planar evolution of planar silicon CMOS technology.

A multigate device, multi-gate MOSFET or multi-gate field-effect transistor (MuGFET) refers to a metal–oxide–semiconductor field-effect transistor (MOSFET) that has more than one gate on a single transistor. The multiple gates may be controlled by a single gate electrode, wherein the multiple gate surfaces act electrically as a single gate, or by independent gate electrodes. A multigate device employing independent gate electrodes is sometimes called a multiple-independent-gate field-effect transistor (MIGFET). The most widely used multi-gate devices are the FinFET and the GAAFET, which are non-planar transistors, or 3D transistors.

GlobalFoundries Inc. is a multinational semiconductor contract manufacturing and design company incorporated in the Cayman Islands and headquartered in Malta, New York. Created by the divestiture of the manufacturing arm of AMD, the company was privately owned by Mubadala Investment Company, a sovereign wealth fund of the United Arab Emirates, until an initial public offering (IPO) in October 2021.

Per the International Technology Roadmap for Semiconductors, the 45 nm process is a MOSFET technology node referring to the average half-pitch of a memory cell manufactured at around the 2007–2008 time frame.

In semiconductor manufacturing, the International Roadmap for Devices and Systems defines the "5 nm" process as the MOSFET technology node following the "7 nm" node. In 2020, Samsung and TSMC entered volume production of "5 nm" chips, manufactured for companies including Apple, Marvell, Huawei and Qualcomm.

In semiconductor manufacturing, the "7 nm" process is a term for the MOSFET technology node following the "10 nm" node, defined by the International Roadmap for Devices and Systems (IRDS), which was preceded by the International Technology Roadmap for Semiconductors (ITRS). It is based on FinFET technology, a type of multi-gate MOSFET technology.

Dr. Gary Patton is an American technologist and business executive. He is currently the Corporate Vice President and General Manager of Design Enablement and Components Research in the Technology Development Group at Intel. He has spent most of his career in IBM, starting in IBM's Research Division and holding management and executive positions in IBM's Microelectronics Division in Technology Development, Design Enablement, Manufacturing, and Business Line Management.

In semiconductor manufacturing, the 3nm process is the next die shrink after the 5 nm MOSFET technology node. South Korean chipmaker Samsung started shipping its 3 nm gate all around (GAA) process, named 3GAA, in mid-2022. On 29 December 2022, Taiwanese chip manufacturer TSMC announced that volume production using its 3 nm semiconductor node (N3) was under way with good yields. An enhanced 3 nm chip process called "N3E" may have started production in 2023. American manufacturer Intel planned to start 3 nm production in 2023.

In semiconductor manufacturing, the "2 nm process" is the next MOSFET die shrink after the "3 nm" process node.

The "28 nm" lithography process is a half-node semiconductor manufacturing process based on a die shrink of the "32 nm" lithography process. It appeared in production in 2010.