JP5197961B2 - マルチチップパッケージモジュールおよびその製造方法 - Google Patents

マルチチップパッケージモジュールおよびその製造方法 Download PDFInfo

- Publication number

- JP5197961B2 JP5197961B2 JP2006545467A JP2006545467A JP5197961B2 JP 5197961 B2 JP5197961 B2 JP 5197961B2 JP 2006545467 A JP2006545467 A JP 2006545467A JP 2006545467 A JP2006545467 A JP 2006545467A JP 5197961 B2 JP5197961 B2 JP 5197961B2

- Authority

- JP

- Japan

- Prior art keywords

- package

- die

- substrate

- inverted

- adhesive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 5

- 239000000758 substrate Substances 0.000 claims abstract description 190

- 125000006850 spacer group Chemical group 0.000 claims abstract description 98

- 238000000034 method Methods 0.000 claims abstract description 27

- 239000000853 adhesive Substances 0.000 claims description 68

- 230000001070 adhesive effect Effects 0.000 claims description 68

- 229910000679 solder Inorganic materials 0.000 claims description 26

- 238000000465 moulding Methods 0.000 claims description 13

- 150000001875 compounds Chemical class 0.000 claims description 11

- 239000002245 particle Substances 0.000 claims description 6

- 239000004809 Teflon Substances 0.000 claims description 5

- 229920006362 Teflon® Polymers 0.000 claims description 5

- 239000002313 adhesive film Substances 0.000 claims description 5

- 238000004140 cleaning Methods 0.000 claims description 2

- 238000005538 encapsulation Methods 0.000 claims 1

- 229910052751 metal Inorganic materials 0.000 description 63

- 239000002184 metal Substances 0.000 description 63

- 239000010410 layer Substances 0.000 description 55

- 239000000463 material Substances 0.000 description 11

- 238000013461 design Methods 0.000 description 10

- 238000007689 inspection Methods 0.000 description 10

- 238000012545 processing Methods 0.000 description 10

- 239000004593 Epoxy Substances 0.000 description 8

- 239000002775 capsule Substances 0.000 description 8

- 238000005516 engineering process Methods 0.000 description 6

- 238000000926 separation method Methods 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 4

- 238000013459 approach Methods 0.000 description 4

- 230000008901 benefit Effects 0.000 description 4

- 239000000919 ceramic Substances 0.000 description 4

- 239000004020 conductor Substances 0.000 description 4

- 229910052802 copper Inorganic materials 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 239000011521 glass Substances 0.000 description 4

- 238000004806 packaging method and process Methods 0.000 description 4

- 239000000047 product Substances 0.000 description 4

- 239000004065 semiconductor Substances 0.000 description 4

- 229910052710 silicon Inorganic materials 0.000 description 4

- 239000010703 silicon Substances 0.000 description 4

- 239000004642 Polyimide Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 229910052782 aluminium Inorganic materials 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 239000012467 final product Substances 0.000 description 3

- 230000010354 integration Effects 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- 229920001721 polyimide Polymers 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 2

- 239000012790 adhesive layer Substances 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 239000011324 bead Substances 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 239000000945 filler Substances 0.000 description 2

- 208000032754 Infant Death Diseases 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000002507 cathodic stripping potentiometry Methods 0.000 description 1

- 230000002860 competitive effect Effects 0.000 description 1

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000032798 delamination Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000013100 final test Methods 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 239000010931 gold Substances 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000010348 incorporation Methods 0.000 description 1

- 238000007373 indentation Methods 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000010421 standard material Substances 0.000 description 1

- 238000010561 standard procedure Methods 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/12—Mountings, e.g. non-detachable insulating substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/34—Arrangements for cooling, heating, ventilating or temperature compensation ; Temperature sensing arrangements

- H01L23/42—Fillings or auxiliary members in containers or encapsulations selected or arranged to facilitate heating or cooling

- H01L23/433—Auxiliary members in containers characterised by their shape, e.g. pistons

- H01L23/4334—Auxiliary members in encapsulations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L25/00—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof

- H01L25/03—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes

- H01L25/04—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers

- H01L25/065—Assemblies consisting of a plurality of individual semiconductor or other solid state devices ; Multistep manufacturing processes thereof all the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/00, or in a single subclass of H10K, H10N, e.g. assemblies of rectifier diodes the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L25/0657—Stacked arrangements of devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

- H01L2224/0554—External layer

- H01L2224/0555—Shape

- H01L2224/05552—Shape in top view

- H01L2224/05553—Shape in top view being rectangular

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/484—Connecting portions

- H01L2224/48463—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond

- H01L2224/48465—Connecting portions the connecting portion on the bonding area of the semiconductor or solid-state body being a ball bond the other connecting portion not on the bonding area being a wedge bond, i.e. ball-to-wedge, regular stitch

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

- H01L2224/491—Disposition

- H01L2224/4912—Layout

- H01L2224/49175—Parallel arrangements

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73215—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/0651—Wire or wire-like electrical connections from device to substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06575—Auxiliary carrier between devices, the carrier having no electrical connection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/04—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers

- H01L2225/065—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices not having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/06503—Stacked arrangements of devices

- H01L2225/06582—Housing for the assembly, e.g. chip scale package [CSP]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1017—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support

- H01L2225/1023—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement the lowermost container comprising a device support the support being an insulating substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1047—Details of electrical connections between containers

- H01L2225/1052—Wire or wire-like electrical connections

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2225/00—Details relating to assemblies covered by the group H01L25/00 but not provided for in its subgroups

- H01L2225/03—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00

- H01L2225/10—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers

- H01L2225/1005—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00

- H01L2225/1011—All the devices being of a type provided for in the same subgroup of groups H01L27/00 - H01L33/648 and H10K99/00 the devices having separate containers the devices being of a type provided for in group H01L27/00 the containers being in a stacked arrangement

- H01L2225/1047—Details of electrical connections between containers

- H01L2225/1058—Bump or bump-like electrical connections, e.g. balls, pillars, posts

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/42—Wire connectors; Manufacturing methods related thereto

- H01L24/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L24/49—Structure, shape, material or disposition of the wire connectors after the connecting process of a plurality of wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/73—Means for bonding being of different types provided for in two or more of groups H01L24/10, H01L24/18, H01L24/26, H01L24/34, H01L24/42, H01L24/50, H01L24/63, H01L24/71

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/00014—Technical content checked by a classifier the subject-matter covered by the group, the symbol of which is combined with the symbol of this group, being disclosed without further technical details

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/191—Disposition

- H01L2924/19101—Disposition of discrete passive components

- H01L2924/19107—Disposition of discrete passive components off-chip wires

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/30107—Inductance

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3025—Electromagnetic shielding

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Wire Bonding (AREA)

- Encapsulation Of And Coatings For Semiconductor Or Solid State Devices (AREA)

Description

Claims (18)

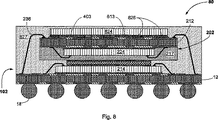

- 積み重ねられた第1及び第2パッケージを含み、前記第1および第2パッケージの各々は、基板に取り付けられたダイを含み、前記第1パッケージのダイは、ワイヤボンドによって前記第1パッケージの基板に接続され、第2パッケージは、反転されると共に、第2パッケージのダイと第1パッケージのダイとの間の空間のための施策を備えて第1パッケージのダイの上に積み重ねられ、前記施策は、スペーサを接着剤により第1パッケージと第2パッケージとの間に固定した構造であり、前記接着剤は、テフロン(登録商標)粒子を有する接着剤、または接着フィルムである、マルチチップパッケージモジュール。

- 積み重ねられた第1及び第2パッケージを含み、第1パッケージは、基板に取り付けられたダイを有するBGAパッケージであり、前記第1パッケージのダイは、ワイヤボンドによって前記第1パッケージの基板に電気的に接続され、前記第2パッケージは、基板に取り付けられたダイを含み、第2パッケージが反転されるので、ダイが取り付けられた第2パッケージの基板表面は、下方向を向き、反転されたパッケージは、第1パッケージのダイと反転された前記第2パッケージとの間の離間のための施策を備えて、第1パッケージのダイの上に固定され、前記施策は、スペーサを接着剤により前記第1パッケージと前記第2パッケージとの間に固定した構造であり、前記接着剤は、テフロン粒子を有する接着剤、または接着フィルムである、マルチチップパッケージモジュール。

- ワイヤボンドが、第1パッケージのダイのパッドと、反転された第2パッケージの上方向側のZ方向相互接続ワイヤボンドパッドとを接続する、請求項2に記載のマルチチップパッケージモジュール。

- ワイヤボンドが、第1パッケージの基板の上方向側のZ方向相互接続ワイヤボンドパッドと、反転された第2パッケージの上方向側のZ方向相互接続ワイヤボンドパッドとを接続する、請求項2に記載のマルチチップパッケージモジュール。

- ワイヤボンドが、第1パッケージの基板の上方向側のZ方向相互接続ワイヤボンドパッドと、反転された第2パッケージの上方向側のZ方向相互接続ワイヤボンドパッドとを接続し、ワイヤボンドが、第1パッケージのダイのパッドと、反転された第2パッケージの

上方向側のZ方向相互接続ワイヤボンドパッドとを接続する、請求項2に記載のマルチチップパッケージモジュール。 - 反転された第2パッケージは、複数の反転されたダイを含む請求項2に記載のマルチチップパッケージモジュール。

- 第1パッケージは、複数のダイを含み、反転された第2パッケージは、前記ダイの最上位に取り付けられる、請求項2に記載のマルチチップパッケージモジュール。

- 反転された第2パッケージの上に取り付けられる補助ダイをさらに含む請求項2に記載のマルチチップパッケージモジュール。

- 補助ダイは、第2パッケージの基板にワイヤボンドされる請求項8に記載のマルチチップパッケージモジュール。

- 補助ダイは、第1パッケージの基板にワイヤボンドされる請求項8に記載のマルチチップパッケージモジュール。

- ヒートスプレッダーをさらに含む請求項2に記載のマルチチップパッケージモジュール。

- ヒートスプレッダーは、最上位のパッケージの上方向を向く表面に固定される請求項11に記載のマルチチップパッケージモジュール。

- ヒートスプレッダーは、第2パッケージの補助ダイの上方向を向く表面に固定される請求項11に記載のマルチチップパッケージモジュール。

- 電気非伝導性で熱伝導性のモールドがモジュールカプセル化に採用される請求項2に記載のマルチチップパッケージモジュール。

- ダイの上に積み重ねられた、反転されたパッケージを有するマルチチップパッケージモジュールの製造方法であって、第1基板の上方向側に取り付けられた第1ダイを有する第1パッケージ、および、第2基板の上方向側に取り付けられた第2ダイを有する第2パッケージを提供し、前記第1パッケージの前記第1ダイの上に上下反転された前記第2パッケージを積み重ね、前記第2パッケージの下方を向いた面と、前記第1ダイを前記第1基板に接続するワイヤボンドとが相互にダメージを与えるのを防止すべく、前記第2パッケージと前記第1ダイとの間の離間のために施策がなされ、

前記施策は、スペーサを接着剤により第1パッケージと第2パッケージとの間に固定した構造であり、前記接着剤は、テフロン粒子を有する接着剤、または接着フィルムである、方法。 - ダイの上に積み重ねられた、反転されたパッケージを有するマルチチップパッケージモジュールの製造方法であって、第1パッケージの第1ダイを第1パッケージの第1基板に取り付け、前記第1基板に前記第1ダイをワイヤボンドし、前記第1ダイの上にスペーサを固定し、第2パッケージの第2ダイを第2パッケージの第2基板に取り付け、前記スペーサの上に反転された前記第2パッケージを固定し、Z方向相互接続ワイヤボンディングのためのワイヤボンドサイトを用意すべく、第1プラズマ洗浄を実施し、Z方向相互接続ワイヤボンディングを実行し、モールドの好接着のための表面を用意すべく、第2プラズマ洗浄を実施し、モールドを導入して養生し、はんだボールを取り付ける方法であり、

前記スペーサは接着剤により前記第1パッケージと前記第2パッケージとの間に固定され、前記接着剤は、テフロン粒子を有する接着剤、または接着フィルムである、方法。 - Z方向相互接続に続き、第2パッケージの上方向側に接着剤を提供し、接着剤の上にヒートスプレッダーを配置し、接着剤を養生することをさらに含む請求項16に記載の方法。

- Z方向相互接続に続き、モールドキャビティー内にヒートスプレッダーを配置し、キャビティー内のヒートスプレッダーの上のダイの上に固定される、組み立てられて反転されたパッケージを配置し、キャビティー内に成型コンパウンドを導入し、コンパウンドを養生してモールドすることをさらに含む請求項16に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US53042303P | 2003-12-17 | 2003-12-17 | |

| US60/530,423 | 2003-12-17 | ||

| PCT/US2004/042413 WO2005059967A2 (en) | 2003-12-17 | 2004-12-16 | Multiple chip package module having inverted package stacked over die |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007516616A JP2007516616A (ja) | 2007-06-21 |

| JP5197961B2 true JP5197961B2 (ja) | 2013-05-15 |

Family

ID=34700137

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006545467A Active JP5197961B2 (ja) | 2003-12-17 | 2004-12-16 | マルチチップパッケージモジュールおよびその製造方法 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8970049B2 (ja) |

| JP (1) | JP5197961B2 (ja) |

| KR (1) | KR101076537B1 (ja) |

| TW (1) | TWI357663B (ja) |

| WO (1) | WO2005059967A2 (ja) |

Families Citing this family (125)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100401020B1 (ko) * | 2001-03-09 | 2003-10-08 | 앰코 테크놀로지 코리아 주식회사 | 반도체칩의 스택킹 구조 및 이를 이용한 반도체패키지 |

| US6856009B2 (en) * | 2003-03-11 | 2005-02-15 | Micron Technology, Inc. | Techniques for packaging multiple device components |

| TWI283467B (en) * | 2003-12-31 | 2007-07-01 | Advanced Semiconductor Eng | Multi-chip package structure |

| WO2006052616A1 (en) | 2004-11-03 | 2006-05-18 | Tessera, Inc. | Stacked packaging improvements |

| US7745918B1 (en) | 2004-11-24 | 2010-06-29 | Amkor Technology, Inc. | Package in package (PiP) |

| KR100593703B1 (ko) * | 2004-12-10 | 2006-06-30 | 삼성전자주식회사 | 돌출부 와이어 본딩 구조 보강용 더미 칩을 포함하는반도체 칩 적층 패키지 |

| US7822912B2 (en) * | 2005-03-14 | 2010-10-26 | Phision Electronics Corp. | Flash storage chip and flash array storage system |

| US8395251B2 (en) * | 2005-05-12 | 2013-03-12 | Stats Chippac Ltd. | Integrated circuit package to package stacking system |

| US20060284298A1 (en) * | 2005-06-15 | 2006-12-21 | Jae Myun Kim | Chip stack package having same length bonding leads |

| SG130055A1 (en) | 2005-08-19 | 2007-03-20 | Micron Technology Inc | Microelectronic devices, stacked microelectronic devices, and methods for manufacturing microelectronic devices |

| US8796836B2 (en) | 2005-08-25 | 2014-08-05 | Micron Technology, Inc. | Land grid array semiconductor device packages |

| US7291900B2 (en) | 2005-08-25 | 2007-11-06 | Micron Technology, Inc. | Lead frame-based semiconductor device packages incorporating at least one land grid array package |

| SG130066A1 (en) | 2005-08-26 | 2007-03-20 | Micron Technology Inc | Microelectronic device packages, stacked microelectronic device packages, and methods for manufacturing microelectronic devices |

| JP5522561B2 (ja) * | 2005-08-31 | 2014-06-18 | マイクロン テクノロジー, インク. | マイクロ電子デバイスパッケージ、積重ね型マイクロ電子デバイスパッケージ、およびマイクロ電子デバイスを製造する方法 |

| CN100433327C (zh) * | 2005-09-15 | 2008-11-12 | 南茂科技股份有限公司 | 芯片封装体与堆叠型芯片封装结构 |

| US7652922B2 (en) | 2005-09-30 | 2010-01-26 | Mosaid Technologies Incorporated | Multiple independent serial link memory |

| JP5193045B2 (ja) | 2005-09-30 | 2013-05-08 | モサイド・テクノロジーズ・インコーポレーテッド | 出力制御部を備えたメモリ |

| US20070165457A1 (en) * | 2005-09-30 | 2007-07-19 | Jin-Ki Kim | Nonvolatile memory system |

| JP4930970B2 (ja) * | 2005-11-28 | 2012-05-16 | ルネサスエレクトロニクス株式会社 | マルチチップモジュール |

| US8093717B2 (en) * | 2005-12-09 | 2012-01-10 | Intel Corporation | Microstrip spacer for stacked chip scale packages, methods of making same, methods of operating same, and systems containing same |

| US8258599B2 (en) * | 2005-12-15 | 2012-09-04 | Atmel Corporation | Electronics package with an integrated circuit device having post wafer fabrication integrated passive components |

| US20070138628A1 (en) * | 2005-12-15 | 2007-06-21 | Lam Ken M | Apparatus and method for increasing the quantity of discrete electronic components in an integrated circuit package |

| US8058101B2 (en) | 2005-12-23 | 2011-11-15 | Tessera, Inc. | Microelectronic packages and methods therefor |

| CN100459124C (zh) * | 2005-12-30 | 2009-02-04 | 日月光半导体制造股份有限公司 | 多芯片封装结构 |

| US20070158537A1 (en) * | 2006-01-10 | 2007-07-12 | Nanogate Optoelectronic Robot, Inc. | Package for Image Sensor and Identification Module |

| US7768083B2 (en) | 2006-01-20 | 2010-08-03 | Allegro Microsystems, Inc. | Arrangements for an integrated sensor |

| US20070170599A1 (en) * | 2006-01-24 | 2007-07-26 | Masazumi Amagai | Flip-attached and underfilled stacked semiconductor devices |

| US8120156B2 (en) * | 2006-02-17 | 2012-02-21 | Stats Chippac Ltd. | Integrated circuit package system with die on base package |

| US20080237824A1 (en) * | 2006-02-17 | 2008-10-02 | Amkor Technology, Inc. | Stacked electronic component package having single-sided film spacer |

| US7675180B1 (en) | 2006-02-17 | 2010-03-09 | Amkor Technology, Inc. | Stacked electronic component package having film-on-wire spacer |

| US20070231970A1 (en) * | 2006-03-31 | 2007-10-04 | Tsuyoshi Fukuo | Cured mold compound spacer for stacked-die package |

| TWI296148B (en) * | 2006-04-28 | 2008-04-21 | Advanced Semiconductor Eng | Stackable semiconductor package and the method for making the same |

| US7633144B1 (en) | 2006-05-24 | 2009-12-15 | Amkor Technology, Inc. | Semiconductor package |

| TWI298198B (en) * | 2006-05-30 | 2008-06-21 | Advanced Semiconductor Eng | Stackable semiconductor package |

| TWI339436B (en) * | 2006-05-30 | 2011-03-21 | Advanced Semiconductor Eng | Stackable semiconductor package |

| US7838971B2 (en) * | 2006-07-11 | 2010-11-23 | Atmel Corporation | Method to provide substrate-ground coupling for semiconductor integrated circuit dice constructed from SOI and related materials in stacked-die packages |

| US7932590B2 (en) * | 2006-07-13 | 2011-04-26 | Atmel Corporation | Stacked-die electronics package with planar and three-dimensional inductor elements |

| JP5069879B2 (ja) * | 2006-07-31 | 2012-11-07 | 三洋電機株式会社 | 回路装置 |

| US7687892B2 (en) * | 2006-08-08 | 2010-03-30 | Stats Chippac, Ltd. | Quad flat package |

| TWI317993B (en) * | 2006-08-18 | 2009-12-01 | Advanced Semiconductor Eng | Stackable semiconductor package |

| KR100809701B1 (ko) * | 2006-09-05 | 2008-03-06 | 삼성전자주식회사 | 칩간 열전달 차단 스페이서를 포함하는 멀티칩 패키지 |

| US8269319B2 (en) * | 2006-10-13 | 2012-09-18 | Tessera, Inc. | Collective and synergistic MRAM shields |

| US8154881B2 (en) * | 2006-11-13 | 2012-04-10 | Telecommunication Systems, Inc. | Radiation-shielded semiconductor assembly |

| JP5616636B2 (ja) * | 2006-12-14 | 2014-10-29 | ラムバス・インコーポレーテッド | マルチダイメモリ素子 |

| WO2008074185A1 (en) * | 2006-12-19 | 2008-06-26 | Intel Corporation | Integrated circuit package and its manufacturing method, memory system |

| US7687897B2 (en) * | 2006-12-28 | 2010-03-30 | Stats Chippac Ltd. | Mountable integrated circuit package-in-package system with adhesive spacing structures |

| US7714377B2 (en) * | 2007-04-19 | 2010-05-11 | Qimonda Ag | Integrated circuits and methods of manufacturing thereof |

| US7915667B2 (en) * | 2008-06-11 | 2011-03-29 | Qimonda Ag | Integrated circuits having a contact region and methods for manufacturing the same |

| US7969018B2 (en) * | 2008-07-15 | 2011-06-28 | Infineon Technologies Ag | Stacked semiconductor chips with separate encapsulations |

| KR101007932B1 (ko) * | 2008-07-25 | 2011-01-14 | 세크론 주식회사 | 패턴 위치 결정 방법, 캐비티 위치 결정 방법 및 솔더 범프형성 방법 |

| DE102008054735A1 (de) * | 2008-12-16 | 2010-06-17 | Robert Bosch Gmbh | Leadless-Gehäusepackung |

| US8533853B2 (en) | 2009-06-12 | 2013-09-10 | Telecommunication Systems, Inc. | Location sensitive solid state drive |

| JP2011077108A (ja) * | 2009-09-29 | 2011-04-14 | Elpida Memory Inc | 半導体装置 |

| KR20110074135A (ko) * | 2009-12-24 | 2011-06-30 | 삼성전자주식회사 | 내장 회로 기판을 구비한 시스템 인 패키지 |

| US8482111B2 (en) | 2010-07-19 | 2013-07-09 | Tessera, Inc. | Stackable molded microelectronic packages |

| US9159708B2 (en) | 2010-07-19 | 2015-10-13 | Tessera, Inc. | Stackable molded microelectronic packages with area array unit connectors |

| KR101075241B1 (ko) | 2010-11-15 | 2011-11-01 | 테세라, 인코포레이티드 | 유전체 부재에 단자를 구비하는 마이크로전자 패키지 |

| US20120146206A1 (en) | 2010-12-13 | 2012-06-14 | Tessera Research Llc | Pin attachment |

| US8618659B2 (en) | 2011-05-03 | 2013-12-31 | Tessera, Inc. | Package-on-package assembly with wire bonds to encapsulation surface |

| KR101128063B1 (ko) | 2011-05-03 | 2012-04-23 | 테세라, 인코포레이티드 | 캡슐화 층의 표면에 와이어 본드를 구비하는 패키지 적층형 어셈블리 |

| US9105483B2 (en) | 2011-10-17 | 2015-08-11 | Invensas Corporation | Package-on-package assembly with wire bond vias |

| US8749037B1 (en) * | 2011-10-28 | 2014-06-10 | Altera Corporation | Multi-access memory system and a method to manufacture the system |

| US9502360B2 (en) * | 2012-01-11 | 2016-11-22 | Taiwan Semiconductor Manufacturing Company, Ltd. | Stress compensation layer for 3D packaging |

| US8946757B2 (en) | 2012-02-17 | 2015-02-03 | Invensas Corporation | Heat spreading substrate with embedded interconnects |

| US9349706B2 (en) | 2012-02-24 | 2016-05-24 | Invensas Corporation | Method for package-on-package assembly with wire bonds to encapsulation surface |

| US8372741B1 (en) | 2012-02-24 | 2013-02-12 | Invensas Corporation | Method for package-on-package assembly with wire bonds to encapsulation surface |

| KR20130105175A (ko) * | 2012-03-16 | 2013-09-25 | 삼성전자주식회사 | 보호 층을 갖는 반도체 패키지 및 그 형성 방법 |

| US9768137B2 (en) * | 2012-04-30 | 2017-09-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Stud bump structure for semiconductor package assemblies |

| US8835228B2 (en) | 2012-05-22 | 2014-09-16 | Invensas Corporation | Substrate-less stackable package with wire-bond interconnect |

| US9385006B2 (en) * | 2012-06-21 | 2016-07-05 | STATS ChipPAC Pte. Ltd. | Semiconductor device and method of forming an embedded SOP fan-out package |

| US9391008B2 (en) | 2012-07-31 | 2016-07-12 | Invensas Corporation | Reconstituted wafer-level package DRAM |

| US9502390B2 (en) | 2012-08-03 | 2016-11-22 | Invensas Corporation | BVA interposer |

| US9418971B2 (en) | 2012-11-08 | 2016-08-16 | Taiwan Semiconductor Manufacturing Company, Ltd. | Package-on-package structure including a thermal isolation material and method of forming the same |

| US8975738B2 (en) | 2012-11-12 | 2015-03-10 | Invensas Corporation | Structure for microelectronic packaging with terminals on dielectric mass |

| US8878353B2 (en) | 2012-12-20 | 2014-11-04 | Invensas Corporation | Structure for microelectronic packaging with bond elements to encapsulation surface |

| US9136254B2 (en) | 2013-02-01 | 2015-09-15 | Invensas Corporation | Microelectronic package having wire bond vias and stiffening layer |

| JP6128993B2 (ja) * | 2013-06-28 | 2017-05-17 | キヤノン株式会社 | 積層型半導体装置、プリント回路板、電子機器及び積層型半導体装置の製造方法 |

| US9034696B2 (en) | 2013-07-15 | 2015-05-19 | Invensas Corporation | Microelectronic assemblies having reinforcing collars on connectors extending through encapsulation |

| US8883563B1 (en) | 2013-07-15 | 2014-11-11 | Invensas Corporation | Fabrication of microelectronic assemblies having stack terminals coupled by connectors extending through encapsulation |

| US9023691B2 (en) | 2013-07-15 | 2015-05-05 | Invensas Corporation | Microelectronic assemblies with stack terminals coupled by connectors extending through encapsulation |

| US9167710B2 (en) | 2013-08-07 | 2015-10-20 | Invensas Corporation | Embedded packaging with preformed vias |

| US9685365B2 (en) | 2013-08-08 | 2017-06-20 | Invensas Corporation | Method of forming a wire bond having a free end |

| US20150076714A1 (en) * | 2013-09-16 | 2015-03-19 | Invensas Corporation | Microelectronic element with bond elements to encapsulation surface |

| US9082753B2 (en) | 2013-11-12 | 2015-07-14 | Invensas Corporation | Severing bond wire by kinking and twisting |

| US9087815B2 (en) | 2013-11-12 | 2015-07-21 | Invensas Corporation | Off substrate kinking of bond wire |

| US9583456B2 (en) | 2013-11-22 | 2017-02-28 | Invensas Corporation | Multiple bond via arrays of different wire heights on a same substrate |

| US9263394B2 (en) | 2013-11-22 | 2016-02-16 | Invensas Corporation | Multiple bond via arrays of different wire heights on a same substrate |

| US9379074B2 (en) | 2013-11-22 | 2016-06-28 | Invensas Corporation | Die stacks with one or more bond via arrays of wire bond wires and with one or more arrays of bump interconnects |

| US9735082B2 (en) | 2013-12-04 | 2017-08-15 | Taiwan Semiconductor Manufacturing Company, Ltd. | 3DIC packaging with hot spot thermal management features |

| US9667900B2 (en) * | 2013-12-09 | 2017-05-30 | Optiz, Inc. | Three dimensional system-on-chip image sensor package |

| US9583411B2 (en) | 2014-01-17 | 2017-02-28 | Invensas Corporation | Fine pitch BVA using reconstituted wafer with area array accessible for testing |

| US9214454B2 (en) | 2014-03-31 | 2015-12-15 | Invensas Corporation | Batch process fabrication of package-on-package microelectronic assemblies |

| US10381326B2 (en) | 2014-05-28 | 2019-08-13 | Invensas Corporation | Structure and method for integrated circuits packaging with increased density |

| US9646917B2 (en) | 2014-05-29 | 2017-05-09 | Invensas Corporation | Low CTE component with wire bond interconnects |

| US9412714B2 (en) | 2014-05-30 | 2016-08-09 | Invensas Corporation | Wire bond support structure and microelectronic package including wire bonds therefrom |

| US9899794B2 (en) * | 2014-06-30 | 2018-02-20 | Texas Instruments Incorporated | Optoelectronic package |

| US9627367B2 (en) | 2014-11-21 | 2017-04-18 | Micron Technology, Inc. | Memory devices with controllers under memory packages and associated systems and methods |

| US9735084B2 (en) | 2014-12-11 | 2017-08-15 | Invensas Corporation | Bond via array for thermal conductivity |

| US9888579B2 (en) | 2015-03-05 | 2018-02-06 | Invensas Corporation | Pressing of wire bond wire tips to provide bent-over tips |

| US9502372B1 (en) | 2015-04-30 | 2016-11-22 | Invensas Corporation | Wafer-level packaging using wire bond wires in place of a redistribution layer |

| US9761554B2 (en) | 2015-05-07 | 2017-09-12 | Invensas Corporation | Ball bonding metal wire bond wires to metal pads |

| US9786632B2 (en) * | 2015-07-30 | 2017-10-10 | Mediatek Inc. | Semiconductor package structure and method for forming the same |

| US9490222B1 (en) | 2015-10-12 | 2016-11-08 | Invensas Corporation | Wire bond wires for interference shielding |

| US10490528B2 (en) | 2015-10-12 | 2019-11-26 | Invensas Corporation | Embedded wire bond wires |

| US10332854B2 (en) | 2015-10-23 | 2019-06-25 | Invensas Corporation | Anchoring structure of fine pitch bva |

| US10181457B2 (en) | 2015-10-26 | 2019-01-15 | Invensas Corporation | Microelectronic package for wafer-level chip scale packaging with fan-out |

| US9911718B2 (en) | 2015-11-17 | 2018-03-06 | Invensas Corporation | ‘RDL-First’ packaged microelectronic device for a package-on-package device |

| US9659848B1 (en) | 2015-11-18 | 2017-05-23 | Invensas Corporation | Stiffened wires for offset BVA |

| KR102372300B1 (ko) * | 2015-11-26 | 2022-03-08 | 삼성전자주식회사 | 스택 패키지 및 그 제조 방법 |

| US9984992B2 (en) * | 2015-12-30 | 2018-05-29 | Invensas Corporation | Embedded wire bond wires for vertical integration with separate surface mount and wire bond mounting surfaces |

| US9704819B1 (en) * | 2016-03-29 | 2017-07-11 | Hong Kong Applied Science And Technology Research Institute Co. Ltd. | Three dimensional fully molded power electronics module having a plurality of spacers for high power applications |

| US9935075B2 (en) | 2016-07-29 | 2018-04-03 | Invensas Corporation | Wire bonding method and apparatus for electromagnetic interference shielding |

| US9859255B1 (en) * | 2016-10-01 | 2018-01-02 | Intel Corporation | Electronic device package |

| KR20180055635A (ko) * | 2016-11-14 | 2018-05-25 | 삼성전자주식회사 | 반도체 모듈 |

| US10299368B2 (en) | 2016-12-21 | 2019-05-21 | Invensas Corporation | Surface integrated waveguides and circuit structures therefor |

| US10935612B2 (en) | 2018-08-20 | 2021-03-02 | Allegro Microsystems, Llc | Current sensor having multiple sensitivity ranges |

| JP7094828B2 (ja) * | 2018-08-21 | 2022-07-04 | キヤノン株式会社 | 集積回路装置 |

| US20200402958A1 (en) * | 2019-06-20 | 2020-12-24 | Advanced Semiconductor Engineering, Inc. | Semiconductor device packages and methods of manufacturing the same |

| US11293979B2 (en) | 2019-10-22 | 2022-04-05 | Peter Shun Shen Wang | Method of and an arrangement for analyzing manufacturing defects of multi-chip modules made without known good die |

| CN113539989B (zh) * | 2020-04-13 | 2023-07-21 | 烽火通信科技股份有限公司 | 一种多芯片散热封装结构及封装方法 |

| TWI761864B (zh) * | 2020-06-19 | 2022-04-21 | 海華科技股份有限公司 | 散熱式晶片級封裝結構 |

| US11308257B1 (en) | 2020-12-15 | 2022-04-19 | International Business Machines Corporation | Stacked via rivets in chip hotspots |

| US11567108B2 (en) | 2021-03-31 | 2023-01-31 | Allegro Microsystems, Llc | Multi-gain channels for multi-range sensor |

| TWI765791B (zh) * | 2021-07-30 | 2022-05-21 | 華碩電腦股份有限公司 | 印刷電路板與具有該印刷電路板之電子裝置 |

| TWI843347B (zh) * | 2022-12-20 | 2024-05-21 | 矽品精密工業股份有限公司 | 電子封裝件及其製法 |

Family Cites Families (124)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02312265A (ja) * | 1989-05-26 | 1990-12-27 | Mitsubishi Electric Corp | 半導体装置 |

| US5446620A (en) * | 1990-08-01 | 1995-08-29 | Staktek Corporation | Ultra high density integrated circuit packages |

| FR2670322B1 (fr) * | 1990-12-05 | 1997-07-04 | Matra Espace | Modules de memoire a l'etat solide et dispositifs de memoire comportant de tels modules |

| JPH05152505A (ja) | 1991-11-25 | 1993-06-18 | Fujitsu Ltd | 電子回路実装基板 |

| JPH05160170A (ja) | 1991-12-10 | 1993-06-25 | Fujitsu Ltd | 半導体装置の製造方法及び製造装置 |

| JPH05206365A (ja) | 1992-01-30 | 1993-08-13 | Fuji Electric Co Ltd | 半導体装置およびその組立用リードフレーム |

| US5222014A (en) * | 1992-03-02 | 1993-06-22 | Motorola, Inc. | Three-dimensional multi-chip pad array carrier |

| US5422435A (en) * | 1992-05-22 | 1995-06-06 | National Semiconductor Corporation | Stacked multi-chip modules and method of manufacturing |

| FR2694840B1 (fr) | 1992-08-13 | 1994-09-09 | Commissariat Energie Atomique | Module multi-puces à trois dimensions. |

| US5340771A (en) * | 1993-03-18 | 1994-08-23 | Lsi Logic Corporation | Techniques for providing high I/O count connections to semiconductor dies |

| US5444296A (en) * | 1993-11-22 | 1995-08-22 | Sun Microsystems, Inc. | Ball grid array packages for high speed applications |

| US5675180A (en) * | 1994-06-23 | 1997-10-07 | Cubic Memory, Inc. | Vertical interconnect process for silicon segments |

| US5436203A (en) * | 1994-07-05 | 1995-07-25 | Motorola, Inc. | Shielded liquid encapsulated semiconductor device and method for making the same |

| MY112145A (en) * | 1994-07-11 | 2001-04-30 | Ibm | Direct attachment of heat sink attached directly to flip chip using flexible epoxy |

| US5652185A (en) | 1995-04-07 | 1997-07-29 | National Semiconductor Corporation | Maximized substrate design for grid array based assemblies |

| DE69634376D1 (de) * | 1995-05-12 | 2005-03-31 | St Microelectronics Inc | IC-Packungsfassungssystem mit niedrigem Profil |

| US5719440A (en) * | 1995-12-19 | 1998-02-17 | Micron Technology, Inc. | Flip chip adaptor package for bare die |

| US7166495B2 (en) * | 1996-02-20 | 2007-01-23 | Micron Technology, Inc. | Method of fabricating a multi-die semiconductor package assembly |

| US6075289A (en) * | 1996-10-24 | 2000-06-13 | Tessera, Inc. | Thermally enhanced packaged semiconductor assemblies |

| US5994166A (en) * | 1997-03-10 | 1999-11-30 | Micron Technology, Inc. | Method of constructing stacked packages |

| US5898219A (en) * | 1997-04-02 | 1999-04-27 | Intel Corporation | Custom corner attach heat sink design for a plastic ball grid array integrated circuit package |

| JP2964983B2 (ja) | 1997-04-02 | 1999-10-18 | 日本電気株式会社 | 三次元メモリモジュール及びそれを用いた半導体装置 |

| JPH10294423A (ja) * | 1997-04-17 | 1998-11-04 | Nec Corp | 半導体装置 |

| US5982633A (en) * | 1997-08-20 | 1999-11-09 | Compaq Computer Corporation | Opposed ball grid array mounting |

| JP3834426B2 (ja) * | 1997-09-02 | 2006-10-18 | 沖電気工業株式会社 | 半導体装置 |

| CA2218307C (en) * | 1997-10-10 | 2006-01-03 | Gennum Corporation | Three dimensional packaging configuration for multi-chip module assembly |

| JP3644662B2 (ja) * | 1997-10-29 | 2005-05-11 | 株式会社ルネサステクノロジ | 半導体モジュール |

| JPH11219984A (ja) | 1997-11-06 | 1999-08-10 | Sharp Corp | 半導体装置パッケージおよびその製造方法ならびにそのための回路基板 |

| US5899705A (en) * | 1997-11-20 | 1999-05-04 | Akram; Salman | Stacked leads-over chip multi-chip module |

| JP2000208698A (ja) * | 1999-01-18 | 2000-07-28 | Toshiba Corp | 半導体装置 |

| JP3178405B2 (ja) | 1998-03-05 | 2001-06-18 | 住友金属工業株式会社 | 熱応力を緩和した積層半導体装置モジュール |

| SG75958A1 (en) | 1998-06-01 | 2000-10-24 | Hitachi Ulsi Sys Co Ltd | Semiconductor device and a method of producing semiconductor device |

| US6451624B1 (en) | 1998-06-05 | 2002-09-17 | Micron Technology, Inc. | Stackable semiconductor package having conductive layer and insulating layers and method of fabrication |

| US6034875A (en) * | 1998-06-17 | 2000-03-07 | International Business Machines Corporation | Cooling structure for electronic components |

| US5977640A (en) * | 1998-06-26 | 1999-11-02 | International Business Machines Corporation | Highly integrated chip-on-chip packaging |

| JP3643706B2 (ja) * | 1998-07-31 | 2005-04-27 | 三洋電機株式会社 | 半導体装置 |

| JP2000058691A (ja) | 1998-08-07 | 2000-02-25 | Sharp Corp | ミリ波半導体装置 |

| US6051887A (en) * | 1998-08-28 | 2000-04-18 | Medtronic, Inc. | Semiconductor stacked device for implantable medical apparatus |

| US6201302B1 (en) * | 1998-12-31 | 2001-03-13 | Sampo Semiconductor Corporation | Semiconductor package having multi-dies |

| JP3685947B2 (ja) * | 1999-03-15 | 2005-08-24 | 新光電気工業株式会社 | 半導体装置及びその製造方法 |

| JP4075204B2 (ja) | 1999-04-09 | 2008-04-16 | 松下電器産業株式会社 | 積層型半導体装置 |

| US6118176A (en) * | 1999-04-26 | 2000-09-12 | Advanced Semiconductor Engineering, Inc. | Stacked chip assembly utilizing a lead frame |

| US6890798B2 (en) * | 1999-06-08 | 2005-05-10 | Intel Corporation | Stacked chip packaging |

| US6238949B1 (en) | 1999-06-18 | 2001-05-29 | National Semiconductor Corporation | Method and apparatus for forming a plastic chip on chip package module |

| JP3526788B2 (ja) * | 1999-07-01 | 2004-05-17 | 沖電気工業株式会社 | 半導体装置の製造方法 |

| SG87046A1 (en) * | 1999-08-17 | 2002-03-19 | Micron Technology Inc | Multi-chip module with stacked dice |

| US6424033B1 (en) * | 1999-08-31 | 2002-07-23 | Micron Technology, Inc. | Chip package with grease heat sink and method of making |

| WO2001018864A1 (fr) * | 1999-09-03 | 2001-03-15 | Seiko Epson Corporation | Dispositif a semi-conducteurs, son procede de fabrication, carte de circuit et dispositif electronique |

| JP2001156212A (ja) * | 1999-09-16 | 2001-06-08 | Nec Corp | 樹脂封止型半導体装置及びその製造方法 |

| JP2001094045A (ja) * | 1999-09-22 | 2001-04-06 | Seiko Epson Corp | 半導体装置 |

| JP3415509B2 (ja) | 1999-09-28 | 2003-06-09 | エヌイーシーマイクロシステム株式会社 | 半導体装置 |

| JP3485507B2 (ja) * | 1999-10-25 | 2004-01-13 | 沖電気工業株式会社 | 半導体装置 |

| JP2001127246A (ja) * | 1999-10-29 | 2001-05-11 | Fujitsu Ltd | 半導体装置 |

| US6376904B1 (en) * | 1999-12-23 | 2002-04-23 | Rambus Inc. | Redistributed bond pads in stacked integrated circuit die package |

| JP2001223326A (ja) | 2000-02-09 | 2001-08-17 | Hitachi Ltd | 半導体装置 |

| KR100335717B1 (ko) * | 2000-02-18 | 2002-05-08 | 윤종용 | 고용량 메모리 카드 |

| US6462421B1 (en) * | 2000-04-10 | 2002-10-08 | Advanced Semicondcutor Engineering, Inc. | Multichip module |

| JP2001308262A (ja) * | 2000-04-26 | 2001-11-02 | Mitsubishi Electric Corp | 樹脂封止bga型半導体装置 |

| TW445610B (en) * | 2000-06-16 | 2001-07-11 | Siliconware Precision Industries Co Ltd | Stacked-die packaging structure |

| TW459361B (en) * | 2000-07-17 | 2001-10-11 | Siliconware Precision Industries Co Ltd | Three-dimensional multiple stacked-die packaging structure |

| US6472758B1 (en) | 2000-07-20 | 2002-10-29 | Amkor Technology, Inc. | Semiconductor package including stacked semiconductor dies and bond wires |

| JP2002040095A (ja) * | 2000-07-26 | 2002-02-06 | Nec Corp | 半導体装置及びその実装方法 |

| US6607937B1 (en) * | 2000-08-23 | 2003-08-19 | Micron Technology, Inc. | Stacked microelectronic dies and methods for stacking microelectronic dies |

| US6593648B2 (en) * | 2000-08-31 | 2003-07-15 | Seiko Epson Corporation | Semiconductor device and method of making the same, circuit board and electronic equipment |

| JP4570809B2 (ja) * | 2000-09-04 | 2010-10-27 | 富士通セミコンダクター株式会社 | 積層型半導体装置及びその製造方法 |

| US6492726B1 (en) | 2000-09-22 | 2002-12-10 | Chartered Semiconductor Manufacturing Ltd. | Chip scale packaging with multi-layer flip chip arrangement and ball grid array interconnection |

| JP2002118201A (ja) * | 2000-10-05 | 2002-04-19 | Hitachi Ltd | 半導体装置およびその製造方法 |

| JP3913481B2 (ja) | 2001-01-24 | 2007-05-09 | シャープ株式会社 | 半導体装置および半導体装置の製造方法 |

| TW459363B (en) | 2000-11-22 | 2001-10-11 | Kingpak Tech Inc | Integrated circuit stacking structure and the manufacturing method thereof |

| JP2002170921A (ja) * | 2000-12-01 | 2002-06-14 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| JP3798620B2 (ja) | 2000-12-04 | 2006-07-19 | 富士通株式会社 | 半導体装置の製造方法 |

| US6340846B1 (en) * | 2000-12-06 | 2002-01-22 | Amkor Technology, Inc. | Making semiconductor packages with stacked dies and reinforced wire bonds |

| JP2002176136A (ja) | 2000-12-08 | 2002-06-21 | Mitsubishi Electric Corp | マルチチップパッケージ、半導体及び半導体製造装置 |

| US6777819B2 (en) * | 2000-12-20 | 2004-08-17 | Siliconware Precision Industries Co., Ltd. | Semiconductor package with flash-proof device |

| US6734539B2 (en) * | 2000-12-27 | 2004-05-11 | Lucent Technologies Inc. | Stacked module package |

| JP2002208656A (ja) * | 2001-01-11 | 2002-07-26 | Mitsubishi Electric Corp | 半導体装置 |

| JP2002222903A (ja) | 2001-01-26 | 2002-08-09 | Mitsubishi Electric Corp | 半導体パッケージ及び半導体装置 |

| US6388313B1 (en) * | 2001-01-30 | 2002-05-14 | Siliconware Precision Industries Co., Ltd. | Multi-chip module |

| JP2002231885A (ja) * | 2001-02-06 | 2002-08-16 | Mitsubishi Electric Corp | 半導体装置 |

| JP4780844B2 (ja) * | 2001-03-05 | 2011-09-28 | Okiセミコンダクタ株式会社 | 半導体装置 |

| TW502408B (en) * | 2001-03-09 | 2002-09-11 | Advanced Semiconductor Eng | Chip with chamfer |

| JP2002280516A (ja) * | 2001-03-19 | 2002-09-27 | Toshiba Corp | 半導体モジュール |

| SG108245A1 (en) * | 2001-03-30 | 2005-01-28 | Micron Technology Inc | Ball grid array interposer, packages and methods |

| US6400007B1 (en) * | 2001-04-16 | 2002-06-04 | Kingpak Technology Inc. | Stacked structure of semiconductor means and method for manufacturing the same |

| US6888240B2 (en) | 2001-04-30 | 2005-05-03 | Intel Corporation | High performance, low cost microelectronic circuit package with interposer |

| US6472741B1 (en) * | 2001-07-14 | 2002-10-29 | Siliconware Precision Industries Co., Ltd. | Thermally-enhanced stacked-die ball grid array semiconductor package and method of fabricating the same |

| JP2002373969A (ja) * | 2001-06-15 | 2002-12-26 | Oki Electric Ind Co Ltd | 半導体装置及び半導体装置の製造方法 |

| US6900528B2 (en) * | 2001-06-21 | 2005-05-31 | Micron Technology, Inc. | Stacked mass storage flash memory package |

| US6734552B2 (en) * | 2001-07-11 | 2004-05-11 | Asat Limited | Enhanced thermal dissipation integrated circuit package |

| DE10138278C1 (de) * | 2001-08-10 | 2003-04-03 | Infineon Technologies Ag | Elektronisches Bauteil mit aufeinander gestapelten elektronischen Bauelementen und Verfahren zur Herstellung derselben |

| KR100445073B1 (ko) * | 2001-08-21 | 2004-08-21 | 삼성전자주식회사 | 듀얼 다이 패키지 |

| US6787916B2 (en) * | 2001-09-13 | 2004-09-07 | Tru-Si Technologies, Inc. | Structures having a substrate with a cavity and having an integrated circuit bonded to a contact pad located in the cavity |

| US6847105B2 (en) * | 2001-09-21 | 2005-01-25 | Micron Technology, Inc. | Bumping technology in stacked die configurations |

| US6599779B2 (en) * | 2001-09-24 | 2003-07-29 | St Assembly Test Service Ltd. | PBGA substrate for anchoring heat sink |

| JP4917225B2 (ja) | 2001-09-28 | 2012-04-18 | ローム株式会社 | 半導体装置 |

| TW523887B (en) * | 2001-11-15 | 2003-03-11 | Siliconware Precision Industries Co Ltd | Semiconductor packaged device and its manufacturing method |

| US6737750B1 (en) * | 2001-12-07 | 2004-05-18 | Amkor Technology, Inc. | Structures for improving heat dissipation in stacked semiconductor packages |

| US20030113952A1 (en) * | 2001-12-19 | 2003-06-19 | Mahesh Sambasivam | Underfill materials dispensed in a flip chip package by way of a through hole |

| TW523894B (en) * | 2001-12-24 | 2003-03-11 | Siliconware Precision Industries Co Ltd | Semiconductor device and its manufacturing method |

| JP3865055B2 (ja) | 2001-12-28 | 2007-01-10 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| JP2003273317A (ja) | 2002-03-19 | 2003-09-26 | Nec Electronics Corp | 半導体装置及びその製造方法 |

| JP3688249B2 (ja) | 2002-04-05 | 2005-08-24 | Necエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP3550391B2 (ja) | 2002-05-15 | 2004-08-04 | 沖電気工業株式会社 | 半導体装置及びその製造方法 |

| US6906415B2 (en) * | 2002-06-27 | 2005-06-14 | Micron Technology, Inc. | Semiconductor device assemblies and packages including multiple semiconductor devices and methods |

| US6600222B1 (en) * | 2002-07-17 | 2003-07-29 | Intel Corporation | Stacked microelectronic packages |

| KR100442880B1 (ko) * | 2002-07-24 | 2004-08-02 | 삼성전자주식회사 | 적층형 반도체 모듈 및 그 제조방법 |

| US7132311B2 (en) * | 2002-07-26 | 2006-11-07 | Intel Corporation | Encapsulation of a stack of semiconductor dice |

| US6972481B2 (en) | 2002-09-17 | 2005-12-06 | Chippac, Inc. | Semiconductor multi-package module including stacked-die package and having wire bond interconnect between stacked packages |

| US7053476B2 (en) * | 2002-09-17 | 2006-05-30 | Chippac, Inc. | Semiconductor multi-package module having package stacked over die-down flip chip ball grid array package and having wire bond interconnect between stacked packages |

| US20040061213A1 (en) * | 2002-09-17 | 2004-04-01 | Chippac, Inc. | Semiconductor multi-package module having package stacked over die-up flip chip ball grid array package and having wire bond interconnect between stacked packages |

| US6838761B2 (en) * | 2002-09-17 | 2005-01-04 | Chippac, Inc. | Semiconductor multi-package module having wire bond interconnect between stacked packages and having electrical shield |

| US7064426B2 (en) * | 2002-09-17 | 2006-06-20 | Chippac, Inc. | Semiconductor multi-package module having wire bond interconnect between stacked packages |

| US7034387B2 (en) * | 2003-04-04 | 2006-04-25 | Chippac, Inc. | Semiconductor multipackage module including processor and memory package assemblies |

| KR20050074961A (ko) * | 2002-10-08 | 2005-07-19 | 치팩, 인코포레이티드 | 역전된 제 2 패키지를 구비한 반도체 적층형 멀티-패키지모듈 |

| TW567601B (en) | 2002-10-18 | 2003-12-21 | Siliconware Precision Industries Co Ltd | Module device of stacked semiconductor package and method for fabricating the same |

| SG114585A1 (en) * | 2002-11-22 | 2005-09-28 | Micron Technology Inc | Packaged microelectronic component assemblies |

| TW576549U (en) * | 2003-04-04 | 2004-02-11 | Advanced Semiconductor Eng | Multi-chip package combining wire-bonding and flip-chip configuration |

| TWI225292B (en) | 2003-04-23 | 2004-12-11 | Advanced Semiconductor Eng | Multi-chips stacked package |

| US6818980B1 (en) | 2003-05-07 | 2004-11-16 | Asat Ltd. | Stacked semiconductor package and method of manufacturing the same |

| US7342248B2 (en) * | 2003-05-15 | 2008-03-11 | Shinko Electric Industries Co., Ltd. | Semiconductor device and interposer |

| TWI299551B (en) * | 2003-06-25 | 2008-08-01 | Via Tech Inc | Quad flat no-lead type chip carrier |

| US6930378B1 (en) * | 2003-11-10 | 2005-08-16 | Amkor Technology, Inc. | Stacked semiconductor die assembly having at least one support |

| US20060138631A1 (en) * | 2003-12-31 | 2006-06-29 | Advanced Semiconductor Engineering, Inc. | Multi-chip package structure |

| US20060043556A1 (en) | 2004-08-25 | 2006-03-02 | Chao-Yuan Su | Stacked packaging methods and structures |

-

2004

- 2004-12-16 JP JP2006545467A patent/JP5197961B2/ja active Active

- 2004-12-16 WO PCT/US2004/042413 patent/WO2005059967A2/en active Application Filing

- 2004-12-16 US US11/014,257 patent/US8970049B2/en active Active

- 2004-12-17 TW TW093139543A patent/TWI357663B/zh active

-

2006

- 2006-06-16 KR KR1020067012034A patent/KR101076537B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| US8970049B2 (en) | 2015-03-03 |

| TW200536130A (en) | 2005-11-01 |

| WO2005059967A3 (en) | 2009-06-04 |

| TWI357663B (en) | 2012-02-01 |

| US20050133916A1 (en) | 2005-06-23 |

| WO2005059967A2 (en) | 2005-06-30 |

| KR20070088258A (ko) | 2007-08-29 |

| KR101076537B1 (ko) | 2011-10-24 |

| JP2007516616A (ja) | 2007-06-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5197961B2 (ja) | マルチチップパッケージモジュールおよびその製造方法 | |

| TWI442520B (zh) | 具有晶片尺寸型封裝及第二基底及在上側與下側包含暴露基底表面之半導體組件 | |

| JP4503677B2 (ja) | 上側および下側の基板表面を露出させた半導体パッケージ | |

| TWI331392B (en) | Module having stacked chip scale semiconductor packages | |

| KR101172527B1 (ko) | 상부면 및 하부면에서 노출된 기판 표면들을 갖는 반도체적층 패키지 어셈블리 | |

| US7425758B2 (en) | Metal core foldover package structures | |

| US8927332B2 (en) | Methods of manufacturing semiconductor device assemblies including face-to-face semiconductor dice | |

| TWI393228B (zh) | 覆晶及焊線封裝半導體 | |

| TWI329918B (en) | Semiconductor multi-package module having wire bond interconnection between stacked packages | |

| TW200416787A (en) | Semiconductor stacked multi-package module having inverted second package | |

| US20100314730A1 (en) | Stacked hybrid interposer through silicon via (TSV) package | |

| JP2005535103A (ja) | 半導体パッケージ装置ならびに製作および試験方法 | |

| US20220013471A1 (en) | Ic package | |

| US7235870B2 (en) | Microelectronic multi-chip module | |

| US20060284298A1 (en) | Chip stack package having same length bonding leads | |

| US11227814B2 (en) | Three-dimensional semiconductor package with partially overlapping chips and manufacturing method thereof | |

| US20080237831A1 (en) | Multi-chip semiconductor package structure | |

| TW202213163A (zh) | 半導體結構 | |

| TWI838125B (zh) | 半導體封裝及其製造方法 | |

| JP2001007255A (ja) | 高効率放熱型チップ寸法パッケージ方法及び装置 | |

| TW202435412A (zh) | 半導體封裝及其製造方法 | |

| KR100813621B1 (ko) | 적층형 반도체 소자 패키지 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071114 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080626 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100628 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20100810 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100823 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20100810 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20100823 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101005 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110104 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111220 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120828 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20121127 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121204 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20121204 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130115 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130206 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5197961 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |