JP4906135B2 - Memory card - Google Patents

Memory card Download PDFInfo

- Publication number

- JP4906135B2 JP4906135B2 JP2009242129A JP2009242129A JP4906135B2 JP 4906135 B2 JP4906135 B2 JP 4906135B2 JP 2009242129 A JP2009242129 A JP 2009242129A JP 2009242129 A JP2009242129 A JP 2009242129A JP 4906135 B2 JP4906135 B2 JP 4906135B2

- Authority

- JP

- Japan

- Prior art keywords

- external connection

- card

- connection terminal

- memory

- interface

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Credit Cards Or The Like (AREA)

Description

本発明は、インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載したメモリカードに関する。 The present invention relates to a memory card on which a security controller is mounted together with an interface controller and a memory.

特許文献1にはMMC(マルチメディアカード:登録商標)規格との互換性を維持しながらマルチバンクやマルチファンクションを実現するために、MMC規格に準拠のメモリカードにSIM(Subscriber Identity Module)を搭載してセキュリティの強化を図るようにした技術が記載される。

In

特許文献2には、フラッシュメモリチップとセキュリティー処理を実行するICカードチップと、外部からの指示に従ってそれらを制御するコントローラチップを実装した記憶装置について記載がある。

また非特許文献1はマルチメディアカードの規格が記載される。

Non-Patent

本発明者は、インタフェースコントローラ及びメモリと共にICカード用マイクロコンピュータのようなセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードについて検討した。 The present inventor studied a memory card that implements a multifunction by installing a security controller such as an IC card microcomputer together with an interface controller and a memory.

第1は、インタフェースコントローラとセキュリティコントローラが接続されているとき、外部から供給された動作電源電圧を、インタフェースコントローラ及びメモリのための動作電源電圧の供給を停止し、セキュリティコントローラだけに動作電源電圧を供給可能な場合に、セキュリティコントローラだけに動作電源を投入して専らセキュリティー処理を実行させるというような動作形態において不都合の有ることが明らかにされた。即ち、インタフェースコントローラに動作電源が投入されていないと、前記セキュリティーコントローラに接続する前記インタフェースコントローラのインタフェース部において出力バッファの出力制御状態が不定になって低インピーダンス状態にされている場合が有り、このような状態でセキュリティーコントローラのパワーオンリセット若しくは起動のためのクロックや信号が外部から供給されると、そのクロックや信号が低インピーダンス状態の前記インタフェース部に流れ込んで、無視し得ないノイズになったり誤動作を生ずる虞のあることが見出された。特にセキュリティーコントローラ等が外部と非接触でインタフェースするような場合には通信感度を著しく低下されることが懸念される。 First, when the interface controller and the security controller are connected, the operation power supply voltage supplied from the outside is stopped, the supply of the operation power supply voltage for the interface controller and the memory is stopped, and the operation power supply voltage is supplied only to the security controller. It has been clarified that there is an inconvenience in the operation mode in which only the security controller is turned on and the security processing is executed exclusively when it can be supplied. That is, if the operating power is not turned on to the interface controller, the output control state of the output buffer in the interface unit of the interface controller connected to the security controller may be indefinite and in a low impedance state. When a clock or signal for power-on reset or activation of the security controller is supplied from the outside in such a state, the clock or signal flows into the interface section in a low impedance state, resulting in noise that cannot be ignored. It has been found that there is a risk of malfunction. In particular, when the security controller or the like interfaces with the outside in a non-contact manner, there is a concern that the communication sensitivity may be significantly reduced.

第2は、前記セキュリティーコントローラが非接触インタフェース機能を有するとき、カードの配線基板に通信感度向上のための外部アンテナの接続端子を設ける場合に、信号やクロック等その他の接続端子との配置関係を考慮することの重要性が本発明者によって見出された。即ち、配線基板上で信号やクロック等の接続端子に至る配線の引き回しと、外部アンテナの接続端子に至る配線の引き回しとが錯綜して相互に近接したり跨いだりすることが多くなると、クロストークや誘導等によって信号線やクロック配線にノイズが重畳される。若しくは信号線やクロック配線からのクロストークや誘導等によるノイズが、外部高周波アンテナから受信される高周波信号に重畳され、非接触動作時の入出力データに誤りを生じ得る。外部アンテナの接続端子に対してはそのようなノイズの発生を極力抑えることができるような配置を採用することが必要になる。さらに、インタフェースコントローラ及びメモリのための動作電源電圧の供給を停止し、セキュリティコントローラに動作電源電圧を供給可能な場合に、インタフェースコントローラの動作電源電圧レベルよりセキュリティコントローラの動作電源電圧レベルが高い場合には、高いレベルの動作電源を供給する外部接続端子の配置についても上記同様の考慮が必要になる。 Second, when the security controller has a non-contact interface function, when the connection terminal of the external antenna for improving the communication sensitivity is provided on the wiring board of the card, the arrangement relationship with other connection terminals such as a signal and a clock is changed. The importance of consideration has been found by the inventors. In other words, if the routing of wiring to the connection terminals such as signals and clocks on the wiring board and the routing of wiring to the connection terminals of the external antenna are often complicated, the crosstalk will increase. Noise is superimposed on the signal line and the clock wiring by induction or induction. Alternatively, noise due to crosstalk or induction from the signal line or the clock wiring is superimposed on the high-frequency signal received from the external high-frequency antenna, and an error may occur in the input / output data during the non-contact operation. It is necessary to adopt an arrangement that can suppress the generation of such noise as much as possible for the connection terminal of the external antenna. Furthermore, when the operation power supply voltage level of the security controller is higher than the operation power supply voltage level of the interface controller when the supply of the operation power supply voltage for the interface controller and the memory is stopped and the operation power supply voltage can be supplied to the security controller Therefore, the same consideration as described above is required for the arrangement of the external connection terminals for supplying high-level operation power.

本発明の目的は、インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードにおけるノイズの発生を抑制することにある。 An object of the present invention is to suppress the occurrence of noise in a memory card that implements a multifunction by mounting a security controller together with an interface controller and a memory.

本発明の目的は、インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードにおいて、セキュリティコントローラだけに動作電源を投入してセキュリティー処理を実行させる動作形態におけるノイズの発生を抑制することにある。 An object of the present invention is to suppress the generation of noise in an operation mode in which an operation power is turned on only for a security controller and a security process is executed in a memory card that implements a multifunction by installing a security controller together with an interface controller and a memory. There is.

またインタフェースコントローラとセキュリティコントローラの動作電源を分離することにより、メモリカード全体としての消費電力を低減することにある。 Another object is to reduce the power consumption of the entire memory card by separating the operating power of the interface controller and the security controller.

本発明の別の目的は、インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードにおいて、非接触インタフェース機能を有する前記セキュリティーコントローラに外部アンテナを接続するための接続端子の配置が他の接続端子との関係でノイズの発生を助長しないようにすることにある。 Another object of the present invention is to arrange a connection terminal for connecting an external antenna to the security controller having a non-contact interface function in a memory card that realizes multi-function by mounting a security controller together with an interface controller and a memory. The purpose is to prevent the generation of noise in relation to other connection terminals.

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。 The above and other objects and novel features of the present invention will be apparent from the description of this specification and the accompanying drawings.

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば下記の通りである。 The following is a brief description of an outline of typical inventions disclosed in the present application.

〔1〕本発明に係るメモリカードは、複数の外部接続端子が形成された配線基板に、前記外部接続端子に接続されたインタフェースコントローラ(7)と、前記インタフェースコントローラに接続されたメモリ(8)と、前記インタフェースコントローラに接続されたセキュリティコントローラ(9)とが搭載され、前記インタフェースコントローラ及びメモリに動作電源を供給する第1の外部接続端子(C4)とは別に前記セキュリティーコントローラに動作電源を供給可能な第2の外部接続端子(C15)を有し、前記セキュリティーコントローラに接続する前記インタフェースコントローラのインタフェース部は前記第2の外部接続端子から動作電源を受け前記第1の外部接続端子からの動作電源供給が停止可能にされる。 [1] A memory card according to the present invention includes an interface controller (7) connected to the external connection terminal on a wiring board on which a plurality of external connection terminals are formed, and a memory (8) connected to the interface controller. And a security controller (9) connected to the interface controller, and supply operating power to the security controller separately from the first external connection terminal (C4) that supplies operating power to the interface controller and memory. An interface unit of the interface controller that has a second external connection terminal (C15) that can be connected to the security controller receives an operation power from the second external connection terminal, and operates from the first external connection terminal. The power supply can be stopped.

インタフェースコントローラへの動作電源の供給が断たれてもそのインタフェース部(11)にはセキュリティーコントローラへの動作電源が供給されるから、インタフェース部の出力が不定状態にならず、そこに不定な電流が流れてノイズになることを抑制することができる。インタフェース部に無駄な電流が全く流れないようにするには、前記インタフェース部は前記第1の外部接続端子からの動作電源供給が停止された状態において高インピーダンス状態に制御されればよい。 Even if the operation power supply to the interface controller is cut off, the interface section (11) is supplied with the operation power to the security controller, so the output of the interface section does not become indefinite, and an indefinite current flows there. It can suppress flowing and becoming noise. In order to prevent any unnecessary current from flowing through the interface unit, the interface unit may be controlled to a high impedance state in a state where the operation power supply from the first external connection terminal is stopped.

本発明の具体的な形態では、前記インタフェース部は前記第1の外部接続端子に供給される第1電源電圧による信号レベルと前記第2の外部接続端子に供給される第2電源電圧による信号レベルとの間のレベルシフトを行なうレベルシフト機能を有する。 In a specific form of the present invention, the interface unit has a signal level based on a first power supply voltage supplied to the first external connection terminal and a signal level based on a second power supply voltage supplied to the second external connection terminal. Level shift function for performing level shift between the two.

本発明の具体的な形態では、前記セキュリティーコントローラのインタフェース端子として、クロック信号を入力する第3の外部接続端子(C11)、データ入出力用の第4の外部接続端子(C13)、リセット信号入力用の第5の外部接続端子(C10)を有する。このとき、前記第3の外部接続端子乃至第5の外部接続端子は、前記インタフェースコントローラが認識するカードモードに応じてインタフェースコントローラが入出力信号用の外部接続端子として利用可能である。例えば並列データ入出力ビット数が相違する幾つかのカードモードに対応することができる。前記インタフェースコントローラが第3の外部接続端子乃至第5の外部接続端子をデータ入出力用の外部接続端子として利用するとき、セキュリティーコントローラはインタフェースコントローラ経由で外部とのインタフェースを行なうことができる。このとき、前記第3の外部接続端子乃至第5の外部接続端子を分離スイッチ回路(12)にてインタフェースコントローラから切り離しておけば、前記第3の外部接続端子乃至第5の外部接続端子に接続する外部回路に、セキュリティーコントローラのインタフェース機能に従ってインタフェースコントローラとの間でやり取りされる信号が不所望に外部に出力されるのを抑制することができる。 In a specific form of the present invention, as an interface terminal of the security controller, a third external connection terminal (C11) for inputting a clock signal, a fourth external connection terminal (C13) for data input / output, and a reset signal input 5th external connection terminal (C10). At this time, the third external connection terminal to the fifth external connection terminal can be used by the interface controller as external connection terminals for input / output signals according to the card mode recognized by the interface controller. For example, it is possible to cope with several card modes having different numbers of parallel data input / output bits. When the interface controller uses the third external connection terminal to the fifth external connection terminal as data input / output external connection terminals, the security controller can interface with the outside via the interface controller. At this time, if the third external connection terminal to the fifth external connection terminal are separated from the interface controller by the separation switch circuit (12), they are connected to the third external connection terminal to the fifth external connection terminal. Thus, it is possible to suppress an undesired output of a signal exchanged with the interface controller according to the interface function of the security controller to the external circuit.

本発明の具体的な形態として、前記セキュリティーコントローラは、外部と非接触インタフェースが可能なICカード用マイクロコンピュータ及び外部と接触インタフェースが可能なICカード用マイクロコンピュータの双方又は何れか一方であってよい。また、前記セキュリティーコントローラは、外部と非接触インタフェースと接触インタフェースの双方が可能なICカード用マイクロコンピュータであってよい。 As a specific form of the present invention, the security controller may be an IC card microcomputer capable of a non-contact interface with the outside and / or an IC card microcomputer capable of a contact interface with the outside. . Further, the security controller may be an IC card microcomputer capable of both a non-contact interface and a contact interface.

本発明の具体的な形態として、前記セキュリティーコントローラが外部と非接触インタフェースが可能なICカード用マイクロコンピュータであるとき、前記外部接続端子として非接触インタフェースのための高周波アンテナを接続可能なアンテナ接続端子(C14,C16)を有する場合、前記アンテナ接続端子は前記第2の外部接続端子に隣接して前記第1の外部接続端子の近傍に配置されることが望ましい。そのようなアンテナ接続端子は非接触インタフェースの感度を上げるための外部高周波アンテナの接続に用いられる。アンテナ接続端子に印加される電圧は比較的高く周波数も高い。従って、配線基板上で信号やクロック等の接続端子に至る配線の引き回しと、外部アンテナの接続端子に至る配線の引き回しとが錯綜して相互に近接したり跨いだりすることが多くなると、クロストークや誘導等によって信号線やクロック配線にノイズが重畳される。若しくは信号線やクロック配線からのクロストークや誘導等によるノイズが、外部高周波アンテナから受信される高周波信号に重畳され、非接触動作時の入出力データに誤りを生じ得る。前記アンテナ接続端子は前記第2の外部接続端子に隣接して前記第1の外部接続端子の近傍に配置されるから、その配置はノイズの発生を極力抑えるのに好適な配置となる。 As a specific form of the present invention, when the security controller is a microcomputer for an IC card capable of non-contact interface with the outside, an antenna connection terminal capable of connecting a high-frequency antenna for non-contact interface as the external connection terminal In the case of having (C14, C16), it is desirable that the antenna connection terminal is disposed adjacent to the second external connection terminal and in the vicinity of the first external connection terminal. Such an antenna connection terminal is used for connection of an external high-frequency antenna for increasing the sensitivity of the non-contact interface. The voltage applied to the antenna connection terminal is relatively high and the frequency is high. Therefore, if the routing of wiring to the connection terminals such as signals and clocks on the wiring board and the routing of wiring to the connection terminals of the external antenna are complicated, crosstalk will increase. Noise is superimposed on the signal line and the clock wiring by induction or induction. Alternatively, noise due to crosstalk or induction from the signal line or the clock wiring is superimposed on the high-frequency signal received from the external high-frequency antenna, and an error may occur in the input / output data during the non-contact operation. Since the antenna connection terminal is arranged adjacent to the second external connection terminal and in the vicinity of the first external connection terminal, the arrangement is suitable for suppressing noise generation as much as possible.

前記複数個の外部接続端子は、メモリカードの挿入方向の前後に隣合う列相互間で列方向の配置がずらされた千鳥状の配置を有する。この千鳥状配置により、メモリカードが着脱されるカードスロットには、その多数のスロット端子を交互に突出量を変えて並列配置するという比較的簡単に構成によって多端子化に対応することができる。例えば、メモリカードの挿入方向前後に隣合う後側の配列に、前記第2の外部接続端子乃至第5の外部接続端子と前記アンテナ接続端子を有する。特に、前記第2の外部接続端子及び前記アンテナ接続端子は列方向配置の中央部に位置すればよい。前記第2の外部接続端子は前記アンテナ接続端子に対して千鳥状配置とすればよい。 The plurality of external connection terminals have a staggered arrangement in which the arrangement in the column direction is shifted between adjacent columns before and after the insertion direction of the memory card. With this staggered arrangement, it is possible to cope with the increase in the number of terminals by a relatively simple configuration in which a large number of slot terminals are alternately arranged in parallel in card slots from which memory cards are attached and detached. For example, the second external connection terminal to the fifth external connection terminal and the antenna connection terminal are arranged in a rear array adjacent to the memory card in the insertion direction. In particular, the second external connection terminal and the antenna connection terminal may be located at the center of the column direction arrangement. The second external connection terminals may be staggered with respect to the antenna connection terminals.

本発明の更に別の具体的な形態として、前記インタフェースコントローラ、メモリ及びセキュリティーコントローラが夫々個別の半導体チップであるとき、メモリを構成する半導体チップの上にインタフェースコントローラを構成する半導体チップを積層し、それら半導体チップの同じ向きの辺に沿って配置された電極パッドに配線基板の電極をワイヤボンディングするのがよい。ボンディングワイヤを短くでき、ワイヤの干渉も少なくなる。 As yet another specific form of the present invention, when the interface controller, the memory and the security controller are individual semiconductor chips, the semiconductor chip constituting the interface controller is stacked on the semiconductor chip constituting the memory, It is preferable to wire bond the electrodes of the wiring board to the electrode pads arranged along the sides in the same direction of the semiconductor chips. Bonding wires can be shortened and wire interference is reduced.

〔2〕本発明に係るメモリカードは、複数の外部接続端子が形成された配線基板に、前記外部接続端子に接続されたインタフェースコントローラと、前記インタフェースコントローラに接続されたメモリと、セキュリティコントローラとが搭載され、前記インタフェースコントローラ及びメモリに動作電源を供給する第1の外部接続端子とは別に前記セキュリティーコントローラに動作電源を供給可能な第2の外部接続端子を有し、前記セキュリティーコントローラは、外部と非接触インタフェースが可能なICカード用マイクロコンピュータであって、前記外部接続端子として非接触インタフェースのためのアンテナを接続可能なアンテナ接続端子を有し、前記アンテナ接続端子は前記第2の外部接続端子に隣接して前記第1の外部接続端子の近傍に配置される。 [2] A memory card according to the present invention includes a wiring board on which a plurality of external connection terminals are formed, an interface controller connected to the external connection terminals, a memory connected to the interface controller, and a security controller. And a second external connection terminal capable of supplying operating power to the security controller separately from the first external connection terminal that is mounted and supplies operating power to the interface controller and the memory. An IC card microcomputer capable of a non-contact interface, wherein the external connection terminal has an antenna connection terminal to which an antenna for a non-contact interface can be connected, and the antenna connection terminal is the second external connection terminal Adjacent to the first external connection end It is disposed in the vicinity of.

前記複数個の外部接続端子は、メモリカードの挿入方向の前後に隣合う列相互間で列方向の配置がずらされた千鳥状の配置を有する。この千鳥状配置により、カードスロットには、その多数のスロット端子を交互に突出量を変えて並列配置するという比較的簡単に構成によって多端子化に対応することができる。例えば、メモリカードの挿入方向前後に隣合う後側の配列に、前記第2の外部接続端子乃至第5の外部接続端子と前記アンテナ接続端子を有する。特に、前記第2の外部接続端子及び前記アンテナ接続端子は列方向配置の中央部に位置すればよい。前記第2の外部接続端子は前記アンテナ接続端子に対して千鳥状配置とすればよい。 The plurality of external connection terminals have a staggered arrangement in which the arrangement in the column direction is shifted between adjacent columns before and after the insertion direction of the memory card. Due to this staggered arrangement, the card slot can be made multi-terminal with a relatively simple configuration in which a large number of slot terminals are alternately arranged in parallel with different projection amounts. For example, the second external connection terminal to the fifth external connection terminal and the antenna connection terminal are arranged in a rear array adjacent to the memory card in the insertion direction. In particular, the second external connection terminal and the antenna connection terminal may be located at the center of the column direction arrangement. The second external connection terminals may be staggered with respect to the antenna connection terminals.

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。 The effects obtained by the representative ones of the inventions disclosed in the present application will be briefly described as follows.

インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードにおいて、セキュリティコントローラだけに動作電源を投入してセキュリティー処理を実行させる動作形態におけるノイズの発生を抑制することができる。 In a memory card that implements a multifunction by installing a security controller together with an interface controller and a memory, it is possible to suppress the occurrence of noise in an operation mode in which only the security controller is turned on to perform security processing.

インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードにおいて、非接触インタフェース機能を有する前記セキュリティーコントローラに外部アンテナを接続するための接続端子の配置が他の接続端子との関係でノイズの発生を助長しないようにすることができる。 In a memory card that realizes multi-function by installing a security controller together with an interface controller and memory, the arrangement of connection terminals for connecting an external antenna to the security controller having a non-contact interface function is related to other connection terminals. It is possible to prevent the generation of noise.

インタフェースコントローラ及びメモリと共にセキュリティコントローラを搭載してマルチファンクションを実現するメモリカードにおけるノイズの発生を抑制することができる。 It is possible to suppress the generation of noise in a memory card that implements a multifunction by installing a security controller together with an interface controller and a memory.

《通信携帯端末装置》

図2には本発明の一例に係るメモリカードを適用した携帯電話機などの通信携帯端末装置の概略が示される。通信携帯端末装置1は例えばシステム全体の制御を行うマイクロプロセッサ(MPU)2と、移動体通信のために変調及び復調などのベースバンド処理を行うベースバンド処理部(BB)3、規定の高周波による送受信を行う高周波部(RFcl)4、及びメモリカード(MRYC)5を有する。MRYC5は通信携帯端末装置1の図示を省略するカードスロットに着脱可能にされる。MPU2はMRYC5にとってカードホストとして位置付けられる。

《Communication portable terminal device》

FIG. 2 shows an outline of a communication portable terminal device such as a cellular phone to which a memory card according to an example of the present invention is applied. The communication portable

MRYC5は、例えば、メモリ記憶機能、E−コマースなどに対する高レベルのセキュリティー処理機能、交通機関における課金等のための低レベルのセキュリティー処理機能、コンテンツデータの暗号化・復号処理機能等のマルチファンクションを提供する。 MRYC5 has multi-functions such as memory storage function, high-level security processing function for e-commerce, low-level security processing function for charging in transportation, etc., content data encryption / decryption processing function, etc. provide.

《ICカードマイコン内蔵MRYC》

図1にはMRYC5の構成が例示される。MFMC5は、複数個の外部接続端子C1〜C16が形成された配線基板に、インタフェースコントローラ7と、前記インタフェースコントローラ7に接続されたフラッシュメモリ8と、前記インタフェースコントローラ7に接続されたセキュリティコントローラとしてのIC(インテグレーテッド・サーキット)カード用マイクロコンピュータ(ICカードマイコンとも称する)9が搭載される。前記インタフェースコントローラ7、フラッシュメモリ8、及びICカードマイコン9は夫々個別の半導体集積回路チップで構成されている。

<< MRYC with built-in IC card microcomputer >>

FIG. 1 illustrates the configuration of MRYC5. The

インタフェースコントローラ7は、メモリカードとしての外部インタフェース機能、フラッシュメモリの仕様に応じたメモリインタフェース機能、そしてメモリカードコマンドを用いてICカードマイコンとインタフェースするICカードマイコンインタフェース機能を持つ。ここで、MRYC5はマルチメディアカード規格準拠のメモリカードとしての外部インタフェー仕様を満足するものとされる。

The

フラッシュメモリ8は電気的に消去及び書き込み可能な不揮発性メモリである。フラッシュメモリ8は、特に図示はしないが、電気的に消去及び書き込み可能な不揮発性メモリセルトランジスタ(フラッシュメモリセルとも記す)を有する。フラッシュメモリセルは、特に図示はしないが、フローティングゲートを有する所謂スタックドゲート構造、或いはONO(オキサイド・ナイトライド・オキサイド)ゲート絶縁膜を備えたメモリトランジスタ部と選択トランジスタ部から成る所謂スプリットゲート構造を有する。前記フラッシュメモリセルは、前記フローティングゲート等に電子が注入されると閾値電圧が上昇し、また、前記フローティングゲート等から電子を引き抜くと閾値電圧が低下する。前記フラッシュメモリセルは、データ読み出しのためのワード線電圧に対する閾値電圧の高低に応じた情報を記憶することになる。特に制限されないが、本明細書においてメモリセルトランジスタの閾値電圧が低い状態を消去状態、高い状態を書き込み状態と称する。

The

ICカードマイコン9は、特に図示はしないがCPUとその動作プログラムおよび認証に利用する制御情報など保有する不揮発性メモリを備え、その動作プログラムに従って認証処理などを行う。ここではICカードマイコン9は外部と接触インタインタフェースと非接触インタフェースが可能な接触・非接触デュアルウェイのICカードとされる。接触インタフェースは1ビットのデータ入出力端子I/O、クロック端子CLK、リセット端子RESを用いたシリアル通信で行われる。非接触インタフェースは端子TML1,TML2に接続するアンテナを用いた高周波通信で行われる。図には外部アンテナ10と同調コンデンサ13が代表的に示されている。特に図示はしないが、非接触インタフェースは端子TML1,TML2に接続する内部アンテナをMRYC5のパッケージ内部若しくは回路基板上に設け、端子C14,C16に外部アンテナ10を接続した時に内部アンテナをスイッチで切り離し可能にする構成を備えもよい。

Although not shown in particular, the

前記外部接続端子C1〜C16の内、C1〜C7の機能と配置はMMC規格に準拠し、C8〜C13は多ビットのデータバスに対応する。C14〜C16は新設である。 Among the external connection terminals C1 to C16, functions and arrangement of C1 to C7 conform to the MMC standard, and C8 to C13 correspond to a multi-bit data bus. C14 to C16 are newly established.

図3にはMRYC5のカードモードに応じた外部接続端子C1〜C16の機能割り当てが示される。1ビットモード、4ビットモード、8ビットモードはMRYC5の外部に対するデータ入出力ビット数を意味する。非接触カード機能のみとは外部インタフェース機能として非接触インタフェース機能だけしか持たないICカードマイコンを搭載した場合を意味し、この例については後でその詳細を説明する。図において、RSV(for MMC)はMMCモードにおけるリザーブ端子、CS(for SPI)はSPIモードにおけるチップセレクト端子、CMDはコマンド端子、Vss1,Vss2は回路の接地端子、Vddは電源端子、CLKはメモリカードのクロック端子、DATはシリアルデータ入出力端子、RES−icはICカードマイコンのリセット端子、CLK−icはICカードマイコンのクロック端子、Vcc−icはICカードマイコンの電源端子、LA,LBはアンテナ接続端子、Vcc−ICはICカードマイコンへの専用電源端子、DAT0〜DAT7は並列データ入出力端を意味する。 FIG. 3 shows the function assignment of the external connection terminals C1 to C16 according to the card mode of MRYC5. The 1-bit mode, 4-bit mode, and 8-bit mode mean the number of data input / output bits with respect to the outside of MRYC5. Only the non-contact card function means a case where an IC card microcomputer having only a non-contact interface function is mounted as an external interface function, and details of this example will be described later. In the figure, RSV (for MMC) is a reserve terminal in MMC mode, CS (for SPI) is a chip select terminal in SPI mode, CMD is a command terminal, Vss1 and Vss2 are circuit ground terminals, Vdd is a power supply terminal, and CLK is a memory. Card clock terminal, DAT is serial data input / output terminal, RES-ic is IC card microcomputer reset terminal, CLK-ic is IC card microcomputer clock terminal, Vcc-ic is IC card microcomputer power supply terminal, LA and LB are An antenna connection terminal, Vcc-IC is a dedicated power supply terminal for the IC card microcomputer, and DAT0 to DAT7 are parallel data input / output terminals.

図3から明らかなように、基本的に、C1〜C9がメモリカードインタフェース機能に、C10〜C16がICカードインタフェース機能に割り当てられる。ただし、C10〜C13は、1ビットモードと4ビットモードではICカードインタフェース機能に割り当てられるが、8ビットモードではDAT4〜DAT7の並列データ入出力端子としてメモリカードインタフェース機能に割り当てられる。この端子C10〜C13の機能割り当ての相違は、図1の回路では、インタフェースコントローラ7とICカードマイコン9を接続する配線L1〜L4として現れる。要するに、インタフェースコントローラ7のインタフェース部11において外部接続端子C10〜C13との接続に割り当てられる配線L1〜L4はICカードマイコン9の端子Vcc、I/O−ic、CLK−ic、RES−icに接続する。分離スイッチ回路12は、8ビットモードにおいて、インタフェースコントローラ7がICカードマイコン9と通信を行うときインタフェースコントローラ7の制御によりカット・オフされて外部接続端子C10、C11、C13との接続を分離し、且つインタフェースコントローラ7がC12をDAT6として外部と通信を行うときICカードマイコン9の端子Vccとの接続を分離し、8ビットモードで外部接続端子C10〜C13に割り当てられるデータ端子DAT4〜DAT7の機能と配線L1〜L4に接続される端子Vcc、I/O、CLK、RESの機能との相違による選択をMRYC5側で行う。

As is apparent from FIG. 3, C1 to C9 are basically assigned to the memory card interface function, and C10 to C16 are assigned to the IC card interface function. However, although C10 to C13 are assigned to the IC card interface function in the 1-bit mode and the 4-bit mode, they are assigned to the memory card interface function as parallel data input / output terminals of DAT4 to DAT7 in the 8-bit mode. The difference in function assignment of the terminals C10 to C13 appears as wirings L1 to L4 connecting the

ここで図1を参照してICカードマイコン9に対する動作電源の供給について説明する。前記インタフェースコントローラ7及びフラッシュメモリ8に動作電源Vddを供給する外部接続端子(第1の外部接続端子)C4とは別に前記ICカードマイコン9に動作電源Vcc−ICを供給可能な外部接続端端子(第2の外部接続端子)C15を有している。ICカードマイコン9に対する動作電源の供給は、図1の構成ではC12,C15が行なうが、C12による動作電源の供給は本質的ではない。C15で代替可能である。尚、分離スイッチ回路12のスイッチSW1は端子C15を追加したことによって必要になったスイッチである。即ち、C12の利用形態の如何に拘わらず配線L4にはC15からVcc−ICが常時供給されることになるからである。

Here, the operation power supply to the

端子C15はインタフェース部11にも動作電源を供給し、C4からの動作電源Vddの供給停止状態において、配線L1〜L4に接続するインタフェース部11における入出力回路の入力インピーダンスの低下や出力不定状態を解消する。即ち、MRYC5のICカードマイコン9だけを動作させるような場合に無駄な電力消費を抑えるためにC4からの電源Vddの供給を止めたとき、インタフェース部11における出力バッファの出力状態が不定になると、この状態で、C10〜C13を使った接触インタフェースでICカードマイコン9のパワーオンリセットを行なってICカードマイコンを動作させたとき、例えばC11からのクロック信号がインタフェース部11の出力バッファに流入して過電流が流れたり、C13を介して入出力される信号が同じくインタフェース部11の出力バッファに流入して過電流が流れたりする。このような過電流はノイズとなり、また無駄な電力消費を増大させる。更にそのようなノイズは、アンテナ10を介する非接触インタフェースにおける感度や通信特性を低下させる。インタフェースコントローラ7への動作電源Vddの供給停止時にインタフェース部11にC15からICカードマイコン9用に動作電源Vcc−ICを供給することによって配線L1〜L4に接続するインタフェース部11の出力バッファの出力不定状態を解消する。

The terminal C15 also supplies operating power to the

上記不定状態の解消には、例えば、電源Vdd供給停止に応答して配線L1〜L4に接続する出力バッファを高インピーダンス状態に制御する。 In order to eliminate the indefinite state, for example, the output buffer connected to the wirings L1 to L4 is controlled to be in a high impedance state in response to the supply stop of the power supply Vdd.

図4には電源Vdd供給停止に応答して高インピーダンス状態に制御可能な出力バッファが例示される。出力バッファ15は、例えばVddを動作電源とするCMOSインバータ16とVcc−ICを動作電源とするCMOSクロックドインバータ17の直列回路を有する。CMOSクロックドインバータ17は、pチャネル型MOSトランジスタQp1,Qp2とnチャネル型MOSトランジスタQn3、Qn4の直列回路を主体に、MOSトランジスタQp1,Qn4をスイッチ制御するインバータ18と電源電圧ディテクタ19を有する。電源電圧ディテクタ19は電源電圧Vddが投入されて動作保証電圧を超えたときVcc−ICレベルのハイレベル、電源電圧Vdd供給が遮断されたとき回路の接地電圧Vssであるローレベルにされる検出信号20を出力する。インバータ18はVcc−ICを動作電源とする。これにより、Vcc−ICが投入されている状態で、Vddが供給されているときクロックドインバータ17は出力動作可能にされ、Vddの供給が遮断されるとクロックドインバータ17は高インピーダンス状態に制御される。尚、クロックドインバータ17の電源に高抵抗R1を介して電源Vddが接続されているのはVcc−ICが遮断されたときの動作安定化のためである。

FIG. 4 illustrates an output buffer that can be controlled to a high impedance state in response to the stop of the supply of the power supply Vdd. The

図4でVddとVcc−ICのレベルが相違し、Vdd≦Vcc−ICであることを考慮している。即ち、インバータ16の論理閾値電圧(VTL)をVdd/2とすると、クロックドインバータ17の論理閾値電圧もこれに合わせてVdd/2とされる。要するに、出力バッファ15は電源電圧Vddによる信号ベルトと前記電源電圧Vcc−ICによる信号レベルとの間のレベルシフトを行なうレベルシフト機能を有する。

In FIG. 4, it is considered that the levels of Vdd and Vcc-IC are different and Vdd ≦ Vcc-IC. That is, when the logic threshold voltage (VTL) of the

尚、電源Vdd遮断時に前記インタフェース部の出力不定状態を解消するには上記レベルシフト機能を有する出力バッファ15における高インピーダンス制御に限定されず、図5に例示されるように、インタフェース部11とICカードマイコンとの切り離しには電源Vdd遮断時にオフ状態にされるバススイッチ21を採用し、レベルシフトには図6の差動アンプを利用した回路をインタフェース部11に設ければよい。図6の回路において差動アンプの電源に高抵抗R1を介して電源Vddが接続されているのはVcc−ICが遮断されたときの動作安定化のためである。

Note that the output indefinite state of the interface unit when the power supply Vdd is shut off is not limited to the high impedance control in the

図7にはMRYC5の第2の構成例が示される。図1に対して分離スイッチ回路12はスイッチSW1だけで構成される。1ビットモードまたは4ビットモードにおいて、インタフェースコントローラ7がICカードマイコン9と通信を行うときインタフェースコントローラ7の制御によりカット・オフされて外部接続端子C10、C11、C13との接続を分離するスイッチを不要とした。8ビットモードで外部接続端子C10〜C13に割り当てられるデータ端子DAT4〜DAT7の機能と1ビットモードまたは4ビットモードにおいて配線L1〜L4に接続される端子Vcc、I/O、CLK、RESの機能との相違による選択はMRYC5の外部で行えばよい。その他の構成は図1と同じである。

FIG. 7 shows a second configuration example of MRYC5. In contrast to FIG. 1, the

図8にはMRYC5の第3の構成例が示される。図1の構成に対してICカードマイコンへの動作電源供給を端子C15だけで行なうようにした。スイッチSW1が不用になる。特に図示はしないが図7と図8を組合わせて分離スイッチ回路12全体を廃止する構成を採用することも可能である。

FIG. 8 shows a third configuration example of MRYC5. In contrast to the configuration of FIG. 1, the operation power supply to the IC card microcomputer is performed only at the terminal C15. The switch SW1 becomes unnecessary. Although not shown in particular, it is possible to employ a configuration in which the entire

図9にはMRYC5の第4の構成例が示される。同図に示されるMRYC5は、分離スイッチ回路12を図示しないが、図7または図8の接続関係を持つICカードマイコン9と、更に接触インタフェースのみを有し、インタフェースコントローラ7のインタフェース部11にのみ接続する別のICカードマイコン24を搭載して構成される。その他の構成は図1と同様である。本実施例においては、ICカードマイコン24はインタフェースコントローラ7のコプロセッサとして動作し、ICカードマイコン24のみで独立して動作することはない。

FIG. 9 shows a fourth configuration example of MRYC5. The

図10にはMRYC5の第5の構成例が示される。同図に示されるMRYC5は図7または図8の構成に対し、非接触インタフェースのみを有する別のICカードマイコン25をさらに搭載して構成される。ICカードマイコン9への動作電源の供給はC12(Vcc−ic)で行ない、ICカードマイコン25への動作電源の供給はC15(Vcc−IC)で行なう。非接触インタフェースを有するICカードマイコン25は電磁波がアンテナ11を横切ることによって生ずる誘導起電力をその動作電源とすることができるので、C15からICカードマイコン25への動作電源供給は必須ではない。ICカードマイコン25の電源安定化による動作の安定化を企図する場合にC15からの動作電源供給が意味をもつ。

FIG. 10 shows a fifth configuration example of MRYC5. The

図11にはインタフェースコントローラ7の詳細が例示される。インタフェースコントローラ7はホストインタフェース回路30、マイクロコンピュータ31、フラッシュコントローラ32、バッファコントローラ33、バッファメモリ34、及びインタフェース部11から成る。バッファメモリ34はDRAM(Dynamic Random Access memory)又はSRAM(Static Random Access Memory)等から成る。インタフェース回路11にはICカードマイコン9が接続される。マイクロコンピュータ31はCPU(中央処理装置)37、CPU37の動作プログラムを保有するプログラムメモリ(PGM)38、及びCPU37のワーク領域に利用されるワークメモリ(WRAM)39などによって構成される。前記MMC仕様に対応するインタフェース制御態様の制御プログラムはPGM38が保有する。

FIG. 11 illustrates details of the

ホストインタフェース回路30はメモリカードイニシャライズコマンドを発行すると、割込みによってマイクロコンピュータ31にMMCインタフェース制御態様の制御プログラムを実行可能にする。マイクロコンピュータ31はその制御プログラムを実行する事によってホストインタフェース回路30による外部インタフェース動作を制御し、フラッシュコントローラ32によるフラッシュメモリ8に対するアクセス(書き込み、消去、及び読み出し動作)とデータ管理を制御し、バッファコントローラ33によるメモリカード固有のデータフォーマットとメモリに対する共通のデータフォーマットとの間のフォーマット変換を制御する。

When the

バッファメモリ34には、フラッシュメモリ8から読み出されたデータ又はフラッシュメモリ8に書き込まれるデータが一時的に保持される。フラッシュコントローラ32はフラッシュメモリ8をハードディスク互換のファイルメモリとして動作させ、データをセクタ単位で管理する。

The

尚、前記フラッシュコントローラ32は図示を省略するECC回路を備え、メモリへのデータ格納に際してECCコードを付加し、読み出しデータに対してECCコードによるエラー検出・訂正処理を行う。

The

図12には前記ICカードマイコン9の詳細が例示される。ICカードマイコン9は、CPU41、ワークRAMとしてのRAM(ランダム・アクセス・メモリ)42、タイマ43、EEPROM(エレクトリカリ・イレーザブル・アンド・プログラマブル・リード・オンリ・メモリ)44、コプロセッサユニット45、マスクROM(リード・オンリ・メモリ)46、システムコントロールロジック47、入出力ポート(I/Oポート)48、データバス49、アドレスバス50及びRF部51を有する。

FIG. 12 illustrates details of the

前記マスクROM46はCPU41の動作プログラム(暗号化プログラム、復号プログラム、インタフェース制御プログラム等)及びデータを格納するのに利用される。前記RAM42はCPU41のワーク領域又はデータの一時記憶領域とされ、例えばSRAM(スタティック・ランダム・アクセス・メモリ)若しくはDRAM(ダイナミック・ランダム・アクセス・メモリ)から成る。I/Oポート48にICカードコマンドが供給されると、システムコントロールロジック47がこれをデコードし、当該コマンドの実行に必要な処理プログラムをCPU41に実行させる。即ち、CPU41は、システムコントロールロジック47から指示されるアドレスでマスクROM46をアクセスして命令をフェッチし、フェッチした命令をデコードし、デコード結果に基づいてオペランドフェッチやデータ演算を行う。コプロセッサユニット45はCPU41の制御に従ってRSAや楕円曲線暗号演算における剰余演算処理などを行う。I/Oポート48は1ビットの入出力端子I/Oを有し、データの入出力と外部割り込み信号の入力に兼用される。I/Oポート48はデータバス49に結合され、データバス49には前記CPU41、RAM42、タイマ43、EEPROM44、及びコプロセッサユニット45等が接続される。システムコントロールロジック47はICカードマイコン9の動作モードの制御及び割り込み制御を行い、更に暗号鍵の生成に利用する乱数発生ロジック等を有する。ICカードマイコン9はリセット信号RESによってリセット動作が指示されると、内部が初期化され、CPU41はマスクROM46のプログラムの先頭番地から命令実行を開始する。ICカードマイコン9はクロック信号CLKに同期動作される。

The

前記EEPROM44は、電気的に消去処理及び書込み処理が可能にされ、個人を特定するために用いられるID情報や認証証明書などのデータを格納する領域として用いられる。EEPRPM44に代えてフラッシュメモリ或は強誘電体メモリなどを採用してもよい。ICカードマイコン9は外部とのインタフェースに外部接続端子を用いる接触インタフェースと、アンテナを用いる非接触インタフェースの一方または双方をサポートする。非接触インタフェースを行うためのRF部51はチップのアンテナ端子TML1,TML2を有する。アンテナを経由してRF部51より電力が供給されたり、あるいはシステムコントロールロジック47により内部バスを経由して非接触インタフェースが選択されると、RF部51は前記アンテナが所定の電磁波(例えば高周波の変動磁束やマイクロ波)を横切ることによって生ずる誘導起電力を動作電源として動作電源を発生し、該所定の電波の周波数に対応して生ずる誘導電流を基にした内部クロック信号CLK、該所定の電波に重なって受け渡されるデータをRF部51で分離した内部データ、さらにリセット信号RES、の夫々を生成し、アンテナから非接触で情報の入出力を行なう。ICカードマイコン9の内部において、非接触インタフェースを介して動作するRF部51は、接触インタフェースを介して動作するICカード動作用のCPU41などとは独立した小規模の回路で構成するのが好ましい。RF部51として、その内部に非接触カード動作に必要な回路、例えば非接触カード用プロセッサ、当該プロセッサの制御プログラム領域及びワーク領域に用いられるメモリ、そしてRF送受信及び電源回路部が設けられる。このようにRF部51はプロセッサ機能とその制御プログラムというように独立した小規模の回路で構成されるため、例えば接触端子を介しての電源供給が得られない環境においても、外部からの誘導起電力によって回路を動作させることが容易となる。また、RF部51は内部のデータバス49及びアドレスバス50を経由することにより、非接触インタフェース部分と接触インタフェース部分との間でデータを入出力することも可能である。

The

MRYC5におけるセキュリティー処理動作を説明する。例えばフラッシュメモリ8のセキュア領域にはユーザ識別情報が格納されている。コンテンツデータをダウンロードするときはユーザ識別情報を秘密鍵として暗号化されたライセンス情報を一緒にダウンロードする。コンテンツデータを復号するための復号キーはライセンス情報に含まれ、ライセンス情報はユーザ識別情報を復号キーに用いて復号される。これによってコンテンツデータに対する著作権保護を行う。係るセキュリティー処理はマイクロコンピュータ31によるプログラム制御で行なわれる。

The security processing operation in MRYC5 will be described. For example, user identification information is stored in the secure area of the

ICカードマイコン9によるセキュリティー処理について説明する。例えばICカードマイコン9は電子決済サービスなどに利用可能なISO/IEC15408の評価・認証機関による認証済み機能を実現している。EEPROM44には所定の認証証明書を保有し、ホストから認証要求が有ったときはその認証証明書を送り、これに対して認証を得ることを条件に、後続の通信処理が可能にされる。このようなセキュリティー処理の動作プログラムはマスクROM46が保有する。ICカードマイコン9による認証処理はICカードマイコン9内部に閉じた環境で行うのがセキュリティーの観点より望ましい。この点で、ICカードマイコン9の電源だけを投入して外部接続端子C10〜C13又はアンテナを介して外部インタフェースを行なう意義がある。用途上又は技術的にセキュリティー上の問題がない場合にはインタフェースコントローラ7経由でセキュリティー処理を行うことは差し支えない。また、MRYCの製造後、製品出荷までの過程において、外部接続端子C10〜C13を介して、ICカードマイコン9に各種アプリケーションソフトの書込みやカード発行処理を容易に行なうことができる。

A security process by the

例えば上述の如くICカードマイコン9が電子決済サービスなどに利用可能なISO/IEC15408の評価・認証機関による認証済みである場合、キャッシュカード、クレジットカード或いは定期券などのカードホルダにMRYC5を挿入し、非接触インタフェースを用いてそれらカード機能を実現することが可能になる。

For example, as described above, when the

ICカードマイコン9は電子決済などレベルの高いセキュリティー処理に利用されることを考慮すると、ICカードマイコン9の異常な状態に対して全ての内部状態を初期化するパワーオンリセットはインタフェースコントローラ7等に比べて頻繁に行われる可能性が高い。これを考慮すると、ICカードマイコン9には専用の電源供給端子C12(Vcc−ic)、C15(Vcc−IC)を設けているので、MRYC5全体をリセットすること無くICカードマイコン9単独で自由にパワーオンリセット可能になる。これにより、セキュリティーを保証しつつMRYC5の勝手を向上させることができる。

Considering that the

《MRYCの外部接続端子配列》

図13には前記MRYC5をMMC規格のハーフサイズのパッケージに封止した時の外観を示す。図14には前記MRYC5をMMC規格のスタンダードサイズのパッケージに封止した時の外観を示す。両方の図面には外部接続端子の配列が明瞭に示されており、その配列は双方等しくされている。各端子C1〜C16の機能割り当ては図3で説明した通りである。C1〜C7はプリミティブなMMC規格に対応する。C8〜C9は4ビットモードのための拡張端子、C10〜C13はICカードマイコン接触インタフェース並びに8ビットモードのための拡張端子、C14及びC16は外部アンテナ接続用の拡張端子、C15はICカードマイコン専用の電源供給のための拡張端子である。C1〜C16はメモリカードの挿入方向(矢印X方向)の前後に隣合う列相互間で列方向の配置がずらされた千鳥状の配置を有する。第1列目はC1〜C7である。C8〜C13は第1列目の外部接続端子列に対して離間配置された第2列目を構成する。C10〜C13の外部接続端子の大きさはC1〜C7の外部接続端子の大きさと一定の範囲において同じである。C8の外部接続端子は前記第1列目に配置されコネクタ端子列の列方向一端の端子C7と列方向で完全に隣合う位置まで延在され、C9の外部接続端子は前記第1列目に配置され端子列の端子C1と列方向で部分的に重なって隣合う位置まで延在されている。第1列目の外部接続端子列と第2列目の外部接続端子列とは、C4とC15を除き、外部接続端子の列方向配置が列方向で相互にずれて、千鳥状に配置されている。

《MRYC external connection terminal arrangement》

FIG. 13 shows an appearance when the

上記千鳥状配置により、MRYC5が装着される図示を省略するカードスロットには、その多数のスロット端子(ピン)を交互に突出量を変えて並列配置するという比較的簡単に構成によって多端子化に対応することができる。この多端子化という点で、後列の前記C11とC12の間の領域に新設された端子C14〜C16も千鳥状に配置される。

Due to the zigzag arrangement, the card slot (not shown) in which the

前記外部接続端子として非接触インタフェースのための高周波アンテナ10を接続可能なアンテナ接続端子C14,C16を有する場合、前記アンテナ接続端子C14,C16は前記ICカードマイコン専用電源端子としての外部接続端子C15に隣接して前記電源Vdd供給用外部接続端子C4の近傍に配置される。そのようなアンテナ接続端子C14,C16はICカードマイコンにおける非接触インタフェースの感度を上げるために外部高周波アンテナの接続に用いられる。アンテナ接続端子C14,C16に印加される電圧は比較的高く周波数も高い。従って、MRYC5の配線基板上で信号やクロック等の接続端子に至る配線の引き回しと、外部アンテナの接続端子C14,C16に至る配線の引き回しとが錯綜して相互に近接したり跨いだりすることが多くなると、クロストークや誘導等によって信号線やクロック配線にノイズが重畳される。若しくは信号線やクロック配線からのクロストークや誘導等によるノイズが、外部高周波アンテナから受信される高周波信号に重畳され、RF部51で分離するデータに誤りを生じ得る。前記アンテナ接続端子C14,C16は前記ICカードマイコン専用電源端子としての外部接続端子C15に隣接して前記電源Vdd供給用外部接続端子C4の近傍に配置されるから、その配置はノイズの発生を極力抑えるのに好適な配置となる。

When the antenna connection terminals C14 and C16 that can be connected to the high-

図13及び図14で説明した外部接続端子の形状については図15の如く一部変更することが可能である。ここではC9とC8の形状を短くしている。これはカードスロットのC8及びC9に接触する端子の位置が、第1列目にあるカードスロットへの対応を企図したものである。また、図16に例示されるように外部接続端子数を削減することも可能である。外部接続端子C8,C9を廃止し、MMC規格の1ビットモードとICカードマイコンの接触インタフェースサポートを考慮した端子配列になる。図15、図16の場合にも外部接続端子の千鳥状配置と、C14,C16のアンテナ接続端子とICカードマイコン専用電源供給端子C15との配置関係はそのまま踏襲されている。 The shape of the external connection terminal described in FIGS. 13 and 14 can be partially changed as shown in FIG. Here, the shapes of C9 and C8 are shortened. This is intended to correspond to the card slot in which the position of the terminal contacting C8 and C9 of the card slot is in the first row. Also, as illustrated in FIG. 16, the number of external connection terminals can be reduced. The external connection terminals C8 and C9 are abolished, and the terminal arrangement takes into account the MMC standard 1-bit mode and IC card microcomputer contact interface support. 15 and 16, the staggered arrangement of the external connection terminals and the arrangement relationship between the antenna connection terminals C14 and C16 and the IC card microcomputer dedicated power supply terminal C15 are followed as they are.

《カードスロットへの挿入及び電源供給》

図23乃至図26にはメモリカードをカードスロットへ挿入する過程及びその過程の考察により得られたメモリカードへの電源供給について示されている。

《Insertion into card slot and power supply》

23 to 26 show the process of inserting a memory card into the card slot and the power supply to the memory card obtained by considering the process.

図23にはメモリカード5とメモリカード5が挿入されるカードスロット70が示され、カードスロット70にはメモリカード5の挿入を検知するためのセンサ71、メモリカード5の外部接続端子C1乃至C16のそれぞれに接触する端子72〜87が設けられ、前記端子85,87には外部アンテナ88が接続されている。

FIG. 23 shows a

図24にはメモリカード5がカードスロット70に挿入される第1過程を示している。第1過程の段階では端子C15に接続される端子86がメモリカード5の端子C4に接触しており、またカードスロット70の端子79〜85,87がメモリカード5の第1列の端子C1〜C9に接触する可能性があることを示している。メモリカード5の端子C15は電位Vcc−ICを供給する端子であり、インタフェースコントローラ7やフラッシュメモリ8に供給する電源Vddと同じ若しくはより高い電位が供給される。この状態でインタフェースコントローラ7やフラッシュメモリ8にVcc−ICが供給され、メモリカード5の第1列の端子C1〜C9にカードスロット70の端子79〜85,87が接触することで電気的に回路が形成されるおそれがある。また外部アンテナ88には外部の電界に応じて電位を発生させるため、端子85,87がアンテナ接続端子C14,C16以外の端子に接触し、この電位がインタフェースコントローラ7に印可されるおそれがある。

FIG. 24 shows a first process in which the

図25にはメモリカード5がカードスロット70に挿入される第2過程を示している。第2過程の段階では、カードスロット70の端子79〜85,87がメモリカード5の第1列の端子C1〜C9に接触することはないが、カードスロット70の端子75と86がメモリカード5の外部接続端子C4を介して接続され、端子75にVddを供給するための図示しない回路にVcc−ICが供給されるおそれがある。また端子C4に端子75と端子86とが接触することでインタフェースコントローラ7やフラッシュメモリ8にVcc−ICが供給され、端子72〜74,76〜80が端子C1〜C3,C5〜C9と接触することで電気的に回路が形成されるおそれがある。

FIG. 25 shows a second process in which the

図26にはメモリカード5がカードスロット70に挿入される第3過程を示している。第3過程の段階では、カードスロット70の端子72〜87とメモリカード5の端子C1〜C16が適切に接続されている。

FIG. 26 shows a third process in which the

図24及び図25に示す過程において生じうる問題については、メモリカード5における解決策と、カードスロット70を有するホスト装置での解決策とがある。

The problems that may occur in the process shown in FIGS. 24 and 25 include a solution in the

メモリカード5での解決策としては、端子C4とインタフェースコントローラ7及びフラッシュメモリ8との間に電源回路を備えておき、端子C4から電源Vddが供給されていることを検知した後に、インタフェースコントローラ7及びフラッシュメモリ8に動作電源の供給を開始するとともに、端子C1乃至C13をインタフェースコントローラ7と接続するようにすればよい。

As a solution in the

一方ホスト装置での解決策としては、Vcc−ICの供給及び外部アンテナ88に発生する電位の供給を第3過程において開始することで解決可能である。則ち、カードスロット70の端子72〜87がメモリカードの端子C1〜C16と過程的な接触をしていないことをセンサ71で検知した後に、Vcc−ICの供給を開始すればよい。カードスロット70の端子85,87がメモリカード5の端子と過程的な接触を生じないようにメモリカード5及びカードスロット70の端子を形成するか、または外部アンテナ88と端子85,87の間に電気的に接続/切断が可能なスイッチ回路を設け、センサ71で過程的な接触をしていないことを検知した後に、外部アンテナ88を端子85,87と電気的に接続すればよい。

On the other hand, a solution in the host device can be solved by starting the supply of the Vcc-IC and the supply of the potential generated in the

またVdd,Vss1,Vss2の各電位については、常時供給していても、センサ71でメモリカード5がカードスロット70に挿入されたことを検知した後に供給を開始しても良い。カードスロット70の端子74,77は基準電位の供給端子であり、また図示する構造では過程的な接触をすることがないからである。また端子75はVcc−ICと同電位またはより低い電位であるVddの供給端子であるため、端子C4を介して端子86と接続されていたとしても、Vcc−ICを供給するための図示しない回路にVddが供給されても特に問題を生じないと考えられるためである。

The potentials Vdd, Vss1, and Vss2 may be constantly supplied, or may be started after the

《カードスロットからの引き抜き及び電源供給》

また図示はしないが、カードスロット70からメモリカード5が引き抜かれる場合のことを考察する。この場合、フラッシュメモリ8においてデータの消去またはデータの書き込みの動作途中でカードスロット70からメモリカード5が引き抜かれた場合、フラッシュメモリ8への動作電源の供給が遮断されることで、不所望なデータの破損を生じ、またはデプリートと呼ばれる状態を生じることによりメモリカード5自体の認識ができなくなる場合がある。このような事態を回避するために、ホスト装置はセンサ71でメモリカード5がカードスロット70から引き抜かれたことを検知した場合、所定の端子を介してメモリカード5にそのことを通知するとともに、端子86から電位Vddを供給するようにすればよい。これにより図25の第2過程から図24の第1過程に亘って、端子C4に電位Vddを供給することができる。また端子74についても端子C3との接触時間を長くすることができるように、具体的には端子74を端子84と同程度の長さとするとともに、端子C3との接触点をより長くすることで電気的な接続を維持することが可能となる。これらのことにより、メモリカード5はデータの書き込みを完了させ、またはセンサ71での検出通知に応じて少なくともデプリート状態を回避する処理を行う時間を確保することが可能となる。

<Pulling out from card slot and supplying power>

Although not shown, the case where the

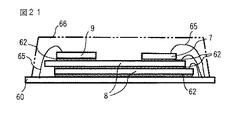

《チップのスタック構造》

図17には夫々個別の半導体集積回路チップ化された前記インタフェースコントローラ7、フラッシュメモリ8、及びICカードマイコン9のスタック実装構造が平面的に示され、図18にはその実装構造の縦断面が概略的に示される。所要の配線層が形成されたガラスエポキシ樹脂基板のような配線基板60の一面には外部接続電極C1〜C16が形成され、他面には所要の配線に接続した多数のボンディングパッド61が形成されている。ボンディングパッド61はアルミニウム、銅又は鉄合金などの導電パターンで形成される。外部接続電極C1〜C16はアルミニウム、銅又は鉄合金などの導電パターンに金メッキやニッケルメッキ、パラジウムメッキ等が施されて形成される。外部接続電極C1〜C16とボンディングパッド61との接続は配線基板60上の図示を省略する配線パターン及び配線基板60を厚さ方向に貫通するスルーホール等によって行われる。配線基板60の上には、2個の個別チップ化されたフラッシュメモリ8がずれて重ねられ、その上に単一チップ化されたインタフェースコントローラ7が重ねられる。配線基板60とチップ、チップとチップの結合はダイボンド剤62にて行なわれる。重ねられらた3個のチップには重ねられた状態で同じ向きの辺に沿って電極パッド64が配置され、配置された電極パッド64に配線基板の対応するボンディングパッド61がボンディングワイヤ65でワイヤボンディングされる。重ねられた3個のチップのボンディング用電極パッド64は重ねられた状態で同じ向きの辺に沿って配置されているから、ボンディングワイヤ65を短くでき、ワイヤ65の干渉も少なくなる。単体チップのICカードマイコン9は単体で配線基板60にダイボンディングされて、チップの電極パッドが回路基板の対応するボンディングパッドにボンディングされる。配線基板60上にスタックされたチップは樹脂モールドなどで封止される。66はモールド封止領域である。

《Chip stack structure》

FIG. 17 is a plan view showing a stack mounting structure of the

図19には図17及び図18のスタック構造に対してICカードマイコン9を2チップスタックする構造が示される。2個のICカードマイコン9のチップは同種で同サイズの場合は直接重ねるとチップ上の電極パッドが隠れてしまう。その場合にはスペーサ用のダミーチップ67を間に挟めばよい。当然ダミーチップ67はICカードマイコンチップよりも小さい。

FIG. 19 shows a structure in which the

図20には夫々個別の半導体集積回路チップ化された前記インタフェースコントローラ7、フラッシュメモリ8、及びICカードマイコン9の更に別のスタック実装構造が平面的に示され、図21にはその実装構造の縦断面が概略的に示される。図17乃至図19との相違点は2個の個別チップ化されたフラッシュメモリ8がスタックされ、その上に、夫々個別チップ化されたインタフェースコントローラ7とICカードマイコン9が別々にスタックされる。その他の構成は図17及び図18のスタック構造と同じであり、同一機能を有する部材には同一符号を付してその詳細な説明を省略する。

FIG. 20 is a plan view showing still another stack mounting structure of the

図22には図20及び図21のスタック構造に対してICカードマイコン9を2チップスタックする構造が示される。2個のICカードマイコン9のチップは同種で同サイズであるから直接重ねず、間にスペーサ用のダミーチップ67を挟める。フラッシュメモリ8は必要に応じて1チップまたは3チップ以上のチップスタックも同様に可能である。

FIG. 22 shows a structure in which two

以上本発明者によってなされた発明を実施形態に基づいて具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。 Although the invention made by the present inventor has been specifically described based on the embodiments, it is needless to say that the present invention is not limited thereto and can be variously modified without departing from the gist thereof.

例えば、本発明はMMC規格のメモリカードだけでなくその他の規格に準拠するマルチファンクション形態のメモリカードに広く適用することができる。従って、外部接続端子の機能、配列、数などは適宜変更可能である。またメモリはフラッシュメモリに限定されず、強磁性体メモリなど、その他記憶形式のメモリであってよい。セキュリティーコントローラはISO/IEC15408の評価・認証機関による認証済み機能を実現しているものに限定されない。単なる暗号化・復号を行なうマイクロコンピュータであってもよい。 For example, the present invention can be widely applied not only to MMC standard memory cards but also to multi-function memory cards conforming to other standards. Therefore, the function, arrangement, number, etc. of the external connection terminals can be changed as appropriate. The memory is not limited to a flash memory, and may be a memory of other storage format such as a ferromagnetic memory. The security controller is not limited to the one that realizes an authenticated function by an ISO / IEC 15408 evaluation / certification organization. It may be a microcomputer that performs simple encryption / decryption.

5 メモリカード

7 インタフェースコントローラ

8 フラッシュメモリ

9 デュアルウェイのICカードマイコン

10 アンテナ

11 インタフェース部

12 分離スイッチ回路

C4 Vdd供給用外部接続端子(第1の外部接続端子)

C12 Vcc−ic供給用外部接続端子

C15 Vcc−IC供給用外部接続端子(第2の外部接続端子)

C11 CLK−ic割当て用外部接続端子(第3の外部接続端子)

C13 I/O−ic割当て用外部接続端子(第4の外部接続端子)

C10 RES−ic割当て用外部接続端子(第5の外部接続端子)

C14,C16 アンテナ接続用外部接続端子

12 分離スイッチ回路

15 出力バッファ

17 クロックドインバータ

24 接触インタフェース型のICカードマイコン

25 非接触インタフェース型のICカードマイコン

60 回路基板

61 配線基板上の電極(ボンディングパッド)

64 半導体チップ上の電極パッド

65 ボンディングワイヤ

DESCRIPTION OF

C12 Vcc-ic supply external connection terminal C15 Vcc-IC supply external connection terminal (second external connection terminal)

C11 CLK-ic assignment external connection terminal (third external connection terminal)

C13 I / O-ic assignment external connection terminal (fourth external connection terminal)

C10 RES-ic assignment external connection terminal (fifth external connection terminal)

C14, C16 External connection terminal for

64 Electrode Pad on

Claims (5)

前記インタフェースコントローラ及びメモリに動作電源を供給する第1の外部接続端子とは別に前記セキュリティーコントローラに動作電源を供給可能な第2の外部接続端子を有し、

前記セキュリティーコントローラは、外部と非接触インタフェースが可能なICカード用マイクロコンピュータであって、

前記外部接続端子として非接触インタフェースのためのアンテナを接続可能なアンテナ接続端子を有し、

前記アンテナ接続端子は、前記第2の外部接続端子に隣接して前記第1の外部接続端子の近傍に配置され、且つ前記第1の外部接続端子よりも前記第2の外部接続端子の近くに配置されることを特徴とするメモリカード。 On the wiring board on which a plurality of external connection terminals are formed, an interface controller connected to the external connection terminals, a memory connected to the interface controller, and a security controller are mounted,

A second external connection terminal capable of supplying operating power to the security controller separately from the first external connection terminal supplying operating power to the interface controller and the memory;

The security controller is an IC card microcomputer capable of non-contact interface with the outside,

An antenna connection terminal capable of connecting an antenna for a non-contact interface as the external connection terminal;

The antenna connection terminal is disposed adjacent to the first external connection terminal adjacent to the second external connection terminal, and closer to the second external connection terminal than the first external connection terminal. memory card being arranged.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009242129A JP4906135B2 (en) | 2009-10-21 | 2009-10-21 | Memory card |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009242129A JP4906135B2 (en) | 2009-10-21 | 2009-10-21 | Memory card |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003316002A Division JP4412947B2 (en) | 2003-09-08 | 2003-09-08 | Memory card |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010015606A JP2010015606A (en) | 2010-01-21 |

| JP4906135B2 true JP4906135B2 (en) | 2012-03-28 |

Family

ID=41701597

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009242129A Expired - Fee Related JP4906135B2 (en) | 2009-10-21 | 2009-10-21 | Memory card |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4906135B2 (en) |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1218276C (en) * | 2000-04-28 | 2005-09-07 | 株式会社日立制作所 | IC card |

| JP2002342732A (en) * | 2001-05-18 | 2002-11-29 | Matsushita Electric Ind Co Ltd | Compact ic card and compact ic card adapter and terminal equipment |

| JP3865629B2 (en) * | 2001-07-09 | 2007-01-10 | 株式会社ルネサステクノロジ | Storage device |

-

2009

- 2009-10-21 JP JP2009242129A patent/JP4906135B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010015606A (en) | 2010-01-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4412947B2 (en) | Memory card | |

| JP4447553B2 (en) | Multifunction card device | |

| US7946500B2 (en) | Memory card and semiconductor device | |

| US7296754B2 (en) | IC card module | |

| US7389937B2 (en) | Card-shaped memory device incorporating IC card function | |

| US7757958B2 (en) | Card-shaped memory device incorporating IC card function, adapter for the same and host device | |

| CN101512559A (en) | IC card and IC card socket | |

| JP2007183776A (en) | Semiconductor device | |

| JP4906135B2 (en) | Memory card | |

| JP2010086550A (en) | Semiconductor card device | |

| TWI309386B (en) | ||

| JP2006236200A (en) | Card type storage device and host device thereof | |

| JP4761479B2 (en) | IC card | |

| JPWO2007010595A1 (en) | Semiconductor device and manufacturing method thereof |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091021 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100527 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111020 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111206 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120105 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120106 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150120 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4906135 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |