Industry Standard Architecture (ISA) is the 16-bit internal bus of IBM PC/AT and similar computers based on the Intel 80286 and its immediate successors during the 1980s. The bus was (largely) backward compatible with the 8-bit bus of the 8088-based IBM PC, including the IBM PC/XT as well as IBM PC compatibles.

A motherboard is the main printed circuit board (PCB) in general-purpose computers and other expandable systems. It holds and allows communication between many of the crucial electronic components of a system, such as the central processing unit (CPU) and memory, and provides connectors for other peripherals. Unlike a backplane, a motherboard usually contains significant sub-systems, such as the central processor, the chipset's input/output and memory controllers, interface connectors, and other components integrated for general use.

HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel high-bandwidth, low-latency point-to-point link that was introduced on April 2, 2001. The HyperTransport Consortium is in charge of promoting and developing HyperTransport technology.

PCI Express, officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers' graphics cards, sound cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism, and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization.

The front-side bus (FSB) is a computer communication interface (bus) that was often used in Intel-chip-based computers during the 1990s and 2000s. The EV6 bus served the same function for competing AMD CPUs. Both typically carry data between the central processing unit (CPU) and a memory controller hub, known as the northbridge.

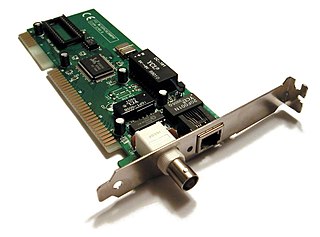

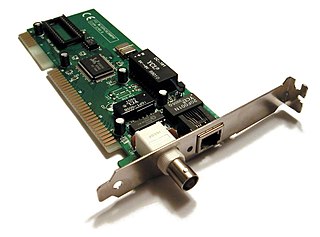

A network interface controller is a computer hardware component that connects a computer to a computer network.

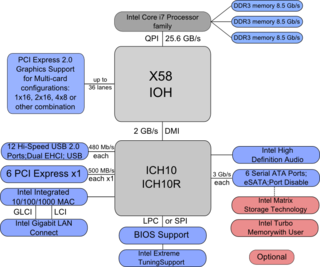

In a computer system, a chipset is a set of electronic components on one or more integrated circuits that manages the data flow between the processor, memory and peripherals. The chipset is usually found on the motherboard of computers. Chipsets are usually designed to work with a specific family of microprocessors. Because it controls communications between the processor and external devices, the chipset plays a crucial role in determining performance.

In computing, a northbridge is a microchip that comprises the core logic chipset architecture on motherboards to handle high-performance tasks, especially for older personal computers. It is connected directly to a CPU via the front-side bus (FSB), and is usually used in conjunction with a slower southbridge to manage communication between the CPU and other parts of the motherboard.

The southbridge is one of the two chips in the core logic chipset on older personal computer (PC) motherboards, the other being the northbridge. As of 2023, most personal computer devices no longer use a set of two chips, and instead have a single chip acting as the 'chipset', for example Intel's Z790 chipset.

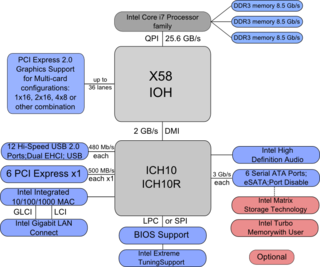

Intel Hub Architecture (IHA), also known as Accelerated Hub Architecture (AHA) was Intel's architecture for the 8xx family of chipsets, starting in 1999 with the Intel 810. It uses a memory controller hub (MCH) that is connected to an I/O controller hub (ICH) via a 266 MB/s bus. The MCH chip supports memory and AGP, while the ICH chip provides connectivity for PCI, USB, sound, IDE hard disks and LAN.

The Intel 810 chipset was released by Intel in early 1999 with the code-name "Whitney" as a platform for the P6-based Socket 370 CPU series, including the Pentium III and Celeron processors. Some motherboard designs include Slot 1 for older Intel CPUs or a combination of both Socket 370 and Slot 1. It targeted the low-cost segment of the market, offering a robust platform for uniprocessor budget systems with integrated graphics. The 810 was Intel's first chipset design to incorporate a hub architecture which was claimed to have better I/O throughput and an integrated GPU, derived from the Intel740.

I/O Controller Hub (ICH) is a family of Intel southbridge microchips used to manage data communications between a CPU and a motherboard, specifically Intel chipsets based on the Intel Hub Architecture. It is designed to be paired with a second support chip known as a northbridge. As with any other southbridge, the ICH is used to connect and control peripheral devices.

Tolapai is the code name of Intel's embedded system on a chip (SoC) which combines a Pentium M (Dothan) processor core, DDR2 memory controllers and input/output (I/O) controllers, and a QuickAssist integrated accelerator unit for security functions.

The Intel X58 is an Intel chip designed to connect Intel processors with Intel QuickPath Interconnect (QPI) interface to peripheral devices. Supported processors implement the Nehalem microarchitecture and therefore have an integrated memory controller (IMC), so the X58 does not have a memory interface. Initially supported processors were the Core i7, but the chip also supported Nehalem and Westmere-based Xeon processors.

The Platform Controller Hub (PCH) is a family of Intel's single-chip chipsets, first introduced in 2009. It is the successor to the Intel Hub Architecture, which used two chips–a northbridge and southbridge, and first appeared in the Intel 5 Series.

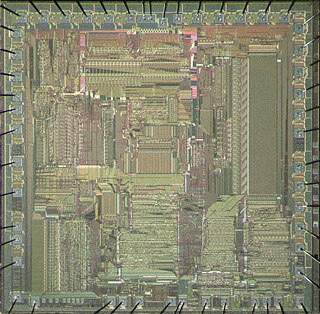

AMD Lance Am7990 IEEE 802.3 Ethernet media access controller (MAC) controller were introduced in 1985. Its architecture is the basis for AMD's PCnet Family of highly integrated single-chip Ethernet controllers. The one exception is the Am79C940 MAC. The Am7990 chip was fabricated in NMOS technology and has no integrated Manchester encoder/decoder (ENDEC) nor does it have an integrated 10BASE-T transceiver.

LGA 1156, also known as Socket H or H1, is an Intel desktop CPU socket. Its incompatible successor is LGA 1155.

The Intel X79 is a Platform Controller Hub (PCH) designed and manufactured by Intel for their LGA 2011 and LGA 2011-1.