KR100821616B1 - Two numbers comparator in vlsi circuits - Google Patents

Two numbers comparator in vlsi circuits Download PDFInfo

- Publication number

- KR100821616B1 KR100821616B1 KR1020060127879A KR20060127879A KR100821616B1 KR 100821616 B1 KR100821616 B1 KR 100821616B1 KR 1020060127879 A KR1020060127879 A KR 1020060127879A KR 20060127879 A KR20060127879 A KR 20060127879A KR 100821616 B1 KR100821616 B1 KR 100821616B1

- Authority

- KR

- South Korea

- Prior art keywords

- bit

- numbers

- superior

- unit

- bitwise

- Prior art date

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/02—Comparing digital values

- G06F7/026—Magnitude comparison, i.e. determining the relative order of operands based on their numerical value, e.g. window comparator

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F7/00—Methods or arrangements for processing data by operating upon the order or content of the data handled

- G06F7/06—Arrangements for sorting, selecting, merging, or comparing data on individual record carriers

- G06F7/20—Comparing separate sets of record carriers arranged in the same sequence to determine whether at least some of the data in one set is identical with that in the other set or sets

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- Computational Mathematics (AREA)

- Mathematical Analysis (AREA)

- Mathematical Optimization (AREA)

- Pure & Applied Mathematics (AREA)

- Logic Circuits (AREA)

Abstract

Description

도 1은 본 발명에 의한 반도체 집적회로의 두 숫자 비교기를 나타낸 블록구성도이다. 1 is a block diagram illustrating two numeric comparators of a semiconductor integrated circuit according to the present invention.

도 2는 본 발명에 의한 슈피리어 엔코딩부를 나타낸 도면이다. 2 is a view showing a superior encoding unit according to the present invention.

도 3은 본 발명에 의한 두 숫자 비교 방식을 설명하기 위한 도면이다. 3 is a view for explaining a two number comparison method according to the present invention.

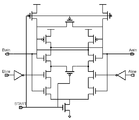

도 4는 본 발명에 의한 비트와이즈 컴페티션부를 나타낸 회로구성도이다. 4 is a circuit diagram illustrating a bitwise competition unit according to the present invention.

도 5는 본 발명에 의한 판별부를 나타낸 회로구성도이다. 5 is a circuit configuration diagram showing a discriminating unit according to the present invention.

- 도면의 주요부분에 대한 부호의 설명 - -Explanation of symbols for the main parts of the drawings-

10 : 슈피리어 엔코딩부10: Superior encoding part

20 : 비트와이트 컴페티션부20: bitight competition

30 : 판별부30: determination unit

본 발명은 반도체 집적회로의 두 숫자 비교기에 관한 것으로서, 보다 상세하게는 반도체 집적회로에서 긴 비트의 두 숫자의 크기를 비교할 때 뺄셈기에 의한 연산 결과를 통해 판단하지 않고 두 숫자의 각 비트를 MSB로부터 비트단위로 각각 비교하여 먼저 1이 나오는 쪽의 숫자를 큰 수로 결정함으로써 트랜지스터 개수를 줄여 효율적인 연산을 수행할 수 있도록 하는 반도체 집적회로의 두 숫자 비교기에 관한 것이다. The present invention relates to a two-digit comparator of a semiconductor integrated circuit, and more particularly, when comparing the sizes of two long bits in a semiconductor integrated circuit, each bit of the two numbers is determined from the MSB without being judged by the operation result of the subtractor. The present invention relates to a two-digit comparator of a semiconductor integrated circuit that compares bit by bit and determines the number of the first one by a large number, thereby reducing the number of transistors and performing an efficient operation.

일반적으로 이미지 처리나 그래픽 처리 등의 분야에서 두 숫자의 크기를 비교하는데 있어 뺄셈기를 이용하여 'A-B' 연산을 수행한 후, 양의 값이 나오면 A가 큰 값, 음의 값이 나오면 B가 큰 값, '0'이 나오면 같은 값으로 결정하였다. In general, in the fields of image processing and graphic processing, the 'AB' operation is performed by using a subtractor to compare the sizes of two numbers, and when A is positive, A is large, and when it is negative, B is large. When the value, '0', was determined, the same value was determined.

하지만 이런 방법은 단순히 두 숫자의 크기를 비교하는 목적에 비하여 두 수의 연산을 위한 트랜지스터의 수가 많이 필요하기 때문에 불필요한 정보도 많이 얻게 되어 비효율적인 측면이 있을 뿐만 아니라 여러 숫자의 크기 비교를 많이 수행하게 되는 위의 이미지 처리나 그래픽 처리 분야에서는 이러한 방법이 저 성능의 주요 원인이 될 수 있는 문제점이 있다. However, this method requires a lot of transistors for two numbers of operations compared to the purpose of simply comparing the sizes of two numbers, which leads to a lot of unnecessary information and inefficient aspects as well. In the above image processing or graphics processing field, there is a problem that this method may be the main cause of low performance.

본 발명은 상기와 같은 문제점을 해결하기 위해 창작된 것으로서, 본 발명의 목적은 반도체 집적회로에서 긴 비트의 두 숫자의 크기를 비교할 때 뺄셈기에 의한 연산 결과를 통해 판단하지 않고 두 숫자의 각 비트를 MSB로부터 비트단위로 각각 비교하여 먼저 1이 나오는 쪽의 숫자를 큰 수로 결정함으로써 트랜지스터 개수를 줄여 효율적인 크기 비교연산을 수행할 수 있도록 하는 반도체 집적회로의 두 숫자 비교기를 제공함에 있다. The present invention has been made to solve the above problems, and an object of the present invention is to determine each bit of two numbers without judging through the operation result by the subtractor when comparing the sizes of two long bits in a semiconductor integrated circuit. The present invention provides a two-digit comparator for semiconductor integrated circuits that compares bit by bit from the MSB and determines the number of the first one by a large number, thereby reducing the number of transistors and performing an efficient size comparison operation.

상기와 같은 목적을 실현하기 위한 본 발명은 어느 한 숫자의 각 비트에 대응되는 다른 한 숫자의 각 비트에 대해 우위인 비트를 변환하여 출력하는 슈피리어 엔코딩부와, 비교하기 위한 두 숫자에 대해 각각 슈피리어 엔코딩부에서 변환되어 출력된 두 우위값의 각 비트를 최상위비트로부터 순차적으로 각 비트를 비교하여 각 비트의 크기를 결정하여 출력하는 비트와이즈 컴페티션부와, 비트와이즈 컴페티션부에서 순차적으로 각 비트의 크기가 결정되어 출력되는 값을 입력받아 크기가 결정된 최초의 상위 비트에 따라 두 숫자의 크기를 판별하는 판별부를 포함하여 이루어진 것을 특징으로 한다. The present invention for achieving the above object is a superior encoding unit for converting and outputting the bit that is superior to each bit of the other number corresponding to each bit of any one number, and for the two numbers for comparison Each bit of the two leading values converted and output from the superior encoding unit are sequentially compared with each bit from the most significant bit to determine the size of each bit. And a determination unit for determining the size of the two numbers according to the first higher bit whose size is determined by sequentially receiving the output value after the size of each bit is determined.

본 발명에서 슈피리어 엔코딩부는 어느 한 숫자를 반전하여 다른 한 숫자와 노어게이팅하는 것을 특징으로 한다. In the present invention, the superior encoding unit is characterized in that inverting any one number and the other gating with the other number.

본 발명에서 슈피리어 엔코딩부는 두 비트 중 우위인 비트는 '1'로 변환되고 동일한 비트는 '0'으로 변환되는 것을 특징으로 한다. In the present invention, the superior encoding unit is characterized in that the uppermost bit of the two bits are converted to '1' and the same bit is converted to '0'.

본 발명에서 비트와이즈 컴페티션부에서 두 숫자의 최상위 비트는 부호비트가 아닌 것을 특징으로 한다. In the present invention, the most significant bit of two numbers in the bitwise competition unit is not a sign bit.

본 발명에서 비트와이즈 컴페티션부에서 최상위 비트가 부호비트인 숫자체계 에서는 두 숫자의 최상위 비트를 맞바꾸어 판단하는 것을 특징으로 한다. In the present invention, in the number system in which the most significant bit is a sign bit in the bitwise competition unit, the most significant bit of two numbers is exchanged and determined.

본 발명에서 판별부는 크기가 결정된 최초의 상위 비트 값을 고정하여 출력하는 것을 특징으로 한다. In the present invention, the determination unit may be configured to output the fixed first upper bit value of which size is determined.

이와 같이 이루어진 본 발명은 반도체 집적회로에서 크기를 비교하기 위한 두 숫자의 각 비트에 대해 슈피리어 엔코딩부를 통해 우위비트를 변환하여 최상위 비트로부터 각 비트의 크기를 결정하여 최초의 상위 비트값이 크기에 따라 두 숫자의 크기를 판단함으로써 적은 소자의 수로 효율적인 연산을 수행할 수 있도록 한다. According to the present invention, in the semiconductor integrated circuit, the first upper bit value is large by determining the size of each bit from the most significant bit by converting the leading bit through the superior encoding unit for each bit of two numbers for comparing the sizes. By judging the size of the two numbers, the number of devices can be efficiently operated.

이하, 본 발명의 바람직한 실시예를 첨부된 도면을 참조하여 설명하며 종래 구성과 동일한 부분은 동일한 부호 및 명칭을 사용한다. 또한 본 실시예는 본 발명의 권리범위를 한정하는 것은 아니고, 단지 예시로 제시된 것이며 당 분야에서 통상의 지식을 가진 자라면 본 발명의 기술적 사상 내에서 많은 변형이 가능할 것이다.Hereinafter, exemplary embodiments of the present invention will be described with reference to the accompanying drawings, and the same parts as in the prior art use the same reference numerals and names. In addition, the present embodiment is not intended to limit the scope of the present invention, but is presented by way of example only and those skilled in the art will be capable of many modifications within the technical spirit of the present invention.

도 1은 본 발명에 의한 반도체 집적회로의 두 숫자 비교기를 나타낸 블록구성도이다. 1 is a block diagram illustrating two numeric comparators of a semiconductor integrated circuit according to the present invention.

여기에 도시된 바와 같이 어느 한 숫자의 각 비트에 대응되는 다른 한 숫자의 각 비트에 대해 우위인 비트를 변환하여 출력하는 슈피리어 엔코딩(superior encoding)부(10)와, 비교하기 위한 두 숫자에 대해 각각 슈피리어 엔코딩부(10)에서 변환되어 출력된 두 우위값의 각 비트를 최상위 비트로부터 순차적으로 각 비트 를 비교하여 각 비트의 크기를 결정하여 출력하는 비트와이즈 컴페티션(bitwise competition)부(20)와, 비트와이즈 컴페티션부(20)에서 순차적으로 각 비트의 크기가 결정되어 출력되는 값을 입력받아 크기가 결정된 최초의 상위 비트에 따라 두 숫자의 크기를 판별하는 판별부(30)로 이루어진다. As shown here, a

위와 같이 이루어진 본 발명은 비트 단위로 크기를 비교하기 위해 먼저, 슈피리어 엔코딩부(10)를 통해 비교하기 위한 두 숫자의 각 비트에 우위인 비트를 변환하게 된다. In the present invention made as described above, in order to compare the size in bits, the superior bit is first converted to each bit of two numbers for comparison through the

슈피리어 엔코딩부(10)는 한 입력이 다른 입력보다 확실하게 큰 경우에만 '1'로 코딩이 된다. 즉, AsupB(A superior to B)는 A가 '1'이고 B가 '0'인 경우에만 '1'이 된다. 마찬가지로 BsupA(B superior to B)는 B가 '1'이고 A가 '0'인 경우에만 '1'이 된다. A와 B가 같은 경우는 AsupB, BsupA 모두 0이 되게 된다.The

도 2는 본 발명에 의한 슈피리어 엔코딩부를 나타낸 도면이다. 2 is a view showing a superior encoding unit according to the present invention.

여기에 도시된 바와 같이 AsupB = ~A · B로, BsupA = ~B · A 로 간단하게 인코딩을 표현식으로 나타낼 수 있다. As shown here, the encoding can be expressed simply as AsupB = ~ A · B and BsupA = ~ B · A.

즉, A 숫자의 각 비트에 대한 우위 비트를 확인하기 위해서는 A를 반전한 후 B와 노어게이팅함으로써 구하게 된다. In other words, in order to identify the leading bit for each bit of the A number, the inversion of A is performed by Nor gating with B.

따라서 각 비트 당 NOR gate 하나를 이용하여 간단히 하드웨어로 구현할 수 있게 된다. Therefore, it can be easily implemented in hardware by using one NOR gate per bit.

이와 같이 비교하기 위한 두 숫자를 각 비트별로 슈피리어 엔코딩부(10)를 거쳐 출력되는 supA와 supB 값은 비트와이즈 컴페티션부(20)에서 각 비트의 크기를 결정하게 된다. The supA and supB values outputted through the

즉, 각 비트별로 슈피리어 엔코딩부(10)를 거쳐 변환된 신호인 AsupB<i>와 BsupA<i>는 동시에 1이 될 수 없기 때문에 AsupB와 BsupA 중에서 최상위 비트로부터 '1'이 먼저 나오는 쪽이 더 큰 숫자라고 판단할 수 있게 된다. That is, since AsupB <i> and BsupA <i>, which are signals converted through the

이와 같은 방법은 최상위 비트가 부호비트가 아닌 숫자 체계(Unsigned number system)에서 판단 가능한 방법이며, 최상위 비트가 부호비트인 숫자 체계(Signed number system)에 적용하기 위해서는 최상위 비트를 서로 맞바꾸어 주어야 한다. This method is a method that can be determined in an unsigned number system, where the most significant bit is not a sign bit, and in order to be applied to a signed number system in which the most significant bit is a sign bit, the most significant bits must be interchanged.

이는 최상위 비트가 부호비트인 숫자 체계에서는 최상위 비트는 (-)값을 의미하기 때문에 한 숫자의 최상위 비트가 1이고 다른 숫자의 최상위 비트가 0일 경우, 최상위 비트가 부호비트가 아닌 숫자 체계와는 반대로 최상위 비트가 1인 경우가 반드시 작은 쪽이 되기 때문이다. This is because in the number system where the most significant bit is the sign bit, the most significant bit means a negative value.If the most significant bit of one number is 1 and the most significant bit of the other number is 0, the most significant bit is not the same as the number system. On the contrary, the case where the most significant bit is 1 is necessarily the smaller one.

또한, 최상위 비트가 아닌 비트들은 최상위 비트가 부호비트가 아닌 숫자 체계와 동일하기 때문에, 최상위 비트만 맞바꾸어 주고 나머지 비트들은 같은 방식으로 연결하여 연산하면 최상위 비트가 부호비트인 숫자 체계에서도 올바른 결과를 얻을 수 있다.In addition, since the most significant bit is the same as the number system, not the most significant bit, only the most significant bit is exchanged and the remaining bits are concatenated in the same way. You can get it.

도 3은 본 발명에 의한 두 숫자 비교 방식을 설명하기 위한 도면이다. 3 is a view for explaining a two number comparison method according to the present invention.

여기에 도시된 예는 간단한 4bit의 두 숫자를 비교하는 방식으로써 supA(AsupB)의 경우가 supB(BsupA)의 경우 보다 최상위 비트에서부터 '1'이 먼저 나오기 때문에 뒤의 '1'과는 상관없이 A가 B보다 크다고 결정할 수 있다. The example shown here is a simple method of comparing two numbers of 4 bits, where supA (AsupB) is preceded by '1' from the most significant bit than supB (BsupA), regardless of the later '1'. Can be determined to be greater than B.

즉, 슈피리어 엔코딩부(10)로부터 대응되는 비트가 동시에 1이 되는 경우는 발생하지 않기 때문에, 최상위 비트로부터 순차적으로 어느 쪽이 먼저 '1'이 발생하는지만 알면 두 숫자의 크기를 비교할 수 있게 된다. That is, since the corresponding bits from the

도 4는 본 발명에 의한 비트와이즈 컴페티션부를 나타낸 회로구성도이다. 4 is a circuit diagram illustrating a bitwise competition unit according to the present invention.

여기에 도시된 바와 같이 비트와이즈 컴페티션부(20)는 두 개의 병렬 라인이 있고 각 라인에 비트마다 두 개의 NMOS 트랜지스터가 직렬로 그라운드와 연결되어 있다. 이때 두 라인의 이름은 Aline과 Bline이며, 라인측에 연결된 NMOS 트랜지스터에는 슈피리어 엔코딩부(10)를 거친 AsupB와 BsupA 신호가 입력되고, 그라운드측에 연결된 NMOS 트랜지스터에는 START1 ~ START8 신호가 최상위 비트(MSB)쪽에서부터 최하위 비트(LSB)쪽으로 입력된다.As shown here, the

따라서 START 신호가 '0' 일 때는 Aline, Bline 모두 '1'로 프리차지 된다. 즉, 그라운드측에 연결된 NMOS 트랜지스터가 풋(foot) 트랜지스터의 역할을 하기 때문에 두 라인의 전압은 '1'로 유지된다. 이후 슈피리어 엔코딩부(10)에서 변환이 종료된 후 변환된 값이 입력되면, 풋 트랜지스터의 입력인 START 신호들이 트리거링 되기 시작하게 된다. Therefore, when the START signal is '0', both Aline and Bline are precharged to '1'. That is, since the NMOS transistor connected to the ground side acts as a foot transistor, the voltages of the two lines are kept at '1'. When the converted value is input after the conversion is completed in the

그러면, 최상위 비트인 START1부터 '0'에서 '1'로 활성화되기 시작하여 START8까지 차례대로 활성화되어 판별부(30)로 출력될 때 각각 인버터를 매개로 출 력된다. START 신호 활성화에 의해 해당 비트의 SupA와 SupB 신호는 라인에 영향을 주게 되어 SupA나 SupB 신호가 '1'일 경우에는 라인의 전압을 '0'으로 떨어뜨리게 된다. Then, starting from the most significant bits START1 to '1' to '1' and then activated to START8 in turn, when outputted to the

따라서, START 신호는 최상위 비트로부터 활성화가 되기 때문에 Aline, Bline 중 '0'으로 먼저 떨어지는 쪽이, 슈피리어 엔코딩부(10)에서 변환된 신호가 최상위 비트 쪽으로부터 먼저 '1'이 나오는 쪽이 된다. 즉, 최상위 비트 방향에서부터 일정 시간 간격으로 각각의 비트를 경쟁시켜서, 먼저 '1'이 나오는 쪽이 해당 라인을 먼저 '0'으로 떨어뜨리게 되며, 먼저 떨어지는 쪽이 큰 수가 된다. Therefore, since the START signal is activated from the most significant bit, the one falling first to '0' among Aline and Bline, and the one from which the signal converted by the

따라서 판별부(30)에서 두 라인 중 먼저 '0'으로 떨어지는 쪽을 감지해 그 결과를 다음 비트의 결과에 상관없이 유지하도록 함으로써 판별 결과를 출력하게 된다. Therefore, the

도 5는 본 발명에 의한 판별부를 나타낸 회로구성도이다. 5 is a circuit configuration diagram showing a discriminating unit according to the present invention.

본 발명에 의한 판별부(30)는 센스앰프에 피드백 패스가 더해진 형태로써 START 신호는 센스앰프의 인에이블(enable) 신호와 같은 역할을 한다. The

이 START 신호가 '0' 일 때는 두 출력 Awin, Bwin을 비롯한 각 노드들이 VDD로 프리차지가 되게 되고, 이 START 신호가 '1'이 되면 회로 동작이 시작되게 된다. When this START signal is '0', each node including the two outputs Awin and Bwin is precharged to VDD. When this START signal is '1', circuit operation starts.

판별부(30)의 두 입력은 비트와이즈 컴페티션부(20)의 Aline과 Bline이 각각 인버터를 거친 입력됨에 따라 비트와이즈 컴페티션부(20)에서 비트간 경쟁하여 먼 저 이겨 '0'으로 떨어지는 라인은 인버터를 거치면서 먼저 '0'에서 '1'로 올라가게 되고, 센스앰프를 동작시켜 '1'을 유지하고 있던 두 출력 중 상대 라인에 해당하는 출력을 '0'으로 끌어 내리게 된다. 즉, 비트와이즈 컴페티션부(20)에서 A가 이겨 Aline이 Bline보다 먼저 '0'으로 떨어졌다면, 판별부(30)의 출력 Awin과 Bwin 중 Awin은 그대로 '1'이 유지되고 Bwin은 '0'으로 떨어지게 된다. As the two inputs of the

이와 같이 Awin과 Bwin이 결정되어 둘 중 하나가 '0'으로 떨어지게 되면 그 결과가 피드백되어 풋 트랜지스터를 끊게 되고, 결과값은 다음 비트 입력값에 상관없이 초기 결정값이 유지되게 된다. Thus, if Awin and Bwin are determined and one of them falls to '0', the result is fed back and the foot transistor is cut off.

위와 같은 방법으로 판별부(30)는 두 라인 중 먼저 '0'으로 떨어지는 쪽을 감지해 그 결과를 유지하는 역할을 수행하며, 이로써 두 숫자 중 어느 쪽이 큰 쪽인지 알 수 있게 된다. In the same manner as above, the

만약 두 수가 같다면, Aline과 Bline은 둘 다 '0'으로 떨어지지 않으므로 판별부(30)의 두 결과는 모두 '1'로 남아있게 된다. If the two numbers are the same, both Aline and Bline do not fall to '0' so that both results of the

따라서 판별부(30)의 두 결과가 모두 '1'로 남아있다면, 두 숫자의 크기가 같다고 판단할 수 있다.Therefore, if both results of the

본 실시예에서는 8비트 비트와이즈 컴페티션부(20)를 이용하여 두 8비트 수를 비교할 수 있음을 보았으며, 이것은 16비트, 32비트 또는 64비트로 확장되는 것이 가능하다. 하지만, 비트수가 길어지면 트리거링 하는 START신호를 발생시키는데 딜레이가 크게 소요되므로, 한 라인 쌍에 모든 비트를 경쟁시키는 것은 효과적이지 못하다. In the present embodiment, the 8-bit

따라서 32비트처럼 긴 비트 수를 비교할 때에는 8비트 단위로 나누어 8비트 비트와이즈 컴페티션부(20) 4개를 동시에 실행시키고, 마지막에 이것들 중 옳은 결과를 선택해 주는 간단한 먹스(Mux)를 추가시킴으로써 간단하게 구성할 수 있다. Therefore, when comparing the number of bits as long as 32 bits, it is easy to divide 4 bits into 8 bit units and execute four 8-bit

즉, 4개의 결과 중 최종 결과를 선택할 때는 최상위 비트로부터 우선순위를 주어 첫 번째 결과의 최상위 비트의 결과를 택하고, 만약 이것이 비겼다면 두 번째 최상위 비트의 결과를 택한다. 마찬가지 방법으로, 이것이 또 비겼다면 또 다음 최상위 비트의 결과를 택하는 방법으로 비교하면 숫자의 비트 수가 길다고 할지라도 늘어나는 딜레이의 페널티는 크지 않게 된다.In other words, when selecting the final result among the four results, the result is given the priority from the most significant bit to select the result of the most significant bit of the first result, and if this is empty, the result of the second most significant bit is selected. In the same way, if it is empty again and compares the result of the next most significant bit, the penalty of increasing delay is not great, even if the number of bits in the number is long.

위와 같이 비트와이즈 컴페티션을 통해 두 긴 숫자를 비교하는 비교기의 경우 각 비트 당 슈피리어 엔코딩을 위해 게이트 2개, 비트와이즈 컴페티션부(20)의 라인에 연결되는 4개의 트랜지스터로 구성할 수 있으며, 이외에 판별부(30)와 먹스만으로 두 긴 숫자의 비교기 구성이 가능함에 따라 기본의 뺄셈기를 기본으로 한 비교기가 소모하는 평균적인 트랜지스터의 개수와 비교하면 1/4 이하임을 알 수 있다. As described above, a comparator comparing two long numbers through bitwise partitioning may include four transistors connected to a line of two gates and a

더구나 비트 수가 길어질수록 그 차이는 더욱 크게 되는데 비트와이즈 컴페티션에 의한 본 발명의 비교기는 성능면에서 캐리 carry lookahead 방법을 사용한 뺄셈기보다 조금 느리기는 하지만 큰 차이가 없다. Moreover, the longer the number of bits becomes, the larger the difference becomes. Although the comparator of the present invention by bitwise competition is slightly slower than the subtractor using the carry carry lookahead method, there is no big difference.

즉, 표 1에 나타낸 바와 같이 32비트의 두 수를 비교할 경우, 트랜지스터의 숫자(면적 관련)와 최대 딜레이의 비교할 때 본 발명에 의해 비트와이즈 컴페티션에 의한 비교기는 훨씬 적은 트랜지스터 개수로도 비슷한 성능으로 두 수의 비교를 효율적으로 수행하게 된다.That is, when comparing two numbers of 32 bits as shown in Table 1, the comparator with bitwise competition according to the present invention has similar performance with a much smaller number of transistors when comparing the number of transistors (area related) with the maximum delay. This makes the comparison of two numbers more efficient.

상술한 바와 같이 본 발명은 반도체 집적회로에서 긴 비트의 두 숫자의 크기를 비교할 때 뺄셈기에 의한 연산 결과를 통해 판단하지 않고 두 숫자의 각 비트를 MSB로부터 비트단위로 각각 비교하여 먼저 1이 나오는 쪽의 숫자를 큰 수로 결정함으로써 트랜지스터 개수를 줄여 효율적인 크기 비교연산을 수행할 수 있는 이점이 있다. As described above, according to the present invention, when comparing the sizes of two long bits in a semiconductor integrated circuit, each bit of the two numbers is compared from the MSB bit by bit without being judged by the operation result of the subtractor. The number of transistors is determined to be a large number, so that the number of transistors can be reduced to perform an efficient size comparison.

Claims (6)

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060127879A KR100821616B1 (en) | 2006-12-14 | 2006-12-14 | Two numbers comparator in vlsi circuits |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020060127879A KR100821616B1 (en) | 2006-12-14 | 2006-12-14 | Two numbers comparator in vlsi circuits |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| KR100821616B1 true KR100821616B1 (en) | 2008-04-16 |

Family

ID=39571443

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020060127879A KR100821616B1 (en) | 2006-12-14 | 2006-12-14 | Two numbers comparator in vlsi circuits |

Country Status (1)

| Country | Link |

|---|---|

| KR (1) | KR100821616B1 (en) |

Cited By (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20160064047A1 (en) * | 2014-09-03 | 2016-03-03 | Micron Technology, Inc. | Comparison operations in memory |

| US9583163B2 (en) | 2015-02-03 | 2017-02-28 | Micron Technology, Inc. | Loop structure for operations in memory |

| US9659605B1 (en) | 2016-04-20 | 2017-05-23 | Micron Technology, Inc. | Apparatuses and methods for performing corner turn operations using sensing circuitry |

| US9697876B1 (en) | 2016-03-01 | 2017-07-04 | Micron Technology, Inc. | Vertical bit vector shift in memory |

| US9741399B2 (en) | 2015-03-11 | 2017-08-22 | Micron Technology, Inc. | Data shift by elements of a vector in memory |

| US9747961B2 (en) | 2014-09-03 | 2017-08-29 | Micron Technology, Inc. | Division operations in memory |

| US9830999B2 (en) | 2014-06-05 | 2017-11-28 | Micron Technology, Inc. | Comparison operations in memory |

| US9892767B2 (en) | 2016-02-12 | 2018-02-13 | Micron Technology, Inc. | Data gathering in memory |

| US9898252B2 (en) | 2014-09-03 | 2018-02-20 | Micron Technology, Inc. | Multiplication operations in memory |

| US9898253B2 (en) | 2015-03-11 | 2018-02-20 | Micron Technology, Inc. | Division operations on variable length elements in memory |

| US9904515B2 (en) | 2014-09-03 | 2018-02-27 | Micron Technology, Inc. | Multiplication operations in memory |

| US9910637B2 (en) | 2016-03-17 | 2018-03-06 | Micron Technology, Inc. | Signed division in memory |

| US10032493B2 (en) | 2015-01-07 | 2018-07-24 | Micron Technology, Inc. | Longest element length determination in memory |

| US10042608B2 (en) | 2016-05-11 | 2018-08-07 | Micron Technology, Inc. | Signed division in memory |

| US10043570B1 (en) | 2017-04-17 | 2018-08-07 | Micron Technology, Inc. | Signed element compare in memory |

| US10146537B2 (en) | 2015-03-13 | 2018-12-04 | Micron Technology, Inc. | Vector population count determination in memory |

| US10147467B2 (en) | 2017-04-17 | 2018-12-04 | Micron Technology, Inc. | Element value comparison in memory |

| US10153008B2 (en) | 2016-04-20 | 2018-12-11 | Micron Technology, Inc. | Apparatuses and methods for performing corner turn operations using sensing circuitry |

| US10607665B2 (en) | 2016-04-07 | 2020-03-31 | Micron Technology, Inc. | Span mask generation |

| US11029951B2 (en) | 2016-08-15 | 2021-06-08 | Micron Technology, Inc. | Smallest or largest value element determination |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01142824A (en) * | 1987-11-28 | 1989-06-05 | Mitsubishi Electric Corp | Comparator |

-

2006

- 2006-12-14 KR KR1020060127879A patent/KR100821616B1/en not_active IP Right Cessation

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01142824A (en) * | 1987-11-28 | 1989-06-05 | Mitsubishi Electric Corp | Comparator |

Cited By (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9830999B2 (en) | 2014-06-05 | 2017-11-28 | Micron Technology, Inc. | Comparison operations in memory |

| US10593418B2 (en) | 2014-06-05 | 2020-03-17 | Micron Technology, Inc. | Comparison operations in memory |

| US11205497B2 (en) | 2014-06-05 | 2021-12-21 | Micron Technology, Inc. | Comparison operations in memory |

| US9940981B2 (en) | 2014-09-03 | 2018-04-10 | Micron Technology, Inc. | Division operations in memory |

| US10705798B2 (en) | 2014-09-03 | 2020-07-07 | Micron Technology, Inc. | Multiplication operations in memory |

| US20160064047A1 (en) * | 2014-09-03 | 2016-03-03 | Micron Technology, Inc. | Comparison operations in memory |

| US9747961B2 (en) | 2014-09-03 | 2017-08-29 | Micron Technology, Inc. | Division operations in memory |

| US9589602B2 (en) * | 2014-09-03 | 2017-03-07 | Micron Technology, Inc. | Comparison operations in memory |

| US10409554B2 (en) | 2014-09-03 | 2019-09-10 | Micron Technology, Inc. | Multiplication operations in memory |

| US10409555B2 (en) | 2014-09-03 | 2019-09-10 | Micron Technology, Inc. | Multiplication operations in memory |

| US9898252B2 (en) | 2014-09-03 | 2018-02-20 | Micron Technology, Inc. | Multiplication operations in memory |

| US10713011B2 (en) | 2014-09-03 | 2020-07-14 | Micron Technology, Inc. | Multiplication operations in memory |

| US9904515B2 (en) | 2014-09-03 | 2018-02-27 | Micron Technology, Inc. | Multiplication operations in memory |

| US9779789B2 (en) | 2014-09-03 | 2017-10-03 | Micron Technology, Inc. | Comparison operations in memory |

| US9940985B2 (en) | 2014-09-03 | 2018-04-10 | Micron Technology, Inc. | Comparison operations in memory |

| US10032493B2 (en) | 2015-01-07 | 2018-07-24 | Micron Technology, Inc. | Longest element length determination in memory |

| US10593376B2 (en) | 2015-01-07 | 2020-03-17 | Micron Technology, Inc. | Longest element length determination in memory |

| US10984841B2 (en) | 2015-01-07 | 2021-04-20 | Micron Technology, Inc. | Longest element length determination in memory |

| US10176851B2 (en) | 2015-02-03 | 2019-01-08 | Micron Technology, Inc. | Loop structure for operations in memory |

| US9583163B2 (en) | 2015-02-03 | 2017-02-28 | Micron Technology, Inc. | Loop structure for operations in memory |

| US9928887B2 (en) | 2015-03-11 | 2018-03-27 | Micron Technology, Inc. | Data shift by elements of a vector in memory |

| US9898253B2 (en) | 2015-03-11 | 2018-02-20 | Micron Technology, Inc. | Division operations on variable length elements in memory |

| US9741399B2 (en) | 2015-03-11 | 2017-08-22 | Micron Technology, Inc. | Data shift by elements of a vector in memory |

| US10146537B2 (en) | 2015-03-13 | 2018-12-04 | Micron Technology, Inc. | Vector population count determination in memory |

| US11663005B2 (en) | 2015-03-13 | 2023-05-30 | Micron Technology, Inc. | Vector population count determination via comparsion iterations in memory |

| US10896042B2 (en) | 2015-03-13 | 2021-01-19 | Micron Technology, Inc. | Vector population count determination via comparison iterations in memory |

| US10026459B2 (en) | 2016-02-12 | 2018-07-17 | Micron Technology, Inc. | Data gathering in memory |

| US9892767B2 (en) | 2016-02-12 | 2018-02-13 | Micron Technology, Inc. | Data gathering in memory |

| US9697876B1 (en) | 2016-03-01 | 2017-07-04 | Micron Technology, Inc. | Vertical bit vector shift in memory |

| US9947376B2 (en) | 2016-03-01 | 2018-04-17 | Micron Technology, Inc. | Vertical bit vector shift in memory |

| US9910637B2 (en) | 2016-03-17 | 2018-03-06 | Micron Technology, Inc. | Signed division in memory |

| US10409557B2 (en) | 2016-03-17 | 2019-09-10 | Micron Technology, Inc. | Signed division in memory |

| US10607665B2 (en) | 2016-04-07 | 2020-03-31 | Micron Technology, Inc. | Span mask generation |

| US11437079B2 (en) | 2016-04-07 | 2022-09-06 | Micron Technology, Inc. | Span mask generation |

| US10699756B2 (en) | 2016-04-20 | 2020-06-30 | Micron Technology, Inc. | Apparatuses and methods for performing corner turn operations using sensing circuitry |

| US10153008B2 (en) | 2016-04-20 | 2018-12-11 | Micron Technology, Inc. | Apparatuses and methods for performing corner turn operations using sensing circuitry |

| US9990967B2 (en) | 2016-04-20 | 2018-06-05 | Micron Technology, Inc. | Apparatuses and methods for performing corner turn operations using sensing circuitry |

| US9659605B1 (en) | 2016-04-20 | 2017-05-23 | Micron Technology, Inc. | Apparatuses and methods for performing corner turn operations using sensing circuitry |

| US10540144B2 (en) | 2016-05-11 | 2020-01-21 | Micron Technology, Inc. | Signed division in memory |

| US10042608B2 (en) | 2016-05-11 | 2018-08-07 | Micron Technology, Inc. | Signed division in memory |

| US11029951B2 (en) | 2016-08-15 | 2021-06-08 | Micron Technology, Inc. | Smallest or largest value element determination |

| US11526355B2 (en) | 2016-08-15 | 2022-12-13 | Micron Technology, Inc. | Smallest or largest value element determination |

| US10622034B2 (en) | 2017-04-17 | 2020-04-14 | Micron Technology, Inc. | Element value comparison in memory |

| US10147467B2 (en) | 2017-04-17 | 2018-12-04 | Micron Technology, Inc. | Element value comparison in memory |

| US10043570B1 (en) | 2017-04-17 | 2018-08-07 | Micron Technology, Inc. | Signed element compare in memory |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100821616B1 (en) | Two numbers comparator in vlsi circuits | |

| JPH07105726B2 (en) | Priority encoder | |

| JPH08339291A (en) | Selection circuit of maximum value | |

| JPH1093424A (en) | Decision circuit | |

| US5944771A (en) | Arithmetic operation system for binary addition/subtraction | |

| US7271703B2 (en) | 2-bit binary comparator and binary comparing device using the same | |

| US4903005A (en) | Comparator circuit | |

| US7439774B2 (en) | Multiplexing circuit for decreasing output delay time of output signal | |

| KR101540539B1 (en) | Magnitude Comparator Using Logic Gates | |

| US5148057A (en) | Circuit apparatus for detecting preceding value one | |

| JP3712508B2 (en) | N-bit comparator | |

| US6177862B1 (en) | High speed comparator | |

| US6195673B1 (en) | FOD (first-one-detector) circuit | |

| US6665698B1 (en) | High speed incrementer/decrementer | |

| CN115940921A (en) | bus buffer circuit | |

| US7349937B2 (en) | Fast incrementer using zero detection and increment method thereof | |

| US20040015534A1 (en) | Method for adding one to a binary number | |

| KR100486255B1 (en) | Data detection circuit and method | |

| US5635862A (en) | High-speed block id encoder circuit using dynamic logic | |

| US20040001505A1 (en) | Circuit for adding one to a binary number | |

| KR100321740B1 (en) | Comparator | |

| US6895420B1 (en) | Apparatus and method for sharing data FET for a four-way multiplexer | |

| KR100201030B1 (en) | Select encoder network | |

| US8010586B2 (en) | Apparatus and method of generating DBI signal in semiconductor integrated circuit | |

| JP5521784B2 (en) | Data transmission system, apparatus and method |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20120330 Year of fee payment: 5 |

|

| LAPS | Lapse due to unpaid annual fee |