CN111240849A - Deadlock detection circuit and detection method for asynchronous pipeline circuit - Google Patents

Deadlock detection circuit and detection method for asynchronous pipeline circuit Download PDFInfo

- Publication number

- CN111240849A CN111240849A CN202010020665.4A CN202010020665A CN111240849A CN 111240849 A CN111240849 A CN 111240849A CN 202010020665 A CN202010020665 A CN 202010020665A CN 111240849 A CN111240849 A CN 111240849A

- Authority

- CN

- China

- Prior art keywords

- station

- upstream

- detection

- matching circuit

- asynchronous

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/52—Program synchronisation; Mutual exclusion, e.g. by means of semaphores

- G06F9/524—Deadlock detection or avoidance

Landscapes

- Engineering & Computer Science (AREA)

- Software Systems (AREA)

- Theoretical Computer Science (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Pipeline Systems (AREA)

Abstract

A deadlock detection circuit of an asynchronous pipeline circuit is installed on an asynchronous pipeline and comprises an upstream detection matching circuit and a downstream feature matching circuit; the upstream detection matching circuit is connected in parallel with the sending end water station of the protected asynchronous water flowing section and is used for judging whether the sending end water flowing station is an error upstream water flowing station or not according to detection completion signals of the input end and the output end of the sending end water flowing station; the downstream characteristic matching circuit is connected with a receiving end water station of the protected asynchronous water flowing section in parallel and used for judging whether the receiving end water station is an error downstream water station or not according to the detection completion signals of the input end and the output end of the receiving end water station; and the upstream detection matching circuit is in communication connection with the downstream characteristic matching circuit and is used for judging whether the protected asynchronous flow section is deadlocked or not according to the error states of the upstream flow station and the downstream flow station. The technical scheme provided by the invention can detect the circuit deadlock caused by the error and simultaneously position the error occurrence position causing the asynchronous pipeline circuit deadlock.

Description

Technical Field

The invention relates to the field of asynchronous circuit design, in particular to a deadlock detection circuit and a deadlock detection method for an asynchronous pipeline circuit.

Background

The asynchronous pipeline is a typical scene of asynchronous circuit design, because the asynchronous pipeline is controlled by adopting an asynchronous handshake signal, a global clock is eliminated, the asynchronous pipeline has the characteristic of data driving, a series of problems and challenges faced by the traditional synchronous circuit can be effectively overcome, particularly the problem of clock domain crossing caused by global clock distribution, the asynchronous pipeline has the advantages of low dynamic power consumption, robust time sequence, good electromagnetic compatibility, good expansibility, modular design support and the like, and the asynchronous pipeline is widely regarded by academia and the industrial industry.

One important indicator of designing an asynchronous pipeline is fault tolerance. Along with the great reduction of the size of a semiconductor process, the power supply voltage of a chip is continuously reduced, the clock frequency is continuously improved, the density of the chip is continuously increased, electronic devices are more sensitive to environmental changes, various noise sources, high-energy particle radiation and the like can easily cause signal transmission delay and instantaneous turnover, time sequence errors caused by signal transmission delay changes, instantaneous logic errors caused by signal short-time error turnover, permanent logic errors caused by manufacturing defects or long-term running abrasion and the like, the occurrence probability is greatly increased, and the negative influences are brought to the reliability of an asynchronous production line. In an asynchronous pipeline, a logic error of 1 bit can not only pollute data, but also disturb or even destroy the handshake process, so that a handshake request cannot get a response, or when the response is completed, the pipeline cannot receive a new request, resulting in 'circuit deadlock' of the asynchronous pipeline.

Logical errors can be divided into transient errors and permanent errors. Common instantaneous errors are the positive direction, namely high level, or the negative direction, namely low level, glitch signal jump, the circuit is not damaged, the errors can be automatically eliminated in a short time after the errors occur, and the following signal change cannot be influenced; in order to simplify the behavior analysis of the permanent errors, the permanent errors are usually modeled by using a "stuck-at" gate-level error model, which includes two types of errors, stuck-at-0 and stuck-at-1, and respectively indicates that the value of a certain signal is permanently 0 or 1. The probability of permanent errors is small, but the harmfulness is high, and once the permanent errors occur, the circuit without the fault-tolerant mechanism basically means the abandonment of the circuit. In the conventional synchronous circuit, whether the transient error or the permanent error is caused, the main error performance is the data error, the circuit is still in operation, and the detection of the transient error or the permanent error can be realized by continuously collecting the error state of the circuit. For example, transient errors can be easily detected by using fault-tolerant coding, and when a plurality of transient errors are continuously detected at the same place, permanent errors can be determined to occur at the same place based on the assumption that the probability of the errors occurring at the same place is very low.

The core of asynchronous circuit design is the asynchronous protocol. The four-segment 1-of-n asynchronous handshake protocol is one of the most commonly used asynchronous protocols, is a general term for the four-segment handshake protocol and the 1-of-n data encoding mode, and has been widely applied to the design of quasi-delay insensitive asynchronous pipelines. The asynchronous assembly line is composed of a plurality of asynchronous flow stations and links connecting the flow stations, and any two stages of asynchronous flow stations can be respectively abstracted into sending end asynchronous flow stations and receiving end asynchronous flow stations according to the flow direction of data. Two adjacent asynchronous water flow stations are connected through a forward data link and a reverse response link.

The quasi-delay insensitive asynchronous pipeline realized by using the four-section 1-of-n asynchronous handshake protocol can effectively overcome timing errors, is very attractive for large-scale long-distance on-chip communication, and still suffers from circuit deadlock caused by logic errors.

The fault-tolerant technology oriented to the asynchronous circuit is less researched, once the circuit deadlock occurs in the asynchronous production line, firstly, the deadlock detection is needed, the error is positioned, and then the error recovery can be carried out. Therefore, the detection of deadlocks is crucial. Most of traditional fault-tolerant methods for synchronous circuits realize detection of instantaneous errors or permanent errors by continuously collecting error states of the circuits, while in a circuit deadlock state, an asynchronous production line falls into a stagnation state, a detection circuit can only obtain the current production line state, cannot obtain error information accumulated continuously along with time, and is difficult to effectively realize deadlock detection.

Therefore, in order to overcome the above-mentioned drawbacks, the present invention provides a low-complexity and highly scalable deadlock detection circuit and detection method, which can detect a circuit deadlock caused by an error and locate a position where the error causing the asynchronous pipeline circuit deadlock occurs.

Disclosure of Invention

In order to solve the above-mentioned deficiencies in the prior art, the present invention provides a deadlock detection circuit and a deadlock detection method for an asynchronous pipeline circuit.

The technical scheme provided by the invention is as follows:

in a deadlock detection circuit for an asynchronous pipeline circuit, mounted on an asynchronous pipeline, the improvement wherein the circuit comprises an upstream detection matching circuit and a downstream feature matching circuit;

the upstream detection matching circuit is connected in parallel with the sending end water station of the protected asynchronous water flowing section and is used for judging whether the sending end water flowing station is an error upstream water flowing station or not according to detection completion signals of the input end and the output end of the sending end water flowing station;

the downstream characteristic matching circuit is connected with a receiving end water station of the protected asynchronous water flowing section in parallel and used for judging whether the receiving end water station is an error downstream water station or not according to the detection completion signals of the input end and the output end of the receiving end water station;

and the upstream detection matching circuit is in communication connection with the downstream characteristic matching circuit and is used for judging whether the protected asynchronous flow section is deadlocked or not according to the error states of the upstream flow station and the downstream flow station.

Preferably, the upstream detection matching circuit comprises a rollover detector, an upstream feature matcher, a synchronizer, a control state machine and a clock counter;

the turnover detector comprises two input ends and an output end; a first input end of the turnover detector is connected to a detection completion signal of an output end of the water station at the sending end, and a second input end of the turnover detector is connected with the control state machine; the upstream feature matcher comprises three input ends and one output end; the output end of the turnover detector is connected with the first input end of the upstream feature matcher; a second input end of the upstream feature matcher is accessed to a detection completion signal at the output end of the sending-end water station, and a third input end of the upstream feature matcher is accessed to a detection completion signal at the input end of the sending-end water station;

the system comprises an upstream feature matcher, a synchronizer and a control state machine, wherein the upstream feature matcher, the synchronizer and the control state machine are sequentially connected, and the synchronizer is used for synchronizing signals output by the upstream feature matcher according to a clock of the control state machine and sending generated signals to the control state machine;

the clock counter is connected with the control state machine and is used for sending an overtime signal to the control state machine;

the control state machine is in communication connection with the downstream feature matching circuit and is used for sending an inquiry signal to the downstream feature matching circuit and receiving a response of the downstream feature matching circuit so as to judge whether the protected asynchronous pipeline section is deadlocked or not;

and the control state machine is connected with the external circuit and is used for informing the external circuit that the protected asynchronous pipeline section is deadlocked.

Preferably, the upstream feature matcher comprises an exclusive or gate (11) and an and gate (12);

two input ends of the exclusive-OR gate (11) are respectively connected to the detection completion signals of the input end and the output end of the transmitting end flowing water station; the output end of the exclusive-OR gate (11) is connected with one input end of the AND gate (12); the output end of the turnover detector is connected with the other input end of the AND gate (12).

Preferably, the downstream feature matching circuit comprises: an exclusive-nor gate (9) and an asymmetric C unit (8);

two input ends of the exclusive OR gate (9) are respectively connected with input and output completion detection signals of a receiving end water station, and an output end of the exclusive OR gate (9) is connected with a positive input end of the asymmetric C unit (8);

and the common input end of the asymmetric C unit (8) is connected with the control state machine, and the output end of the asymmetric C unit (8) is also connected with the control state machine and used for realizing communication connection with the upstream detection matching circuit.

A deadlock detection method of a deadlock detection circuit of an asynchronous pipeline circuit, the method comprising:

when the upstream detection matching circuit detects that the water station at the sending end of the protected asynchronous water flow section is an error upstream water flow station, the upstream detection matching circuit communicates with the downstream feature matching circuit;

if the downstream feature matching circuit detects that the receiving end water station of the protected asynchronous water flow section is also an error downstream water flow station, judging that the protected asynchronous water flow section is deadlocked, and informing the upstream detection matching circuit;

and the upstream detection matching circuit informs an external circuit of deadlock of the protected asynchronous pipeline section.

Preferably, when the upstream detection matching circuit detects that the sending-end water flow station of the protected asynchronous water flow section is the wrong upstream water flow station, the communication with the downstream feature matching circuit includes:

the upstream detection matching circuit starts signal turnover detection of the water flowing station at the sending end and characteristic matching of an error upstream water flowing station according to a set time period;

if the completion detection signal of the output end of the transmitting end water flow station is detected not to generate signal inversion in a set time period, and the transmitting end water flow station is successfully matched with the characteristics of the assembly line error upstream water flow station with deadlock, the transmitting end water flow station of the protected asynchronous water flow section is judged to be the error upstream water flow station, a downstream characteristic matching circuit is informed, and deadlock error detection is started; otherwise, the upstream detection matching circuit continuously detects whether the error occurs in the water flow station at the sending end of the protected asynchronous water flow section.

Preferably, if the downstream feature matching circuit detects that the receiving-end water flow station of the protected asynchronous water flow segment is also an erroneous downstream water flow station, it determines that the protected asynchronous water flow segment is deadlocked, and notifies the upstream detection matching circuit, including:

after receiving the notification of the upstream detection matching circuit, the downstream feature matching circuit starts feature matching between the receiving end flow station and the wrong downstream flow station, and continues to detect signal inversion of the upstream sending end flow station, if the receiving end flow station successfully matches the features of the assembly line wrong downstream flow station with deadlock in a set time period and the upstream receiving end flow station does not detect signal inversion, the receiving end flow station of the protected asynchronous flow section is judged to be the wrong downstream flow station, and the upstream detection matching circuit is notified;

otherwise, continuing waiting for the notification of the upstream detection matching circuit, and starting to detect whether the error occurs in the receiving end water flow station of the protected asynchronous water flow section again.

Preferably, the pipeline error upstream pipeline station characteristic of the deadlock comprises:

the completion detection signal output by the sending end water flow station is not turned over, the completion detection signal input and output by the sending end water flow station presents the alternating characteristics of 0 and 1, and the current time period is finished;

the wrong downstream waterflow station features include: the characteristic state of the sending end water station is an error state, the detection completion signals input and output by the receiving end water station present the characteristics of all 0 or all 1, and the current time period is finished;

the completion detection signal comprises 0 and 1, wherein 0 represents that the corresponding asynchronous pipelining station has completed the reset operation in the four-segment handshake protocol and is in the setting state; 1 represents that the corresponding asynchronous pipelining station has completed the set operation in the four-segment handshake protocol, and is in the state of being reset.

Compared with the prior art, the invention has the beneficial effects that:

according to the technical scheme provided by the invention, the upstream detection matching circuit is arranged at the stream station at the sending end of the asynchronous stream section, the downstream characteristic matching circuit is arranged at the stream station at the receiving end, and the upstream detection matching circuit and the downstream characteristic matching circuit are in communication connection, so that when a handshake protocol is damaged and a circuit deadlock occurs due to an error in an asynchronous pipeline, the circuit deadlock caused by the error can be detected, meanwhile, the error occurrence position causing the circuit deadlock of the asynchronous pipeline is positioned, and necessary information is provided for the elimination of the asynchronous pipeline deadlock and the recovery of the error.

The technical scheme provided by the invention has low complexity and high expandability, and is easy to understand and popularize.

Drawings

FIG. 1 is a block diagram of a deadlock detection circuit of an asynchronous pipelining station according to the present invention;

FIG. 2 is a schematic diagram of a deadlock detection method of an asynchronous water station according to the present invention;

FIG. 3 is a diagram of a four-stage 1-of-n asynchronous pipeline abstraction model according to the present invention;

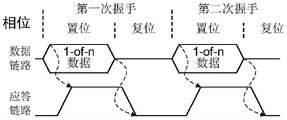

FIG. 4 is a timing diagram of a four-segment 1-of-n asynchronous handshake protocol according to the present invention;

FIG. 5 is a schematic diagram of the internal structure and external connection of the asynchronous water station of the present invention;

FIG. 6 is a downstream feature matching circuit of the present invention;

FIG. 7 is an upstream detection matching circuit of the present invention;

FIG. 8 is a diagram of the rollover detector of the present invention;

FIG. 9 is a schematic diagram of the operation of the control state machine of the present invention;

FIG. 10 is a block diagram of an implementation of the asynchronous flow station circuit of the present invention;

wherein: 1-sending a completion detection signal acko _ s at the output end of the end-side pipelining station; 2-sending a completion detection signal acki _ s at the input end of the end-to-end pipelining station; 3-completion detection signal acko _ r at the output end of the receiving end pipelining station; 4-completion detection signal acki _ r at the input end of the receiving end pipelining station; 5-the upstream detection matching circuit inquires a signal enquiry of the state of the receiving end flowing water station; 6-a signal deadlock _ ack which is output by the downstream characteristic matching circuit and reflects the characteristic state of the receiving end water station; 7-the upstream detection matching circuit outputs a signal deadlocking _ conf reflecting the final deadlock detection state to the external circuit; 8-asymmetric C-cell; 9-XNOR gate; 10-output signal r1 at the output of the exclusive nor gate 9; 11-exclusive or gate; 12-an and gate; 13-the output signal diff _ s of the exclusive or gate 11; 14-output signal s1 of and gate 12; 15-signal s2 generated after output signal s1 of and gate 12 is synchronized; 16-control the output signal start of the state machine; 17-output signal act of the rollover detector; 18-timeout signal timeout output by clock counter; 19-an asynchronous latch; 20-C unit.

Detailed Description

For a better understanding of the present invention, reference is made to the following description taken in conjunction with the accompanying drawings and examples.

Examples 1,

A deadlock detection circuit of an asynchronous pipeline circuit is installed on an asynchronous pipeline, as shown in figure 1, and comprises an upstream detection matching circuit and a downstream feature matching circuit;

the upstream detection matching circuit is connected in parallel with the sending end water station of the protected asynchronous water flowing section and is used for judging whether the sending end water flowing station is an error upstream water flowing station or not according to detection completion signals of the input end and the output end of the sending end water flowing station;

the downstream characteristic matching circuit is connected with a receiving end water station of the protected asynchronous water flowing section in parallel and used for judging whether the receiving end water station is an error downstream water station or not according to the detection completion signals of the input end and the output end of the receiving end water station;

and the upstream detection matching circuit is in communication connection with the downstream characteristic matching circuit and is used for judging whether the protected asynchronous flow section is deadlocked or not according to the error states of the upstream flow station and the downstream flow station.

Specifically, the upstream detection matching circuit comprises a rollover detector, an upstream feature matcher, a synchronizer, a control state machine and a clock counter;

the turnover detector comprises two input ends and an output end; a first input end of the turnover detector is connected to a detection completion signal of an output end of the water station at the sending end, and a second input end of the turnover detector is connected with the control state machine; the upstream feature matcher comprises three input ends and one output end; the output end of the turnover detector is connected with the first input end of the upstream feature matcher; a second input end of the upstream feature matcher is accessed to a detection completion signal at the output end of the sending-end water station, and a third input end of the upstream feature matcher is accessed to a detection completion signal at the input end of the sending-end water station;

the system comprises an upstream feature matcher, a synchronizer and a control state machine, wherein the upstream feature matcher, the synchronizer and the control state machine are sequentially connected, and the synchronizer is used for synchronizing signals output by the upstream feature matcher according to a clock of the control state machine and sending generated signals to the control state machine;

the clock counter is connected with the control state machine and is used for sending an overtime signal to the control state machine;

the control state machine is in communication connection with the downstream feature matching circuit and is used for sending an inquiry signal to the downstream feature matching circuit and receiving a response of the downstream feature matching circuit so as to judge whether the protected asynchronous pipeline section is deadlocked or not;

and the control state machine is connected with the external circuit and is used for informing the external circuit that the protected asynchronous pipeline section is deadlocked.

Specifically, the upstream feature matcher comprises an exclusive or gate 11 and an and gate 12;

two input ends of the exclusive-or gate 11 are respectively connected to the detection completion signals of the input end and the output end of the transmission end flowing water station; the output end of the exclusive-or gate 11 is connected with one input end of the and gate 12; the output of the rollover detector is connected to the other input of the and gate 12.

Specifically, the downstream feature matching circuit includes: an exclusive or gate 9 and an asymmetric C cell 8;

two input ends of the exclusive or gate 9 are respectively connected with a detection completion signal of an input end and an output end of a receiving end water station, and an output end of the exclusive or gate 9 is connected with a positive input end of the asymmetric C unit 8;

and a common input end of the asymmetric C unit 8 is connected with the control state machine, and an output end of the asymmetric C unit 8 is also connected with the control state machine, and is used for realizing communication connection with the upstream detection matching circuit.

Examples 2,

A deadlock detection method using the deadlock detection circuit of the asynchronous pipeline circuit, as shown in fig. 2, includes:

step 1: when the upstream detection matching circuit detects that the water station at the sending end of the protected asynchronous water flow section is an error upstream water flow station, the upstream detection matching circuit communicates with the downstream feature matching circuit;

step 2: if the downstream feature matching circuit detects that the receiving end water station of the protected asynchronous water flow section is also an error downstream water flow station, judging that the protected asynchronous water flow section is deadlocked, and informing the upstream detection matching circuit;

and step 3: and the upstream detection matching circuit informs an external circuit of deadlock of the protected asynchronous pipeline section.

the upstream detection matching circuit starts signal turnover detection of the water flowing station at the sending end and characteristic matching of an error upstream water flowing station according to a set time period;

if the completion detection signal of the output end of the transmitting end water flow station is detected not to generate signal inversion in a set time period, and the transmitting end water flow station is successfully matched with the characteristics of the assembly line error upstream water flow station with deadlock, the transmitting end water flow station of the protected asynchronous water flow section is judged to be the error upstream water flow station, a downstream characteristic matching circuit is informed, and deadlock error detection is started; otherwise, the upstream detection matching circuit continuously detects whether the error occurs in the water flow station at the sending end of the protected asynchronous water flow section.

after receiving the notification of the upstream detection matching circuit, the downstream feature matching circuit starts feature matching between the receiving end flow station and the wrong downstream flow station, and continues to detect signal inversion of the upstream sending end flow station, if the receiving end flow station successfully matches the features of the assembly line wrong downstream flow station with deadlock in a set time period and the upstream receiving end flow station does not detect signal inversion, the receiving end flow station of the protected asynchronous flow section is judged to be the wrong downstream flow station, and the upstream detection matching circuit is notified;

otherwise, continuing waiting for the notification of the upstream detection matching circuit, and starting to detect whether the error occurs in the receiving end water flow station of the protected asynchronous water flow section again.

Specifically, the characteristics of the pipeline error upstream pipeline station where the deadlock occurs include:

the completion detection signal of the output end of the sending end water station is not turned, the completion detection signals of the input end and the output end of the sending end water station present the characteristic of 0 and 1 alternation, and the current time period is finished;

the wrong downstream waterflow station features include: the characteristic state of the water station at the sending end is an error state, the detection completion signals of the input end and the output end of the water station at the receiving end show the characteristics of all 0 or all 1, and the current time period is finished;

the completion detection signal comprises 0 and 1, wherein 0 represents that the corresponding asynchronous pipelining station has completed the reset operation in the four-segment handshake protocol and is in the setting state; 1 represents that the corresponding asynchronous pipelining station has completed the set operation in the four-segment handshake protocol, and is in the state of being reset.

And step 3: and the upstream feature matching circuit informs an external circuit of deadlock of the protected asynchronous pipeline section.

Examples 3,

The four-segment 1-of-n asynchronous handshake protocol is one of the most commonly used asynchronous protocols, is a general term for the four-segment handshake protocol and the 1-of-n data encoding mode, and has been widely applied to the design of quasi-delay insensitive asynchronous pipelines. The asynchronous pipeline is composed of a plurality of asynchronous flow stations and links connecting the flow stations, any two stages of asynchronous flow stations can be abstracted to be asynchronous flow stations of a sending end and a receiving end respectively according to the flow direction of data, and the data flow from left to right as shown in figure 3, so the flow stations 1 and 4 can be called asynchronous flow stations of the sending end and the receiving end respectively, and the adjacent flow stations of two stages are connected through forward data links and reverse response links. In fig. 3, the data signal transmitted by the forward data link adopts a 1-of-n data coding scheme, and the reverse response link transmits a response signal with a width of 1 bit. The 1-of-n data coding is also called unique heat coding, namely n binary bits are used for coding n decimal data from 0 to n-1, and each legal 1-of-n code word has only one effective bit, namely only one bit in each legal code word is 1 and other bits are 0. The timing diagram of the change of the data and the response signal in the four-segment handshake protocol is shown in fig. 4, each handshake process includes two "phases" of "set" and "reset", and therefore, the data transmitted in the pipeline alternately undergoes the processes of "set" and "reset": when the data is set, the data signal transmitted by the pipeline is gradually changed from all 0 s to complete 1-of-n data, the data is formed by one or more legal 1-of-n code words, the completion of the setting means that the receiving end water flow station receives the complete 1-of-n data, and at the moment, the value of a response signal generated by a completion detection circuit of the receiving end water flow station is changed into 1 and is reversely transmitted to the previous stage water flow station; when the data signal is reset, all the output data signals of the pipeline station at the sending end gradually become 0, and the completion of the reset indicates that all the output data signals of the pipeline station are inverted into 0 to separate legal 1-of-n data code words, the value of the response signal generated by the pipeline station at the receiving end becomes 0, and the response signal is reversely transmitted to the pipeline station at the previous stage.

The quasi-delay insensitive asynchronous pipeline realized by using the four-section 1-of-n asynchronous handshake protocol can effectively overcome timing errors, is very attractive for large-scale long-distance on-chip communication, and still suffers from circuit deadlock caused by logic errors. The forming process of circuit deadlock is illustrated by taking permanent errors occurring on a four-section 1-of-n asynchronous pipeline as an example: according to four-section 1-of-n asynchronous handshake protocol, under normal condition, if data transmission is started once, a sending end water flow station of a pipeline prepares 1-of-n coded data at first and waits for a receiving end water flow station to receive, and the receiving end water flow station responds according to the current self state: if the current receiving end is busy, the receiving end water flow station can not receive new data, and the generated response signal keeps low level continuously, which indicates that no request of the transmitting end is responded; the sending end keeps outputting 1-of-n data unchanged and waits for the receiving end to receive the data; when the receiving end is idle, the receiving end water station starts to receive data and carries out 'setting' operation, and after the receiving end receives complete 1-of-n data, the generated response signal is inverted to high level to inform the receiving end water station that 'resetting' can be started. Therefore, if in the process of setting, a permanent error causes that the response signal cannot be correctly inverted, that is, the value of the response signal is always 0, the sending end cannot know whether the receiving end has received the data, and only can keep the request state all the time, and the handshake protocol is damaged, so that the pipeline is stalled to generate circuit deadlock. A similar situation can also occur during the "reset" phase or on the data link, seriously threatening the reliability of the system.

In order to make the technical solution of the present invention more clear, the following description is made in detail in conjunction with a four-segment quasi-delay insensitive asynchronous pipeline basic link model.

Selecting a four-section handshake protocol and a delay insensitive coding mode, designing an asynchronous pipeline basic link model, wherein the whole pipeline comprises a plurality of asynchronous flow stations, the flow stations are formed by connecting forward data links and backward response links, and other combinational logics among the flow stations are not considered, as shown in fig. 5, the asynchronous pipeline basic link model is characterized in that:

a. data transmitted in the pipeline is encoded using delay insensitive encoding, typical delay insensitive encoding including 1-of-n encoding, with the data passing through the pipeline along the forward data link via multiple stages of asynchronous watersheds. Thus, the data link is actually made up of a plurality of parallel interconnecting metal lines, the width of which is determined by the encoding scheme employed and the width of the individual data packets.

b. The asynchronous water station has the same structure and is composed of a plurality of asynchronous latches 19 connected in parallel and a completion detection circuit, as shown in fig. 10. The asynchronous latch 19 is used for latching and transmitting data and is formed by a plurality of C units 20. The completion detection circuit is present at the output of the asynchronous pipelining station and is capable of generating a 1-bit completion detection signal or response signal based on the output data of the asynchronous latch 19 of the pipelining station, which is transmitted back to the pipelining station at the previous stage via the response link and serves as its input. Thus, the forward flowing data and the reverse flowing completion detection signal or reply signal form a loop. The completion detection signal can reflect the state of the data output by the current pipeline station, for the completion detection circuit under the four-segment handshake protocol, the output completion detection signal can alternately go through the processes of 1 and 0 conversion, which respectively indicate that the pipeline station receives a complete data and completes the reset of the data, and the typical completion detection circuit is formed by a tree-shaped OR gate and a C unit. In a four-segment quasi-delay insensitive asynchronous pipeline, a data signal containing request information and a completion detection signal jointly reflect the request and response processes of asynchronous handshake. The asynchronous latch 19 may also be built from multiple D flip-flops.

Determining the granularity of deadlock detection according to fault tolerance requirements: the whole production line is divided into a plurality of flow sections, each flow section is an object protected by fault tolerance, therefore, if an error occurs in the protected flow section and causes circuit deadlock, the flow section where the error is located can be positioned, and the length of the flow section or the number of flow stations contained in the flow section reflects the granularity of deadlock detection.

The assembly line is divided into a plurality of assembly line sections according to the fault-tolerant requirement and the requirement of the circuit on the fault-tolerant overhead. Assuming that an asynchronous pipeline has n flow stations, under the condition of highest fault tolerance requirement, the asynchronous pipeline can be divided into n-1 flow sections, and each flow section comprises 2 flow stations; in the case of the lowest fault tolerance requirement, the whole pipeline is protected as 1 pipeline segment.

The finer the granularity of pipeline segmentation, the higher the fault tolerance capability, but the more redundant circuits are added, which leads to the increase of circuit area overhead and also influences the overall reliability of the system; the coarser the granularity of segmentation, the weaker the fault-tolerant capability, but the smaller the added redundant circuit, the smaller the area overhead brought, and the smaller the influence of the redundant circuit on the reliability of the whole system. The method needs to combine a circuit design flow, repeatedly and iteratively evaluate between the fault-tolerant capability requirement and the fault-tolerant design overhead, and determine the division granularity of the production line.

And adding a deadlock detection circuit for each pipeline segment to be protected, detecting and judging whether circuit deadlock occurs in the protected pipeline segment, and realizing error positioning. As shown in fig. 1, the deadlock detection circuit mainly includes an upstream detection matching circuit located at the pipelining station at the transmitting end of the pipelining segment, and a downstream feature matching circuit located at the pipelining station at the receiving end of the pipelining segment.

The working principle of the deadlock detection circuit is as follows: when a long data message flows through an asynchronous pipeline, a long data path is formed in the pipeline, and the path comprises a plurality of asynchronous pipeline stations, as shown in fig. 3, each asynchronous pipeline station alternately executes a setting process and a resetting process according to a four-segment handshake protocol, and both an instant error and a permanent error can destroy the four-segment handshake protocol to cause the established data path circuit to be deadlocked, thereby causing the whole asynchronous pipeline circuit to be deadlocked, and through analysis, the asynchronous pipeline after the deadlock shows the following characteristics: stopping the flow of the data message latched in the assembly line, and avoiding the overturning of any signal, including a data signal and a detection completion signal; the data message latched by the wrong upstream pipelining station is not polluted by errors, namely the data message without errors is blocked before the wrong pipelining section and can not continuously flow downwards, the phenomenon of 'one section empty and one section full' after the four-section handshake asynchronous pipelining is blocked is shown, and a completion detection signal generated by the wrong upstream pipelining station has the characteristic of alternation of 0 and 1; the data messages latched by the wrong downstream pipelining station may be contaminated by errors, which causes the wrong downstream asynchronous pipelining station to latch the same data, and further, the completion detection signal values of the wrong downstream asynchronous pipelining station are the same, which presents the characteristics of all 0 s or all 1 s. By adding a deadlock detection circuit for the pipeline section to be protected and judging whether the pipeline section meets the three characteristics, whether the pipeline section has circuit deadlock caused by errors can be judged, and therefore accurate detection and positioning of the circuit deadlock are achieved.

The deadlock detection circuit works as follows:

a. a downstream feature matching circuit is added at a receiving end water flowing station of a protected water flowing section, namely the last asynchronous water flowing station, as shown in fig. 6, whether the receiving end water flowing station meets the feature of a pipeline error downstream water flowing station with deadlock is judged, namely, a completion detection signal of the error downstream water flowing station presents the feature of all 0 or all 1, which can be judged by matching whether a completion detection signal acki _ r at an input end of a 4-receiving end asynchronous water flowing station and a completion detection signal acko _ r at an output end of a 5-receiving end asynchronous water flowing station are equal or not, and specifically realized by an exclusive or gate 9, if the two completion detection signals are equal, the two completion detection signals are all 0 or all 1, and the feature of the error downstream water flowing station is met, namely, the value of an output signal r1 at the output end of the exclusive or gate 9 is 1; if not, the output signal r1 at the output of 10 has a value of 0, indicating that the flow station is not the wrong downstream flow station. The downstream characteristic matching circuit receives 5 the enquiry signal output by the upstream detection matching circuit as an input, and outputs 6 signals deadlock _ ack which is output by the downstream characteristic matching circuit and reflects the characteristic state of the receiving end flowing water station to the upstream detection matching circuit according to the value of the output signal r1 at the output end of the 10-exclusive OR gate 9, wherein an asymmetric C unit 8 is used for generating 6 signals deadlock _ ack which is output by the downstream characteristic matching circuit and reflects the characteristic state of the receiving end flowing water station, the positive input end of the asymmetric C unit is connected with the output signal r1 at the output end of the 10-exclusive OR gate 9, and the common input end of the asymmetric C unit is connected with the signal enquiry which is output by the 5-upstream detection matching circuit and inquires the state of the receiving end flowing water station. When the upstream detection matching circuit queries the state of the receiving-end flowing water station, that is, when the value of the signal enquiry of the state of the receiving-end flowing water station queried by the 5 upstream detection matching circuit is 1, if the receiving-end flowing water station conforms to the characteristics of the deadlock-occurring pipeline error downstream flowing water station, that is, the value of the output signal r1 at the output end of the 10-exclusive-or 9 is 1, the value of the signal deadlock _ ack, which is output by the output 6 downstream characteristic matching circuit of the asymmetric C unit 8 and reflects the characteristic state of the receiving-end flowing water station, is 1, that is, the downstream characteristic matching circuit informs the upstream detection matching circuit that the receiving-end flowing water station conforms to the characteristics of the deadlock-occurring pipeline error downstream flowing water station. When the value of the signal enquiry for inquiring the state of the receiving-end running water station by the upstream detection matching circuit 5 is 0, no matter how much the value of the output signal r1 at the output end of the exclusive-nor gate 9 is, the value of the signal deadlock _ ack which is output by the downstream feature matching circuit 6 and reflects the feature state of the receiving-end running water station is always 0, which indicates that if the upstream detection matching circuit does not inquire the state of the receiving-end running water station.

b. An upstream detection matching circuit is added at a streaming station at a sending end of a protected streaming segment, as shown in fig. 7, the upstream detection matching circuit mainly comprises a rollover detector, an upstream feature matcher, a synchronizer, a control state machine and a clock counter, and has the following main functions:

1) the rollover detector, shown in fig. 8, is active low, i.e., low indicates that a rollover is detected. The roll-over detector comprises two input signals, 1 the completion detection signal acko _ s output by the sending end pipelining station and 16 the output signal start of the control state machine, and 17 the output signal act of the roll-over detector. The specific working principle is as follows: when the output signal start of the 16-control state machine is 0, the roll-over detector is in a non-operating state, and the output signal is 1 regardless of whether the value of the completion detection signal acko _ s output by the sending-end waterflow station is high or low. When the detected signal is 1, the turnover detector is in a working state and starts to detect the turnover state of the detected signal, when the detected value is not turned over, the output signal is kept to be 1, and once the detected signal is turned over, the output signal is changed to be 0. The output signal act of the 17 roll-over detector is connected to an upstream feature matcher.

Whether the signal is turned over is detected through a completion detection signal acko _ s at the output end of the sampling 1 sending end pipeline station, and whether the pipeline is empty or suspended is judged. If the completion detect signal is not detected to have a signal inversion for a period of time, then the pipeline segment has no data flowing during this period of time and the entire pipeline may be considered empty or stalled.

2) The upstream feature matcher is configured to match whether the sending-end pipelining station conforms to the feature of the pipeline error upstream pipelining station with the deadlock, that is, a completion detection signal of the error upstream pipelining station exhibits an alternate 0-1 feature, and this may be determined by matching a completion detection signal acki _ s at an input end of the sending-end pipelining station 2 and a completion detection signal acko _ s at an output end of the sending-end pipelining station 1, whether the completion detection signals acki _ s and the completion detection signal acko _ s are not equal, and specifically implemented by using an xor gate 11. If the two completion detection signals are not equal, the station meets the characteristics of the wrong upstream station, and the value of the 13 output signal diff _ s output through the exclusive or gate 11 is 1. 13-output signal diff _ s of exclusive or gate 11 and output signal act of the 17-flip detector are two inputs of and gate 12, thus output signal s1 of 14 and gate 12; 15-signal s2 generated after output signal s1 of and gate 12 is synchronized; the output signal s1 of the 16 control state machine can reflect the state of signal inversion and feature matching in time.

3) The synchronizer is located between the upstream feature matcher and the control state machine, and is used for synchronizing an output signal s1 of the and gate 12 output by the upstream feature matcher according to a clock of the control state machine, generating 15 the signal and sending the signal to the control state machine, so as to reduce the probability of metastable state occurrence.

4) The clock counter can count the edge transition of the clock signal, which is a necessary signal in the synchronous circuit, according to the predefined clock number clk _ num, not shown in the diagram, and every time the upper edge or the lower edge of the clock signal transitions clk _ num times, that is, after clk _ num clock cycles pass, the 18-clock counter outputs the timeout signal timeout of 1, and then when the next clock cycle arrives, the timeout signal timeout of the 18-clock counter outputs 0. In other words, every clk _ num clock cycles, the timeout signal timeout output from the 18-clock counter is 1, which controls the control state machine. The clk _ num should be set as large as possible according to the scale of the circuit, so as to ensure that the timeout period is long enough, and further improve the correctness of the pipeline state judgment.

5) The control state machine is a core circuit for realizing deadlock detection and controls the whole detection process. The input of the control state machine comprises a signal s2 generated by synchronizing an output signal s1 of a 15 AND gate 12 which is from a synchronizer and reflects the signal inversion and the characteristic matching state of a transmitting-end pipeline station, a timeout signal timeout which is from an 18-clock counter used for realizing a timeout mechanism, a deadlock _ ack signal which is output by a 6 downstream characteristic matching circuit and reflects the characteristic state of a receiving-end pipeline station, and a clock signal which is common to synchronous circuits, wherein the clock signal is an essential signal in the synchronous circuits and is not shown in FIG. 7; the output of the controller comprises an output signal start of a 16-control state machine which is output to a rollover detector and used for starting signal rollover detection, an enquiry signal which is output to a downstream feature matching circuit and used for inquiring the feature of a receiving-end flow station, and 7, an upstream detection matching circuit outputs a signal deadlocking _ conf which reflects a final deadlock detection state to an external circuit, if the deadlocking _ conf is 1, it is indicated that deadlock generated by an error is detected on the flow section, the flow section is an erroneous flow section, and the external circuit needs to process the error according to the deadlocking _ conf signal; if the deadline _ conf is 0, it indicates that the pipeline segment is normal, and no deadlock caused by an error occurs, and no fault-tolerant processing is needed. The core of the control state machine is a state machine realized by a synchronous circuit, which reflects the whole deadlock detection process, and the working flow schematic diagram of the control state machine is shown in fig. 9:

step 1: and when the upstream detection matching circuit detects that the water flow station at the sending end of the protected asynchronous water flow section is the wrong upstream water flow station, the upstream detection matching circuit communicates with the downstream feature matching circuit.

In the initial state, an output signal start of a 16 control state machine of the control state machine, a 5 upstream detection matching circuit queries a signal enquiry of the state of the receiving end flowing water station, and a 7 upstream detection matching circuit outputs a signal deadlock _ conf reflecting the final deadlock detection state to an external circuit, default to 0, a timeout signal timeout output by an 18 clock counter defaults to 0, and waits for the arrival of a first timeout signal.

After a timeout period, the timeout signal timeout output by the 18-clock counter is 1, the output signal start of the 16-control state machine is 1, the upstream detection matching circuit is started, the rollover detector starts to perform signal rollover detection on the detection completion signal from the sending-end water flow station, and the upstream feature matcher compares two continuous detection completion signals from the input end and the output end of the sending-end water flow station and observes the timeout signal. If any signal inversion is detected before the next timeout signal arrives, or the flow station does not match the characteristics of the wrong upstream flow station, that is, the completion detection signal acko _ s output by the 1 sending end flow station is equal to the completion detection signal acki _ s at the input end of the 2 sending end flow station, then the output signal s1 of the 14 and gate 12 is 0; the output signal s1 of the 15 and gate 12 is synchronized to generate a signal s2 which is 0, and the state machine circuit immediately returns to the initial state to start the next round of detection. If no signal inversion is detected within a timeout period and the sampled detection completion signals are not equal all the time, the signal s2 generated after the output signal s1 of the 15 and gate 12 is synchronized is 1, and then when the next timeout signal arrives, that is, the timeout signal timeout output by the 18-clock counter is 1, the state machine jumps to the next state and starts to query the state of the downstream feature matching circuit.

Step 2: and if the downstream feature matching circuit detects that the receiving end water flow station of the protected asynchronous water flow section is also an error downstream water flow station, judging that the protected asynchronous water flow section is deadlocked, and informing the upstream detection matching circuit.

And controlling an upstream detection matching circuit of the state machine 5 to inquire whether a signal enquiry of the state of the receiving end flow station is 1, matching whether the receiving end flow station accords with the characteristics of a production line error downstream flow station with deadlock or not, and continuously detecting signal turnover of the upstream sending end flow station. If the two continuous completion detection signals sampled by the downstream feature matching circuit from the input end and the output end of the receiving-end pipeline station are unequal before the next timeout signal arrives, the result is that the signal deadlock _ ack which is output by the downstream feature matching circuit 6 and reflects the feature state of the receiving-end pipeline station is 0, or the signal inversion is detected at the sending-end pipeline station, namely the signal s2 generated after the output signal s1 of the 15 and 12 is synchronized is 0, the pipeline is determined not to be deadlocked, and the control state machine immediately returns to the initial state. If the signal deadlock _ ack output by the downstream feature matching circuit 6 and reflecting the feature state of the receiving-end downstream water station is always 1 in the next timeout period, which indicates that the receiving-end downstream water station matches the feature of the wrong downstream water station and no signal inversion is detected, and the signal s2 generated after the output signal s1 of the gate 12 is synchronized 15 is 1, then when the next timeout signal arrives, that is, the timeout signal timeout output by the 18-clock counter is 1, the control state machine 7 outputs the signal deadlock _ conf output by the upstream feature matching circuit to the external circuit and reflecting the final deadlock detection state to be 1, and it is determined that the deadlock generated by the error is detected on the section of the water, which is the section of the error, so that the accurate positioning and detection of the error are realized.

And step 3: and the upstream detection matching circuit informs an external circuit of deadlock of the protected asynchronous pipeline section. The external circuit carries out fault-tolerant processing on the flow section in the deadlock state.

The above facts prove that, in the technical scheme provided by the invention, the upstream detection matching circuit is installed at the transmitting end of the pipelining station of the asynchronous pipelining segment, the downstream characteristic matching circuit is installed at the receiving end of the pipelining station, and the upstream detection matching circuit and the downstream characteristic matching circuit are in communication connection, so that when a handshake protocol is damaged and a circuit deadlock occurs due to an error in an asynchronous pipelining, the circuit deadlock caused by the error can be detected, meanwhile, the occurrence position of the error causing the circuit deadlock of the asynchronous pipelining is positioned, and necessary information is provided for the elimination of the asynchronous pipelining deadlock and the recovery of the error.

As will be appreciated by one skilled in the art, embodiments of the present application may be provided as a method, system, or computer program product. Accordingly, the present application may take the form of an entirely hardware embodiment, an entirely software embodiment or an embodiment combining software and hardware aspects. Furthermore, the present application may take the form of a computer program product embodied on one or more computer-usable storage media (including, but not limited to, disk storage, CD-ROM, optical storage, and the like) having computer-usable program code embodied therein.

The present application is described with reference to flowchart illustrations and/or block diagrams of methods, apparatus (systems), and computer program products according to embodiments of the application. It will be understood that each flow and/or block of the flow diagrams and/or block diagrams, and combinations of flows and/or blocks in the flow diagrams and/or block diagrams, can be implemented by computer program instructions. These computer program instructions may be provided to a processor of a general purpose computer, special purpose computer, embedded processor, or other programmable data processing apparatus to produce a machine, such that the instructions, which execute via the processor of the computer or other programmable data processing apparatus, create means for implementing the functions specified in the flowchart flow or flows and/or block diagram block or blocks.

These computer program instructions may also be stored in a computer-readable memory that can direct a computer or other programmable data processing apparatus to function in a particular manner, such that the instructions stored in the computer-readable memory produce an article of manufacture including instruction means which implement the function specified in the flowchart flow or flows and/or block diagram block or blocks.

These computer program instructions may also be loaded onto a computer or other programmable data processing apparatus to cause a series of operational steps to be performed on the computer or other programmable apparatus to produce a computer implemented process such that the instructions which execute on the computer or other programmable apparatus provide steps for implementing the functions specified in the flowchart flow or flows and/or block diagram block or blocks.

The present invention is not limited to the above embodiments, and any modifications, equivalent replacements, improvements, etc. made within the spirit and principle of the present invention are included in the scope of the claims of the present invention which are filed as the application.

Claims (8)

1. A deadlock detection circuit of an asynchronous pipeline circuit is installed on the asynchronous pipeline circuit and is characterized in that the circuit comprises an upstream detection matching circuit and a downstream feature matching circuit;

the upstream detection matching circuit is connected in parallel with the sending end water station of the protected asynchronous water flowing section and is used for judging whether the sending end water flowing station is an error upstream water flowing station or not according to detection completion signals of the input end and the output end of the sending end water flowing station;

the downstream characteristic matching circuit is connected with a receiving end water station of the protected asynchronous water flowing section in parallel and used for judging whether the receiving end water station is an error downstream water station or not according to the detection completion signals of the input end and the output end of the receiving end water station;

and the upstream detection matching circuit is in communication connection with the downstream characteristic matching circuit and is used for judging whether the protected asynchronous flow section is deadlocked or not according to the error states of the upstream flow station and the downstream flow station.

2. The deadlock detection circuit for an asynchronous pipeline circuit according to claim 1, wherein the upstream detection matching circuit comprises a rollover detector, an upstream feature matcher, a synchronizer, a control state machine, and a clock counter;

the turnover detector comprises two input ends and an output end; a first input end of the turnover detector is connected to a detection completion signal of an output end of the water station at the sending end, and a second input end of the turnover detector is connected with the control state machine; the upstream feature matcher comprises three input ends and one output end; the output end of the turnover detector is connected with the first input end of the upstream feature matcher; a second input end of the upstream feature matcher is accessed to a detection completion signal at the output end of the sending-end water station, and a third input end of the upstream feature matcher is accessed to a detection completion signal at the input end of the sending-end water station;

the system comprises an upstream feature matcher, a synchronizer and a control state machine, wherein the upstream feature matcher, the synchronizer and the control state machine are sequentially connected, and the synchronizer is used for synchronizing signals output by the upstream feature matcher according to a clock of the control state machine and sending generated signals to the control state machine;

the clock counter is connected with the control state machine and is used for sending an overtime signal to the control state machine;

the control state machine is in communication connection with the downstream feature matching circuit and is used for sending an inquiry signal to the downstream feature matching circuit and receiving a response of the downstream feature matching circuit so as to judge whether the protected asynchronous pipeline section is deadlocked or not;

and the control state machine is connected with the external circuit and is used for informing the external circuit that the protected asynchronous pipeline section is deadlocked.

3. Deadlock detection circuit of an asynchronous pipelined circuit according to claim 2 characterized in that said upstream feature matcher comprises an exclusive or gate (11) and an and gate (12);

two input ends of the exclusive-OR gate (11) are respectively connected to the detection completion signals of the input end and the output end of the transmitting end flowing water station; the output end of the exclusive-OR gate (11) is connected with one input end of the AND gate (12); the output end of the turnover detector is connected with the other input end of the AND gate (12).

4. The deadlock detection circuit of an asynchronous pipeline circuit according to claim 2, wherein the downstream feature matching circuit comprises: an exclusive-nor gate (9) and an asymmetric C unit (8);

two input ends of the exclusive OR gate (9) are respectively connected to detection completion signals of an input end and an output end of the receiving end water station, and an output end of the exclusive OR gate (9) is connected with a positive input end of the asymmetric C unit (8);

and the common input end of the asymmetric C unit (8) is connected with the control state machine, and the output end of the asymmetric C unit (8) is also connected with the control state machine and used for realizing communication connection with the upstream detection matching circuit.

5. A deadlock detection method for a deadlock detection circuit of an asynchronous pipeline circuit, the method comprising:

when the upstream detection matching circuit detects that the water station at the sending end of the protected asynchronous water flow section is an error upstream water flow station, the upstream detection matching circuit communicates with the downstream feature matching circuit;

if the downstream feature matching circuit detects that the receiving end water station of the protected asynchronous water flow section is also an error downstream water flow station, judging that the protected asynchronous water flow section is deadlocked, and informing the upstream detection matching circuit;

and the upstream detection matching circuit informs an external circuit of deadlock of the protected asynchronous pipeline section.

6. The deadlock detection method according to claim 5, wherein the communicating with the downstream feature matching circuit when the upstream detection matching circuit detects that the sending-end pipelining station of the protected asynchronous pipelining section is the wrong upstream pipelining station comprises:

the upstream detection matching circuit starts signal turnover detection of the water flowing station at the sending end and characteristic matching of an error upstream water flowing station according to a set time period;

if the completion detection signal output by the transmitting end water flow station is detected not to generate signal inversion in a set time period and the transmitting end water flow station is successfully matched with the characteristics of the assembly line error upstream water flow station with deadlock, judging that the transmitting end water flow station of the protected asynchronous water flow section is the error upstream water flow station, informing a downstream characteristic matching circuit, and starting deadlock error detection; otherwise, the upstream detection matching circuit continuously detects whether the error occurs in the water flow station at the sending end of the protected asynchronous water flow section.

7. The deadlock detection method according to claim 6, wherein, if the downstream feature matching circuit detects that the receiving-end site of the protected asynchronous pipeline segment is also the wrong downstream pipeline segment, determining that the deadlock occurs in the protected asynchronous pipeline segment, and notifying the upstream feature matching circuit, comprises:

after receiving the notification of the upstream detection matching circuit, the downstream feature matching circuit starts feature matching between the receiving end flow station and the wrong downstream flow station, and continues to detect signal inversion of the upstream sending end flow station, if the receiving end flow station successfully matches the features of the assembly line wrong downstream flow station with deadlock in a set time period and the upstream receiving end flow station does not detect signal inversion, the receiving end flow station of the protected asynchronous flow section is judged to be the wrong downstream flow station, and the upstream detection matching circuit is notified;

otherwise, continuing waiting for the notification of the upstream detection matching circuit, and starting to detect whether the error occurs in the receiving end water flow station of the protected asynchronous water flow section again.

8. The method of deadlock detection for an asynchronous pipeline circuit according to claim 7, wherein the characteristics of the pipeline error upstream pipeline station where a deadlock occurs comprise:

the completion detection signal of the output end of the sending end water station is not turned, the completion detection signals of the input end and the output end of the sending end water station present the characteristic of 0 and 1 alternation, and the current time period is finished;

the wrong downstream waterflow station features include: the characteristic state of the water station at the sending end is an error state, the detection completion signals of the input end and the output end of the water station at the receiving end show the characteristics of all 0 or all 1, and the current time period is finished;

the completion detection signal comprises 0 and 1, wherein 0 represents that the corresponding asynchronous pipelining station has completed the reset operation in the four-segment handshake protocol and is in the setting state; 1 represents that the corresponding asynchronous pipelining station has completed the set operation in the four-segment handshake protocol, and is in the state of being reset.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202010020665.4A CN111240849A (en) | 2020-01-09 | 2020-01-09 | Deadlock detection circuit and detection method for asynchronous pipeline circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| CN202010020665.4A CN111240849A (en) | 2020-01-09 | 2020-01-09 | Deadlock detection circuit and detection method for asynchronous pipeline circuit |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN111240849A true CN111240849A (en) | 2020-06-05 |

Family

ID=70866313

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN202010020665.4A Pending CN111240849A (en) | 2020-01-09 | 2020-01-09 | Deadlock detection circuit and detection method for asynchronous pipeline circuit |

Country Status (1)

| Country | Link |

|---|---|

| CN (1) | CN111240849A (en) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6738871B2 (en) * | 2000-12-22 | 2004-05-18 | International Business Machines Corporation | Method for deadlock avoidance in a cluster environment |

| CN109215728A (en) * | 2017-07-01 | 2019-01-15 | 英特尔公司 | Memory circuit and method for distributed memory hazard detection and Fault recovery |

| US20190377580A1 (en) * | 2008-10-15 | 2019-12-12 | Hyperion Core Inc. | Execution of instructions based on processor and data availability |

-

2020

- 2020-01-09 CN CN202010020665.4A patent/CN111240849A/en active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6738871B2 (en) * | 2000-12-22 | 2004-05-18 | International Business Machines Corporation | Method for deadlock avoidance in a cluster environment |

| US20190377580A1 (en) * | 2008-10-15 | 2019-12-12 | Hyperion Core Inc. | Execution of instructions based on processor and data availability |

| CN109215728A (en) * | 2017-07-01 | 2019-01-15 | 英特尔公司 | Memory circuit and method for distributed memory hazard detection and Fault recovery |

Non-Patent Citations (4)

| Title |

|---|

| GUANGDA ZHANG等: ""Deadlock Recovery in Asynchronous Networks on Chip in the Presence of Transient Faults"", 《2015 21ST IEEE INTERNATIONAL SYMPOSIUM ON ASYNCHRONOUS CIRCUITS AND SYSTEMS》 * |

| GUANGDA ZHANG等: ""Handling Physical-Layer Deadlock Caused by Permanent Faults in Quasi-Delay-Insensitive Networks-on-Chip"", 《IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS》 * |

| N JULAI等: ""Error detection and correction of single event upset (SEU) tolerant latch"", 《2012 IEEE 18TH INTERNATIONAL ON-LINE TESTING SYMPOSIUM (IOLTS)》 * |

| WEI SONG等: ""On-Line Detection of the Deadlocks Caused by Permanently Faulty Links in Quasi-Delay Insensitive Networks on Chip"", 《GLSVLSI "14: PROCEEDINGS OF THE 24TH EDITION OF THE GREAT LAKES SYMPOSIUM ON VLSI》 * |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100468286C (en) | Data retention latch provision within integrated circuits | |

| Apperson et al. | A scalable dual-clock FIFO for data transfers between arbitrary and haltable clock domains | |

| CN112667450B (en) | Dynamically configurable fault-tolerant system with multi-core processor | |

| CN102497200B (en) | Clock signal loss detecting circuit and clock signal loss detecting method | |

| US9191033B2 (en) | Circuit for asynchronous communications, related system and method | |

| Balasubramanian | A robust asynchronous early output full adder | |

| Beer et al. | Metastability in better-than-worst-case designs | |

| US4686677A (en) | Apparatus and method for detecting time-related faults | |

| CN113009961B (en) | Cross-clock synchronous circuit and SoC system | |

| US9112489B2 (en) | Sequential logic circuit and method of providing setup timing violation tolerance therefor | |

| EP3053269B1 (en) | Preventing timing violations | |

| CN100588149C (en) | Circuit for transferring object event happened in object clock field to monitoring clock field | |

| CN111240849A (en) | Deadlock detection circuit and detection method for asynchronous pipeline circuit | |

| EP0772133A2 (en) | System for data synchronisation | |

| Zhang et al. | Transient fault tolerant QDI interconnects using redundant check code | |

| CN113282134A (en) | Hot backup triple-modular redundancy computer time synchronization implementation device and method | |

| CN102754407B (en) | Providing a feedback loop in a low latency serial interconnect architecture and communication system | |

| CN106059545B (en) | A kind of sequential control circuit for low-power consumption assembly line | |

| CN202364199U (en) | Detection circuit for clock signal loss | |

| US8994416B2 (en) | Adaptive multi-stage slack borrowing for high performance error resilient computing | |

| CN217213701U (en) | Circuit for multi-clock switching, FPGA and electronic equipment | |

| Lechner et al. | A generic architecture for robust asynchronous communication links | |

| CN105430409A (en) | Flow control method and flower control device based on counter | |

| JP2006031133A (en) | Semiconductor device | |

| Zhang | Fault Tolerant Techniques for Asynchronous Networks on Chip |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PB01 | Publication | ||

| PB01 | Publication | ||

| SE01 | Entry into force of request for substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| RJ01 | Rejection of invention patent application after publication |

Application publication date: 20200605 |

|

| RJ01 | Rejection of invention patent application after publication |