# CMOS Transistor R & C

| Copyright (c) 2011-2013 Young W. Lim.                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License". |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

| Please send corrections (or suggestions) to youngwlim@hotmail.com.                                                                                                                                                                                                                                                                                                              |

| This document was produced by using OpenOffice and Octave.                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                 |

## **NMOS** Bias

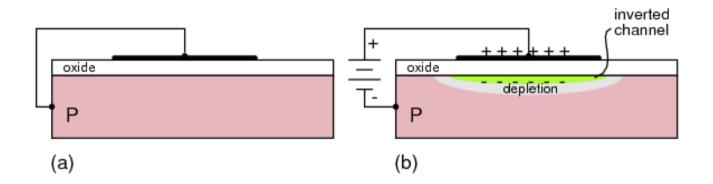

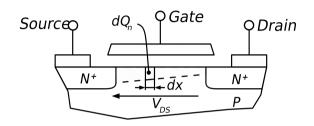

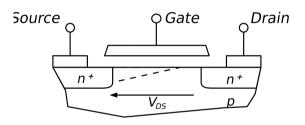

N-channel MOS capacitor: (a) no charge, (b) charged.

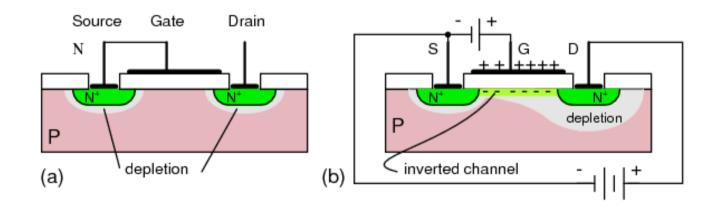

N-channel MOSFET (enhancement type): (a) 0 V gate bias, (b) positive gate bias.

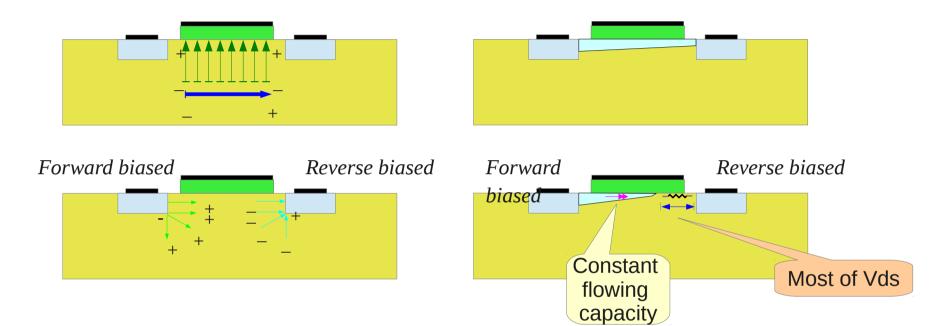

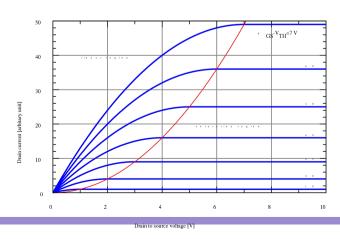

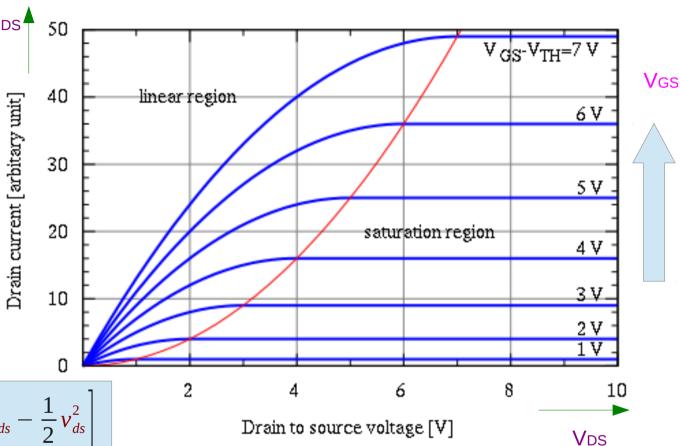

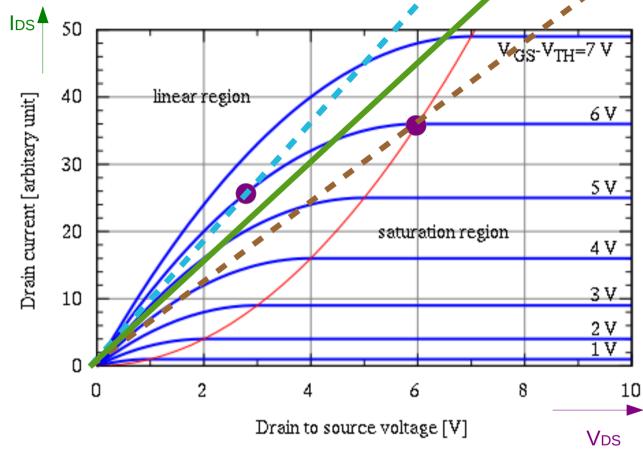

## Pinch-Off

## Simple Transistor Model (1)

#### Cutoff, subthreshold, or weak-inversion mode

When  $V_{GS} < V_{t}$ :

$$I_d = 0$$

#### **Triode mode or linear region (the ohmic mode)**

$$I_d = k' \frac{W}{L} \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right]$$

#### Saturation or active mode

When

$$V_{GS} > V_{t}$$

and  $V_{DS} \ge (V_{GS} - V_{t})$

$$I_d = \frac{1}{2} k' \frac{W}{L} (v_{gs} - v_t)^2$$

## Simple Transistor Model (2)

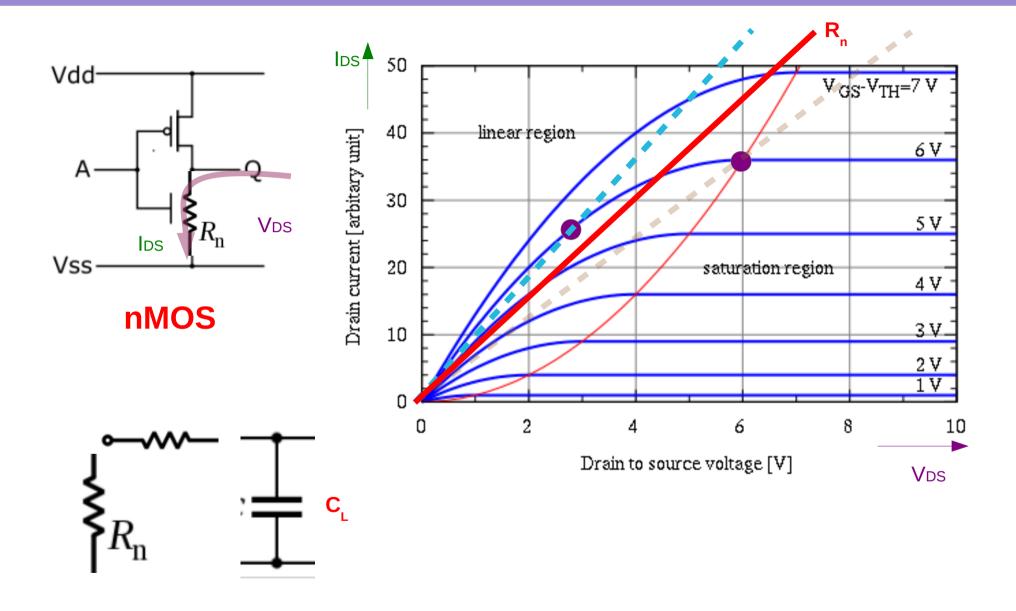

#### linear region

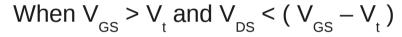

When

$$V_{GS} > V_{t}$$

and  $V_{DS} < (V_{GS} - V_{t})$

$$I_d = k' \frac{W}{L} \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right]$$

# $2(v_{gs}-v_t)$ $(v_{gs}-v_t)$ VDS

#### Saturation or active mode

When

$$V_{GS} > V_{t}$$

and  $V_{DS} \ge (V_{GS} - V_{t})$

$$I_d = \frac{1}{2} k' \frac{W}{L} (v_{gs} - v_t)^2$$

# Simple Transistor Model (3)

#### Cutoff

$$V_{GS} < V_{t}$$

:

#### **Linear region**

$$V_{GS} > V_{t}$$

$V_{DS} < (V_{GS} - V_{t})$

#### **Saturation**

$$V_{GS} > V_{t}$$

$$V_{DS} > (V_{GS} - V_{t})$$

$$I_d = k' \frac{W}{L} \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right]$$

$$I_d = \frac{1}{2} k' \frac{W}{L} (v_{gs} - v_t)^2$$

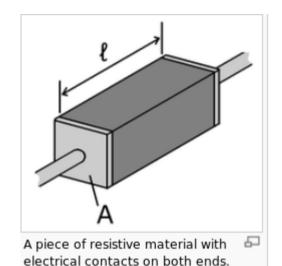

## Resistance (1)

$$R = \frac{V}{I}$$

$$G = \frac{I}{V}$$

Ohm's law

$$V \propto I$$

$$R = \frac{V}{I}, \qquad G = \frac{I}{V}$$

the derivative  $\dfrac{dV}{dI}$  may be most useful; this is called the "differential resistance".

8

$$I_d = k' \frac{W}{L} \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right]$$

# Resistance (2)

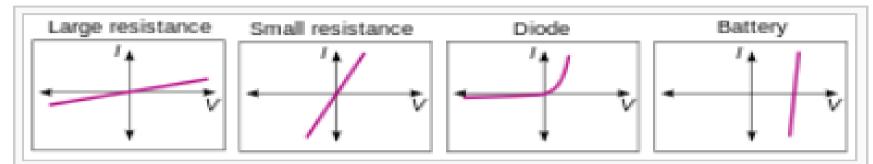

The current-voltage characteristics of four devices: Two resistors, a diode, and a battery. The horizontal axis is voltage drop, the vertical axis is current. Ohm's law is satisfied when the graph is a straight line through the origin. Therefore, the two resistors are "ohmic", but the diode and battery are not.

#### **Slope**

the derivative  $\dfrac{dV}{dI}$  may be most useful; this is called the "differential resistance".

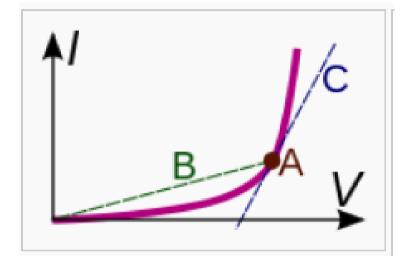

## Resistance (3)

The IV curve of a non-ohmic device (purple). Point A represents the current and voltage values right now. The **static resistance** is the inverse slope of line B through the origin. The **differential resistance** is the inverse slope of tangent line C.

Static resistance (also called chordal or DC resistance) - This corresponds to the usual definition of resistance; the voltage divided by the current

$$R_{\text{static}} = \frac{v}{i}$$

.

Differential resistance (also called dynamic, incremental or small signal resistance) -Differential resistance is the derivative of the voltage with respect to the current; the slope of the IV curve at a point

$$R_{\text{diff}} = \frac{dv}{di}$$

## Resistance (4)

## Resistance (5)

## Resistance (6)

## Resistance (7)

14

# Capacitance

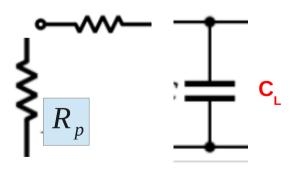

## **RC Circuit**

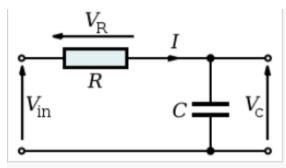

Series RC circuit

By viewing the circuit as a voltage divider, the voltage across the capacitor is:

$$V_C(s) = \frac{1/Cs}{R + 1/Cs} V_{in}(s) = \frac{1}{1 + RCs} V_{in}(s)$$

and the voltage across the resistor is:

$$V_R(s) = \frac{R}{R+1/Cs}V_{in}(s) = \frac{RCs}{1+RCs}V_{in}(s).$$

$$V_C(t) = V \left( 1 - e^{-t/RC} \right)$$

$$V_R(t) = V e^{-t/RC}.$$

## Time Constant

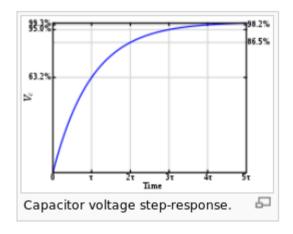

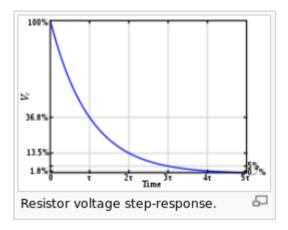

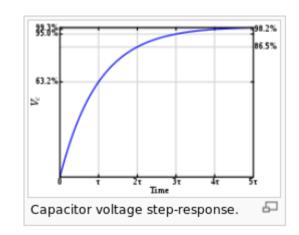

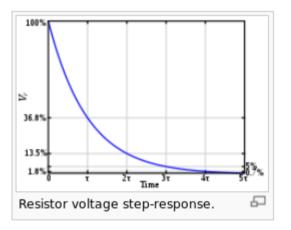

Thus, the voltage across the capacitor tends towards *V* as time passes, while the voltage across the resistor tends towards 0, as shown in the figures. This is in keeping with the intuitive point that the capacitor will be charging from the supply voltage as time passes, and will eventually be fully charged.

These equations show that a series RC circuit has a time constant, usually denoted au=RC being the time it takes the voltage across the component to either rise (across C) or fall (across R) to within 1/e of its final value. That is, au is the time it takes  $V_C$  to reach V(1-1/e) and  $V_R$  to reach V(1/e).

The rate of change is a  $\operatorname{\it fractional}\left(1-\frac{1}{e}\right)$  per au. Thus, in going from

t=N au to t=(N+1) au , the voltage will have moved about 63.2% of

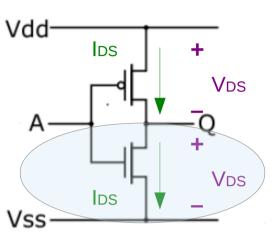

# Simple Model

$$V_{gs}$$

$$V_{ds}$$

$$I_d$$

$$I_d = k' \frac{W}{L} \left[ (v_{gs} - v_t) v_{ds} - \frac{1}{2} v_{ds}^2 \right]$$

$$I_d = \frac{1}{2} k' \frac{W}{L} (v_{gs} - v_t)^2$$

$$\left\{ egin{array}{c} {\sf v}_t \ {\sf k}' \end{array}

ight\}$$

measured

$$\left\{ rac{W}{L}

ight.$$

determined by the layout tool used

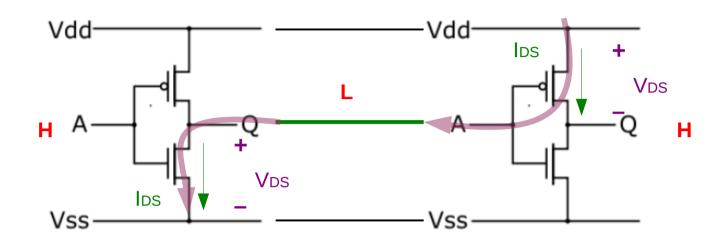

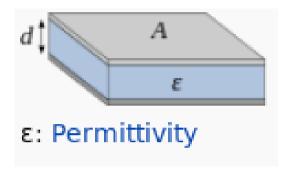

## **Transistor Parasitics**

$C_g$

gate capacitance

$C_{gs}$

$C_{ds}$

source/drain overlap capacitance

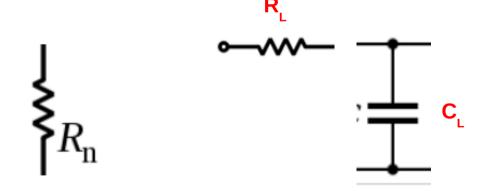

## Wire Parasitics

wires vias transistors

# Spice Model

wires vias transistors

# Design Rule

wires vias transistors

#### References

- [1] http://en.wikipedia.org/

- [2] http://www.allaboutcircuits.com/

- [3] W. Wolf, "Modern VLSI Design: Systems on Silicon

- [4] N. Weste, D. Harris, "CMOS VLSI Design: A Circuits and Systems Perspective"