# Nanowire-Based 3-D Transmission-Line Transformer for Millimeter-Wave Applications

Tadeu M. Frutuoso<sup>®</sup>, João Lé<sup>®</sup>, Yoann Berthoud<sup>®</sup>, Julio M. Pinheiro<sup>®</sup>, Marc Margalef-Rovira<sup>®</sup>, Philippe Ferrari<sup>®</sup>, *Senior Member, IEEE*, Gustavo P. Rehder<sup>®</sup>, and Ariana L. C. Serrano<sup>®</sup>, *Member, IEEE*

Abstract—In this letter, 3-D transformers based on transmission lines (TLs) working at mm-wave frequencies are presented. They were realized in a low-cost technology based on metallic-filled nanoporous membranes. Several transformers were designed and measured with different numbers of turns, from 1 to 6 turns. They exhibit working frequencies from 14.5 up to 110 GHz. The 1-dB bandwidth (BW) of the realized transformers is better than 12 GHz, and the insertion loss (IL) is between 1.1 and 1.6 dB, thus demonstrating a high efficiency at mm-waves. Transformers could be further improved by better optimizing the TLs and their return current path, which is a key parameter to be considered, given the distributed nature of the proposed transformers.

*Index Terms*—3-D circuits, millimeter-wave circuits, system integration, transformer.

### I. INTRODUCTION

**T**RANSFORMERS play an important role in microwave and mm-wave circuits' and systems' design. Their main applications concern matching and biasing networks [1], polyphase networks [2], signal generation [3], baluns [4], and power divider/combiner [5]. Their implementation in monolithic low-cost integrated technologies such as (Bi)CMOS at mm-wave frequencies is very common today. Most of the works refer to traditional transformers that use two windings (primary and secondary) aiming at low loss and high magnetic coupling coefficient. The primary and secondary spirals can be placed in the same layer [6], [7] or in different layers [8]–[10]. Using different layers with the spirals vertically aligned has shown better performance and size/cost reduction [11].

Manuscript received 17 December 2021; accepted 2 February 2022. Date of publication 5 May 2022; date of current version 7 October 2022. This work was supported in part by FAPESP under Grant 2016/25779-9 and Grant 2018/08782-1, and in part by CNPq under Grant 309577/2020-9, Grant 311031/2018-8, and Grant 431200/2018-1. (*Corresponding author: Ariana L. C. Serrano.*)

Tadeu M. Frutuoso is with CEA, 38000 Grenoble, France (e-mail: tadeu.motafrutuoso@cea.fr).

João Lé, Julio M. Pinheiro, Gustavo P. Rehder, and Ariana L. C. Serrano are with LME, Escola Politécnica da Universidade de São Paulo, Sao Paulo 05508-010, Brazil (e-mail: joao.le@usp.br; juliomota@alumni.usp.br; gprehder@usp.br; aserrano@usp.br).

Yoann Berthoud is with G2ELab, 38000 Grenoble, France, and also with Schneider Electric, 38320 Eybens, France (e-mail: yoann.berthoud@ icloud.com).

Marc Margalef-Rovira is with CNRS, Centrale Lille, UMR 8520–IEMN, Univ. Polytechnique Hauts-de-France, Univ. Lille, F-59000 Lille, France (e-mail: marc.margalef-rovira@iemn.fr).

Philippe Ferrari is with the RFIC-Laboratory, Grenoble INP, Université Grenoble Alpes, 38000 Grenoble, France (e-mail: philippe.ferrari@ univ-grenoble-alpes.fr).

Color versions of one or more figures in this letter are available at https://doi.org/10.1109/LMWC.2022.3159096.

Digital Object Identifier 10.1109/LMWC.2022.3159096

(a) Ground Ground (b)  $S=10 \mu m$  Vias Vias Top metalBottom metal

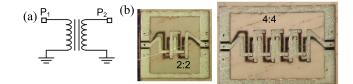

Fig. 1. (a) Illustration of the 2:2 3-D transformer. (b) Three-dimensional view of the 2:2 transformer. (c) Side view of the transformers.

Some other CMOS works refer to transmission-line transformers (TLTs) [12], [13]. TLTs consist of one or more pairs of transmission lines (TLs) interconnected in a way to provide a specific impedance ratio and have been widely studied in the whole frequency spectrum since their publication [14], [15]. In this case, evaluating the transformer performance based on the spirals' performance and their magnetic coupling factor is no longer valid. A more suitable manner to compare the performance of all types of transformers is the power transfer from the input to the output, in terms of the insertion loss (IL).

No matter which topology, (Bi)CMOS transformers are built as far as possible from the lossy silicon substrate [16], reducing eddy current and parasitic capacitances, and preferable at the top thick layers, reducing losses due to series resistance. Despite the good performance, the maximum impedance ratio is limited by the technology considering the limits of the strip width allowed [10]. Their size is still large compared with the rest of the system [17], [18] easily reaching 100 × 100  $\mu$ m<sup>2</sup>, when considering not only the spirals but also the required outer spacing from other metals. For instance, removing the power amplifier input and output transformers in [17], it would be possible to reduce the size (and therefore the cost) by half.

Heterogeneous 3-D integration (off chip solution) is an interesting alternative solution that brings flexibility and performance to the transformer design, addressing the issues related to monolithic integration. Transformers have been presented in high-resistivity silicon substrate in lower microwave frequencies [19]–[23], but the numerous vias necessary for their fabrication increases significantly the loss, becoming not suitable for mm-wave applications.

In this letter, we propose TLT transformers operating at mm-waves with broadband characteristic. The TLT is formed by two TLs 3-D meandered around each other forming a

1531-1309 © 2022 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See https://www.ieee.org/publications/rights/index.html for more information.

Fig. 2. (a) Transformer schematic. (b) Photographs of the fabricated 3-D transformers (4:4, right; 2:2, left).

solenoid-like topology, as shown in Fig. 1. Since they are TLs, they require return current paths, formed by the metallic rings (one for each layer) drawn around the "solenoids." The transformers were built using a cost-effective technology based on an alumina metal-filled nanoporous membrane (MnM), where vias can be very easily realized, since the fabrication of the vias enters a standard fabrication process flow, with outstanding form factors and performance [24]. The advantage of the MnM technology is its low cost and good performance. The technology has been first introduced in [25] for the realization of slow wave TLs, with its electrical model presented in [26]. The availability of small vias allowed the development of compact 3-D inductors with high-quality factor at mmwaves, as shown in [27]. Therefore, the MnM technology is a high-performance interposer very suitable for heterogeneous 3-D integration [28], embedding passive components and circuits into the membrane.

## II. MNM TRANSFORMERS' PRINCIPLE, MODEL, AND DESIGN

The proposed 3-D transformer is formed by two 3-D meandered TLs, referred as primary and secondary, both fabricated in two metal layers, at the top (blue) and at the bottom (yellow) of a 50- $\mu$ m-thick nanoporous alumina membrane. These layers are interconnected by vias realized by a forest of metallic nanowires, which are grown inside the nanopores electrochemically as described in [27]. The vias used here are 25 × 25  $\mu$ m<sup>2</sup> to follow the width of the TLs, but smaller vias and lines could be fabricated if needed.

The relative dielectric constant  $\varepsilon_r$  and loss tangent tan $\delta$  of the porous alumina substrate are 6.7 and 0.01, respectively, as determined in [25]. Since the membrane used as substrate is translucid, the bottom layer of the 3-D transformers can be as seen in Fig. 2. The end of each TL was grounded to simplify the measurement to a two-port setup, as indicated in Fig. 2(a). The return current paths required for the TLs have a strong impact on the transformer response and must be considered from the earliest stages of design. An asymmetric TL topology was used to show impedance matching flexibility in the design when compared with the symmetric layout in [19].

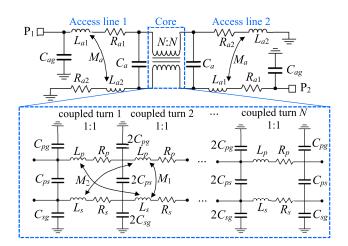

The model of an N:N transformer is shown in Fig. 3, showing the access lines and the transformer core. Despite the similarity to the traditional transformer model, the proposed model deals with distributed capacitances and inductances related to the coupled TLs. All the values of the model parameters can be extracted from simple capacitance and inductance simulations. The relevance of such an approach is that it is physically related, and therefore, the designer can change any dimension of the TLs to obtain the desired

Fig. 3. Model of the N:N 3-D transformers including access lines and transformer core.

response. The model is also scalable, so it can be used for TLs with any number of turns.

The access lines are modeled by the series inductance  $L_a$  and resistance  $R_a$ , the shunt capacitance  $C_{ag}$ , and the capacitance between access  $C_a$ . As the lengths of the two access lines of a TL are not symmetrical, in one end we have  $L_{a1}$  and  $R_{a1}$  and in the other end  $L_{a2}$  and  $R_{a2}$ . The magnetic coupling between accesses is modeled by the mutual inductance  $M_a$ . Regarding the transformer core, the variables for the primary TL  $(L_p, R_p, C_{pg})$  and the secondary TL  $(L_s, R_s, C_{sg})$  were defined for each turn of the coupled TL (1:1). The electric coupling between the two TLs is modeled by  $C_{ps}$ . Due to its asymmetry, we have included in the model the coupling between adjacent turns, which is not used in the symmetrical case. Each coupled turn is magnetically coupled through two mutual inductances,  $M_1$  and  $M_2$ , representing the mutual inductance of the coupled turn and between adjacent turns, respectively.

The model uses the following equations:

$$L_{(p \text{ or } s)\text{tot}} = N \cdot L_{(p \text{ or } s)} + L_{a1} + L_{a2}$$

(1)

$$C_{(p \text{ or } s)\text{gtot}} = N \cdot C_{(p \text{ or } s)g} + C_{\text{ag}}$$

(2)

$$C_{\rm ps\ tot} = N \cdot C_{\rm ps} + 2C_a \tag{3}$$

$$M_{\text{tot}} = N \cdot M_1 + 2(N-1) \cdot M_2 + 2M_a \tag{4}$$

where N is the number of turns.

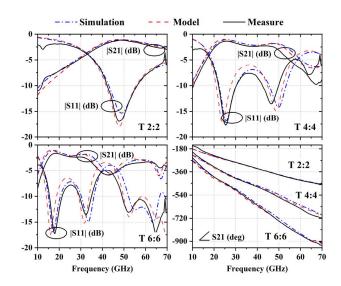

The transformers' accesses and TLs were simulated in ANSYS Maxwell for different numbers of turns without connections to the return path. The values of  $L_p$ ,  $L_s$ ,  $C_{pg}$ ,  $C_{sg}$ , and  $C_{ps}$  were extracted from the slope of their curves and the values of  $C_a$ ,  $L_{a1}$ , and  $L_{a2}$  by the value where their curves intercept the y-axis following (1)–(4).  $C_{ag}$  and  $M_a$  were extracted from the simulation of the accesses alone. Then  $M_1$  and  $M_2$  were calculated from (4). The TLs and access lines' resistances were calculated using the dimensions of each strip, the copper conductance, and a simple skin effect model. As an example, the extracted parameters for each element of the model of a 2:2 transformer are presented in Table I and its comparison with a full-wave 3-D electromagnetic (EM) simulation and its measurement is shown in Fig. 4.

TABLE I

2:2 Transformer Model Parameters

| $L_{a1}$ | $L_{a2}$ | $C_{pg}$ | $C_{sg}$              | $C_{ps}$              | $C_{ag}$       |

|----------|----------|----------|-----------------------|-----------------------|----------------|

| 93.5 pH  | 89.4 pH  | 3.7 fF   | 0.75 fF               | 23,6 fF               | 5.7 fF         |

| Ca       | Ls       | $L_p$    | <i>M</i> <sub>1</sub> | <i>M</i> <sub>2</sub> | M <sub>a</sub> |

| 0.3 fF   | 316 pH   | 222 pH   | 101 pH                | 46 pH                 | 20 pH          |

Fig. 4. Comparison between measurement, model, and simulation results for the 2:2, 4:4, and 6:6 3-D transformers.

| Ref.         | Technology        | Min. IL        | Min. MAG* | 1-dB BV | V [GHz]            | Area           |          |

|--------------|-------------------|----------------|-----------|---------|--------------------|----------------|----------|

|              | Technology        |                | [dB]      | [dB]    | MAG                | IL             | $[mm^2]$ |

| [29]         | 65nm CMOS         |                | 1.5       | -       | -                  | 56-64          | 0.032    |

| [20]         | HR silicon        |                | 0.24      | -       | -                  | 6.26-12.25     | 0.997    |

| [9]          | 65nm CMOS         |                | -         | 0.5     | 45-90              | -              | 0.017    |

| [10]         |                   | m SiGe<br>CMOS | -         | 0.8     | 10-80              | -              | 0.02     |

| [5]          | 180nm             | BiCMOS         | -         | 2.5     | 45-50 <sup>+</sup> | -              | 0.08     |

| [17]         | 90nm              | n CMOS         | 5         | -       | -                  | 55-65          | 0.01     |

| This<br>work |                   | 1:1            | 1.2       | 0.6     | 15.5-103           | 56.0-91        | 0.24     |

|              | 2:2<br>3:3<br>4:4 | 2:2            | 1.1       | 0.8     | $19.5 - 70^+$      | 47.6-60        | 0.39     |

|              |                   | 3:3            | 1.2       | 1.1     | $18-70^{+}$        | 27.3-43        | 0.456    |

|              |                   | 4:4            | 1.4       | 1.2     | 14.8-48.5          | 20.7-38        | 0.54     |

|              |                   | 6:6            | 1.6       | 1.3     | 12.8-33            | 14.9-33        | 0.671    |

|              |                   | 1:1 WB         | 1.5       | 0.4     | $15.3 - 110^{+}$   | $78.5 - 110^+$ | 0.116    |

TABLE II Comparison of MM-wave Transformers

\*MAG defined in [31]

<sup>+</sup> upper boundary limited by the measuring equipment

#### **III. FABRICATION AND MEASUREMENT**

The fabrication of the 3-D transformers follows the same steps as the 3-D inductors presented in [27]. The 3-D transformers were characterized up to 110 GHz using ground-signal-ground (GSG) probes (MPI Titan probes with 100  $\mu$ mpitch) in a cascade manual probe station (EPS-150MMW) and a Keysight PNA 5227B vector network analyzer. A line-reflect-reflect-match (LRRM) calibration was performed. To prevent short-circuiting the bottom of the transformers with the metallic chuck of the probe station, a 5-mm-thick ROHACELL 51 IG foam was used as spacing.

Six different transformers were designed, simulated, fabricated, and tested with different numbers of turns: 1–6 turns,

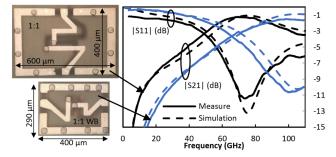

Fig. 5. 1:1 3-D transformers. The 1:1 WB has shorter TLs and the return current path is closer, resulting in higher frequency operation and larger 1-dB BW.

i.e., 1:1–6:6 ratios. The circuit model and the simulations performed in Keysight Advanced Design System (ADS) were compared with the measurements in Fig. 4 and are in very good agreement. The frequency where the circuit presents the minimum IL is inversely proportional to the number of turns, and hence, to the TLs' length, as expected. The summary of the measured performance is given in Table II showing that the proposed transformers have a performance similar or even better than those manufactured using CMOS technologies. The transformers show working frequencies up to 110 GHz, with BWs wider than 12 GHz and IL better than 1.6 dB.

The model is proven to be scalable, which provides a powerful tool for the design of new and improved TLTs. All the dimensions provided in Fig. 1 can be modified according to the model to reach the designer's needs, being the minimum distance between lines and minimum linewidth of 5  $\mu$ m. Moreover, any topology with TLs with any number of turns can be easily designed using this model. For high impedance ratios, different connections between the TLs can be designed as indicated in [30], giving a high degree of freedom for the designer. By considering an effective dielectric constant equal to 3.5, which is almost the average between the air and the dielectric constant of the nanoporous membrane, it can be noted that each TL has half-wavelength in average, which corroborates the resonant frequencies observed in the return loss presented in Fig. 4. This can be used to understand how to optimize transformers. To illustrate this, two different 1:1 transformers were fabricated with different dimensions: smaller turns (shorter TL) and closer return current path, to increase the frequency and enlarge the 1-dB BW, as shown in Fig. 5.

## IV. CONCLUSION

In this letter, a cost-effective technology has been proposed for the realization of 3-D mm-wave transformers. Measurements showed working frequencies from 14.5 to 110 GHz and IL between 1.1 and 1.6 dB. To our knowledge, the presented result at 110 GHz is the highest in a low-cost, interposer technology. The circuit elements of the proposed model are physical related to layout features, allowing an accurate insight of its frequency response and performance. It has also been shown that each TL's length leads to halfwavelength resonances, and their characteristic impedance limits the transformer 1-dB BW to around 20 GHz. Future work will be focused toward the development of a baluns and high ratio impedance transformers.

#### References

- D. Pepe, I. Chlis, and D. Zito, "Transformer-based input integrated matching in cascode amplifiers: Analytical proofs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 5, pp. 1495–1504, May 2018.

- [2] H. Liu, B. Guo, H. Wang, and J. Wu, "A Ka-band vector-sum phase shifter in 65 nm CMOS for phased array receivers," in *Proc. Int. Conf. Electr., Commun., Comput. Eng. (ICECCE)*, 2021, pp. 1–5, doi: 10.1109/ICECCE52056.2021.9514160.

- [3] F. Piri, M. Bassi, N. Lacaita, A. Mazzanti, and F. Svelto, "A >40dB IRR, 44% fractional-bandwidth ultra-wideband mm-wave quadrature LO generator for 5G networks in 55 nm CMOS," in *IEEE ISSCC Dig. Tech. Papers*, San Francisco, CA, USA, Feb. 2018, pp. 368–370.

- [4] L. Iotti, M. Bassi, A. Mazzanti, and F. Svelto, "Design of lowpower wideband frequency quadruplers based on transformer-coupled resonators for E-band backhaul applications," *Integration*, vol. 58, pp. 413–420, Jun. 2017.

- [5] D. Pan, Z. Duan, L. Sun, S. Guo, L. Cheng, and P. Gui, "A 76–81 GHz CMOS PA with 16-dBm PSAT and 30-dB amplitude control for MIMO automotive radars," in *Proc. IEEE 45th Eur. Solid State Circuits Conf.* (*ESSCIRC*), 2019, pp. 329–332, doi: 10.1109/ESSCIRC.2019.8902347.

- [6] J. R. Long, "Monolithic transformers for silicon RF IC design," *IEEE J. Solid-State Circuits*, vol. 35, no. 9, pp. 1368–1382, Sep. 2000, doi: 10.1109/4.868049.

- [7] O. El-Gharniti, E. Kerherve, and J.-B. Begueret, "Modeling and characterization of on-chip transformers for silicon RFIC," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 4, pp. 607–615, Apr. 2007, doi: 10.1109/TMTT.2007.893647.

- [8] V. N. R. Vanukuru and A. Chakravorty, "High efficiency millimeterwave stacked two turn transformer using only top two thick metals," in *Proc. Int. Microw. RF Conf. (IMaRC)*, 2014, pp. 251–254, doi: 10.1109/IMaRC.2014.7039020.

- [9] B. Leite, E. Kerherv, and D. Belot, "Design and characterization of CMOS millimeter-wave transformers," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Dec. 2009, pp. 402–406, doi: 10.1109/IMOC.2009. 5427555.

- [10] B. Leite, E. Kerhervé, J. Bágueret, and D. Belot, "Design of high transformation ratio millimeter-wave integrated transformers," *Int. J. Microw. Wireless Technol.*, vol. 4, no. 2, pp. 233–239, 2012, doi: 10.1017/S1759078711001073.

- [11] T. O. Dickson, M.-A. LaCroix, S. Boret, D. Gloria, R. Beerkens, and S. P. Voinigescu, "30–100-GHz inductors and transformers for millimeter-wave (Bi)CMOS integrated circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 1, pp. 123–133, Jan. 2005, doi: 10.1109/TMTT.2004.839329.

- [12] T. S. D. Cheung and J. R. Long, "Design and modeling of mm-wave monolithic transformers," in *Proc. Bipolar/BiCMOS Circuits Technol. Meeting*, 2006, pp. 1–4, doi: 10.1109/BIPOL.2006.311145.

- [13] D. Hou *et al.*, "Distributed modeling of six-port transformer for millimeter-wave SiGe BiCMOS circuits design," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 12, pp. 3728–3738, Dec. 2012, doi: 10.1109/TMTT.2012.2220563.

- [14] G. Gunella, "Novel matching systems for high frequencies," Brown-Boveri Rev., vol. 31, pp. 327–329, Sep. 1944.

- [15] C. L. Ruthroff, "Some broad-band transformers," *Proc. IRE*, vol. 47, pp. 1337–1342, Aug. 1959.

- [16] K. T. Ng, B. Rejaei, and J. N. Burghartz, "Substrate effects in monolithic RF transformers on silicon," *IEEE Trans. Microw. Theory Techn.*, vol. 50, no. 1, pp. 377–383, Jan. 2002, doi: 10.1109/22.981289.

- [17] D. Chowdhury, P. Reynaert, and A. M. Niknejad, "Design considerations for 60 GHz transformer-coupled CMOS power amplifiers," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2733–2744, Oct. 2009, doi: 10.1109/JSSC.2009.2028752.

- [18] Z. Xu, Q. J. Gu, and M.-C.-F. Chang, "A 100–117 GHz W-band CMOS power amplifier with on-chip adaptive biasing," *IEEE Microw. Wireless Compon. Lett.*, vol. 21, no. 10, pp. 547–549, Oct. 2011, doi: 10.1109/LMWC.2011.2163815.

- [19] Z. Feng, M. R. Lueck, D. S. Temple, and M. B. Steer, "Highperformance solenoidal RF transformers on high-resistivity silicon substrates for 3D integrated circuits," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 7, pp. 2066–2072, Jul. 2012, doi: 10.1109/TMTT.2012.2195026.

- [20] F. Wang, R. Ren, X. Yin, N. Yu, and Y. Yang, "A transformer with high coupling coefficient and small area based on TSV," *Integration*, vol. 81, pp. 211–220, Nov. 2021, doi: 10.1016/j.vlsi.2021.07.003.

- [21] D. C. Laney *et al.*, "Microwave transformers, inductors and transmission lines implemented in an Si/SiGe HBT process," *IEEE Trans. Microw. Theory Techn.*, vol. 49, no. 8, pp. 1507–1510, Aug. 2001, doi: 10.1109/22.939934.

- [22] B. Zhang et al., "3D TSV transformer design for DC-DC/AC-DC converter," in Proc. 60th Electron. Compon. Technol. Conf. (ECTC), 2010, pp. 1653–1656, doi: 10.1109/ECTC.2010.5490761.

- [23] S. H. Li et al., "Fully 3-D symmetrical TSV monolithic transformer for RFIC," in Proc. 65th Electron. Compon. Technol. Conf. (ECTC), 2015, pp. 987–993, doi: 10.1109/ECTC.2015.7159715.

- [24] J. M. Pinheiro *et al.*, "110-GHz through-substrate-via transition based on copper nanowires in alumina membrane," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 2, pp. 784–790, Feb. 2018.

- [25] A. L. C. Serrano *et al.*, "Modeling and characterization of slowwave microstrip lines on metallic-nanowire-filled-membrane substrate," *IEEE Trans. Microw. Theory Techn.*, vol. 62, no. 12, pp. 3249–3254, Dec. 2014, doi: 10.1109/TMTT.2014.2366108.

- [26] J. M. Pinheiro, G. P. Rehder, F. Podevin, P. Ferrari, and A. L. C. Serrano, "Slow-wave microstrip line model for PCB and metallic-nanowire-filledmembrane technologies," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 2, pp. 1238–1249, Feb. 2021, doi: 10.1109/TMTT.2020.3040414.

- [27] A. L. C. Serrano et al., "3D inductors with nanowire through substrate vias," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Honololu, HI, USA, Jun. 2017, pp. 1641–1644.

- [28] M. V. Pelegrini *et al.*, "Interposer based on metallic-nanowire-membrane (MnM) for mm-wave applications," in *Proc. 46th Eur. Microw. Conf.* (*EuMC*), London, U.K., Oct. 2016, pp. 1461–1464.

- [29] L. Jing, A. Li, D. Luo, C. R. Rowell, and C. P. Yue, "Millimeterwave 4:1 transformer-based balun design for CMOS RF IC's," in *Proc. IEEE Int. Wireless Symp.*, Mar. 2015, pp. 1–4, doi: 10.1109/IEEE-IWS.2015.7164519.

- [30] E. Rotholz, "Transmission-line transformers," *IEEE Trans. Microw. Theory Techn.*, vol. MTT-29, no. 4, pp. 327–331, Apr. 1981, doi: 10.1109/TMTT.1981.1130352.

- [31] D. C. Laney *et al.*, "Lateral microwave transformers and inductors implemented in a Si/SiGe HBT process," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 1999, pp. 855–858, doi: 10.1109/MWSYM.1999.779521.