# (19) 中华人民共和国国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 114300435 A (43) 申请公布日 2022. 04. 08

(21)申请号 202111157994.4

(22)申请日 2021.09.30

(30) 优先权数据

20200625.0 2020.10.07 EP

(71) 申请人 英飞凌科技奥地利有限公司 地址 奥地利菲拉赫西门子大街2号

(72) 发明人 S • 尤费列夫 R • 费勒

A•凯斯勒 G•诺鲍尔

P•巴尔姆

(74) 专利代理机构 中国专利代理(香港)有限公

司 72001

代理人 刘茜璐 周学斌

(51) Int.CI.

*H01L* 23/495 (2006.01) *H01L* 25/16 (2006.01)

权利要求书2页 说明书10页 附图7页

### (54) 发明名称

半导体模块

### (57) 摘要

提供了一种半导体模块,其包括低侧开关、高侧开关和控制芯片。低侧开关和高侧开关被布置成彼此横向邻近,并且通过开关节点连接器耦合以形成半桥电路。开关节点连接器包括两个或更多个支路,所述两个或更多个支路具有相对于低侧开关和高侧开关的布置,并且各自具有横截面积。两个或更多个支路的布置和横截面积被选择成使开关节点连接器内的电流密度分布变得均质。

1.一种半导体模块(10、30、40、80、90),包括:

低侧开关(11);

高侧开关(12);

控制芯片(13):

其中,所述低侧开关(11)和所述高侧开关(12)被布置成彼此横向邻近,并且通过开关 节点连接器(14)耦合以形成半桥电路,并且

其中,所述开关节点连接器(14)包括两个或更多个支路(15、16),所述两个或更多个支路具有相对于所述低侧开关(11)和相对于所述高侧开关(12)的布置,并且各自具有横截面积,其中,所述两个或更多个支路(15、16)的所述布置和所述横截面积被选择成使所述开关节点连接器(14)内的电流密度分布变得均质。

- 2.根据权利要求1所述的半导体模块(10、30、40、80、90),其中,所述开关节点连接器(14)包括布置在所述低侧开关(11)上的第一部分(21)、布置在所述高侧开关(12)上的第二部分(22),并且所述两个或更多个支路(15、16)在所述第一部分(21)与所述第二部分(22)之间延伸,其中,所述两个或更多个支路(15、16)彼此间隔开。

- 3.根据权利要求1或2所述的半导体模块(10、30、40、80、90),其中,所述第二支路(16) 具有比所述第一支路(15)的横截面积更小的横截面积,和/或所述第二支路(16)具有比所 述第一支路(15)的长度更大的长度。

- 4.根据权利要求1至3中任一项所述的半导体模块(10、30、40、80、90),其中,所述开关节点连接器(14)在所述低侧开关(11)的漏极焊盘(23、43)与所述高侧开关(12)的源极焊盘(24、47)之间延伸,并且所述两个或更多个支路(15、16)位于所述低侧开关(11)的漏极焊盘(23、43)与所述高侧开关(12)的源极焊盘(24、47)之间。

- 5.根据权利要求1至4中任一项所述的半导体模块(10、30、40、80),其中,所述开关节点连接器(14)具有导电层(60)的形式,所述导电层包括至少一个孔(25)以形成彼此物理间隔开的第一支路(15)和第二支路(16)。

- 6.根据权利要求1至4中任一项所述的半导体模块(90),其中,

所述开关节点连接器(14)具有接触夹(91)的形式,其包括至少一个孔(92)以形成彼此物理间隔开的第一支路(15)和第二支路(16)。

- 7.根据权利要求5或6所述的半导体模块(10、30、40、80、90),其中,所述孔(25、92)至少部分地位于所述控制芯片(13)上方。

- 8.根据权利要求5至7中任一项所述的半导体模块(10、30、40、90),其中,所述第一支路和第二支路(15、16)围绕所述控制芯片(13)的相对侧而延伸。

- 9.根据权利要求1至8中任一项所述的半导体模块(10、30、40、80、90),其中,所述低侧 开关(11)和所述高侧开关(12)均具有基本长方体的形式,并且以L形彼此横向邻近布置。

- 10. 根据权利要求1至9中任一项所述的半导体模块(10、30、40、80、90),其中,

所述两个或更多个支路(15、16)形成在单个层中,或者

所述两个或更多个支路(15、16)在通过一个或多个导电连接而连接的至少两个层中延伸。

11.根据权利要求1至10中任一项所述的半导体模块(10、30、40、80、90),其中,所述控制芯片(13)包括栅极驱动器电路,并且耦合到所述低侧开关(11)的栅极和所述高侧开关

### (12)的栅极。

- 12.根据权利要求1至11中任一项所述的半导体模块(10、30、40、80、90),其中,所述半导体模块(10、30、40×80、90)包括覆盖区,所述覆盖区包括 $V_{high}$ 焊盘(54)、 $V_{low}$ 焊盘(56)、开关节点焊盘(61)和一个或多个逻辑焊盘(63),其中,所述开关节点连接器(14)耦合到所述半导体模块(10、30、40×80、90)的所述开关节点焊盘(61)。

- 13. 根据权利要求1至12中任一项所述的半导体模块(10、30、40、80、90),其中,所述低侧开关(11)和所述高侧开关(12)通过所述开关节点连接器(14)串联耦合在所述半导体模块(10、30、40、80、90)的所述 $V_{low}$ 焊盘(56)和所述 $V_{high}$ 焊盘(54)之间,并且所述开关节点连接器(14)位于所述模块(10、30、40、80、90)内。

- 14.根据权利要求1至13中任一项所述的半导体模块(10、30、40、80、90),其中,所述低侧开关(11)和所述高侧开关(12)均由垂直晶体管器件提供。

- 15. 根据权利要求12至14中任一项所述的半导体模块(10、30、40、80、90),其中,

所述低侧开关(11)包括面向所述 $V_{low}$ 焊盘(56)的第一侧(42)上的源极焊盘(41)、以及与所述第一侧(42)相对的第二侧(44)上的漏极焊盘(43),其中,所述漏极焊盘(43)连接到所述开关节点连接器(14),并且

所述高侧开关(12)包括第一侧(48)上的源极焊盘(47)、以及与所述第一侧(48)相对的第二侧(46)上的漏极焊盘(45),其中,所述高侧开关(12)的所述漏极焊盘(45)面向所述 $V_{\rm high}$ 焊盘(54),并且所述源极焊盘(47)连接到所述开关节点连接器(14)。

# 半导体模块

#### 背景技术

[0001] 用于功率电子应用中的晶体管通常用硅(Si)半导体材料来制造。用于功率应用的常见晶体管器件包括Si Cool-MOS®、Si功率MOSFET和Si绝缘栅双极晶体管(IGBT)。这些晶体管器件可连接在一起以提供电路或电路部分。例如,两个晶体管器件可以电连接以形成半桥电路。这种电路通常需要控制电路,其包括可用于切换晶体管的栅极驱动器电路。

[0002] 被耦合以形成半桥电路的两个晶体管器件和具有控制电路的器件可以容纳在单个半导体封装内,其可被称为功率级。由于封装内有限空间可用空间,在封装或模块中的器件之间提供连接具有一些挑战。EP 2 463 904 A2公开了一种多芯片功率方形扁平无引线封装,其中,该封装的引线框被用于电互连。然而,对包括多于一个半导体器件的封装的改善是合期望的。

## 发明内容

[0003] 根据本发明,提供了一种半导体模块,其包括低侧开关、高侧开关和控制芯片。低侧开关和高侧开关被布置成彼此横向邻近,并且通过开关节点连接器耦合以形成半桥电路。开关节点连接器包括两个或更多个支路,所述两个或更多个支路具有相对于低侧开关和高侧开关的布置,并且各自具有横截面积。两个或更多个支路的布置和横截面积被选择成使开关节点连接器内的电流密度分布变得均质。

[0004] 支路的布置包括它们的横向形状和在模块内的布线,例如支路是否具有在低侧开关和高侧开关之间的直接布线或间接布线,并且因此,它们的长度以及它们在模块内相对于低侧开关和高侧开关的位置,例如每个支路的两端相对于低侧开关和高侧开关的位置。

[0005] 由于使用这两个或更多个支路,半导体模块在两个晶体管器件之间的开关节点连接中为功率级提供了更均质的电流流动。这继而可以导致功率损耗和封装电阻的降低。为了使电流流动变得更均质并使其更均匀,开关节点连接器的低电流密度区域通过使用两个支路由附加的"桥"或次级电流路径而连接。两个路径和支路可以通过开关节点连接器中的开口分离,以平衡电流流动并使功率损耗密度分布更均质。两个或更多个支路或晶体管器件的不同区之间的导电路径帮助平衡和平滑开关节点连接器中的非均质的DC电流分布(其可能会在高侧开关接通和低侧开关断开时出现),并去除DC功率损耗密度分布中的热点。由于电流密度分布的不均匀性倾向于随着由于涡电流的产生而引起的开关频率的增加而增加,所以半导体模块可用于具有MHz范围内的驱动器频率的器件。

[0006] 在一些实施例中,开关节点连接器包括布置在低侧开关上的第一部分、布置在高侧开关上的第二部分,并且两个或更多个支路在第一部分和第二部分之间延伸。两个或更多个支路彼此间隔开。在该实施例中,第一和第二支路在公共的第一和第二部分之间延伸,其提供了开关节点连接器的相对的远端部分,并且提供了两个分离的导体,其在第一和第二部分之间以及在低侧开关和高侧开关之间具有不同的布线。

[0007] 在一些实施例中,第二支路的横截面积小于第一支路的横截面积,和/或第二支路的长度大于第一支路的长度。支路的横截面积和长度两者之一可以被调整成使开关节点连

接器内的电流密度分布变得均质。

[0008] 低侧开关和高侧开关都可以由晶体管器件提供。在一些实施例中,低侧开关和高侧开关都由垂直晶体管器件提供。在一些实施例中,开关节点连接器在低侧开关的漏极焊盘与高侧开关的源极焊盘之间延伸,并且两个或更多个支路位于低侧开关的漏极焊盘与高侧开关的源极焊盘之间。因此,支路位于模块内,并且在低侧开关的漏极焊盘与高侧开关的源极焊盘之间横向延伸。

[0009] 在一些实施例中,开关节点连接器具有导电层的形式,该导电层包括至少一个孔以形成彼此物理间隔开的第一支路和第二支路。

[0010] 导电层可用于基于嵌入芯片技术的半导体模块中,其中,低侧开关、高侧开关和控制芯片被嵌入在共同的绝缘层中。导电层可以是沉积层或由支撑在绝缘层上的金属箔层来提供,例如核心层包括增强的热固性树脂。

[0011] 在一些实施例中,开关节点连接器具有接触夹的形式,该接触夹包括至少一个孔以形成彼此物理间隔开的第一支路和第二支路。接触夹可用于包括引线框或重分布基板的半导体模块,其中,低侧开关、高侧开关及控制芯片被安装在基板的重分布结构或引线框的部分上。

[0012] 在一些实施例中,孔至少部分地定位在控制芯片上方。控制芯片的整个横向区域可以位于孔内,或者开关节点连接器的区可以位于控制芯片上方并与控制芯片重叠。例如,如果控制芯片通过接合线连接到重分布层,使得接合线的附加高度可以位于孔内,和/或如果控制芯片具有比低侧开关和高侧开关更大的厚度,则这种布置可能是有用的。

[0013] 在一些实施例中,第一和第二支路围绕控制芯片的相对的横向侧而延伸。

[0014] 在一些实施例中,低侧开关和高侧开关各自具有大致长方体的形式,并且以L形彼此横向邻近布置。这种布置在提供具有小横向尺寸的模块时是有用的,因为长方体的长边可以沿着模块的两个邻接边而布置。控制芯片可被布置在其余角落中。

[0015] 在一些实施例中,低侧开关、高侧开关和控制芯片彼此横向邻近布置,使得它们基本上共面。

[0016] 在一些实施例中,低侧开关、高侧开关和控制芯片彼此横向邻近布置,使得低侧开关、高侧开关和控制芯片中的每一个的主表面基本上共面。

[0017] 在一些实施例中,在单个层中形成两个或更多个支路,或者两个或更多个支路在通过一个或多个导电连接而连接的至少两个层中延伸。导电连接可以是例如焊料连接或导电通孔。如果使用两个层,则两个层可以布置在控制芯片的相对侧上或者控制芯片的相同侧上,即在控制芯片上方或下方。

[0018] 在一些实施例中,控制芯片包括栅极驱动器电路,并且耦合到低侧开关的栅极和高侧开关的栅极。

[0019] 在一些实施例中,半导体模块包括覆盖区,该覆盖区包括 $V_{high}$ 焊盘、 $V_{low}$ 焊盘、开关节点焊盘和一个或多个逻辑焊盘,其中,开关节点连接器耦合到半导体模块的开关节点焊盘。

[0020] 在一些实施例中,低侧开关和高侧开关通过开关节点连接器串联耦合在半导体模块的V<sub>low</sub>焊盘和V<sub>high</sub>焊盘之间,并且开关节点连接器位于该模块内。

[0021] 在一些实施例中,低侧开关和高侧开关都由垂直晶体管器件提供。在一些实施例

中,低侧开关包括面向 $V_{low}$ 焊盘的第一侧上的源极焊盘、和与第一侧相对的第二侧上的漏极焊盘,其中,低侧开关的漏极焊盘连接到开关节点连接器。高侧开关包括第一侧上的源极焊盘、和与第一侧相对的第二侧上的漏极焊盘,其中,高侧开关的漏极焊盘面向 $V_{high}$ 焊盘,而高侧开关的源极焊盘连接到开关节点连接器。

[0022]  $V_{high}$ 焊盘、 $V_{low}$ 焊盘、开关节点焊盘和一个或多个逻辑焊盘可以由引线框的部分来提供。在这些实施例中,低侧开关的源极焊盘安装在 $V_{low}$ 焊盘上,而高侧开关的漏极焊盘安装在引线框的 $V_{high}$ 焊盘上。

[0023] 在使用嵌入芯片技术而制造的半导体模块中, $V_{high}$ 焊盘、 $V_{low}$ 焊盘、开关节点焊盘和一个或多个逻辑焊盘可以形成在模块的绝缘层上,该绝缘层覆盖低侧开关、高侧开关和控制芯片。低侧开关的源极焊盘可以通过一个或多个导电通孔而连接到 $V_{low}$ 焊盘,并且高侧开关的漏极焊盘可以通过一个或多个导电通孔而连接到 $V_{high}$ 焊盘。

[0024] 在一些实施例中,垂直晶体管器件是MOSFET(金属氧化物半导体场效应晶体管)器件、绝缘栅双极晶体管(IGBT)器件或双极结晶体管(BJT)。

[0025] 晶体管器件的电极或端子在此被称为源极、漏极和栅极。如在此所使用的,这些术语还包括其他类型的晶体管器件(例如绝缘栅双极晶体管(IGBT))的功能等效端子。例如,如这里所使用的,术语"源极"不仅包括MOSFET器件和超结器件的源极,而且还包括绝缘栅双极晶体管(IGBT)器件的发射极和双极结晶体管(BJT)器件的发射极,术语"漏极"不仅包括MOSFET器件或超结器件的漏极,而且还包括绝缘栅双极晶体管(IGBT)器件的集电极和BJT器件的集电极,并且术语"栅极"不仅包括MOSFET器件或超结器件的栅极,而且还包括绝缘栅双极晶体管(IGBT)器件的栅极和BJT器件的基极。

[0026] 在一些实施例中,半导体模块还包括电感器。在一些实施例中,电感器是电耦合在开关节点连接器和输出焊盘 $V_{out}$ 之间的输出电感器。在这些实施例中,半导体模块包括覆盖区,该覆盖区包括 $V_{high}$ 焊盘、 $V_{low}$ 焊盘、 $V_{out}$ 焊盘和一个或多个逻辑焊盘。

[0027] 本领域技术人员在阅读以下详细描述并查看附图后将认识到附加的特征和优点。

#### 附图说明

[0028] 附图中的要素不一定相对于彼此成比例。相同的附图标记表示相应的类似部件。 各种所示实施例的特征可以组合,除非它们彼此排斥。示例性实施例在附图中描绘并且在 随后的描述中详述。

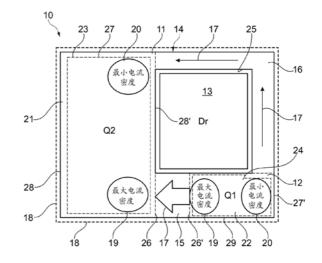

[0029] 图1示出根据一个实施例的半导体模块的示意性平面图;

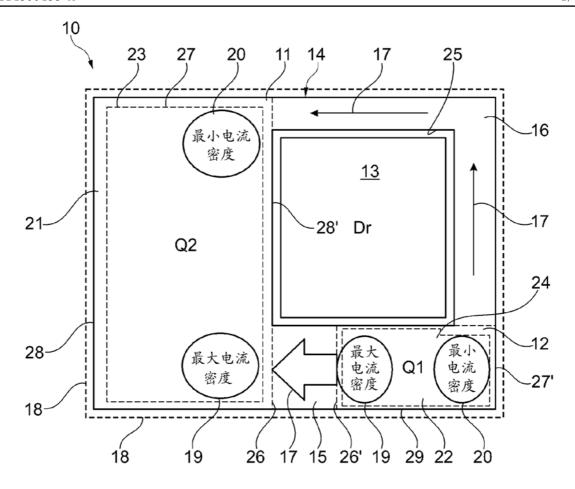

图2示出根据一个实施例的半导体模块的示意性平面图;

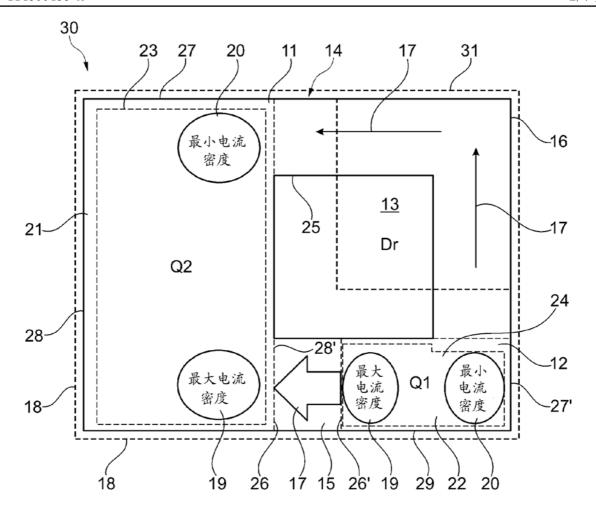

图3包括图3A和3B,示出根据一个实施例的半导体模块的平面图和截面图:

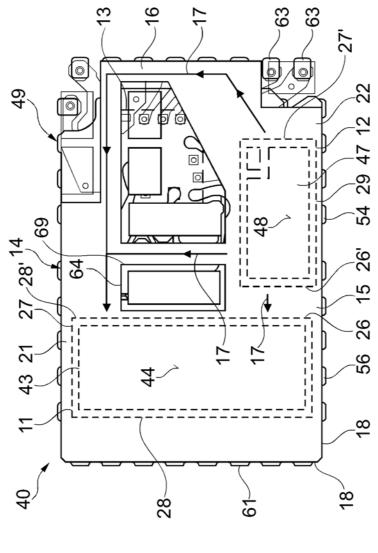

图4示出根据一个实施例的半导体模块的平面图:

图5包括图5A至图5C,示出根据一个实施例的半导体模块的透视图、侧视图和部分透明的平面图;

图6示出根据一个实施例的半导体模块的透视图。

# 具体实施方式

[0030] 在以下详细描述中,参考了附图,附图形成了详细描述的一部分,并且在附图中通

过说明的方式示出了其中可以实践本发明的具体实施例。在这方面,参考所描述的(一个或多个)附图的取向来使用诸如"顶部"、"底部"、"前面"、"后面"、"头部"、"尾部"等之类的方向术语。由于实施例的组件可以以多个不同的取向来定位,所以方向术语被用于说明的目的,而绝不是限制。应该理解,在不脱离本发明范围的情况下,可以利用其他实施例,并且可以进行结构或逻辑上的改变。其以下详细描述不应被理解为限制性的,并且本发明的范围由所附权利要求来限定。

[0031] 下面将解释多个示例性实施例。在这种情况下,在附图中,相同的结构特征由相同或相似的附图标记来标识。在本说明书的上下文中,"横向"或"横向方向"应当被理解为表示大致平行于半导体材料或半导体载板的横向范围而延伸的方向或范围。因此,横向方向是大致平行于这些表面或侧面延伸的。与此相对,术语"垂直"或"垂直方向"应被理解为表示大致垂直于这些表面或侧面并因此垂直于横向方向而延伸的方向。因此,垂直方向在半导体材料或半导体载板的厚度方向上延伸。

[0032] 如本说明书中所采用的,当诸如层、区或基板之类的要素被称为在另一要素"上"或延伸到另一要素"上"时,其可以直接在另一要素上或直接延伸到另一要素上,或者也可以存在中间要素。与之相对,当要素被称为"直接在"另一要素上或"直接延伸到"另一要素上时,则不存在中间要素。

[0033] 如在本说明书中所使用的,当一个元件被称为"连接"或"耦合"到另一元件时,它可以直接连接或耦合到另一元件,或者也可以存在中间元件。与之相对,当一个元件被称为"直接连接"或"直接耦合"到另一元件时,则不存在中间元件。

[0034] 本发明解决了对集成功率级(也称为集成功率转换器)中的电流流动进行平衡,以便改善电性能。集成功率级通常包括半桥电路和控制芯片,所述半桥电路包括低侧开关和高侧开关,所述控制芯片通常具有用于驱动高侧开关和低侧开关的驱动器电路。功率级通常被提供为半导体模块。

[0035] 导致晶体管器件(其提供低侧开关和高侧开关)的Rdson减小的功率半导体技术的持续发展导致了期望进一步减小功率级封装的电阻,以便改善总效率,因为集成功率级的电阻会影响传导损耗,并且因此会影响功率级中的总损耗。一些功率级模块具有非均质的电流流动,例如在两个晶体管器件之间的开关节点连接中,这继而可能导致功率损耗和封装电阻的增加。一些功率级模块具有两个晶体管器件的非对称相互位置。这种非对称相互位置可能会导致非均质的电流流动,尤其是在两个晶体管器件之间的开关节点连接中。电流密度分布的不均匀性倾向于随着由于涡电流的产生而引起的频率的增加而增加,使得这种负面效应对于具有MHz范围内的驱动器频率的器件来说尤其强烈。

[0036] 根据本发明,为了使电流流动变得均质(homogenise)并使其在功率级内更均匀,提出了通过除初级路径之外的"桥"或次级电流路径来连接晶体管器件的低电流密度区域。初级路径通常是两个晶体管之间的最短路径。这在开关节点连接中产生两个路径,以平衡电流流动,并使功率损耗密度分布能够变得更均质。晶体管器件的不同区之间的两个支路或导电路径有助于平衡和平滑开关节点连接器中的非均质DC电流分布以用于高侧导通-低侧关断切换,并且有助于去除开关节点连接器中的DC功率损耗密度分布中的热点。

[0037] 这种平衡方法聚焦于减轻由切换引起的涡电流效应,该涡电流效应被预期成针对较高频率范围而增加。另外,还没有发现所提出的设计改变具有回路电感的任何增加。

[0038] 该方法适用于使用嵌入芯片技术来制造的模块和基于引线框的技术,例如比如封装的PQFN。

[0039] 可以提供次级电流路径而不需要任何附加的处理步骤或对模块基本结构的改变。根据设计,可以在不同的层中形成用于电流流动的次级电流路径。一个选项是在与初级电流路径相同的层中对次级电流路径进行布线。如果没有足够的空间来为相同层中的两个路径提供布线,则也可以至少部分地在初级电流路径之上的层中或在初级电流路径之下的层中进行布线,例如在嵌入式芯片封装的核心层中或在管芯的相对侧上的层上。模块和使用该模块的系统的性能和可靠性都得以改善。另外,不需要改变模块覆盖区。提供了功率级的电性能,特别是由于电阻的减小而导致的效率的增加。

[0040] 图1示出了根据一个实施例的半导体模块10的示意性平面图。半导体模块10包括也用Q2表示的低侧开关11、也表示为Q1的高侧开关12、以及也用DR表示的控制芯片13。低侧开关11和高侧开关12彼此横向邻近地布置,并且通过开关节点连接器14耦合以形成半桥电路。开关节点连接器14包括两个支路15、16,它们具有相对于低侧开关11和高侧开关12的布置,并且每个支路分别具有横截面积A1、A2。两个支路15、16的布置和横截面积A1、A2被选择成使开关节点连接器14内的电流密度分布变得均质。开关节点连接器14用于在高侧开关12和低侧开关11之间载送电流,如图1中由箭头17所示。

[0041] 支路15、16的布置包括它们的横向形状和在模块10内的布线,例如支路是否具有在低侧开关11和高侧开关12之间的直接布线或间接布线,并且因此,它们的长度以及它们在模块10内相对于低侧开关11和高侧开关12的位置,例如每个支路15、16的两端相对于低侧开关11和高侧开关12的位置。

[0042] 在图1所示的半导体模块10中,低侧开关11和高侧开关12均具有大致长方体形式,并且彼此横向邻近布置,且彼此间隔开以形成L形。低侧开关11的长边28和高侧开关的长边29基本上平行于模块10的基本上彼此垂直的两个邻接边18。这种L形可以被认为是低侧开关11和高侧开关12的相互不对称的布置。在不采取进一步措施的情况下,与低侧开关11和高侧开关12的彼此面对的侧面26、26'直接邻近的区19中的开关节点连接器14中的电流密度将比远离该边界定位(例如,在低侧开关11的相对侧面27和高侧开关12的相对侧面27′处)的开关节点连接器14的区20中的电流密度高得多,如图1中由椭圆19、20示意性地指示的。

[0043] 为了使电流变得均质并在开关节点连接器14内提供更均匀的电流密度分布以便减小或甚至消除最大电流密度区19和最小电流密度区20之间的差异,开关节点连接器14设置有两个支路15、16,这两个支路在物理上彼此分离,并因此提供了用于在高侧开关12和低侧开关11之间载送电流的两个单独路径17。由第一支路15提供的较高电流密度区19之间的路径17可表示为初级路径,而由第二支路16提供的路径17可表示为次级路径。

[0044] 在图1所示的实施例中,控制芯片13定位成与低侧开关11和高侧开关12横向邻近,使得其定位成与进行切换的低侧开关11和高侧开关12的长边邻近并间隔开。开关节点连接器14的第一支路15与控制芯片13的一侧邻近延伸,而第二支路16围绕控制芯片13的两个相对的侧边缘延伸。

[0045] 开关节点连接器14包括布置在低侧开关11上的第一部分21和布置在高侧开关12上的第二部分22。两个支路15、16在第一部分21和第二部分22之间延伸,使得开关节点连接

器14具有远端21、22,所述远端21、22通过由物理上分开的支路15、16提供的单独路径而耦合。在该实施例中,第一支路15和第二支路16围绕控制芯片13的外围延伸,使得控制芯片13不被开关节点连接器14覆盖。

[0046] 第一支路15在两个较高电流密度区19之间延伸,而第二支路16在两个较低电流密度区20之间延伸。在该实施例中,第二支路16的横截面积A2小于第一支路15的横截面积A1。两个支路15、16的横截面积A1、A2以及每个支路15、16的横截面积之间的比率A1/A2可以被选择成使两个支路15、16内以及直接位于低侧开关11和高侧开关12上的第一和第二部分21、22中的电流密度变得均质。作为替选或附加,第二支路16的长度大于第一支路15的长度。

[0047] 在一些实施例中,低侧开关11和高侧开关均由晶体管器件提供,该晶体管器件是具有垂直漂移路径的垂直晶体管器件。在垂直晶体管器件中,漏极电极由后表面处的漏极区形成。源极电极和栅极电极形成在相对的前表面处。晶体管器件可以是MOSFET(金属氧化物半导体场效应晶体管)器件、绝缘栅双极晶体管(IGBT)器件、或双极结晶体管(BJT)。

[0048] 晶体管器件的电极或端子在此被称为源极、漏极和栅极。如在此所使用的,这些术语还包括其他类型的晶体管器件(例如绝缘栅双极晶体管(IGBT))的功能等效端子。例如,如这里所使用的,术语"源极"不仅包括MOSFET器件和超结器件的源极,而且还包括绝缘栅双极晶体管(IGBT)器件的发射极和双极结晶体管(BJT)器件的发射极,术语"漏极"不仅包括MOSFET器件或超结器件的漏极,而且还包括绝缘栅双极晶体管(IGBT)器件的集电极和BJT器件的集电极,并且术语"栅极"不仅包括MOSFET器件或超结器件的栅极,而且还包括绝缘栅双极晶体管(IGBT)器件的栅极和BJT器件的基极。

[0049] 开关节点连接器14在低侧开关11的漏极焊盘23和高侧开关12的源极焊盘24之间延伸,以串联连接低侧开关11和高侧开关12。因此,开关节点连接器14的第一部分21位于漏极焊盘23上,第二部分22位于源极焊盘24上,并且两个支路15、14在低侧开关11的漏极焊盘23和高侧开关12的源极焊盘24之间延伸并且在模块10内。

[0050] 在一些实施例中,开关节点连接器14具有导电层的形式,其包括至少一个孔25以便形成第一支路15和第二支路16。在图1所示的实施例中,孔25具有横向尺寸和形状,并且被定位成使得控制芯片13完全位于孔25内。以导电层形式的开关节点连接器14可以有效地用在具有基于嵌入芯片技术并具有叠层结构的半导体模块中,在该叠层结构中低侧开关11、高侧开关12和控制芯片13嵌入在绝缘层中并彼此横向邻近地布置在公共绝缘层内。

[0051] 在一些实施例中,开关节点连接器14具有接触夹的形式,其包括至少一个孔25,以形成彼此物理地间隔开的第一支路15和第二支路16。例如,以接触夹形式的开关节点连接器14可用于使用基于引线框的技术的半导体模块。

[0052] 图2示出了根据一个实施例的半导体模块30的示意性平面图。本实施例的变化在于开关节点连接器14的第二支路16的位置相对于控制芯片13的位置。在本实施例中,提供了L形的第二支路16,其在低侧开关11和高侧开关12的侧面27、27'之间延伸,它们位于模块20的对角相对的角落中并且与低密度区20邻近,如参考图1所述的实施例。第二支路16以及因此开关节点连接器14部分地位于控制芯片13的两个邻接边缘之上,使得仅控制芯片13的角落保持不被第二支路16和开关节点连接器14覆盖,并且使得开关节点连接器14特别是第二支路16与控制芯片13部分地重叠。开关节点连接器14中的孔25位于控制芯片13的区域的

仅一部分之上。在本实施例中,第二支路16被示为具有比图1中所示的实施例中更大的横截面积A2。因此,图2的实施例的支路15、16的横截面积的比率即A1/A2小于图1中所示的实施例中的比率。

[0053] 在半导体模块30中,控制芯片13位于半导体模块30的外围边缘处,其由虚线31表示。

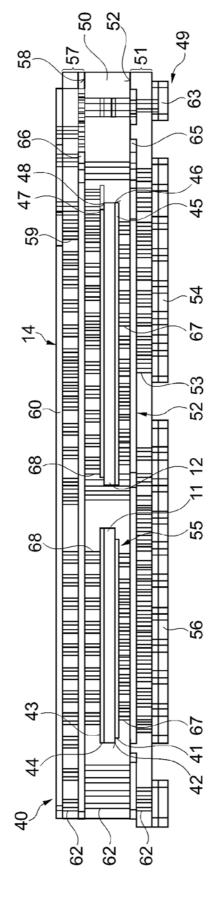

[0054] 图3包括图3A和3B,分别示出了根据一个实施例的半导体模块40的平面图和截面图。半导体模块40包括低侧开关11、高侧开关12和控制芯片13。低侧开关11、高侧开关12和控制芯片13彼此横向邻近布置。低侧开关11和高侧开关12均具有基本长方体的形式,并且被布置为使得低侧开关11的长边28和高侧开关12的长边29定位成基本上平行于模块18的邻接边18,并且使得高侧开关12的短边26'基本上平行于低侧开关11的长边28',使得在平面图中形成L形。

[0055] 低侧开关11和高侧开关12均由垂直晶体管器件形成。低侧开关11包括在其下侧42上的源极焊盘41、以及在其下侧42上的栅极焊盘(其在图3B的截面图中不可见)、以及在其上侧44上的漏极焊盘43。高侧开关12包括在其下侧46上的漏极焊盘45、以及在其上侧48上的源极焊盘47和栅极焊盘(其在截面图中不可见)。低侧开关11和高侧开关12被布置为基本上彼此共面,使得下表面42、40面向半导体模块40的下表面70。下表面70提供覆盖区,其包括半导体模块40的外部接触表面49。

[0056] 半导体模块40具有使用嵌入芯片技术来制造的叠层结构,使得低侧开关11、高侧开关12及控制芯片13被嵌入核心绝缘层50中。半导体模块40包括第一重分布层51,其位于绝缘核心层50的下表面52上。第一重分布层51包括绝缘层、横向导电层49及延伸穿过绝缘层的导电通孔53。导电层提供了外部接触表面49。第一重分布层包括第一导电重分布结构52,其包括导电通孔53并在漏极焊盘45和半导体模块40的V<sub>high</sub>焊盘54之间延伸。第一重分布层51还包括第二重分布结构55,其包括导电通孔53并在源极焊盘42和第一重分布层51的下表面上的V<sub>low</sub>接触焊盘56之间延伸。第一重分布层51还包括用于栅极焊盘中的每一个的其他导电重分布结构以及在控制芯片13和模块40的逻辑焊盘63之间的其他导电重分布结构。

[0057] 半导体模块40还包括位于绝缘核心层50的上表面58上的第二重分布层57,其用于形成开关节点连接器14,其在高侧开关12的源极焊盘47和低侧开关11的漏极焊盘43之间延伸。第二重分布层57包括绝缘层、横向导电层60以及延伸穿过绝缘层的导电通孔59。在本实施例中,开关节点连接器14还包括导电通孔59,其延伸穿过第二重分布层57并且在基本上平坦的导电层60之间延伸以电耦合高侧开关12的源极焊盘47和低侧开关11的漏极焊盘43。开关节点连接器14还通过一个或多个导电通孔连接到位于半导体模块40的下表面70上的开关节点焊盘V<sub>SW</sub> 61,所述一个或多个导电通孔在穿过第一和第二重分布层51、57的导电层60与绝缘核心层50之间延伸。

[0058] 半导体模块40还包括多个逻辑焊盘63,其位于模块40的下表面上,并且电连接到控制芯片13。一些逻辑焊盘63还可以提供用于低侧开关11和/或高侧开关12的感测功能。

[0059] 在一些实施例中,第一和第二重分布层51、57中的一者或两者具有多层重分布结构,其包括多于一个水平横向导电层。

[0060] 如图3A的平面图所示,开关节点连接器14的平面导电层60包括两个支路15、16,它

们围绕位于控制芯片13上方的孔25的相对侧而延伸。在该实施例中,控制芯片13部分地未被开关节点连接器14覆盖。第一和第二支路15、16在位于高侧开关12上的公共第二部分22和连接在低侧开关11上的公共第一部分21之间延伸。第二支路16的宽度和横截面积小于第一支路15的宽度和所得的横截面积。在该实施例中,开关节点连接器14和导电层60还包括另一孔64,电感器可以位于该孔64中。

[0061] 在一些实施例中,在外部接触焊盘49与低侧开关11、高侧开关12和开关节点连接器14之间的重新布线结构的一部分被形成在绝缘核心层50上。例如,绝缘核心层50可以由增强热固性树脂提供,如通常用于印刷电路板的核心层那样并且其包括由位于两个相对表面52、58上的金属箔形成的导电层65、66。这些导电层65、66可以被图案化以形成重分布结构的部分,例如在低侧开关11的源极焊盘41和V<sub>1ow</sub>焊盘56之间以及在高侧开关12的漏极焊盘45和V<sub>high</sub>焊盘54之间。其他导电通孔67位于该导电层65和低侧开关11和高侧开关12的相应焊盘41、45之间。类似地,位于绝缘核心层50的相对表面58上的导电层66可以形成开关节点连接器14的导电重分布结构的一部分,其中,其他导电通孔68位于该横向导电层66和高侧开关12的源极焊盘47之间以及导电层66和低侧开关11的漏极焊盘43之间。

[0062] 两个支路15、16提供了用于在源极焊盘47和漏极焊盘43之间载送电流的两个布线。第一布线由第一支路15提供,其直接在彼此面对的高侧开关12和低侧开关11的侧面26、26'之间延伸。第二支路16提供第二布线,其最初从高侧开关12沿远离低侧开关11的方向延伸并且形成围绕控制芯片13的外围的环路,以在高侧开关12和低侧开关11的两个对角相对端部之间提供导电连接。两个支路15、16的这种布置用于使开关节点连接器14内的电流分布变得均质。

[0063] 由开关节点焊盘61和V<sub>high</sub>焊盘54之间的第二支路16提供的次级电流路径被用于平衡电流密度分布,降低器件的导通和总电阻。对于这种类型的模块40,仿真指示了在2 MHz驱动器频率和15%占空比下的传导损耗可以比没有第二支路16并且仅具有由第一支路15提供的单个电流路径的布置减少2.3%和3.4%。

[0064] 用于电感器的孔64可以横向地定位在低侧开关11和控制芯片13之间,并且与定位在控制芯片13上方的孔25间隔开。因此,在该实施例中,开关节点连接器14可以被认为包括第三支路69,其在所有三个支路15、16、69所共有并且定位在高侧开关12上的第二部分21与所有三个支路15、16、69所共有的定位在低侧开关11上的第一部分21之间延伸。在高侧开关12的源极焊盘47和低侧开关11的漏极焊盘43之间提供了沿不同方向延伸的三个导电路径17。

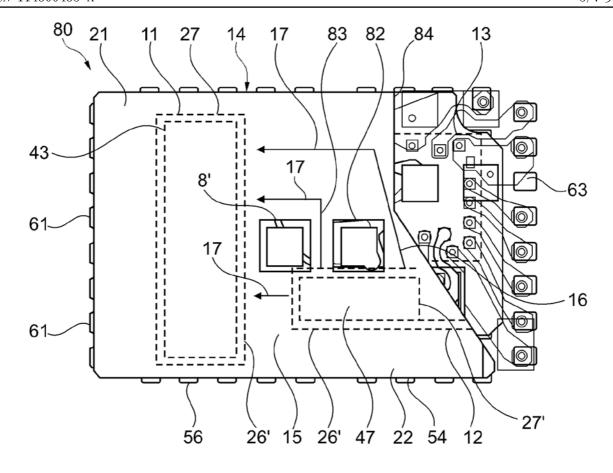

[0065] 图4示出根据一个实施例的半导体模块80的平面图。在该实施例中,开关节点连接器14包括两个孔81、82,其定位成与高侧开关12和低侧开关11横向邻近,并且其每个露出用于电容器的接触焊盘。在该实施例中,开关节点连接器14并且具体地横向导电层60具有横向的形式,使得控制芯片13的一部分或全部定位成与开关节点连接器14的外围84横向邻近。

[0066] 第二支路16形成在第二孔82和导电层60的外围84之间。第二支路16部分地位于控制芯片13之上,并且控制芯片13和低侧开关11及高侧开关12之间。第二支路16位于与高侧开关12和低侧开关11相同的控制芯片13的一侧上,而不是如图1至3所示的实施例中那样位于控制芯片13的相对侧上。

[0067] 开关节点连接器14包括位于高侧开关12的源极焊盘47上的第二部分22和位于低侧开关11的漏极焊盘43上的第一部分21之间的三个支路15、16、83。第二支路16在两个对角最外部(即高侧开关12和低侧开关11的侧面27、27')之间延伸,并且因此,除了在高侧开关12和低侧开关11的彼此面对的侧面26、26'之间直接延伸的第一支路15的最短路径17之外,还提供了另一路径17。第三支路83在两个孔81、82之间延伸,并且从位于高侧开关12的源极焊盘47上的第二部分22和位于低侧开关11的漏极焊盘43上的第一部分21延伸。第三支路83提供了位于第一和第二支路15、16的路径17之间的附加的路径17。

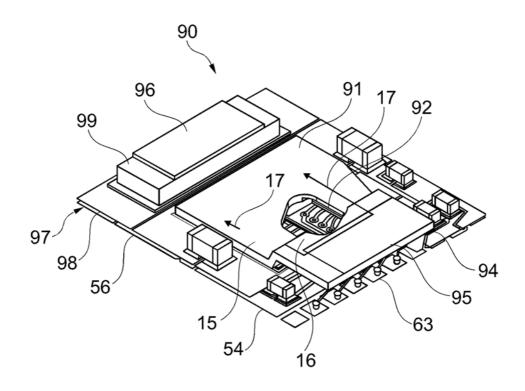

[0068] 图5包括图5A至图5C,示出了根据一个实施例的半导体模块80的透视图、侧视图和部分透明的平面图。

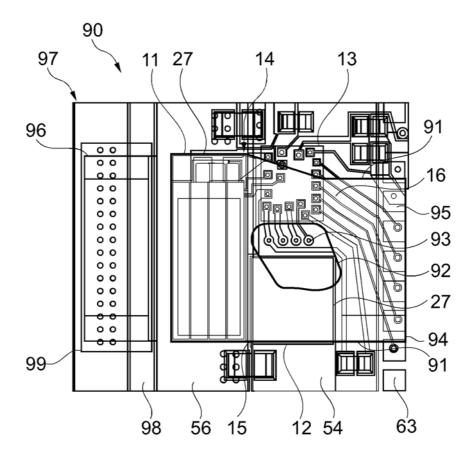

[0069] 半导体模块90包括彼此横向邻近布置的低侧开关11、高侧开关12和控制芯片13、以及在高侧开关12和低侧开关11之间延伸的开关节点连接器14。

[0070] 在一些实施例中,包括具有两个或更多个支路的开关节点连接器14的半导体模块使用用于封装低侧开关11、高侧开关12和控制芯片13的嵌入技术来制造。然而,半导体模块也可以使用诸如基于引线框的技术之类的其他封装技术来制造。

[0071] 图5所示的半导体模块90是基于引线框97设计的,由此引线框97的部分提供了 $V_{high}$ 焊盘54、 $V_{low}$ 焊盘56、开关节点焊盘61和一个或多个逻辑焊盘63。例如使用焊料或导电粘合剂,将低侧开关11的源极安装并电连接到 $V_{low}$ 焊盘56上,并且将高侧开关12的漏极安装并电连接到 $V_{high}$ 焊盘54上。控制开关13安装在管芯焊盘上,该管芯焊盘可以提供模块的外部焊盘或者可以位于模块内。

[0072] 在该实施例中,半导体模块90包括开关节点连接器14,其由接触夹91提供。接触夹91由独立构件形成,该独立构件由金属或合金形成,典型地由铜或铜基合金形成。以接触夹91形式的开关节点连接器14包括孔92,其被定位成使得当安装在模块90中时,孔92至少部分地定位在控制芯片13上方,并且提供在高侧开关12和低侧开关11之间延伸的两个支路15、16。第一支路15直接在高侧开关12和低侧开关11的侧面26、26'之间延伸,而第二支路16围绕孔92在布置在模块90的对角相对角落中的相对侧面27、27'之间的孔92的相对侧上延伸。

[0073] 在此实施例中,到控制芯片13的连接93位于开关节点连接器14的孔内。导电夹91还包括延伸部分94,其相对侧具有升高的腿,使得第二支路16的部分可位于半导体模块90的其他组件上方。在一些实施例中,开关节点连接器14连接至开关节点焊盘。在一些实施例中,模块90还包括耦合在开关节点连接器14和V<sub>out</sub>焊盘之间的输出电感器。

[0074] 半导体模块90还包括焊盘95、96,其上可以安装图5中未示出的输出电感器。焊盘95位于提供开关节点连接器14的接触夹91的上表面上,并且位于延伸部分94上。焊盘96位于与低侧开关11的面向外的长边邻近布置的基座99上。基座99布置在V<sub>out</sub>焊盘98上。在安装位置中,输出电感器的一端连接到开关节点连接器14上的焊盘95,而另一端连接到V<sub>out</sub>焊盘98。V<sub>out</sub>焊盘98可以继而连接到从半导体模块90接收功率的负载。基座99和延伸部分94使得输出电感器能够安装在高侧开关12、低侧开关11和控制芯片11的上方。

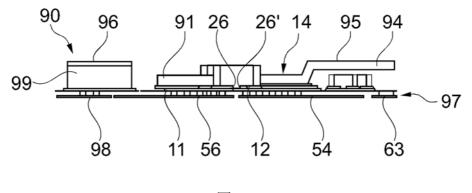

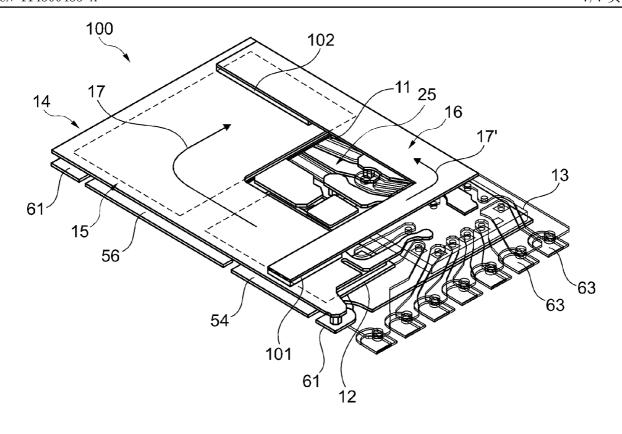

[0075] 图6示出根据一个实施例的半导体模块100的透视图。半导体模块100具有类似于图1和2所示的低侧开关11、高侧开关12和控制芯片13的布置。在该实施例中,开关节点连接器14具有由单独的分立元件提供并且在两个不同层中延伸的两个支路15、16。这些层被布

置在距引线框97的主表面不同的垂直距离处。支路15、16中的每一个可以由例如导电层或金属箔来提供。

[0076] 第一支路15具有L形并且位于两层中的下层中。第一支路15在第一远端处位于高侧芯片12的源极上并与之电连接,并在第二远端处与低侧开关的漏极电连接。第二支路16也具有L形,并且相对于第一支路15横向定位,使得在两个L形之间形成至少部分地位于控制芯片13上方的孔25。第二支路16定位在第一支路15上和上方。第二支路16的第一远端定位在高侧开关12上方的第一支路15上,且第二支路16的第二远端定位在低侧开关11上方的第一支路15上。

[0077] 因此,第二支路16位于第一支路15上方以形成堆叠,使得第一支路15位于开关和第二支路16之间。在其他实施例中,支路15、16的垂直布置可以颠倒,使得第二支路16位于开关和第一支路15之间。开关节点连接器14的两个支路15和16都布置在控制芯片13的相同侧,但是在控制芯片13垂直上方的不同平面中。在其他未示出的实施例中,两个支路15、16可以布置在位于控制芯片13的相对侧上(即位于控制芯片13的上方和下方)的平面中。

[0078] 两个支路15、16通过在两层之间垂直延伸的导电连接101、102而连接。例如,导电连接101、102可以由焊料或一个或多个导电通孔来形成。焊料连接可以用于使用基于引线框的封装技术而制造的半导体模块,并且导电通孔可以用于使用嵌入封装技术而制造的半导体模块。L形第二支路16的臂具有比L形第一支路17的臂更小的宽度,使得第二支路16提供第二电流载送路径17',并且第一支路15提供开关节点连接器14内的初级电流载送路径17。

[0079] 为了便于描述,使用诸如"之下"、"下方"、"下部"、"上方"、"上部"等之类的空间相对术语来解释一个要素相对于第二要素的定位。这些术语旨在包括除了与图中所示的那些不同的取向之外的器件的不同取向。此外,诸如"第一"、"第二"等之类的术语也用于描述各种要素、区、部分等,并且也不旨在是限制性的。在整个说明书中,相同的术语指代相同的要素。

[0080] 如本文所用,术语"具有"、"含有"、"包含"、"包括"等是开放式术语,其指示了所述要素或特征的存在,但不排除另外的要素或特征。冠词"一"、"一个"和"该"旨在包括复数以及单数,除非上下文另有明确指示。应当理解,除非另外特别指出,否则本文所述的各种实施例的特征可彼此组合。

[0081] 尽管在此已经示出和描述了特定实施例,但是本领域普通技术人员应当理解,在不偏离本发明范围的情况下,可以用各种替代和/或等同实现来替代所示出和描述的特定实施例。本申请旨在覆盖这里讨论的具体实施例的任何修改或变化。因此,本发明旨在仅由权利要求及其等同替换物来限制。

图 1

图 2

图 3A

图 3B

图 4

图 5A

图 5B

图 5C

图 6