# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111048523 A (43)申请公布日 2020.04.21

(21)申请号 201911167550.1

(22)申请日 2019.11.25

(71)申请人 武汉华星光电半导体显示技术有限 公司

地址 430079 湖北省武汉市东湖新技术开 发区高新大道666号光谷生物创新园 C5栋305室

(72)发明人 胡泉 李松杉

(74)专利代理机构 深圳紫藤知识产权代理有限 公司 44570

代理人 何辉

(51) Int.CI.

*H01L* 27/12(2006.01) *H01L* 21/77(2017.01)

权利要求书1页 说明书6页 附图3页

### (54)发明名称

阵列基板及其制备方法

#### (57)摘要

本申请提供一种阵列基板及其制备方法,该 阵列基板包括在衬底上依次层叠设置栅极层、栅 极绝缘层、有源层、沟道保护层、刻蚀阻挡层、以 及源漏极层,其中,有源层包括沟道区和掺杂区, 沟道保护层设置于沟道区上;通过在有源层的沟 道区上方设置沟道保护层,利用沟道保护层良好 的物理特性和化学特性,可以大幅度减少沟道区 界面的缺陷,同时防止水或氧气进入薄膜晶体 管,从而改善了阵列基板的电性能,进而改善了 对显示面板的驱动效果,改善了显示器件的发光 特性。

1.一种阵列基板,其特征在于,包括:

衬底:

栅极层,形成于所述衬底上,图案化形成栅极;

栅极绝缘层,形成于所述栅极层上,覆盖所述栅极层和所述衬底:

有源层,形成于所述栅极绝缘层上,图案化形成有源区,所述有源区包括沟道区和掺杂区;

沟道保护层,形成于所述有源层上,图案化形成位于所述沟道区上方的沟道保护区:

刻蚀阻挡层,形成于所述沟道保护层上,覆盖所述沟道保护层、所述有源层、以及所述栅极绝缘层:

源漏极层,形成于所述刻蚀阻挡层上,图案化形成源极和漏极,所述源极或所述漏极通过过孔与所述掺杂区相连。

- 2. 如权利要求1所述的阵列基板,其特征在于,所述沟道保护区仅对应于所述沟道区。

- 3. 如权利要求1所述的阵列基板,其特征在于,所述沟道保护区对应于所述沟道区和部分所述掺杂区。

- 4. 如权利要求1所述的阵列基板,其特征在于,所述沟道保护层的材料为铟锌氧化物。

- 5. 如权利要求3所述的阵列基板,其特征在于,所述沟道保护层的厚度为4~6nm。

- 6.一种阵列基板的制备方法,其特征在于,包括:

提供衬底:

在所述衬底上制备栅极层;

在所述栅极层上制备栅极绝缘层:

在所述栅极绝缘层上制备有源层;

在所述有源层上制备沟道保护层:

在所述沟道保护层上制备刻蚀阻挡层;

在所述刻蚀阻挡层上制备源漏极层。

7.如权利要求6所述的制备方法,其特征在于,所述在所述栅极绝缘层上制备有源层的 具体步骤包括:

采用物理气相沉积法,在所述栅极绝缘层上沉积一层铟镓锌氧化物薄膜:

对所述铟镓锌氧化物薄膜进行图案化,形成有源区;

对所述有源区进行部分掺杂,形成掺杂区和沟道区。

8. 如权利要求6所述的制备方法,其特征在于,所述在所述有源层上制备沟道保护层的 具体步骤包括:

采用物理气相沉积法,在所述沟道区上沉积一层铟锌氧化物薄膜,作为沟道保护层。

- 9.如权利要求8所述的制备方法,其特征在于,所述铟锌氧化物薄膜的沉积厚度为4~6nm。

- 10.如权利要求6所述的制备方法,其特征在于,所述在所述沟道保护层上制备刻蚀阻挡层的具体步骤包括:

采用化学气相沉积法,在所述沟道保护层上沉积一层氧化硅薄膜,作为刻蚀阻挡层,所述刻蚀阻挡层覆盖所述沟道保护层、所述有源层、以及所述栅极绝缘层。

# 阵列基板及其制备方法

## 技术领域

[0001] 本申请涉及显示领域,具体涉及一种阵列基板及其制备方法。

## 背景技术

[0002] Oxide TFT (Thin Film Transistor,氧化物薄膜晶体管)由于电子迁移率高,漏电流低,制备温度低等特点,引起了广泛的关注。

[0003] 现有技术中,0xide TFT的制作方式是在制备了氧化物有源层后,再制备蚀刻阻挡层,最后再制作源漏极,完成TFT器件的制作。但是这样做出的TFT器件,氧化物有源层的背沟道缺陷较多,和刻蚀阻挡层形成的界面容易受到水和氧气的影响,进而对TFT的电性产生很大的影响,影响显示面板的驱动,进而影响显示器的发光特性。

[0004] 因此,现有0xide TFT存在缺陷,需要改进。

# 发明内容

[0005] 本申请提供一种阵列基板,以缓解现有0xide TFT存在缺陷的问题。

[0006] 为解决以上问题,本申请提供的技术方案如下:

[0007] 本申请提供一种阵列基板,其包括:

[0008] 衬底:

[0009] 栅极层,形成于所述衬底上,图案化形成栅极;

[0010] 栅极绝缘层,形成于所述栅极层上,覆盖所述栅极层和所述衬底;

[0011] 有源层,形成于所述栅极绝缘层上,图案化形成有源区,所述有源区包括沟道区和掺杂区:

[0012] 沟道保护层,形成于所述有源层上,图案化形成位于所述沟道区上方的沟道保护区;

[0013] 刻蚀阻挡层,形成于所述沟道保护层上,覆盖所述沟道保护层、所述有源层、以及所述栅极绝缘层;

[0014] 源漏极层,形成于所述刻蚀阻挡层上,图案化形成源极和漏极,所述源极或所述漏极通过过孔与所述掺杂区相连。

[0015] 在一些实施例中,所述沟道保护区仅对应于所述沟道区。

[0016] 在一些实施例中,沟道保护区对应于所述沟道区和部分所述掺杂区。

[0017] 在一些实施例中,沟道保护层的材料为铟锌氧化物。

[0018] 在一些实施例中,沟道保护层的厚度为4~6nm。

[0019] 同时,本申请实施例提供一种阵列基板的制备方法,其包括:

[0020] 提供衬底:

[0021] 在所述衬底上制备栅极层;

[0022] 在所述栅极层上制备栅极绝缘层;

[0023] 在所述栅极绝缘层上制备有源层:

- [0024] 在所述有源层上制备沟道保护层:

- [0025] 在所述沟道保护层上制备刻蚀阻挡层;

- [0026] 在所述刻蚀阻挡层上制备源漏极层。

- [0027] 在一些实施例中,所述在所述栅极绝缘层上制备有源层的具体步骤包括:

- [0028] 采用物理气相沉积法,在所述栅极绝缘层上沉积一层铟镓锌氧化物薄膜;

- [0029] 对所述铟镓锌氧化物薄膜进行图案化,形成有源区;

- [0030] 对所述有源区进行部分掺杂,形成掺杂区和沟道区。

- [0031] 在一些实施例中,所述在所述有源层上制备沟道保护层的具体步骤包括:

- [0032] 采用物理气相沉积法,在所述沟道区上沉积一层铟锌氧化物薄膜,作为沟道保护层。

- [0033] 在一些实施例中,所述铟锌氧化物薄膜的沉积厚度为4~6nm。

- [0034] 在一些实施例中,所述在所述沟道保护层上制备刻蚀阻挡层的具体步骤包括:

- [0035] 采用化学气相沉积法,在所述沟道保护层上沉积一层氧化硅薄膜,作为刻蚀阻挡层,所述刻蚀阻挡层覆盖所述沟道保护层、所述有源层、以及所述栅极绝缘层。

[0036] 本申请提供一种阵列基板及其制备方法,该阵列基板包括在衬底上依次层叠设置栅极层、栅极绝缘层、有源层、沟道保护层、刻蚀阻挡层、以及源漏极层,其中,有源层包括沟道区和掺杂区,沟道保护层设置于沟道区上;通过在有源层的沟道区上方设置沟道保护层,利用沟道保护层良好的物理特性和化学特性,可以大幅度减少沟道区界面的缺陷,同时防止水或氧气进入薄膜晶体管,从而改善了阵列基板的电性能,进而改善了对显示面板的驱动效果,改善了显示器的发光特性。

#### 附图说明

[0037] 下面结合附图,通过对本申请的具体实施方式详细描述,将使本申请的技术方案及其它有益效果显而易见。

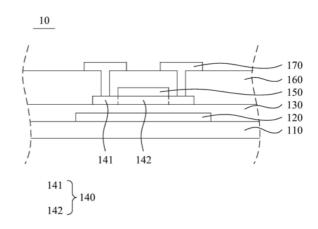

[0038] 图1为本申请实施例提供的阵列基板的第一种结构示意简图。

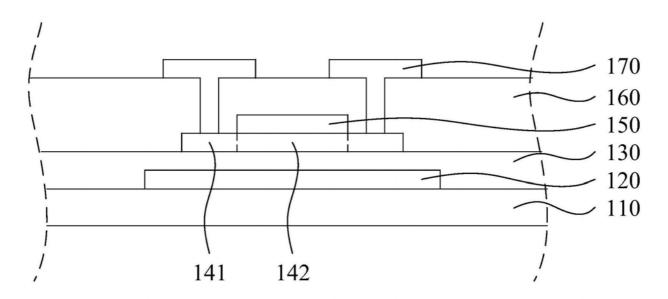

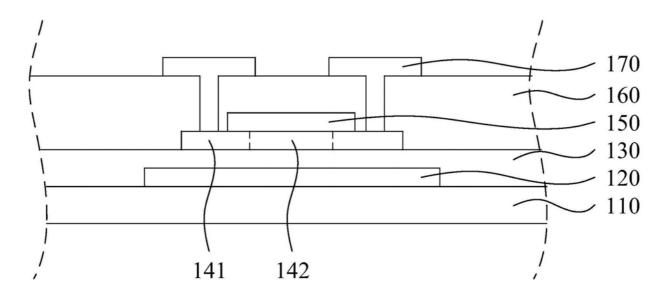

[0039] 图2为本申请实施例提供的阵列基板的第二种结构示意简图。

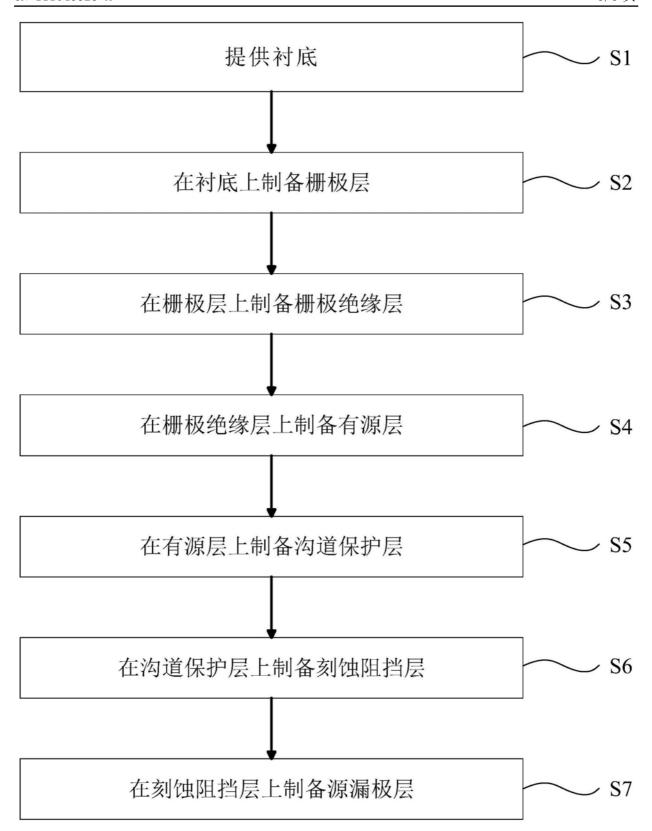

[0040] 图3为本申请实施例提供的阵列基板的制备流程示意简图。

#### 具体实施方式

[0041] 下面将结合本申请的具体实施方案,对本申请实施方案和/或实施例中的技术方案进行清楚、完整的描述,显而易见的,下面所描述的实施方案和/或实施例仅仅是本申请一部分实施方案和/或实施例,而不是全部的实施方案和/或实施例。基于本申请中的实施方案和/或实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方案和/或实施例,都属于本申请保护范围。

[0042] 本申请所提到的方向用语,例如[上]、[下]、[左]、[右]、[前]、[后]、[内]、[外]、[侧]等,仅是参考附加图式的方向。因此,使用的方向用语是用以说明和理解本申请,而非用以限制本申请。术语"第一"、"第二"等仅用于描述目的,而不能理解为指示或是暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有"第一"、"第二"等的特征可以明示或者隐含地包括一个或者更多个该特征。

[0043] 针对现有氧化物阵列基板有源层的背沟道缺陷较多的问题,本申请提供一种阵列基板可以缓解这个问题。

[0044] 在一种实施例中,如图1、图2所示,本申请提供的阵列基板包括:

[0045] 衬底;

[0046] 栅极层,形成于衬底上,图案化形成栅极;

[0047] 栅极绝缘层,形成于栅极层上,覆盖栅极层和衬底;

[0048] 有源层,形成于栅极绝缘层上,图案化形成有源区,有源区包括沟道区和掺杂区;

[0049] 沟道保护层,形成于有源层上,图案化形成位于沟道区上方的沟道保护区;

[0050] 刻蚀阻挡层,形成于沟道保护层上,覆盖沟道保护层、有源层、以及栅极绝缘层;

[0051] 源漏极层,形成于刻蚀阻挡层上,图案化形成源极和漏极,源极或漏极通过过孔与掺杂区相连。

[0052] 本实施例提供一种阵列基板,该阵列基板通过在有源层上设置沟道保护层,所述沟道保护层覆盖有源层内的沟道区,利用沟道保护层良好的物理特性和化学特性,可以大幅度减少沟道区界面的缺陷,同时防止水或氧气进入薄膜晶体管,从而改善了阵列基板的电性能,进而改善了对显示面板的驱动效果,改善了显示器的发光特性。

[0053] 氧化物阵列基板按结构分,可分为刻蚀阻挡型、背沟道刻蚀型、共面型三种。其中,共面型氧化物阵列基板由于需要七张光刻进行制作,且相应的显示器件的稳定性和均匀性也难以控制,因此工艺复杂,其产业化前景不被看好。背沟道刻蚀型氧化物阵列基板在设备改造方面需求量低,但在制备过程中容易被刻蚀液破坏。相比较而言,刻蚀阻挡型是目前应用最广泛的氧化物阵列基板,工艺容易控制,性能也较为稳定。

[0054] 氧化物阵列基板的半导体材料包括铟、锌、镓、镁、锡等金属的氧化物或多种过渡金属氧化物的混合物,目前最具代表性的材料是非晶态的铟镓锌氧 (Amorphous Indium Gallium Zinc Oxide,InGaZnO),即通常所说的IGZO TFT。即通常所说的IGZO TFT可在室温下采用通常的物理沉积方法生长,不受基板尺寸限制,TFT面积大,均匀性好,基板表面平整度佳,同时TFT的载流子迁移速率可达 $10\sim40\,\mathrm{cm}^2/(\mathrm{V}\bullet\mathrm{s})$ ,且开关比较大;此外,IGZO TFT具有透明及非晶态沟道的优点,可以应用于一定程度的柔性和透明显示。

[0055] 但是,氧化物TFT由于其载流子为氧空位,因此,其性能容易受到环境中的水、氧气等因素的影响,TFT特性的稳定性存在一定问题,如何改善氧化物半导体的界面性能,以及其抵抗外界环境中水氧的能力,成为改善氧化物TFT特性的重要环节。

[0056] 在一种实施例中,如图1和图2所示,本申请提供一种氧化物阵列基板,该阵列基板为底栅结构,所述阵列基板10包括:

[0057] 衬底110,衬底110为玻璃衬底或柔性衬底。玻璃衬底由铝硅酸盐和其他成分构成,要求是低碱、平整度高、耐高温和热膨胀系数低等。柔性衬底一般包括第一柔性衬底、第二柔性衬底、以及位于第一柔性衬底和第二柔性衬底之间的无机层;其中第一柔性衬底和第二柔性衬底的材料为聚乙酰胺或聚对苯二甲酸乙二醇酯,用于保证柔性衬底的柔性;无机层的材料为氮化硅或氧化硅,用于阻隔阵列基板外的水或氧气进入薄膜晶体管。

[0058] 栅极层120,形成于衬底110上,图案化形成栅极以及扫描信号线,栅极层120的材料一般为金属钼、金属铝或铝合金。

[0059] 栅极绝缘层130,形成于栅极层120上,覆盖栅极层120和衬底110。栅极绝缘层一般

为氧化硅/氮化硅形成的堆叠结构,氮化硅具有较高的击穿电压,可作为良好的栅极绝缘材料,氧化硅与多晶硅表面具有良好的晶界匹配和应力匹配,同时氧化硅具有良好的台阶覆盖性。

[0060] 有源层140,形成于栅极绝缘层130上,图案化形成有源区,有源区通过掺杂,形成掺杂区141和沟道区142。在本申请实施例中,所述有源层的材料为铟镓锌氧;所述掺杂区,为高浓度磷离子注入掺杂,以形成N型薄膜晶体管的源漏极区,或为高浓度硼离子注入掺杂,以形成P型薄膜晶体管的源漏极区。

[0061] 沟道保护层150,形成于有源层140上,图案化形成位于沟道区142上方的沟道保护区。沟道保护层的材料为铟锌氧化物,沟道保护层的厚度为4~6nm,优选沟道保护层的厚度为5nm。

[0062] 铟锌氧化物是一种很好的氧化物半导体材料,具有较高的电子迁移率和良好的电学性质,可以修补铟镓锌氧背沟道的缺陷,同时还可以防止水和氧气对铟镓锌氧的侵蚀。在铟镓锌氧的背沟道和刻蚀阻挡层之间增设铟镓锌氧保护层,可以大幅度减少铟镓锌氧背沟道的界面缺陷,从而大幅度改善铟镓锌氧化物阵列基板的电性能,提高铟镓锌氧化物薄膜晶体管的驱动效果,进而改善显示面板的发光特性。

[0063] 刻蚀阻挡层160,形成于沟道保护层150上,覆盖沟道保护层150、有源层140、以及栅极绝缘层130。刻蚀阻挡层的材料为氧化硅,或氮化硅,或氧化硅和氮化硅的叠层结构。刻蚀阻挡层160用于保护有源层140的沟道区142免遭刻蚀液的侵蚀。

[0064] 源漏极层170,形成于刻蚀阻挡层160上,图案化形成源极和漏极,源极和漏极分别通过过孔与位于有源区142两侧的掺杂区141相连。源漏极层170的材料为钛/铝/钛的叠层结构,或是钼/铝/钼的叠层结构。

[0065] 在一种实施例中,如图1所示,沟道保护区仅对应于有源层140的沟道区142。沟道保护区刚好对沟道区142进行覆盖,并对其进行保护,避免了沟道保护区对其他膜层结构或是区域结构的影响;同时,只在沟道区142的上方设置沟道保护层,避免了对材料的浪费。

[0066] 在另一种实施例中,如图2所示,沟道保护区对应于有源层140的沟道区142和部分掺杂区141。如此对沟道保护区的制备精度要求相对降低,同时可以确保整个沟道区能够得到保护。

[0067] 同时,如图3所示,本申请还提供一种阵列基板的制备方法,包括:

[0068] S1、提供衬底:

[0069] S2、在衬底上制备栅极层;

[0070] S3、在栅极层上制备栅极绝缘层:

[0071] S4、在栅极绝缘层上制备有源层:

[0072] S5、在有源层上制备沟道保护层;

[0073] S6、在沟道保护层上制备刻蚀阻挡层;

[0074] S7、在刻蚀阻挡层上制备源漏极层。

[0075] 本实施例提供一种阵列基板的制备方法,该制备方法通过在有源层上制备沟道保护层,利用沟道保护层良好的物理特性和化学特性,可以大幅度减少沟道区界面的缺陷,同时防止水或氧气进入薄膜晶体管,从而改善了阵列基板的电性能,进而改善了对显示面板的驱动效果,改善了显示器的发光特性。

[0076] 在一种实施例中,S1提供衬底的具体步骤包括:

[0077] 提供玻璃衬底或柔性衬底,并对所述衬底进行清洁处理。先采用异丙醇、丙酮额混合溶液清洗衬底表面,洗去灰尘和大块颗粒物;然后将衬底放入含有5%左右洗涤剂的去离子水溶液中,加热超声震荡;再分别在去离子水和丙酮中超声震荡,进一步清洁;最后用气体风干衬底,以备进行后续制程。

[0078] 在一种实施例中,S2在衬底上制备栅极层的具体步骤包括:

[0079] 采用磁控溅射的方式,在衬底上溅射一层金属钼的薄膜。现有阵列基板制备工艺中,一般都采用磁控溅射来进行导电薄膜的沉积;氧化铟锡薄膜一般采用强磁场,金属薄膜采用弱磁场;衬底温度一般低于100度,这样溅射的膜层刻蚀速率高,不会有残留;溅射靶材表面到衬底表面的间距一般控制在80~100nm。

[0080] 经过一道光刻工艺,制备出栅极和栅极线。在金属钼的薄膜上沉积一层光刻胶层,采用一套栅极掩膜版,对所述光刻胶层进行曝光,然后用显影液对曝光过后的光刻胶进行显影,得到栅极层图案;然后对裸露在外的栅极层金属钼进行湿法刻蚀,去除没有光刻胶保护的金属钼;再对剩余的光刻胶进行去除,保留下来的金属钼即为图案化的栅极层。

[0081] 在一种实施例中,S3在栅极层上制备栅极绝缘层的具体步骤包括:

[0082] 采用等离子化学气相沉积法,在栅极层和衬底上沉积一层氮化硅,以形成栅极绝缘层,所述栅极绝缘层覆盖栅极层和衬底。栅极绝缘层需要有较高的介电常数,这样栅极氧化层电容(栅极与有源层沟道区之间的电容)更大,更容易产生沟道的反型层。

[0083] 在一种实施例中,S4在栅极绝缘层上制备有源层的具体步骤包括:

[0084] 再次采用磁控溅射的方法,在栅极绝缘层上沉积一层铟镓锌氧化物。在强磁场作用下,沉积铟镓锌氧化物的薄膜,且磁控溅射衬底的温度应低于100度。

[0085] 采用第二次光刻工艺,对铟镓锌氧化物层进行图案化,形成有源区。在铟镓锌氧化物薄膜上沉积一层光刻胶层,采用一套有源层掩膜版,对所述光刻胶层进行曝光,然后用显影液对曝光过后的光刻胶进行显影,得到有源层图案;然后对裸露在外的铟镓锌氧化物进行湿法刻蚀,去除没有光刻胶保护的铟镓锌氧化物;再对剩余的光刻胶进行去除,保留下来的铟镓锌氧化物即为图案化有源层后得到的有源区。

[0086] 对有源区进行部分掺杂,形成掺杂区和沟道区。在有源区上沉积一层光阻层,采用一套掺杂掩膜版,对有源区的预定区域进行离子掺杂;所述离子掺杂可以是高浓度磷离子注入掺杂,以形成N型薄膜晶体管的源漏极区,掺杂所采用的气体为PH3;也可以是高浓度硼离子注入掺杂,以形成P型薄膜晶体管的源漏极区,掺杂所采用的气体为BF3;由于离子植入导致光阻层表面发生碳化,膜质变得致密难剥,通过对光阻层表面轰击和蚀刻将硬化膜灰化,并将光阻层进行剥离;得到包括掺杂区和沟道区的有源区。

[0087] 在一种实施例中,S5在有源层上制备沟道保护层的具体步骤包括:

[0088] 采用物理气相沉积法,在沟道区上沉积一层铟锌氧化物薄膜,作为沟道保护层。所述物理气象沉积可以是磁控溅射,可以是蒸镀,也可以是其他符合要求的制备方法。所制备的铟锌氧化物薄膜,根据掩膜版的不同,可以仅形成于有源层的沟道区的上方,也可以形成于有源层的沟道区的上方和部分掺杂区的上方;所述铟锌氧化物薄膜的沉积厚度约为4~6nm,优选沟道保护层的厚度为5nm。

[0089] 在一种实施例中,S6在沟道保护层上制备刻蚀阻挡层的具体步骤包括:

[0090] 采用等离子体化学气相沉积法,在沟道保护层上沉积一层氧化硅薄膜,作为刻蚀阻挡层,所述刻蚀阻挡层覆盖所述沟道保护层、所述有源层、以及所述栅极绝缘层。

[0091] 在一种实施例中,S7在刻蚀阻挡层上制备源漏极层的具体步骤包括:

[0092] 在制备源漏极层前,需在阵列基板的预定位置制备过孔,用于在沉积源漏极金属的过程中,将有源层、栅极层与源漏极层通过过孔连接。过孔的制备需要对栅极绝缘层进行刻蚀,所采用的刻蚀方法为干法刻蚀,包括反应性离子刻蚀和感应耦合等离子体刻蚀。

[0093] 在完后过孔制备后的基板,采用磁控溅射方式,在刻蚀阻挡层上溅射一层氧化铟锡薄膜。在强磁场作用下,沉积氧化铟锡薄膜,这主要是因为氧化铟锡薄膜的溅射不适于采用高功率的方式溅射,在高功率的情况下,高能量的氩离子轰击氧化铟锡靶材,会引起氧化铟锡靶材表面氧化铟化,而氧化铟导电性不好,影响自持放电;且磁控溅射衬底的温度应低于100度,此时形成的氧化铟锡薄膜为非晶态,刻蚀速率高,不会有残留。

[0094] 采用第三次光刻工艺,对氧化铟锡薄膜进行图案化处理,形成源极、漏极、数据信号线、以及电源信号线。

[0095] 根据上述实施例可知:

[0096] 本申请实施例提供一种阵列基板及其制备方法,该阵列基板包括在衬底上依次层叠设置栅极层、栅极绝缘层、有源层、沟道保护层、刻蚀阻挡层、以及源漏极层,其中,有源层包括沟道区和掺杂区,沟道保护层设置于沟道区上;通过在有源层的沟道区上方设置沟道保护层,利用沟道保护层良好的物理特性和化学特性,可以大幅度减少沟道区界面的缺陷,同时防止水或氧气进入薄膜晶体管,从而改善了阵列基板的电性能,进而改善了对显示面板的驱动效果,改善了显示器件的发光特性。

[0097] 综上所述,虽然本申请已以优选实施例揭露如上,但上述优选实施例并非用以限制本申请,本领域的普通技术人员,在不脱离本申请的精神和范围内,均可作各种更动与润饰,因此本申请的保护范围以权利要求界定的范围为准。

10

$$141 \ 142$$

$140$

图1

10

$${141 \atop 142}$$

} 140

图2

图3