# (10) **DE 101 04 265 B4** 2008.09.25

(12)

# **Patentschrift**

(21) Aktenzeichen: 101 04 265.5 (22) Anmeldetag: 31.01.2001 (43) Offenlegungstag: 22.08.2002 (45) Veröffentlichungstag

der Patenterteilung: 25.09.2008

(51) Int Cl.8: **H01L 27/22** (2006.01)

H01L 21/768 (2006.01) H01L 21/8239 (2006.01) **G11C 11/15** (2006.01) **G11C 11/16** (2006.01)

Innerhalb von drei Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(73) Patentinhaber:

Qimonda AG, 81739 München, DE

(74) Vertreter:

Müller - Hoffmann & Partner Patentanwälte, 81667 München

(72) Erfinder:

Schlösser, Till, 81825 München, DE

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

DE 101 13 853 A1

US 58 38 608 A

US 58 38 604 A

US 58 04 458 A

US 54 96 759 A

EΡ 09 18 334 A2

Y.Z. Hu [u.a.]: Chemical-mechanical polishing as an enabling technology for giant magnetoresistance

devices in Thin Solid Films, 308-309(1997), pp.555-561;

#### (54) Bezeichnung: Verfahren zum Herstellen einer Halbleiterschaltungsanordnung

(57) Hauptanspruch: Verfahren zum Herstellen einer Speichereinrichtung mit einer Mehrzahl von MRAM-Zellen, bei welcher mindestens ein Schaltungselement (30) in einem Kreuzungsbereich (40) mindestens zweier Leitungselemente (10, 20) und zwischen diesen angeordnet wird, mit den Schritten:

- Ausbilden mindestens eines Substratbereichs (50),

- Ausbilden mindestens eines ersten und eines zweiten Leitungselements (10, 20) auf Oberflächenbereichen (50a) des Substratbereichs (50) und mit mindestens einem Kreuzungsbereich (40),

- Ausbilden mindestens eines Schaltungselements (30) zwischen einer vom Substratbereich (50) abgewandten Seite (10a) des ersten Leitungselements (10) und einer dem Substratbereich (50) zugewandten Seite (20b) des zweiten Leitungselements (20) und im Kreuzungsbereich (40) der Leitungselemente (10, 20),

- wobei zumindest das Strukturieren des Schaltungselements (30) in einem gemeinsamen Herstellungsschritt mit dem Strukturieren des ersten Leitungselements (10) durchgeführt wird, und zwar zunächst in einem ersten Atzschritt für das erste Leitungselement (10) und jeweils einem ersten Teil des jeweiligen Schaltungselementes (30),

- wobei...

#### **Beschreibung**

**[0001]** Die Erfindung betrifft ein Verfahren zum Herstellen einer Halbleiterschaltungsanordnung.

[0002] Bei vielen Halbleiterschaltungsanordnungen sind an Kreuzungsbereichen zweier Leitungselemente, z. B. von metallischen Leitungsbahnen oder dergleichen, Schaltungselemente vorgesehen, z. B. auch zwischen den Leitungselementen. Dies trifft z. B. für eine Vielzahl von Speichereinrichtungen oder dergleichen zu, insbesondere für Speicherzellen auf der Basis von sogenannten MRAM-Zellen. Bei sogenannten Crosspoint-MRAM-Zellen sind zwischen jeweils zwei gekreuzten Metallbahnen die Speicherelemente in Form von sogenannten TMR-Schichtstapeln mit sehr kleiner Dimensionierung vorgesehen.

[0003] Bei der Herstellung von Halbleiterschaltungsanordnungen werden diese häufig schichtartig sukzessive aufgebaut. Dabei besteht die Schwierigkeit, dass insbesondere beim Anordnen von Schaltungselementen in Kreuzungsbereichen von Leitungselementen aufgrund der häufig sehr kleinen Dimensionierung eine hohe geometrische Genauigkeit und Reproduzierbarkeit nur mit verhältnismäßig hohem Aufwand erreicht werden kann. Diese geometrische Genauigkeit und Reproduzierbarkeit ist aber notwendig, um z. B. bei MRAM-Zellen auch eine entsprechende Reproduzierbarkeit der magnetischen Eigenschaften der Speicherzellen zu gewährleisten.

[0004] Bei bekannten Verfahren werden die Schaltungselemente, insbesondere also die TMR-Stapelschichten, mittels eigener Lithographieschritte und -ebenen prozessiert. Das bedeutet, dass nach dem Aufbringen einer ersten Klasse von Leitungselementen oder Leiterbahnen – ebenfalls im Rahmen einer eigenen Lithographiesbene mit einem eigenen Lithographieschritt – nachfolgend dann in einem separaten Prozessabschnitt die Schaltungselemente, z. B. die MRAM-Zellen, ausgebildet werden. Abschließend werden dann die Leitungselemente oder Leiterbahnen der zweiten Klasse ebenfalls in einem eigenen Lithographieschritt strukturiert.

**[0005]** Aus der EP 0 918 334 A2 ist eine magnetische Speichereinrichtung bekannt, bei welcher eine Anordnung magnetischer Speicherzellen im Zusammenhang mit einer entsprechenden Anordnung von Leitern vorgesehen ist. Beim Prozessieren der Leiter und der magnetischen Schichten soll der Aufwand beim Anordnen der entsprechenden Strukturierungsmasken reduziert werden. Beim Strukturieren liegen bestimmte Anteile der magnetischen Stapel vorstrukturiert vor, wogegen bestimmte Leitungselemente noch keinem Strukturierungsprozess unterzogen wurden.

[0006] Die US 5,838,604 A betrifft eine

MRAM-Struktur sowie entsprechende Herstellungsverfahren, wobei insbesondere mit magnetischen Speicherelementen verbundene Dioden ausgebildet werden, um im Betrieb einen Stromfluss nur bei aktivierten MRAM-Zellen im Sinne einer Spaltenauswahl und Zeilenauswahl zu gewährleisten.

[0007] Die US 5,804,458 A betrifft ein Verfahren zum Herstellen magnetischer Speicherzellen, wobei unter Verwendung eines Maskenmaterials eine Abfolge von Speicherstapeln ausgebildet wird. Eine vorgesehene Spacerstruktur ist bei dem hier dargestellten Herstellungsverfahren Bestandteil der Maskenelemente selbst.

[0008] Die Veröffentlichung "Chemical-Mechanical Polishing As An Enabling Technology for Giant Magnetoresistance Devices", Thin Solid Films 308-309 (1997), Seiten 555-561, betrifft die Anwendung des CMP-Verfahrens im Bereich der Herstellung so genannter GMR-Stapel, die auch für magnetische Speicherelemente relevant sind. Es wird dargestellt, dass zunächst GMR-Stapel ausgebildet und dann strukturiert werden. Erst nach der Abfolge verschiedener Strukturierungsmaßnahmen erfolgt dann das Strukturieren einer vorgesehenen ersten Metallisierungsschicht.

**[0009]** Der Erfindung liegt die Aufgabe zugrunde, ein Verfahren zum Herstellen einer Halbleiterschaltungsanordnung bereitzustellen, bei welchem auf besonders einfache und gleichwohl verlässliche Art und Weise Schaltungselemente mit hoher geometrischer Genauigkeit strukturiert werden können.

**[0010]** Die Aufgabe wird bei einem Verfahren zum Herstellen einer Halbleiterschaltungsanordnung erfindungsgemäß durch die Merkmale des Anspruchs 1 gelöst. Vorteilhafte Weiterbildungen des erfindungsgemäßen Verfahren sind Gegenstand der abhängigen Ansprüche.

[0011] Die Erfindung schafft ein Verfahren zum Herstellen einer Speichereinrichtung mit einer Mehrzahl von MRAM-Zellen, bei welcher mindestens ein Schaltungselement in einem Kreuzungsbereich mindestens zweier Leitungselemente und zwischen diesen angeordnet wird, mit den Schritten: Ausbilden mindestens eines Substratbereichs, Ausbilden mindestens eines ersten und eines zweiten Leitungselements auf Oberflächenbereichen des Substratbereichs und mit mindestens einem Kreuzungsbereich, Ausbilden mindestens eines Schaltungselements zwischen einer vom Substratbereich abgewandten Seite des ersten Leitungselements und einer dem Substratbereich zugewandten Seite des zweiten Leitungselements und im Kreuzungsbereich der Leitungselemente, wobei zumindest das Strukturieren des Schaltungselements in einem gemeinsamen Herstellungsschritt mit dem Strukturieren des ersten

### DE 101 04 265 B4 2008.09.25

Leitungselements durchgeführt wird, und zwar zunächst in einem ersten Atzschritt für das erste Leitungselement und jeweils einem ersten Teil des jeweiligen Schaltungselementes, wobei der erste Atzschritt in Teilschritten durchgeführt wird, wobei dabei in einem ersten Teilätzschritt zunächst der erste Teil des Schaltungselements bis zur Oberfläche einer ersten Metallschicht für das erste Leitungselement strukturiert wird, wobei dann entstandene Kantenbereiche des ersten Teils des Schaltungselements passiviert werden durch Oxidabscheidung mittels einer Spacertechnik und wobei dann in einem zweiten Teilätzschritt jeweils das erste Leitungselement bis zur Oberseite eines Substratbereichs strukturiert wird mit gemeinsam bündig sich vertikal erstreckender Flanke des ersten Leitungselements und der Passivierung.

[0012] Bei dem vorgeschlagenen Verfahren zum Herstellen einer Halbleiterschaltungsanordnung, insbesondere einer Speichereinrichtung oder dergleichen, mit einer Mehrzahl von Speicherzellen, insbesondere MRAM-Zellen oder dergleichen, bei welcher mindestens ein Schaltungselement jeweils im Wesentlichen in einem Kreuzungsbereich zweier Leitungselemente und zwischen diesen angeordnet ist, wird also zunächst ein Substratbereich ausgebildet. Dann wird mindestens ein erstes und ein zweites Leitungselement auf einem Oberflächenbereich des Substratbereichs und mit mindestens einem Kreuzungsbereich ausgebildet, wobei mindestens ein Schaltungselement im Wesentlichen zwischen einer vom Substratbereich abgewandten Seite des ersten Leitungselements und einer dem Substratbereich zugewandten Seite des zweiten Leitungselements im Wesentlichen im Kreuzungsbereich der Leitungselemente ausgebildet wird.

[0013] Bei dem erfindungsgemäßen Verfahren zum Herstellen einer Halbleiterschaltungsanordnung ist es also vorgesehen, dass zumindest das Ausbilden, insbesondere das Strukturieren, des jeweiligen Schaltungselements jeweils zumindest teilweise im Wesentlichen gleichzeitig und/oder gemeinsam mit dem Ausbilden, insbesondere Strukturieren, des ersten und/oder zweiten Leitungselements durchgeführt wird.

[0014] Es ist somit eine Idee der vorliegenden Erfindung, die Schaltungselemente der Halbleiterschaltungsanordnung, welche jeweils in Kreuzungsbereichen der Leitungselemente auszubilden sind, nicht im Rahmen eines getrennten Herstellungsabschnitts auszubilden, sondern jeweils gleichzeitig und/oder gemeinsam mit den Leitungselementen selbst. Das bedeutet, dass die für das Ausbilden der Leitungselemente notwendigen Prozessschritte zumindest teilweise auch für das Ausbilden der Schaltungselemente selbst nutzbar gemacht werden. Dadurch entfallen herkömmliche und separat vorzusehende Herstel-

lungsschritte und auch die entsprechenen Einrichtungen. Folglich vereinfacht sich das Herstellungsverfahren für die Halbleiterschaltungsanordnung deutlich, was zu einer Zeit- und Kosteneinsparung bei der Herstellung führt. Darüber hinaus werden bestimmte Justierschwierigkeiten und geometrische Ungenauigkeiten beim Ausbilden der entsprechenden Positionen der Schaltungselemente im Kreuzungsbereich der Leitungselemente vermieden, weil die Schaltungselemente sozusagen in einem Zug mit den Leitungselementen in einem selbstjustierenden Prozess strukturiert werden.

[0015] Besonders bevorzugt ist das erfindungsgemäße Verfahren zum Herstellen einer Halbleiterschaltungsanordnung im Bereich der Halbleiterspeichereinrichtungen, insbesondere auf der Grundlage von MRAM-Zellen. Demgemäß ist es vorgesehen, dass als Schaltungselemente jeweils Speicherelemente ausgebildet werden, insbesondere als TMR-Stapel einer MRAM-Zelle oder dergleichen.

**[0016]** Beim Ausbilden des Substratbereichs wird vorzugsweise ein Halbleiterbereich mit einem Isolationsbereich und einer entsprechenen CMOS-Struktur ausgebildet. Auf diesem so ausgebildeten Substratbereich wird dann entsprechend die Anordnung mit der Mehrzahl erster und zweiter Leitungselemente und der entsprechenden Schaltungselemente vorgesehen.

[0017] Gemäß einer besonders bevorzugten Ausführungsform des erfindungsgemäßen Verfahrens ist es vorgesehen, dass zum Ausbilden der ersten Leitungselemente zunächst eine erste Materialschicht oder Metallschicht im Wesentlichen auf der Oberseite des Substratbereichs aufgebracht wird, insesondere in großganzflächiger oder zweidimensionaler Form und/oder insbesondere unter Verwendung von Aluminium oder dergleichen. Zusätzlich kann auf der Oberseite des Substratbereichs auch noch eine Haftschicht und/oder Diffusionsbarriere, z. B. durch Abscheiden von Titannitrid (TiN), vorgesehen sein.

[0018] Da es zur Gewährleistung der Reproduzierbarkeit und Vergleichbarkeit der elektromagnetischen Eigenschaften der Schaltungselemente maßgeblich auf die Geometrie ankommt, ist es vorgesehen, dass gemäß einer weiteren Ausführungsform des erfindungsgemäßen Verfahrens die erste Materialschicht oder Metallschicht für die ersten Leitungselemente planarisiert wird, insbesondere durch Polieren, ein CMP-Verfahren oder dergleichen.

**[0019]** Es wird ferner bevorzugt, dass auf die erste Materialschicht oder Metallschicht für die ersten Leitungselemente eine Materialschicht für die Schaltungselemente abgeschieden wird. Dies geschieht vorzugsweise in groß- oder ganzflächiger oder zweidimensionaler Art und Weise und/oder insbesondere

in Form sogenannter TMR-Stapel oder dergleichen.

[0020] Zur Ausbildung der ersten Leitungselemente auf dem Oberflächenbereich des Substratbereichs ist es vorgesehen, dass auf der Materialschicht für die Schaltungselemente zunächst eine erste Maske, insbesondere eine Hartmaske, vorzugsweise aus Siliziumnitrid (SiN), ausgebildet wird. Diese Maske kann z. B. eine für Leitungselemente oder Leitungsbahnen übliche Streifenmaske sein. Dann ist es vorgesehen, dass nachfolgend in einem ersten Ätzschritt die ersten Leitungselemente und im Wesentlichen gleichzeitig damit zumindest ein erster Teil der Schaltungselemente strukturiert werden. Dies geschieht vorzugsweise entlang der Ausdehnung der ersten Maske, also insbesondere entlang der Streifenrichtung. Des Weiteren ist es gegebenenfalls vorgesehen, dass dann nachfolgend mit einem Zwischenisolationsbereich aufgefüllt wird, insbesondere mit einem Oxid, um die so erhaltene Struktur mechanisch zu stabilisieren und eine für den Betrieb notwendige elektrische Isolation in lateraler Richtung zu erreichen. Das Auffüllen erfolgt insbesondere mit Abschluss zur Oberseite der ersten Maske.

[0021] Bei vielen Schaltungselementen von Halbleiterschaltungseinrichtungen ist es notwendig bestimmte Flächenbereiche oder Kantenbereiche, die sich im Wesentlichen vertikal erstrecken, zu schützen, mechanisch zu stabilisieren und zu passivieren. Gemäß einer weiteren bevorzugten Ausführungsform des erfindungsgemäßen Verfahrens zum Herstellen einer Halbleiterschaltungsanordnung ist es vorgesehen, dass der erste Ätzschritt in Teilschritten durchgeführt wird. Dabei ist es vorgesehen, dass zunächst in einem ersten Teilätzschritt der erste Teil des Schaltungselements bis zur Oberfläche der ersten Materialschicht oder Metallschicht für das erste Leitungselement strukturiert wird. Nachfolgend werden dann entstandene Kantenbereiche des strukturierten ersten Teils des Schaltungselements passiviert. Dies geschieht vorzugsweise durch Oxidabscheidung, z. B. mittels einer Spacertechnik. Dann wird nachfolgend in einem zweiten Teilätzschritt jeweils das erste Leitungselement bis zur Oberfläche oder Oberseite des Substratbereichs strukturiert. Dabei wird bevorzugt, dass eine im Wesentlichen bündig und sich vertikal erstreckende gemeinsame Flanke des ersten Leitungselements und der Passivierung des Teils des Schaltungselements entsteht.

[0022] Insgesamt bedeutet dies zum Beispiel, dass beim ersten Teilätzschritt bis zur Oberfläche der ersten Materialschicht für das erste Leitungselement ein relativ schmaler Steg oder ein relativ schmales Linienelement freigeätzt wird, insbesondere in Form eines TMR-Stapels. Nachfolgend werden dann die Kanten dieses Stapels entsprechend durch eine Spacerabscheidung passiviert und somit mechanisch stabilisiert und geschützt. Der so abgeschiede-

ne Spacer hat dabei eine nur geringe laterale Ausdehnung und deckt nur die Seitenbereiche oder Kantenbereiche des strukturierten Teils des Schaltungselements ab. Danach wird ein breiteres Linienelement, welches das erste geätzte Linienelement abdeckt, bis zur Oberfläche des Substratbereichs herunter in die erste Materialschicht für das erste Leitungselement hineingeätzt. Somit entsteht auf der Oberseite des Substratbereichs eine linienartige Anordnung von Stapeln, wobei jeder Stapel gebildet wird von einer Materialschicht für das erste Leitungselement, einer darauf folgenden Materialschicht, welche schmaler ist, für den strukturierten ersten Teil der Schaltungselemente und einer darauf angeordneten ebenso schmalen Maskenschicht. Die Seitenbereiche oder Kantenbereiche der Materialschicht für das Schaltungselement und der Maskenschicht sind durch den Spacer passiviert, wobei die Spacer lateral bündig mit der Materialschicht für die ersten Leitungselemente abschließen.

[0023] Vorteilhafterweise wird für das weitere Prozessieren nachfolgend die erste Maske, welche auf der Materialschicht für das Schaltungselement aufliegt, abgetragen. Dadurch wird eine notwendige Kontaktierung des Schaltungselements oder eines Teils davon zwischen dem ersten und dem zweiten Leitungselement erst möglich, denn die Hartmaske wirkt in der Regel im Wesentlichen elektrisch isolierend.

[0024] Das Ausbilden der zweiten Leitungselemente geschieht vorteilhafterweise nach dem Ausbilden der ersten Leitungselemente und des entsprechenden Teils der Schaltungselemente. Zum Ausbilden der zweiten Leitungselemente wird zunächst eine zweite Materialschicht oder Metallschicht abgeschieden. Dies geschieht insbesondere in groß- oder ganzflächiger oder zweidimensionaler und/oder insbesondere unter Verwendung von Aluminium oder dergleichen. Gemäß der vorangehenden Strukturierung für die ersten Leitungselemente und für den ersten Teil der Schaltungselemente kann die Abscheidung der zweiten Materialschicht für die zweiten Leitungselemente z. B. auf der gemeinsamen einbettenden Zwischenisolationsschicht erfolgen.

**[0025]** Erfindungsgemäß wird gegebenenfalls die zweite Materialschicht oder Metallschicht für die zweiten Leitungselemente planarisiert, insbesondere durch Polieren, ein CMP-Verfahren oder dergleichen.

[0026] Vorteilhafterweise wird zum Ausbilden der zweiten Leitungselemente und/oder eines weiteren Teils der Schaltungselemente nachfolgend zunächst eine zweite Maske, insbesondere eine Hartmaske, vorzugsweise aus Siliziumnitrid (SiN) oder dergleichen, ausgebildet. Dies kann ebenfalls wiederum eine Streifenmaske sein, wobei dann vorzugsweise

## DE 101 04 265 B4 2008.09.25

die Richtung der Streifen sich von der Richtung der Streifen der ersten Maske unterscheidet, die insbesondere im Wesentlichen senkrecht auf dieser steht. Weiterhin werden dann nachfolgend in einem zweiten Atzschritt die zweiten Leitungselemente und im Wesentlichen gleichzeitig damit zweite Teile der Schaltungselemente strukturiert. Dies geschieht vorzugsweise entlang der Ausdehnung der zweiten Maske, insbesondere entlang der Streifenrichtung der zweiten Maske. Des Weiteren kann gegebenenfalls ein Zwischenisolierungsbereich zur Auffüllung aufgebracht werden, insbesondere in Form einer Zwischenoxidschicht und/oder insbesondere mit Abschluss auf der Oberseite der zweiten Maske oder der Oberseite der Materialschicht der zweiten Leitungselemente.

[0027] Wie bei dem ersten Atzschritt, so kann aus Gründen einer schonenden Präparation, insbesondere der Flankenbereiche oder Seitenbereiche der Schaltungselemente, auch der zweite Atzschritt in Teilschritten durchgeführt werden. Dabei wird in bevorzugter Art und Weise in einem ersten Teilätzschritt bis zur Oberfläche der Materialschicht für die Schaltungselemente oder bis zur Oberfläche der ersten Maske die zweite Materialschicht oder zweite Metallschicht für die zweiten Leitungselemente geätzt. In einem zweiten Teilätzschritt wird dann die Materialschicht für die Schaltungselemente, insbesondere also die TMR-Stapel, gegebenenfalls mit etwas größerer Breite bis zur Oberfläche der ersten Leitungselemente geätzt, wobei dann gegebenenfalls wieder mittels einer Spacertechnik die Randbereiche oder Kantenbereiche der so strukturierten Teile der Schaltungselemente passiviert und geschützt werden.

[0028] Danach wird gegebenenfalls vorteilhafterweise wieder mit einem Zwischenisolationsbereich aufgefüllt, insbesondere mit einem Zwischenoxid oder dergleichen und/oder insbesondere mit Abschluss auf dem Niveau der Oberseite der zweiten Maske oder der Oberseite der zweiten Leitungselemente.

**[0029]** Vorteilhafterweise wird beim Strukturieren der ersten und zweiten Leitungselemente jeweils eine Streifenmaske verwendet, wobei vorteilhafterweise die Streifenrichtungen verschieden sind, die insbesondere im Wesentlichen senkrecht aufeinanderstehen.

**[0030]** Weitere Aspekte der vorliegenden Erfindung ergeben sich aus den nachfolgend ausgeführten Bemerkungen:

Der bei Crosspoint-MRAM-Zellen zwischen jeweils zwei gekreuzten Metallbahnen oder Leitungsbahnen angeordnete TMR-Schichtstapel muss in sehr kleiner Dimensionierung und gleichwohl mit hoher geometrischer Genauigkeit ausgebildet und strukturiert werden. Dies ist im Hinblick auf die Reproduzierbarkeit

der magnetischen Eigenschaften wichtig.

[0031] Bei herkömmlichen Herstellungsvorgängen wird die TMR-Schicht jeweils im Rahmen eines eigenen Lithographieschritts mit einer eigenen Lithographieebene belichtet und strukturiert. Einerseits ist die Lithographie kleiner Einzelstrukturen sehr schwierig und innerhalb des Gesamtprozesses aufwendig. Ferner ergeben sich nicht zu vermeidende Ungenauigkeiten bei der Justage. Andererseits hängt die relative Lage der TMR-Stapel zu den Metallbahnen oder Leitungsbahnen stark von den Justiertoleranzen ab. Diese betragen typischerweise etwa ein Drittel der maximalen Auflösung.

[0032] Bei dem erfindungsgemäßen Vorgehen beruht der Herstellungsprozess auf einem Metallisierungsschema, bei welchem die Metallbahnen geätzt werden. Dies geschieht typischerweise wie bei einer Aluminiummetallisierung. Dabei wird der TMR-Stapel in vollständiger Art und Weise und selbstjustiert zu den Metallbahnen ausgeführt, wie das oben beschrieben wurde, und zwar indem das Strukturieren der TMR-Stapel zumindest teilweise gleichzeitig und/oder gemeinsam mit dem Strukturieren der Metallbahnen ausgeführt wird.

[0033] Somit entfallen erfindungsgemäß in vorteilhafter Art und Weise die üblicherweise sich einstellenden Justierungenauigkeiten zwischen den Metallbahnen und dem TMR-Element. Es können des Weiteren rechteckige Zellen mit gut kontrollierbarer Geometrie ausgebildet werden. Das Entfallen einer weiteren Lithographieebene und einer entsprechenden sehr kritischen Maske führt zu einer Kostenreduktion. Als einfache Lithographieebenen oder Lithographieschritte verbleiben derartige Schritte mit Streifenmasken, wodurch der Herstellungsprozess weiter vereinfacht wird.

**[0034]** Nachfolgend wird die Erfindung anhand einer schematischen Zeichnung auf der Grundlage bevorzugter Ausführungsformen der vorliegenden Erfindung näher erläutert.

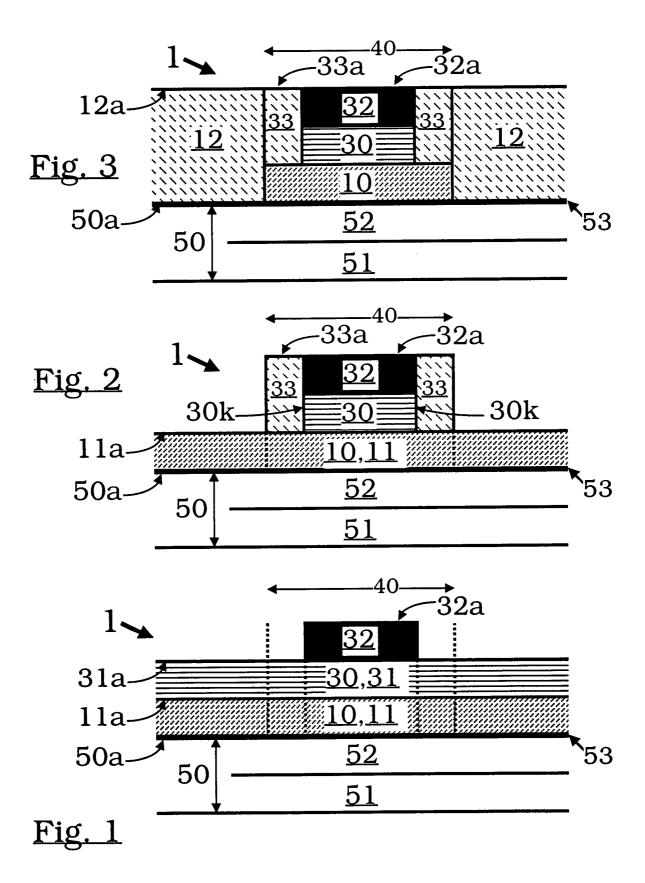

**[0035]** Fig. 1–Fig. 3 sind geschnittene Seitenansichten verschiedener Zwischenzustände für eine Halbleiterschaltungsanordnung im Rahmen einer Ausführungsform des erfindungsgemäßen Verfahrens, und zwar in einer ersten Blickrichtung.

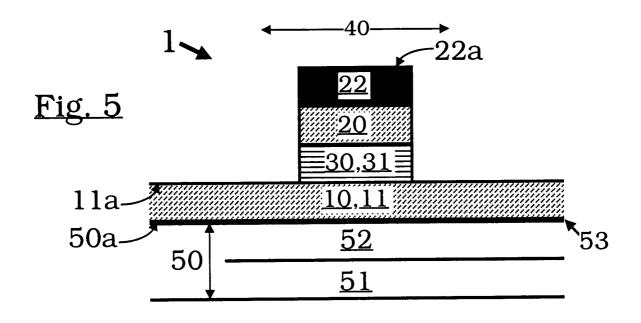

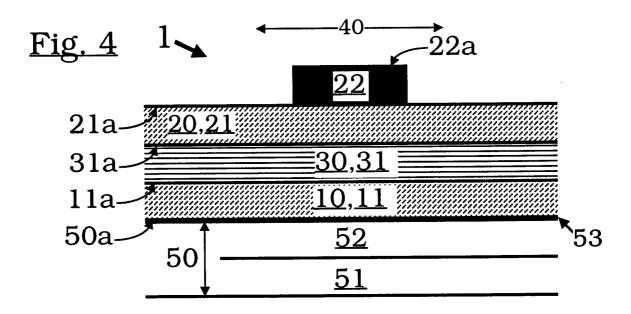

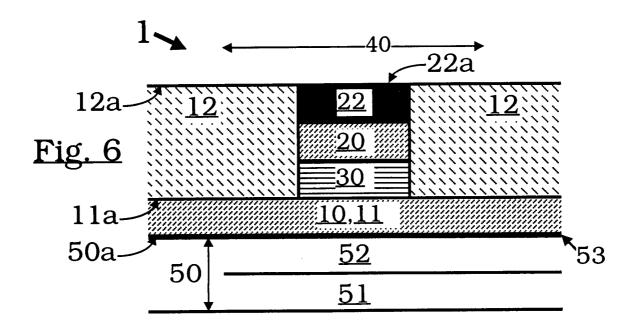

**[0036]** Fig. 4–Fig. 6 sind seitliche Querschnittsansichten weiterer Zwischenstufen einer Halbleiterschaltungsanordnung im Rahmen der Ausführungsform des erfindungsgemäßen Verfahrens, und zwar entlang einer anderen Blickrichtung.

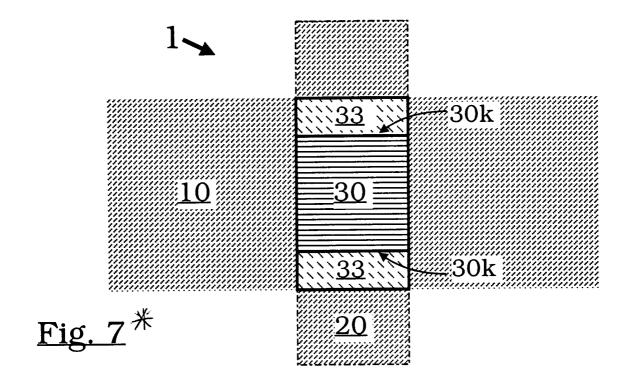

[0037] Fig. 7 ist eine teilweise geschnittene Draufsicht auf die Halbleiterschaltungsanordnung der Fig. 1–Fig. 6 nach deren Fertigstellung im Rahmen

der Ausführungsform des erfindungsgemäßen Verfahrens.

[0038] Die Fig. 1–Fig. 6 zeigen verschiedene Stadien bei der Herstellung einer Halbleiterschaltungsanordnung 1 im Rahmen einer Ausführungsform des erfindungsgemäßen Verfahrens, und zwar für die Fig. 1–Fig. 3 aus einer Blickrichtung entlang eines ersten auszubildenden Leitungselements 10 und für die Fig. 4–Fig. 6 entlang eines zweiten auszubildenden Leitungselements 20.

[0039] Die Fig. 1 zeigt in seitlicher Querschnittsansicht eine erste Zwischenstufe bei der Herstellung einer Halbleiterschaltungsanordnung 1 gemäß der Ausführungsform des erfindungsgemäßen Verfahrens. Der ausgebildete Substratbereich 50 mit seiner Oberfläche oder Oberseite 50a ist schichtweise aufgebaut, und zwar mit dem eigentlichen Halbleitersubstrat 51, einem darauf vorgesehenen Isolationsbereich 52 und einer darauf angeordneten Haftschicht und Diffusionsbarriere 53, z. B. aus Titannitrid (TiN). Auf der Oberfläche oder Oberseite 50a des Substratbereichs 50 wurde dann in zweidimensionaler Form zunächst eine erste Materialschicht 11 oder Metallisierungsschicht 11 für erste auszubildende Leitungselemente 10 und darauf folgend auf deren Oberseite 11a eine Materialschicht 31 für die auszubildenden Schaltungselemente 30 ausgebildet. In vorzusehenden Kreuzungsbereichen 40 für die insgesamt auszubildenden ersten und zweiten Leitungselemente 10 und 20 wurde dann nachfolgend eine erste Maske 32 mit Oberseite 32a abgeschieden, z. B. in Form einer Siliziumnitridhartmaske oder dergleichen.

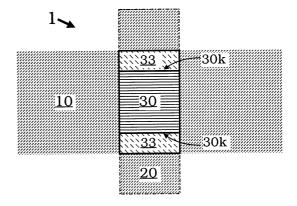

[0040] Im Übergang zu dem in Fig. 2 gezeigten Zwischenzustand ist bei der Halbleiterschaltungsanordnung 1 ein erster Teilätzschritt bis zur Oberfläche oder Oberseite 11a der ersten Materialschicht 11 durchgeführt worden, um gemäß der abgeschiedenen ersten Maske 32 einen ersten Teil für das Schaltungselement 30 auszubilden. Nachfolgend wurden dann noch an den Kantenbereichen 30k mittels einer Spacertechnik entsprechende Passivierungen 33 abgeschieden, um insbesondere die Seiten- oder Kantenbereiche 30k der Schaltungselemente 30 zu schützen.

[0041] Im Übergang zu dem in Fig. 3 gezeigten Zwischenzustand wurde in einem zweiten Teilätzschritt die erste Materialschicht oder Metallschicht 11 für die ersten Leitungselemente 10 bis auf die Oberseite 50a des Substratbereichs 50 heruntergeätzt, und zwar bündig mit der lateralen Ausdehnung der Passivierungen 33 des Schaltungselements 30 im auszubildenden Kreuzungsbereich 40. Fig. 3 zeigt den Zwischenzustand nach Auffüllen mit einer entsprechenden Zwischenisolationsschicht 12 oder Zwischenoxidschicht 12 bis zur Oberfläche 32a der ersten Maske 32.

[0042] Die Fig. 4-Fig. 6 zeigen weitere nachfolgende Zwischenstufen bei der Herstellung der Halbleiterschaltungsanordnung 1 gemäß der hier beschriebenen Ausführungsform des erfindungsgemäßen Verfahrens, und zwar ebenfalls wieder in Form seitlicher Querschnittsansichten, diesmal aber in Blickrichtung der auszubildenden zweiten Leitungseinrichtung 20.

[0043] Ausgehend von dem in Fig. 3 gezeigten Zwischenzustand wurde im Übergang zu dem in Fig. 4 gezeigten Zwischenzustand zunächst die erste Maske 32 vollständig entfernt und dann eine zweite Materialschicht 21 oder zweite Metallisierungsschicht 21 mit Oberseite 21a für die auszubildenden zweiten Leitungselemente 20 abgeschieden und entsprechend planarisiert. Nachfolgend wurde dann auf die Oberseite 21a der zweiten Materialschicht 21 oder Metallisierungsschicht 21 eine zweite Maske 22 abgeschieden, so dass sich insbesondere in den auszubildenden Kreuzungsbereichen 40 ein entsprechender Überlapp ergibt.

[0044] Anschließend wurde dann ein weiterer Teilätzschritt durchgeführt, bei welchem bis auf die Oberfläche 11a der ersten Materialschicht 11 oder Metallschicht 11 herunter die nicht durch die zweite Maske abgedeckten Bereiche der zweiten Metallisierungsschicht 21 und der Materialschicht 11 für die Schaltungselemente 10 entfernt wurden. Dieser Zustand ist in Fig. 5 dargestellt.

**[0045]** Im Übergang zur Fig. 6 wurde dann nachfolgend eine Einbettung 12 in einen Zwischenisolationsbereich 12, welcher mit der Oberseite 22a der zweiten Maske 22 abgeschlossen wird, ausgebildet.

[0046] Fig. 7 zeigt in einer schematischen und teilweise geschnittenen Draufsicht den Endzustand bei der erfindungsgemäßen Herstellung einer Halbleiterschaltungsanordnung 1 im Kreuzungsbereich 40 zweier Leitungselemente 10 und 20. In diesem Kreuzungsbereich 40 ist ein Schaltungselement 30 in Form eines TMR-Stapels einer MRAM-Zelle ausgebildet, wobei zum Schutz der Kantenbereiche 30k des Schaltungselements 30 Passivierungselemente 33 vorgesehen sind.

## Bezugszeichenliste

| Halbleiterschaltungsanordnung        |

|--------------------------------------|

| Erstes Leitungselement               |

| Oberseite                            |

| Erste Materialschicht, Metallschicht |

| Oberseite                            |

| Zwischenisolationsschicht, -bereich  |

| Oberseite                            |

| Zweites Leitungselement              |

| Oberseite                            |

| Zweite Maske                         |

| Oberseite                            |

|                                      |

### DE 101 04 265 B4 2008.09.25

- 30 Schaltungselement

- 30a Oberseite

- 30k Kantenbereich

- 31 Materialschicht

- 31a Oberseite

- 32 Erste Maske

- 32a Oberseite

- 33 Passivierungselement

- 40 Kreuzungsbereich

- 50 Substratbereich

- 50a Oberseite

- 51 Halbleitersubstrat

- 52 Isolationsbereich

- 53 Haftschicht, Diffusionsbarriere

#### Patentansprüche

1. Verfahren zum Herstellen einer Speichereinrichtung mit einer Mehrzahl von MRAM-Zellen, bei welcher mindestens ein Schaltungselement (30) in einem Kreuzungsbereich (40) mindestens zweier Leitungselemente (10, 20) und zwischen diesen angeordnet wird.

mit den Schritten:

- Ausbilden mindestens eines Substratbereichs (50).

- Ausbilden mindestens eines ersten und eines zweiten Leitungselements (10, 20) auf Oberflächenbereichen (50a) des Substratbereichs (50) und mit mindestens einem Kreuzungsbereich (40),

- Ausbilden mindestens eines Schaltungselements

(30) zwischen einer vom Substratbereich (50) abgewandten Seite (10a) des ersten Leitungselements

(10) und einer dem Substratbereich (50) zugewandten Seite (20b) des zweiten Leitungselements (20) und im Kreuzungsbereich (40) der Leitungselemente (10. 20).

- wobei zumindest das Strukturieren des Schaltungselements (30) in einem gemeinsamen Herstellungsschritt mit dem Strukturieren des ersten Leitungselements (10) durchgeführt wird, und zwar zunächst in einem ersten Atzschritt für das erste Leitungselement (10) und jeweils einem ersten Teil des jeweiligen Schaltungselementes (30),

- wobei der erste Atzschritt in Teilschritten durchgeführt wird,

- wobei dabei in einem ersten Teilätzschritt zunächst der erste Teil des Schaltungselements (30) bis zur Oberfläche (11a) einer ersten Metallschicht (11) für das erste Leitungselement (10) strukturiert wird,

- wobei dann entstandene Kantenbereiche (30k) des ersten Teils des Schaltungselements (30) passiviert werden durch Oxidabscheidung (33) mittels einer Spacertechnik und

- wobei dann in einem zweiten Teilätzschritt jeweils das erste Leitungselement (10) bis zur Oberseite (50a) eines Substratbereichs (50) strukturiert wird mit gemeinsam bündig sich vertikal erstreckender Flanke des ersten Leitungselements (10) und der Passivierung (33).

- 2. Verfahren nach Anspruch 1, bei welchem als Schaltungselement (30) jeweils ein Speicherelement (30) in Form eines TMR-Stapels einer MRAM-Zelle ausgebildet wird.

- 3. Verfahren nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass beim Ausbilden des Substratbereichs (50) ein Halbleiterbereich (51) mit einem Isolationsbereich (52) darauf und einer CMOS-Struktur ausgebildet wird.

- 4. Verfahren nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass beim Ausbilden der ersten Leitungselemente (10) zunächst die erste Material- oder Metallschicht (11) auf der Oberseite (50a) des Substratbereichs (50) aufgebracht wird in groß- oder ganzflächiger Form.

- 5. Verfahren nach Anspruch 4, dadurch gekennzeichnet, dass die erste Material- oder Metallschicht (11) planarisiert wird durch Polieren.

- 6. Verfahren nach einem der Ansprüche 4 oder 5, dadurch gekennzeichnet, dass auf die erste Materialoder Metallschicht (11) die Materialschicht (31) für die Schaltungselemente (30) abgeschieden wird in großoder ganzflächiger Form.

- 7. Verfahren nach Anspruch 6, dadurch gekennzeichnet.

- dass auf der Materialschicht (31) für die Schaltungselemente (30) als eine erste Maske (32) eine Hartmaske aus Siliziumnitrid ausgebildet wird.

- dass im ersten Ätzschritt die ersten Leitungselemente (10) und gleichzeitig damit jeweils der erste Teil des Schaltungselements (30) strukturiert werden entlang der Ausdehnung der ersten Maske (32) und dass mit einem Oxid als Zwischenisolationsbereich (12) aufgefüllt wird mit Abschluss auf der Oberseite (32a) der ersten Maske (32).

- 8. Verfahren nach Anspruch 7, dadurch gekennzeichnet, dass dann nachfolgend die erste Maske (32) durch einen weiteren Ätzschritt entfernt wird.

- 9. Verfahren nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet,

- dass nach dem Ausbilden der ersten Leitungselemente (10) und des jeweiligen ersten Teils der Schaltungselemente (30) zum Ausbilden der zweiten Leitungselemente (20) zunächst eine zweite Metallschicht (21) abgeschieden wird in groß- oder ganzflächiger Form,

- wobei die zweite Metallschicht (21) planarisiert wird durch Polieren.

- 10. Verfahren nach Anspruch 9, dadurch gekennzeichnet.

- dass dann zunächst eine zweite Maske (22) in Form einer Hartmaske aus Siliziumnitrid ausgebildet

wird,

- dass dann in einem zweiten Ätzschritt die zweiten Leitungselemente (20) und gleichzeitig damit ein zweiter Teil der Schaltungselemente (30) strukturiert werden entlang der Ausdehnung der zweiten Maske (22) und

- dass mit einem Zwischenisolationsbereich (12) aufgefüllt wird in Form eines Oxids mit Abschluss auf der Oberseite (22a) der zweiten Maske (22), wobei auf die Oberfläche (20a) des zweiten Leitungselements (20) planarisiert wird durch Polieren.

- 11. Verfahren nach Anspruch 10, dadurch gekennzeichnet.

- dass der zweite Ätzschritt in Teilschritten wird.

- dass dabei in einem ersten Teilätzschritt nachfolgend zunächst jeweils das zweite Leitungselement

(20) bis auf die Oberfläche des Zwischenisolationsbereichs (12) strukturiert wird und

- dass dann in einem zweiten Teilätzschritt der zweite

Teil des jeweiligen Schaltungselements (30) bis auf die Oberfläche (10a) des ersten Leitungselements (10) strukturiert wird.

- 12. Verfahren nach einem der Ansprüche 10 oder 11, dadurch gekennzeichnet, dass nach dem Strukturieren der ersten Leitungselemente (10), der zweiten Leitungselemente (20) und der Schaltungselemente (30) mit einem Zwischenoxid als Zwischenisolationsbereich (12) mit Abschluss auf der Oberseite (22a) der zweiten Maske (22) oder der Oberfläche (20a) des zweiten Leitungselements (20) aufgefüllt wird.

- 13. Verfahren nach einem der vorangehenden Ansprüche, dadurch gekennzeichnet, dass zum Strukturieren der ersten und zweiten Leitungselemente (10, 20) Streifenmasken (32, 22) mit verschiedenen Streifenrichtungen senkrecht zueinander verwendet werden.

Es folgen 3 Blatt Zeichnungen

## Anhängende Zeichnungen