(19)**日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号 特許第7097773号

(P7097773)

(45)発行日 令和4年7月8日(2022.7.8)

(24)登録日 令和4年6月30日(2022.6.30)

(51)国際特許分類

H 0 4 N

FΤ

Α

H 0 1 L 27/146 (2006.01)

5/369(2011.01)

H 0 1 L 27/146 H 0 4 N

5/369

請求項の数 19 (全14頁)

| (21)出願番号<br>(22)出願日 | 特願2018-140709(P2018-140709)<br>平成30年7月26日(2018.7.26) | (73)特許権者 | <br>000001007<br>キヤノン株式会社 |

|---------------------|------------------------------------------------------|----------|---------------------------|

| (65)公開番号            | 特開2020-17682(P2020-17682A)                           |          | 東京都大田区下丸子3丁目30番2号         |

| (43)公開日             | 令和2年1月30日(2020.1.30)                                 | (74)代理人  | 110003281                 |

| 審查請求日               | 令和3年6月15日(2021.6.15)                                 |          | 特許業務法人大塚国際特許事務所           |

|                     |                                                      | (72)発明者  | 波多野 雄一朗                   |

|                     |                                                      |          | 東京都大田区下丸子3丁目30番2号         |

|                     |                                                      |          | キヤノン株式会社内                 |

|                     |                                                      | (72)発明者  | 白井 誉浩                     |

|                     |                                                      |          | 東京都大田区下丸子3丁目30番2号         |

|                     |                                                      |          | キヤノン株式会社内                 |

|                     |                                                      | 審査官      | 西出 隆二                     |

|                     |                                                      |          |                           |

|                     |                                                      |          |                           |

|                     |                                                      |          | 最終頁に続く                    |

(54)【発明の名称】 固体撮像装置、基板および撮像システム

## (57)【特許請求の範囲】

#### 【 請 求 項 1 】

第1半導体領域と、前記第1半導体領域の上に配置された第2半導体領域と、前記第2半 導体領域の上に配置された第3半導体領域とを有し、前記第1半導体領域、前記第2半導 体領域および前記第3半導体領域によってチップ端面が構成された半導体チップを含む固 体撮像装置であって、

前記第1半導体領域は、第1導電型の領域であり、前記第2半導体領域は、前記第1導電 型の反対の第2導電型の領域であり、

前記第3半導体領域は、光電変換領域と、読出回路領域と、前記光電変換領域および前記 読出回路領域を取り囲むように配置された周辺領域とを含み、前記周辺領域は、分離領域 と、前記チップ端面と前記分離領域との間に配置された外周領域とを含み、

前記分離領域は、前記第2導電型の領域であり、前記外周領域は、前記第1導電型の領域 である、

ことを特徴とする固体撮像装置。

# 【請求項2】

前記第1半導体領域の上面と前記分離領域の下面との距離が第2半導体領域の厚さ以下で

ことを特徴とする請求項1に記載の固体撮像装置。

## 【請求項3】

前記第1半導体領域の上面と前記分離領域の下面との距離が前記第2半導体領域の厚さよ

#### り薄い、

ことを特徴とする請求項1に記載の固体撮像装置。

#### 【請求項4】

前記光電変換領域は、前記第1導電型の領域と、前記第2導電型の第1領域と、を含み、前記読出回路領域は、前記第1導電型の領域と、前記第2導電型の第2領域とを含み、前記分離領域は、前記第2導電型の第3領域と、前記第2導電型の第4領域とを含み、前記第1半導体領域の上面から前記第1領域の下面および前記第4領域の下面までの各距離は、前記第1半導体領域の前記上面から前記第2領域の下面および前記第3領域の下面までの各距離より小さい。

ことを特徴とする請求項1に記載の固体撮像装置。

## 【請求項5】

前記第1半導体領域の前記上面から前記第1領域の前記下面までの距離は、前記第1半導体領域の前記上面から前記第4領域の前記下面までの距離と等しい、

ことを特徴とする請求項4に記載の固体撮像装置。

#### 【請求項6】

前記第1半導体領域の前記上面から前記第2領域の前記下面までの距離は、前記第1半導体領域の前記上面から前記第3領域の前記下面までの距離と等しい、

ことを特徴とする請求項4又は5に記載の固体撮像装置。

#### 【請求項7】

前記第4領域は、前記第3領域を外側領域と内側領域とに分離するように配置されている、ことを特徴とする請求項4乃至6のいずれか1項に記載の固体撮像装置。

#### 【請求項8】

前記第1半導体領域の前記上面に平行な方向において、前記第4領域の幅は、前記外側領域の幅および前記内側領域の幅のそれぞれより小さい、

ことを特徴とする請求項7に記載の固体撮像装置。

## 【請求項9】

前記周辺領域の上面は、凹部を有し、

前記分離領域は、前記凹部の底面の下に配置された前記第2導電型の第3領域および前記第2導電型の第4領域を含み、

前記凹部に絶縁体が配置されている、

ことを特徴とする請求項1に記載の固体撮像装置。

## 【請求項10】

前記第4領域は、前記第3領域を外側領域と内側領域とに分離するように配置されている、ことを特徴とする請求項9に記載の固体撮像装置。

#### 【請求項11】

前記第1半導体領域の上面から前記第4領域の下面までの距離は、前記第1半導体領域の 前記上面から前記第3領域の下面までの距離より小さい、

ことを特徴とする請求項10に記載の固体撮像装置。

## 【請求項12】

前記第3領域および前記第4領域は、前記凹部の前記底面に接している、

ことを特徴と請求項9乃至11のいずれか1項に記載の固体撮像装置。

## 【請求項13】

前記読出回路領域は、前記第1導電型の領域と、前記第2導電型の第2領域とを含み、

前記第2領域の下面は、前記第2半導体領域の上面から離隔し、

前記第2領域には、回路素子が配置され、

前記第3領域および前記第4領域には、回路素子が配置されていない、

ことを特徴とする請求項9乃至12のいずれか1項に記載の固体撮像装置。

## 【請求項14】

前記第1半導体領域の前記上面から前記第2領域の前記下面までの距離は、前記第1半導体領域の前記上面から前記第3領域の下面までの距離と等しい、

10

20

30

ことを特徴とする請求項13に記載の固体撮像装置。

#### 【請求項15】

前記読出回路領域は、前記第1導電型の領域と、前記第2導電型の第2領域とを含み、 前記分離領域は、前記第2導雷型の第3領域と前記第2導雷型の第4領域とを含み、 前記読出回路領域および前記周辺領域は、前記第2領域の下面および前記第3領域の下面 に接するように前記第2半導体領域の上面に平行に広がった前記第1導電型の第5領域を

ことを特徴とする請求項1に記載の固体撮像装置。

#### 【請求項16】

前記第1半導体領域の上面と前記第4領域の下面との距離が前記第2半導体領域の厚さ以 下である、

ことを特徴とする請求項15に記載の固体撮像装置。

## 【請求項17】

前記光電変換領域に前記第1導電型の電荷蓄積領域が配置されている、

ことを特徴とする請求項1乃至16のいずれか1項に記載の固体撮像装置。

複数の半導体チップ領域が配置された領域を有する基板であって、

前記複数の半導体チップ領域の間のダイシングライン領域に配置されたTEGを備え、 前記複数の半導体チップ領域の各々は、前記基板からダイシングされた状態において請求 項1乃至17のいずれか1項に記載の固体撮像装置を含み、

前記TEGは、前記複数の半導体チップ領域のうちの1つの半導体チップの端面と前記複 数の半導体チップ領域のうちの他の半導体チップの端面との間に配置されている、 ことを特徴とする基板。

#### 【請求項19】

請求項1乃至17のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とする撮像システム。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、固体撮像装置、基板および撮像システムに関する。

## 【背景技術】

## [0002]

特許文献1には、固体撮像装置におけるチップ切断面にPN接合面が現れると、切断面の 表面がリーク電流の発生原因となったり、リーク電流の流路となったりするおそれが高く なり、ひいてはリーク電流の増大を招くおそれが高くなることが記載されている。このよ うな課題を解決するための構造として、特許文献 1 には、切断面を P 型の半導体層、 P ウ ェルおよびP型半導体基板のみで形成し、切断面にPN接合面が現れないようにした構造 が記載されている(段落0024、0025等)。

## 【先行技術文献】

【特許文献】

[0003]

【文献】特開2006-286933号公報

## 【発明の概要】

【発明が解決しようとする課題】

#### [0004]

ここで、特許文献 1 に記載された発明の思想は、切断面に P 型の半導体領域のみを露出さ せるものである。ダイシングライン部にTEG(Test Element Group) を配置することは、切断面のP型およびN型の双方の半導体領域が露出することを意味す るので、特許文献1に記載された発明の思想に反すると言える。しかし、TEGをチップ

10

20

30

40

領域に形成すると、1枚の基板から得られるチップ(固体撮像装置)の数が低下すること に加え、露光工程が複雑化(例えば、1回のリソグラフィー工程において2枚のレチクル が必要になるなど)し、コスト増加をもたらしうる。

本発明は、半導体チップの端面のPN接合で発生しうるリーク電流が光電変換領域に影響 を与えることを抑制しつつダイシングライン部にTEGを配置するために有利な構造を有 する固体撮像装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### [0006]

本発明の1つの側面は、第1半導体領域と、前記第1半導体領域の上に配置された第2半 導体領域と、前記第2半導体領域の上に配置された第3半導体領域とを有し、前記第1半 導体領域、前記第2半導体領域および前記第3半導体領域によってチップ端面が構成され た半導体チップを含む固体撮像装置に関するものであり、前記第1半導体領域は、第1導 電型の領域であり、前記第2半導体領域は、前記第1導電型の反対の第2導電型の領域で あり、前記第3半導体領域は、光電変換領域と、読出回路領域と、前記光電変換領域およ び前記読出回路領域を取り囲むように配置された周辺領域とを含み、前記周辺領域は、分 離領域と、前記チップ端面と前記分離領域との間に配置された外周領域とを含み、前記分 離領域は、前記第2導電型の領域であり、前記外周領域は、前記第1導電型の領域である。

## 【発明の効果】

#### [0007]

本発明によれば、半導体チップの端面のPN接合で発生しうるリーク電流が光電変換領域 に影響を与えることを抑制しつつダイシングライン部にTEGを配置するために有利な構 造を有する固体撮像装置が提供される。

## 【図面の簡単な説明】

## [00008]

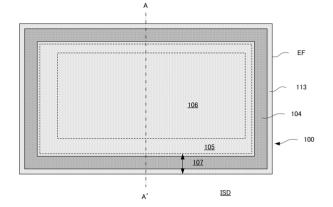

- 【図1】本発明の第1実施形態の固体撮像装置の構成を模式的に示す平面図。

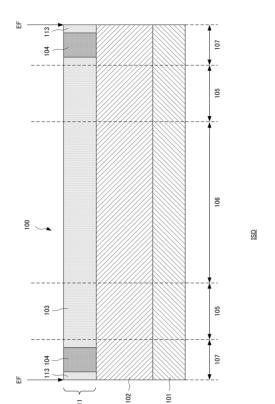

- 【図2】図1のA-A′線で切断された第1実施形態の固体撮像装置の断面構造の一部を模 式的に示す図。

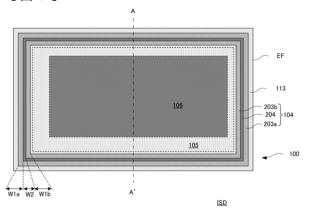

- 【図3】本発明の第2実施形態の固体撮像装置の構成を模式的に示す平面図。

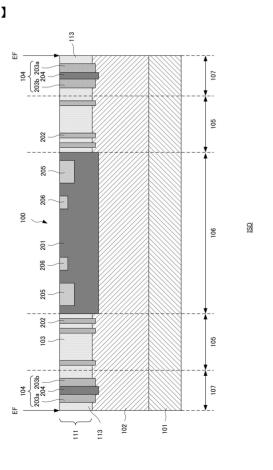

- 【図4】図3のA-A′線で切断された第2実施形態の固体撮像装置の断面構造の一部を模 式的に示す図。

- 【図5】図3のA-Aႛ線で切断された第3実施形態の固体撮像装置の断面構造の一部を模

- 【図6】図3のA-A′線で切断された第4実施形態の固体撮像装置の断面構造の一部を模 式的に示す図。

- 【図7】本発明の第5実施形態の基板の模式的な断面構造の一部を模式的に示す図。

- 【図8】本発明の一実施形態の固体撮像装置が組み込まれた撮像システムの一例を例示す る図。

## 【発明を実施するための形態】

## [0009]

以下、添付図面を参照しながら本発明のその例示的な実施形態を通して説明する。

## [0010]

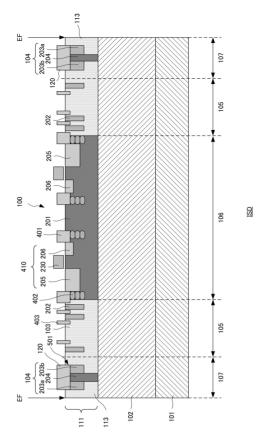

図1には、本発明の第1実施形態の固体撮像装置ISDの構成が模式的に示されている。 図2には、図1のA-A'線で切断された第1実施形態の固体撮像装置ISDの断面構造の 一部が模式的に示されている。固体撮像装置ISDは、例えば、CMOSイメージセンサ またはCCDイメージセンサ等のイメージセンサとして構成されうる。固体撮像装置IS Dは、 2 次元イメージセンサとして構成されてもよいし、 1 次元イメージセンサ(ライン センサ)として構成されてもよい。以下では、 n 型および p 型の一方を第 1 導電型と呼び 、n型およびp型の他方を第2導電型と呼ぶ。第2導電型は、第1導電型とは反対の導電 型である。第1導電型がn型であれば、第2導電型はp型であり、第1導電型がp型であ

10

20

30

40

れば、第2導電型はn型である。なお、図2では、第3半導体領域111の上面より上に配置される構造は、図示が省略されている。また、図2では、第3半導体領域111を利用して構成される光電変換素子およびトランジスタ等の素子は、図示が省略されている。

#### [0011]

固体撮像装置ISDは、半導体チップ100を含む。半導体チップ100は、第1半導体領域101と、第1半導体領域101の上に配置された第2半導体領域102と、第2半導体領域102の上に配置された第3半導体領域111とを有する。半導体チップ100の端面EFは、複数の半導体チップ100が配列された基板から複数の半導体チップ100を分離するためのダイシング工程によって現れる面である。端面EFは、第1半導体領域101(の端面)、第2半導体領域102(の端面)および第3半導体領域111(の端面)によって構成される。

#### [0012]

第1半導体領域101は、第1導電型の領域であり、第2半導体領域102は、第2導電型の領域である。第3半導体領域111は、光電変換領域106と、読出回路領域105と、周辺領域107とを含みうる。光電変換領域106は、第1導電型の不従物を含む領域103を含みうる。光電変換領域106は、相互に電気的に分離された複数の光電変換素子(不図示)を含む。各光電変換素子は、光電変換によって発生した電荷を蓄積する電荷蓄積領域を含みうる。読出回路領域105は、第1導電型の不純物を含む領域103を含みうる。

## [0013]

読出回路領域105は、光電変換領域106に配置された複数の光電変換素子から信号を 読み出すための読出回路が配置された領域である。読出回路は、例えば、複数の光電変換 素子(画素)で構成される画素アレイにおける行を選択する行選択回路、選択された行の 光電変換素子からの信号を読み出す信号処理回路、信号処理回路によって読み出された信 号を順に出力する列選択回路等を含みうる。周辺領域107は、光電変換領域106およ び読出回路領域105を取り囲むように配置される。

#### [0014]

周辺領域107は、分離領域104と、チップ端面EFと分離領域104との間に配置された外周領域113とを含む。分離領域104は、第2導電型の領域であり、外周領域113は、第1導電型の領域である。第1半導体領域101の上面(この例では、第1半導体領域101と第2半導体領域102との界面)と分離領域104の下面との距離は、例えば、第2半導体領域102の厚さ以下でありうる。

## [0015]

第1半導体領域101は、例えば、第1導電型のシリコン基板で構成されうる。第2半導 体領域102は、例えば、第2導電型の第1半導体領域101の上にエピタキシャル成長 法によって形成されたエピタキシャル層でありうる。第3半導体領域111は、例えば、 第2半導体領域102の上にエピタキシャル成長法で形成された第1導電型のエピタキシ ャル層(領域103)に対してイオンを注入することによって形成された複数の第1導電 型の領域および複数の第2導電型の領域を有する。第3半導体領域111の光電変換領域 106の光電変換素子等は、例えば、第2半導体領域102の上にエピタキシャル成長法 によって形成された第1導電型のエピタキシャル層(領域103)に対してイオンを注入 することによって形成されうる。第3半導体領域111の読出回路領域105は、例えば 、第2半導体領域102の上にエピタキシャル成長法によって形成された第1導電型のエ ピタキシャル層(領域103)に対してイオンを注入することによって形成されうる。第 3 半導体領域111の分離領域104は、例えば、第2半導体領域102の上にエピタキ シャル成長法によって形成されたエピタキシャル層(領域103)に対してイオンを注入 することによって形成されうる。第3半導体領域111の外周領域113は、例えば、第 2 半導体領域102の上にエピタキシャル成長法によって形成された第1導電型のエピタ キシャル層(領域103)そのものの一部によって形成されうる。

## [0016]

10

20

30

半導体チップ100の端面EFには、第2導電型の第2半導体領域102と第1導電型の外周領域113との接合が露出している。端面EFに露出した第2半導体領域102と外周領域113との接合は、キャリアを発生させうる。しかし、このキャリアが読出回路領域105の読出回路および光電変換領域106の光電変換素子に与える影響は、周辺領域107に第2導電型の分離領域104が配置されることによって低減されうる。このような低減効果は、例えば、固体撮像装置ISDが50秒位以上の長時間の電荷蓄積を行う場合に有効に機能しうる。

## [0017]

なお、第1半導体領域101と第2半導体領域102とによって形成されるPN接合が端面EFに露出した部分でもキャリアが発生しうる。しかし、このキャリアが読出回路領域105の読出回路および光電変換領域106の光電変換素子に移動することは、第2半導体領域102によって妨げられる。

## [0018]

固体撮像装置ISDまたは半導体チップ100がそれを搭載した基板からダイシングされる際に、端面EFの外側(図2では、左側の端面EFの更に左側、又は、右側の端面EFの更に右側))に配置されたTEGは、除去されうる。TEGは、ダイシングによって除去されるダイシングライン部(スクライブライン部)におけるエピタキシャル層(領域103)に形成される。よって、ダイシングライン部におけるエピタキシャル層(領域103)には、例えば、光電変換領域106の光電変換素子と同一の構造を有する光電変換素子を形成したり、プロセスの妥当性を確認するためのプロセスTEGを形成したりすることができる。

#### [0019]

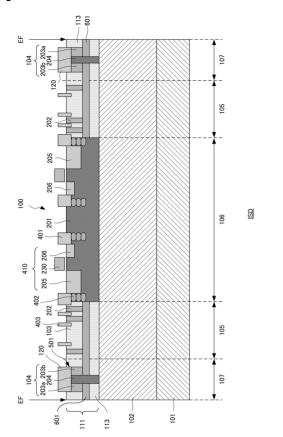

図3には、本発明の第2実施形態の固体撮像装置ISDの構成が模式的に示されている。 図4には、図3のA-A<sup>°</sup>線で切断された固体撮像装置ISDの断面構造の一部が模式的に 示されている。なお、第2実施形態として言及しない事項は、第1実施形態に従いうる。

## [0020]

光電変換領域106は、第2導電型の第1領域201と、第1導電型の複数の領域205と、第1導電型の複数の領域206とを含みうる。読出回路領域105は、第1導電型の少なくとも1つの領域103と、第2導電型の少なくとも1つの第2領域202とを含みうる。周辺領域107の分離領域104は、第2導電型の第3領域203a、203 b と、第2導電型の第4領域204とを含みうる。なお、図4では、第3半導体領域111の上面より上に配置される構造は、図示が省略されている。また、図4では、トランジスタ等の素子は、図示が省略されている。

## [0021]

光電変換領域106の第1導電型の各領域205は、第2導電型の第1領域201とともにフォトダイオード(光電変換素子)を構成しうる。図4において、光電変換領域106の第1導電型の各領域206は、例えば、フォローティングディフュージョン、および、MOSトランジスタのソース領域・ドレイン領域を代表して示されたものである。読出回路領域105の第1導電型の領域103には、第2導電型の複数のMOSトランジスタが配置されうる。読出回路領域105の第2導電型の第2領域202には、第1導電型の複数のMOSトランジスタ等の回路素子が配置されうる。一方、周辺領域107の分離領域104(第3領域203a、203b、第4領域204)には、MOSトランジスタおよび光電変換素子等の回路素子が配置されない。周辺領域107は、チップ端面EFと分離領域104との間に配置された外周領域113を含む。

## [0022]

一例において、第1半導体領域101の上面から第1領域201の下面および第4領域204の下面までの各距離は、第1半導体領域101の上面から第2領域202の下面および第3領域203(203a、203b)の下面までの各距離より小さい。換言すると、一例において、第3半導体領域111の表面を基準とする第1領域201の下面および第4領域204の下面の深さは、第3半導体領域111の表面を基準とする第2領域202

10

20

30

40

の下面および第3領域203の下面の深さより深い。以下、深さは、特に言及しない限りは、第3半導体領域111の表面を基準とする深さとして説明される。

## [0023]

一例において、第1半導体領域101の上面から第1領域201の下面までの距離は、第1半導体領域101の上面から第4領域204の下面までの距離と等しい。換言すると、一例において、第1領域201の下面の深さは、第4領域204の下面の深さと等しい。また、一例において、第1領域201における第2導電型の不純物濃度の最大値は、第4領域204における第2導電型の不純物濃度の最大値と等しい。第1領域201と第4領域204とは、同一の工程(同一のフォトリソグラフィー工程、および、同一のイオン注入工程)において形成されうる。これは、工程数の削減に寄与する。ここで、同一工程で第1領域201と第4領域204の形成することは、フォトマスク(レチクル)の枚数の削減に寄与する他、光電変換領域106に対する分離領域104の第4領域204の相対位置を保証することに寄与する。これは、外周領域113から光電変換領域106へのキャリアの遮断特性を安定化させるために有利である。

#### [0024]

一例において、第1半導体領域101の上面から第2領域202の下面までの距離は、第1半導体領域101の上面から第3領域203の下面までの距離と等しい。換言すると、一例において、第2領域202の下面の深さは、第3領域203の下面の深さと等しい。また、一例において、第2領域202における第2導電型の不純物濃度の最大値は、第3領域203における第2導電型の不純物濃度の最大値と等しい。第2領域202および第3領域203は、同一の工程(同一のフォトリソグラフィー工程、および、同一のイオン注入工程)において形成されうる。第4領域204は、第3領域203を外側領域203aと内側領域203bとに分離するように配置されうる。

#### [0025]

一例において、第1領域201における第2導電型の不純物濃度および第4領域204における第2導電型の不純物濃度は、第2領域202における第2導電型の不純物濃度および第3領域203における第2導電型の不純物濃度よりも低い。

#### [0026]

図3の平面図(平面視)において、第3領域203(203a、203b)および第4領域204は、光電変換領域106および読出回路領域105をそれらの側方から取り囲むように配置されている。一例において、第1半導体領域101の上面に平行な方向において、第4領域204の幅W2は、外側領域203aの幅W1aおよび内側領域203bの幅W1bのそれぞれより小さい。

## [0027]

図5には、本発明の第3実施形態の固体撮像装置ISDの断面構造の一部が模式的に示されている。ここで、図5に示された断面構造は、図3におけるA-A'線の断面構造に相当する。なお、第3実施形態として言及しない事項は、第1、第2実施形態に従いうる。光電変換領域106には、素子分離401が配置され、読出回路領域105には、素子分離403が配置されている。素子分離401、403は、例えば、LOCOS(LocalOxidation of Silicon)またはSTI(Shallow Trench Isolation)で構成されうる。なお、図5では、第3半導体領域111の上面より上に配置される構造、および、トランジスタ等の素子は、一部を除いて、図示が省略されている。

#### [0028]

光電変換領域106は、第2導電型の第1領域201と、第1導電型の複数の領域205と、第1導電型の複数の領域206とを含みうる。読出回路領域105は、第1導電型の少なくとも1つの領域103と、第2導電型の少なくとも1つの第2領域202とを含みうる。光電変換領域106は、複数の画素410を有し、1つの画素410は、第1導電型の領域205によって構成される1つの電荷蓄積領域を含みうる。画素410と画素410とは、素子分離401の他、素子分離401の下に配置された第2導電型の領域40

10

20

30

40

2によって分離されうる。一例において、領域402における第2導電型の不純物濃度の最大値は、第1領域201における第2導電型の不純物濃度の最大値よりも1桁ないし2桁ほど高い。領域402は、第2導電型の複数の領域の積層構造によって形成されうる。該複数の領域は、第3半導体領域111の表面に近いほど高い第2導電型の不純物濃度を有するように構成されうる。

## [0029]

周辺領域107の分離領域104は、第2導電型の第3領域203a、203bと、第2導電型の第4領域204とを含みうる。読出回路領域105の第1導電型の領域103には、第2導電型の複数のMOSトランジスタが配置されうる。読出回路領域105の第2導電型の第2領域202には、第1導電型の複数のMOSトランジスタが配置されうる。一方、周辺領域107の分離領域104(第3領域203a、203b、第4領域204)には、MOSトランジスタおよび光電変換素子等の素子が配置されない。周辺領域107は、チップ端面EFと分離領域104との間に配置された外周領域113を含む。

#### [0030]

第1領域201および第4領域204は、第2半導体領域102の上面と接触するように配置されうる。一例において、第1半導体領域101の上面から第1領域201の下面および第4領域204の下面までの各距離は、第1半導体領域101の上面から第2領域202の下面および第3領域203(203a、203b)の下面までの各距離より小さい。換言すると、一例において、第1領域201の下面および第4領域204の下面の深さは、第2領域202の下面および第3領域203の下面の深さより深い。あるいは、第2領域202の下面と第2半導体領域102の上面との間には、領域103の一部が配置されうる。あるいは、第2領域202の下面と第2半導体領域102の上面から離隔されうる。

#### [0031]

一例において、第1領域 2 0 1 の下面および第4領域 2 0 4 の下面の深さは、4 ~ 6  $\mu$  m の範囲内、例えば 5  $\mu$  m であり、第 2 領域 2 0 2 の下面および第 3 領域 2 0 3 の下面の深さは、0 . 5  $\mu$  m ~ 1 . 5  $\mu$  m の範囲内、例えば 1  $\mu$  m である。一例において、第 1 領域 2 0 1 および第 4 領域 2 0 4 は、第 3 半導体領域 1 1 1 の上面に近いほど高い第 2 導電型の不純物濃度を有しうる。例えば、第 1 領域 2 0 1 および第 4 領域 2 0 4 における第 2 導電型の不純物濃度は、第 3 半導体領域 1 1 1 の下面の付近では 1  $\times$  1 0 1 5 ~ 1  $\times$  1 0 1 6 c m - 3 の範囲内でありうる。また、第 1 領域 2 0 1 および第 4 領域 2 0 4 における第 2 導電型の不純物濃度は、第 3 半導体領域 1 1 1 の表面から 0 . 2  $\mu$  m 程度の深さでは、1  $\times$  1 0 1 9 ~ 1  $\times$  1 0 2 0 c m - 3 の範囲内でありうる。

## [0032]

ー例において、同一深さにおいて、第 1 領域 2 0 1 および第 4 領域 2 0 4 における第 2 導電型の不純物濃度は、第 2 領域 2 0 2 および第 3 領域 2 0 3 における第 2 導電型の不純物濃度よりも低い。例えば、深さ 1  $\mu$  m において、第 3 領域 2 0 3 における第 2 導電型の不純物濃度は、 1  $\times$  1 0 <sup>1 7</sup>  $\sim$  1  $\times$  1 0 <sup>1 8</sup> c m  $\sim$  3 の範囲内でありうる。

## [0033]

周辺領域107(周辺領域107における第3半導体領域111)の上面は、凹部501を有しうる。周辺領域107に設けられた分離領域104は、凹部501の底面の下に配置された第2導電型の第3領域203(203a、203b)および第2導電型の第4領域204を含むように構成されうる。凹部501には、絶縁体120が配置されうる。絶縁体120は、素子分離401、403と同時に形成されうる。第4領域204は、凹部501の下において第3領域203を外側領域203aと内側領域203bとに分離するように配置されうる。第3領域203(203a、203b)および第4領域204は、凹部501の底面に接するように配置されうる。

## [0034]

第 3 領域 2 0 3 ( 2 0 3 a 、 2 0 3 b ) および第 4 領域 2 0 4 は、第 3 半導体領域 1 1 1 に対するイオン注入によって形成されうる。このイオン注入によって第 3 半導体領域 1 1

10

20

30

40

1の表面がダメージを受けうる。しかし、凹部501に絶縁体120を配置し、その下に第3領域203(203a、203b)および第4領域204を配置することによって、長時間の電荷蓄積を行う場合におけるノイズの増加を抑制することができる。

#### [0035]

第3実施形態においても、周辺領域107に第2導電型の分離領域104が配置されることによって、このキャリアが読出回路領域105の読出回路および光電変換領域106の 光電変換素子に与える影響が低減あるいは遮断されうる。

#### [0036]

図6には、本発明の第4実施形態の固体撮像装置ISDの断面構造の一部が模式的に示されている。第4実施形態の固体撮像装置ISDは、図5に示された第3実施形態の固体撮像装置ISDの変形例である。第4実施形態として言及しない事項は、第3実施形態に従いうる。

## [0037]

読出回路領域 1 0 5 は、第 1 導電型の領域 1 0 3 と、第 2 導電型の第 2 領域 2 0 2 とを含む。周辺領域 1 0 7 は、分離領域 1 0 4 を含み、分離領域 1 0 4 は、第 2 導電型の第 3 領域 2 0 3 ( 2 0 3 a 、 2 0 3 b ) と第 2 導電型の第 4 領域 2 0 4 とを含みうる。読出回路領域 1 0 5 および周辺領域 1 0 7 は、第 2 領域 2 0 2 の下面および第 3 領域 2 0 3 の下面に接するように第 2 半導体領域 1 0 2 の上面に平行に広がった第 1 導電型の第 5 領域 6 0 1 を含む。第 5 領域 6 0 1 における第 1 不純物の最大濃度を有する部分の深さは、例えば、1 、5  $\mu$ m~2 、5  $\mu$ mの範囲内であり、例えば 2  $\mu$ mである。第 5 領域 6 0 1 における第 1 不純物濃度は、1 × 1 0 1 6 ~ 1 × 1 0 1 7 c m - 3 の範囲内でありうる。

#### [0038]

以上の構成は、半導体チップ100の端面EFで発生するキャリアが光電変換領域106に侵入することを抑制しつつ、第2領域202/第3領域203と第2半導体領域102との間のリークも抑制し耐圧不良の発生を防ぐために有利である。

## [0039]

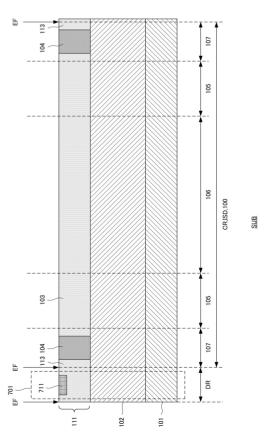

ここで、以上の第1乃至第4実施形態の固体撮像装置ISDは、第1導電型をn型、第2 導電型をp型として実施する一例を説明する。第1半導体領域101は、N+型シリコン 基板で構成され、第1半導体領域101の上に第2半導体領域102としてP型エピタキ シャル層が形成され、第2半導体領域102の上に第3半導体領域111として更にP型 エピタキシャル層が形成されうる。そして、第3半導体領域111としてのP型エピタキ シャル層の光電変換領域106に電子収集型の複数の光電変換素子が形成されうる。

## [0040]

図7には、本発明の第5実施形態の基板SUBの模式的な断面構造が示されている。基板SUBは、複数の半導体チップ領域CR(ISD)が配置された領域を有する。基板SUBは、複数の半導体チップ領域CR(図7には1つの半導体チップ領域CSのみ示されている)の間のダイシングライン領域(スクライブライン領域)に配置されたTEG711を備える。複数の半導体チップ領域CRの各々は、基板SUBからダイシングされた状態において固体撮像装置ISD(半導体チップ100)となる回路構成を含む。TEG711は、複数の半導体チップ領域CRのうちの1つの半導体チップCRの端面EFと該複数の半導体チップ領域CRのうちの他の半導体チップCRの端面EFとの間に配置されている。ダイシングライン領域(スクライブライン領域)は、基板SUBをダイシングするための領域、即ち、ダイシングによって取り除かれる領域である。

#### [0041]

TEG711は、例えば、光電変換領域106に配置される光電変換素子等の素子および 読出回路領域105に配置されるMOSトランジスタ等の素子と同様の素子含みうる。あ るいは、TEG711は、プロセスの妥当性を確認するためのプロセスTEGを含みうる 。TEG711は、第1導電型の領域103に形成されうる。よって、ダイシングライン 部701における第1導電型の領域103には、例えば、光電変換領域106の光電変換 素子と同一の構造を有する光電変換素子を形成したり、プロセスの妥当性を確認するため 10

20

30

40

のプロセスTEGを形成したりすることができる。

#### [0042]

上記の実施形態において、第3半導体領域111の上には、配線層を含む層間絶縁膜、カ ラーフィルタ層およびマイクロレンズアレイ等が配置され、これにより、表面照射型の固 体撮像装置が形成されうる。ただし、本発明は、裏面照射型の固体撮像装置に適用されて もよい。

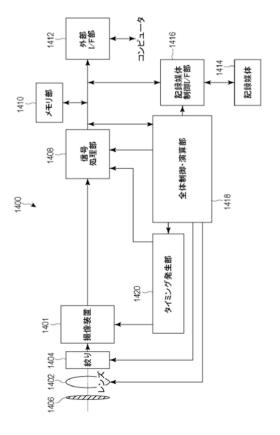

## [0043]

上記の固体撮像装置ISDは、種々の撮像システムに組み込まれうる。そのような撮像シ ステムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機 、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの 光学系と固体撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。

## [0044]

図8には、上記の固体撮像装置ISDが組み込まれた撮像システムの一例が示されている 。図8に示された例では、撮像システムがデジタルスチルカメラとして具体化されている 。図8に例示した撮像システム1400は、前述の固体撮像装置ISDとしての固体撮像 装置1401、被写体の光学像を固体撮像装置1401に結像させるレンズ1402を有 する。また、レンズ1402を通過する光量を可変にするための絞り1404、レンズ1 4 0 2 の保護のためのバリア 1 4 0 6 を有する。レンズ 1 4 0 2 及び絞り 1 4 0 4 は、固 体撮像装置1401に光を集光する光学系である。固体撮像装置1401は、実施の形態 1または2で説明した固体撮像装置1であって、レンズ1402により結像された光学像 を画像データに変換する。

#### [0045]

撮像システム1400は、また、固体撮像装置1401より出力される出力信号の処理を 行う信号処理部1408を有する。信号処理部1408は、固体撮像装置1401が出力 するアナログ信号をデジタル信号に変換するAD変換を行う。また、信号処理部1408 はその他、必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。信 号処理部1408の一部であるAD変換部は、固体撮像装置1401が設けられた半導体 基板に形成されていてもよいし、固体撮像装置1401とは別の半導体基板に形成されて いてもよい。また、固体撮像装置1401と信号処理部1408とが同一の半導体基板に 形成されていてもよい。

## [0046]

撮像システム1400は、さらに、画像データを一時的に記憶するためのメモリ部141 0、外部コンピュータ等と通信するための外部インターフェース部(外部I/F部)14 12を有する。さらに撮像システム1400は、撮像データの記録又は読み出しを行うた めの半導体メモリ等の記録媒体1414、記録媒体1414に記録又は読み出しを行うた めの記録媒体制御インターフェース部(記録媒体制御I/F部)1416を有する。なお 、記録媒体1414は、撮像システム1400に内蔵されていてもよく、着脱可能であっ てもよい。

## [0047]

さらに撮像システム1400は、各種演算とデジタルスチルカメラ全体を制御する全体制 御・演算部1418、固体撮像装置1401と信号処理部1408に各種タイミング信号 を出力するタイミング発生部1420を有する。ここで、タイミング信号などは外部から 入力されてもよく、撮像システム1400は少なくとも固体撮像装置1401と、固体撮 像装置1401から出力された出力信号を処理する信号処理部1408とを有すればよい。

## [0048]

固体撮像装置1401は、撮像信号を信号処理部1408に出力する。信号処理部140 8は、固体撮像装置1401から出力される撮像信号に対して所定の信号処理を実施し、 画像データを出力する。信号処理部1408は、撮像信号を用いて、画像形成を行う。例 えば、信号処理部1408は、固体撮像装置1401のノイズ信号及び第1画素信号及び 第2画素信号に基づくデジタル信号を用いて焦点検出を行う。また、固体撮像装置140

10

20

30

1のノイズ信号及び第2または第4画素信号に基づくデジタル信号を用いて画像形成を行う。

## 【符号の説明】

[0049]

ISD: 固体撮像装置、100: 半導体チップ、101: 第1半導体領域、102: 第2半導体領域、103: 領域、104: 分離領域、105: 読出回路領域、106: 光電変換領域、111: 第3半導体領域、201: 第1領域、202: 第2領域、203: 第3領域、204: 第4領域、601: 第5領域

10

20

30

# 【図面】

【図1】

【図2】

Ξ

【図3】

【図4】

50

40

10

20

【図5】

【図6】

【図7】

【図8】

50

40

10

20

## フロントページの続き

```

(56)参考文献

特開2006-147757(JP,A)

特開2006-286933(JP,A)

特開平07-142586(JP,A)

特開2000-150848(JP,A)

特開2005-236013(JP,A)

特開2014-090172(JP,A)

特開2008-091781(JP,A)

特開2010-239005(JP,A)

特開2003-258229(JP,A)

特開2003-324213(JP,A)

特開2016-009691(JP,A)

特開2010-028141(JP,A)

国際公開第2016/143553(WO,A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H 0 4 N

5/369

```