## (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2019/117883 A1

(51) International Patent Classification:

**H01L 29/15** (2006.01) **H01L 29/66** (2006.01) **H01L 39/02** (2006.01)

(21) International Application Number:

PCT/US2017/065932

(22) International Filing Date:

13 December 2017 (13.12.2017)

(25) Filing Language:

English

(26) Publication Language:

English

- (71) Applicant: INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, California 95054-1549 (US).

- (72) Inventors: YOSCOVITS, Zachary R.; 16145 NW Schendel Avenue, Unit 21B, Beaverton, Oregon 97006 (US).

LAMPERT, Lester; 17564 NW Springville Rd., Unit 4, Portland, Oregon 97229 (US). CAUDILLO, Roman; 2305 SE 16th Avenue, Portland, Oregon 97214 (US).

ROBERTS, Jeanette M.; 17898 NW Pumpkin Ridge Road, North Plains, Oregon 97133 (US). GEORGE, Hubert C.; 7016 NW Eleanor Avenue, Portland, Oregon 97229 (US). THOMAS, Nicole K.; 1125 NW 12th Ave, Apt 309, Portland, Oregon 97209 (US). SINGH, Kanwaljit; Wierdsmaplein 41, 3072 MJ Rotterdam (NL). MICHALAK, David J.; 1511 SW Park Avenue, Apt 811, Portland, Oregon 97201 (US). PILLARISETTY, Ravi; 1330 SW 3rd Ave, Apt. 1103, Portland, Oregon 97201 (US). CLARKE, James S.; 5676 NW 204th Place, Portland, Oregon 97229 (US).

- (74) Agent: HARTMANN, Natalya; Patent Capital Group, 2816 Lago Vista Lane, Rockwall, Texas 75032 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP,

(54) Title: QUBIT DEVICES WITH JOSEPHSON JUNCTIONS FABRICATED USING AIR BRIDGE OR CANTILEVER

FIG. 4

(57) **Abstract:** One aspect of the present disclosure proposes a method of fabricating quantum circuit assemblies that include Josephson Junctions. The method is based on providing a structure that forms a bridge or a cantilever over a lead for the bottom electrode of a future Josephson Junction, forming an opening in the bridge/cantilever so that the opening is above the lead for the bottom electrode, and then depositing bottom and top electrode materials, as well as the tunnel barrier material for the Josephson Junction, through the opening. Such a method may result in Josephson Junctions having an improved performance compared to Josephson Junctions fabricated using existing techniques, and may be efficiently used in large-scale manufacturing.

KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Declarations under Rule 4.17:**

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- of inventorship (Rule 4.17(iv))

#### **Published:**

— with international search report (Art. 21(3))

# QUBIT DEVICES WITH JOSEPHSON JUNCTIONS FABRICATED USING AIR BRIDGE OR CANTILEVER <u>Technical Field</u>

**[0001]** This disclosure relates generally to the field of quantum computing, and more specifically, to Josephson Junctions for use in quantum circuits and to methods of fabrication thereof.

## **Background**

**[0002]** Quantum computing refers to the field of research related to computation systems that use quantum-mechanical phenomena to manipulate data. These quantum-mechanical phenomena, such as superposition (in which a quantum variable can simultaneously exist in multiple different states) and entanglement (in which multiple quantum variables have related states irrespective of the distance between them in space or time), do not have analogs in the world of classical computing.

[0003] Quantum computers use so-called quantum bits, referred to as qubits (both terms "bits" and "qubits" often interchangeably refer to the values that they hold as well as to the actual devices that store the values). Similar to a bit of a classical computer, at any given time, a qubit can be either 0 or 1. However, in contrast to a bit of a classical computer, a qubit can also be 0 and 1 at the same time, which is a result of superposition of quantum states – a uniquely quantum-mechanical phenomenon. Entanglement also contributes to the unique nature of qubits in that input data to a quantum processor can be spread out among entangled qubits, allowing manipulation of that data to be spread out as well: providing input data to one qubit results in that data being shared to other qubits with which the first qubit is entangled.

**[0004]** Compared to well-established and thoroughly researched classical computers, quantum computing is still in its infancy, with the highest number of qubits in a solid-state quantum processor currently being below 100. One of the main challenges resides in protecting qubits from decoherence so that they can stay in their information-holding states long enough to perform the necessary calculations and read out the results. Another challenge resides in fabricating qubits in a manner that may be used in large-scale manufacturing.

# **Brief Description of the Drawings**

**[0005]** Embodiments will be readily understood by the following detailed description in conjunction with the accompanying drawings. To facilitate this description, like reference numerals designate like structural elements. Embodiments are illustrated by way of example, and not by way of limitation, in the figures of the accompanying drawings.

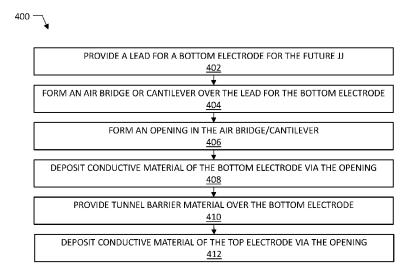

[0006] FIG. 1 provides a schematic illustration of an exemplary superconducting quantum circuit, according to some embodiments of the present disclosure.

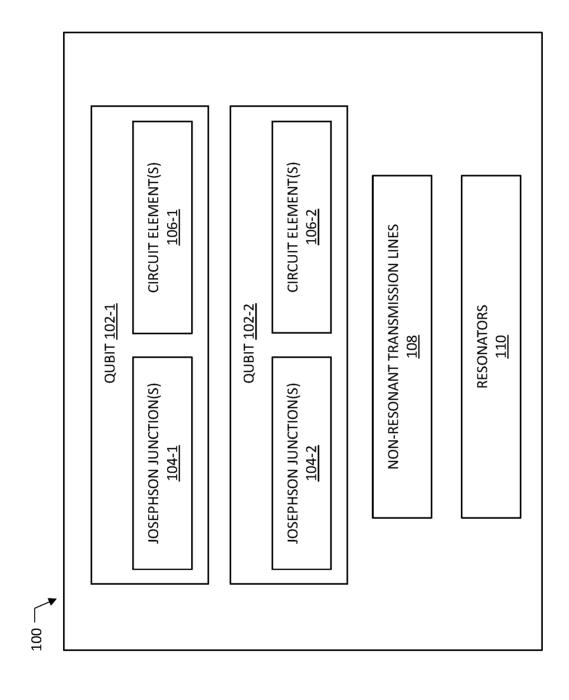

**[0007]** FIGS. 2A-2C provide a schematic illustration of a photoresist mask provided over a substrate for fabricating a Josephson Junction using a double-angle shadow evaporation approach.

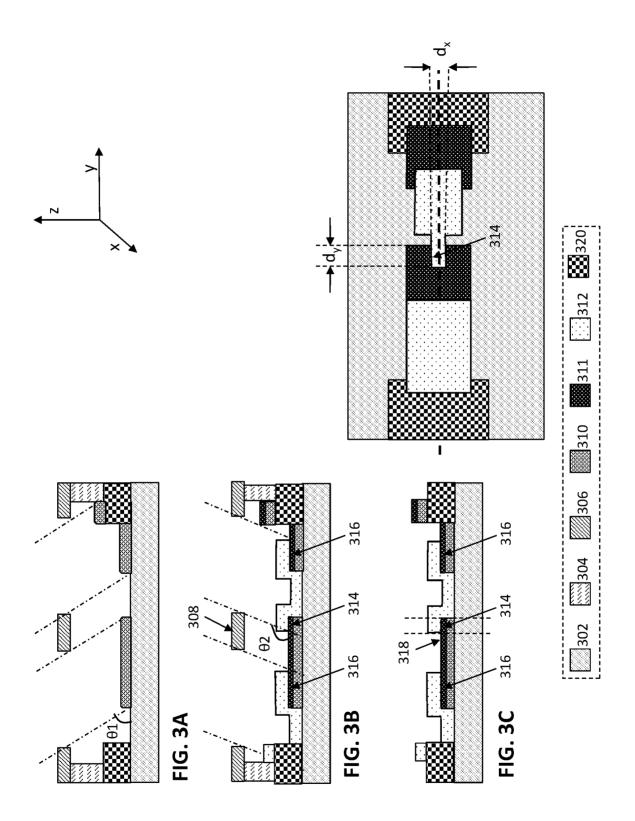

**[0008]** FIGS. 3A-3C provide a schematic illustration of fabricating Josephson Junctions using a conventional double-angle shadow evaporation approach.

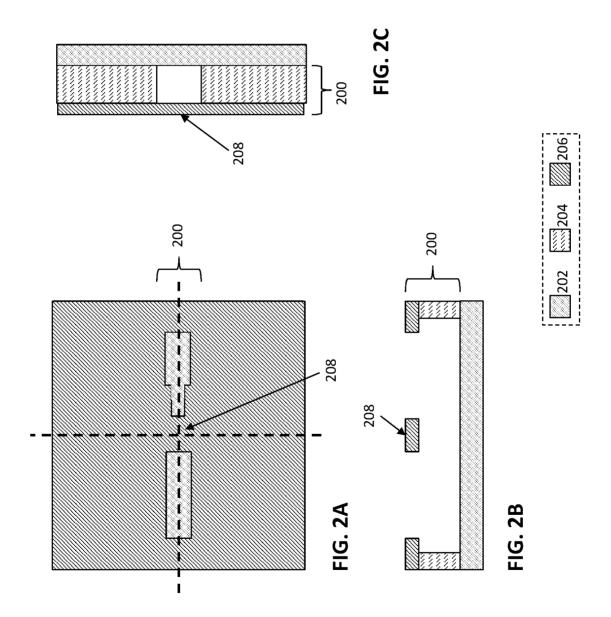

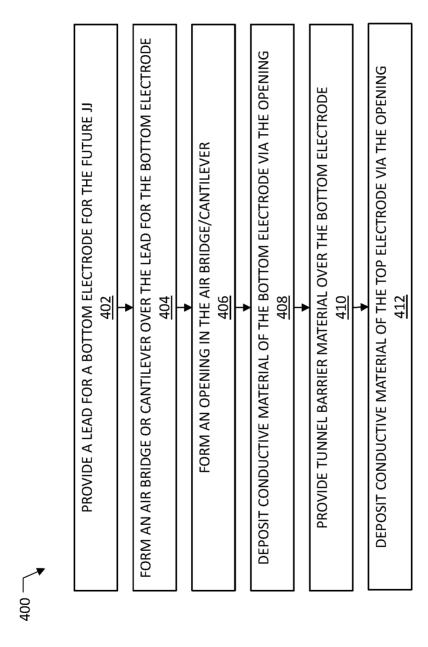

[0009] FIG. 4 provides a flow chart of an air bridge/cantilever method for fabricating Josephson Junctions for quantum circuit assemblies, according to some embodiments of the present disclosure.

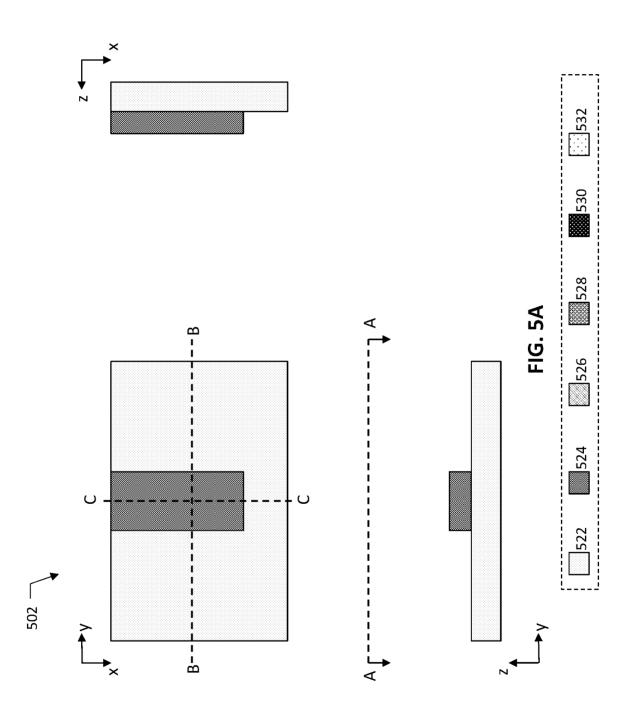

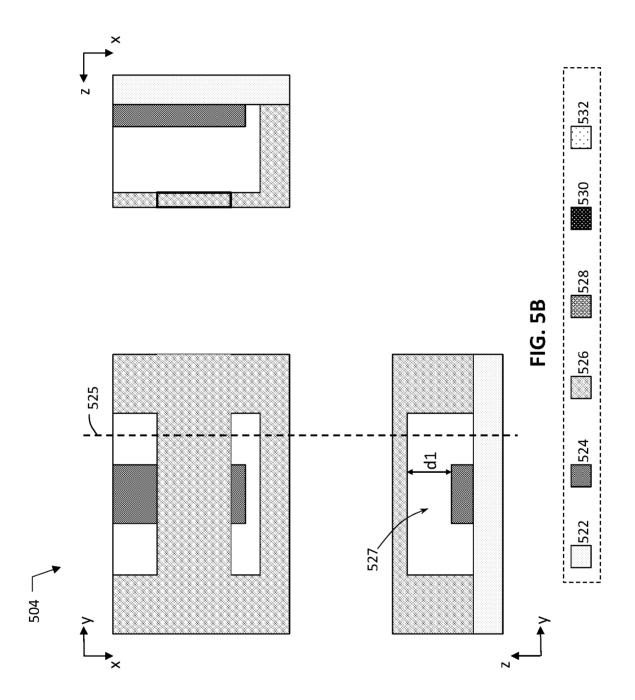

**[0010]** FIGS. 5A-5F are cross-sections illustrating various exemplary stages in the manufacture of a quantum circuit assembly using the air bridge/cantilever method of FIG. 4, in accordance with various embodiments of the present disclosure.

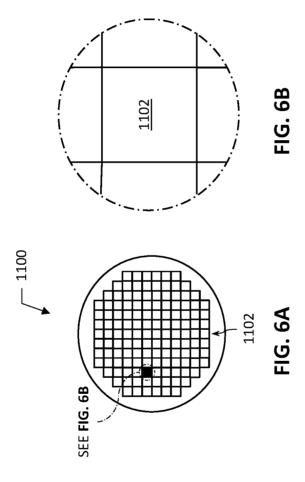

[0011] FIGS. 6A and 6B are top views of a wafer and dies that may include one or more of quantum circuit assemblies disclosed herein.

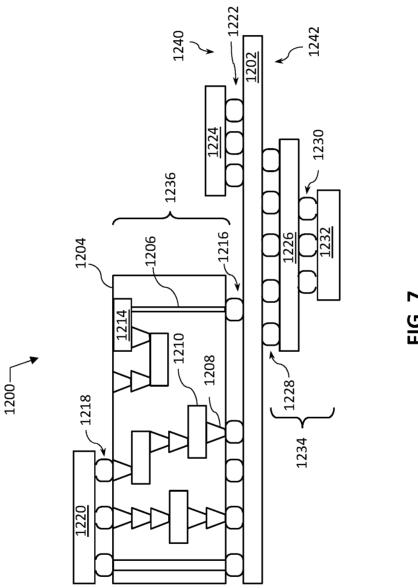

**[0012]** FIG. 7 is a cross-sectional side view of a device assembly that may include one or more of quantum circuit assemblies disclosed herein.

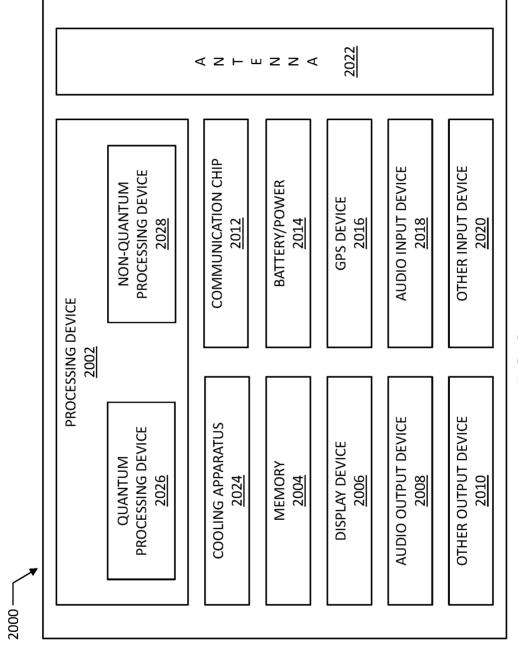

**[0013]** FIG. 8 is a block diagram of an exemplary quantum computing device that may include one or more of quantum circuit assemblies disclosed herein, in accordance with various embodiments.

## **Detailed Description**

## <u>Overview</u>

[0014] As briefly described above, quantum computing, or quantum information processing, refers to the field of research related to computation systems that use quantum-mechanical phenomena to manipulate data. One example of quantum-mechanical phenomena is the principle of quantum superposition, which asserts that any two or more quantum states can be added together, i.e. superposed, to produce another valid quantum state, and that any quantum state can be represented as a sum of two or more other distinct states. Quantum entanglement is another example of quantum-mechanical phenomena. Entanglement refers to groups of particles being generated or interacting in such a way that the state of one particle becomes intertwined with that of the others. Furthermore, the quantum state of each particle cannot be described independently. Instead, the quantum state is given for the group of entangled particles as a whole. Yet another example of quantum-mechanical phenomena is sometimes described as a "collapse" because it asserts that when we observe (measure) particles, we unavoidably change their properties in that, once observed, the particles cease to be in a state of superposition or entanglement (i.e. by trying to ascertain anything about the particles, we collapse their state).

**[0015]** Put simply, superposition postulates that a given particle can be simultaneously in two states, entanglement postulates that two particles can be related in that they are able to instantly coordinate their states irrespective of the distance between them in space and time, and collapse

postulates that when one observes a particle, one unavoidably changes the state of the particle and its' entanglement with other particles. These unique phenomena make manipulation of data in quantum computers significantly different from that of classical computers (i.e. computers that use phenomena of classical physics). Therefore, both the industry and the academics continue to focus on a search for new and improved physical systems whose functionality could approach that expected of theoretically designed qubits.

**[0016]** Physical systems for implementing qubits that have been explored until now include e.g. superconducting qubits, single trapped ion qubits, silicon (Si) quantum dot qubits, photon polarization qubits, etc.

**[0017]** Out of the various physical implementations of qubits listed above, superconducting qubits are promising candidates for building a quantum computer. All of superconducting qubits operate based on the Josephson effect, which refers to a macroscopic quantum phenomenon of supercurrent, i.e. a current that, due to zero electrical resistance, flows indefinitely long without any voltage applied, across a device known as a Josephson Junction.

[0018] Josephson Junctions are integral building blocks in superconducting quantum circuits where they form the basis of quantum circuit elements that can approximate functionality of theoretically designed qubits. Therefore, improvements with respect to fabricating Josephson Junctions for use in quantum circuit assemblies are always desirable. In particular, it would be desirable to have methods for fabricating Josephson Junctions that have adequate performance and can be manufactured on large-scale.

[0019] Embodiments of the present disclosure propose methods of fabricating quantum circuit assemblies that include Josephson Junctions, as well as qubit devices comprising Josephson Junctions. In one aspect of the present disclosure, a method of fabricating a quantum circuit assembly with at least one Josephson Junction is disclosed. The disclosed method is based on providing a structure that forms a bridge or a cantilever over a lead for the bottom electrode of a future Josephson Junction, thus giving rise to the name "air bridge/cantilever method" used herein to describe this method. The air bridge/cantilever method further includes forming an opening in the bridge/cantilever so that the opening is above the lead for the bottom electrode, and then depositing bottom and top electrode materials, as well as the tunnel barrier material for the Josephson Junction, through the opening. Such a method may result in Josephson Junctions having an improved performance compared to Josephson Junctions fabricated using existing techniques, e.g. because it may help decrease amount of spurious (i.e. unintentional and undesirable) two-level systems (TLS's), thought to be the dominant source of superconducting qubit decoherence, in the vicinity of Josephson Junctions. In addition, such a method may be efficiently used in large-scale

manufacturing, providing a substantial improvement with respect to conventional approaches, such as e.g. double-angle shadow evaporation approach, which include fabrications steps that are not suitable for implementing with larger wafer sizes used by leading edge device manufactures. [0020] In order to provide substantially lossless connectivity to, from, and between the qubits, some or all of the electrically conductive portions of various quantum circuit elements described herein (e.g. electrodes of Josephson Junctions and leads to such electrodes) may be made from one or more superconductive materials. However, some or all of these electrically conductive portions could be made from electrically conductive materials which are not superconductive. In the following, unless specified otherwise, reference to an electrically conductive material or circuit element implies that a superconductive material can be used, and vice versa (i.e. reference to a superconductor implies that a conductive material which is not superconductive may be used). Furthermore, any material described herein as a "superconductive/superconducting material" may refer to one or more materials, including alloys of materials, which exhibit superconducting behavior at typical qubit operating conditions (e.g. materials which exhibit superconducting behavior at very low temperatures at which qubits typically operate), but which may not exhibit such behavior at higher temperatures (e.g. at room temperatures). Examples of such materials include aluminum (Al), niobium (Nb), niobium nitride (NbN), titanium nitride (TiN), niobium titanium nitride (NbTiN), indium (In), and molybdenum rhenium (MoRe), all of which are particular types of superconductors at qubit operating temperatures, as well as their alloys.

[0021] While some descriptions are provided with reference to superconducting qubits, in particular to transmons, a particular class of superconducting qubits, at least some teachings of the present disclosure may be applicable to implementations of any qubits, including superconducting qubits other than transmons and/or including qubits other than superconducting qubits, which may employ non-linear inductive elements, such as Josephson Junctions, all of which implementations are within the scope of the present disclosure. For example, the quantum circuit device assemblies described herein may be used in hybrid semiconducting-superconducting quantum circuits.

**[0022]** In the following detailed description, reference is made to the accompanying drawings that form a part hereof, and in which is shown, by way of illustration, embodiments that may be practiced. It is to be understood that other embodiments may be utilized and structural or logical changes may be made without departing from the scope of the present disclosure. Therefore, the following detailed description is not to be taken in a limiting sense.

**[0023]** In the drawings, some schematic illustrations of exemplary structures of various devices and assemblies described herein may be shown with precise right angles and straight lines, but it is to be understood that such schematic illustrations may not reflect real-life process limitations which may

cause the features to not look so "ideal" when any of the structures described herein are examined using e.g. scanning electron microscopy (SEM) images or transmission electron microscope (TEM) images. In such images of real structures, possible processing defects could also be visible, such as e.g. not-perfectly straight edges of materials, tapered vias or other openings, inadvertent rounding of corners or variations in thicknesses of different material layers, occasional screw, edge, or combination dislocations within the crystalline region, and/or occasional dislocation defects of single atoms or clusters of atoms. There may be other defects not listed here but that are common within the field of device fabrication.

[0024] Various operations may be described as multiple discrete actions or operations in turn in a manner that is most helpful in understanding the claimed subject matter. However, the order of description should not be construed as to imply that these operations are necessarily order dependent. In particular, these operations may not be performed in the order of presentation. Operations described may be performed in a different order from the described embodiment. Various additional operations may be performed, and/or described operations may be omitted in additional embodiments.

[0025] For the purposes of the present disclosure, the phrase "A and/or B" means (A), (B), or (A and B). For the purposes of the present disclosure, the phrase "A, B, and/or C" means (A), (B), (C), (A and B), (A and C), (B and C), or (A, B, and C). The term "between," when used with reference to measurement ranges, is inclusive of the ends of the measurement ranges. As used herein, the notation "A/B/C" means (A), (B), and/or (C).

[0026] The description uses the phrases "in an embodiment" or "in embodiments," which may each refer to one or more of the same or different embodiments. Furthermore, the terms "comprising," "including," "having," and the like, as used with respect to embodiments of the present disclosure, are synonymous. The disclosure may use perspective-based descriptions such as "above," "below," "top," "bottom," and "side"; such descriptions are used to facilitate the discussion and are not intended to restrict the application of disclosed embodiments. The accompanying drawings are not necessarily drawn to scale. Unless otherwise specified, the use of the ordinal adjectives "first," "second," and "third," etc., to describe a common object, merely indicate that different instances of like objects are being referred to, and are not intended to imply that the objects so described must be in a given sequence, either temporally, spatially, in ranking or in any other manner.

[0027] The terms "over," "under," "between," and "on" as used herein refer to a relative position of one material layer or component with respect to other layers or components. For example, one layer disposed over or under another layer may be directly in contact with the other layer or may have one or more intervening layers. Moreover, one layer disposed between two layers may be

directly in contact with the two layers or may have one or more intervening layers. In contrast, a first layer "on" a second layer is in direct contact with that second layer. Similarly, unless explicitly stated otherwise, one feature disposed between two features may be in direct contact with the adjacent features or may have one or more intervening layers.

[0028] In the following detailed description, various aspects of the illustrative implementations will be described using terms commonly employed by those skilled in the art to convey the substance of their work to others skilled in the art. For example, the terms "oxide," "carbide," "nitride," etc. refer to compounds containing, respectively, oxygen, carbon, nitrogen, etc. The terms "substantially," "close," "approximately," "near," and "about," generally refer to being within +/- 20% of a target value based on the context of a particular value as described herein or as known in the art. Similarly, terms indicating orientation of various elements, such as e.g. "coplanar," "perpendicular," "orthogonal," "parallel," or any other angle between the elements, generally refer to being within +/- 5-10% of a target value based on the context of a particular value as described herein or as known in the art. Furthermore, as used herein, terms indicating what may be considered an idealized behavior, such as e.g. "superconducting" or "lossless", are intended to cover functionality that may not be exactly ideal but is within acceptable margins for a given application. For example, a certain level of loss, either in terms of non-zero electrical resistance or non-zero amount of spurious TLS's may be acceptable such that the resulting materials and structures may still be referred to by these "idealized" terms. Specific values associated with an acceptable level of loss are expected to change over time as fabrication precision will improve and as fault-tolerant schemes may become more tolerant of higher losses, all of which are within the scope of the present disclosure.

[0029] Still further, while the present disclosure may include references to microwave signals, this is done only because current qubits are designed to work with such signals because the energy in the microwave range is higher than thermal excitations at the temperature that qubits are typically operated at. In addition, techniques for the control and measurement of microwaves are well known. For these reasons, typical frequencies of qubits are in 1-10 GHz, e.g. in 4-10 GHz, range, in order to be higher than thermal excitations, but low enough for ease of microwave engineering. However, advantageously, because excitation energy of qubits is controlled by the circuit elements, qubits can be designed to have any frequency. Therefore, in general, qubits could be designed to operate with signals in other ranges of electromagnetic spectrum and embodiments of the present disclosure could be modified accordingly. All of these alternative implementations are within the scope of the present disclosure.

## **Quantum computing and Josephson Junctions**

[0030] FIG. 1 provides a schematic illustration of an exemplary superconducting quantum circuit 100 that may include any of the quantum circuit assemblies described herein.

[0031] As shown in FIG. 1, an exemplary superconducting quantum circuit 100 may include two or more qubits 102 (reference numerals following after a dash, such as e.g. qubit 102-1 and 102-2 indicate different instances of the same or analogous element). Each of the superconducting qubits 102 may include one or more Josephson Junctions 104 electrically connected to one or more other circuit elements 106, which, in combination with the Josephson Junction(s) 104, form a non-linear circuit providing a unique two-level quantum state for the qubit. In general, a Josephson Junction includes two superconductors coupled by a so-called weak link that weakens the superconductivity between the two superconductors. In some embodiments, weak links of Josephson Junctions may be implemented by e.g. providing a thin layer of an insulating or a semiconducting material, typically referred to as a "barrier" or a "tunnel barrier," sandwiched, in a stack-like arrangement, between two layers of superconductor, which two superconductors typically referred to, respectively, as a "bottom/base electrode" and a "top electrode" of a Josephson Junction. Josephson Junction provides a non-linear inductive element to the circuit and allows the qubit to become an anharmonic oscillator. The anharmonicity is determined by the ratio of the charging energy, which stems from the total capacitance between a first and second element of the qubit, and the Josephson energy of the non-linear inductive element (e.g., Josephson Junction). The anharmonicity is what allows the state of the qubit to be controlled to a high level of fidelity. In addition to controlling the anharmonicity, the charging and Josephson energies also control the qubit frequency. [0032] Typically, when a qubit employs only one Josephson Junction, a frequency of the qubit cannot be changed substantially beyond what is defined by the design unless one of the qubit capacitive elements is tunable. Employing two or more Josephson Junctions, e.g. arranged in a socalled superconducting quantum interference device (SQUID), allows controlling the frequency of the qubit, which, in turn, allows greater control as to whether and when the qubit interacts with other components of a quantum circuit, e.g. with other qubits. In general, a SQUID of a superconducting qubit includes a pair of Josephson Junctions and a loop of a conductive, typically superconductive material (i.e. a superconducting loop), connecting a pair of Josephson Junctions. Applying a net magnetic field in a certain orientation to the SQUID loop of a superconducting qubit allows controlling the frequency of the qubit. In particular, applying magnetic field to the SQUID region of a superconducting qubit is generally referred to as a "flux control" of a qubit, and the magnetic field is generated by providing direct current (DC) or a pulse of current through an

electrically conductive or superconductive line generally referred to as a "flux bias line" (also known

as a "flux line" or a "flux coil line"). By providing flux bias lines sufficiently close to SQUIDs, magnetic fields generated as a result of currents running through the flux bias lines extend to the SQUIDs, thus tuning qubit frequencies.

[0033] Turning back to FIG. 1, within each qubit 102, the one or more Josephson Junctions 104 may be directly electrically connected to one or more other circuit elements 106, which, in combination with the Josephson Junction(s) 104, form a non-linear oscillator circuit providing multi-level quantum system where the first two to three levels define the qubit under normal operation. The circuit elements 106 could be e.g. shunt capacitors, superconducting loops of a SQUID, electrodes for setting an overall capacitance of a qubit, or/and ports for capacitively coupling the qubit to one or more of a readout resonator, a coupling resonator, and a direct microwave drive line, or electromagnetically coupling the qubit to a flux bias line.

[0034] As also shown in FIG. 1, an exemplary quantum circuit 100 typically includes a plurality of non-resonant transmission lines 108, and a plurality of resonators 110. The non-resonant transmission lines 108 are typically used for providing microwave signals to different quantum circuit elements and components, such as e.g. various control lines for various qubits, and may be considered to implement external control of qubits. For example, for superconducting qubits, examples of the non-resonant transmission lines 108 include flux bias lines, microwave lines, and readout lines. On the other hand, the resonators 110 may be viewed as implementing internal control lines for qubit. For superconducting qubits, examples of the resonators 100 include coupling and readout resonators.

[0035] In general, a resonator 110 of a quantum circuit differs from a non-resonant microwave transmission line 108 in that a resonator is deliberately designed to support resonant oscillations (i.e. resonance), under certain conditions. In contrast, non-resonant transmission lines may be similar to conventional microwave transmission lines in that they are designed to avoid resonances, especially resonances at frequencies/wavelengths close to the resonant frequencies/wavelengths of any resonant object used in the quantum computing circuits, e.g., qubits, bus resonators, or readout resonators in the proximity of such non-resonant lines. Once non-resonant transmission lines are manufactured, some of them may inadvertently support some resonances, but, during its design, efforts are taken to minimize resonances, standing waves, and reflected signals as much as possible, so that all of the signals can be transmitted through these lines without, or with as little resonance as possible.

[0036] On-chip capacitive coupling between quantum or control elements can be achieved either through use of coupling components such as a coupling component on a neighboring qubit, a lumped element capacitor, a lumped element resonator, or a transmission line segment. A

transmission line segment is a resonator that is made by employing fixed boundary conditions, and these boundary conditions control the frequencies/wavelengths which will resonate within a given transmission line segment used to implement a resonator. In order to satisfy boundary conditions for resonance, each end of a transmission line segment resonator can be either a node, if it is shorted to ground (e.g. where one end of the transmission line segment structure is electrically connected to a ground plane), or an antinode, if it is capacitively or inductively coupled to ground or to another quantum circuit element. Thus, resonators 110 differ from non-resonant microwave transmission lines 108 in how these lines are terminated at the relevant ends. A line used to route a signal on a substrate, i.e. one of the non-resonant transmission lines 108, typically extends from a specific source, e.g. a bonding pad or another type of electrical connection to a source, to a specific load (e.g. a short circuit proximate to SQUID loop, a quantum dot device, another bonding pad, or another electrical connection to a load). In other words, non-resonant transmission lines 108 terminate with direct electrical connections to sources, ground sinks, and/or loads. On the other hand, a transmission line resonator is typically composed of a piece of transmission line terminated with either two open circuits (in case of a half-wavelength resonator) or an open and a short circuit (in case of a quarter-wavelength resonator). In this case, for a desired resonant frequency, transmission line length may e.g. be a multiple of a microwave wavelength divided by 2 or 4, respectively. However, other terminations are possible, for example capacitive or inductive, and in this case the required line length to support resonance will be different from that identified above. For example, capacitive terminations may be used for resonators which are coupled to qubits, to a feedline, line, or to another resonator by a capacitive interaction.

[0037] Besides line termination by capacitive or inductive coupling or a short circuit, in order to support resonant oscillations, transmission line segments of the resonators 110 need to be of a specific length that can support such oscillations. That is why, often times, resonators 110 may be laid out on a substrate longer than the actual distance would require (i.e. a non-resonant transmission line would typically be laid out to cover the distance in the most compact manner possible, e.g. without any curves, wiggles, or excess length, while a resonator may need to have curves, wiggles, and be longer than the shortest distance between the two elements the resonator is supposed to couple in order to be sufficiently long to support resonance).

**[0038]** One type of the resonators 110 used with superconducting qubits are so-called coupling resonators (also known as "bus resonators"), which allow one method to couple different qubits together in order to realize quantum logic gates. These types of resonators are analogous in concept and have analogous underlying physics as readout resonators, except that a coupling or "bus" resonator involves only capacitive couplings between two or more qubits whereas a readout

resonator involves capacitive coupling between two or more qubits and a feedline. A coupling resonator may be implemented as a microwave transmission line segment that includes capacitive or inductive connections to ground on both sides (e.g. a half-wavelength resonator), which results in oscillations (resonance) within the transmission line. While the ends of a coupling resonator have open circuits to the ground, each side of a coupling resonator is coupled, either capacitively or inductively, to a respective (i.e. different) qubit by being in the appropriate location and sufficient proximity to the qubit. Because different regions of a coupling resonator have coupling with a respective different qubit, the two qubits are coupled together through the coupling resonator. Thus, coupling resonators may be employed for implementing logic gates.

[0039] Another type of the resonators 110 used with superconducting qubits are so-called readout resonators, which may be used to read the state(s) of qubits. In some embodiments, a corresponding readout resonator may be provided for each qubit. A readout resonator, similar to the bus coupling resonator, is a transmission line segment. On one end it may have an open circuit connection to ground as well as any capacitively or inductively coupled connections to other quantum elements or a non-resonant microwave feedline. On the other end, a readout resonator may either have a capacitive connection to ground (for a half-wavelength resonator) or may have a short circuit to the ground (for a quarter-wavelength resonator), which also results in oscillations within the transmission line, with the resonant frequency of the oscillations being close to the frequency of the qubit. A readout resonator is coupled to a qubit by being in the appropriate location and sufficient proximity to the qubit, again, either through capacitive or inductive coupling. Due to a coupling between a readout resonator and a qubit, changes in the state of the qubit result in changes of the resonant frequency of the readout resonator. In turn, changes in the resonant frequency of the readout resonator. In turn, changes in the external electronics e.g. wire or solder bonding pads.

[0040] For the non-resonant transmission lines 108, some descriptions of flux bias lines were provided above and, in the interests of brevity are not repeated here. In general, running a current through a flux bias line, provided e.g. from a wirebonding pads or any other connection element, allows tuning (i.e. changing) the frequency of a corresponding qubit 102 to which a given flux bias line is connected. As a result of running the current in a given flux bias line, magnetic field is created around the line. If such a magnetic field is in sufficient proximity to a given qubit 102, e.g. by a portion of the flux bias line being provided next (sufficiently close) to the qubit 102, the magnetic field couples to the qubit, thereby changing the spacing between the energy levels of the qubit. This, in turn, changes the frequency of the qubit since the frequency is directly related to the spacing between the energy levels via the equation E=hv (Planck's equation), where E is the energy (in this

case the energy difference between energy levels of a qubit), h is the Planck's constant and v is the frequency (in this case the frequency of the qubit). As this equation illustrates, if E changes, then v changes. Different currents and pulses of currents can be sent down each of the flux lines allowing for independent tuning of the various qubits.

[0041] Typically, the qubit frequency may be controlled in order to bring the frequency either closer to or further away from another resonant item, for example a coupling resonator or a coupled neighbor qubit, to implement multi-qubit interactions, as may be desired in a particular setting. [0042] For example, if it is desirable that a first qubit 102-1 and a second qubit 102-2 interact, via a coupling resonator (i.e. an example of the resonators 110) connecting these qubits, then both qubits 102 may need to be tuned to be at nearly the same frequency or a detuning equal, or nearly equal, to the anharmonicity. One way in which such two qubits could interact is that, if the frequency of the first qubit 102-1 is tuned very close to the resonant frequency of the coupling resonator, the first qubit can, when in the excited state, relax back down to the ground state by emitting a photon (similar to how an excited atom would relax) that would resonate within the coupling resonator. If the second qubit 102-2 is also at this energy (i.e. if the frequency of the second qubit is also tuned very close to the resonant frequency of the coupling resonator), then it can absorb the photon emitted from the first qubit, via the coupling resonator coupling these two qubits, and be excited from its ground state to an excited state. Thus, the two qubits interact, or are entangled, in that a state of one qubit is controlled by the state of another qubit. In other scenarios, two qubits could interact via exchange of virtual photons, where these three elements do not have to be tuned to be at the same frequency with one another. In general, two or more qubits could be configured to interact with one another by tuning their frequencies to specific values or ranges.

**[0043]** On the other hand, it may sometimes be desirable that two qubits coupled by a coupling resonator do not interact, i.e. the qubits are independent. In this case, by applying magnetic flux, by means of controlling the current in the appropriate flux bias line, to one qubit it is possible to cause the frequency of the qubit to change enough so that the photon it could emit no longer has the right frequency to resonate on the coupling resonator or on the neighboring qubit via a virtual photon transfer through the bus. If there is nowhere for such a frequency-detuned photon to go, the qubit will be better isolated from its surroundings and will live longer in its current state. Thus, in general, two or more qubits could be configured to reduce interactions with one another by tuning their frequencies to specific values or ranges.

**[0044]** The state(s) of each qubit 102 may be read by way of its corresponding readout resonator of the resonators 110. As explained below, the state of qubit 102 induces a shift in the resonant frequency in the associated readout resonator. This shift in resonant frequency can then be read

out using its coupling to a feedline. To that end, an individual readout resonator may be provided for each qubit. As described above, a readout resonator may be a transmission line segment that includes a capacitive connection to ground on one side and is either shorted to the ground on the other side (for a quarter-wavelength resonator) or has a capacitive connection to ground (for a half-wavelength resonator), which results in oscillations within the transmission line (resonance) that depends upon the state of a proximal qubit. A readout resonator may be coupled to its corresponding qubit 102 by being in an appropriate location and sufficient proximity to the qubit, more specifically in an appropriate location and sufficient proximity to a first element (or "island) of the qubit 102 that capacitively couples to the readout resonator, when the qubit is implemented as a transmon. Due to a coupling between the readout resonator and the qubit, changes in the state of the qubit result in changes of the resonant frequency of the readout resonator. In turn, by ensuring that the readout resonator is in sufficient proximity to a corresponding microwave feedline, changes in the resonant frequency of the readout resonator induce changes in the transmission coefficients of the microwave feedline, detected externally.

[0045] A coupling resonator, or, more generally, a coupling component, allows coupling different qubits together, e.g. as described above, in order to realize quantum logic gates. A coupling component could be comprised of a coupling component on a neighboring qubit, a lumped element capacitor, a lumped element resonator, or a coupling transmission line segment. A coupling transmission line segment (e.g., coupling resonator or bus resonator) is similar to a readout resonator in that it is a transmission line segment that includes capacitive connections to various objects (e.g., qubits, ground, etc.) on both sides (i.e. a half-wavelength resonator), which also results in oscillations within the coupling resonator. Each side/end of a coupling component is coupled (again, either capacitively or inductively) to a respective qubit by being in appropriate location and sufficient proximity to the qubit, namely in sufficient proximity to a first element (or "island") of the qubit that capacitively couples to the coupling component, when the qubit is implemented as a transmon. Because each side of a given coupling component has coupling with a respective different qubit, the two qubits are coupled together through the coupling component. Thus, coupling components may be employed in order to implement multi-qubit interactions.

**[0046]** In some implementations, a microwave line may be used to not only readout the state of the qubits as described above, but also to control the state of the qubits. When a single microwave line is used for this purpose, the line operates in a half-duplex mode where, at some times, it is configured to readout the state of the qubits, and, at other times, it is configured to control the state of the qubits. In other implementations, microwave lines may be used to only readout the state of the qubits as described above, while separate drive lines, may be used to control the state of the

qubits. In such implementations, microwave lines used for readout may be referred to as readout lines, while microwave lines used for controlling the state of the qubits may be referred to as drive lines. Drive lines may control the state of their respective qubits 102 by providing to the qubits a microwave pulse at the qubit frequency, which in turn stimulates (i.e. triggers) a transition between the states of the qubit. By varying the length of this pulse, a partial transition can be stimulated, giving a superposition of the states of the qubit.

[0047] Flux bias lines, microwave lines, readout lines, drive lines, coupling components, and readout resonators, such as e.g. those described above, together form interconnects for supporting propagation of microwave signals. Further, any other connections for providing direct electrical interconnection between different quantum circuit elements and components, such as e.g. connections from electrodes of Josephson Junctions to plates of the capacitors or to superconducting loops of SQUIDs or connections between two ground lines of a particular transmission line for equalizing electrostatic potential on the two ground lines, may also be referred to as interconnects. Still further, the term "interconnect" may also be used to refer to elements providing electrical interconnections between quantum circuit elements and components and non-quantum circuit elements, which may also be provided in a quantum circuit, as well as to electrical interconnections between various non-quantum circuit elements provided in a quantum circuit. Examples of non-quantum circuit elements which may be provided in a quantum circuit may include various analog and/or digital systems, e.g. analog to digital converters, mixers, multiplexers, amplifiers, etc.

[0048] In various embodiments, various conductive circuit elements of supporting circuitry included in a quantum circuit such as the quantum circuit 100 could have different shapes and layouts. In general, the term "line" as used herein in context of signal lines or transmission lines does not imply straight lines, unless specifically stated so. For example, some resonant or non-resonant transmission lines or parts thereof (e.g. conductor strips of resonant or non-resonant transmission lines) may comprise more curves, wiggles, and turns while other resonant or non-resonant transmission lines or parts thereof may comprise less curves, wiggles, and turns, and some transmission lines or parts thereof may comprise substantially straight lines. At least some of the Josephson Junctions 104 included within the qubits 102 shown in FIG. 1 may be fabricated according to various embodiments of the improved method described herein.

**[0049]** The qubits 102, the non-resonant transmission lines 108, and the resonators 110 of the quantum circuit 100 may be provided on, over, or at least partially embedded in a substrate (not shown in FIG. 1). The substrate may be any substrate suitable for realizing quantum circuit assemblies described herein. In one implementation, the substrate may be a crystalline substrate

such as, but not limited to a silicon or a sapphire substrate, and may be provided as a wafer or a portion thereof. In other implementations, the substrate may be non-crystalline. In general, any material that provides sufficient advantages (e.g. sufficiently good electrical isolation and/or ability to apply known fabrication and processing techniques) to outweigh the possible disadvantages (e.g. negative effects of spurious TLS's), and that may serve as a foundation upon which a quantum circuit may be built, falls within the spirit and scope of the present disclosure. Additional examples of substrates include silicon-on-insulator (SOI) substrates, III-V substrates, and quartz substrates.

[0050] In various embodiments, quantum circuits such as the one shown in FIG. 1 may be used to implement components associated with a quantum integrated circuit (IC). Such components may include those that are mounted on or embedded in a quantum IC, or those connected to a quantum IC. The quantum IC may be either analog or digital and may be used in a number of applications within or associated with quantum systems, such as e.g. quantum processors, quantum amplifiers, quantum sensors, etc., depending on the components associated with the IC. The IC may be employed as part of a chipset for executing one or more related functions in a quantum system.

\*\*Josephson Junctions fabricated using double-angle shadow evaporation\*\*

**[0051]** In order to highlight the advantages offered by novel quantum circuit assemblies fabricated using the air bridge/cantilever method proposed herein, it would be helpful to first explain how Josephson Junctions are fabricated using the double-angle shadow evaporation (also sometimes referred to as a "hanging resist" method) in conventional quantum circuits.

[0052] In summary, the name "double-angle shadow evaporation" reflects the fact that the method involves metal deposition, typically carried out by metal evaporation, at two different angles of incidence with respect to the substrate (hence, double-angle). The name further reflects the fact that metal deposition is performed through a hanging photoresist mask which casts a shadow on at least a part of the substrate, obscuring metal deposition on that part (hence, shadow evaporation/evaporation).

[0053] FIGS. 2A-2C provide a schematic illustration of one example of a photoresist mask 200 provided over a substrate 202 for fabricating Josephson Junctions using a double-angle shadow evaporation approach. Each of FIGS. 2A-2C provides a view of the same photoresist mask 200 over the substrate 202, but perspectives of these views are different. FIG. 2A provides a top down view (i.e. a view from a point above the substrate 202). FIG. 2B provides a cross-sectional view with a cross-section of the structure of FIG. 2A taken along a horizontal dashed line shown in FIG. 2A. Finally, FIG. 2C provides a cross-sectional view with a cross-section of the structure of FIG. 2A taken along a vertical dashed line shown in FIG. 2A. A legend provided within a dashed box at the bottom

of FIGS. 2A-2C illustrates patterns used to indicate different elements shown in FIGS. 2A-2C, so that the FIGs are not cluttered by many reference numerals.

[0054] Josephson Junctions may be created by a double-angle shadow evaporation approach using a two-layer photoresist mask 200 that includes a bottom photoresist layer 204 and a top photoresist layer 206 as shown in FIGS. 2A-2C. The bottom layer 204 is undercut from the top layer 206 in that some portions of the top layer 206 hang, or are suspended, over the bottom layer 204. The bottom layer 204 is undercut in such a manner that the top layer 206 of photoresist forms a suspended bridge 208, known as a Dolan bridge, over a section of the substrate 202. Ways for fabricating such undercuts in photoresist are well known in the art of photolithographic processing and, therefore, are not described here in detail.

[0055] In order to form a Josephson Junction, metals are then deposited through the photoresist mask 200 with the suspended bridge. Conventionally, this is done as illustrated in FIGS. 3A-3C. [0056] Each of FIGS. 3A-3C illustrates a result of different subsequent fabrication steps. FIG. 3C provides two views of the same structure. The view on the right side of FIG. 3C is a top down view (i.e. a view similar to that shown in FIG. 2A). The view on the left side of FIG. 3C is a cross-sectional view with a cross-section of the structure of FIG. 3C taken along a horizontal dashed line shown in FIG. 3C (i.e. a view similar to that shown in FIG. 2B). Each of FIGS. 3A and 3B only provide a crosssectional view similar to that of the left side of FIG. 3C but at an earlier fabrication step. Similar to FIGS. 2A-2C, a legend provided within a dashed box at the bottom of FIGS. 3A-3C illustrates patterns used in the figures to indicate different elements shown in FIGS. 3A-3C. Moreover, similar reference numerals in FIGS. 2A-2C and FIGS. 3A-3C are used to illustrate analogous elements in the figures. For example, reference numerals 202 and 302, shown, respectively, in FIGS. 2 and 3 refer to a substrate, reference numerals 204 and 304 - to a bottom mask layer, and so on. When provided with reference to one of the FIGS. 2A-2C and FIGS. 3A-3C, discussions of these elements are applicable to other figures, unless stated otherwise. Thus, in the interests of brevity, discussions of similar elements are not repeated for each of the figures but, rather, the differences between the figures are described. [0057] As previously described herein, a Josephson Junction may include a thin layer of dielectric sandwiched between two layers of superconductors, the dielectric layer acting as the barrier in a superconducting tunnel junction. According to the double-angle shadow evaporation approach, such a device is conventionally fabricated by, first, depositing a layer of a first superconductor 310 on the substrate 302, as shown in FIG. 3A, through the two-layer mask such as e.g. the one shown in FIGS. 2A-2C. The first superconductor is deposited at an angle with respect to the substrate 302, as shown in FIG. 3A with an angle  $\theta$ 1. Slanted dotted-dashed lines in FIG. 3A illustrate the direction of

deposition of the first superconductor 310. A layer of the first superconductor 310 may have a thickness between e.g. about 10 and 200 nanometers (nm), e.g. between about 30 and 100 nm. [0058] The first superconductor 310 forms a bottom (base) electrode of the future Josephson Junction. A layer of insulator 311 (also referred to herein as a "dielectric layer 311" or a "dielectric 311"), shown in FIGs. 3B and 3C, is then provided over the first superconductor 310 to form a tunnel barrier of the future Josephson Junction. The tunnel barrier is formed by oxidizing the first superconductor 310, thus creating a layer of first superconductor oxide on its surface. Such an oxide may have a thickness between e.g. about 1 and 5 nm, typically for qubit applications between about 1 and 2 nm.

[0059] The fact that the choice of a tunnel barrier in a double-angle shadow evaporation method is constrained to an oxide of the base electrode superconductor limits the choice of the superconductor used as the first superconductor 310 in that the superconductor must be such that a controlled layer of oxide may be created on it. In practice, aluminum oxide is the only controlled oxide that may be formed from a metal. Therefore, currently aluminum is the only superconducting metal that is used for the base electrode of Josephson Junctions fabricated using the double-angle shadow evaporation technique.

**[0060]** After the layer of dielectric 311 is provided on the first superconductor 310, a second superconductor 312 is deposited through the mask but at a different angle with respect to the substrate 302 than  $\theta$ 1. FIG. 3B illustrates the second angle as an angle  $\theta$ 2 and slanted dotted-dashed lines in FIG. 3B illustrate the direction of deposition of the second superconductor 312. In some embodiments, the first and the second superconductors 310, 312 are deposited at the opposite angles, if measured with respect to a normal to the substrate 302. Conventionally, the second superconductor 320 is aluminum because the first superconductor must be aluminum, as described above. A layer of the second superconductor 312 may have a thickness between e.g. about 10 and 200 nm, typically between about 30 and 100 nm. The second superconductor 312 forms a counter electrode (i.e. counter to the bottom electrode formed by the first superconductor 310) of the future Josephson Junction, typically referred to as a "top" electrode.

**[0061]** The first and second superconductors 310, 312 are usually deposited using a non-conformal process, such as e.g. evaporative deposition. After deposition of the second superconductor 312, the deposition mask is removed, removing with it any first and/or second superconductor 310, 312 deposited on top of it.

**[0062]** In general, the above-described process of creating patterned structures of one or more target materials (in this case, structures made of the first and second superconductors 310, 312) on the surface of a substrate using a sacrificial material such as photoresist is referred to as a lift-off

method. Lift-off is a type of an additive technique, as opposed to subtracting techniques like etching, and may be applied in cases where a direct etching of structural material would have undesirable effects on one or more layers below.

**[0063]** After the deposition mask is removed, the resulting Josephson Junction is left on the substrate 302 as shown in FIG. 3C as a Josephson Junction 314. The Josephson Junction 314 is formed by the small region of overlap under the photoresist bridge 308 (i.e. the area under the bridge 308 where the first superconductor 310, covered with a layer of a thin insulating material is overlapped by the second superconductor 312). Dimensions of the Josephson Junction 314 along x-axis and y-axis, shown in FIG. 3C as  $d_x$  and  $d_y$ , respectively, are typically between about 50 and 1000 nm for any of  $d_x$  and  $d_y$ .

**[0064]** As a result of performing the double-angle shadow evaporation as described above, junctions of the first and second superconductors may also form on each side of the Josephson Junction 314, such junctions shown in FIGS. 3B and 3C as junctions 316. However, because these junctions are of much larger dimensions than the Josephson Junction 314, e.g. measured several thousands of nm in the x-direction and hundreds of nm or more in the y-direction, they are essentially infinite for the Josephson effect to take place and, therefore, act as superconductors rather than Josephson Junctions.

[0065] One problem with the fabrication approach described above is that it includes steps which

are not suitable for manufacturing on the larger wafer sizes used in the semiconductor industry. For example, angled metal deposition step does not produce a uniform film across the wafer and would prohibit uniform qubit performance across large area. Moreover, the fabrication approach described above relies on lift-off of metal films to produce wires remaining on the wafer. The lift-off technique is not amenable to the chemical waste systems of wafer cleaning tools and would not facilitate high volume manufacturing or even an extension to many qubits on a single wafer. [0066] Another problem with the double-angle shadow evaporation approach is that the resulting Josephson Junction is surrounded by dielectric material on several sides. For example, as shown on the left side (i.e. cross-section) view of FIG. 3C indicating the boundaries of the Josephson Junction 314 with vertical dashed lines, the dielectric 311 that forms the tunnel barrier of the Josephson Junction 314 extends further, outside of the boundaries of the Josephson Junction 314, e.g. into the area 318 immediately adjacent to the Josephson Junction, because the dielectric 311 is provided across the entire bottom superconductor 310. The right side (i.e. top) view of FIG. 3C illustrates that the dielectric material 311 surrounds the Josephson Junction 314 on three of the four sides. As described above, one major source of loss, and thus decoherence in superconducting qubits are spurious TLS's, e.g. those caused by defects in the areas surrounding Josephson Junctions.

Dielectrics surrounding the tunnel barriers and superconductors of Josephson Junctions, such as e.g. the dielectric portions 318 shown in FIG. 3C, may be one of the causes of spurious TLS's, leading to qubit decoherence.

[0067] Yet another problem with the use of the double-angle shadow evaporation approach is that it limits materials which may be employed in forming Josephson Junctions. As described above, Josephson Junctions fabricated the double-angle shadow evaporation approach can only use Al as the superconductor for the base electrode. This may be problematic because interconnects in quantum circuits are typically made from other superconducting materials such as e.g. Nb, TiN and NbTiN and interfaces between the different superconducting materials used for Josephson Junctions and interconnects connected thereto present yet another source of losses. Any losses are especially significant in context of quantum circuits where, sometimes, energy as small as that of a single photon is to be transmitted, making loss tolerance very low.

[0068] An air bridge/cantilever method disclosed herein may improve on at least some of the problems described above.

## <u>Josephson Junctions fabricated using an air bridge or cantilever</u>

[0069] FIG. 4 provides a flow chart of an air bridge/cantilever method 400 for fabricating Josephson Junctions for quantum circuit assemblies, according to some embodiments of the present disclosure. [0070] Although the operations of the method 400 are illustrated in FIG. 4 once each and in a particular order, the operations may be performed in any suitable order and repeated as desired. For example, one or more operations may be performed in parallel to manufacture multiple quantum circuit assemblies as described herein substantially simultaneously. In another example, the operations may be performed in a different order to reflect the architecture of a particular quantum circuit component in which one or more quantum circuit assemblies with Josephson Junctions fabricated according to the air bridge/cantilever method are to be included. [0071] In addition, the exemplary manufacturing method 400 may include other operations not specifically shown in FIG. 4, such as e.g. various cleaning or planarization operations as known in the art. For example, in some embodiments, the substrate may be cleaned prior to or/and after any of the processes of the method 400 described herein, e.g. to remove surface-bound organic and metallic contaminants, as well as subsurface contamination. In some embodiments, cleaning may be carried out using e.g. a chemical solutions (such as peroxide), and/or with ultraviolet (UV) radiation combined with ozone, and/or oxidizing the surface (e.g., using thermal oxidation) then removing the oxide (e.g. using hydrofluoric acid (HF)). In another examples, the structures/assemblies described

herein may be planarized prior to or/and after any of the processes of the method 400 described

herein, e.g. to remove overburden or excess materials. In some embodiments, planarization may be

carried out using either wet or dry planarization processes, e.g. planarization be a chemical mechanical planarization (CMP), which may be understood as a process that utilizes a polishing surface, an abrasive and a slurry to remove the overburden and planarize the surface.

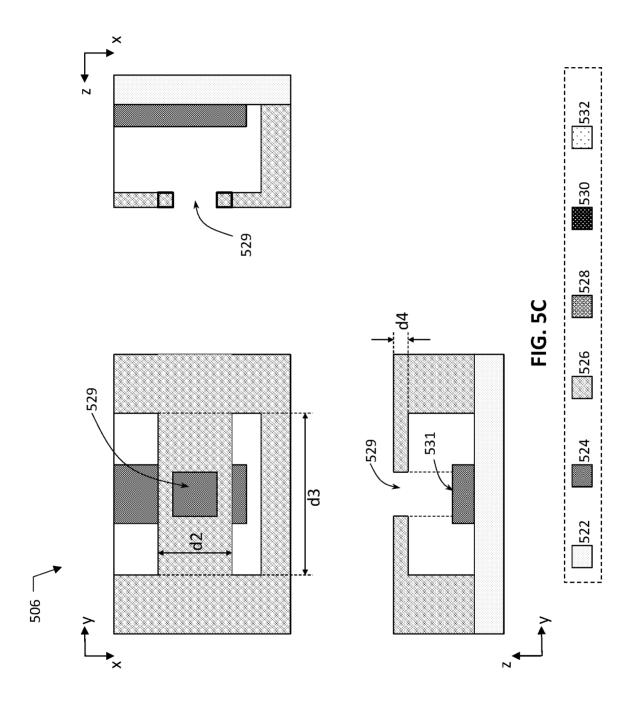

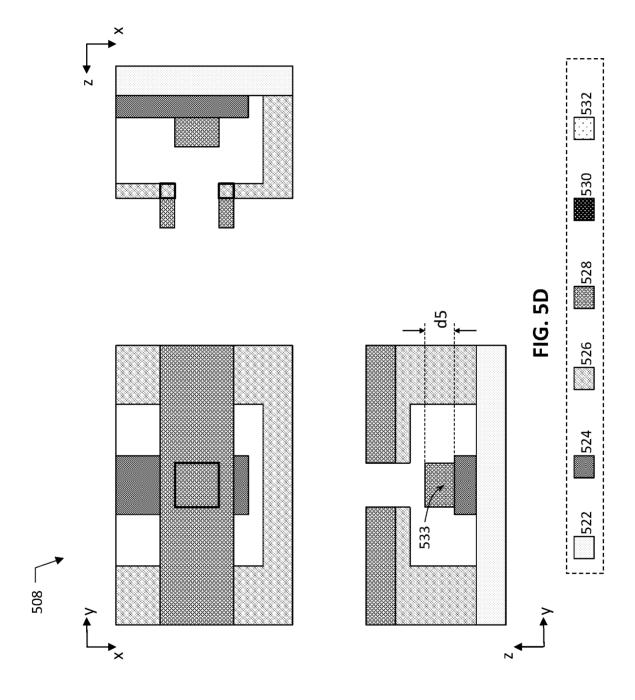

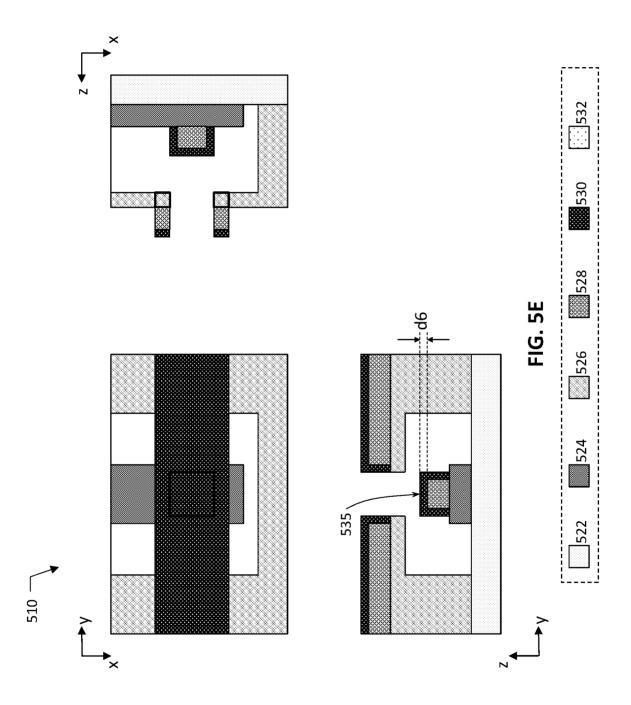

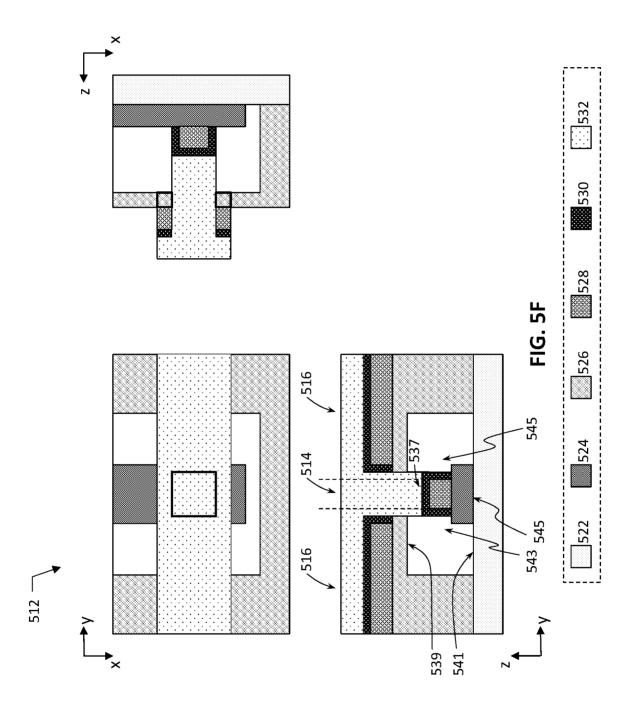

[0072] Various operations of the method 400 may be illustrated with reference to exemplary embodiments shown in FIGS. 5A-5F, but the method 400 may be used to manufacture any suitable quantum circuit assemblies with Josephson Junctions according to any embodiments of the present disclosure. FIGS. 5A-5F are cross-sections illustrating various example stages in the manufacture of a quantum circuit assembly using the air bridge/cantilever method of FIG. 4 in accordance with some embodiments of the present disclosure. Each one of FIGS. 5A-5F illustrates a top down view (top left illustration in each of FIGS. 5A-5F) of the x-y plane of the coordinate system indicated in these FIGS., a first cross-sectional view (bottom left illustration in each of FIGS. 5A-5F) along the z-y plane, and a second cross-sectional view (top right illustration in each of FIGS. 5A-5F) along the x-z plane. Thus, the top down view shown in FIGS. 5A-5F is the view looking down from a plane indicted in FIG. 5A as a plane AA, the first cross-sectional view is a cross-section along a plane indicted in FIG. 5A as a plane BB, and the second cross-sectional view is a cross-section along a plane indicted in FIG. 5A as a plane CC. In FIGS. 5A-5F, same reference numerals refer to the same or analogous elements/materials shown.

[0073] The method 400 may begin with providing, over a substrate, a layer of an electrically conductive material shaped to form a first/bottom electrode lead for the future Josephson Junction (process 402 shown in FIG. 4, a result of which is illustrated with an assembly 502 shown in FIG. 5A). The assembly 502 illustrates a substrate 522, which could be any of the substrates described above, with a first/bottom electrode lead 524 provided over the substrate.

[0074] In various embodiments, the electrically conductive material forming the bottom electrode lead provided in the process 402 may include any conducting or superconducting material suitable for providing electrical connectivity in a quantum circuit, such as e.g. Al, Nb, NbN, NbTiN, TiN, MoRe, etc., or any alloy of two or more superconducting/conducting materials, and a thickness of the bottom electrode lead (i.e. a dimension measured along the z-axis of the coordinate system as shown in FIGS. 5A-5F) provided in the process 402 may be between about 50 and 500 nanometers, including all values and ranges therein, e.g. between about 100 and 250 nm.

**[0075]** In various embodiments, any suitable deposition and patterning techniques may be used for providing the bottom electrode lead 524 in the process 402. Examples of deposition techniques for depositing a layer of an electrically conductive material for forming the bottom electrode lead 524 include atomic layer deposition (ALD), physical vapor deposition (PVD) (e.g. evaporative deposition, magnetron sputtering, or e-beam deposition), chemical vapor deposition (CVD), or electroplating.

Examples of patterning techniques include photolithographic or electron-beam (e-beam) patterning, possibly in conjunction with a dry etch, such as e.g. radio frequency (RF) reactive ion etch (RIE) or inductively coupled plasma (ICP) RIE, to pattern the layer of an electrically conductive material into the bottom electrode lead 524 of the specified geometries for a given implementation.

[0076] The method may then proceed with providing an air bridge or a cantilever of an electrically conductive material over the bottom electrode lead 524 (process 404 shown in FIG. 4, a result of which is illustrated with an assembly 504 shown in FIG. 5B). The assembly 504, as well as the subsequent assemblies shown in FIGS. 5A-5F, illustrates an example of an air bridge 526 formed over a portion of the bottom electrode lead 524. However, illustrations of FIGS. 5A-5F are equally applicable to cantilevers, e.g. a cantilever which would be formed if, looking from the left to the right in the top and first cross-sectional views of FIG. 5B, the air bridge 526 shown there would end at a dashed line 525 (i.e. if there electrically conductive material of the "air bridge" 526 would not be shown to the right of the dashed line 525). Therefore, in the following, the air bridge 526 shown in FIG. 5B and subsequent FIGS. is referred to as an air bridge/cantilever 526.

[0077] In various embodiments, the electrically conductive material forming the air bridge/cantilever 526 provided in the process 404 may include any conducting or superconducting material suitable for providing electrical connectivity in a quantum circuit, such as e.g. any of such materials described above, and may be the same or different from the electrically conductive material of the bottom electrode lead 524. The reason why the air bridge/cantilever 526 is to be formed from an electrically conductive material is because later on the air bridge/cantilever 526 will serve as a top electrode lead for the Josepshon Junction.

[0078] Providing the air bridge/cantilever 526 in the process 404 creates a region 527, indicated in FIG. 5B, above the bottom electrode lead 524, which region may be seen as a partial cavity around the bottom electrode lead 524 where a portion of the air bridge/cantilever 526 is suspended above a portion of the bottom electrode lead 524. In some embodiments, a distance between the suspended portion of the air bridge/cantilever 526 and the bottom electrode lead 524 (i.e. a dimension measured along the z-axis of the coordinate system as shown in FIGS. 5A-5F and indicated in FIG. 5B as a distance "d1") may be between about 50 and 50000 nm, including all values and ranges therein, e.g. between about 100 and 1000 nm, or between about 300 and 500 nm.

[0079] As shown in FIG. 5B, if the bottom electrode lead 524 is provided in a first plane that is

substantially parallel to the plane of the substrate 522, then the suspended portion of the air bridge/cantilever 526 which will later form the top electrode lead for the Josephson Junction is provided in a second plane that is substantially parallel to the plane of the substrate 522, the second plane being further away from the substrate than the first plane. If the suspended portion is then

projected onto the first plane (i.e. the plane of the bottom electrode lead 524), then the bottom electrode lead 524 would be perpendicular to the projection of the suspended portion, in some embodiments of the present disclosure. In other embodiments, the suspended portion of the air bridge/cantilever 526 does not have to be perpendicular to the bottom electrode lead 524, as long as the suspended portion extends sufficiently over the bottom electrode lead 524 to form an opening over the bottom electrode lead 524 in a later fabrication process (namely, in a process 406 of the method 400 shown in FIG. 4). Formation of such an opening will also influence various dimensions of the air bridge/cantilever 526 provided in the process 404. Thus, the air bridge/cantilever 526 provided in the process 404 can be of any dimensions suitable for supporting the opening formed in the process 406, e.g. suitable in terms of having sufficient mechanical stability to remain suspended over the bottom electrode lead 524 during subsequent fabrication processes and, later on, during operation of the assembly. Some such dimensions for the air bridge/cantilever 526 will be described below, together with the dimensions of the opening formed in the process 406.

[0080] In various embodiments, any suitable deposition and patterning techniques may be used for providing the air bridge/cantilever 526 in the process 404, such as e.g. techniques which rely on use of a sacrificial material in order to form the region 527 around the bottom electrode lead 524. One example of such a technique could be to use a sacrificial material to form a structure around the bottom electrode lead 524 of the shape, dimensions, and location of the region 527, then deposit the electrically conductive material of the air bridge/cantilever 526, and then remove the sacrificial material, e.g. by etching, thus creating an open region 527 around the bottom electrode lead 524 as shown in FIG. 5B. In such a technique, the sacrificial material would need to have sufficient etch selectivity with respect to the other materials around, such as e.g. materials of the substrate 522, of the bottom electrode lead 524, or of the air bridge/cantilever 526, so that etching of the sacrificial structure would not substantially etch these other materials. As known in the art, two materials are said to have "sufficient etch selectivity" when etchants used to etch one material do not substantially etch the other, enabling selective etching of one material but not the other. In some embodiments, the sacrificial material which may be used to form the region 527 may be a sacrificial dielectric material, such as e.g. a dielectric material including, or being, one or more of a silicon oxide (i.e. a compound comprising silicon and oxygen, e.g. SiO2), a hafnium oxide (i.e. a compound comprising hafnium and oxygen, e.g. HfO2), a silicon nitride (i.e. a compound comprising silicon and nitrogen, e.g. SiN), a silicon oxynitride (i.e. a compound comprising silicon, oxygen, and nitrogen, e.g. SiON), an aluminum oxide (i.e. a compound comprising aluminum and oxygen, e.g. Al2O3), an aluminum hafnium oxide (i.e. a compound comprising aluminum, hafnium, and oxygen, e.g. AlHfO),

a carbon-doped oxide (i.e. a compound comprising carbon and oxygen), organic polymers such as perfluorocyclobutane or polytetrafluoroethylene, fluorosilicate glass (FSG), and organosilicates such as silsesquioxane, siloxane, or organosilicate glass. Besides appropriate etching characteristics, some other considerations in selecting a suitable material for forming the sacrificial structure may include e.g. possibilities of smooth film formation, low shrinkage and outgassing, and good dielectric properties (such as e.g. low electrical leakage, suitable value of a dielectric constant, and thermal stability).

**[0081]** In other embodiments, other suitable techniques may be used for providing the air bridge/cantilever 526 in the process 404, all of which being within the scope of the present disclosure.

[0082] The method 400 may then continue with providing an opening in the suspended portion of the air bridge/cantilever in an area that is above the bottom electrode lead for the future Josephson Junction (process 406 shown in FIG. 4, a result of which is illustrated with an assembly 506 shown in FIG. 5C). The assembly 506 illustrates an opening 529 in the suspended portion of the air bridge/cantilever 526 in an area that is above the bottom electrode lead 524. While the opening 529 is shown in FIG. 5C as a square opening, other shapes may be used in other embodiments, e.g. the opening 529 may be substantially circular, oval, polygonal, or irregularly shaped. In some embodiments, the area of the opening 529 (i.e. a dimension measured in the x-y plane of the coordinate system as shown in FIGS. 5A-5F) may be between about 100 and 5,000,000 nm², including all values and ranges therein, e.g. between about 500 and 100,000 nm², or between about 10,000 and 25000 nm². Bottom and top electrodes of the future Josephson Junction will be provided via the opening 529, and, therefore, dimensions of the opening 529 should be small enough so that the Josephson Junction formed using the opening would exhibit the Josephson effect and not merely act as a superconductor, as was described above with reference to the junctions 316 shown in FIG. 3C.

[0083] As described above, dimensions of the air bridge/cantilever 526 should be able to support formation of the opening 529 in the process 406. For example, in some embodiments, a width of the air bridge/cantilever 526 (i.e. a dimension measured along the x-axis of the coordinate system as shown in FIGS. 5A-5F and indicated in FIG. 5C as a distance "d2") may be at least about 1.2 times greater than the width of the opening 529 (measured in the in the same dimension as that of the air bridge/cantilever 526), e.g. at least about 2 times greater, or at least about 3 times greater. In another example, in some embodiments, a length of the suspended portion of the air bridge/cantilever 526 (i.e. a dimension measured along the y-axis of the coordinate system as shown in FIGS. 5A-5F and indicated in FIG. 5C as a distance "d3") may be at least about 2 times greater than

analogous dimension of the opening 529 (i.e. also measured along the y-axis), e.g. at least about 2.5 times greater, or at least about 3 times greater. In yet another example, in some embodiments, a thickness of the suspended portion of the air bridge/cantilever 526 (i.e. a dimension measured along the z-axis of the coordinate system as shown in FIGS. 5A-5F and indicated in FIG. 5C as a distance "d4") may be between about 10 and 2000 nm, including all values and ranges therein, e.g. between about 50 and 1000 nm, or between about 100 and 500 nm.

[0084] In various embodiments, any suitable techniques may be used for providing the opening 529 in the process 406, such as e.g. reactive ion etching.

[0085] As is seen in FIG. 5C, formation of the opening 529 results in exposing a portion 531 of the bottom electrode lead 524 underneath the suspended portion of the air bridge/cantilever 526. The method 400 may then proceed with depositing an electrically conductive, preferably superconductive, material through the opening to form a first/bottom electrode of the future Josephson Junction (process 406 shown in FIG. 4, a result of which is illustrated with an assembly 508 shown in FIG. 5D). The assembly 508 illustrates an electrically conductive material 528 deposited over the air bridge/cantilever 526, where, because of the opening 529, some of the material 528 is deposited on the exposed area 531 of the bottom electrode lead 524, thus forming a bottom electrode 533 of the future Josephson Junction.

[0086] In some embodiments, a thickness of the first electrode 533 (i.e. a dimension measured along the z-axis of the coordinate system as shown in FIGS. 5A-5F and indicated in FIG. 5D as a distance "d5") may be between about 10 and 2000 nm, including all values and ranges therein, e.g. between about 50 and 1000 nm, or between about 100 and 500 nm. In some embodiments, an area of the bottom electrode 533 may be smaller than the area of the opening 529, e.g. between about 1 and 50 % smaller, including all values and ranges therein, e.g. between about 5 and 30 % smaller, or between about 10 and 20 % smaller.

[0087] In various embodiments, the electrically conductive material 528 forming the bottom electrode 533 provided in the process 408 may include any conducting or superconducting material suitable for providing electrical connectivity in a quantum circuit, such as e.g. any of such materials described above, and may be the same or different from the electrically conductive materials of the bottom electrode lead 524 or/and the air bridge/cantilever 526. Any suitable deposition techniques, possibly in combination with patterning, may be used for providing the electrically conductive material 528 forming the bottom electrode 533 in the process 408, such as e.g. those described above.

[0088] Next, the method 400 may include providing, over the bottom electrode, a layer of a material that can serve as a tunnel barrier of the future Josephson Junction (process 410 shown in

FIG. 4, a result of which is illustrated with an assembly 510 shown in FIG. 5E). One way to provide such a tunnel barrier material is to oxidize the conductive material 528 of the bottom electrode 533, and this is what is schematically illustrated in the assembly 510 showing a tunnel barrier material 530 in a form of a layer of oxide formed in the exposed portions of the conductive material 528, including on the sidewalls, of the bottom electrode 533. For example, the bottom electrode 533 could be made from Al and the tunnel barrier material 530 would then be an oxide of Al. However, in other embodiments, a tunnel barrier material, which could be either a dielectric or a semiconductor material, may be deposited over the bottom electrode 533 through the opening 529. In such other embodiments, depending on the nature of the tunnel barrier material 530 and depending on the deposition technique used to provide the tunnel barrier material 530, such a material may or may not be present on the sidewalls of the bottom electrode 533 as shown in FIG. 5E, all of which embodiments are within the scope of the present disclosure.

[0089] In various embodiments, the tunnel barrier material 530 could be selected as any dielectric material of sufficiently high quality (i.e. low losses in terms of spurious TLS's), such as e.g. silicon oxide, hafnium oxide, or aluminum oxide. In some embodiments, the tunnel barrier material 530 may include an oxide deposited over the bottom electrode 533 using e.g. CVD or/and plasmaenhanced CVD (PECVD). In still other embodiments, the tunnel barrier material 530 may include a dielectric material formed over the bottom electrode 533 using coating techniques involving crosslinking of liquid precursors into solid dielectric materials. In some embodiments, the surface of the bottom electrode 533 may be cleaned or treated prior to applying the dielectric to reduce surface contamination and minimize interface traps and/or promote adhesion, for example using chemical or plasma clean, or applying heat in a controlled environment. In some embodiments, an "interface layer" may be provided between the bottom electrode 533 and the tunnel barrier material 530 deposited thereon to prevent, decrease, or minimize spontaneous and uncontrolled formation of other interfacial layers. In some embodiments, an adhesion promoter or adhesion layer may be applied prior to deposition of the tunnel barrier material 530.

[0090] When the tunnel barrier material 530 is formed as an oxide of the conductive material 528, the process 410 may include performing a controlled oxidation process to oxidize a layer at the exposed upper, and possibly sidewall, surface(s) of the conductive material 528. In some embodiments, such a layer of oxide 530 may be provided as a two-step process. In the first step, inferior-quality surface oxide may be removed (i.e. surface oxide which may have formed on the conductive material 528 spontaneously, i.e. uncontrollably, in previous steps and/or exposure to ambient conditions), e.g. using a light sputtering step such as e.g. argon (Ar) sputtering. In the second step which follows the first step, high quality surface oxide of controlled thickness and

quality is grown with a controlled oxidation step in substantially pure oxygen, e.g. 1-10 minutes in substantially pure oxygen at a pressure of about .1-1 millibar, where the exact time and pressure may be selected so as to set the oxide thickness and quality of the oxide and thus the desired resistance of the Josephson Junction, in conjunction with its area, and thereby set the frequency of the qubit, in conjunction with the charging energy Ec and the Josephson energy Ej for the particular qubit design.