(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5305543号 (P5305543)

(45) 発行日 平成25年10月2日(2013.10.2)

(24) 登録日 平成25年7月5日(2013.7.5)

(51) Int. Cl. FLGO6F 12/00 (2006, 01)GO6F 12/00 564D G 1 1 C 11/401 (2006, 01) GO6F 597D 12/00G 1 1 C 11/4076 (2006.01) G 1 1 C 11/34 362Z G 1 1 C 11/34 354C

請求項の数 15 (全 19 頁)

(21) 出願番号 特願2010-539527 (P2010-539527) (86) (22) 出願日 平成20年3月3日 (2008.3.3) (65) 公表番号 特表2011-508311 (P2011-508311A) (43) 公表日 平成23年3月10日 (2011.3.10) (86) 国際出願番号 PCT/US2008/055661 (87) 国際公開番号 W02009/082502

(87) 国際公開日 平成21年7月2日 (2009.7.2) 審査請求日 平成22年11月16日 (2010.11.16)

(31) 優先権主張番号 61/016,317

(32) 優先日 平成19年12月21日 (2007.12.21)

(33) 優先権主張国 米国(US)

前置審査

||(73)特許権者 501055961

ラムバス・インコーポレーテッド アメリカ合衆国、 カリフォルニア州 9 4089、サニーヴェール、スイート 7 00、エンタープライズ ウェイ 105

|(74)代理人 100079108

弁理士 稲葉 良幸

||(74)代理人 100109346

弁理士 大貫 敏史

|(72)発明者 ギオバンニニ、トマス

アメリカ合衆国, カリフォルニア州 95 148, サンノゼ, ディーダム ドライブ 3614

最終頁に続く

(54) 【発明の名称】メモリシステムの書き込みタイミングを較正する方法および装置

#### (57)【特許請求の範囲】

### 【請求項1】

書き込み動作の実行に関わる複数の信号の間のタイミング関係を較正する方法であって

前記複数の信号は、メモリ制御装置と、メモリチップのセットの中のメモリチップとの間で伝達され、

前記方法は、

前記メモリチップ上に配置された位相検出器を用いて、前記メモリチップにおいて、前記メモリ制御装置から受信されたデータストローブ信号とクロック信号との間の位相関係を較正するステップと、

少なくとも 1 つの書き込み・読み出し・検証の動作を実行して前記データストローブ信号と前記クロック信号との間のクロックサイクル関係を較正するステップとを含み、

前記書き込み・読み出し・検証の動作は、前記クロック信号に対する前記データストローブ信号の遅延を前記クロック信号のクロック周期単位で変化させることを含む、方法。

#### 【請求項2】

前記データストローブ信号と前記クロック信号との間の位相関係を較正するステップは

前記クロック信号に対して様々に遅延させたパルスを前記データストローブ信号上にア サートすること、および

前記データストローブ信号と前記クロック信号とが揃っていることを示す遷移を、前記 位相検出器の出力において探すこと、

を含む、請求項1に記載の方法。

### 【請求項3】

前記クロックサイクル関係を較正するステップは、

前記クロック信号に対する前記データストローブ信号の遅延をクロック周期単位で変化 させること、

前記メモリチップ内の特定のロケーションに値を書き込むこと、

前記メモリチップ内の前記特定のロケーションから値を読み出すこと、および、

前記特定のロケーションから読み出した値が、前記特定のロケーションに書き込んだ値 と一致するかどうかを検証することによって、前記データストローブ信号と前記クロック 信号とが較正されているかどうかを判定すること、

を連続的に実行することを含む、請求項1に記載の方法。

## 【請求項4】

前記メモリチップの前記セットの中のすべてのメモリチップについて繰り返される、請 求項1に記載の方法。

#### 【請求項5】

前記メモリチップの前記セットの中のメモリチップについての前記タイミング関係は、 前記メモリチップのそれぞれが結合されている制御パスに沿って遅延が増える順に較正さ れる、請求項1に記載の方法。

#### 【請求項6】

読み出し動作時に前記データストローブ信号とデータストローブイネーブル信号との間 のタイミング関係を調節するステップをさらに含む、請求項1に記載の方法。

#### 【請求項7】

書き込み動作の実行に関わる複数の信号の間のタイミング関係を較正する方法であって

前記複数の信号は、メモリ制御装置と、メモリチップのセットの中のメモリチップとの 間で伝達され、

前記方法は、

前記メモリチップ上に配置された位相検出器を用いて、前記メモリチップにおいて、前 記メモリ制御装置から受信されたデータストローブ信号とクロック信号との間の位相関係 を較正するステップと、

前記データストローブ信号と前記クロック信号との間のクロックサイクル関係を較正す ることを、

前記クロック信号に対する前記データストローブ信号の遅延をクロック周期単位で変 化させること、

前記メモリチップ内の特定のロケーションに値を書き込むこと、

前記メモリチップ内の前記特定のロケーションから値を読み出すこと、および、

前記特定のロケーションから読み出した値が、前記特定のロケーションに書き込んだ 値と一致するかどうかを検証することによって、前記データストローブ信号と前記クロッ ク信号とが較正されているかどうかを判定すること、

を反復することによって行うステップと、

を含む、方法。

## 【請求項8】

メモリ制御装置と、

前記メモリ制御装置と結合されたメモリチップのセットと、

#### を備え、

前記メモリチップの前記セットの中の各メモリチップは、前記メモリチップにおいて前 記メモリ制御装置から受信したデータストローブ信号およびクロック信号の間の位相関係 を較正するように構成された位相検出器を含み、

20

10

30

50

前記メモリ制御装置は、少なくとも1つの書き込み・読み出し・検証の動作を実行して前記データストローブ信号と前記クロック信号との間のクロックサイクル関係を較正するように構成され、

前記書き込み - 読み出し - 検証の動作は、前記クロック信号に対する前記データストローブ信号の遅延をクロック周期単位で変化させることを含む、システム。

## 【請求項9】

前記メモリチップの前記セットは、前記クロック信号がマルチドロップ方式で前記メモリ制御装置から前記メモリチップの前記セットにルーティングされるように、前記メモリ制御装置と結合されており、

前記データストローブ信号は、ダイレクト接続で前記メモリ制御装置から前記メモリチップの前記セットにルーティングされ、前記クロック信号と前記データストローブ信号との間の遅延差は1クロック周期を超えてもよい、請求項8に記載のシステム。

#### 【請求項10】

前記メモリ制御装置は、前記データストローブ信号と前記クロック信号との間の位相関係を較正する際に、前記クロック信号に対して様々に遅延させたパルスを前記データストローブ信号上にアサートすること、および、前記データストローブ信号および前記クロック信号の位置が揃っていることを示す遷移を前記位相検出器の出力において探すこと、を行うように構成された、請求項8に記載のシステム。

#### 【請求項11】

前記メモリ制御装置は、前記クロックサイクル関係を較正する際に、

前記クロック信号に対する前記データストローブ信号の遅延をクロック周期単位で変化させること、

前記メモリチップ内の特定のロケーションに値を書き込むこと、

前記メモリチップ内の前記特定のロケーションから値を読み出すこと、および、

前記特定のロケーションから読み出した値が、前記特定のロケーションに書き込んだ値と一致するかどうかを検証することによって、前記データストローブ信号と前記クロック信号とが較正されているかどうかを判定すること、

を連続的に実行するように構成された、請求項8に記載のシステム。

### 【請求項12】

前記メモリチップの前記セットの中のすべてのメモリチップを順次較正するように構成された、請求項8に記載のシステム。

## 【請求項13】

前記メモリチップの前記セットの中のメモリチップについての前記タイミング関係は、前記メモリチップの前記セットの中の前記メモリチップにアドレス情報および制御情報を提供するマルチドロップパスに沿って遅延が増える順に較正される、請求項8に記載のシステム。

## 【請求項14】

前記メモリ制御装置は、読み出し動作時に前記データストローブ信号とデータストローブイネーブル信号との間のタイミング関係を調節するように構成された、請求項8に記載のシステム。

## 【請求項15】

メモリ制御装置内の動作方法であって、

前記メモリ制御装置は、クロック信号を受信するメモリチップと結合され、かつ、書き込み動作時に、データを<u>データ</u>ストローブ信号とともに前記メモリチップに供給し、前記メモリデバイスは前記データストローブ信号を用いて前記データを捕捉し、

前記方法は、前記メモリチップ上に配置された位相検出器を用いて、前記メモリチップにおいて、前記メモリ制御装置から受信されたデータストローブ信号とクロック信号との間の位相関係を較正するステップを含み、

前記方法は、較正モード時には、

前記データストローブ信号とクロック信号との間のクロックサイクル関係を較正するこ

20

10

40

50

とを、

前記クロック信号に対する前記データストローブ信号の遅延をクロック周期単位で変化させること、

前記メモリチップ内の特定のロケーションに第1の値を書き込むこと、

前記メモリチップ内の前記特定のロケーションから第2の値を読み出すこと、および

前記特定のロケーションから読み出した値が、前記特定のロケーションに書き込んだ値と一致するかどうかを検証することによって、前記データストローブ信号と前記クロック信号とが較正されているかどうかを判定すること、

を反復することによって行うステップを含む、方法。

と及後することによって行う人ブックを占む、万法【発明の詳細な説明】

【技術分野】

[00001]

本実施形態は、主として、コンピュータシステム用メモリの書き込み動作の実行に必要な信号のタイミングを較正する手法に関する。

【図面の簡単な説明】

[0002]

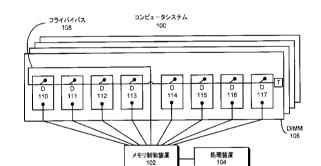

- 【図1】コンピュータシステムの一実施形態を示す図である。

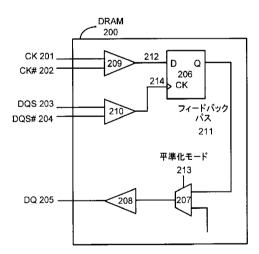

- 【図2】位相検出器の一実施形態を示す図である。

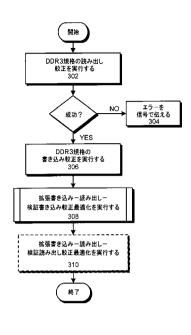

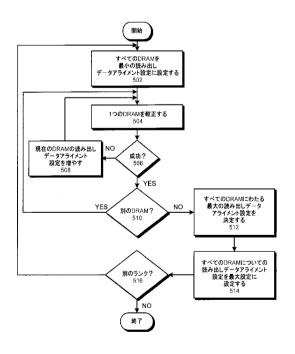

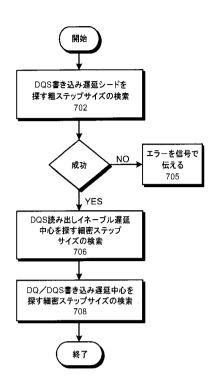

- 【図3】メモリタイミング較正処理の一実施形態を示すフローチャートである。

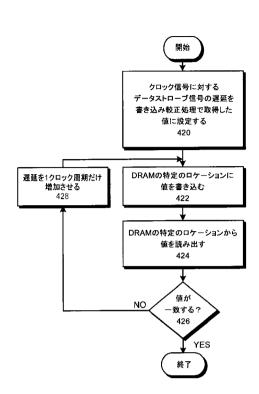

- 【図4】メモリタイミングの較正を行う書き込み 読み出し 検証処理の一実施形態を示すフローチャートである。

- 【図 5 】読み出しデータアライメント設定を較正する処理の一例を示すフローチャートである。

- 【図 6 】読み出しデータアライメント設定を較正する処理の別の例を示すフローチャート である。

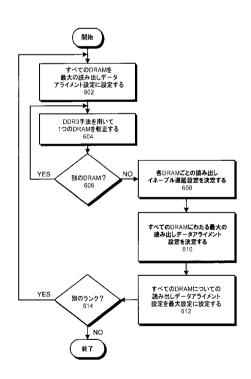

- 【図7】メモリタイミング較正処理の別の例を示すフローチャートである。

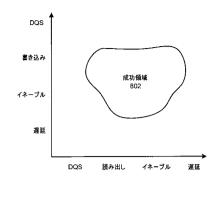

- 【図8】成功領域および失敗領域を示すグラフである。

- 【図9】修正された位相検出回路の一実施形態を示す図である。

- 【図10】較正処理の一例を示すタイミング図である。

- 【図11】較正位相検出回路の変形形態を示す図と、関連するタイミング図である。

- 【図12】書き込みタイミング較正処理の一例を示すフローチャートである。

- 【図13】システムの一実施形態を示すブロック図である。

【発明を実施するための形態】

[0003]

以下の説明は、当業者が本開示の実施形態を作成および利用できるように行うものであり、特定の用途およびその要件の文脈で行うものである。本開示の実施形態に対する各種の修正は、当業者には自明であろう。また、本明細書において定義される一般原則は、本明細書の趣旨および範囲から逸脱することなく、他の実施形態および用途に適用可能である。したがって、本明細書は、図示された実施形態に限定されるものではなく、本明細書で開示される原理および特徴と矛盾しない最も広い範囲を与えられるものとする。

[0004]

書き込み動作の実行に関わる複数の信号の間のタイミング関係を較正する装置の実施形態を説明する。これらの実施形態の1つとして、メモリチップのセットに結合されたメモリ制御装置がある。これらのメモリチップのそれぞれには位相検出器が含まれ、位相検出器は、メモリチップにおいてメモリ制御装置から受信したデータストローブ信号およびクロック信号の間の位相関係の較正を可能にするように構成されている。さらに、メモリ制御装置は、1つまたは複数の書き込み・読み出し・検証の動作を実行してデータストローブ信号とクロック信号との間のクロックサイクル関係を較正するように構成されており、この書き込み・読み出し・検証の動作では、クロック信号に対するデータストローブ信号

10

20

30

40

の遅延をクロック周期単位で変化させる。

## [0005]

実施形態によっては、メモリチップのセットは、フライバイトポロジを介してメモリ制御装置と結合されており、クロック信号は、「フライバイパス」を通ってマルチドロップ方式で、メモリ制御装置からメモリチップのセットへルーティングされ、データ信号およびデータストローブ信号は、直接接続によって、メモリ制御装置からメモリチップのセットへルーティングされる。なお、フライバイパス上のクロック信号と直接パス上のデータストローブ信号との間の遅延差に起因する「フライバイ遅延分離(delay separation)」は、1クロック周期を超えてもよい。実施形態によっては、フライバイパスに沿って遅延が増える順にメモリチップを較正する。

[0006]

実施形態によっては、メモリ制御装置は、データストローブ信号とクロック信号との間の位相関係を較正する際に、クロック信号に対して様々に遅延させたパルスをデータストローブ信号上にアサートして、データストローブ信号およびクロック信号の位置が揃っていることを示す遷移を、位相検出器の出力において探すように構成されている。

[0007]

実施形態によっては、メモリ制御装置は、クロックサイクル関係を較正する際に、クロック信号に対するデータストローブ信号の遅延をクロック周期単位で変化させるステップと、メモリチップ内の特定のロケーションに値を書き込むステップと、そのメモリチップ内の特定のロケーションから値を読み出すステップと、その特定のロケーションから読み出した値が、その特定のロケーションに書き込んだ値と一致するかどうかを検証することによって、データストローブ信号とクロック信号とが較正されているかどうかを判定するステップと、を連続的に実行するように構成されている。

[00008]

実施形態によっては、本装置は、メモリチップのセットのすべてのメモリチップを順次 較正するように構成されている。

[0009]

実施形態によっては、較正は、ロバストなデータパターンを用いて最大メモリ速度で実行される。

[0010]

実施形態によっては、メモリ制御装置はさらに、読み出し動作時にデータストローブ信号とデータストローブイネーブル信号との間のタイミング関係を調節するように構成されている。

[0011]

実施形態によっては、メモリシステムの書き込み動作の実行に関わる複数の信号の間のタイミング関係を較正する、別のシステムを提供する。本システムは、較正モード時には、メモリチップのセットの中のメモリチップにおいて複数の信号を受信する。これらの信号は、メモリ制御装置からのクロック信号、マーキング信号、データストローブ信号などであり、マーキング信号は、クロック信号の中の特定のクロックサイクルをマーキングするパルスを含む。次に、本システムは、マーキング信号を用いてクロック信号の中の特定クロックサイクルに窓を掛けて窓掛けクロック信号を生成することにより、データストローブ信号とクロック信号との間のタイミング関係の較正を容易にする。次に、本システムは、メモリチップ上の位相検出器において、データストローブ信号を用いて窓掛けクロック信号を対しの対象置がタイミング関係を較正できるように、捕捉した窓掛けクロック信号をメモリ制御装置に返す。

[0012]

実施形態によっては、マーキング信号は、フライバイパス上の選択された信号線を通ってメモリ制御装置からメモリに伝達される。選択された信号線は、メモリシステムが較正モードでない場合には、別の信号を搬送する。

[0013]

10

20

30

40

20

30

40

50

実施形態によっては、選択された信号線は、メモリシステムが較正モードでない場合には、書き込みイネーブル信号を搬送する。

#### [0014]

実施形態によっては、データストローブ信号を用いて窓掛けクロック信号を捕捉する際に、データストローブ信号をクロックとして、窓掛けクロック信号をフリップフロップに取り込むことが必要である。

#### [0015]

実施形態によっては、書き込み動作の実行に必要な複数の信号の間のタイミング関係の較正を容易にする半導体メモリデバイスが開示されている。本メモリデバイスは、クロック信号を受信するクロック入力を含んでいる。さらに、本メモリデバイスは、メモリ制御装置からマーキング信号を受信する第1の入力を含んでいる。マーキング信号は、クロック信号の中の特定クロックサイクルをマーキングするパルスを含む。本メモリデバイスはさらに、メモリ制御装置からデータストローブ信号を受信する第2の入力と、位相検出器とを含んでいる。位相検出器は、マーキング信号を用いてクロック信号の中の特定クロックサイクルに窓を掛け、さらに、データストローブ信号を用いて窓掛けクロックサイクルを捕捉する。本メモリデバイスは、捕捉した窓掛けクロックサイクルをフィードバック信号としてメモリ制御装置に与える出力を含んでいる。

### [0016]

実施形態によっては、メモリ制御装置は、クロック信号を受信するメモリチップと結合されており、データストローブ信号とクロック信号との間のクロックサイクル関係を較正する較正モードを含んでおり、較正は、クロック信号に対するデータストローブ信号の遅延をクロック周期単位で変化させるステップと、メモリチップ内の特定のロケーションに第1の値を書き込むステップと、その、メモリチップ内の特定のロケーションから第2の値を読み出すステップと、その特定のロケーションから読み出した値が、その特定のロケーションに書き込んだ値と一致するかどうかを検証することによって、データストローブ信号とクロック信号とが較正されているかどうかを判定するステップと、を反復することによって行われる。

#### [0017]

実施形態によっては、本システムは、クロック信号の立ち上がりエッジをクロックとして、マーキング信号を、全体遅延がDRAMの書き込み遅延に相当するカスケード接続されたフリップフロップに通すことにより、窓掛けクロック信号を生成する。このカスケード接続の出力がクロックの立ち下がりエッジで取り込まれて、位相検出器イネーブル信号が作成される。次に、本システムは、位相検出器イネーブル信号とクロック信号との論理積をとることにより、窓掛けクロック信号を生成する。

### [0018]

## コンピュータシステム

メモリシステムは非常に高い(たとえば、1000メガ転送/秒(「MT/s」)を超える)データレートで動作を開始するため、要求されるレベルのシグナリング性能を達成するためには、「フライバイ」メモリトポロジを用いることが可能である。たとえば、図1に示したコンピュータシステム100を参照されたい。コンピュータシステム100は、処理装置104を含んでおり、処理装置104は、メモリ制御装置102を介してデュアルインラインメモリモジュール(「DIMM」)106と通信している。このコンピュータシステムは、フライバイレイアウトトポロジを有しており、このトポロジでは、1つまたは複数の要求(RQ)信号およびクロック(CK)信号を含む制御信号が、メモリ制御装置102から複数の同期動的ランダムアクセスメモリ(「SDRAM」または「DRAM」)チップ110~117にルーティングされる。本実施形態では、DIMM 106内の制御信号およびクロック信号が、フライバイパス108を用いたマルチドロックで、DRAMチップ110~117のそれぞれと結合されている。要求信号は、アドレス信号を含むことが可能であり、(一実施形態ではパターン長が互いに等しい)複数の信号線と、クロック信号線とによって伝搬される。要求信号およびクロック信号は、フライ

20

30

40

50

## [0019]

一実施形態では、データストローブ(DQS)信号およびデータ(DQ)信号は、各DRAMチップごとに、メモリ制御装置102の専用DQインタフェースポートと、DQインタフェースとの間を、ポイントツーポイントでルーティングされる。複数のランクをサポートするシステムでは、直接接続は、メモリ制御装置102の専用DQインタフェースの接続点で、データストローブ(DQS)信号およびデータ(DQ)信号をルーティングすることを必要とする場合がある。「ランク」は、ひとまとまりのDRAMチップであって、あるランクのDRAMチップである。(それぞれが単一ランクのDRAMチップである。(それぞれが単一ランクを引きるひとまとまりのDRAMチップである。(それぞれが単一ランクをはデュアルランクを有する)複数のDIMMモジュールをサポートするシステムでは、はデュアルランクを有すると、複数のDIMMモジュールをサポートと、各DIMMモジュール内の対応するDRAMチップの各DQインタフェースの接続点との間で、データストローブ(DQS)信号およびデータ(DQ)信号をルーティングすることを必要とする場合がある)。

#### [0020]

一実施形態では、データストローブ信号(DQS)は、データ信号(DQ)と一緒にルーティングすることが可能であり、集積回路(すなわち、メモリ制御装置またはDRAM)のレシーバにおいてデータを受信するために用いる。たとえば、書き込み動作時に、メモリ制御装置がデータをDRAMに送信している場合、メモリ制御装置は、DQS信号をデータと一緒に送信し、DQS信号は、DRAMにおいて、そのデータを受信するために用いられる。読み出し動作時には、DRAMがデータをメモリ制御装置に送信している場合、DRAMは、メモリ制御装置に送信するデータと一緒にDQS信号を送信する。DQS信号は、メモリ制御装置で受信された後、そのDQS信号と一緒に送信されたデータをストローブするために用いられる。DQS信号は、読み出し動作および書き込み動作の用の双方向信号線で送信してよく、あるいは、読み出し動作および書き込み動作のそれぞれに対して別々の単方向信号線を用意してもよい。

#### [0021]

フライバイレイアウトトポロジで構成されたメモリシステムを特徴とする一実施形態では、RQ/CK伝搬遅延は、フライバイ信号パスからRQ信号およびCK信号を受信するDRAMのそれぞれに対して増加していく。このため、連続する各DRAMごとに、受信されるRQ/CK信号とDQ/DQS信号との間のスキューが増加していく。書き込みトランザクション時にこの作用を補償するために、メモリ制御装置102は、連続するDRAMのそれぞれにRQ/CKが送信されるタイミングに対して増加していくDQ/DQS送信遅延を導入する。同様に、読み出しトランザクション時には、メモリ制御装置102は、連続するDRAMのそれぞれに対して増加していくDQS読み出しイネーブル受信サンプル遅延を導入する。メモリ制御装置102によって導入される、これらの書き込み遅延および読み出し遅延を、それぞれ「書き込み平準化」遅延および「読み出し平準化」遅延と称する。

#### [0022]

また、読み出しトランザクション時には、フライバイ信号パスからRQ信号およびCK信号を受信する、連続するDRAMのそれぞれに対して最適読み出しデータアライメント設定が増加していき、フライバイ信号パスの最後尾にあるDRAMに必要な読み出しデータアライメント設定が最大になる可能性がある。この最大読み出しデータアライメント設定が決定すれば、これを用いてすべてのDQ/DQSグループについて設定を計算するこ

とにより、メモリ制御装置102のDQブロックのそれぞれにおいて受信される読み出し データのアライメントを行うことが可能である。

#### [0023]

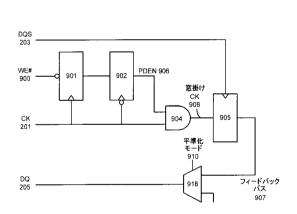

一実施形態では、DDR3規格(JEDEC Solid State Technology Associationによって 公布されたJESD79-3)に従って設計されたDRAMチップに、タイミング調節を容易にす る回路を組み込むことが可能である。たとえば、図2は、DRAMチップ200内にある 位相検出回路を示しており、この回路は、フライバイパス上のクロック信号と、直接パス 上のデータストローブ信号との間の位相調節を容易にする。この位相検出回路では、演算 増幅器209が、CK信号201およびCK#信号202からなる差動クロック信号を、 非差動クロック信号212に変換する。同様に、演算増幅器210が、DQS信号203 およびDQS#信号204からなる差動ストローブ信号を、非差動データストローブ信号 2 1 4 に変換する。次に、非差動データストローブ信号 2 1 4 をクロックとして、非差動 クロック信号212がフリップフロップ206に取り込まれる。フリップフロップ206 の出力は、フィードバックパス211を通り、多重化器207を通り、ドライバ208を 通って、データ線DO 205にフィードされる。なお、多重化器207は、平準化モー ド信号213の値に基づいて、フリップフロップ206の出力を選択的にデータ線DQ 2 0 5 にフィードする。これにより、メモリ制御装置 1 0 2 は、クロック信号 2 1 2 およ びデータストローブ信号214の位相が揃っているかどうかを判定することが可能になり 、これによって、メモリ制御装置102(図1)は、クロック信号212に対して様々に 遅延させたパルスをデータストローブ信号214上にアサートして、データ線DQ 20 5上に現れる遷移を、位相検出器の出力において探すことにより、データストローブ信号 214とクロック信号212との間の位相関係を較正することが可能になる。

#### [0024]

図2を参照して上述した実施形態では、上述の位相検出回路によるタイミング調節の結果が、調節処理において書き込み / 読み出しのデータ完全性が検証されていないために正しくないという状況が起こりうる。特に、クロック信号とデータストローブ信号との間のフライバイ遅延分離が 1 クロック周期を超える場合は、上述のタイミング調節処理において位相関係が適正に調節されるが、このタイミング調節は、クロック周期単位でずれる可能性がある。

## [0025]

そのような状況を考慮するために、タイミング調節処理において書き込み / 読み出しのデータ完全性を検証する実施形態を以下に示す。そのような検証を行うことで、それらの実施形態は、対象 DRAMにおいて、ロバストなデータパターンの書き込みおよび読み出しを行い、かつ、トポロジ内の他の DRAMにデータパターンを同時伝達することにより、タイミング調節処理において、スイッチングノイズの実際的な影響を明らかにすることが可能になる。

## [0026]

### DRAM較正処理

図3は、メモリタイミング較正処理の一実施形態を示すフローチャートである。本実施形態では、以下の事柄を、本較正処理の前提とする。(1)要求(RQ)信号とクロック(CK)信号との間のタイミング関係は、RQとCKとの間の推定平均スキューを補償するように設定されているものとする。(2)各DQ/DQSグループごとのデータ信号(DQ)とデータストローブ信号(DQS)との間のタイミング関係は、DQとDQSとの間の推定平均スキューを補償するように設定されているものとする。(3)また、DRAMは、RQ/CK遅延が増えていく順番で連続して処理されるものとする。(4)さらに、どの2つのDQ/DQSグループの間のスキューも、1CKサイクルよりはかなり小さいものとする。

## [0027]

図3を参照すると、本処理は、読み出し較正(読み出し平準化)処理を実行すること(オペレーション302)から始まり、オペレーション302では、(図1に示したフライ

10

20

30

40

20

30

40

50

バイRQおよび直接DQのトポロジに結合されたDRAMセットの)各DRAMにあるレジスタまたは他の記憶装置が、あらかじめ定義されたデータパターンをメモリ制御装置に供給する。フライバイRQバス上でメモリ制御装置から最も近くに位置する(したがって、RQ/CKフライト時間遅延が最小である)DRAMは、フライバイRQバス上でメモリ制御装置から最も遠くに位置する(したがって、RQ/CKフライト時間遅延が最大である)DRAMより先に、あらかじめ定義されたデータパターンを送信する。次に、メモリ制御装置は、メモリ制御装置における各受信DQブロックごとの受信タイミングオフセットを決定することが可能であり、これは、たとえば、各受信DQブロックの読み出しデータストローブイネーブル遅延を、受信した読み出しデータストローブの到着時刻は、対応するDRAMで受信された読み出しコマンドの伝搬遅延に応じて決まる。

[0028]

本システムがオペレーション302で較正処理に成功しなかった場合、本システムは、 エラーを信号で伝える(オペレーション304)。成功した場合、本システムは、書き込み較正(書き込み平準化)処理を実行する(オペレーション306)(なお、この書き込み較正処理は、一実施形態では、図2に示したような、各DRAM内にある位相検出回路を利用することが可能である)。一実施形態では、書き込み較正処理は、DQSストローブ信号を供給することを含み、(図1に示したフライバイRQおよび直接DQのトポロジに結合されたDRAMセットの)各DRAMが、このDQSストローブ信号を用いてクロック信号CKをサンプリングし、その結果を直接DQ線でメモリ制御装置に返す。書き込み較正処理では、メモリ制御装置は、次に、メモリ制御装置における各送信DQプロックごとの送信タイミングオフセットを決定することにより、たとえば、各DRAMにおいて連続して受信される、対応する書き込みコマンドの伝搬遅延に起因する書き込みデータスキューを平準化することが可能である。

[0029]

書き込み較正処理(オペレーション306)後は、クロック信号およびデータストローブ信号の位相が揃っているはずであるが、これらの信号のタイミングはさらに、クロック周期単位でずれている可能性がある。この問題を解消するために、一実施形態では、本システムは、拡張書き込み・読み出し・検証書き込み較正最適化を実行する(オペレーション308)(この処理については、後で図4を参照して詳述する)。本システムはさらに、拡張書き込み・読み出し・検証読み出し較正最適化を実行することが可能である(オペレーション310)。

[0030]

図4は、書き込みタイミングの較正を行う書き込み・読み出し・検証処理の一例を示すフローチャートである。この処理の開始時には、本システムは、クロック信号に対するデータストローブ信号の遅延を、書き込み較正処理で取得した値に設定する(オペレーション420)。これは、書き込み較正処理において、そのDQS遅延検索が最小遅延設定から開始されたことを前提としている。次に、本システムは、DRAMの特定のロケーションに値を書き込み(オペレーション422)、次に、同じロケーションから値を読み出す(オペレーション424)。次に、本システムは、そのメモリロケーションに書き込んだ値とそのメモリロケーションから読み出した値とが一致するかどうかを判定する(オペレーション426)。一致しない場合、本システムは、遅延を1クロック周期だけ増加させて(オペレーション428)、オペレーション422に戻る。一方、値が一致した場合は、書き込み動作が成功したことになり、このことは、本システムが較正済みであり、したがって、較正処理が完了したことを示している。

[0031]

読み出しデータアライメント較正

一実施形態では、本システムはさらに、異なる複数のDRAMデバイスからの読み出し データのずれを補償する較正が必要である。フライバイトポロジを用いたシステムにおい て構成された、連続する複数のDRAMデバイスからの読み出しデータは、連続的に増加

20

30

40

50

した遅延でメモリ制御装置に到着する。一実施形態では、読み出しアライメント処理は、 メモリ制御装置における連続するDQレシーバブロックに読み出しデータをキューイング することを含む。

### [0032]

異なる複数のDRAMデバイスからの読み出しデータは、連続的に増加した遅延でメモリ制御装置に到着した後、メモリ制御装置内の一回路で受信され、この回路で一時的に保存されてから、メモリ制御装置のクロックと内部的に揃えられ、さらなる処理が行われる。「読み出しアライメント」(「読み出しデータアライメント」とも呼ばれる)は、読み出しデータが、たとえば、メモリ制御装置内の先入れ先出しバッファ(「FIFO」)から出力されてメモリ制御装置のコアに供給される際に、読み出しデータを同じクロック信号と同期させることを含む。このクロック信号は、データのスライスごとに異なる読み出しデータストローブイネーブル信号と同じではなく、FIFOへのデータの書き込みを可能にする。FIFOの代わりに、あるいはFIFOと組み合わせて、バッファ回路エレメントおよび/またはフリップフロップ回路エレメントを使用することが可能である。

### [0033]

より具体的に説明すると、図5は、読み出しデータアライメント設定を較正する処理の一実施形態を示すフローチャートである。本システムは、まず、すべてのDRAMを、可能な最小の読み出しデータアライメント設定に設定する(オペレーション502)。次に、本システムは、図3で既に説明した手法を用いて1つのDRAMを較正し(オペレーション504)、次に、そのDRAMの較正処理が成功したかどうかを判定する(オペレーション506)。そのDRAMの較正処理が成功したかどうかを判定するは、現在の読み出しデータアライメント設定を増やして(オペレーション508)、オペレーション504に戻る。一方、DRAMの較正処理が成功した場合、本システムは、較正するがを判定する(オペレーション510)。存在する場合、本システムは、オペレーション504に戻って、次のDRAMを較正する。存在しない場合、本システムは、すべてのDRAMにわたる最大の読み出しデータアライメント設定を、この最大設定に設定する(オペレーション514)。

### [0034]

次に、本システムは、較正すべき別のランクのDRAMが存在するかどうかを判定する(オペレーション516)。存在する場合、本システムは、オペレーション502に戻って、次のランクのDRAMを較正する。一方、さらなるランクのDRAMがない場合、処理は完了する。

## [0035]

図6に示した代替実施形態では、読み出しアライメント設定を、可能な最大設定に初期化した後、減らす。より具体的に説明すると、この代替実施形態では、本システムは、まず、すべてのDRAMを、可能な最大の読み出しデータアライメント設定に設定する(オペレーション602)。次に、本システムは、図3で既に説明した手法を用いて1つのDRAMを較正し(オペレーション604)、次に、較正すべき別のDRAMが存在するかどうかを判定する(オペレーション606)。存在する場合、本システムは、オペレーション604に戻って、次のDRAMを較正する。存在しない場合、本システムは、各DRAMごとの読み出しイネーブル遅延設定を決定し(オペレーション608)、次に、すべてのDRAMにわたる最大の読み出しデータアライメント設定を決定する(オペレーション610)。次に、本システムは、すべてのDRAMについての読み出しデータアライメント設定を、この最大設定に設定する(オペレーション612)。

## [0036]

次に、本システムは、較正すべき別のランクのDRAMが存在するかどうかを判定する(オペレーション614)。存在する場合、本システムは、オペレーション602に戻って、次のランクのDRAMを較正する。一方、さらなるランクのDRAMがない場合、処理は完了する。

20

30

40

50

#### [0037]

1つのDRAMのついての2D書き込み - 読み出し - 検証較正手法

図7は、2次元(「2D」)書き込み - 読み出し - 検証較正手法を用いるメモリタイミング較正処理の代替実施形態を示すフローチャートである。この2D検索手法では、2パス方式を用いる。第1パスでは、送信位相設定および受信位相設定(それぞれ、書き込み平準化遅延および読み出し平準化遅延)に粗ステップサイズを用いる(オペレーション702)。本システムは、まず、送信位相を、2D検索領域の原点から増分させながら進める。本システムは、各送信位相ごとに、受信位相を増分させながら進めることによって「粗パス」領域を見つけようとする。本システムは、十分大きな粗パス領域が見つかるまで、送信位相をいっぱいまで進め続ける。これが発生した時は第1パスを終了し、最終送信位相を、本手法の第2パスのためのシード(seed)として用いる。

[0038]

本システムが粗パス領域を見つけられず、したがって、第1パスが成功しなかった場合 、本システムは、エラーを信号で伝える(オペレーション705)。

#### [0039]

一方、本システムが粗パス領域を見つけることに成功した場合、本システムは、DQS 読み出しイネーブル遅延中心を探す細密ステップサイズの検索を実行し(オペレーション706)、次に、DQ/DQS書き込み遅延中心を探す細密ステップサイズの検索を実行する(オペレーション708)。より具体的に説明すると、第2パスでは、細密ステップサイズを受信位相設定に用いて、第1パス送信位相の間に生成されたシードから始めて、第1パス送信位相を囲む全体パス領域を見つける。その後、この領域の中心を見つけ、その中心受信位相を最適受信位相設定として用いる。第2パスでは、次に、細密ステップサイズを受信位相設定に用いて、この中心受信位相から始めて、中心受信位相設定を囲む全体パス領域を見つける。その後、本システムは、この領域の中心を見つけ、その中心送信位相を送信位相設定として用いる。

#### [0040]

なお、上述の2 D較正手法は、たとえば、DDR2 SDRAMチップまたは他のタイプのメモリデバイスに用いることが可能である。したがって、図5のフロー図のオペレーション504をこの2 D手法に置き換えれば、図5のフロー図が使用可能になる。代替として、図6のフロー図のオペレーション604をこの2 D手法に置き換えれば、図6のフロー図が使用可能になる。

[0041]

図8は、成功領域および失敗領域を示すグラフである。なお、上述の2D検索は、読み出しイネーブル遅延と書き込みイネーブル遅延との可能なすべての組み合わせに対して2D成功領域802を識別するものである。

[0042]

位相検出回路 1

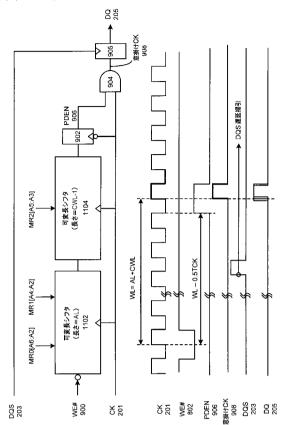

図9は、(たとえば、1クロックサイクルより大きなDRAMフライバイ遅延分離に対する書き込みタイミング較正を容易にすることが可能な)位相検出回路の一実施形態を示す。この位相検出回路では、マーキングパルスが、たとえば、書き込みイネーブル(「WE#」)信号線900において受信され、このマーキングパルスは、クロック信号201の立ち上がりエッジおよび立ち下がりエッジをそれぞれクロックとして用いる2つのDフリップフロップ(D-flops)901および902を経てフィードされる。これにより、所望の時間スロットに対応する窓を有する位相検出器イネーブル信号(PDEN)906が生成される。次に、PDEN信号906とクロック信号904との論理積をとることにより、窓掛けクロック信号908が生成される。一実施形態では、WE#は、CKと一緒にフライバイパスを通ってルーティングされ、伝搬する。

[0043]

次に、データストローブ信号(DQS)203をクロックとして、窓掛けクロック信号908がフリップフロップ905に取り込まれる。フリップフロップ905の出力は、フ

ィードバックパス 9 0 5 を通り、多重化器 9 1 8 を通って、データ線 D Q 2 0 5 にフィードされる。なお、多重化器 9 1 8 は、平準化モード信号 9 1 0 の値に基づいて、フリップフロップ 2 0 6 の出力を選択的にデータ線 D Q 2 0 5 にフィードする。

### [0044]

このフィードバック信号により、メモリ制御装置は、クロック信号 2 0 1 と D Q S 2 0 3 が揃っているかどうかを判定することが可能になり、これによって、メモリ制御装置は、クロック信号 2 0 1 に対して様々に遅延させたパルスを D Q S 2 0 3 上にアサートして、データ線 D Q 2 0 5 上に現れる遷移を、位相検出器の出力において探すことにより、 D Q S 2 0 3 とクロック信号 2 0 1 との間のタイミング関係を較正することが可能になる。

#### [0045]

なお、このマーキングパルスの伝達には、フライバイパス上の任意のコマンド線または制御線を用いることが可能である。したがって、この目的のためには、WE#コマンド線の代わりに別のコマンド線または制御線を用いることも可能なので、特定のコマンド線WE#を用いることは必須ではない(たとえば、様々な実施形態において、WE#の代わりに、RAS#、CAS#などのコマンド線、あるいは、チップセレクト(CS#)やクロックイネーブル(CKE#)などの制御線を用いることが可能である)。本実施形態では、WE#コマンド線を用いているが、これは、WE#コマンド線が、通常動作時(すなわち、非較正モード動作時)にメモリ書き込み機能に関連付けられているためである。

## [0046]

窓掛けクロック信号908は、生成された後に、DQS信号203をクロックとしてフリップフロップ905に取り込まれる。図2に示した回路と同様に、フリップフロップ905の出力は、フィードバックパス907を通り、多重化器918を通って、データ線DQ 205にフィードされる。この処理において、多重化器918は、平準化モード信号910の値に基づいて、フリップフロップ905の出力を選択的にデータ線DQ 205にフィードする。したがって、平準化モード動作の間に、メモリ制御装置は、窓掛けクロック信号908およびデータストローブ信号DQS 203の位相が揃っているかどうかを判定することが可能である。これによって、メモリ制御装置は、窓掛けクロック信号908に対して様々に遅延させたパルスをDQS信号203上にアサートして、データ線DQ 205上に現れる遷移を、位相検出器の出力において探すことにより、DQS信号203と窓掛けクロック信号908との間のタイミング関係を較正することが可能になる。

## [0047]

これに対し、DRAMフライバイ遅延分離が1クロックサイクルを超える場合、図9に示した回路がゼロから1への遷移を発生させるのは、DQS信号203およびクロック信号201の位相が揃っていて、さらに、適正なクロックサイクルに対してこれらの位置が揃っている場合だけである。この点は、図2に示した回路と異なる。図2の回路がゼロから1への遷移を発生させるのは、DQS信号203およびクロック信号201の位相が揃っていて、適正なクロックサイクルに対してこれらの位置が揃っていない場合である。

## [0048]

### 較正処理

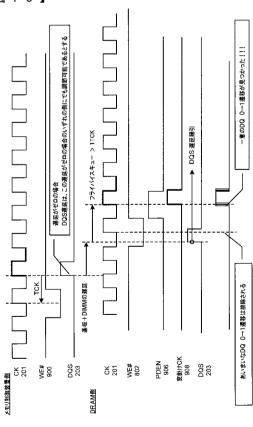

図10は、図9に示した回路を用いる較正処理の一例を示すタイミング図である。図10の上部は、メモリ制御装置側の信号のタイミングを示しており、図10の下部は、メモリチップ(DRAM)側の信号のタイミングを示している。図10では、メモリ制御装置は、クロック信号(CK 201)およびデータストローブ信号(DQS 203)をDRAMに送信する。

## [0049]

図10に示したように、DQSパルスがメモリ制御装置によってアサートされる。本実施形態では、DRAMを収容しているDIMMへのCK信号およびすべてのDQS信号が、回路基板上で等長配線によりルーティングされている。回路基板上でのフライトの時間を経て、CKおよびDQSは、DIMM内の各DRAMに伝搬する。この処理において、

10

20

30

DQS信号は、それぞれ等しい距離を経て、DIMM内の各DRAMにルーティングされる。一方、CKは、フライバイパスを通って連続的に各DRAMにルーティングされる。この結果、フライバイパス沿いの各DRAMにおいてCKとDQSとの間のスキューが連続的に増えていく。メモリクロック速度が増え続けると、これらのDRAMフライバイ遅延分離は1クロックサイクルを超え始める。この結果、CKとDQSとの間のスキューは、1クロックサイクルより大きくなる。一実施形態では、少なくとも1つのコマンド信号(たとえば、WE#)が、CKと一緒にフライバイパスを通ってルーティングされ、伝搬する。

### [0050]

図10のDRAM側で、DQSパルスに付けた矢印が示すように、較正処理では、CKに対してDQSパルス遅延を掃引することにより、標準的な位相検出器の出力においてゼロから1への遷移を見つける。ゼロから1への遷移が検出されることは、CKとDQSとの間の位相が正確に揃っていることを示す。

## [0051]

なお、メモリ制御装置は、DQSパルスがアサートされる1クロックサイクル前に、WE#信号900をアサートする。メモリ制御装置とDRAMとの間を信号が伝搬した後、CK信号201とDQS信号203との間には、1クロックサイクルを超えるスキューが存在する。図9の回路に示すように、WE#信号900は、ステージされ、反転されて、所望のCK時間スロットに窓を掛ける。その結果として得られる窓信号PDENにより、図10の下部に示したように、遷移の誤検出が防止される。

#### [0052]

### 位相検出回路 2

図11は、DRAM内で利用可能な位相検出回路の一実施形態を、関連するタイミング図とともに示したものである。この実施形態は、図9に示した実施形態と同様であり、WE#信号900が、(フリップフロップ901を通ってではなく)DRAM上のWE#信号900用ステージ回路を通ってステージされている点が異なる。

#### [0053]

より具体的に説明すると、WE#信号900は、第1の可変長シフタ1102および第2の可変長シフタ1104を通ってステージされ、第1の可変長シフタ11002は、追加遅延(AL)用であって遅延はALにプログラムされており、第2の可変長シフタ11004は、CAS書き込み遅延(CWL)用であって、遅延は=CWL-1にプログラムされており、この「1」は、フリップフロップ902を通る際の遅延に相当する。追加遅延は、カラムコマンド(たとえば、読み出しコマンドや書き込みコマンド)がDRAMで受信されてから、そのコマンドが内部で適用またはポストされるまでのプログラム可能な遅延であり、そのコマンドが内部で適用またはポストされてから、その書き込みは遅延であり、そのコマンドが内部で適用またはポストされてから、その書き込みに関連付けられたデータがDRAMによってサンプリングされるまでのプログラム可能な遅延である。このステージ回路を用いることにより、メモリ制御装置は、通常動作時と同じ書き込み遅延で書き込み較正処理を実行することが可能である。

#### [0054]

## 較正処理

図12は、書き込みタイミング較正処理の一実施形態を示すフローチャートである。この処理では、クロック信号、マーキング信号、およびデータストローブ信号を、メモリ制御装置からメモリチップに送信する(オペレーション1202)。次に、マーキング信号を用いて、クロック信号の中の特定のクロックサイクルに「窓を掛ける」(オペレーション1204)。これにより、窓掛けクロック信号が生成される。

#### [0055]

次に、データストローブ信号上のパルスを用いて、窓掛けクロック信号をメモリエレメントに捕捉する(オペレーション1206)。次に、この捕捉した窓掛けクロック信号を、フィードバック信号としてメモリ制御装置に戻す(オペレーション1208)。

20

10

30

40

#### [0056]

次に、メモリ制御装置は、このフィードバック信号を用いて、クロック信号とデータストローブ信号との間のタイミング関係を較正する(オペレーション1210)。たとえば、この較正処理は、クロック信号に対して様々に遅延させたパルスをデータストローブ信号上にアサートすることを伴って、データストローブ信号とクロック信号とが揃っていることを示す遷移を、位相検出器の出力において探すことが可能である。

#### [0.057]

なお、図1~12に含まれる構成要素またはオペレーションは、より少なくても、より多くてもよい。さらに、2つ以上の構成要素またはオペレーションを1つの構成要素またはオペレーションにまとめることが可能であり、かつ/または、1つまたは複数の構成要素またはオペレーションの位置を変更することが可能である。

#### [0058]

さらに、図1~12に示した構成要素および/または機能性は、アナログ回路および/またはデジタル回路で実装可能である。さらに、図1~12の構成要素および/または機能性は、ハードウェアおよび/またはソフトウェアで実装可能である。

#### [0059]

本明細書に記載のデバイスおよび回路は、当該技術分野において利用可能なコンピュータ支援設計ツールを用いて実装可能であり、そのような回路のソフトウェア記述を含むコンピュータ可読ファイルによって具現化可能である。これらのソフトウェア記述は、挙動レベル、レジスタ転送レベル、論理コンポーネントレベル、トランジスタレベル、およびレイアウトジオメトリレベルの記述であってよい。さらに、ソフトウェア記述は、記憶媒体に格納したり、搬送波で伝達したりすることが可能である。

#### [0060]

そのような記述が実装可能なデータ形式としては、Cのような挙動言語をサポートしている形式、VerilogやVHDLのようなレジスタ転送レベル(RTL)言語をサポートしている形式、ジオメトリ記述言語(GDSII、GDSIII、GDSIV、CIF、MEBESなど)をサポートしている形式、および他の好適な形式および言語が含まれ、これらに限定されない。さらに、そのようなファイルを機械可読媒体でデータ転送することは、インターネット上の多用な媒体(たとえば、電子メール)により電子的に行われることが可能である。なお、実際のファイルは、機械可読媒体(4mm磁気テープ、8mm磁気テープ、3.5インチフロッピー(登録商標)媒体、CD、DVDなど)に実装可能である。

#### [0061]

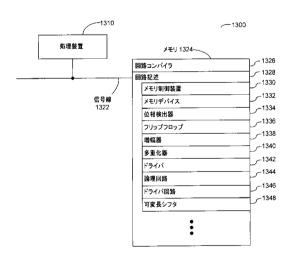

図13は、そのようなコンピュータ可読ファイルを格納するシステム1300の一実施形態を示すブロック図である。本システムは、少なくとも1つのデータ処理装置または中央処理ユニット(CPU)1310と、メモリ1324と、これらの構成要素を互いに結合する1つまたは複数の信号線または通信バス1322とを含むことが可能である。メモリ1324は、ランダムアクセスメモリおよび / または不揮発性メモリを含むことが可能であり、たとえば、ROM、RAM、EPROM、EEPROM、フラッシュ、1つまたは複数のスマートカード、1つまたは複数の磁気ディスク記憶デバイス、および / または1つまたは複数の光学式記憶デバイスを含むことが可能である。

#### [0062]

メモリ1324は、回路コンパイラ1326および回路記述1328を格納することが可能である。回路記述1328は、回路の記述、すなわち、上述の回路のサブセットを含むことが可能である。具体的には、回路記述1328は、1つまたは複数のメモリ制御装置1330、1つまたは複数のメモリデバイス1332、1つまたは複数の位相検出器1334、1つまたは複数のフリップフロップ1336、1つまたは複数の増幅器1338、1つまたは複数の多重化器1340、1つまたは複数のドライバ1342、1つまたは複数の論理回路1344、1つまたは複数のドライバ回路1346、および/または1つまたは複数の可変長シフタ1348の回路記述を含むことが可能である。

10

20

30

## [0063]

なお、システム1300に含まれる構成要素は、より少なくても、より多くてもよい。 さらに、2つ以上の構成要素を単一の構成要素にまとめることが可能であり、かつ/また は、1つまたは複数の構成要素の位置を変更することが可能である。

## [0064]

【図1】

前述の実施形態の記載は、例示および説明のみを目的としたものである。これらは、網羅的であることも、本明細書を開示の形態に限定することも意図していない。したがって、当業者にとっては、様々な修正や変形形態が自明であろう。さらに、上述の開示は、本明細書を限定することを意図するものではない。本明細書の範囲は、添付の請求項によって定義される。

【図2】

【図5】 【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

## フロントページの続き

(72)発明者 グプタ,アロク

アメリカ合衆国,カリフォルニア州 94536,フレモント,サマー ホーリー コモン 37 549

(72)発明者 シャエファー,イアン

アメリカ合衆国,カリフォルニア州 95030,ロス ガトス,ジャクソン ストリート 23

(72)発明者 ウー,スティーブン,シー.

アメリカ合衆国,カリフォルニア州 95070,サラトガ,カントリー スクワイアー レーン 12180

#### 審査官 渡部 博樹

(56)参考文献 特開2007-280289(JP,A)

特開2007-164697(JP,A)

特表2001-505693(JP,A)

特開2003-050739(JP,A)

特開2006-099245(JP,A)

(58)調査した分野(Int.CI., DB名)

G06F12/00-G06F12/06

G06F13/16-G06F13/18

G11C 11/401

G11C 11/4076