# (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4049010号 (P4049010)

(45) 発行日 平成20年2月20日(2008.2.20)

(24) 登録日 平成19年12月7日(2007.12.7)

| (51) Int.Cl. |               | F I            |          |                         |

|--------------|---------------|----------------|----------|-------------------------|

| GO9G 3/30    | (2006.01)     | GO9G           | 3/30     | J                       |

| GO9G 3/20    | (2006.01)     | GO9G           | 3/30     | K                       |

| HO1L 51/50   | (2006.01)     | GO9G           | 3/20     | 6 1 1 J                 |

|              |               | G09G           | 3/20     | 623L                    |

|              |               | GO9G           | 3/20     | 623R                    |

|              |               |                |          | 請求項の数 2 (全 19 頁) 最終頁に続く |

| (21) 出願番号    | 特願2003-125979 | (P2003-125979) | (73) 特許村 | 権者 000002185            |

| (22) 出願日     | 平成15年4月30日    | ` ′            |          | ソニー株式会社                 |

| (65) 公開番号    | 特開2004-333594 | ` '            | l        | 東京都港区港南1丁目7番1号          |

| (43) 公開日     | 平成16年11月25日   | , ,            | (74) 代理丿 | 人 100094053             |

| 審査請求日        | 平成17年3月7日(2   | 2005.3.7)      |          | 弁理士 佐藤 隆久               |

|              |               |                | (72) 発明者 |                         |

|              |               |                |          | 東京都品川区北品川6丁目7番35号 ソ     |

|              |               |                |          | 二一株式会社内                 |

|              |               |                | (72) 発明者 |                         |

|              |               |                |          | 東京都品川区北品川6丁目7番35号 ソ     |

|              |               |                |          | 二一株式会社内                 |

|              |               |                | (72) 発明者 |                         |

|              |               |                |          | 東京都品川区北品川6丁目7番35号 ソ     |

|              |               |                |          | 二一株式会社内                 |

|              |               |                |          | 最終頁に続く                  |

# (54) 【発明の名称】表示装置

# (57)【特許請求の範囲】

# 【請求項1】

映像信号が信号電流として供給される表示装置であって、

マトリクス状に複数配列された画素回路と、

上記画素回路のマトリクス配列に対して列毎に配線され、輝度情報に応じた信号電流が供給されるデータ線と、

上記データ線に対応して設けられ、入力映像信号電流をサンプルホールドする複数のサンプルホールド回路を有し、各サンプルホールド回路を順次動作させて、全てのサンプルホールド回路に映像信号を点順次にサンプルホールドさせ、上記複数のサンプルホールド回路にサンプルホールドされた電流値を対応するデータ線に出力させる水平セレクタと、を有し、

上記各サンプルホールド回路は、

ソースが所定電位に接続された電界効果トランジスタと、

上記電界効果トランジスタのドレインとゲートとの間に接続された第 1 のスイッチと、

上記電界効果トランジスタのドレインと上記信号電流の供給線との間に接続された 第 2 のスイッチと、

上記電界効果トランジスタのゲートと所定電位との間に接続されたキャパシタと、 サンプルホールド動作が終了し、他のサンプルホールド回路がサンプルホールド動 作を行っている間に、サンプリングされた信号電流に相当する電流を上記電界効果トラン

ジスタのドレインに供給するリーク除去回路と、を有し、

上記リーク除去回路は、

所定電位と上記電界効果トランジスタのドレインとの間に接続されたダイオード接続されたトランジスタと第3のスイッチが直列に接続されている

表示装置。

#### 【請求項2】

映像信号が信号電流として供給される表示装置であって、

マトリクス状に複数配列された画素回路と、

上記画素回路のマトリクス配列に対して列毎に配線され、輝度情報に応じた信号電流が 供給されるデータ線と、

10

20

30

上記データ線に対応して設けられ、入力映像信号電流をサンプルホールドする複数のサンプルホールド回路を有し、各サンプルホールド回路を順次動作させて、全てのサンプルホールド回路に映像信号を点順次にサンプルホールドさせ、上記複数のサンプルホールド回路にサンプルホールドされた電流値を対応するデータ線に出力させる水平セレクタと、を有し、

上記各サンプルホールド回路は、

ソースが所定電位に接続された第1の電界効果トランジスタと、

<u>ソースが上記第1の電界効果トランジスタのドレインに接続された第2の電界効果</u>トランジスタと、

上記第2の電界効果トランジスタのドレインとゲートとの間に接続された第1のス イッチと、

上記第2の電界効果トランジスタのドレインと上記信号電流の供給線との間に接続された第2のスイッチと、

上記第1の電界効果トランジスタのドレインとゲートとの間に接続された第3のス イッチと、

上記第1の電界効果トランジスタのゲートと所定電位との間に接続された第1のキャパシタと、

上記第2の電界効果トランジスタのゲートと所定電位との間に接続された第2のキャパシタと、

サンプルホールド動作が終了し、他のサンプルホールド回路がサンプルホールド動作を行っている間に、サンプリングされた信号電流に相当する電流を上記第2の電界効果トランジスタのドレインに供給するリーク除去回路と、を有し、

上記リーク除去回路は、

上記リーク除去回路は、所定電位と上記<u>第2の</u>電界効果トランジスタのドレインとの間に接続されたダイオード接続されたトランジスタと<u>第4の</u>スイッチが直列に接続されている

表示装置。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

40

50

本発明は、有機 EL (Elect rolumi nescence )ディスプレイなどの、電流値によって輝度が制御される電気光学素子を有する画素回路がマトリクス状に配列された画像表示装置のうち、特に各画素回路内部に設けられた絶縁ゲート型電界効果トランジスタによって電気光学素子に流れる電流値が制御される、いわゆるアクティブマトリクス型画像表示装置に関するものである。

[0002]

#### 【従来の技術】

画像表示装置、たとえば液晶ディスプレイなどでは、多数の画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に光強度を制御することによって画像を表示する。 これは有機 EL ディスプレイなどにおいても同様であるが、有機 EL ディスプレイは各画 素回路に発光素子を有する、いわゆる自発光型のディスプレイであり、液晶ディスプレイに比べて画像の視認性が高い、バックライトが不要、応答速度が速い、等の利点を有する

また、各発光素子の輝度はそれに流れる電流値によって制御することによって発色の階調を得る、すなわち発光素子が電流制御型であるという点で液晶ディスプレイなどとは大きく異なる。

#### [0003]

有機 E L ディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とが可能であるが、前者は構造が単純であるものの、大型かつ高精細のディスプレイの実現が難しいなどの問題がある。

このため、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子、一般にはTFT(Thin Film Transistor、薄膜トランジスタ)によって制御する、アクティブマトリクス方式の開発が盛んに行われている。

### [0004]

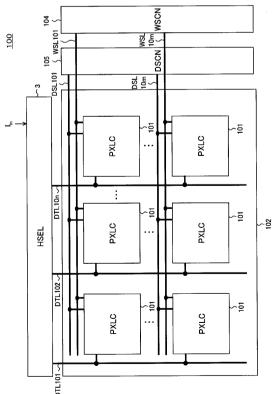

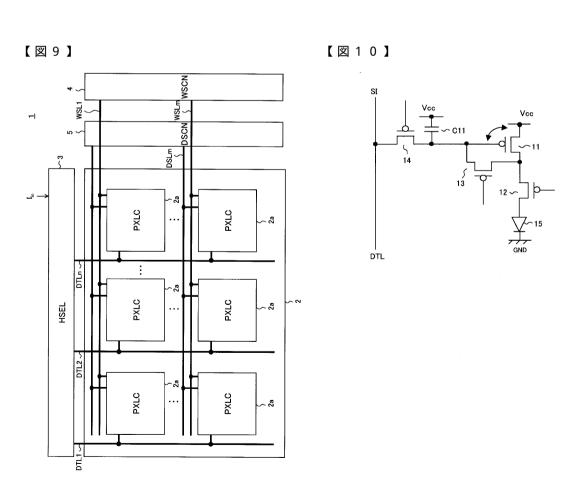

図9は、電流駆動方式を採用した有機EL表示装置の構成を示すブロック図である。この表示装置1は、図9に示すように、画素回路(PXLC)2aがm×nのマトリクス状に配列された画素アレイ部2、水平セレクタ(HSEL)3、ライトスキャナ(WSCN)4、ドライブスキャナ(DSCN)5、水平セレクタ3により選択され輝度情報に応じたデータ信号が供給されるデータ線DTL1~DTLn、ライトスキャナ4により選択駆動される走査線WSL1~WSLm、およびドライブスキャナ5により選択駆動される駆動線DSL1~DSLm、を有する。

#### [0005]

図10は、図9の画素回路2aの一構成例を示す回路図である。

# [0006]

図10の画素回路2aは、pチャネル薄膜電界効果トランジスタ(以下、TFTという) 11~TFT14、キャパシタC11、発光素子である有機EL素子(OLED)15を 有する。また、図10において、DTLは入力信号が電流として伝播されるデータ線を示 している。

有機 E L 素子は多くの場合整流性があるため、OLED(Organic Light Emitting Diode)と呼ばれることがあり、図10その他では発光素子としてダイオードの記号を用いているが、以下の説明においてOLEDには必ずしも整流性を要求するものではない。

図10ではTFT11のソースが電源電位VCC(電源電圧VCCの供給ライン)に接続され、発光素子15のカソード(陰極)は接地電位GNDに接続されている。図10の画素回路2aの動作は以下の通りである。

# [0007]

入力信号(電流信号)SIの書き込み時には、TFT12を非導通に保持した状態で、TFT13,TFT14を導通状態に保持する。

これにより、駆動(ドライブ)トランジスタであるTFT11に信号電流に応じた電流が 流れる。

このとき、TFT11のゲートとドレインは導通状態にあるTFT13により電気的に接続されており、TFT11は飽和領域にて駆動している。

よって、下記式1に基づいて入力電流に相当するゲート電圧が書き込まれ、画素容量であるキャパシタ C 1 1 に保持される。

その後、TFT14を非導通状態に保持して、TFT12を導通状態に保持する。

これにより、入力信号電流に応じた電流がTFT12と発光素子15に流れ、発光素子15はその電流値に応じた輝度で発光する。

上記のように、TFT14を導通させてデータ線に与えられた輝度情報を画素内部に伝える操作を、以下「書き込み」と呼ぶ。

# [0008]

この画素回路2aでは、ドライブトランジスタ11のしきい値Vthや移動度μのバラツ

10

20

30

40

キが補正される。

[0009]

#### 【数1】

Ids =  $1 / 2 \cdot \mu (W / L) Cox (Vgs - | Vth | )^2 ... (1)$

### [0010]

ここで、 $\mu$  はキャリアの移動度を、C o x は単位面積当たりのゲート容量を、W はゲート幅を、L はゲート長を、V g s は T F T 1 1 のゲート・ソース間電圧を、V t h は T F T 1 1 のしきい値 V t h をそれぞれ示している。

(4)

# [0011]

この方式では、映像信号が電流値 I i n としてパネルの水平セレクタ 3 に入力される。入力された電流信号は、水平セレクタ 3 にてサンプルホールドされ、全段がサンプルホールドされた後に、同時に画素が接続されたデータ線 D T L に電流値が出力される。

#### [0012]

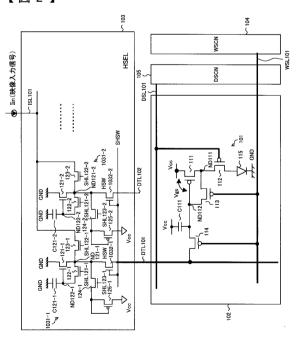

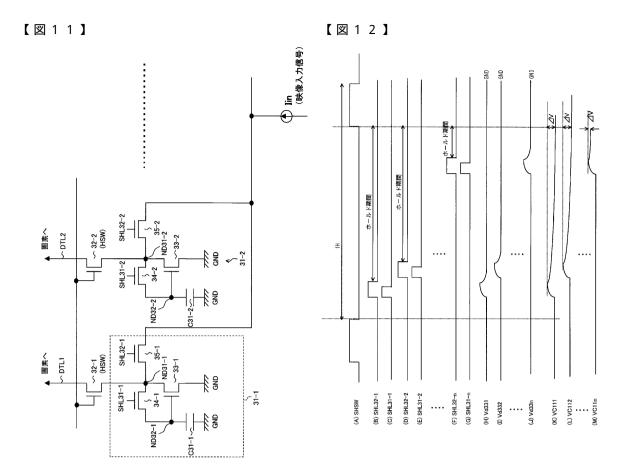

図11は、水平セレクタ3の要部の構成を示す回路図である。

水平セレクタ3は、図11に示すように、画素回路のマトリクス配列に対して列毎に配線され、輝度情報に応じたデータ信号が供給されるデータ線DTL1,DTL2、~、DTLnに対応して設けられた、電流サンプルホールド回路31-1,31-2、~、31-nと、nチャネルTFTからなる水平スイッチ(HSW)32-1,32-2、~、32-nを有している。

# [0013]

電流サンプルホールド回路 3 1 - 1 は、図 1 1 に示すように、TFT 3 3 - 1 , TFT 3 4 - 1、TFT 3 5 - 1、キャパシタ C 3 1 - 1、およびノードN D 3 1 - 1 , N D 3 2 - 1を有している。

同様に、電流サンプルホールド回路 3 1 - 1 は、図 1 1 に示すように、TFT 3 3 - 2 , TFT 3 4 - 2 、TFT 3 5 - 2 、キャパシタ C 3 1 - 2 、およびノード N D 3 1 - 2 , N D 3 2 - 2 を有している。

そして、図示しないが、電流サンプルホールド回路 3 1 - n は、TFT 3 3 - n , TFT 3 4 - n、TFT 3 5 - n、キャパシタ C 3 1 - n、およびノード N D 3 1 - n , N D 3 2 - nを有している。

# [0014]

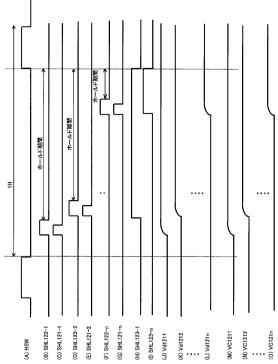

この水平セレクタ3のサンプルホールド動作を、図12(A)~(M)に関連付けて説明する。

なお、図12(A)のSHSWは水平スイッチの切換信号を示している。また、図12(H)は第1列目のTFT33-1のドレイン電位Vd331を、図12(I)は第2列目のTFT33-2のドレイン電位Vd332を、図12(J)は第n列目のTFT33-nのドレイン電位Vd33nを、図12(K)は第1列目のキャパシタC11-1の電位VC111を、図12(L)は第2列目のキャパシタC11-2の電位VC112を、図12(M)は第n列目のキャパシタC11-nの電位VC11nを、それぞれ示している

### [0015]

図 1 2 ( A ) に示すように、切換信号 S H S W を低レベルとして全水平スイッチ H S W をオフさせた状態で、図 1 2 ( B ) , ( C ) に示すように、第 1 列目の電流サンプルホールド回路 3 1 - 1 の T F T 3 4 - 1 , 3 5 - 1 を導通状態とする(オンさせる)。

このとき、入力信号電流 Iin が電流サンプルホールド回路 31-1 内に流れる。このとき、TFT33-1 は、TFT34-1 を介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は上記式 1 に基づいて決定され、図 12 ( K ) に示すように、キャパシタ C 3 1-1 に保持される。

所定のゲート電圧がキャパシタ C 3 1 - 1 に書き込まれた後に、サンプルホールド線 S H

20

10

30

40

L 3 1 - 1 を低レベルとしてTFT 3 4 - 1 を非導通状態とし、その後にサンプルホールド線SHL 3 2 - 1 を低レベルとしてTFT 3 5 - 1 を非導通状態とする。

#### [0016]

次に、同様に、図12(D),(E)に示すように、第2列目の電流サンプルホールド回路31-2のTFT34-2,35-2が接続されたサンプルホールド線SHL31-2,32-2を高レベルとして、TFT34-2,35-2を導通状態とする(オンさせる)。

このとき、入力信号電流 I i n が電流サンプルホールド回路 3 1 - 2 内に流れる。このとき、TFT 3 3 - 2 は、TFT 3 4 - 2 を介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は上記式 1 に基づいて決定され、図 1 2 ( L ) に示すように、キャパシタ C 3 1 - 2 に保持される。

所定のゲート電圧がキャパシタ C 3 1 - 2 に書き込まれた後に、サンプルホールド線 S H L 3 1 - 2 を低レベルとして T F T 3 4 - 2 を非導通状態とし、その後にサンプルホールド線 S H L 3 2 - 2 を低レベルとして T F T 3 5 - 2 を非導通状態とする。

以下、隣接サンプルホールド回路が順次動作してゆき、全ての回路に映像信号 Iinが点順次にサンプルホールドされる。

その後、図12(A)に示すように、水平スイッチHSWが全段同時にオンされ、TFT33-1~TFT33-nが定電流源として機能し、図13に示すように、サンプルホールドされた電流値が各データ線DTL1~DTLnに出力される。

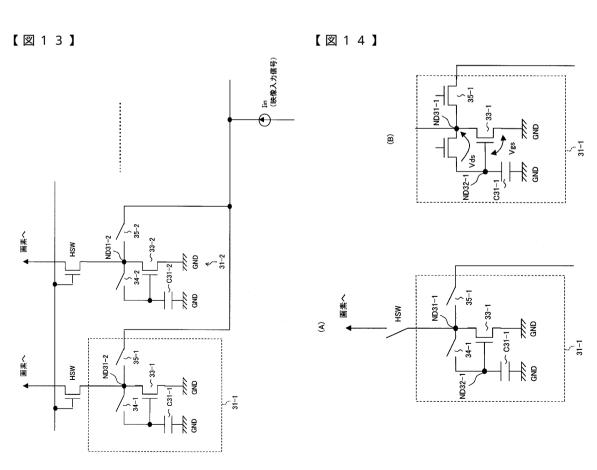

# [0017]

【発明が解決しようとする課題】

しかしながら、上述した水平セレクタ3においては、定電流源として機能するTFT33 (-1~-n)のドレイン電位、特に、サンプルホールド動作が先に行われるTFT33 のドレイン電位が降下し、一定に保持することができないという不利益がある この課題についてさらに詳細に説明する。

### [0018]

ここで、第 1 列目の電流サンプルホールド回路 3 1 - 1 のサンプルホールド時の各ノードの電位を調べる。

電流サンプルホールド回路 3 1 - 1 では、図 1 4 ( A ) に示すように、TFT 3 5 - 1 が非導通状態に保持されて入力電流 I i n がサンプルホールドされる。この期間中、TFT 3 3 - 1 はオンし続けているために、TFT 3 3 - 1 のドレイン電位(ND 3 1 - 1 の電位)は供給源がなくなり、接地電位 G N D レベルまで下降してしまう。

このとき T F T 3 4 - 1 に注目する。 T F T 3 4 - 1 はオフしており、キャパシタ C 3 1 - 1 には電流 I i n に相当するゲート電位が保持されている。

# [0019]

しかしながら、ノードND31-1の電位が接地電位GNDレベルまで落ちることで、TFT34-1には、図14(B)に示すように、ドレイン・ソース間電圧Vdsが印加されてしまい、TFT34-1にはリーク電流が流れる。このリーク電流がキャパシタC31-1から流れ出すことで、TFT33-1のゲート電圧は減少してしまう。これにより、TFT33-1のゲート・ソース間電圧Vgsはサンプルホールド時よりも減少してしまい、その後水平スイッチHSWがオンして飽和領域になったとしても、電流Iinより小さい電流値しか流れなくなってしまう。このリーク量はリーク時間に比例する。

# [0020]

サンプルホールド回路は前述したように点順次にて動作するので、スキャン開始部とスキャン終了部とでは、各容量にゲート電位が保持されている時間が異なる。すなわち、図12(K)~(L)に示すように、スキャン開始部では終了部に比べて保持時間が長くなる

そのため、スキャン開始部ではリーク時間も長くなり、ゲート電圧降下量がスキャン終了部に比べて大きくなる。つまり、画面全体に単色のラスター表示をしたとしても、図15に示すように、スキャン終了部に向かって輝度がグラデーションしてしまう。

10

20

30

40

10

20

30

40

50

特に、有機EL等を駆動するTFTではリーク電流が高いために、この問題は顕著に現れる。

# [0021]

この問題点は有機 ELに関わらず、電流のサンプルを行う場面ではどんな時も問題となる。

たとえば、電流を点順次にてサンプリングし、一括で出力する場合には同様の理由でサンプリング開始部と終了部とで出力の電流値が異なってしまう。

# [0022]

本発明は、かかる事情に鑑みてなされたものであり、その目的は、他の回路のサンプリング期間も、定電流源として機能する出力トランジスタのドレイン電位を一定に保つことができ、出力トランジスタのゲート電位のリークによる変化を抑えることが可能で、出力段の電流値バラツキのない、均一な電流源を得ることができ、スキャン終了部に向かって輝度むらが発生しない高品位な画像を表示することが可能な表示装置を提供することにある

### [0023]

#### 【課題を解決するための手段】

上記目的を達成するため、本発明の第1の観点は、映像信号が信号電流として供給され る表示装置であって、マトリクス状に複数配列された画素回路と、上記画素回路のマトリ クス配列に対して列毎に配線され、輝度情報に応じた信号電流が供給されるデータ線と、 上記データ線に対応して設けられ、入力映像信号電流をサンプルホールドする複数のサン プルホールド回路を有し、各サンプルホールド回路を順次動作さて。全てのサンプルホー ルド回路に映像信号を点順次にサンプルホールドさせ、上記複数のサンプルホールド回路 にサンプルホールドされた電流値を対応するデータ線に出力させる水平セレクタと、を有 し、上記各サンプルホールド回路は、ソースが所定電位に接続された電界効果トランジス タと、上記電界効果トランジスタのドレインとゲートとの間に接続された第1のスイッチ と、上記電界効果トランジスタのドレインと上記信号電流の供給線との間に接続された第 2 のスイッチと、上記電界効果トランジスタのゲートと所定電位との間に接続されたキャ パシタと、サンプルホールド動作が終了し、他のサンプルホールド回路がサンプルホール ド動作を行っている間に、サンプリングされた信号電流に相当する電流を上記電界効果ト ランジスタのドレインに供給するリーク除去回路と、を有し、上記リーク除去回路は、所 定電位と上記電界効果トランジスタのドレインとの間に接続されたダイオード接続された トランジスタと第3のスイッチが直列に接続されている。

#### [0025]

好適には、映像信号が信号電流として供給される表示装置であって、マトリクス状に複 数配列された画素回路と、上記画素回路のマトリクス配列に対して列毎に配線され、輝度 情報に応じた信号電流が供給されるデータ線と、上記データ線に対応して設けられ、入力 映像信号電流をサンプルホールドする複数のサンプルホールド回路を有し、各サンプルホ ールド回路を順次動作させて、全てのサンプルホールド回路に映像信号を点順次にサンプ ルホールドさせ、上記複数のサンプルホールド回路にサンプルホールドされた電流値を対 応するデータ線に出力させる水平セレクタと、を有し、上記各サンプルホールド回路は、 ソースが所定電位に接続された第1の電界効果トランジスタと、ソースが上記第1の電界 効果トランジスタのドレインに接続された第2の電界効果トランジスタと、上記第2の電 界効果トランジスタのドレインとゲートとの間に接続された第1のスイッチと、上記第2 の電界効果トランジスタのドレインと上記信号電流の供給線との間に接続された第2のス イッチと、上記第1の電界効果トランジスタのドレインとゲートとの間に接続された第3 のスイッチと、上記第1の電界効果トランジスタのゲートと所定電位との間に接続された 第1のキャパシタと、上記第2の電界効果トランジスタのゲートと所定電位との間に接続 された第2のキャパシタと、サンプルホールド動作が終了し、他のサンプルホールド回路 がサンプルホールド動作を行っている間に、サンプリングされた信号電流に相当する電流 を上記第2の電界効果トランジスタのドレインに供給するリーク除去回路と、を有し、上 記リーク除去回路は、上記リーク除去回路は、所定電位と上記第2の電界効果トランジスタのドレインとの間に接続されたダイオード接続されたトランジスタと第4のスイッチが直列に接続されている。

# [0027]

本発明によれば、たとえば第1列目のサンプルホールド回路の第1および第2のスイッチ を導通状態とする(オンさせる)。

このとき、入力信号電流がサンプルホールド回路内に流れる。このとき、電界効果トランジスタは、第1のスイッチを介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は上記式1に基づいて決定され、キャパシタに保持される。

所定のゲート電圧がキャパシタに書き込まれた後に、たとえば第 1 のスイッチを非導通状態とし、その後に第 2 のスイッチを非導通状態とする。

次に、同様に、第2列目のサンプルホールド回路の第1および第2のスイッチを導通状態とする(オンさせる)。

このとき、入力信号電流が第2列目のサンプルホールド回路内に流れる。このとき、電界効果トランジスタは、第1のスイッチを介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は上記式1に基づいて決定され、キャパシタに保持される。

所定のゲート電圧がキャパシタに書き込まれた後に、たとえば第 1 のスイッチを非導通状態とし、その後に第 2 のスイッチを非導通状態とする。

# [0028]

以下、隣接サンプルホールド回路が順次動作してゆき、全ての回路に映像信号が点順次に サンプルホールドされる。

そして、自段のサンプルホールドが終了し、他段がサンプルホールドを行っている期間に、たとえばサンプルホールドが終了したサンプルホールド回路は、第3のスイッチを導通 状態とする。

すると、ダイオード接続されているトランジスタは、電界効果トランジスタを含む定電流源に従った電流 I i n が流れる。ここでは定電流源には入力電流がサンプルホールドされているので、ダイオード接続されているトランジスタと、定電流源を構成する電界効果トランジスタには電流 I i n が流れる。

このとき、ダイオード接続されたトランジスタにはサンプリングされた電流 I i n に相当する定電流が流れる。トランジスタは飽和領域にて動作するので、このトランジスタのゲート電圧(ドレイン電圧)は式 1 に基づき動作点が決定される。このゲート電位は電界効果トランジスタのドレイン電位と等しくなる。

ここで、電界効果トランジスタのドレイン電位が電界効果トランジスタのゲート電圧になるべく等しくなるようにダイオード接続されたトランジスタサイズの設計を行うことで、 第1のスイッチを構成するたとえばトランジスタのソースとドレインの電圧差を抑制する ことができる。

以上より、電流の点順次サンプリングにおいても、スキャン開始と終了部ブロックとでリーク量を殆ど変わらなくでき、均一な出力電流を得ることができる(。

その後、全サンプルホールド回路の電界効果トランジスタが定電流源として機能し、サン プルホールドされた電流値が各データ線に並列的に出力される。

これにより、スキャン終了部に向かって輝度むらが発生しない高品位な画像を表示することが可能となる。

# [0029]

#### 【発明の実施の形態】

以下、本発明の実施形態を添付図面に関連付けて説明する。

#### [0030]

# 第1実施形態

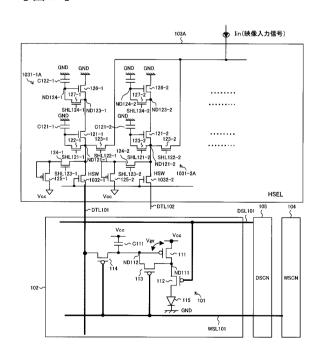

図1は、本第1の実施形態に係る電流駆動方式を採用した有機 EL表示装置の構成例を示すブロック図である。

10

20

30

40

図2は、図1の有機EL表示装置において本実施形態に係る画素回路および水平セレクタの具体的構成を示す回路図である。

### [0031]

この表示装置100は、図1および図2に示すように、画素回路(PXLC)101がm×nのマトリクス状に配列された画素アレイ部102、水平セレクタ(HSEL)103、ライトスキャナ(WSCN)104、ドライブスキャナ(DSCN)105、水平セレクタ103により選択され輝度情報に応じたデータ信号が電流信号として順次に供給されるデータ線DTL101~DTL10n、ライトスキャナ104により選択駆動される走査線WSL101~WSL10m、およびドライブスキャナ105により選択駆動される駆動線DSL101~DSL10mを有する。

[0032]

なお、画素アレイ部102において、画素回路101はm×nのマトリクス状に配列されるが、図1においては図面の簡単化のために2×3のマトリクス状に配列した例を示している。

また、図2においては図面に簡単化のために、水平セレクタ103は、第1列と第2列目の電流サンプルホールド回路と水平スイッチHSWのみを記載しているが第n列目まで同様の構成を有する電流サンプルホールド回路が各DTL101~DTL10nに対応して配置される。

また、図 2 においても、図面の簡単化のために一つの画素回路の具体的な構成を示している。

[0033]

本第1の実施形態に係る画素回路101は、図2に示すように、pチャネルTFT111~TFT114、キャパシタC111、有機EL素子(OLED:電気光学素子)からなる発光素子115、第1のノードND111、および第2のノードND112を有する。また、図2において、DTL101はデータ線を、WSL101は走査線を、DSL101は駆動線、SHLサンプルホールド線をそれぞれ示している。

[0034]

画素回路101において、電源電位 V CCと接地電位 G N D との間にTFT111、第1の ノード N D 1 1 1、TFT112、および発光素子115が直列に接続されている。 具体的には、ドライブトランジスタとしてのTFT111のソースが電源電圧 V CCの供給 ラインに接続され、ドレインが第1のノード N D 1 1 1に接続されている。TFT112のソースが第1のノード N D 1 1 1に接続され、ドレインが発光素子115のアノードに接続され、発光素子115のカソードが接地電位 G N D に接続されている。そして、TF

T111のゲートが第2のノードND112に接続され、TFT112のゲートが第2の 制御線としての駆動線DSL101に接続されている。

第 1 のノードND 1 1 1 と第 2 のノードND 1 1 2 とに、TFT 1 1 3 ソース・ドレインが接続され、TFT 1 1 3 のゲートが走査線WSL 1 0 1 に接続されている。

キャパシタ C 1 1 1 の第 1 電極が第 2 の ノード N D 1 1 2 に接続され、第 2 電極が電源電位 V CC に接続されている。

データ線 D T L 1 0 1 と第 2 の ノード N D 1 1 2 とに T F T 1 1 4 の ソース・ドレインが接続され、 T F T 1 1 4 の ゲートが走査線 W S L 1 0 1 に接続されている。

[0035]

水平セレクタ103は、図2に示すように、画素回路のマトリクス配列に対して列毎に配線され、輝度情報に応じたデータ信号が供給されるデータ線DTL101,DTL012、~、DTL10nに対応して設けられた、電流サンプルホールド回路1031-1,1031-2、~、1031-nと、nチャネルTFTからなる水平スイッチ(HSW)1032-1,1032-2、~、1032-nを有している。

[0036]

電流サンプルホールド回路 3 1 - 1 は、図 2 に示すように、 n チャネルTFT 1 2 1 - 1 ~ T FT 1 2 4 - 1、 p チャネルTFT 1 2 5 - 1、キャパシタ C 1 2 1 - 1、およびノ

10

20

30

40

ードND121-1,ND122-1を有している。

#### [0037]

電流サンプルホールド回路 1 0 3 1 - 2 は、図 2 に示すように、 n チャネルTFT 1 2 1 - 2 ~ TFT 1 2 4 - 2 、 p チャネルTFT 1 2 5 - 2 、キャパシタ C 1 2 1 - 2 、およびノードND 1 2 1 - 2 , ND 1 2 2 - 2 を有している。

そして、図示しないが、電流サンプルホールド回路1031-nは、nチャネルTFT1 21-n~TFT124-n、pチャネルTFT125-n、キャパシタC121-n、 およびノードND121-n,ND122-nを有している。

TFT121(-1~-n)が本発明に係る電界効果トランジスタを構成し、TFT12 2(-1~-n)が第1のスイッチを構成し、TFT123(-1~-n)が第2のスイッチを構成し、TFT124(-1~-n)が第3のスイッチを構成し、TFT125(-1~-n)がダイオード接続されたトランジスタを構成する。

#### [0038]

電流サンプルホールド回路 1 0 3 1 - 1 において、TFT 1 2 1 - 1 のソースが接地電位 GNDに接続され、ドレインがノードND 1 2 1 - 1 に接続され、ゲートがノードND 1 2 2 - 1 に接続されている。ノードND 1 2 1 - 1 とノードND 1 2 2 - 1 とにTFT 1 2 2 - 1 のソース・ドレインがそれぞれ接続されている。TFT 1 2 2 - 1 のゲートがサンプルホールド線SHL 1 2 1 - 1 に接続されている。

キャパシタ C 1 2 1 - 1 の 第 1 電極 が ノード N D 1 2 2 - 1 に接続され、第 2 電極 が接地 電位 G N D に接続されている。

ノードND121 - 1 と入力電流信号の供給線ISL101とにTFT123のソース・ドレインがそれぞれ接続されている。TFT123のゲートがサンプルホールド線SHL122 - 1 に接続されている。

また、TFT125のソースが電源電圧VCCの供給ラインに接続され、TFT125のゲートとドレイン同士が接続されている。すなわち、TFT125はダイオード接続されている。

そして、TFT125のゲートとドレインの接続点とノードND121とにTFT124のソース・ドレインがそれぞれ接続され、TFT124のゲートがサンプルホールド線S HL123-1に接続されている。

また、ノードND121が水平スイッチ1032-1に接続されている。

#### [0039]

そして、TFT124とTFT125により本発明に係るリーク除去回路が構成されている。

### [0040]

なお、他の電流サンプルホールド回路1031-2~1031-nの接続形態は、上述した電流サンプルホールド回路1031-1と同様に行われることから、ここではその詳細は省略する。

### [0041]

次に、上記構成の動作を、水平セレクタの動作を中心に、図3(A)~(O)に関連付けて説明する。

# [0042]

なお、図 3 ( A )の S H S W は水平スイッチの切換信号を示している。また、図 3 ( J )は第 1 列目の T F T 1 2 1 - 1 のドレイン電位 V d 1 2 1 1 を、図 3 ( K )は第 2 列目の T F T 1 2 1 - 2 のドレイン電位 V d 1 2 1 2 を、図 3 ( L )は第 n 列目の T F T 1 2 1 - n のドレイン電位 V d 1 2 1 n を、図 3 ( M )は第 1 列目のキャパシタ C 1 1 - 1 の電位 V C 1 2 1 1 を、図 3 ( N )は第 2 列目のキャパシタ C 1 1 - 2 の電位 V C 1 2 1 2 を、図 3 ( O )は第 n 列目のキャパシタ C 1 1 - n の電位 V C 1 2 1 n を、それぞれ示している。

# [0043]

図3(A)に示すように、切換信号SHSWを低レベルとして全水平スイッチHSWをオ

20

10

30

40

フさせた状態で、図3(B),(C)に示すように、第1列目の電流サンプルホールド回路1031-1のTFT122-1,123-1が接続されたサンプルホールド線SHL121-1,122-1,123-1を導通状態とする(オンさせる)。

このとき、入力信号電流 I i n が電流サンプルホールド回路 1 0 3 1 - 1 内に流れる。このとき、TFT 1 2 1 - 1 は、TFT 1 2 2 - 1を介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は上記式 1 に基づいて決定され、図 3 (M)に示すように、キャパシタ C 1 2 1 - 1 に保持される。

所定のゲート電圧がキャパシタ C 1 2 1 - 1 に書き込まれた後に、サンプルホールド線 S H L 1 2 1 - 1を低レベルとしてTFT 1 2 2 - 1を非導通状態とし、その後にサンプルホールド線 S H L 1 2 2 - 1を低レベルとしてTFT 1 2 3 - 1を非導通状態とする。

[0044]

次に、同様に、図3(D),(E)に示すように、第2列目の電流サンプルホールド回路1031-2のTFT122-2,123-2が接続されたサンプルホールド線SHL121-2,122-2,123-2を導通状態とする(オンさせる)。

このとき、入力信号電流 I i n が電流サンプルホールド回路 1 0 3 1 - 2 内に流れる。このとき、TFT 1 2 1 - 2 は、TFT 1 2 2 - 2 を介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は上記式 1 に基づいて決定され、図 3 (N)に示すように、キャパシタ C 1 2 1 - 2 に保持される。

所定のゲート電圧がキャパシタ C 1 2 1 - 2 に書き込まれた後に、サンプルホールド線 S H L 1 2 1 - 2 を低レベルとして T F T 1 2 2 - 2 を非導通状態とし、その後にサンプルホールド線 S H L 1 2 2 - 2 を低レベルとして T F T 1 2 3 - 2 を非導通状態とする。

[0045]

以下、隣接サンプルホールド回路が順次動作してゆき、全ての回路に映像信号 Iinが点順次にサンプルホールドされる。

[0046]

本実施形態では、自段のサンプルホールドが終了し、他段がサンプルホールド行っている期間に、たとえばサンプルホールドが終了した電流サンプルホールド回路1031-1は、図3(H)に示すように、サンプルホールド線SHL123-1を高レベルとしてTFT124を導通状態とする。

すると、TFT125 - 1 は、ゲートとドレインが接続されているので、定電流源TFT 121 - 1 に従った電流が流れる。ここでは定電流源TFT121 - 1 には入力電流 I i n がサンプルホールドされているので、TFT125 - 1 とTFT121 - 1 には電流 I i n が流れる。

[0047]

このときの、TFT121 - 1のドレイン電圧であるノードND121の電位について考察する。

上述したように、TFT125-1にはサンプリングされた電流 I i n に相当する定電流が流れる。TFT125-1は飽和領域にて動作するので、TFT125-1のゲート電圧(ドレイン電圧)は式1に基づき動作点が決定される。このゲート電位はノードND121の電位と等しくなる。

ここで、ノードND121の電位がTFT121-1のゲート電圧になるべく等しくなるようにTFT125-1のサイズ設計を行う(ただしTFT121-1は飽和領域で駆動する)ことで、TFT122-1のソースとドレインの電圧差を抑制することができる。この電圧差が少なければ、TFT122-1のリーク量は大幅に抑制することができ、図3(M)~(O)に示すように、リークによるTFT121-1のゲート電圧の降下を抑えられる。

以上より、電流の点順次サンプリングにおいても、スキャン開始と終了部ブロックとでリーク量の殆ど変わらなくでき、均一な出力電流を得ることができる(。

10

20

30

40

その後、図3(A)に示すように、水平スイッチHSWが全段同時にオンされ、TFT121-1~TFT121-nが定電流源として機能し、サンプルホールドされた電流値が各データ線DTL101~DTL10nに出力される。

これにより、図4に示すように、スキャン終了部に向かって輝度むらが発生しない高品位な画像を表示することが可能となる。

#### [0048]

また、画素回路101において、入力信号(電流信号)SIの書き込み時には、駆動線DSL101を高レベルとしてTFT112を非導通に保持した状態で、走査線WSL101を低レベルとしてTFT113,TFT114を導通状態に保持する。

これにより、ドライブトランジスタであるTFT111に信号電流に応じた電流が流れる

このとき、TFT111のゲートとドレインは導通状態にあるTFT113により電気的に接続されており、TFT111は飽和領域にて駆動している。

よって、上記式1に基づいて入力電流に相当するゲート電圧が書き込まれ、画素容量であるキャパシタC111に保持される。

その後、TFT114を非導通状態に保持して、TFT12を導通状態に保持する。

これにより、入力信号電流に応じた電流がTFT112と発光素子115に流れ、発光素子115はその電流値に応じた輝度で発光する。

#### [0049]

本第1の実施形態によれば、自段のサンプルホールドが終了し、他段がサンプルホールド行っている期間に、たとえばサンプルホールドが終了した電流サンプルホールド回路1031-1は、リーク除去回路を作動させてTFT125-1によりはサンプリングされた電流 I i n に相当する定電流をノードND121-1に流すように構成したことから、他の回路のサンプリング期間も、定電流源として機能する出力トランジスタTFT121のドレイン電位を一定に保つことができ、出力トランジスタのゲート電位のリークによる変化を抑えることが可能となる。

その結果、出力段の電流値バラツキのない、均一な電流源を得ることができ、スキャン終 了部に向かって輝度むらが発生しない高品位な画像を表示することができる。

# [0050]

# 第2実施形態

図 5 は、本第 2 の実施形態に係る電流駆動方式を採用した有機 E L 表示装置の構成例を示すプロック図である。

#### [0051]

本第2の実施形態が上述した第1の実施形態と異なる点は、TFT121,122とキャパシタC121からなる定電流源回路に、さらにnチャネルTFT126,127、およびキャパシタC122による定電流源回路を、ノードND121と接地電位GND間にカスコード接続(2段直列接続)したことにある。

### [0052]

ここでは、電流サンプルホールド回路 1 0 3 1 - 1 A を例に説明する。他の電流サンプルホールド回路 1 0 3 1 - 2 A ~ 1 0 3 1 - n A は電流サンプルホールド回路 1 0 3 1 - 1 A と同様の構成であることからここでの説明は省略する。

#### [0053]

電流サンプルホールド回路 1 0 3 1 - 1 A においては、第 2 の電界効果トランジスタとしてのTFT 1 2 1 - 1 のソースが接地電位 G N D の代わりにノード N D 1 2 3 - 1 に接続され、第 1 の電界効果トランジスタとしてのTFT 1 2 6 - 1 のドレインがノード N D 1 2 3 - 1 に接続され、TFT 1 2 6 - 1 のソースが接地電位 G N D に接続されている。TFT 1 2 6 - 1 のゲートがノード N D 1 2 4 - 1 に接続されている。

そして、ノードND123-1とノードND124-1とに第3のスイッチとしてのTFT127-1のソース・ドレインがそれぞれ接続され、TFT127-1のゲートがサンプルホールド線SHL124-1に接続されている。

10

20

30

40

第2のキャパシタC122-1の第1電極がノードND124-1に接続され、第2電極が接地電位GNDに接続されている。

本第2の実施形態においては、TFT124(-1~-n)が本発明の第4のスイッチを 構成する。

# [0054]

図 5 の電流サンプルホールド回路 1 0 3 1 - 1 A においては、サンプルホールド線 S H L 1 2 1 - 1 , S H L 1 2 2 - 1 , S H L 1 2 7 - 1を高レベルとしてTFT 1 2 2 - 1 , 1 2 3 - 1 , 1 2 7 - 1を導通状態とする。

TFT123-1が導通状態となったことに伴い、信号電流 Iin が電流サンプルホールド回路1031-1A内に流れる。

このとき、TFT121-1は、TFT122-1を介してゲート・ドレインが接続されており、飽和領域にて動作する。そのゲート電圧は前述した式1に基づいて決定され、キャパシタC121-1に保持される。

同様に、TFT121 - 1を介してノードND123 - 1に電流が供給され、このとき、TFT126 - 1は、TFT127 - 1を介して飽和領域にて動作する。そのゲート電圧は前述した式1に基づいて決定され、キャパシタC122 - 1に保持される。

このように、所定のゲート電圧がキャパシタ C 1 2 1 - 1、および C 1 2 2 - 1に書き込まれた後に、サンプルホールド線 S H L 1 2 7 - 1を低レベルとしてTFT 1 2 7 - 1を非導通状態とし、次に、サンプルホールド線 S H L 1 2 2 - 1を低レベルとしてTFT 1 2 2 - 1を非導通状態とした後に、サンプルホールド線 S H L 1 2 3 - 1を低レベルとしてTFT 1 2 3 - 1を非導通状態とする。そして、TFT 1 2 3 - 1を非導通状態とした後、サンプルホールド線 S H L 1 2 3 - 1を高レベルとしてTFT 1 2 8を導通状態とする。

この回路には電流 I i n が流れるが、TFT125-1のゲート電圧(ドレイン電圧)は電流 I i n に相当する電圧になる。この場合、TFT12-11とTFT126-1とは飽和領域で駆動できるようにTFT125-1のサイズ設計を行う。

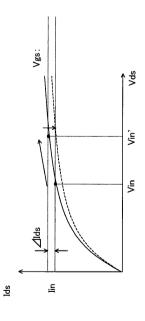

#### [0055]

ここでTFT121-1の動作点について考察する。

TFT124-1が導通状態となると、TFT121-1のドレイン電圧(B)はTFT125-1のドレイン電圧に等しくなってしまい、図6に示すように、TFT121-1のソース・ドレイン間電圧 V d s は増加し(Vin Vin Vin')、流れる電流値はアーリ効果分である I d s だけ増加する。

しかしながら、TFT126-1を含む定電流源は電流Iinを流し続けるので、TFT121-1のソース電圧は電流Iinに相当する電流値を得るために増加する。しかし、TFT121-1のソース電圧の変化による電流値の変化は式1に従い二乗で効くので、このソース電位は殆ど変化しない。

図 6 では、この変化した後のTFT121 - 1 のドレイン電圧(Vd) - ドレイン電流( Id) 曲線を破線で示している。

# [0056]

ここで、TFT121-1のソース電位はTFT126-1のドレイン電位(A)と同電位である。よって、カスコード接続を行っている場合はTFT126-1のドレイン電圧は、電流Iinを書き込んだときの値、つまりTFT126-1のゲート電圧と殆ど等しい値を有する。

これにより、TFT127-1のソース・ドレイン電圧はほぼ 0 V となり、リーク電流によるTFT126-1のゲート電圧の降下を大幅に抑えることができる。

# [0057]

以上より、有機 EL等でのシェーディングや、電流の点順次サンプルホールド回路において、本実施形態のように、トランジスタの動作点サイズ設計を行うことなく、ばらつきのない電流出力が得られる。

なお、本方式では、リーク除去の回路トランジスタ125はpチャネルとしてあるが、n

10

20

30

40

チャネルのトランジスタをダイオード接続させたものでもよい。

# [0058]

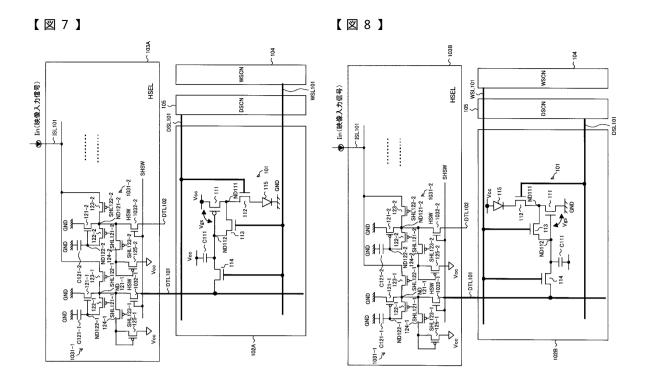

上述した実施形態においては、画素回路102を構成するTFTを全てpチャネルとした が、駆動トランジスタとしてのTFT111の他のスイッチとして機能するTFT112 ,113,114は、図7に示すように、n チャネルTFTであっても、C M O S であっ てもよい。

また、上述した実施形態においては、水平セレクタ103の電流サンプルホールド回路1 031-1~1031-nのスイッチとして機能するTFT122(-1~-n)~12 4 ( - 1 ~ - n ) は、図 7 に示すように p チャネル T F T であってもよい。

#### [0059]

さらに、上述した実施形態では、画素回路102を構成するTFTを全てpチャネルとし たが、駆動トランジスタとしてのTFT111、スイッチとして機能するTFT112. 113,114の全てのTFTを、図8に示すように、nチャネルTFTで構成すること も可能である。

当然、RL発光素子115との接続はアノード接続であってもカソード接続であってもよ

この場合、電流サンプルホールド回路1031-1~1031-nのドライブトランジス タの極性は、図8に示すようにpチャネルである必要がある。

# [0060]

# 【発明の効果】

20

30

40

10

以上説明したように、本発明によれば、他の回路のサンプリング期間も、定電流源として 機能する出力トランジスタのドレイン電位を一定に保つことができ、出力トランジスタの ゲート電位のリークによる変化を抑えることができる。

ホールド期間中のリークを除去することで、ホールド時間差による出力電流値のバラツキ を抑制することができ、均一な定電流源を形成できる。

さらに、サンプルホールド回路にカスコード接続を用いることで、このバラツキ量を殆ど 完全に抑制することができる。

上記のバラツキ抑制の効果は、リーク電流の大きなTFTにおいて顕著である。そのため 、TFTを用いた電流駆動の有機ELディスプレイでの高ユニフォーミティを持つ画質を 得ることができる。

【図面の簡単な説明】

【図1】本発明に係る有機EL表示装置の構成を示すブロック図である。

【図2】図1の有機EL表示装置において本実施形態に係る画素回路の具体的な構成を示 す回路図である。

【図3】本第1の実施形態に係る動作を説明するためのタイミングチャートである。

【図4】本第1の実施形態の利点を説明するための図である。

【図5】本第2の実施形態に係る電流駆動方式を採用した有機EL表示装置の構成例を示 すブロック図である。

【図6】本第2の実施形態の動作を説明するための図である。

【図7】画素回路および電流サンプルホールド回路の他の構成例を示す回路図である。

【図8】画素回路および電流サンプルホールド回路のさらに他の構成例を示す回路図であ

【図9】一般的な有機EL表示装置の構成を示すブロック図である。

【図10】図9の画素回路の一構成例を示す回路図である。

【図11】図9の水平セレクタの要部の具体的な構成を示す回路図である。

【図12】図11の回路の動作を説明するためのタイミングチャートである。

【図13】図11の回路の動作を説明するための図である。

【図14】図11の回路の課題を説明するための図である。

【図15】図11の回路の課題を説明するための図である。

【符号の説明】

100…表示装置、101…画素回路(PXLC)、102…画素アレイ部、103,103A…水平セレクタ(HSEL)、1031-1~1031-n…電流サンプルホールド回路、104…ライトスキャナ(WSCN)、105…ドライブスキャナ(DSCN)、111~114…TFT、115…発光素子、121(-1~n)~127(-1~n)…TFT、DTL101~DTL10n…データ線、WSL101~WS10m…走査線、DSL101~DSL10m…駆動線、ALZ101~ALZ10m…オートゼロ線、ISL101…信号電流の供給線、SHL,SHL121(-1~n)~124(-1~n)…サンプルホールド線。

【図1】

【図2】

【図3】 【図4】

【図5】 【図6】

# 【図15】

# フロントページの続き

(51) Int.CI. F I

G 0 9 G 3/20 6 2 4 B G 0 9 G 3/20 6 4 1 D G 0 9 G 3/20 6 4 2 B H 0 5 B 33/14 A

# 審査官 一宮 誠

(56)参考文献 特開平06-139794(JP,A)

特開平09-319323(JP,A) 特開2003-114645(JP,A)

特開2000-081920(JP,A)

(58)調査した分野(Int.CI., DB名)

G09G 3/00 - 3/38