## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3910301号 (P3910301)

(45) 発行日 平成19年4月25日(2007.4.25)

(24) 登録日 平成19年2月2日(2007.2.2)

| (51) Int.C1. | F 1                           |                         |

|--------------|-------------------------------|-------------------------|

| HO1L 21/265  | <b>(2006.01)</b> HO1L         | 21/265 W                |

| HO1L 21/76   | ( <b>2006.01)</b> HO1L        | 21/265 V                |

| HO1L 27/08   | (2006.01) HO1L                | 21/76 L                 |

| HO1L 21/824  |                               | 27/08 3 3 1 A           |

| HO1L 27/108  | · · ·                         |                         |

|              | •                             | 請求項の数 3 (全 12 頁) 最終頁に続く |

| (21) 出願番号    | 特願平10-354945                  | (73) 特許権者 000003078     |

| (22) 出願日     | 平成10年12月14日 (1998.12.14)      | 株式会社東芝                  |

| (65) 公開番号    | 特開2000-182983 (P2000-182983A) | 東京都港区芝浦一丁目1番1号          |

| (43) 公開日     | 平成12年6月30日 (2000.6.30)        | (74) 代理人 100109900      |

| 審査請求日        | 平成13年3月14日 (2001.3.14)        | 弁理士 堀口 浩                |

|              |                               | (72) 発明者 土明 正勝          |

|              |                               | 神奈川県横浜市磯子区新杉田町8番地 株     |

|              |                               | 式会社東芝 横浜事業所内            |

|              |                               | (72) 発明者 西山 彰           |

|              |                               | 神奈川県横浜市磯子区新杉田町8番地 株     |

|              |                               | 式会社東芝 横浜事業所内            |

|              |                               |                         |

|              |                               | 審査官 加藤 浩一               |

|              |                               |                         |

|              |                               |                         |

|              |                               | 最終頁に続く                  |

(54) 【発明の名称】半導体装置及びその製造方法

## (57)【特許請求の範囲】

#### 【請求項1】

半導体領域と、

シャロートレンチ角部と、

前記半導体領域中に存在するチャネル領域と、

前記半導体領域中に存在するソースおよびドレイン領域と、

前記半導体領域中に前記ソースおよびドレイン領域を形成するpn接合面と、

\_\_前記シャロートレンチ角部と前記 p n 接合面との間<u>の前記ソース或いはドレイン領域</u>に存在し、<u>前記チャネル領域</u>よりも高濃度の酸素或いは窒素を含有する転位伝播阻止領域とを具備することを特徴とする半導体装置。

## 【請求項2】

<u>前記転位伝播阻止領域は、酸素濃度が1×10<sup>17</sup> cm<sup>3</sup> - 1×10<sup>18</sup> cm<sup>3</sup>の</u> 範囲、あるいは窒素濃度が1×10<sup>15</sup> cm<sup>3</sup> - 1×10<sup>16</sup> cm<sup>3</sup>の範囲であることを特徴とする請求項1に記載の半導体装置。

## 【請求項3】

請求項1又は2に記載の半導体装置を製造する方法において、前記シャロートレンチ形成後、素子領域のチャネル幅方向と垂直で基板に対して特定の俯角を持つように、酸素或いは窒素原子の注入を行うことにより、ソース或いはドレイン領域の前記シャロートレンチ角部のみに選択的に酸素原子或いは窒素原子を導入することを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

## [0001]

【発明の属する技術分野】

本発明は、大規模集積化半導体装置及びその製造方法に関する。

#### [0002]

#### 【従来の技術】

高速高機能半導体装置の実現のため、これに用いられる個々の半導体素子の微細化、及びその大規模集積化に対する要求は時を追って増大している。しかしながら、これらの半導体素子の主要な構成要素であるMOSFETの微細化を考えた場合、これには様々な困難が伴う。

### [0003]

例えば、微細な半導体素子間を電気的に絶縁するための素子分離の形成は、素子の高密度集積化のために、より短い距離によって達成されなければならない。しかしながら、素子分離予定半導体基板表面を熱酸化して素子分離酸化膜を形成するLOCOS法では、素子分離酸化膜の周囲が素子領域に張り出す Birds beak 現象が起こり、実効的な素子領域を縮小し、微細な素子間分離が行えないという問題がある。

#### [0004]

このため、素子分離予定領域に、素子分離に必要とされる深さの溝 Shallow trench を形成し、しかる後に、この溝に化学気相成長法 Chemical Vapor Deposition (CVD) などをもちいてシリコン酸化膜などの絶縁物質を形成しこの溝を埋め、さらに半導体基板主平面を平坦化し素子分離を行う技術 Shallow Trench Isolation (STI) が開発されている。

## [0005]

一方、MOSFETのチャネル長(ゲート電極の長さ)の縮小に伴いしきい値電圧が下降する短チャネル効果が知られている。この短チャネル効果では、ゲート電極の加工寸法に、しきい値電圧が大きく依存するため、加工寸法が小さくなると、わずかな加工ずれでも、目途の特性の素子を得る事が不可能となる。このため特に多数の均一な素子を必要とする半導体回路、例えばDynamic Random Access Memory (DRAM)の製造には、極めて不都合となる。

## [0006]

このような短チャネル効果は、MOSFETのソース及びドレイン電極部分での電界の歪みが、チャネル長の縮小に伴い、チャネル部分にまで影響を与えることに起因している。この効果を抑制するためには、チャネル部分の不純物濃度を高くすればよいことが知られているが、チャネル部分の不純物濃度を高くすると基板とソース、ドレイン電極間の電気容量が増大し素子の高速動作を阻害する。このような問題を解決するために、絶縁膜上に形成された薄いシリコン層に半導体素子を形成する技術 (Silicon On Insulator, SOI) が開発されている。

### [0007]

また短チャネル効果は、ソース及びドレインを形成するPn-junction の接合位置を半導体表面に近づける、(即ちPn-junction を "浅くする ")ことで回避することも出来る。しかし、単に、Pn-接合を浅くすると、これにより構成されているソース、ドレイン電極の抵抗が増大し、素子を伝わる信号の高速伝達を阻害する。さらに、接合が浅いと、この部分に電気的接触を得るためのコンタクトを設けた場合、このコンタクトを構成する金属製物質が下方に拡散し接合を突き抜け、接合リークを誘起する恐れが出てくる。

この様な問題に対処するため、ソース、ドレイン電極を形成しようとする半導体基板表面部分に選択的に半導体物質を追加形成し、この領域の表面をもともとの半導体表面(チャネルの形成される面)より上方に移動させ、この追加形成された表面を通じてソース、ドレインのPn-junctionを形成することで、接合の位置は本来の半導体表面(チャネルの形成される面)に対しては浅く、しかし、このように新たに形成された表面に対しては深く、従って、ソース、ドレインを形成する電極部分の厚み(拡散層の厚み)は確保するとい

10

20

30

50

う手法 (Elevated source drain method) が用いられて来た。

### [0008]

### 【発明が解決しようとする課題】

上述した、STIによる素子分離及びElevated Source Drain 構造には、以下の問題がある。

先ず、STI構造の素子では、Shallow trench の埋め込みにはCVD法などによるシリコン酸化膜が用いられる。しかしながら、LOCOSで用いられる熱酸化膜に比べその密度が小さいため、このCVD絶縁膜はその後の熱工程で体積変化を起こしやすく、この結果Shallow trench の一部、特に底面角部に大きな応力が集中する。この底面角部に残留する大きな応力によって、転位が頻繁に発生し、これがこの近傍に形成されている、pn接合を横切ると激しい接合リークを起こすという問題が生じる。pn接合を通じて電流が漏れ出すと、素子の動作が損なわれたり、DRAMなどの記憶素子では、書き込まれた情報が失われてしまい、半導体装置の本来の機能が喪失するという問題がある。

### [0009]

次に、Elevated Source Drain 構造の素子では、エピタキシャル成長技法が用いられるが、この方法は、選択成長を行う表面状態に非常に敏感である。例えば、成長直前の基板表面の自然酸化膜や、ゲート電極加工時に導入されるダメージなどによって、ソース、ドレイン領域内に結晶構造の乱れた結晶欠陥が残留する。このような結晶構造の乱れは、転位発生の核となり、発生した転位がソース、ドレインを構成するpn接合を横切ると激しい接合リークをおこすという問題が生じる。接合を通じて電流が漏れ出すと、素子の動作が損なわれたり、DRAMなどの記憶素子では、書き込まれた情報が失われてしまい、半導体装置の本来の機能が喪失する問題がある。

### [0010]

本発明は、上記のような、従来技術の欠点を除去し、Shallow trench コーナー部や追加 形成されたシリコン層と基板の界面などからの転位発生を抑制し、半導体装置製造工程の 歩留まりを向上させ製造コストの削減された半導体装置およびその製造方法を提供するこ とを目的とする。

#### [0011]

## 【課題を解決するための手段】

上記目的を達成するために、本発明は、STIコーナー部や加形成されたシリコン層と基板の界面などの転位の発生しやすい部位近傍のみに選択的に酸素原子や窒素原子を導入し転位の発生及びその伝播を抑制する半導体装置及びこの製造方法を提供する。

#### [0012]

即ち本発明は、半導体領域と、シャロートレンチ角部と、前記半導体領域中に存在する チャネル領域と、前記半導体領域中に存在するソースおよびドレイン領域と、前記半導体 領域中に前記ソースおよびドレイン領域を形成するpn接合面と、前記シャロートレンチ 角部と前記pn接合面との間の前記ソース或いはドレイン領域に存在し、前記チャネル領 域よりも高濃度の酸素或いは窒素を含有する転位伝播阻止領域とを具備することを特徴と する半導体装置を提供する。

#### [0014]

また本発明は、前記シャロートレンチ形成直後、素子領域のチャネル幅方向と垂直で基板に対して特定の俯角を持つように、酸素或いは窒素原子の注入を行うことにより、ソース或いはドレイン領域の前記シャロートレンチ角部のみに選択的に酸素原子或いは窒素原子を導入することを特徴とする半導体装置の製造方法を提供する。

#### [0016]

## 【発明の実施の形態】

以下に本発明を詳細に説明する。

本発明によると、酸素原子或いは窒素原子が転位発生領域の近くに存在するので、酸素或いは窒素原子は転位核に積極的に取り込まれ転位核の構造を変化させ転位の移動を阻害する。よって、STIコーナー部や形成されたシリコン層と基板の界面などの転位の発生し

10

20

30

40

30

40

50

やすい部位近傍のみに選択的に酸素或いは窒素原子を導入することにより、発生した転位は長距離を移動することなく発生した近傍にとどまる。したがって転位が発生してもこれが p n 接合部分を横切らないので、素子の電気的特性に影響を及ぼさない。特に、酸素はシリコン中をすばやく拡散するので、低温の熱工程でも転位の不動化は効果的に達成される。

#### [0017]

また、本発明によると、酸素原子は p n 接合部分などを避け選択的に導入されるので、酸素原子に由来した析出物なども接合面には形成されない。このため、酸素原子の接合にたいする電気的影響もない。よって、転位の発生しやすい部位が存在しても、高温熱処理無しに、転移による素子の電気的特性に対する影響を回避することが可能となり、半導体装置製造工程の歩留まりを向上させ製造コストの削減された半導体装置の製造方法が達成される。

#### [0018]

次に、本発明によるSOIウエハ上に形成された、STI分離されたトレンチ型DRAMを高歩留まりに製造する工程を示す。

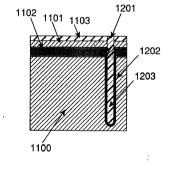

先ず、図1に示すように、n型シリコン半導体下部基板1100、このn型シリコン半導体下部基板上に形成されたシリコン酸化膜層1102、このシリコン酸化膜層1102上に形成された上部シリコン層1101が形成された基板を用意する。この基板上には、パッドシリコン窒化膜層1103が形成され、このパッドシリコン窒化膜層1103と上部シリコン層1101よりシリコン酸化膜層1102を貫き下部シリコン基板1100に至るトレンチ1201が形成されている。

### [0019]

このトレンチ1201は、RIE工程により形成され、CVD工程、CMP工程により、n型シリコン半導体下部基板1100内壁に形成されたキャパシタ絶縁膜1202、トレンチ1201内側を上部シリコン層1101表面まで埋めるノードを構成するn型ポリシリコン1203が形成され電荷蓄積用の深いトレンチ、Deep Trench (DT) が構成されている。

#### [0020]

また、ウエハ製造工程中の熱処理で上部シリコン層 1 1 0 1 の酸素濃度は 1 0 1 6 c m 3 程度にまで落ちている。 n 型ポリシリコン層 1 2 0 3 、 , 絶縁膜 1 2 0 2 , n 型シリコン半導下部基板 1 1 0 0 は D R A M の電荷蓄積用のキャパシタを構成する。

## [0021]

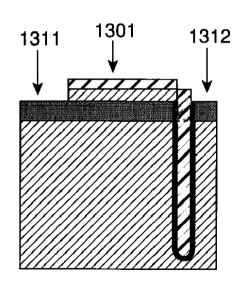

次に、図 2 に示すように、STIを達成するために、上記半導体主表面にLithography 工程、RIE工程などの公知の技法のうち効果的な手法をもって、アクセス用MOSFETを形成すべき素子領域1301、これを囲むshallow trench,1311,1312を形成する。

## [0022]

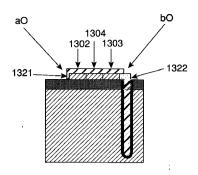

次に、図3に示すように、素子領域1301のチャネル幅方向(紙面垂直方向)と垂直で基板に対して特定の俯角を持つように調整した酸素原子のイオン注入を行う。この時アクセス用MOSFETのソース1302、ドレイン1303領域に同様に酸素原子が注入されるように、イオン注入はa,b二方向から行うことが望ましい。場合によってはドレイン1303領域(ノードポリシリコン1203に接続される側、b方向)にのみ酸素原子を注入してもよい。

このとき酸素原子濃度はshallow trench 角部  $1\ 3\ 2\ 1$  ,  $1\ 3\ 2\ 2$  で、 $1\ \times\ 1\ 0^{17}$  c m  $^{-3}$  -  $1\ \times\ 1\ 0^{18}$  c m  $^{-3}$  の範囲に調節されていることが望ましい。一般に、DRAMの各ce IIのチャネル方向はお互いに平行であるのでこのような斜めイオン注入で効果的にソース  $1\ 3\ 0\ 2$ 、ドレイン  $1\ 3\ 0\ 3$  領域のshallow trench 角部  $1\ 3\ 2\ 1$  ,  $1\ 3\ 2\ 2$  のみに酸素原子を導入することができる。

### [0023]

また、素子領域1301の上面はパッドシリコン窒化膜層1103で保護されているため

30

40

50

に、酸素原子はチャネル領域1304には導入されることはない。よって高温の熱処理を避ける事により、酸素原子の影響がチャネル部分に及ぶことなく、ソース1302、ドレイン1303領域のshallow trench 角部1321,1322のみに限定される。このような工程はイオン注入以外、Lithography 工程のような新たな工程を何ら追加することなく実施できる。

## [0024]

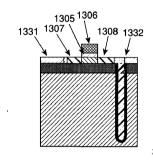

次に、図4に示すように、CVD法、CMP法などの公知の技法のうち効果的な手法をもってshallow trench 1311、1312を例えばシリコン酸化膜のような絶縁物質1311、1332で埋めその表面をパッドシリコン窒化膜層1103などを利用して平坦化し、熱酸化、或いは、CVD法などの公知の技法のうち効果的な手法をもってゲート絶縁膜1305、を形成する。この後、さらにCVD法、RIE法などの公知の技法のうち効果的な手法をもってゲート電極1306、さらに、イオン注入、RTA法などの公知の技法のうち効果的な手法をもってゲース電極1307、ドレイン電極1308を構成する。ドレイン電極とn型ポリシリコン層1203は電気的に接続しており、Buried Strap 構造を達成する。

#### [0025]

これに引き続き、例えば、CVD法により、低誘電率絶縁膜を層間膜として堆積した後、ソース電極へのコンタクトホールを例えば、RIE技術により形成し、さらに、Alなどの配線材料物質を推積し、必要な形状にRIE法などをもちいて配線を形成し、さらに公知の技術を用いて、配線工程、実装工程などを経て、STI分離されたトレンチ型SOI-DRAM半導体装置を完成させる。

### [0026]

上記実施例は、SOI基板を例に取って説明したが、これ以外に、HAI基板、Epi基板に応用できる事はいうまでもない。酸素原子に変わって、窒素原子を導入してもよい。また素子分離がLOCOSの場合にも同様な手法が適応できる。

#### [0027]

次に、本発明のソース、ドレイン電極間に局所的配線を備えた サリサイドCOMS 型 Elevated source drain MOSFET構造を高歩留まりに製造する工程を示す。

## [0028]

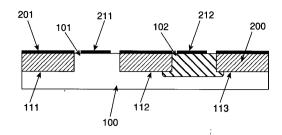

先ず、図 5 に示すように、シリコン半導体基板 1 0 0、このシリコン半導体基板 1 0 0中に形成された、p型不純物を導入された領域(p-well) 1 0 1、n型不純物を導入された領域 (n-well) 1 0 2、及びその表面に形成された浅い溝(shallow trench) 1 1 1 1 1 1 2 1 1 3 とそれを基板表面まで埋める絶縁物質、例えばシリコン酸化膜 1 2 0 0、及びその表面に形成されたゲート絶縁膜 2 1 1 1 2 2 6 有する基板を準備する。

## [0029]

この素子分離領域を備える半導体基板は、Lithography 工程、RIE工程、CVD(chem ical vapor deposition)方による絶縁膜推積、さらに、CMP(chemical mechanic al polishing)方による平坦化、イオン注入技術等の、公知の技術の効果的な方法により達成できる。また、これらのゲート絶縁膜は、シリコン基板100の表面に、50オングストロームの薄いシリコン窒化膜1201を、熱窒化、あるいは、JVD(Jet Vapor Deposition)法等の公知の技術の効果的な方法をもちいて形成後、211,212,111,112,113に該当する部分以外を,Lithography 法をもちいてマスク材、例えば、100オングストロームの薄いシリコン酸化膜で覆い、露出部分を例えば、加熱されたりん酸(H3 PO4)溶液にさらし、選択的に除去し、さらにマスク材となる薄い酸化膜をHF溶液にさらして除去することによって達成できる。この時、ゲート絶縁膜の端は、ゲート電極とこの後追加形成するべきソース、ドレイン電極との間隙に対応する領域にはいっていればよい。ゲート電極からはみ出した絶縁膜は、ゲート電極及び、ソース、ドレイン追加電極形成後に容易に除去できるからである。よって、ゲート絶縁膜をあらかじめ形成するにあたって必要なリソグラフィエ程のあわせ精度は、Source-Drain,Extension部の幅程度となり、容易に実現できる。シリコン基板100の表面は無欠陥層(D2層)を

30

40

50

形成するために酸素濃度は極めて小さくなっている(10<sup>16</sup> cm<sup>-3</sup>程度)。

#### [0030]

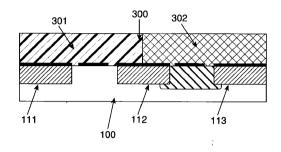

次に、図6に示すように、基板上に、一面に形成されたゲート電極構成物質300、及び、このうち、n型不純物を導入された領域301、p型不純物を導入された領域302を形成する。これらのゲート電極構成物質、300は、シリコン基板100の表面に、ポリシリコン層300、を、例えば、2000オングストローム堆積し、この後、Lithography法によりマスク材、例えばPhoto-resistを形成し、領域301,302に選択的に、それぞれn型不純物、p型不純物を選択的にイオン注入することで達成できる。イオン注入のエネルギーを調節してほぼ均一にポリシリコン層に不純物が導入される用にする。CVD法を用いているため、エピタキシャル成長技法に求められる選択性が必要なくなる。また、この時ポリシリコン層に混入する酸素の量を極小化(10<sup>16</sup> cm<sup>-3</sup> 以下)しておく。このため、均一で、等膜厚のシリコン層を形成することが容易となり、エピタキシャル成長技法に見られるソース、ドレイン追加形成部の膜厚のばらつきがなくなる。これにより、ソース、ドレインを形成するべき不純物を、追加形成されたシリコン表面より導入とを形成する場合に、目途の位置に精度よく接合を形成できる。

## [0031]

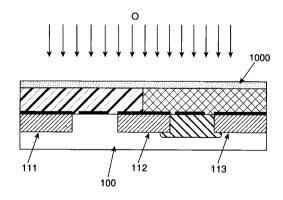

次に、図7に示すように、この後さらに、ポリシリコン上層部1000に酸素原子を例えばイオン注入法をもちいて導入する。或いは、酸素混入量の大きいポリシリコン層をさらに堆積形成してもよい。酸素原子の導入深さは、その後熱処理で追加シリコン層・基板シリコン界面に達するが、酸素原子の析出がp/n 不純物が基板に形成するpn接合面で起こらないように調節する。酸素原子は拡散は、B,Pに比べ速いのでこのように上部のみに酸素を導入することが望ましい。これにより、転移の核となりうる界面に酸素原子が導入され、転移の発生及びその伝播を抑制し、しかも酸素析出などによりpn接合に影響を与えることはない。また、このような工程はイオン注入、或いは、CVD工程以外、Lithog raphy 工程のような新たな工程を何ら追加することなく実施できる。

## [0032]

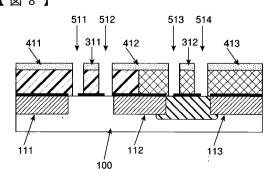

次に、図8に示すように、RIE工程を経て、それぞれ、p-well、101,n-well、102上に形成されたゲート電極311,312及び、ソース、ドレイン領域上に追加形成されたシリコン層411,412,413を形成する。ゲート電極311,312及び、ソース、ドレイン領域上に追加形成されたシリコン層411,412,413を一度に形成できるため、エピタキシャル成長技法による選択成長のような新たな工程を経ずに、Elevated Source/Drain 構造が達成できる。このため、製造コストを削減できる事に注目すべきである。また、この時、ゲート絶縁膜の端は、ゲート電極311,312と追加形成されたシリコン層411,412,413は、本方の領域に入っていればよい。追加形成されたシリコン層411,412,413は、素子分離領域111,112,113、に伸びており、ソース、ドレイン電極と半導体基板の容量を低減している。さらに、追加形成されたシリコン層412は、p-well、101,n-well、102領域を連結している。これによって、単なる、ソース、ドレイン電極の追加形成にとどまらず、局所的素子間配線工程が、このシリコン層により同時に形成できる。よって、新たな局所的素子配線工程が必要なくなり、製造コストを削減できる。

#### [0033]

この後、この基板を熱処理して、シリコン層 4 1 1 , 4 1 2 , 4 1 3 と半導体基板、 1 0 0 とが接している部分から、シリコン層 4 1 1 , 4 1 2 , 4 1 3 に導入された不純物を基板に拡散させ、拡散層 6 1 1 , 6 1 2 , 6 1 3 , 6 1 4 を形成すると同時に、ゲート電極 3 1 1 , 3 1 2 , シリコン層 4 1 1 , 4 1 2 , 4 1 3 中の導電性不純物を活性化する。この時、拡散工程を、酸素原子が追加シリコン層 - 基板シリコン界面には達するが、 p n 接合面に達しない様に調整する。転移の核となりうる界面に酸素原子が導入され、転移の発生及びその伝播を抑制し、しかも p n 接合には影響を与えない。このときの酸素濃度は、追加シリコン層 - 基板シリコン界面で、 1 x 1 0  $^{17}$  c m - 1 x 1 0  $^{18}$  c m  $^{-3}$  の範囲に入っ

ていれば好ましい。

## [0034]

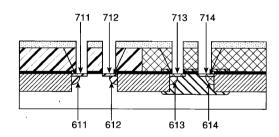

次に、図9に示すように、間隙511,512,513,514に残存するゲート絶縁膜を例えば、加熱されたりん酸(H3PO4)溶液により除去し、さらに、ゲート電極311.312と追加形成されたシリコン層411,412,413、及び、Lithography工程により形成したphoto-resistをマスクとして、間隙511,512,及び513,514にそれぞれ、n型、p型不純物をイオン注入する。さらに例えば、これに急速昇降御熱処理を施す事で、不純物を活性化し、Source-Drain Extention部、711,712,713,714を形成する。浅いSource-Drain Extention部の形成には、イオン注入技術の他、plasma immersion doping, Gas imsersion laser dopong,など、公知の技術の効果的な方法により達成できることは言うまでもない。

#### [0035]

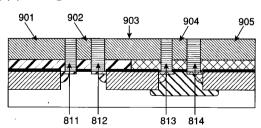

次に、図10に示すように、CVD法により、例えばシリコン酸化膜を2000A推積し、しかる後に、CMP法により、平坦化を施して間隙511,512,513,514を低誘電率絶縁膜811,812,813,814で充填する。この時、ゲート電極311,312及び、追加形成されたシリコン層411,412,413の電極の高さは一様である。よって、表面の平坦化が非常に容易になる。引き続きこの平坦化された表面に、シリコンと選択的に反応する金属、例えばCoを全面にスパッタ法により堆積された後、これに熱処理、例えば窒素雰囲気中、500 の急速熱処理(RTA)、を施すことにより、シリコンとの接触面、即ち、ゲート電極311,312及び、追加形成されたシリコン層411,412,413上でシリサイド化を選択的に進行させ、未反応の金属をHNO3などの溶液で処理し除去することにより、シリサイド層901,902,903,904,905,をゲート、ソース、ドレイン上に自己整合的に形成する。このようにして、サリサイド構造を実現出来る。

### [0036]

追加形成されたソース、ドレイン電極上をシリサイド化されているので、金属原子がソース、ドレイン中を拡散し、接合部分に到達しにくい。このため、接合のリークが防止できる。また、追加形成されたシリコン層 4 1 2 及び、シリサイド層 9 0 3 は局所的素子間配線形成している。

## [0037]

次に、CVD法などにより、低誘電率絶縁膜を層間膜として堆積した後、ソース、ドレイン電極へのコンタクトホールを例えば、RIE技術により形成し、さらに、A1などの配線材料物質を堆積、加工し、さらに公知の技術を用いて、配線工程、実装工程などを経て、STI分離され、局所的配線を備えた、サリサイドCMOS型 Elevated source drain MOSFET構造を完成させる。

## [0038]

以上酸素原子の導入を例として用いたが、同様の効果は窒素原子に於いても同様に得られる。また素子分離が LOCOSの場合にも同様な手法が適用できる。この時の窒素濃度は  $1\times10^{15}$  c m<sup>-3</sup> -  $1\times10^{16}$  c m<sup>-3</sup>の範囲に入っていれば好ましい。

### [0039]

## 【発明の効果】

本発明によれば、半導体素子構造中の転移の発生しやすい部位が存在しても、この部分と p n 接合面との間にあって、しかもこの間を遮断する高濃度酸素領域或いは窒素領域を形成することにより、転移の発生伝播を抑制し、転移が p n 接合を横切る事を阻止する。この時の酸素濃度、窒素濃度は、それぞれ  $1 \times 10^{17}$  c m  $^{-3}$  -  $1 \times 10^{18}$  c m  $^{-3}$  及び  $1 \times 10^{15}$  c m  $^{-3}$  -  $1 \times 10^{16}$  c m  $^{-3}$  の範囲に入っていれば好ましい。これにより、半導体装置製造工程の歩留まりを向上させ製造コストの削減された半導体装置の製造方法が達成される。

### [0040]

特に、shallow trench 角部に選択的に酸素原子或いは窒素原子を導入することにより、

10

20

30

40

30

40

50

この部分に応力が残留しても、酸素或いは窒素原子が転移核に積極的に取り込まれ転移核の構造を変化させ転移の移動を阻害する。よって発生した転移は長距離を移動することなく発生した近傍にとどまる。転移が発生してもこれが p n 接合部分を横切らないので電気的特性に影響を及ぼさない。

## [0041]

また、酸素或いは窒素原子は p n 接合部分などを避け選択的に導入されるので、酸素原子に由来した析出物なども接合面には形成されない。このため、酸素或いは窒素原子の接合にたいする電気的影響もない。

#### [0042]

さらに、shallow trench 形成直後、素子領域のチャネル幅方向と垂直で基板に対して特定の俯角を持つように調整した酸素或いは窒素原子のイオン注入により酸素或いは窒素原子の注入を行う事により、効果的にソース、ドレイン領域のshallow trench 角部のみに酸素原子を導入することができる。また、素子領域の上面はパッド層で保護されているために、酸素或いは窒素原子はチャネル領域には導入されることはない。よってイオン注入以外、Lithography 工程のような新たな工程を何ら追加することなく実施できる。

#### [0043]

あらかじめ、ゲート電極を形成すべき領域に、ゲート絶縁膜となる絶縁性の膜を形成しておき、しかる後に、シリコン層を全面に追加形成し、このシリコン層の上部に酸素或いは窒素原子を導入し、その導入深さを、その後の熱工程で、追加シリコン層 - 基板シリコン界面に達するが、酸素原子或いは窒素原子の析出がp/n 不純物が基板に形成するpn接合面で起こらない様に調節する。

### [0044]

これにより、転移の核となりうる界面に酸素或いは窒素原子が導入され、転移の発生及びその伝播を抑制し、しかも p n 接合には影響を与えない。よって半導体装置製造工程の歩留まりを向上させ製造コストが削減する。

#### [0045]

このような工程はイオン注入、或いは、CVD工程以外、Lithography 工程のような新たな工程を何ら追加することなく実施できる。

加えて、RIE (Reactive Ion Etching)により、ゲート電極及び、ソース、ドレイン領域上に追加形成すべきシリコン層を一度に形成できるため、エピタキシャル成長技法による選択成長のような新たな工程を経ずに、Elevated Source/Drain 構造が達成できる。このため、製造コストを削減できる。

#### [0046]

また、本発明によれば、均一で、等膜厚のシリコン層を形成することが容易となり、エピタキシャル成長技法に見られるソース、ドレイン追加形成部の膜厚のばらつきがなくなる。これにより、ソース、ドレインを形成するべき不純物を、追加形成されたシリコン表面より導入し接合を形成する場合に、目途の位置に精度よく接合を形成できる。

## [0047]

追加形成されたソース、ドレイン電極は素子分離絶縁膜上に任意に設置できる。このため、半導体基板上の可形成されたソース、ドレイン電極は最小限の面積にとどめ、大部分を素子分離絶縁幕上に乗り上げさせる事により、ソース、ドレイン電極と半導体基板の容量を低減することが可能になる。このため、素子の高速動作が可能となる。この追加形成するシリコン層は、一つの素子に必ずしも対応している必要はなく、複数の素子のソース、ドレイン領域を連結するものであってもよい。これによって、単なる、ソース、ドレイン電極の追加形成にとどまらず、局所的素子間配線が、このシリコン層により同時に形成できる。よって、新たな局所的素子間配線工程が必要なくなり、製造コストを削減できる。

#### 【図面の簡単な説明】

【図1】 SOIウエハ上に形成された、STI分離されたトレンチ型DRAMを高歩留まりに製造する工程の断面図。

【図2】 SOIウエハ上に形成された、STI分離されたトレンチ型DRAMを高歩留

まりに製造する工程の断面図。

- 【図3】 SOIウエハ上に形成された、STI分離されたトレンチ型DRAMを高歩留まりに製造する工程の断面図。

- 【図4】 SOIウエハ上に形成された、STI分離されたトレンチ型DRAMを高歩留まりに製造する工程の断面図。

- 【図5】 ソース、ドレイン電極間に局所的配線を備えたサリサイドCMOS型Elevated source drain MOSFET構造を高歩留まりに製造する工程の断面図。

- 【図6】 ソース、ドレイン電極間に局所的配線を備えたサリサイドCMOS型Elevated source drain MOSFET構造を高歩留まりに製造する工程の断面図。

- 【図7】 ソース、ドレイン電極間に局所的配線を備えたサリサイドCMOS型Elevated 19 source drain MOSFET構造を高歩留まりに製造する工程の断面図。

- 【図8】 ソース、ドレイン電極間に局所的配線を備えたサリサイドCMOS型Elevated source drain MOSFET構造を高歩留まりに製造する工程の断面図。

- 【図9】 ソース、ドレイン電極間に局所的配線を備えたサリサイドCMOS型Elevated source drain MOSFET構造を高歩留まりに製造する工程の断面図。

- 【図10】 ソース、ドレイン電極間に局所的配線を備えたサリサイドCMOS型Elevat ed source drain MOSFET構造を高歩留まりに製造する工程の断面図。

## 【符号の説明】

- 100 半導体基板

- 101 p-well領域

- 102 n-well領域

- 111,112,113 shallow trench isolation

- 200 素子分離絶縁酸化膜

- 201、211、212 ゲート絶縁窒化膜

- 300 ポリシリコン

- 3 0 1 n型ポリシリコン領域

- 302 p型ポリシリコン領域

- 3 1 1 n型ポリシリコンゲート電極

- 3 1 2 p型ポリシリコンゲート電極

- 4 1 1 、 4 1 2 、 4 1 3 、 ポリシリコン追加形成ソースドレイン電極 5 1 1 、 5 1 2 、 5 1 3 、 5 1 4 ゲート電極、追加形成ソースドレイン電極間に形成さ

- れた間隔

- 6 1 1、6 1 2、6 1 3、6 1 4 ソース、ドレイン拡散層

- 711、712、713、714 拡張ソース、ドレイン領域

- 8 1 1 、 8 1 2 、 8 1 3 、 8 1 4 層間絶縁膜

- 901、902、903、904、905 シリサイド領域

- 1000 高濃度酸素含有領域

- 1100 SOIウエハ n型シリコン下部半導体基板

- 1101 SOIウエハ上部シリコン層

- 1 1 0 2 S O I ウエハ 絶縁 シリコン酸 化 膜層

- 1103 パッドシリコン窒化膜

- 1201 DRAM電荷蓄積用Deep Trench

- 1 2 0 2 ノード絶縁膜

- 1203 ノードn型ポリシリコン電極

- 1301 アクセストランジスタ用素子領域

- 1302 アクセストランジスタ用ソース領域

- 1303 アクセストランジスタ用ドレイン領域

- 1304 アクセストランジスタ用チャネル領域

- 1305 アクセストランジスタ用ゲート絶縁膜

- 1306 アクセストランジスタ用ゲート電極

50

40

20

- 1307 アクセストランジスタ用ソース電極

- 1308 アクセストランジスタ用ドレイン電極

- 1 3 1 1 、 1 3 1 2 素子分離用shallow trench

- 1321 酸素原子が導入されるソース領域shallow trench 角部

- 1322 酸素原子が導入されるドレイン領域shallow trench 角部

- 1331、1332 CVDシリコン酸化膜

## 【図1】

## 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

## フロントページの続き

(51) Int.CI. F I

H 0 1 L

29/78

(2006.01)

H 0 1 L

29/78

3 0 1 S

H 0 1 L

29/786

(2006.01)

H 0 1 L

29/78

6 2 1

(56)参考文献 特開昭 6 3 - 0 7 9 3 2 9 (JP, A)

特開平01-282815(JP,A)

特開平11-284150(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/265

H01L 21/76

H01L 21/8242

H01L 27/08

H01L 27/108

H01L 29/78

H01L 29/786