# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(12) 8/11 9 8

**G06F 3/041** (2006.01) **G06F 3/044** (2006.01)

(52) CPC특허분류

**G06F 3/0412** (2019.05) **G06F 3/0416** (2019.05)

(51) 국제특허분류(Int. Cl.)

(21) 출원번호 **10-2019-0088386**

(22) 출원일자 2019년07월22일

심사청구일자 **없음**

(11) 공개번호 10-2021-0011217 (43) 공개일자 2021년02월01일

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

이휘득

경기도 파주시 월롱면 엘지로 245

이양식

경기도 파주시 월롱면 엘지로 245

(74) 대리인

특허법인(유한)유일하이스트

전체 청구항 수 : 총 22 항

## (54) 발명의 명칭 터치표시장치

## (57) 요 약

본 발명의 실시예들은 터치표시장치에 관한 것으로서, 더욱 상세하게는, 터치센서와 터치센싱회로를 연결해주는 터치 라우팅 배선들이 비-표시영역에 배치되더라도 작은 베젤 사이즈를 갖고, 터치 라우팅 배선들에 의한 기생 캐패시턴스 형성을 방지해주어 터치 감도를 향상시켜줄 수 있는 터치표시장치에 관한 것이다.

#### 대 표 도 - 도1

# (52) CPC특허분류

**G06F 3/044** (2019.05)

G06F 2203/04103 (2013.01)

G06F 2203/04111 (2013.01)

G06F 2203/04112 (2013.01)

## 명세서

#### 청구범위

#### 청구항 1

기판;

상기 기판 상에 다수의 서브픽셀 영역마다 배치되는 다수의 픽셀전극;

상기 다수의 픽셀전극 상에 배치되며 공통전압이 인가되는 공통전극;

상기 공통전극을 덮으면서 배치되는 봉지층;

표시영역에서 상기 봉지층 상에 배치되는 n개의 제1 터치전극 라인과 m개의 제2 터치전극 라인을 포함하며, 상기 n개의 제1 터치전극 라인과 상기 m개의 제2 터치전극 라인 각각은 1가지 이상의 터치센서메탈을 포함하는 터치센서;

상기 표시영역의 외곽 영역인 비-표시영역 중 상기 표시영역으로부터 제1 방향으로 외곽에 위치하는 제1 비-표 시영역에 배치되며, 2n개의 제1 터치패드 및 2m개의 제2 터치패드를 포함하는 터치패드 부;

상기 봉지층의 경사면을 따라 내려와, 상기 n개의 제1 터치전극 라인 각각의 일단과 타단을 상기 제1 비-표시영역에 배치된 상기 2n개의 제1 터치패드와 전기적으로 연결해주는 2n개의 제1 터치 라우팅 배선; 및

상기 봉지층의 경사면을 따라 내려와, 상기 m개의 제2 터치전극 라인 각각의 일단과 타단을 상기 제1 비-표시영역에 배치된 상기 2m개의 제2 터치패드와 전기적으로 연결해주는 2m개의 제2 터치 라우팅 배선을 포함하고,

상기 2n개의 제1 터치 라우팅 배선 중 둘 이상의 제1 터치 라우팅 배선과, 상기 2m개의 제2 터치 라우팅 배선 중 둘 이상의 제2 터치 라우팅 배선은, 상기 표시영역으로부터 제2 방향으로 외곽에 위치하는 제2 비-표시영역을 지나가고.

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선은, 상기 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선과, 상기 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배 선을 포함하고,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제2 터치 라우팅 배선은, 상기 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선과, 상기 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선을 포함하는 터치표 시장치.

## 청구항 2

제1항에 있어서,

상기 제1 메탈은 상기 표시영역 내 배치된 트랜지스터들의 소스 및 드레인 전극에 포함되는 소스-드레인 메탈 및 상기 표시영역 내 배치된 트랜지스터들의 게이트 전극에 포함되는 게이트 메탈 중 1 가지 이상을 포함하는 터치표시장치.

#### 청구항 3

제1항에 있어서,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선에서, 상기 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선과, 상기 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선은 서로 다른 층에서 서로 엇갈리면서 배치되거나,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제2 터치 라우팅 배선에서, 상기 터치센서메탈이 포함된 하나

이상의 제2 터치 라우팅 배선과 상기 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선은 서로 다른 층에서 서로 엇갈리면서 배치되는 터치표시장치.

## 청구항 4

제1항에 있어서,

상기 표시영역 내 배치된 다수의 게이트 라인과 전기적으로 연결되며, 상기 제2 비-표시영역에 배치되며 상기 제1 메탈이 포함된 트랜지스터들을 포함하는 게이트 구동 회로를 더 포함하는 터치표시장치.

#### 청구항 5

제4항에 있어서,

상기 공통전극으로 상기 공통전압을 전달하며 상기 제2 비-표시영역에 배치된 전원전달패턴을 더 포함하는 터치 표시장치.

#### 청구항 6

제5항에 있어서,

상기 전원전달패턴은 상기 제1 메탈을 포함하는 터치표시장치.

#### 청구항 7

제5항에 있어서,

상기 전원전달패턴은 상기 게이트 구동 회로보다 상기 표시영역에 더 가깝게 배치되는 터치표시장치.

#### 청구항 8

제4항에 있어서.

상기 표시영역에서 상기 제2 비-표시영역까지 확장된 상기 공통전극은 상기 게이트 구동 회로와 중첩되는 터치 표시장치.

## 청구항 9

제4항에 있어서,

상기 공통전극은 상기 게이트 구동 회로가 노출되도록 오픈 되어 있는 터치표시장치.

## 청구항 10

제1항에 있어서,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선과, 상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제2 터치 라우팅 배선은,

상기 표시영역에서 상기 제2 비-표시영역까지 확장된 상기 공통전극과 미 중첩되어 배치되는 터치표시장치.

## 청구항 11

제1항에 있어서,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제2 터치 라우팅 배선은 상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선보다 더 외곽에 배치되는 터치표시장치.

## 청구항 12

제11항에 있어서,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선 중 상기 터치센서메탈이 포함된 하나이상의 제1 터치 라우팅 배선은 상기 봉지층 상에 배치되고,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선 중 상기 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선은 상기 봉지층 아래에 배치되는 터치표시장치.

#### 청구항 13

제12항에 있어서,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선 중 상기 터치센서메탈이 포함된 하나이상의 제1 터치 라우팅 배선의 일부는 상기 제2 비-표시영역 내에서 상기 봉지층의 경사면과 중첩되는 터치표시장치.

#### 청구항 14

제12항에 있어서,

상기 제2 비-표시영역을 지나가는 상기 둘 이상의 제1 터치 라우팅 배선 각각은, 상기 터치센서 메탈이 포함된 상부 배선과 상기 제1 메탈이 포함된 하부 배선을 포함하고,

상기 상부 배선의 일단과 상기 하부 배선의 일단은 상기 봉지층의 끝에서 상기 제1 방향으로 외곽에 위치하는 제1 지점에서 컨택되고.

상기 상부 배선의 타단과 상기 하부 배선의 타단은 상기 봉지층의 반대 끝에서 상기 제1 방향의 반대 방향으로 외곽에 위치한 제3 지점에서 컨택되는 터치표시장치.

## 청구항 15

제1항에 있어서,

상기 n개의 제1 터치전극 라인은 터치 센싱 회로에 의해 구동 신호가 인가되는 송신 전극 라인들이고, 상기 m개의 제2 터치전극 라인은 상기 터치 센싱 회로에 의해 신호 검출이 되는 수신 전극 라인들인 터치표시장치.

### 청구항 16

제1항에 있어서,

상기 n개의 제1 터치전극 라인은 터치 센싱 회로에 의해 신호 검출이 되는 수신 전극 라인들이고, 상기 m개의 제2 터치전극 라인은 상기 터치 센싱 회로에 의해 구동 신호가 인가되는 송신 전극 라인들인 터치표시장치.

#### 청구항 17

제1항에 있어서,

상기 n개의 제1 터치전극 라인 각각은 하나의 바(Bar) 형태이고, 상기 m개의 제2 터치전극 라인 각각은 하나의 바 형태인 터치표시장치.

#### 청구항 18

제1항에 있어서,

상기 n개의 제1 터치전극 라인 각각은, 제1 브릿지 패턴에 의해 연결된 다수의 제1 터치전극을 포함하고, 상기 제1 브릿지 패턴은, 상기 다수의 제1 터치전극과 동일한 층에 위치하고 상기 다수의 제1 터치전극과 일체로 된 패턴이거나, 상기 다수의 제1 터치전극과 다른 층에 위치하여 상기 다수의 제1 터치전극과 연결되는 패턴이거나.

상기 m개의 제2 터치전극 라인 각각은 제2 브릿지(Bridge) 패턴에 의해 연결된 다수의 제2 터치전극을 포함하고, 상기 제2 브릿지 패턴은, 상기 다수의 제2 터치전극과 동일한 층에 위치하고 상기 다수의 제2 터치전극과 일체로 된 패턴이거나, 상기 다수의 제2 터치전극과 다른 층에 위치하여 상기 다수의 제2 터치전극과 연결되는 패턴인 터치표시장치.

#### 청구항 19

제18항에 있어서,

상기 터치센서메탈은 상기 다수의 제1 터치전극 및 상기 제2 터치전극에 포함되는 전극 메탈을 포함하거나, 상기 제1 브릿지 패턴 또는 상기 제2 브릿지 패턴에 포함된 브릿지 메탈을 포함하는 터치표시장치.

#### 청구항 20

제1항에 있어서,

상기 n개의 제1 터치전극 라인 및 상기 m개의 제2 터치전극 라인 각각은 다수의 오픈 영역을 갖는 메쉬 타입이고,

상기 다수의 오픈 영역 각각은 하나 이상의 서브픽셀의 발광 영역과 대응되는 터치표시장치.

#### 청구항 21

제1항에 있어서.

상기 표시영역과 상기 터치패드 부 사이에 배치되며, 상기 터치패드 부의 높이보다 더 높은 높이를 갖고, 상기 표시영역에 배치되는 뱅크와 동일 물질을 포함하는 하나 이상의 댐을 포함하는 터치표시장치.

#### 청구항 22

제1항에 있어서,

상기 공통전극은 상기 표시영역에 배치되어 상기 비-표시영역의 일부 영역까지 연장되고,

상기 봉지층은 상기 표시영역에 배치되어 상기 비-표시영역의 일부 영역까지 연장되되, 상기 공통전극보다는 더 외곽으로 연장되어 배치되는 터치표시장치.

## 발명의 설명

#### 기술분야

[0001] 본 발명의 실시예들은 터치표시장치에 관한 것이다.

## 배경기술

- [0002] 터치표시장치는 영상이나 이미지를 표시하는 기능 이외에, 사용자가 손쉽게 정보 혹은 명령을 직관적이고 편리하게 입력할 수 있도록 해주는 터치 기반의 입력 기능을 제공할 수 있다.

- [0003] 이러한 터치표시장치는 터치 기반의 입력 기능을 제공하기 위해서, 사용자의 터치 유무를 파악하고 터치 좌표를 정확하게 센싱할 수 있어야 한다. 이를 위해, 터치표시장치는 터치센서와 터치센싱회로, 그리고, 터치센서와 터치센싱회로를 연결해주는 터치 라우팅 배선들 등을 포함한다.

- [0004] 요즈음, 여러 이유로 인해, 터치센서를 내장하는 표시패널을 개발하고 있다. 이러한 표시패널의 경우, 터치센서의 내장으로 인하여, 베젤이 커지거나 기생 캐패시턴스가 커지는 문제점이 발생하고 있다.

## 발명의 내용

#### 해결하려는 과제

- [0005] 본 발명의 실시예들은 터치센서와 터치센싱회로를 연결해주는 터치 라우팅 배선들이 비-표시영역에 배치되더라 도, 작은 베젤 사이즈를 갖는 터치표시장치를 제공할 수 있다.

- [0006] 본 발명의 실시예들은 터치센서와 터치센싱회로를 연결해주는 터치 라우팅 배선들에 의한 기생 캐패시턴스 형성을 방지해주어 터치 감도를 향상시켜줄 수 있는 터치표시장치를 제공할 수 있다.

- [0007] 본 발명의 실시예들은 더블 라우팅 구조에 적합한 터치 라우팅 배선들의 배치 구조를 갖는 터치표시장치를 제공할 수 있다.

- [0008] 본 발명의 실시예들은 싱글 라우팅 구조에 적합한 터치 라우팅 배선들의 배치 구조를 갖는 터치표시장치를 제공할 수 있다.

- [0009] 본 발명의 실시예들은 해프-싱글 라우팅 구조에 적합한 터치 라우팅 배선들의 배치 구조를 갖는 터치표시장치를 제공할 수 있다.

### 과제의 해결 수단

- [0010] 일 측면에서, 본 발명의 실시예들은, 기판과, 기판 상에 다수의 서브픽셀 영역마다 배치되는 다수의 픽셀전극과, 다수의 픽셀전극 상에 배치되며 공통전압이 인가되는 공통전극과, 공통전극을 덮으면서 배치되는 봉지층과, 표시영역에서 봉지층 상에 배치되는 n개의 제1 터치전극 라인과 m개의 제2 터치전극 라인을 포함하며, n개의 제1 터치전극 라인과 m개의 제2 터치전극 라인 각각은 1가지 이상의 터치센서메탈을 포함하는 터치센서를 포함하는 터치표시장치를 제공할 수 있다.

- [0011] 터치표시장치는, 표시영역의 외곽 영역인 비-표시영역 중 표시영역으로부터 제1 방향으로 외곽에 위치하는 제1 비-표시영역에 배치되며, 2n개의 제1 터치패드 및 2m개의 제2 터치패드를 포함하는 터치패드 부를 더 포함할 수 있다.

- [0012] 터치표시장치는, 봉지층의 경사면을 따라 내려와, n개의 제1 터치전극 라인 각각의 일단과 타단을 제1 비-표시영역에 배치된 2n개의 제1 터치패드와 전기적으로 연결해주는 2n개의 제1 터치 라우팅 배선과, 봉지층의 경사면을 따라 내려와, m개의 제2 터치전극 라인 각각의 일단과 타단을 제1 비-표시영역에 배치된 2m개의 제2 터치패드와 전기적으로 연결해주는 2m개의 제2 터치 라우팅 배선을 포함할 수 있다.

- [0013] 2n개의 제1 터치 라우팅 배선 중 둘 이상의 제1 터치 라우팅 배선과, 2m개의 제2 터치 라우팅 배선 중 둘 이상의 제 2 터치 라우팅 배선은, 표시영역으로부터 제2 방향으로 외곽에 위치하는 제2 비-표시영역을 지나갈 수 있다.

- [0014] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선은, 터치센서메탈이 포함된 하나 이상의 제1 터치

- 라우팅 배선과, 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선을 포함할 수 있다.

- [0015] 제2 비-표시영역을 지나가는 둘 이상의 제2 터치 라우팅 배선은, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선의, 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선을 포함할 수 있다.

- [0016] 제1 메탈은 터치센서메탈과 다른 메탈로서, 표시영역 내 배치된 트랜지스터들의 소스 및 드레인 전국에 포함되는 소스-드레인 메탈 과 표시영역 내 배치된 트랜지스터들의 게이트 전국에 포함되는 게이트 메탈 중 1 가지 이상을 포함할 수 있다.

- [0017] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선에서, 터치센서메탈이 포함된 하나 이상의 제1 터 치 라우팅 배선과, 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선은 서로 다른 층에서 서로 엇갈리면서 배치될 수 있다.

- [0018] 제2 비-표시영역을 지나가는 둘 이상의 제2 터치 라우팅 배선에서, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선과 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선은 서로 다른 층에서 서로 엇갈리면서 배치될 수 있다.

- [0019] 터치표시장치는, 표시영역 내 배치된 다수의 게이트 라인과 전기적으로 연결되며, 제2 비-표시영역에 배치되며 제1 메탈이 포함된 트랜지스터들을 포함하는 게이트 구동 회로를 더 포함할 수 있다.

- [0020] 터치표시장치는, 공통전극으로 공통전압을 전달하며 제2 비-표시영역에 배치된 전원전달패턴을 더 포함할 수 있다.

- [0021] 전원전달패턴은 터치센서메탈과 다른 제1 메탈을 포함할 수 있다.

- [0022] 전원전달패턴은 게이트 구동 회로보다 표시영역에 더 가깝게 배치될 수 있다.

- [0023] 표시영역에서 제2 비-표시영역까지 확장된 공통전극은 게이트 구동 회로와 중첩될 수 있다.

- [0024] 공통전극은 게이트 구동 회로가 노출되도록 오픈 되어 있을 수 있다.

- [0025] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선과, 제2 비-표시영역을 지나가는 둘 이상의 제2 터치 라우팅 배선은, 표시영역에서 제2 비-표시영역까지 확장된 공통전극과 미 중첩되어 배치될 수 있다.

- [0026] 제2 비-표시영역을 지나가는 둘 이상의 제2 터치 라우팅 배선은 제2 비-표시영역을 지나가는 둘 이상의 제1 터 치 라우팅 배선보다 더 외곽에 배치될 수 있다.

- [0027] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선 중 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선은 봉지층 상에 배치되고, 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선 중 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선은 봉지층 아래에 배치될 수 있다.

- [0028] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선 중 터치센서메탈이 포함된 하나 이상의 제1 터치라우팅 배선의 일부는 제2 비-표시영역 내에서 봉지층의 경사면과 중첩될 수 있다.

- [0029] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선 각각은, 터치센서 메탈이 포함된 상부 배선과 제1 메탈이 포함된 하부 배선을 포함하고, 상부 배선의 일단과 하부 배선의 일단은 봉지층의 끝에서 제1 방향으로 외곽에 위치하는 제1 지점에서 컨택되고, 상부 배선의 타단과 하부 배선의 타단은 봉지층의 반대 끝에서 제1 방향의 반대 방향으로 외곽에 위치한 제3 지점에서 컨택될 수 있다.

- [0030] 제2 비-표시영역을 지나가는 둘 이상의 제1 터치 라우팅 배선 중에서, 하나의 제1 터치 라우팅 배선은 다른 제1 터치 라우팅 배선의 위 또는 아래에 배치된 메탈을 통해 해당 제1 터치전극 라인과 연결될 수 있다.

- [0031] n개의 제1 터치전극 라인은 터치 센싱 회로에 의해 구동 신호가 인가되는 송신 전극 라인들이고, m개의 제2 터 치전극 라인은 터치 센싱 회로에 의해 신호 검출이 되는 수신 전극 라인들일 수 있다.

- [0032] 또는, n개의 제1 터치전극 라인은 터치 센싱 회로에 의해 신호 검출이 되는 수신 전극 라인들이고, m개의 제2 터치전극 라인은 터치 센싱 회로에 의해 구동 신호가 인가되는 송신 전극 라인들일 수 있다.

- [0033] 공통전극은 표시영역에 배치되어 비-표시영역의 일부 영역까지 연장되고, 봉지층은 표시영역에 배치되어 비-표 시영역의 일부 영역까지 연장되되, 공통전극보다는 더 외곽으로 연장되어 배치될 수 있다.

# 발명의 효과

- [0034] 본 발명의 실시예들에 의하면, 터치센서와 터치센싱회로를 연결해주는 터치 라우팅 배선들이 비-표시영역에 배 치되더라도, 터치 라우팅 배선들의 다층 구조를 통해 베벨 사이즈를 줄여줄 수 있다.

- [0035] 본 발명의 실시예들에 의하면, 공통전극의 위치를 고려하여, 터치센서와 터치센싱회로를 연결해주는 터치 라우팅 배선들의 배치 구조 변경을 통해, 터치 라우팅 배선들에 의한 기생 캐패시턴스 형성을 방지해주어 터치 감도를 향상시켜줄 수 있다.

- [0036] 본 발명의 실시예들에 의하면, 더블 라우팅 구조에 적합한 터치 라우팅 배선들의 배치 구조를 갖는 터치표시장 치를 제공할 수 있다.

- [0037] 본 발명의 실시예들에 의하면, 성글 라우팅 구조에 적합한 터치 라우팅 배선들의 배치 구조를 갖는 터치표시장 치를 제공할 수 있다.

- [0038] 본 발명의 실시예들에 의하면, 해프-싱글 라우팅 구조에 적합한 터치 라우팅 배선들의 배치 구조를 갖는 터치표 시장치를 제공할 수 있다.

# 도면의 간단한 설명

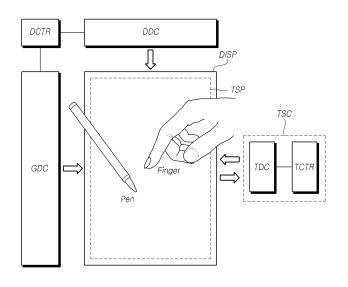

- [0039] 도 1은 본 발명의 실시예들에 따른 터치표시장치의 시스템 구성도이다.

- 도 2는 본 발명의 실시예들에 따른 터치표시장치의 표시패널을 개략적으로 나타낸 도면이다.

- 도 3은 본 발명의 실시예들에 따른 표시패널에 터치패널이 내장되는 구조를 예시적으로 나타낸 도면이다.

- 도 4 내지 도 6은 본 발명의 실시예들에 따른 표시패널에서의 터치센서 구조를 간략하게 나타낸 도면이다.

- 도 7은 본 발명의 실시예들에 따른 표시패널에서의 터치센서 구조의 다른 예시도이다.

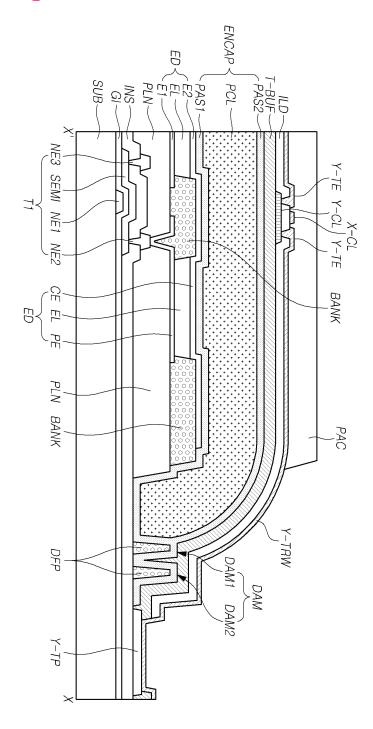

- 도 8은 본 발명의 실시예들에 따른 표시패널의 부분적인 단면도이다.

- 도 9 내지 도 11은 본 발명의 실시예들에 따른 표시패널에 배치된 터치전극을 예시적으로 나타낸 도면이다.

- 도 12 및 도 13은 본 발명의 실시예들에 따른 표시패널에 컬러필터가 포함된 경우의 단면 구조를 예시적으로 나타낸 도면들이다.

- 도 14는 본 발명의 실시예들에 따른 표시패널의 표시영역과 비-표시영역들을 나타낸 도면이다.

- 도 15는 본 발명의 실시예들에 따른 표시패널의 제2 비-표시영역에서, 터치 라우팅 배선들의 배치 구조를 개략화하여 나타낸 도면이다.

- 도 16은 본 발명의 실시예들에 따른 표시패널에서 공통 전극에서 발생되는 노이즈를 나타낸 도면이다.

- 도 17은 본 발명의 실시예들에 따른 터치표시장치의 센싱 시스템의 등가회로를 나타낸 도면이다.

- 도 18 내지 도 27은 본 발명의 실시예들에 따른 터치표시장치가 더블 라우팅 구조를 갖는 경우, 네로우 베젤을 구현하기 위하여, 표시패널의 제2 비-표시영역에서의 제1 터치 라우팅 배선들과 제2 터치 라우팅 배선들 중 제2 터치 라우팅 배선들이 공통전극과 중첩되지 않도록 하는 배치 구조들을 나타낸 도면들이다.

- 도 28은 도 18 내지 도 27의 배치 구조들에 따른 센싱 시스템의 등가회로이다.

- 도 29 내지 도 31은 본 발명의 실시예들에 따른 터치표시장치가 더블 라우팅 구조를 갖는 경우, 네로우 베젤을 구현하기 위하여, 표시패널의 제2 비-표시영역에서의 제1 터치 라우팅 배선들과 제2 터치 라우팅 배선들이 공통 전극과 중첩되지 않도록 하는 배치 구조들을 나타낸 도면들이다.

- 도 32는 도 29 내지 도 31의 배치 구조들에 따른 센싱 시스템의 등가회로이다.

- 도 33 내지 도 40은 본 발명의 실시예들에 따른 터치표시장치가 싱글 라우팅 구조 또는 해프-싱글 라우팅 구조 를 갖는 경우, 네로우 베젤을 구현하기 위하여, 표시패널의 제2 비-표시영역에서의 제1 터치 라우팅 배선들과 제2 터치 라우팅 배선들이 공통전극과 중첩되지 않도록 하는 배치 구조들을 나타낸 도면들이다.

- 도 41은 도 33 내지 도 40의 배치 구조들에 따른 센싱 시스템의 등가회로이다.

- 도 42는 본 발명의 실시예들에 따른 터치표시장치의 네로우 베젤 구현을 위한 배치 구조들에 따라, 터치 신호들과 노이즈의 변화를 나타낸 도면이다.

## 발명을 실시하기 위한 구체적인 내용

- [0040] 이하, 본 발명의 일부 실시예들을 예시적인 도면을 참조하여 상세하게 설명한다. 각 도면의 구성 요소들에 참조 부호를 부가함에 있어서, 동일한 구성 요소들에 대해서는 비록 다른 도면상에 표시되더라도 가능한 한 동일한 부호를 가질 수 있다. 또한, 본 발명을 설명함에 있어, 관련된 공지 구성 또는 기능에 대한 구체적인 설명이 본 발명의 요지를 호릴 수 있다고 판단되는 경우에는 그 상세한 설명은 생략할 수 있다. 본 명세서 상에서 언급된 "포함한다", "갖는다", "이루어진다" 등이 사용되는 경우 "~만"이 사용되지 않는 이상 다른 부분이 추가될 수 있다. 구성 요소를 단수로 표현한 경우에 특별한 명시적인 기재 사항이 없는 한 복수를 포함하는 경우를 포함할 수 있다.

- [0041] 또한, 본 발명의 구성 요소를 설명하는 데 있어서, 제1, 제2, A, B, (a), (b) 등의 용어를 사용할 수 있다. 이 러한 용어는 그 구성 요소를 다른 구성 요소와 구별하기 위한 것일 뿐, 그 용어에 의해 해당 구성 요소의 본질, 차례, 순서 또는 개수 등이 한정되지 않는다.

- [0042] 구성 요소들의 위치 관계에 대한 설명에 있어서, 둘 이상의 구성 요소가 "연결", "결합" 또는 "접속" 등이 된다고 기재된 경우, 둘 이상의 구성 요소가 직접적으로 "연결", "결합" 또는 "접속" 될 수 있지만, 둘 이상의 구성 요소와 다른 구성 요소가 더 "개재"되어 "연결", "결합" 또는 "접속"될 수도 있다고 이해되어야 할 것이다. 여기서, 다른 구성 요소는 서로 "연결", "결합" 또는 "접속" 되는 둘 이상의 구성 요소 중 하나 이상에 포함될 수도 있다.

- [0043] 구성 요소들이나, 동작 방법이나 제작 방법 등과 관련한 시간적 흐름 관계에 대한 설명에 있어서, 예를 들어, "~후에", "~에 이어서", "~다음에", "~전에" 등으로 시간적 선후 관계 또는 흐름적 선후 관계가 설명되는 경우, "바로" 또는 "직접"이 사용되지 않는 이상 연속적이지 않은 경우도 포함할 수 있다.

- [0044] 한편, 구성 요소에 대한 수치 또는 그 대응 정보(예: 레벨 등)가 언급된 경우, 별도의 명시적 기재가 없더라도, 수치 또는 그 대응 정보는 각종 요인(예: 공정상의 요인, 내부 또는 외부 충격, 노이즈 등)에 의해 발생할 수 있는 오차 범위를 포함하는 것으로 해석될 수 있다.

- [0045] 도 1은 본 발명의 실시예들에 따른 터치표시장치의 시스템 구성도이다.

- [0046] 도 1을 참조하면, 본 발명의 실시예들에 따른 터치표시장치는 영상을 디스플레이 하기 위한 영상 디스플레이 기능과 사용자의 손가락, 펜 등의 터치 오브젝트에 의한 터치 조작에 대하여 터치 유무 및/또는 터치 좌표를 센싱하기 위한 터치 센싱 기능을 모두 제공할 수 있다.

- [0047] 영상 디스플레이 기능을 제공하기 위하여, 본 발명의 실시예들에 따른 터치표시장치는 다수의 데이터 라인 및 다수의 게이트 라인이 배치되고 다수의 데이터 라인 및 다수의 게이트 라인에 의해 정의된 다수의 서브픽셀이배열된 표시패널(DISP)과, 다수의 데이터 라인을 구동하는 데이터구동회로(DDC)와, 다수의 게이트 라인을 구동하는 게이트구동회로(GDC)와, 데이터구동회로(DDC) 및 게이트구동회로(GDC)의 동작을 제어하는 디스플레이 컨트롤러(DCTR) 등을 포함할 수 있다.

- [0048] 데이터구동회로(DDC), 게이트구동회로(GDC) 및 디스플레이 컨트롤러(DCTR) 각각은 하나 이상의 개별 부품으로 구현될 수도 있다. 경우에 따라서, 데이터구동회로(DDC), 게이트구동회로(GDC) 및 디스플레이 컨트롤러(DCTR) 중 둘 이상은 하나의 부품으로 통합되어 구현될 수도 있다. 예를 들어, 데이터구동회로(DDC)와 디스플레이 컨트롤러(DCTR)는 하나의 집적회로 칩(IC Chip)으로 구현될 수 있다.

- [0049] 터치 센싱 기능을 제공하기 위하여, 본 발명의 실시예들에 따른 터치표시장치는 터치센서를 포함하는 터치패널 (TSP)과, 터치패널(TSP)로 터치 구동 신호를 공급하고 터치패널(TSP)로부터 터치 센싱 신호를 검출하여, 검출된 터치 센싱 신호를 토대로 터치패널(TSP)에서의 사용자의 터치 유무 또는 터치 위치(터치 좌표)를 센싱하는 터치 센싱회로(TSC)를 포함할 수 있다.

- [0050] 터치센싱회로(TSC)는, 일 예로, 터치패널(TSP)로 터치 구동 신호를 공급하고 터치패널(TSP)로부터 터치 센싱 신호를 검출하는 터치구동회로(TDC)와, 터치구동회로(TDC)에 의해 검출된 터치 센싱 신호를 토대로 터치패널(TSP)에서의 사용자의 터치 유무 및/또는 터치 위치를 센싱하는 터치 컨트롤러(TCTR) 등을 포함할 수 있다.

- [0051] 터치구동회로(TDC)는 터치패널(TSP)로 터치 구동 신호를 공급하는 제1 회로 파트와 터치패널(TSP)로부터 터치 센싱 신호를 검출하는 제2 회로 파트를 포함할 수 있다.

- [0052] 터치구동회로(TDC) 및 터치 컨트롤러(TCTR)는 별도의 부품으로 구현되거나, 경우에 따라서, 하나의 부품으로 통

합되어 구현될 수도 있다.

- [0053] 한편, 데이터구동회로(DDC), 게이트구동회로(GDC) 및 터치구동회로(TDC) 각각은 하나 이상의 집적회로로 구현될 수 있으며, 표시패널(DISP)과의 전기적인 연결 관점에서 COG (Chip On Glass) 타입, COF (Chip On Film) 타입, 또는 TCP (Tape Carrier Package) 타입 등으로 구현될 수 있으며, 게이트구동회로(GDC)는 GIP (Gate In Panel) 타입으로도 구현될 수 있다. 단, 아래에서, 게이트구동회로(GDC)는 GIP 타입으로 구현된 경우를 예로 든다.

- [0054] 한편, 디스플레이 구동을 위한 회로 구성들(DDC, GDC, DCTR)과 터치 센싱을 위한 회로 구성들(TDC, TCTR) 각각은 하나 이상의 개별 부품으로 구현될 수 있다. 경우에 따라서 디스플레이 구동을 위한 회로 구성들(DDC, GDC, DCTR) 중 하나 이상과 터치 센싱을 위한 회로 구성들(TDC, TCTR) 중 하나 이상은 기능적으로 통합되어 하나 이상의 부품으로 구현될 수도 있다.

- [0055] 예를 들어, 데이터구동회로(DDC)와 터치구동회로(TDC)는 하나 또는 둘 이상의 집적회로 칩에 통합 구현될 수 있다. 데이터구동회로(DDC)와 터치구동회로(TDC)가 둘 이상의 집적회로 칩에 통합 구현되는 경우, 둘 이상의 집적회로 칩 각각은 데이터 구동 기능과 터치 구동 기능을 가질 수 있다.

- [0056] 한편, 본 발명의 실시예들에 따른 터치표시장치는 유기발광표시장치, 액정표시장치 등의 다양한 타입일 수 있다. 아래에서는, 설명의 편의를 위해, 터치표시장치 및 표시패널(DISP)은 유기발광표시장치 및 유기발광표시 패널인 것으로 예를 들어 설명한다.

- [0057] 또 한편, 후술하겠지만, 터치패널(TSP)은 터치 구동 신호가 인가되거나 터치 센싱 신호가 검출될 수 있는 터치 센서를 포함할 수 있으며, 터치센서와 터치구동회로(TDC)를 전기적으로 연결해주기 위한 터치 라우팅 배선들을 더 포함할 수 있다.

- [0058] 터치센서는 터치전극 라인들을 포함할 수 있다. 각 터치전극 라인은 하나의 전극으로 된 바(Bar) 타입이거나, 다수의 터치전극이 연결된 타입일 수 있다. 각 터치전극 라인이 다수의 터치전극이 연결된 타입인 경우, 각 터치전극 라인은 다수의 터치전극과 이들을 연결해주는 브릿지 패턴(들)을 포함할 수 있다. 이러한 터치센서는 터치센서메탈을 포함할 수 있다. 여기서, 터치센서메탈은 터치전극에 포함된 전극 메탈과 브릿지 패턴에 포함된 브릿지 메탈 등을 포함할 수 있다. 터치 라우팅 배선은 전극 메탈 및 브릿지 메탈 중 적어도 하나를 포함할 수 있다. 경우에 따라서, 터치센서는 터치전극 라인들뿐만 아니라, 터치 라우팅 배선들을 더 포함한다고도 볼 수 있다.

- [0059] 터치패널(TSP)은 표시패널(DISP)의 외부에 존재할 수도 있다. 즉 터치패널(TSP)과 표시패널(DISP)은 별도로 제작되어 결합될 수 있다. 이러한 터치패널(TSP)을 외장형 타입 또는 애드-온(Add-on) 타입이라고 한다.

- [0060] 이와 다르게, 터치패널(TSP)은 표시패널(DISP)의 내부에 내장될 수도 있다. 즉, 표시패널(DISP)을 제작할 때, 터치패널(TSP)을 구성하는 터치센서는 디스플레이 구동을 위한 전극들 및 신호라인들과 함께 형성될 수 있다. 이러한 터치패널(TSP)을 내장형 타입이라고 한다. 아래에서는, 설명의 편의를 위하여, 터치패널(TSP)이 내장형 타입인 경우로 예를 들어 설명한다.

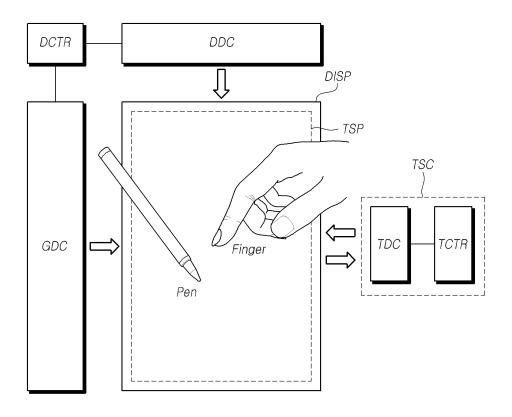

- [0061] 도 2는 본 발명의 실시예들에 따른 터치표시장치의 표시패널(DISP)을 개략적으로 나타낸 도면이다.

- [0062] 도 2를 참조하면, 표시패널(DISP)은 영상이 표시되는 표시영역(AA)과, 표시영역(AA)의 외곽 경계 라인(BL)의 외곽 영역인 비-표시영역(NA)을 포함할 수 있다.

- [0063] 표시패널(DISP)의 표시영역(AA)에는, 영상 디스플레이를 위한 다수의 서브픽셀이 배열되고, 디스플레이 구동을 위한 각종 전극들이나 신호라인들이 배치된다.

- [0064] 표시패널(DISP)의 표시영역(AA)에는, 터치 센싱을 위한 터치센서와, 터치센서와 전기적으로 연결된 다수의 터치 라우팅 배선 등이 배치될 수 있다. 이에 따라, 표시영역(AA)은 터치 센싱이 가능한 터치 센싱 영역이라고도 할 수 있다.

- [0065] 표시패널(DISP)의 비-표시영역(NA)에는, 표시영역(AA)에 배치된 각종 신호라인들이 연장된 링크라인들 또는 표시영역(AA)에 배치된 각종 신호라인들과 전기적으로 연결된 링크라인들과, 이 링크라인들에 전기적으로 연결된 디스플레이 패드들이 배치될 수 있다. 비-표시영역(NA)에 배치된 디스플레이 패드들은 디스플레이 구동 회로 (DDC, GDC 등)가 본딩되거나 전기적으로 연결될 수 있다. 예를 들어, 비-표시영역(NA)에 배치된 디스플레이 패드들은 데이터 라인들이 연장되거나 연결된 데이터 링크 라인들이 연결되는 데이터 패드들을 포함할 수 있다.

- [0066] 표시패널(DISP)의 비-표시영역(NA)에는, 표시영역(AA)에 배치된 터치센서와 전기적으로 연결되는 터치 라우팅

배선들과, 터치 라우팅 배선들이 전기적으로 연결된 터치패드들이 배치될 수 있다. 비-표시영역(NA)에 배치된 패드들은 터치구동회로(TDC)가 본딩되거나 전기적으로 연결될 수 있다.

- [0067] 표시영역(AA)에 배치된 다수의 터치전극 라인 중 일부가 비-표시영역(NA)으로 확장될 수 있으며, 표시영역(AA)에 배치된 다수의 터치전극 라인과 동일한 물질의 하나 이상의 전극(터치전극)이 비-표시영역(NA)에 더 배치될 수도 있다. 표시영역(AA)에 배치된 다수의 터치전극 라인 각각에 포함되는 다수의 터치전극 중 최외곽 터치전극의 일부가 비-표시영역(NA)으로 확장될 수 있으며, 표시영역(AA)에 배치된 다수의 터치전극 라인 각각에 포함되는 다수의 터치전극 과 동일한 물질의 하나 이상의 전극(터치전극)이 더 배치될 수도 있다.

- [0068] 즉, 터치센서는 표시영역(AA) 내에 모두 존재하거나, 터치센서의 대부분은 표시영역(AA)에 존재하고 터치센서의 일부는 비-표시영역(NA)에 존재하거나 표시영역(AA)과 비-표시영역(NA)에 걸쳐서 존재할 수 있다.

- [0069] 한편, 도 2를 참조하면, 본 발명의 실시예들에 따른 터치표시장치의 표시패널(DISP)은 표시영역(AA) 내 어떠한 충(예: 봉지층)이 무너지는 것을 방지하기 위한 적어도 하나의 댐(Dam)이 배치되는 댐 영역(DA)을 포함할 수 있다.

- [0070] 댐 영역(DA)은, 표시영역(AA)과 비-표시영역(NA)의 경계지점에 존재하거나, 경계지점의 근방에 존재할 수 있다. 예를 들어, 댐 영역(DA)은 외곽에서 안쪽으로 들어가다가 갑자기 높아지는 지점의 주변 영역일 수 있다. 또는, 댐 영역(DA)은 봉지층의 경사면을 따라 내려오다가 봉지층의 경사가 갑자기 완만해지거나 다시 높아지는 방향으로 변하는 지점의 주변 영역을 의미할 수도 있다.

- [0071] 댐 영역(DA)에 배치되는 적어도 하나의 댐은, 표시영역(AA)의 모든 방향(예: 4개의 방향)을 둘러싸면서 배치되거나, 표시영역(AA)의 모든 방향(예: 4개의 방향) 중 1개 내지 3개의 방향(예: 무너지기 쉬운 층이 있는 방향)에만 배치될 수도 있다.

- [0072] 댐 영역(DA)에 배치되는 적어도 하나의 댐은, 모두 연결되는 하나의 패턴일 수도 있고 단절된 둘 이상의 패턴으로 이루어질 수도 있다.

- [0073] 댐 영역(DA)에 2개 이상의 댐이 배치되는 경우, 표시영역(AA)에 가까운 댐부터 1차 댐, 2차 댐 등이라고 할 수 있다. 댐 영역(DA)에서, 어느 한 방향에서는 1차 댐만 있고, 어느 다른 한 방향에서는 1차 댐과 2차 댐이 모두 있을 수도 있다.

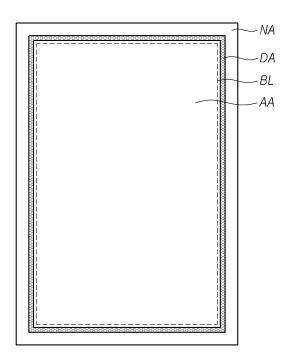

- [0074] 도 3은 본 발명의 실시예들에 따른 표시패널(DISP)에 터치패널이 내장되는 구조를 예시적으로 나타낸 도면이다.

- [0075] 도 3을 참조하면, 표시패널(DISP)의 표시영역(AA)에는, 기판(SUB) 상에 다수의 서브픽셀(SP)이 배열된다.

- [0076] 각 서브픽셀(SP)은, 발광소자(ED)와, 발광소자(ED)를 구동하기 위한 제1 트랜지스터(T1)와, 제1 트랜지스터(T 1)의 제1 노드(N1)로 데이터 전압(VDATA)을 전달해주기 위한 제2 트랜지스터(T2)와, 한 프레임 동안 일정 전압을 유지해주기 위한 스토리지 캐패시터(Cst) 등을 포함할 수 있다.

- [0077] 제1 트랜지스터(T1)는 데이터 전압이 인가될 수 있는 제1 노드(N1), 발광소자(ED)와 전기적으로 연결되는 제2 노드(N2) 및 구동 전압 라인(DVL)으로부터 구동 전압(VDD)이 인가되는 제3 노드(N3)를 포함할 수 있다. 제1 노드(N1)는 게이트 노드이고, 제2 노드(N2)는 소스 노드 또는 드레인 노드일 수 있고, 제3 노드(N3)는 드레인 노드 또는 소스 노드일 수 있다. 이러한 제1 트랜지스터(T1)는 발광소자(ED)를 구동하는 구동 트랜지스터라고도 한다.

- [0078] 발광소자(ED)는 픽셀전극(예: 애노드 전극), 발광층 및 공통전극(예: 캐소드 전극)을 포함할 수 있다. 픽셀전극은 각 서브픽셀(SP)마다 다른 픽셀전압에 해당하는 데이터 전압(VDATA)이 인가될 수 있으며 제1 트랜지스터(T1)의 제2 노드(N2)와 전기적으로 연결되고, 공통전극은 모든 서브픽셀(SP)에 공통으로 인가되는 공통전압에 해당하는 기저 전압(VSS)이 인가될 수 있다.

- [0079] 발광소자(ED)는 유기물을 사용하는 발광소자(ED)이거나 무기물을 사용하는 발광소자(ED)일 수 있다. 유기물을 사용하는 발광소자(ED)에서 발광층은 유기물을 포함하는 유기 발광층을 포함할 수 있으며, 이 경우, 발광소자(ED)는 유기발광다이오드(OLED: Organic Light Emitting Diode)라고 한다.

- [0080] 제2 트랜지스터(T2)는, 게이트 라인(GL)을 통해 인가되는 스캔 신호(SCAN)에 의해 온-오프가 제어되며, 제1 트랜지스터(T1)의 제1 노드(N1)와 데이터 라인(DL) 사이에 전기적으로 연결될 수 있다. 이러한 제2 트랜지스터 (T2)는 스위칭 트랜지스터라고도 한다.

- [0081] 제2 트랜지스터(T2)는 스캔 신호(SCAN)에 의해 턴-온 되면, 데이터 라인(DL)에서 공급된 데이터 전압(VDATA)을 제1 트랜지스터(T1)의 제1 노드(N1)에 전달한다.

- [0082] 스토리지 캐패시터(Cst)는 제1 트랜지스터(T1)의 제1 노드(N1)와 제2 노드(N2) 사이에 전기적으로 연결될 수 있다.

- [0083] 각 서브픽셀(SP)은 도 3에 도시된 바와 같이 2개의 트랜지스터(T1, T2)와 1개의 캐패시터(Cst)를 포함하는 2T(Transistor)1C(Capacitor) 구조를 가질 수 있으며, 경우에 따라서, 1개 이상의 트랜지스터를 더 포함하거나, 1개 이상의 캐패시터를 더 포함할 수도 있다.

- [0084] 스토리지 캐패시터(Cst)는, 제1 트랜지스터(T1)의 제1 노드(N1)와 제2 노드(N2) 사이에 존재할 수 있는 내부 캐패시터(Internal Capacitor)인 기생 캐패시터(예: Cgs, Cgd)가 아니라, 제1 트랜지스터(T1)의 외부에 의도적으로 설계한 외부 캐패시터(External Capacitor)일 수 있다.

- [0085] 제1 트랜지스터(T1) 및 제2 트랜지스터(T2) 각각은 n 타입 트랜지스터이거나 p 타입 트랜지스터일 수 있다.

- [0086] 한편, 전술한 바와 같이, 표시패널(DISP)에는 발광소자(ED), 2개 이상의 트랜지스터(T1, T2) 및 1개 이상의 캐 패시터(Cst) 등의 회로소자가 배치된다. 이러한 회로소자(특히, 발광소자(ED))는 외부의 수분이나 산소 등에 취약하기 때문에, 외부의 수분이나 산소가 회로소자(특히, 발광소자(ED))로 침투되는 것을 방지하기 위한 봉지층 (ENCAP)이 표시패널(DISP)에 배치될 수 있다.

- [0087] 봉지층(ENCAP)은 하나의 층으로 되어 있을 수도 있지만, 다수의 층으로 되어 있을 수도 있다. 예를 들어, 봉지 충(ENCAP)이 다수의 층으로 이루어진 경우, 봉지층(ENCAP)은 하나 이상의 무기 봉지층과 하나 이상의 유기 봉지 충을 포함할 수 있다. 구체적인 예로서, 봉지층(ENCAP)은 제1 무기 봉지층, 유기 봉지층 및 제2 무기 봉지층을 포함하여 구성될 수 있다. 여기서, 유기 봉지층은 제1 무기 봉지층과 제2 무기 봉지층 사이에 위치할 수 있다.

- [0088] 제1 무기 봉지층은 발광소자(ED)와 가장 인접하도록 공통전극(예: 캐소드 전극) 상에 형성될 수 있다. 이러한 제1 무기 봉지층은, 일 예로, 질화실리콘(SiNx), 산화 실리콘(SiOx), 산화질화실리콘(SiON) 또는 산화 알루미늄 (Al<sub>2</sub>O<sub>3</sub>) 등과 같은 저온 중착이 가능한 무기 절연 재질로 형성될 수 있다. 이에 따라, 제1 무기 봉지층이 저온 분위기에서 중착되므로, 제1 무기 봉지층의 증착 공정 시 고온 분위기에 취약한 발광층(유기 발광층)이 손상되는 것을 방지할 수 있다.

- [0089] 유기 봉지층은 제1 무기 봉지층보다 작은 면적으로 형성될 수 있으며, 제1 무기 봉지층의 양 끝단을 노출시키도록 형성될 수 있다. 이러한 유기 봉지층은 터치표시장치의 휘어짐에 따른 각 층들 간의 응력을 완화시키는 완충역할을 하며, 평탄화 성능을 강화할 수 있다. 이 유기 봉지층은, 일 예로, 아크릴 수지, 에폭시 수지, 폴리이미드, 폴리에틸렌 또는 실리콘옥시카본(SiOC) 등과 같은 유기 절연 재질로 형성될 수 있다.

- [0090] 제 2 무기 봉지층은 유기 봉지층 상에 유기 봉지층 및 제1 무기 봉지층 각각의 상부면 및 측면을 덮도록 형성될 수 있다. 이에 따라, 제2 무기 봉지층은 외부의 수분이나 산소가 제1 무기 봉지층 및 유기 봉지층으로 침투하는 것을 최소화하거나 차단할 수 있다. 이러한 제2 무기 봉지층은, 일 예로, 질화실리콘(SiN<sub>x</sub>), 산화 실리콘(SiO<sub>x</sub>), 산화질화실리콘(SiON) 또는 산화 알루미늄(A<sub>12</sub>O<sub>3</sub>) 등과 같은 무기 절연 재질을 포함할 수 있다.

- [0091] 한편, 본 발명의 실시예들에 따른 터치표시장치에서는, 터치패널(TSP)이 봉지층(ENCAP) 상에 형성될 수 있다.

- [0092] 즉, 터치표시장치에서, 터치패널(TSP)에 포함되는 터치센서는 봉지층(ENCAP) 상에 배치될 수 있다. 이를 TOE (Touch Sensor On Encapsulation Layer) 구조라고 한다.

- [0093] 터치 센싱 시, 터치센서에는 터치 신호(터치 구동 신호 또는 터치 센싱 신호)가 인가될 수 있다. 따라서, 터치 센싱 시, 봉지층(ENCAP)을 사이에 두고 배치되는 터치센서와 공통전극 사이에는 터치 신호와 공통 전압(기저전 압 VSS)에 의한 전위차가 형성되고, 이에 따라, 터치 센싱 관점에서는 불필요한 기생 캐패시턴스가 형성될 수 있다. 이러한 기생 캐패시턴스는 터치 감도를 저하시킬 수 있기 때문에, 기생 캐패시턴스를 저하시키기 위하여, 터치센서와 공통전극 간의 거리는, 패널 두께, 패널 제작 공정 및 터치 센싱 성능 및 디스플레이 성능 등을 고려하여 일정 값(예: 5ょm) 이상이 되도록 설계될 수 있다. 터치센서와 공통전극 간의 거리는 봉지층(ENCAP)의 두 께와 비례한다. 따라서, 예를 들어, 기생 캐패시턴스 저감 및 방지를 위하여, 봉지층(ENCAP)의 두께는 최소 5ょm 이상으로 설계될 수 있다.

- [0094] 본 발명의 실시예들에 따른 터치표시장치는 터치센서를 이용하여 셀프-캐패시턴스의 변화를 토대로 터치 유무

및/또는 터치 좌표를 획득할 수도 있고, 터치센서를 뮤추얼-캐패시턴스의 변화를 토대로 터치 유무 및/또는 터치 좌표를 획득할 수도 있다. 아래에서는, 설명의 편의를 위하여, 본 발명의 실시예들에 따른 터치표시장치가 뮤추얼-캐패시턴스에 기반하여 터치를 센싱하는 경우를 예로 든다.

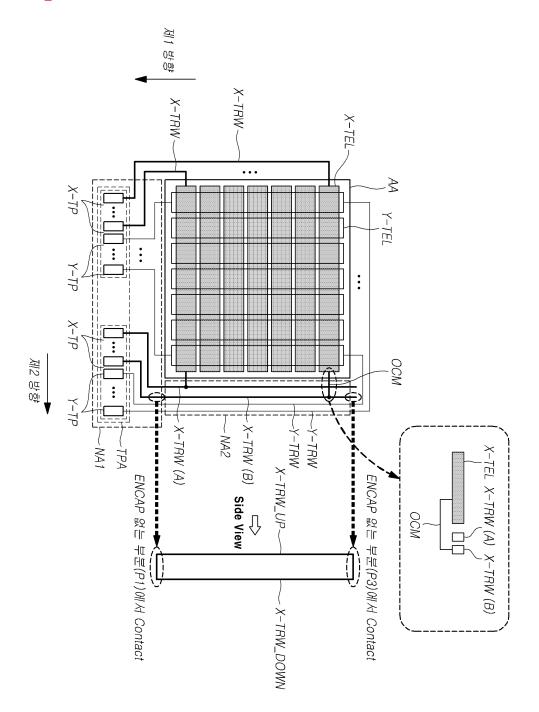

- [0095] 도 4 내지 도 6은 본 발명의 실시예들에 따른 표시패널(DISP)에서의 터치센서 구조를 간략하게 나타낸 도면이다. 도 7은 본 발명의 실시예들에 따른 표시패널(DISP)에서의 터치센서 구조의 다른 예시도이다.

- [0096] 도 4 내지 도 6을 참조하면, 본 발명의 실시예들에 따른 터치표시장치는 터치센서, 터치패드 부(TPA), 터치 라우팅 배선들(X-TRW, Y-TRW) 등을 포함할 수 있다.

- [0097] 터치센서는 표시영역(AA)에서 봉지층(ENCAP) 상에 배치되는 다수의 제1 터치전극 라인(X-TEL)과 다수의 제2 터치전극 라인(Y-TEL)을 포함할 수 있다. 다수의 제1 터치전극 라인(X-TEL)과 다수의 제2 터치전극 라인(Y-TEL) 각각은 1가지 이상의 터치센서메탈을 포함할 수 있다.

- [0098] 터치패드 부(TPA)는 표시영역(AA)으로부터 제1 방향으로 외곽에 위치하는 제1 비-표시영역(NA1)에 배치될 수 있다. 터치패드 부(TPA)는 다수의 제1 터치패드(X-TP) 및 다수의 제2 터치패드(Y-TP)를 포함할 수 있다.

- [0099] 터치 라우팅 배선들(X-TRW, Y-TRW)은 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)을 포함할 수 있다. 다수의 제1 터치 라우팅 배선(X-TRW)은 봉지층(ENCAP)의 경사면을 따라 내려와, 다수의 제1 터치전극 라인(X-TEL)을 제1 비-표시영역(NA1)에 배치된 다수의 제1 터치패드(X-TP)와 전기적으로 연결해줄 수 있다. 다수의 제2 터치 라우팅 배선(Y-TRW)은 봉지층(ENCAP)의 경사면을 따라 내려와, 다수의 제2 터치전극 라인(Y-TEL)을 제1 비-표시영역에 배치된 다수의 제1 터치패드(Y-TP)와 전기적으로 연결해줄 수 있다.

- [0100] 터치센서는 다수의 제1 터치전극 라인(X-TEL)과 다수의 제2 터치전극 라인(Y-TEL)뿐만 아니라, 터치 라우팅 배선들(X-TRW, Y-TRW)을 포함한다고 볼 수도 있다.

- [0101] 본 발명의 실시예들에 따른 터치표시장치는 제1 터치전극 라인(X-TEL)과 제2 터치전극 라인(Y-TEL) 간의 뮤추얼 -캐패시턴스의 변화를 알아내서, 이를 토대로, 핑거 터치 또는 펜 터치를 센싱할 수 있다.

- [0102] 다수의 제1 터치전극 라인(X-TEL) 각각은 제2 방향으로 배치되고, 다수의 제2 터치전극 라인(Y-TEL) 각각은 제2 방향과 다른 제1 방향으로 배치될 수 있다.

- [0103] 본 명세서에서, 제1 방향 및 제2 방향은 상대적으로 서로 다른 방향일 수 있으며, 일 예로, 제1 방향은 Y축 방향이고 제2 방향은 X축 방향일 수 있다. 이와 반대로, 제1 방향은 X축 방향이고 제2 방향은 Y축 방향일 수도 있다. 또한, 제1 방향 및 제2 방향은 서로 직교할 수도 있지만 직교하지 않을 수도 있다. 또한, 본 명세서에서, 제1 방향과 제2 방향은 서로 상대적인 것으로서, 보는 관점에서 따라 달라질 수 있으며, 행과 열 또한 서로 상대적인 것으로서, 보는 관점에서 따라 달라질 수 있다.

- [0104] 도 4 내지 도 6을 참조하면, 다수의 제1 터치전극 라인(X-TEL) 각각은 하나의 전극으로 된 바(Bar) 형태일 수 있고, 다수의 제2 터치전극 라인(Y-TEL) 각각은 하나의 전극으로 된 바 형태일 수 있다.

- [0105] 이 경우, 다수의 제1 터치전극 라인(X-TEL)과 다수의 제2 터치전극 라인(Y-TEL)은, 동일한 층에 배치될 수도 있다.

- [0106] 도 7을 참조하면, 다수의 제1 터치전극 라인(X-TEL) 각각은 제1 브릿지 패턴(X-CL)에 의해 연결된 다수의 제1 터치전극(X-TE)으로 구성될 수 있다. 즉, 1개의 제1 터치전극 라인(X-TEL) 각각은, 동일한 행(제2 방향의 동일 라인)에 배열되는 둘 이상의 제1 터치전극(X-TE)과, 인접한 제1 터치전극(X-TE)을 서로 전기적으로 연결해주는 하나 이상의 제1 브릿지 패턴(X-CL)을 포함할 수 있다. 하나 이상의 제1 브릿지 패턴(X-CL)은 둘 이상의 제1 터치전극(X-TE)과 동일한 층에 위치하고, 둘 이상의 제1 터치전극(X-TE)과 일체로 된 패턴일 수 있다. 이와 다르 게, 하나 이상의 제1 브릿지 패턴(X-CL)은 둘 이상의 제1 터치전극(X-TE)과 다른 층에 위치하며, 둘 이상의 제1 터치전극(X-TE)과 다른 층에 위치하며, 둘 이상의 제1 터치전극(X-TE)과 다르게 형성되어 둘 이상의 제1 터치전극(X-TE)과 연결되는 별도의 패턴일 수도 있다.

- [0107] 도 7을 참조하면, 다수의 제2 터치전극 라인(Y-TEL) 각각은, 제2 브릿지 패턴(Y-CL)에 의해 연결된 다수의 제2 터치전극(Y-TE)으로 구성될 수 있다. 즉, 1개의 제2 터치전극 라인(Y-TEL) 각각은, 동일한 열(제1 방향의 동일라인)에 배열되는 둘 이상의 제2 터치전극(Y-TE)과, 인접한 제2 터치전극(Y-TE)을 서로 전기적으로 연결해주는하나 이상의 제2 브릿지 패턴(Y-CL)을 포함할 수 있다. 하나 이상의 제2 브릿지 패턴(Y-CL)은 둘 이상의 제2 터치전극(Y-TE)과 일체로 된 패턴일 수 있다. 이와 다르게,하나 이상의 제2 브릿지 패턴(Y-CL)은 둘 이상의 제2 터치전극(Y-TE)과 다른 층에 위치하며,둘 이상의 제2

터치전극(Y-TE)과 다르게 형성되어 둘 이상의 제2 터치전극(Y-TE)와 연결되는 별도의 패턴일 수도 있다.

- [0108] 제1 터치전극 라인(X-TEL)과 제2 터치전극 라인(Y-TEL)이 교차되는 영역(터치전극 라인 교차 영역)에서는, 제1 브릿지 패턴(X-CL)과 제2 브릿지 패턴(Y-CL)이 교차될 수 있다. 즉, 제1 터치전극 라인(X-TEL)과 제2 터치전극 라인(Y-TEL)이 교차되는 영역(터치전극 라인 교차 영역)에서는, 제1 브릿지 패턴(X-CL)과 제2 브릿지 패턴(Y-CL)이 교차될 수 있다.

- [0109] 이와 같이, 터치전극 라인 교차 영역에서, 제1 브릿지 패턴(X-CL)과 제2 브릿지 패턴(Y-CL)이 교차된 경우, 제1 브릿지 패턴(X-CL)과 제2 브릿지 패턴(Y-CL)은 서로 다른 층에 위치해야만 한다.

- [0110] 다수의 제1 터치전극 라인(X-TEL)과 다수의 제2 터치전극 라인(Y-TEL)이 교차되도록 배치되기 위해서, 다수의 제1 터치전극(X-TE), 다수의 제1 브릿지 패턴(X-CL), 다수의 제2 터치전극(Y-TE) 및 다수의 제2 브릿지 패턴(Y-CL)은 둘 이상의 층에 위치할 수 있다.

- [0111] 터치센서를 구성하는 터치센서메탈은, 서로 다른 2가지 종류의 메탈을 포함할 수 있다. 예를 들어, 터치센서메탈은, 다수의 제1 터치전극(X-TE)과 다수의 제2 터치전극(Y-TE)에 포함되는 전극 메탈과, 다수의 제1 브릿지 패턴(X-CL) 및 다수의 제2 브릿지 패턴(Y-CL)에 포함되는 브릿지 메탈 등을 포함할 수 있다.

- [0112] 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)은 전극 메탈로 구성될 수도 있다 또는, 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)은 브릿지 메탈로 구성될 수도 있다. 또는, 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW) 각각은 위치하는 층에 따라 전극 메탈 또는 브릿지 메탈로 구성될 수 있다.

- [0113] 도 4 내지 도 6을 참조하면, 다수의 제1 터치전극 라인(X-TEL) 각각은 하나 이상의 제1 터치 라우팅 배선(X-TRW)을 통해 하나 이상의 제1 터치패드(X-TP)와 전기적으로 연결된다. 다수의 제2 터치전극 라인(Y-TEL) 각각은 하나 이상의 제2 터치 라우팅 배선(Y-TRW)을 통해 하나 이상의 제2 터치패드(Y-TP)와 전기적으로 연결된다.

- [0114] 도 4를 참조하면, 본 발명의 실시예들에 따른 표시패널(DISP)에 포함되는 터치 센서 구성 요소들(터치전극 라인 들(X-TEL, Y-TEL), 터치 라우팅 배선들(X-TRW, Y-TRW) 및 터치패드들(X-TP, Y-TP))은 더블 라우팅(Double Routing) 구조로 설계될 수 있다.

- [0115] 더블 라우팅 구조는 2개의 경로(터치 라우팅 배선)를 통해 1곳(터치전극 라인)으로 신호를 공급하거나 2개의 경로(터치 라우팅 배선)를 통해 1곳(터치전극 라인)으로부터 신호를 검출할 수 있는 구조를 의미한다.

- [0116] 더블 라우팅 구조의 경우, 다수의 제1 터치전극 라인(X-TEL) 각각은 2개의 제1 터치 라우팅 배선(X-TRW)을 통해 신호 공급(또는 신호 검출)이 될 수 있다. 다수의 제2 터치전극 라인(Y-TEL) 각각은 2개의 제2 터치 라우팅 배선(Y-TRW)을 통해 신호 검출(또는 신호 공급)이 될 수 있다.

- [0117] 더블 라우팅 구조를 갖고, 다수의 제1 및 제2 터치전극 라인(X-TEL, Y-TEL) 각각이 바 형상을 갖는 경우, 하나의 제1 터치전극 라인(X-TEL)의 양단은 2개의 제1 터치 라우팅 배선(X-TRW)을 통해 2개의 제1 터치패드(X-TP)와 전기적으로 연결될 수 있다. 하나의 제2 터치전극 라인(Y-TEL)의 양단은 2개의 제2 터치 라우팅 배선(Y-TRW)을 통해 2개의 제2 터치패드(Y-TP)와 전기적으로 연결될 수 있다.

- [0118] 더블 라우팅 구조를 갖고, 다수의 제1 및 제2 터치전극 라인(X-TEL, Y-TEL) 각각이 도 7과 같은 구조를 갖는 경우, 하나의 제1 터치전극 라인(X-TEL)에 포함된 다수의 제1 터치전극(X-TE) 중 최 외곽에 배치된 2개의 제1 터치전극(X-TE)은 2개의 제1 터치 라우팅 배선(X-TRW)을 통해 2개의 제1 터치패드(X-TP)와 전기적으로 연결될 수있다. 하나의 제2 터치전극 라인(Y-TEL)에 포함된 다수의 제2 터치전극(Y-TE) 중 최 외곽에 배치된 2개의 제2 터치전극(Y-TE)은 2개의 제2 터치 라우팅 배선(Y-TRW)을 통해 2개의 제2 터치패드(Y-TP)와 전기적으로 연결될수있다.

- [0119] 더블 라우팅 구조를 갖는 경우, 터치센서가 n(n은 2 이상의 자연수)개의 제1 터치전극 라인(X-TEL)과 m(m은 2 이상의 자연수)개의 제2 터치전극 라인(Y-TEL)을 포함한다면, 터치패드 부(TPA)는 2n개의 제1 터치패드(X-TP) 및 2m개의 제2 터치패드(Y-TP)를 포함하고, 터치 라우팅 배선 구조는 2n개의 제1 터치 라우팅 배선(X-TRW)과 2m 개의 제2 터치 라우팅 배선(Y-TRW)을 포함할 수 있다.

- [0120] 도 5를 참조하면, 본 발명의 실시예들에 따른 표시패널(DISP)에 포함되는 터치 센서 구성 요소들(터치전극 라인 들(X-TEL, Y-TEL), 터치 라우팅 배선들(X-TRW, Y-TRW) 및 터치패드들(X-TP, Y-TP))은 싱글 라우팅(Single Routing) 구조로 설계될 수 있다.

- [0121] 싱글 라우팅 구조는 2개의 경로(터치 라우팅 배선)를 통해 1곳(터치전극 라인)으로 신호를 공급하거나 2개의 경로(터치 라우팅 배선)를 통해 1곳(터치전극 라인)으로부터 신호를 검출할 수 있는 구조를 의미한다.

- [0122] 성글 라우팅 구조의 경우, 다수의 제1 터치전극 라인(X-TEL) 각각은 1개의 제1 터치 라우팅 배선(X-TRW)을 통해 신호 검출(또는 신호 공급)이 될 수 있다. 다수의 제2 터치전극 라인(Y-TEL) 각각은 1개의 제2 터치 라우팅 배선(Y-TRW)을 통해 신호 공급(또는 신호 검출)이 될 수 있다.

- [0123] 싱글 라우팅 구조를 갖고, 다수의 제1 및 제2 터치전극 라인(X-TEL, Y-TEL) 각각이 바 형상을 갖는 경우, 하나의 제1 터치전극 라인(X-TEL)의 양단 중 하나만이 1개의 제1 터치 라우팅 배선(X-TRW)을 통해 1개의 제1 터치패 드(X-TP)와 전기적으로 연결될 수 있다. 하나의 제2 터치전극 라인(Y-TEL)의 양단 중 하나만이 1개의 제2 터치 라우팅 배선(Y-TRW)을 통해 1개의 제2 터치패드(Y-TP)와 전기적으로 연결될 수 있다.

- [0124] 성글 라우팅 구조를 갖고, 다수의 제1 및 제2 터치전극 라인(X-TEL, Y-TEL) 각각이 도 7과 같은 구조를 갖는 경우, 하나의 제1 터치전극 라인(X-TEL)에 포함된 다수의 제1 터치전극(X-TE) 중 최 외곽에 배치된 2개의 제1 터치전극(X-TE) 중 하나만이 제1 터치 라우팅 배선(X-TRW)을 통해 제1 터치패드(X-TP)와 전기적으로 연결될 수 있다. 하나의 제2 터치전극 라인(Y-TEL)에 포함된 다수의 제2 터치전극(Y-TE) 중 최 외곽에 배치된 2개의 제2 터치전극(Y-TE) 중 하나만이 제2 터치 라우팅 배선(Y-TRW)을 통해 제2 터치패드(Y-TP)와 전기적으로 연결될 수 있다.

- [0125] 성글 라우팅 구조를 갖는 경우, 터치센서가 n(n은 2 이상의 자연수)개의 제1 터치전극 라인(X-TEL)과 m(m은 2 이상의 자연수)개의 제2 터치전극 라인(Y-TEL)을 포함한다면, 터치패드 부(TPA)는 n개의 제1 터치패드(X-TP) 및 m개의 제2 터치패드(Y-TP)를 포함하고, 터치 라우팅 배선 구조는 n개의 제1 터치 라우팅 배선(X-TRW)과 m개의 제2 터치 라우팅 배선(Y-TRW)을 포함할 수 있다.

- [0126] 도 6을 참조하면, 본 발명의 실시예들에 따른 표시패널(DISP)에 포함되는 터치 센서 구성 요소들(터치전극 라인 들(X-TEL, Y-TEL), 터치 라우팅 배선들(X-TRW, Y-TRW) 및 터치패드들(X-TP, Y-TP))의 일부는 싱글 라우팅 구조를 갖고, 나머지는 더블 라우팅 구조를 갖는 해프-싱글 라우팅(Half-Single Routing) 구조(또는 해프-더블 라우팅 구조라고도 함)로 설계될 수 있다.

- [0127] 도 6에 도시된 해프-싱글 라우팅 구조의 일 예로서, 다수의 제1 터치전극 라인(X-TEL) 각각은 1개의 제1 터치라 라우팅 배선(X-TRW)을 통해 신호 검출(또는 신호 공급)이 되고, 다수의 제2 터치전극 라인(Y-TEL) 각각은 2개의 제2 터치 라우팅 배선(Y-TRW)을 통해 신호 공급(또는 신호 검출)이 될 수 있다. 즉, 다수의 제1 터치전극 라인(X-TEL), 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제1 터치패드(X-TP)는 싱글 라우팅 구조를 갖고, 다수의 제2 터치전극 라인(Y-TEL), 다수의 제2 터치 라우팅 배선(Y-TRW) 및 다수의 제2 터치패드(Y-TP)는 더블 라우팅 구조를 가질 수 있다.

- [0128] 해프-싱글 라우팅 구조의 다른 예로서, 다수의 제2 터치전극 라인(Y-TEL) 각각은 1개의 제2 터치 라우팅 배선 (Y-TRW)을 통해 신호 검출(또는 신호 공급)이 되고, 다수의 제1 터치전극 라인(X-TEL) 각각은 2개의 제1 터치라우팅 배선(X-TRW)을 통해 신호 공급(또는 신호 검출)이 될 수 있다. 즉, 다수의 제2 터치전극 라인(Y-TEL), 다수의 제2 터치 라우팅 배선(Y-TRW) 및 다수의 제2 터치패드(Y-TP)는 싱글 라우팅 구조를 갖고, 다수의 제1 터치전극 라인(X-TEL), 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제1 터치패드(X-TP)는 더블 라우팅 구조를 가질 수 있다.

- [0129] 도 6에 도시된 해프-싱글 라우팅 구조를 갖는 경우, 터치센서가 n(n은 2 이상의 자연수)개의 제1 터치전극 라인 (X-TEL)과 m(m은 2 이상의 자연수)개의 제2 터치전극 라인(Y-TEL)을 포함한다면, 터치패드 부(TPA)는 n개의 제1 터치패드(X-TP) 및 2m개의 제2 터치패드(Y-TP)를 포함하고, 터치 라우팅 배선 구조는 n개의 제1 터치 라우팅 배선(X-TRW)과 2m개의 제2 터치 라우팅 배선(Y-TRW)을 포함할 수 있다.

- [0130] 다수의 제1 터치전극 라인(X-TEL)과 다수의 제2 터치전극 라인(Y-TEL)은 역할(기능)이 구분되는 터치센서 구성 들일 수 있다.

- [0131] 다수의 제1 터치전극 라인(X-TEL)은 터치센싱회로(TSC)에 의해 구동 신호가 인가되는 송신 전극 라인들(구동 전 극 라인들이라고도 함)이고, 다수의 제2 터치전극 라인(Y-TEL)은 터치센싱회로(TSC)에 의해 신호 검출이 되는 수신 전극 라인들(센싱 전극 라인들이라고도 함)일 수 있다.

- [0132] 이와 반대로, 다수의 제1 터치전극 라인(X-TEL)은 터치센싱회로(TSC)에 의해 신호 검출이 되는 수신 전극 라인 들(센싱 전극 라인들이라고도 함)이고, 다수의 제2 터치전극 라인(Y-TEL)은 터치센싱회로(TSC)에 의해 구동 신

호가 인가되는 송신 전극 라인들(구동 전극 라인들이라고도 함)일 수 있다.

- [0133] 이하에서는, 설명의 편의를 위하여, 도 4의 더블 라우팅(Double Routing) 구조의 경우, 다수의 제2 터치전극 라인(Y-TEL)은 수신 전극 라인들(센싱 전극 라인들)이고, 다수의 제1 터치전극 라인(X-TEL)은 송신 전극 라인들 (구동 전극 라인들)인 것으로 가정한다.

- [0134] 그렇지만, 도 4의 더블 라우팅 구조 하에서, 다수의 제2 터치전극 라인(Y-TEL)은 송신 전극 라인들(구동 전극라인들)이고, 다수의 제1 터치전극 라인(X-TEL)은 송신 전극 라인들(구동 전극라인들)일 수도 있다.

- [0135] 이하에서는, 설명의 편의를 위하여, 도 5의 싱글 라우팅(Single Routing) 구조 및 도 6의 해프-싱글 라우팅 (Half-Single Routing) 구조의 경우, 다수의 제2 터치전극 라인(Y-TEL)은 송신 전극 라인들(구동 전극 라인들)이고, 다수의 제1 터치전극 라인(X-TEL)은 수신 전극 라인들(센싱 전극 라인들)인 것으로 가정한다.

- [0136] 그렇지만, 도 5의 성글 라우팅(Single Routing) 구조 및 도 6의 해프-싱글 라우팅(Half-Single Routing) 구조 하에서, 다수의 제2 터치전극 라인(Y-TEL)은 수신 전극 라인들(센싱 전극 라인들)이고, 다수의 제1 터치전극 라인(X-TEL)은 송신 전극 라인들(구동 전극 라인들)일 수도 있다.

- [0137] 한편, 도 8에 도시된 바와 같이, 다수의 제1 터치 라우팅 배선(X-TRW) 각각은 봉지층(ENCAP) 상에서 배치되어 다수의 제1 터치전극 라인(X-TEL)과 연결되고, 봉지층(ENCAP)의 경사면을 따라 내려와서, 봉지층(ENCAP)이 없는 곳까지 연장되어 다수의 제1 터치패드(X-TP)와 전기적으로 연결될 수 있다. 다수의 제2 터치 라우팅 배선(Y-TRW) 각각은, 봉지층(ENCAP) 상에 배치되어 다수의 제2 터치전극 라인(Y-TEL)와 연결되고, 봉지층(ENCAP)의 경 사면을 따라 내려와서, 봉지층(ENCAP)이 없는 곳까지 연장되어 다수의 제2 터치패드(Y-TP)와 전기적으로 연결될 수 있다. 여기서, 봉지층(ENCAP)은 표시영역(AA) 내에 위치할 수 있으며, 경우에 따라서, 비-표시영역(NA)까지 확장될 수도 있다. 봉지층(ENCAP)이 없는 곳은 비-표시영역(NA)이며, 터치패드 부(TPA)는 비-표시영역(NA)에 존 재한다.

- [0138] 도 4 내지 도 6을 참조하면, 표시패널(DISP)은 표시영역(AA)으로부터 제2 방향(도면에서 볼 때, 오른쪽 방향)으로 외곽에 위치하는 제2 비-표시영역(NA2)을 포함할 수 있다.

- [0139] 표시영역(AA)에 배치된 다수의 제1 터치전극 라인(X-TEL) 및 다수의 제2 터치전극 라인(Y-TEL) 중 한 가지 이상 과 연결된 터치 라우팅 배선들(X-TRW, Y-TRW 중 한 가지 이상)은 제1 비-표시영역(NA1)에서의 터치패드 부(TP A)와 연결되기 위하여 제2 비-표시영역(NA2)을 지나가게 된다.

- [0140] 물론, 표시영역(AA)에 배치된 다수의 제1 터치전극 라인(X-TEL) 및 다수의 제2 터치전극 라인(Y-TEL) 중 한 가지 이상과 연결된 터치 라우팅 배선들(X-TRW, Y-TRW 중 한 가지 이상)은 제1 비-표시영역(NA1)에서의 터치패드 부(TPA)와 연결되기 위하여, 표시영역(AA)에서 제2 방향의 반대 방향에 있는 제3 비-표시영역(도면에서 볼 때 왼쪽 방향으로, 도 14의 NA3)을 지나갈 수도 있다. 다만, 아래에서는, 설명의 편의를 위하여, 제2 비-표시영역(NA2)과 제3 비-표시영역(도 14의 NA3) 중 제2 비-표시영역(NA2)만을 예로 든다.

- [0141] 도 4의 더블 라우팅 구조의 경우, 표시영역(AA)에 배치된 다수의 제1 터치전극 라인(X-TEL) 및 다수의 제2 터치전극 라인(Y-TEL)과 각각 연결된 다수의 제1 터치 라우팅 배선(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)이 제1 비-표시영역(NA1)에서의 터치패드 부(TPA)와 연결되기 위하여 제2 비-표시영역(NA2)을 지나간다.

- [0142] 도 5의 싱글 라우팅 구조 및 도 6의 해프-싱글 라우팅 구조의 경우, 표시영역(AA)에 배치된 다수의 제2 터치전 극 라인(Y-TEL)과 연결된 다수의 제2 터치 라우팅 배선(Y-TRW)이 제1 비-표시영역(NA1)에서의 터치패드 부(TP A)와 연결되기 위하여 제2 비-표시영역(NA2)을 지나간다.

- [0143] 후술하겠지만, 도 4 내지 도 6을 참조하면, 라우팅 구조와 무관하게, 제2 비-표시영역(NA2)에 많은 터치 라우팅 배선들이 배치될 수밖에 없고, 이는 네로우 베젤(Narrow Bezel)을 구현하는데 어려움을 주는 결정적인 요인이된다.

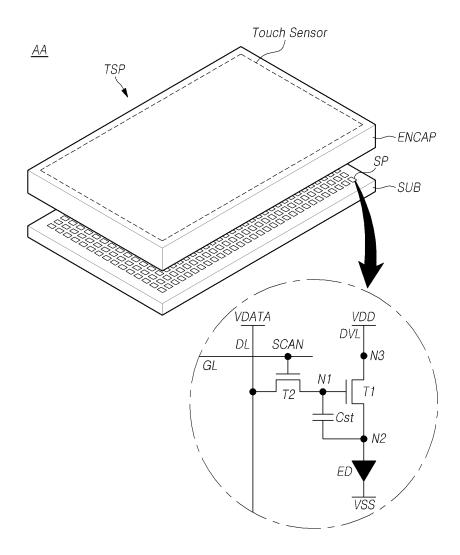

- [0144] 도 8은 본 발명의 실시예들에 따른 표시패널(DISP)의 부분적인 단면도이다. 단, 도 8은 터치센서 구조가 도 7과 같이 되어 있는 경우를 예로 든 것이다.

- [0145] 표시영역(AA) 내 각 서브픽셀(SP)에서의 구동 트랜지스터인 제1 트랜지스터(T1)은 기판(SUB) 상에 배치된다.

- [0146] 제1 트랜지스터(T1)는, 게이트 전극에 해당하는 제1 노드전극(NE1), 소스 전극 또는 드레인 전극에 해당하는 제 2 노드전극(NE2), 드레인 전극 또는 소스 전극에 해당하는 제3 노드전극(NE3) 및 반도체충(SEMI) 등을 포함한다.

- [0147] 제1 노드전극(NE1)과 반도체충(SEMI)은 게이트 절연막(GI)을 사이에 두고 중첩될 수 있다. 제2 노드전극(NE2)은 절연충(INS) 상에 형성되어 반도체충(SEMI)의 일 측과 접촉하고, 제3 노드전극(NE3)은 절연충(INS) 상에 형성되어 반도체충(SEMI)의 타 측과 접촉할 수 있다.

- [0148] 발광소자(ED)는 애노드 전극(또는 캐소드 전극)에 해당하는 픽셀전극(PE)과, 픽셀전극(PE) 상에 형성되는 발광 충(EL)과, 발광충(EL) 위에 형성된 캐소드 전극(또는 애노드 전극)에 해당하는 공통전극(CE) 등을 포함할 수 있다.

- [0149] 픽셀전극(PE)은 평탄화막(PLN)을 관통하는 화소 컨택홀을 통해 노출된 제1 트랜지스터(T1)의 제2 노드전극(NE 2)과 전기적으로 접속된다.

- [0150] 발광충(EL)은 뱅크(BANK)에 의해 마련된 발광영역의 픽셀전극(PE) 상에 형성된다. 발광충(EL)은 픽셀전극(PE) 상에 정공 관련충, 발광충, 전자 관련충 순으로 또는 역순으로 적충되어 형성된다. 공통전극(CE)은 발광충(EL)을 사이에 두고 픽셀전극(PE)과 대향하도록 형성된다.

- [0151] 봉지층(ENCAP)은 외부의 수분이나 산소에 취약한 발광소자(ED)로 외부의 수분이나 산소가 침투되는 것을 차단한다. 이러한 봉지층(ENCAP)은 하나의 층으로 되어 있을 수도 있지만, 도 8에 도시된 바와 같이 다수의 층(PAS1, PCL, PAS2)으로 되어 있을 수도 있다.

- [0152] 예를 들어, 봉지층(ENCAP)이 다수의 층(PAS1, PCL, PAS2)으로 이루어진 경우, 봉지층(ENCAP)은 하나 이상의 무기 봉지층(PAS1, PAS2)과 하나 이상의 유기 봉지층(PCL)을 포함할 수 있다. 구체적인 예로서, 봉지층(ENCAP)은 제1 무기 봉지층(PAS1), 유기 봉지층(PCL) 및 제2 무기 봉지층(PAS2)이 순서대로 적층된 구조로 되어 있을 있다.

- [0153] 여기서, 유기 봉지층(PCL)은, 적어도 하나의 유기 봉지층 또는 적어도 하나의 무기 봉지층을 더 포함할 수도 있다.

- [0154] 제1 무기 봉지층(PAS1)은 발광 소자(ED)와 가장 인접하도록 캐소드 전극에 해당하는 공통전극(CE)이 형성된 기 판(SUB) 상에 형성된다. 이러한 제1 무기 봉지층(PAS1)은, 일 예로, 질화실리콘(SiN<sub>x</sub>), 산화 실리콘(SiO<sub>x</sub>), 산화 질화실리콘(SiO<sub>N</sub>) 또는 산화 알루미늄(Al<sub>2</sub>O<sub>3</sub>) 등과 같은 저온 증착이 가능한 무기 절연 재질로 형성된다. 제1 무기 봉지층(PAS1)이 저온 분위기에서 증착 되므로, 제1 무기 봉지층(PAS1)은 증착 공정 시 고온 분위기에 취약한 유기물을 포함하는 발광층(EL)이 손상되는 것을 방지할 수 있다.

- [0155] 유기 봉지층(PCL)은 제1 무기 봉지층(PAS1)보다 작은 면적으로 형성될 수 있으며, 이 경우, 유기 봉지층(PCL)은 제1 무기 봉지층(PAS1)의 양끝단을 노출시키도록 형성될 수 있다. 유기 봉지층(PCL)은 유기발광표시장치인 터치 표시장치의 휘어짐에 따른 각 층들 간의 응력을 완화시키는 완충 역할을 하며, 평탄화 성능을 강화하는 역할을 할 수 있다. 유기 봉지층(PCL)은, 일 예로, 아크릴 수지, 에폭시 수지, 폴리이미드, 폴리에틸렌 또는 실리콘옥 시카본(SiOC)과 같은 유기 절연 재질로 형성될 수 있다. 일 예로, 유기 봉지층(PCL)이 잉크젯 방식을 통해 형성될 수도 있다.

- [0156] 전술한 바와 같이, 표시패널(DISP)은 댐 영역(DA)을 포함할 수 있다.

- [0157] 댐 영역(DA)은 표시영역(AA)과 비-표시영역(NA)의 경계지점에 존재하거나, 경계지점의 근방에 존재할 수 있다. 예를 들어, 댐 영역(DA)은 외곽에서 안쪽으로 들어가다가 갑자기 높아지는 지점의 주변 영역일 수 있다. 또는, 댐 영역(DA)은 봉지층의 경사면을 따라 내려오다가 봉지층의 경사가 갑자기 완만해지거나 다시 높아지는 방향으로 변하는 지점의 주변 영역을 의미할 수도 있다.

- [0158] 도 8에 도시된 바와 같이, 댐 영역(DA)에 위치하는 하나 이상의 댐(DAM)은 터치패드 부(TPA)와 표시영역(AA) 사이에 배치될 수 있다. 하나 이상의 댐(DAM)은 뱅크(BANK)와 동일 물질을 포함하는 댐 형성 패턴(DFP) 등으로 이루어질 수 있다.

- [0159] 댐 영역(DA)은 비-표시영역(NA)에만 위치할 수도 있고, 비-표시영역(NA)에 대부분이 존재하지만 일부는 표시영역(AA)에 걸쳐있을 수도 있다.

- [0160] 댐 영역(DA)에는 하나 또는 둘 이상의 댐(DAM)이 형성될 수 있다. 예를 들어, 도 8에 도시된 바와 같이, 댐 영역(DA)에는 2개의 댐(DAM1, DAM2)이 존재할 수 있다. 2개의 댐(DAM1, DAM2) 중에서 표시영역(AA)과 더 가까운 댐(DAM1)을 1차 댐(DAM1)이라고 하고, 터치패드 부(TPA)와 상대적으로 더 가깝에 위치하는 댐(DAM2)을 2차 댐

(DAM2)이라고 한다.

- [0161] 댐 영역(DA)에 배치되는 하나 이상의 댐(DAM)은 액상 형태의 유기 봉지층(PCL)이 표시영역(AA)에 적하 될 때, 액상 형태의 유기 봉지층(PCL)이 비-표시영역(NA)의 방향으로 무너져 터치패드 부(TPA) 등을 침범하는 것을 방지할 수 있다.

- [0162] 이러한 효과는, 도 8에 도시된 바와 같이, 2개 이상의 댐(DAM1, DAM2)이 형성된 경우, 더욱 커질 수 있다.

- [0163] 1차 댐(DAM1) 및/또는 2차 댐(DAM2)은 단층 또는 다층 구조로 형성될 수 있다.

- [0164] 1차 댐(DAM1) 및/또는 2차 댐(DAM2)은 기본적으로 댐 형성 패턴(DFP)으로 만들어질 수 있다. 댐 형성 패턴(DFP)은 터치패드 부(TPA)에 배치된 터치패드들(X-TP, Y-TP)보다 높은 높이를 가질 수 있다.

- [0165] 댐 형성 패턴(DFP)은 표시영역(AA)에서 서브픽셀들(SP)을 분리하기 위한 뱅크(BANK)와 동일한 물질로 형성될 수 있다. 경우에 따라서, 댐 형성 패턴(DFP)은 층간 간격을 유지하기 위한 스페이서 등과 동일한 물질로 형성될 수 있다. 이러한 경우, 댐 형성 패턴(DFP)은 뱅크(BANK) 또는 스페이서 등과 동시에 형성될 수 있고, 이에 따라, 마스크 추가 공정 및 비용 상승 없이 댐 구조를 형성할 수 있다.

- [0166] 도 8을 참조하면, 1차 댐(DAM1) 및/또는 2차 댐(DAM2)은 제1 무기 봉지층(PAS1) 및/또는 제2 무기 봉지층 (PAS2)이 댐 형성 패턴(DFP) 상에 적층 된 다층 구조로 되어 있을 수 있다.

- [0167] 유기물을 포함하는 유기 봉지층(PCL)은 가장 안쪽에 있는 1차 댐(DAM1)의 내 측면에만 위치할 수 있다. 이와 다르게, 유기물을 포함하는 유기 봉지층(PCL)은 1차 댐(DAM1) 및 2차 댐(DAM2) 중 적어도 1차 댐(DAM1)의 상부에 위치할 수 있다.

- [0168] 제2 무기 봉지층(PAS2)은 유기 봉지층(PCL)이 형성된 기판(SUB) 상에 유기 봉지층(PCL) 및 제1 무기 봉지층 (PAS1) 각각의 상부면 및 측면을 덮도록 형성될 수 있다. 제2 무기 봉지층(PAS2)은 외부의 수분이나 산소가 제1 무기 봉지층(PAS1) 및 유기 봉지층(PCL)으로 침투하는 것을 최소화하거나 차단한다. 이러한 제2 무기 봉지층 (PAS2)은, 일 예로, 질화실리콘(SiN<sub>x</sub>), 산화 실리콘(SiO<sub>x</sub>), 산화질화실리콘(SiO<sub>N</sub>) 또는 산화 알루미늄(Al<sub>2</sub>O<sub>3</sub>) 등 과 같은 무기 절연 재질로 형성된다.

- [0169] 봉지층(ENCAP) 상에는 터치 버퍼막(T-BUF)이 배치될 수 있다.

- [0170] 제1 및 제2 터치전극들(X-TE, Y-TE), 제1 및 제2 브릿지 패턴(X-CL, Y-CL)은 터치 버퍼막(T-BUF) 상에 위치할 수 있다.

- [0171] 제1 및 제2 터치 라우팅 배선들(X-TRW, Y-TRW) 각각의 전체 또는 일부도 터치 버퍼막(T-BUF) 상에 위치할 수 있다.

- [0172] 터치 버퍼막(T-BUF)은 터치센서와 공통전극(CE) 사이에 위치하는데, 터치센서와 발광 소자(ED)의 공통전극(CE) 사이의 이격 거리가 미리 정해진 최소 이격 거리(예: 5½m)를 유지하도록 설계될 수 있다. 이에 따라, 터치센서와 공통전극(CE) 간의 기생 캐패시턴스를 줄여주거나 방지해줄 수 있고, 이를 통해, 기생 캐패시턴스에 의한 터치 감도 저하를 방지해줄 수 있다.

- [0173] 터치 버퍼막(T-BUF) 없이, 제1 및 제2 터치전극들(X-TE, Y-TE), 제1 및 제2 브릿지 패턴(X-CL, Y-CL)이 봉지층 (ENCAP) 상에 바로 배치될 수도 있다.

- [0174] 터치 버퍼막(T-BUF)은, 터치 버퍼막(T-BUF) 상에 배치되는 터치센서 메탈의 제조 공정 시 이용되는 약액(현상액 또는 식각액 등등) 또는 외부로부터의 수분 등이 유기물을 포함하는 발광층(EL)으로 침투되는 것을 차단할 수 있다. 이에 따라, 터치 버퍼막(T-BUF)은 약액 또는 수분에 취약한 발광층(EL)의 손상을 방지할 수 있다.

- [0175] 터치 버퍼막(T-BUF)은 고온에 취약한 유기물을 포함하는 발광층(EL)의 손상을 방지하기 위해 일정 온도(예: 100 도(℃)) 이하의 저온에서 형성 가능하고 1~3의 저유전율을 가지는 유기 절연 재질로 형성된다. 예를 들어, 터치 버퍼막(T-BUF)은 아크릴 계열, 에폭시 계열 또는 실록산(Siloxan) 계열의 재질로 형성될 수 있다. 유기 절연 재질로 평탄화 성능을 가지는 터치 버퍼막(T-BUF)은 유기발광표시장치의 휘어짐에 따른 봉지층(ENCAP) 내의 각 봉지층(PAS1, PCL, PAS2)의 손상 및 터치 버퍼막(T-BUF) 상에 형성되는 터치 센서 메탈의 깨짐 현상을 방지할 수 있다.

- [0176] 뮤추얼 캐패시턴스 기반의 터치 센서 구조에 따르면, 터치 버퍼막(T-BUF) 상에 제1 터치전극 라인(X-TEL) 및 제 2 터치전극 라인(Y-TEL)이 배치되며, 제1 터치전극 라인(X-TEL) 및 제2 터치전극 라인(Y-TEL)은 교차되게 배치

될 수 있다.

- [0177] 제2 터치전극 라인(Y-TEL)은, 다수의 제2 터치전극(Y-TE)과, 다수의 제2 터치전극(Y-TE) 사이를 전기적으로 연결해주는 다수의 제2 브릿지 패턴(Y-CL)을 포함할 수 있다. 도 8에 도시된 바와 같이, 다수의 제2 터치전극(Y-TE)과 다수의 제2 브릿지 패턴(Y-CL)은 터치 절연막(IND)을 사이에 두고 서로 다른 층에 위치할 수 있다.

- [0178] 도 7과 도 8을 함께 참조하면, 다수의 제2 터치전극(Y-TE)은 y축 방향(도 7의 제1 방향)을 따라 일정한 간격으로 이격될 수 있다. 이러한 다수의 제2 터치전극(Y-TE) 각각은 제2 브릿지 패턴(Y-CL)을 통해 y축 방향으로 인접한 다른 제2 터치전극(Y-TE)과 전기적으로 연결될 수 있다.

- [0179] 제2 브릿지 패턴(Y-CL)은 터치 버퍼막(T-BUF) 상에 형성되며 터치 절연막(IND)을 관통하는 터치 컨택홀을 통해 노출되어 y축 방향으로 인접한 2개의 제2 터치전극(Y-TE)과 전기적으로 접속될 수 있다.

- [0180] 제2 브릿지 패턴(Y-CL)은 뱅크(BANK)와 중첩되도록 배치될 수 있다. 이에 따라, 제2 브릿지 패턴(Y-CL)에 의해 개구율이 저하되는 것을 방지할 수 있다.

- [0181] 도 7과 도 8을 함께 참조하면, 제1 터치전극 라인(X-TEL)은, 다수의 제1 터치전극(X-TE)과, 다수의 제1 터치전 극(X-TE) 사이를 전기적으로 연결해주는 다수의 제1 브릿지 패턴(X-CL)을 포함할 수 있다. 다수의 제1 터치전극 (X-TE)과 다수의 제1 브릿지 패턴(X-CL)은 터치 절연막(IND)을 사이에 두고 서로 다른 층에 위치할 수 있지만, 다수의 제1 브릿지 패턴(X-CL)과 다수의 제1 터치전극(X-TE)은 일체로 되어 동일한 층에 위치할 수도 있다.

- [0182] 도 7과 도 8을 함께 참조하면, 다수의 제1 터치전극(X-TE)은 터치 절연막(ILD) 상에서 x축 방향을 따라 일정한 간격으로 이격될 수 있다. 이러한 다수의 제1 터치전극(X-TE) 각각은 제1 브릿지 패턴(X-CL)을 통해 x축 방향으로 인접한 다른 제1 터치전극(X-TE)과 전기적으로 연결될 수 있다.

- [0183] 제1 브릿지 패턴(X-CL)은 제1 터치전극(X-TE)과 동일 평면 상에 배치되어 별도의 컨택홀 없이 x축 방향으로 인접한 2개의 제1 터치전극(X-TE)과 전기적으로 접속되거나, x축 방향으로 인접한 2개의 제1 터치전극(X-TE)과 일체로 되어 있을 수 있다.

- [0184] 제1 브릿지 패턴(X-CL)은 뱅크(BANK)와 중첩되도록 배치될 수 있다. 이에 따라, 제1 브릿지 패턴(X-CL)에 의해 개구율이 저하되는 것을 방지할 수 있다.

- [0185] 도 8을 참조하면, 제2 터치전극 라인(Y-TEL)은 제2 터치 라우팅 배선(Y-TRW)을 통해 제1 비-표시영역(NA1) 내 터치패드 부(TPA)에 존재하는 제2 터치패드(Y-TP)와 전기적으로 연결될 수 있다. 제2 터치패드(Y-TP)는 터치구 동회로(TDC)와 전기적으로 연결될 수 있다.

- [0186] 이러한 구조와 마찬가지로, 제1 터치전극 라인(X-TEL)은 제1 터치 라우팅 배선(X-TRW)을 통해 제1 비-표시영역 (NA1) 내 터치패드 부(TPA)에 존재하는 제1 터치패드(X-TP)와 전기적으로 연결될 수 있다. 제1 터치패드(X-TP)는 터치구동회로(TDC)와 전기적으로 연결될 수 있다.

- [0187] 제1 터치패드(X-TP) 및 제2 터치패드(Y-TP)를 덮는 패드 커버 전극이 더 배치될 수도 있다.

- [0188] 제1 터치패드(X-TP)는 제1 터치 라우팅 배선(X-TRW)과 별도로 형성될 수도 있고, 제1 터치 라우팅 배선(X-TRW)이 연장되어 형성될 수 도 있다. 제2 터치패드(Y-TP)은 제2 터치 라우팅 배선(Y-TRW)과 별도로 형성될 수도 있고, 제2 터치 라우팅 배선(Y-TRW)이 연장되어 형성될 수 도 있다.

- [0189] 제1 터치패드(X-TP)가 제1 터치 라우팅 배선(X-TRW)이 연장되어 형성되고, 제2 터치패드(Y-TP)가 제2 터치 라우팅 배선(Y-TRW)이 연장되어 형성된 경우, 제1 터치패드(X-TP), 제1 터치 라우팅 배선(X-TRW), 제2 터치패드(Y-TP) 및 제2 터치 라우팅 배선(Y-TRW)은 동일한 제1 도전 물질로 구성될 수 있다. 여기서, 제1 도전 물질은, 일 예로, A1, Ti, Cu, Mo와 같은 내식성 및 내산성이 강하고 전도성이 좋은 금속을 이용하여 단층 또는 다층 구조로 형성될 수 있다.

- [0190] 예를 들어, 제1 도전 물질로 된 제1 터치패드(X-TP), 제1 터치 라우팅 배선(X-TRW), 제2 터치패드(Y-TP) 및 제2 터치 라우팅 배선(Y-TRW)은 Ti/Al/Ti 또는 Mo/Al/Mo와 같이 적충된 3층 구조로 형성될 수 있다.

- [0191] 제1 터치패드(X-TP) 및 제2 터치패드(Y-TP)를 덮을 수 있는 패드 커버 전극은 제1 및 제2 터치전극(X-TE, Y-TE)과 동일 재질로 제2 도전 물질로 구성될 수 있다. 여기서, 제2 도전 물질은 내식성 및 내산성이 강한 ITO 또는 IZO와 같은 투명 도전물질로 형성될 수 있다. 이러한 패드 커버 전극은 터치 버퍼막(T-BUF)에 의해 노출되도록 형성됨으로써 터치구동회로(TDC)와 본딩되거나 또는 터치구동회로(TDC)가 실장된 회로 필름과 본딩될 수 있

다.

- [0192] 여기서, 터치 버퍼막(T-BUF)은 터치 센서 메탈을 덮도록 형성되어 터치 센서 메탈이 외부의 수분 등에 의해 부식되는 것을 방지할 수 있다. 일 예로, 터치 버퍼막(T-BUF)은 유기 절연 재질로 형성되거나, 원편광판 또는 에폭시 또는 아크릴 재질의 필름 형태로 형성될 수 있다. 이러한 터치 보호막(T-BUF)이 봉지층(ENCAP) 상에 없을 수도 있다. 즉, 터치 버퍼막(T-BUF)은 필수적인 구성이 아닐 수도 있다.

- [0193] 제2 터치 라우팅 배선(Y-TRW)은, 터치 라우팅 배선 컨택홀을 통해 제2 터치전극(Y-TE)과 전기적으로 연결되거나, 제2 터치전극(Y-TE)과 일체로 되어 있을 수 있다.

- [0194] 이러한 제2 터치 라우팅 배선(Y-TRW)은, 비-표시영역(NA)까지 신장되어 봉지층(ENCAP)의 경사면을 따라 내려와, 하나 이상의 댐(DAM)을 지나서, 제1 비-표시영역(NA1) 내 터치패드 부(TPA)에 존재하는 제2 터치패드(Y-TP)와 전기적으로 연결될 수 있다. 이에 따라, 제2 터치 라우팅 배선(Y-TRW)은 제2 터치패드(Y-TP)를 통해 터치구동회로(TDC)와 전기적으로 연결될 수 있다.

- [0195] 제2 터치 라우팅 배선(Y-TRW)은, 제2 터치전극(Y-TE)에서의 터치 센싱 신호를 터치구동회로(TDC)로 전달해주거나, 터치구동회로(TDC)로부터 터치 구동 신호를 공급받아 제2 터치전극(Y-TE)에 전달해줄 수 있다.

- [0196] 제1 터치 라우팅 배선(X-TRW)은, 터치 라우팅 배선 컨택홀을 통해 제1 터치전극(X-TE)과 전기적으로 연결되거나, 제1 터치전극(X-TE)과 일체로 되어 있을 수 있다.

- [0197] 이러한 제1 터치 라우팅 배선(X-TRW)은 비-표시영역(NA)까지 신장되어 봉지층(ENCAP)의 경사면을 따라 내려와, 하나 이상의 댐(DAM)을 지나서, 제1 비-표시영역(NA1) 내 터치패드 부(TPA)에 존재하는 제1 터치패드(Y-TP)와 전기적으로 연결될 수 있다. 이에 따라, 제1 터치 라우팅 배선(X-TRW)은 제1 터치패드(X-TP)를 통해 터치구동회로(TDC)와 전기적으로 연결될 수 있다.

- [0198] 제1 터치 라우팅 배선(X-TRW)은, 터치구동회로(TDC)로부터 터치 구동 신호를 공급받아 제1 터치전극(X-TE)에 전달할 수 있고, 제1 터치전극(X-TE)에서의 터치 센싱 신호를 터치구동회로(TDC)로 전달해줄 수도 있다.

- [0199] 제1 터치 라우팅 배선(X-TRW) 및 제2 터치 라우팅 배선(Y-TRW)의 배치는 패널 설계사항에 따라 다양하게 변경 가능하다.

- [0200] 제1 터치전극(X-TE) 및 제2 터치전극(Y-TE) 상에 터치 보호막(PAC)이 배치될 수 있다. 이러한 터치 보호막(PAC)은 하나 이상의 댐(DAM)의 전 또는 후까지 확장되어 제1 터치 라우팅 배선(X-TRW) 및 제2 터치 라우팅 배선(Y-TRW) 상에도 배치될 수 있다.

- [0201] 한편, 도 8의 단면도는 개념적으로 구조를 도시한 것으로서, 보는 방향이나 위치 등에 따라 각 패턴들(각종 충들이나 각종 전극들)의 위치, 두께, 또는 폭이 달라질 수도 있고, 각종 패턴들의 연결 구조도 변경될 수 있으며, 도시된 여러 충들 이외에도 추가적인 충이 더 존재할 수도 있고, 도시된 여러 충들 중 일부는 생략되거나 통합되어 있을 수도 있다. 예를 들어, 뱅크(BANK)의 폭은 도면에 비해 좁을 수도 있고, 댐(DAM)의 높이도 도면보다 낮거나 높을 수 있다.

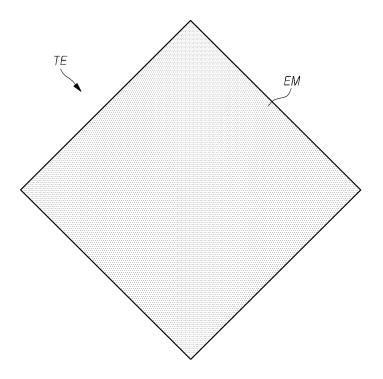

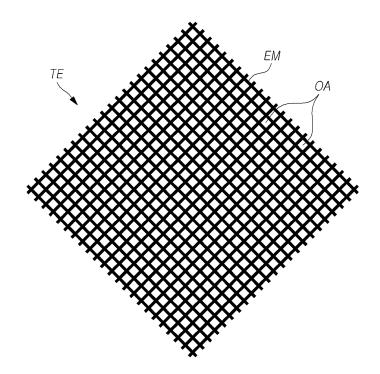

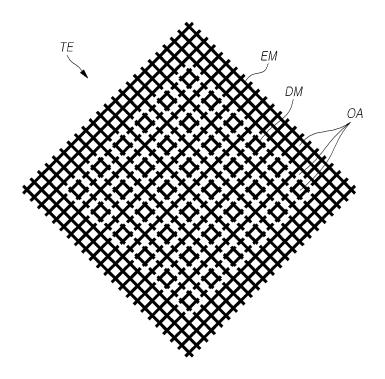

- [0202] 아래에서는, 제1 터치전극 라인(X-TEL) 및 제2 터치전극 라인(Y-TEL) 각각이 도 7과 같은 구조를 갖는 경우, 제 1 터치전극 라인(X-TEL)에 포함되는 제1 터치전극(X-TE)과, 제2 터치전극 라인(Y-TEL)에 포함되는 제2 터치전극 (Y-TE)에 대한 모양 등의 구조를 예시적으로 설명한다. 도 9 내지 도 11에서는, 제1 터치전극(X-TE) 및 제2 터치전극(Y-TE)을 터치전극(TE)이라고 기재한다.

- [0203] 도 9 내지 도 11은 본 발명의 실시예들에 따른 표시패널(DISP)에 배치된 터치전극을 예시적으로 나타낸 도면이다.

- [0204] 도 9를 참조하면, 하나의 터치전극(TE)은 개구부(오픈 영역)가 없는 판 형상의 전극 메탈(EM)일 수 있다. 이 경우, 터치전극(TE)은 투명전극일 수 있다. 즉, 터치전극(TE)은 아래에 배치된 다수의 서브픽셀(SP)에서 발광된 빛들이 위로 투과될 수 있도록 투명전극 물질로 된 전극 메탈(EM)일 수 있다.

- [0205] 도 10을 참조하면, 하나의 터치전극(TE)은 다수의 오픈 영역(OA)을 갖는 메쉬(Mesh) 타입일 수 있다. 즉, 하나의 터치전극(TE)은 다수의 오픈 영역(OA)을 갖도록, 메쉬 타입으로 패터닝 된 전극 메탈(EM)일 수 있다. 여기서, 전극 메탈(EM)은 터치센서메탈 중 하나이다.

- [0206] 하나의 터치전극(TE)에 존재하는 다수의 오픈 영역(OA) 각각은, 하나 이상의 서브픽셀(SP)의 발광 영역과 대응

될 수 있다. 즉, 다수의 오픈 영역(OA)은 아래에 배치된 다수의 서브픽셀(SP)에서 발광된 빛들이 위로 지나가는 경로가 된다.

- [0207] 터치전극(TE)에서 다수의 오픈 영역(OA)이 아닌 실제 전극 부분(즉, 전극 메탈(EM))은 뱅크(BANK) 상에 위치할수 있다.

- [0208] 제1 터치전극 라인(X-TEL) 및 제2 터치전극 라인(Y-TEL) 각각이 바 타입인 경우, 제1 터치전극 라인(X-TEL) 및 제2 터치전극 라인(Y-TEL) 각각은 다수의 오픈 영역(OA)을 갖는 메쉬 타입일 수 있다. 다수의 오픈 영역(OA) 각 각 하나 이상의 서브픽셀(SP)의 발광 영역과 대응될 수 있다.

- [0209] 여러 개의 터치전극(TE)을 형성하는 방법으로서, 여러 개의 터치전극(TE)을 형성하기 위한 영역에 전극 메탈 (EM)을 메쉬 타입으로 넓게 형성한 이후, 터치전극(TE) 간의 경계 라인들을 따라 전극 메(EM)탈을 정해진 패턴으로 커팅하여 전기적으로 분리된 전극 메탈(EM)을 형성한다. 전기적으로 분리된 전극 메탈(EM)이 여러 개의 터치전극(Y-TE)이 된다.

- [0210] 터치전극(Y-TE)의 외곽 모양은, 도 9 내지 도 11에 도시된 바와 같이, 다이아몬드 형상, 마름모 등의 사각형일 수도 있고, 삼각형, 오각형, 또는 육각형 등의 다양한 모양일 수 있다.

- [0211] 도 11을 참조하면, 도 10의 메쉬 타입의 터치전극(TE)이 차지하는 영역 내에는, 메쉬 타입의 전극 메탈(EM)이 끊어져 있는 하나 이상의 더미 메탈(DM)이 존재할 수 있다.

- [0212] 전국 메탈(EM)은 실질적인 터치전극(TE)에 해당하는 부분으로서 터치구동신호가 인가되거나 터치 센싱 신호가 감지되는 부분이지만, 더미 메탈(DM)은 터치전극(TE)의 영역 내에 존재하기는 하지만 터치 구동 신호가 인가되지 않고 터치 센싱 신호도 감지되지 않는 부분이다. 즉, 더미 메탈(DM)은 전기적으로 플로팅(Floating) 된 메탈일 수 있다.

- [0213] 따라서, 전극 메탈(EM)은 터치구동회로(TDC)와 전기적으로 연결될 수 있지만, 더미 메탈(DM)은 터치구동회로 (TDC)와 전기적으로 연결되지 않는다.

- [0214] 모든 터치전극(TE) 각각의 영역 안에는, 하나 이상의 더미 메탈(DM)이 전극 메탈(EM)과 끊어진 상태로 존재할 수 있다. 이와 다르게, 모든 터치전극(TE) 중 일부의 터치전극(TE)의 영역 안에만, 하나 이상의 더미 메탈(DM)이 전극 메탈(EM)과 끊어진 상태로 존재할 수도 있다. 즉, 일부의 터치전극(TE)의 영역 내에는 더미 메탈(DM)이 존재하지 않을 수도 있다.

- [0215] 한편, 더미 메탈(DM)의 역할과 관련하여, 도 10에 도시된 바와 같이, 터치전극(TE)의 영역 내에 하나 이상의 더미 메탈(DM)이 존재하지 않고 전극 메탈(EM)만 메쉬 타입으로 존재하는 경우, 화면 상에 전극 메탈(EM)의 윤곽이 보이는 시인성 이슈가 발생할 수 있다.

- [0216] 이에 비해, 도 11에 도시된 바와 같이, 터치전극(TE)의 영역 내에 하나 이상의 더미 메탈(DM)이 존재하는 경우, 화면 상에 전극 메탈(EM)의 윤곽이 보이는 시인성 이슈가 방지될 수 있다.

- [0217] 또한, 각 터치전극(TE) 별로, 더미 메탈(DM)의 존재 유무 또는 개수(더미 메탈 비율)을 조절함으로써, 각 터치전극(TE) 별로 뮤추얼-캐패시턴스의 크기에 영향을 끼치는 유효 전극 면적을 조절할 수 있다. 이를 통해, 제1 터치전극(X-TE)과 제2 터치전극(Y-TE) 간의 뮤추얼-캐패시턴스의 크기를 조절하여 터치 감도를 향상시킬 수도 있다.

- [0218] 한편, 1개의 터치전극(TE)의 영역 내 형성된 전극 메탈(EM)에서 일부 지점들을 커팅함으로써, 커팅된 전극 메탈(EM)이 더미 메탈(DM)로 형성될 수 있다. 즉, 전극 메탈(EM)과 더미 메탈(DM)은 동일한 층에 형성된 동일한 물질일 수 있다.

- [0219] 도 12 및 도 13은 본 발명의 실시예들에 따른 표시패널(DISP)에 컬러필터가 포함된 경우의 단면 구조를 예시적으로 나타낸 도면들이다. 단, 도 12 및 도 13에서, 터치전극(TE)은 제1 터치전극(X-TE) 및 제2 터치전극(Y-TE)을 의미한다.

- [0220] 도 12 및 도 13을 참조하면, 터치패널(TSP)이 표시패널(DISP)에 내장되고, 표시패널(DISP)이 유기발광표시패널 로 구현되는 경우, 다수의 제1 터치전극(X-TE), 다수의 제2 터치전극(Y-TE), 다수의 제1 브릿지 패턴(X-CL) 및 다수의 제2 브릿지 패턴(Y-CL) 등의 터치 센서는 표시패널(DISP) 내 봉지층(ENCAP) 상에 위치할 수 있다.

- [0221] 전술한 바와 같이, 봉지층(ENCAP) 상에 터치센서를 형성함으로써, 디스플레이 성능 및 디스플레이 관련 층 형성

- 에 큰 영향을 주지 않고, 터치센서를 형성할 수 있다.

- [0222] 한편, 도 12 및 도 13을 참조하면, 참조하면, 봉지충(ENCAP) 아래에 발광소자(ED)의 캐소드 전극일 수 있는 공 통전극(CE)이 위치할 수 있다.

- [0223] 봉지층(ENCAP)의 두께(T)는, 일 예로, 5 마이크로 미터 이상일 수 있다. 봉지층(ENCAP)의 두께를 5 마이크로 미터 이상으로 설계함으로써, 공통전극(CE)와 터치전극들(TE) 사이에 형성되는 기생 캐패시턴스를 줄여줄 수 있다. 이에 따라, 기생 캐패시턴스에 의한 터치 감도 저하를 방지할 수 있다.

- [0224] 각 터치전극(TE)에 형성된 다수의 오픈 영역(OA) 각각은, 수직 방향으로 보면, 하나 이상의 서브픽셀의 발광 영역과 대응될 수 있다. 이에 따라, 표시패널(DISP)의 발광 효율이 향상될 수 있다.

- [0225] 도 12 및 도 13에 도시된 바와 같이, 표시패널(DISP)에는 컬러필터들(CF)이 배치될 수도 있으며, 블랙 매트릭스 (BM)가 더 배치될 수 있다. 블랙 매트릭스(BM)는 컬러필터(CF)와 다른 것일 수도 있다. 이와 다르게, 블랙 매트릭스(BM)는 2가지 이상의 다른 색상의 컬러필터(CF)가 중첩되어 형성된 것일 수도 있다. 컬러필터들(CF)이 있는 층을 색변환층이라고도 한다.

- [0226] 블랙 매트릭스(BM)의 위치는 터치전극(TE)의 전극 메탈(EM)의 위치와 대응될 수 있다. 컬러필터(CF)의 위치는 터치전극(TE)의 오픈 영역(OA)의 위치와 대응될 수 있다. 따라서, 표시패널(DISP)의 발광 성능이 향상될 수 있다.

- [0227] 도 12를 참조하면, 다수의 컬러필터(CF)와 블랙매트릭스(BM)을 포함하는 색 변환층은 다수의 터치전극들(TE) 상에 위치할 수 있다. 다수의 컬러필터(CF)와 블랙매트릭스(BM)을 포함하는 색 변환층은 다수의 터치전극(TE) 상에 배치된 오버코트 층(OC) 상에 위치할 수 있다. 여기서, 오버코트 층(OC)은 터치 보호막(PAC)과 동일한 층일 수도 있고 다른 층일 수도 있다.

- [0228] 도 13을 참조하면, 다수의 컬러필터(CF)와 블랙매트릭스(BM)을 포함하는 색 변환층은 다수의 터치전극들(TE)의 하부에 위치할 수 있다. 다수의 컬러필터(CF)와 블랙매트릭스(BM)을 포함하는 색 변환층 상에 오버코트 층(OC)이 배치되고, 오버코트 층(OC)상에 다수의 터치전극(TE)이 위치할 수 있다.

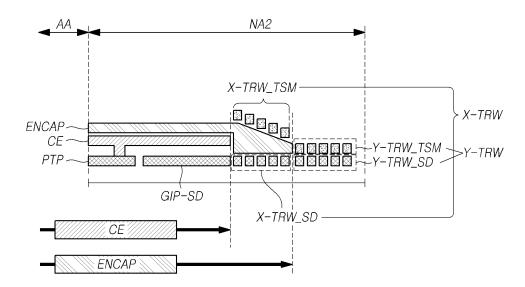

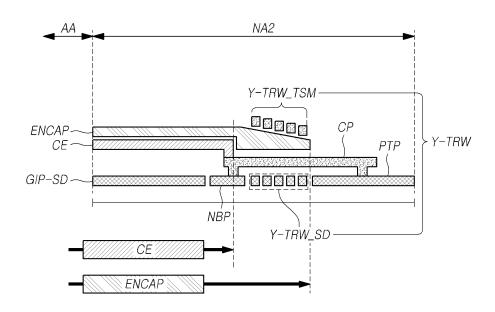

- [0229] 도 14는 본 발명의 실시예들에 따른 표시패널(DISP)의 표시영역(AA)과 비-표시영역들(NA1, NA2, NA3, NA4)을 나타낸 도면이다.

- [0230] 도 14를 참조하면, 본 발명의 실시예들에 따른 표시패널(DISP)은 영상이 표시되는 표시영역(AA)과, 표시영역(AA)의 외곽영역들로서 영상이 표시되지 않는 비-표시영역(NA)을 포함할 수 있다.

- [0231] 예를 들어, 비-표시영역(NA)은 제1 비-표시영역(NA1), 제2 비-표시영역(NA2), 제3 비-표시영역(NA3) 및 제4 비-표시영역(NA4) 등으로 분할될 수 있다.

- [0232] 제1 비-표시영역(NA1), 제2 비-표시영역(NA2), 제3 비-표시영역(NA3) 및 제4 비-표시영역(NA4)은, 설명의 편의를 위하여 비-표시영역(NA)이 분할된 영역들일 뿐, 서로 정확한 경계를 갖거나 서로 분리되지 않을 수 있다.

- [0233] 제1 비-표시영역(NA1)은 표시영역(AA)으로부터 제1 방향(도면에서 하측 방향)으로 외곽에 위치한다. 즉, 제1 비-표시영역(NA1)은 전체 비-표시영역(NA) 중에서 표시영역(AA)의 하측에 위치하는 영역이다.

- [0234] 제2 비-표시영역(NA2)은 표시영역(AA)으로부터 제2 방향(도면에서 우측 방향)으로 외곽에 위치한다. 즉, 제2 비-표시영역(NA2)은 전체 비-표시영역(NA) 중에서 표시영역(AA)의 우측에 위치하는 영역이다.

- [0235] 제3 비-표시영역(NA3)은 표시영역(AA)으로부터 제2 방향의 반대 방향(도면에서 좌측 방향)으로 외곽에 위치한다. 즉, 제3 비-표시영역(NA3)은 전체 비-표시영역(NA) 중에서 표시영역(AA)의 좌측에 위치하는 영역이다.

- [0236] 제4 비-표시영역(NA4)은 표시영역(AA)으로부터 제1 방향의 반대 방향(도면에서 상측 방향)으로 외곽에 위치한다. 즉, 제4 비-표시영역(NA4)은 전체 비-표시영역(NA) 중에서 표시영역(AA)의 상측에 위치하는 영역이다.

- [0237] 제1 내지 제4 비-표시영역(NA1, NA2, NA3, NA4) 각각에서의 배선 배치 구조를 예를 들어 설명한다. 아래의 설명은 도 4 내지 도 6이 참조된다.

- [0238] 제4 비-표시영역(NA4)에는, 다수의 제2 터치전극 라인(Y-TEL)과 연결된 다수의 제2 터치 라우팅 배선(Y-TRW)이

지나갈 수 있다.

- [0239] 제2 비-표시영역(NA2)에는, 제4 비-표시영역(NA4)을 지나친 다수의 제2 터치 라우팅 배선(Y-TRW)이 지나갈 수 있다(도 4 내지 도 6 참조). 제2 비-표시영역(NA2)에는 다수의 제1 터치전극 라인(X-TEL)과 연결된 다수의 제1 터치 라우팅 배선(X-TRW)이 더 지나갈 수 있다(도 4 참조).

- [0240] 제3 비-표시영역(NA3)에는, 다수의 제1 터치전극 라인(X-TEL)과 연결된 다수의 제1 터치 라우팅 배선(X-TRW)이 더 지나갈 수 있다(도 4 내지 도 6 참조). 제3 비-표시영역(NA3)에는, 제4 비-표시영역(NA4)을 지나친 다수의 제2 터치 라우팅 배선(Y-TRW)이 더 지나갈 수 있다.

- [0241] 제1 비-표시영역(NA1)에는, 다수의 제1 터치패드(X-TP) 및 다수의 제2 터치패드(Y-TP)를 포함하는 터치패드 부 (TPA)가 존재한다.

- [0242] 제1 비-표시영역(NA1)에는, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)을 지나가는 모든 터치 라우팅 배선들(X-TRW, Y-TRW)이 모여 터치패드 부(TPA)로 연결된다.

- [0243] 터치패드 부(TPA)가 있는 제1 비-표시영역(NA1)에는 상당히 많은 터치 라우팅 배선들(X-TRW, Y-TRW)이 배치된다.

- [0244] 제1 비-표시영역(NA1)뿐만 아니라, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3) 또한, 많은 터치 라우팅 배선들(X-TRW 및/또는 Y-TRW)이 배치될 수 있다.

- [0245] 또한, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)에는 GIP 타입의 게이트구동회로(GDC)가 배치되는 영역이기 때문에, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)은 그 폭(크기)이 커질 수밖에 없다.

- [0246] 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)의 폭(크기)이 커지게 되면, 터치표시장치 및 표시패널 (DISP)의 베젤이 증가하게 된다. 즉, 터치표시장치의 네로우 베젤(Narrow Bezel)의 구현이 어려워진다.

- [0247] 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)에는 기저 전압(VSS)을 공통전극(CE)으로 전달해주기 위한 전원전달패턴이 배치될 수 있다. 이 경우, 터치표시장치 및 표시패널(DISP)의 베젤이 더욱더 증가하게 된다.

- [0248] 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)의 베젤 증가는, 싱글 라우팅 구조 및 해프-싱글 라우팅 구조보다 더블 라우팅 구조가 더욱 심하지만, 라우팅 구조의 종류에 관계 없이 발생할 수 있는 현상이다.

- [0249] 아래에서는, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)의 베젤 증가 현상과 그에 따른 터치 감도 저 하 현상을 도 15 내지 도 17을 참조하여 더욱 상세히 설명한다. 그리고, 도 18 내지 도 42를 참조하면, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)의 베젤을 감소시킬 수 있는 구조에 대하여 상세하게 설명한다.

- [0250] 단, 아래에서는, 설명의 편의를 위하여, 제2 비-표시영역(NA2)와 제3 비-표시영역(NA3) 중 제2 비-표시영역 (NA2)에 대하여 예시적으로 설명한다. 또한, 아래에서 참조하게 되는 도면들(단면도들)은 개념적으로 나타낸 것으로서, 충들의 높이나 경사 등을 고려하지 않고 도시된 것이다. 이하에 참조되는 도면들은 도 8의 단면 구조에 적용될 것이다.

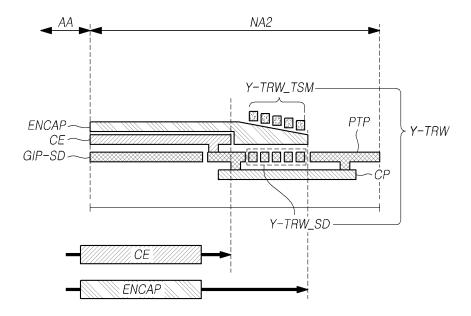

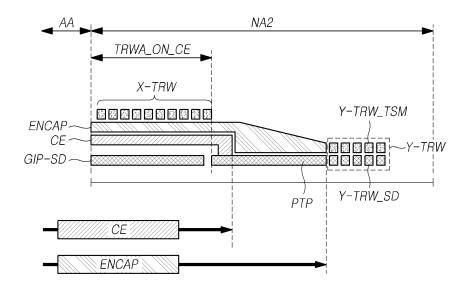

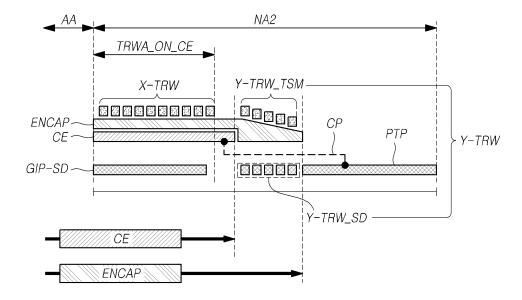

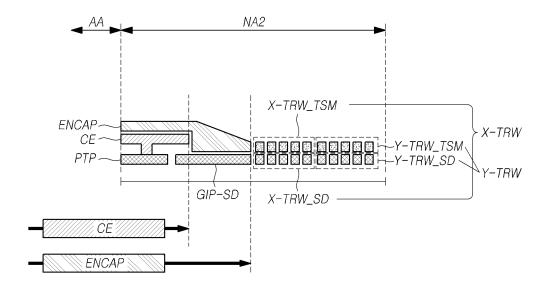

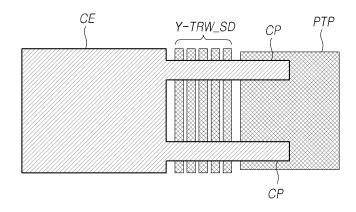

- [0251] 도 15는 본 발명의 실시예들에 따른 표시패널(DISP)의 제2 비-표시영역(NA2)에서, 터치 라우팅 배선들(X-TRW, Y-TRW)의 배치 구조를 개략화하여 나타낸 도면이다.

- [0252] 도 15는 도 4의 더블 라우팅 구조 하에서, 다수의 제1 터치 라우팅 배선들(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)이 제2 비-표시영역(NA2)에 배치되는 구조를 나타낸 단면도이다.

- [0253] 도 15를 참조하면, 표시영역(AA)에 배치되는 공통전극(CE)은 비-표시영역(NA)의 일부 영역까지 연장될 수 있다. 그리고, 표시영역(AA)에 배치되는 봉지층(ENCAP) 또한 비-표시영역(NA)의 일부 영역까지 연장될 수 있다. 봉지층(ENCAP)은 공통전극(CE)보다 더 외곽으로 연장되어 배치된다. 봉지층(ENCAP)은 외곽으로 갈수록 높이가 낮아 저 경사를 이루게 된다. 그리고, 봉지층(ENCAP)의 경사면 끝 부분에 가면 댐(DAM)이 존재할 수 있다. 이는 도 8에도 도시되어 있으며, 이하에서 참조되는 모든 도면들에서도 공통으로 적용된다.

- [0254] 다만, 도 15과 이하에서 참조된 모든 도면들에서 봉지층(ENCAP), 공통전극(CE) 및 터치 라우팅 배선들(X-TRW, Y-TRW) 등은 개념적으로 상대적인 위치 관계만 간략하게 도시한 것일 뿐 실제와는 다를 수 있다. 따라서, 도 15 과 이하에서 참조된 모든 도면들에서 봉지층(ENCAP)의 경사진 면의 위치, 경사 각도, 높이 등도 개념적으로 도시한 것에 불과하다.

- [0255] 도 15를 참조하면, 게이트구동회로(GDC)가 GIP 타입으로 구현된 경우, GIP 타입의 게이트구동회로(GDC)는 제2

비-표시영역(NA1)에 배치되어, 표시영역(AA) 내 배치된 다수의 게이트 라인(GL)과 전기적으로 연결될 수 있다. 게이트구동회로(GDC)는 제2 비-표시영역(NA1)에 배치되되 표시영역(AA)과 인접하여 배치될 수 있다.

- [0256] 도 15를 참조하면, 공통전극(CE)으로 기저전압(VSS)을 공급해주기 위한 전원전달패턴(PTP)가 제2 비-표시영역 (NA2)에 배치될 수 있다. 전원전달패턴(PTP)는 게이트구동회로(GDC)보다 더 외곽에 배치되고, 표시영역(AA)에 확장된 제2 비-표시영역(NA2)에 배치된 공통전극(CE)과 연결될 수 있다.

- [0257] 도 15를 참조하면, 제2 비-표시영역(NA1)에 배치된 다수의 제1 터치 라우팅 배선들(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)은 공통전극(CE)과 중첩될 수 있다.

- [0258] 다시 말해, 제2 비-표시영역(NA2)에서 공통전극(CE)이 존재하는 영역(TRWA\_ON\_CE)에는, 다수의 제1 터치 라우팅 배선들(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)이 공통전극(CE)과 중첩되어 배치될 수 있다.

- [0259] 도 15를 참조하면, 다수의 제1 터치 라우팅 배선들(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)이 공통전극 (CE)과 중첩되어 배치되는 경우, 베젤이 증가할 수 밖에 없고, 전원전달패턴(PTP)의 형성으로 인해 베젤이 더욱 더 커질 수밖에 없다.

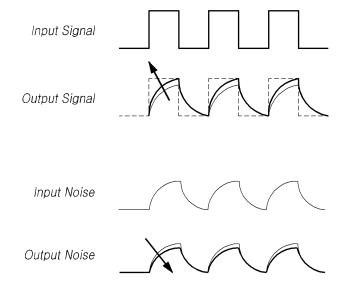

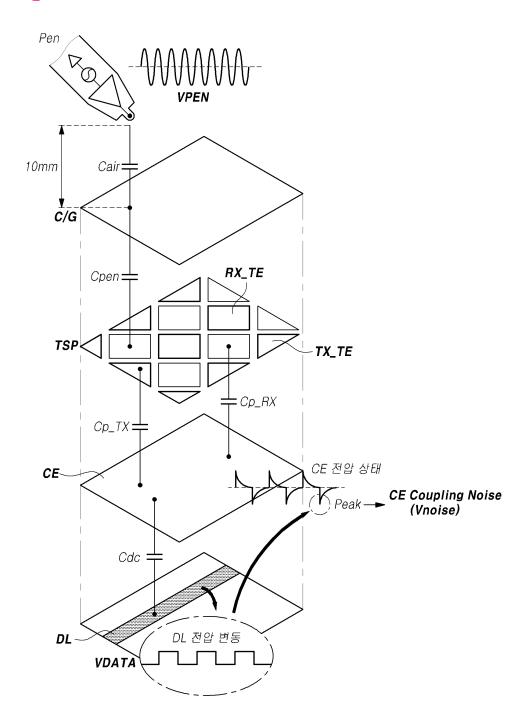

- [0260] 도 16은 본 발명의 실시예들에 따른 표시패널(DISP)에서 공통전극에서 발생되는 노이즈를 나타낸 도면이다.

- [0261] 도 16을 참조하면, 본 발명의 실시예들에 따른 터치표시장치에서, 센싱 동작과 관련하여 발생하는 각종 캐패시 턴스들(Cair, Cpen, Cp\_TX, Cp\_RX, Cdc)이 존재할 수 있다.

- [0262] 표시패널(DISP)에는, 발광소자(ED), 트랜지스터들(T1, T2) 및 스토리지 캐패시터(Cst) 등을 포함하는 서브픽셀들(SP)과 이를 구동하기 위하여 다수의 데이터 라인(DL) 및 다수의 게이트 라인(GL) 등이 배치될 수 있다. 발광소자(ED)는 픽셀전극(PE), 발광충(EL) 및 공통전극(CE)을 포함할 수 있다. 공통전극(CE) 상에 봉지층(ENCAP)이 배치되며, 봉지층(ENCAP) 상에 터치센서가 배치될 수 있다.

- [0263] 봉지층(ENCAP) 상에는 다수의 제1 터치전극 라인(X-TEL) 및 다수의 제2 터치전극 라인(Y-TEL)을 포함하는 터치센서가 배치될 수 있다. 다수의 제1 터치전극 라인(X-TEL)은 다수의 제1 터치전극(X-TE)을 포함하고, 다수의 제2 터치전극 라인(Y-TEL)은 다수의 제2 터치전극(Y-TE)을 포함할 수 있다.

- [0264] 뮤추얼-캐패시턴스 기반의 터치 센싱의 경우, 다수의 제1 터치전극 라인(X-TEL)은 송신 전극 라인들(구동 전극라인들이라고도 함)이고, 다수의 제2 터치전극 라인(Y-TEL)은 수신 전극 라인들(센싱 전극 라인들이라고도 함)일 수 있다. 이와 반대로, 다수의 제1 터치전극 라인(X-TEL)은 수신 전극 라인들(센싱 전극 라인들이라고도함)이고, 다수의 제2 터치전극 라인(Y-TEL)은 송신 전극 라인들(구동 전극라인들이라고도함)일 수 있다.

- [0265] 터치전극 관점에서 볼 때, 뮤추얼-캐패시턴스 기반의 터치 센싱의 경우, 다수의 제1 터치전극(X-TE)은 송신 전 극들(TX\_TE)이고, 다수의 제2 터치전극(Y-TE)은 수신 전극들(RX\_TE)일 수 있다. 이와 반대로, 다수의 제1 터치전극(X-TE)은 수신 전극들(RX\_TE)이고, 다수의 제2 터치전극(Y-TE)은 송신 전극들(TX\_TE)일 수 있다.

- [0266] 전술한 바와 같이, 터치센서에 해당하는 송신 터치전극(TX\_TE) 및 수신 터치전극(RX\_TE)은 봉지층(ENCAP) 상에 위치할 수 있다. 다수의 데이터 라인(DL), 다수의 게이트 라인(GL) 및 구동 트랜지스터(T1) 등은 봉지층(ENCAP)의 아래에 위치할 수 있다.

- [0267] 데이터 라인(DL) 상에 공통전극(CE)이 배치되고, 공통전극(CE) 상에 송신 터치전극(TX\_TE) 및 수신 터치전극(RX\_TE)이 배치되고, 송신 터치전극(TX\_TE) 및 수신 터치전극(RX\_TE) 상에 커버 글라스(C/G)가 위치할 수 있다.

- [0268] 도 16을 참조하면, 전술한 스택 구조에서, 펜의 펜 팁이 커버 클라스(C/G)에 접촉하여 펜 터치가 발생하는 경우, 수신 터치전극(RX\_TE)는 펜의 펜 팁에서 출력된 펜 신호(VPEN)를 수신하게 된다. 이때, 펜과 수신 터치전 극(RX\_TE) 사이에 펜 캐패시턴스(Cpen)가 형성될 수 있다. 또는 핑거가 커버 클라스(C/G)에 접촉하여 핑거 터치가 발생하는 경우, 핑거와 수신 터치전극(RX\_TE) 사이에 핑거 캐패시턴스도 형성될 수 있다. 여기서, 예를 들어, 펜 신호(VPEN)는 정형파(Sine Wave), 삼각파(Triangle Wave), 구형파(Square Wave) 등의 다양한 신호 파형을 가질 수 있다.

- [0269] 도 16을 참조하면, 펜의 펜 팁이 커버 클라스(C/G)에 접촉하지 않고 커버 클라스(C/G)과 일정 거리(예: 10mm 내외)만큼 떨어져, 호버(Hover) 타입의 펜 터치가 발생하는 경우, 펜과 수신 터치전극(RX\_TE) 사이에, 에어 캐패시턴스(Cair)와 펜 캐패시턴스(Cpen)로 나누어져 형성될 수 있다. 즉, 펜과 커버 클라스(C/G) 사이에 에어 캐패시턴스(Cair)가 형성되고, 커버 클라스(C/G)와 수신 터치전극(RX\_TE) 사이에 펜 캐패시턴스(Cpen)가 형성될 수 있다.

- [0270] 도 16을 참조하면, 송신 터치전극(TX\_TE)과 공통전극(CE) 사이에 기생 캐패시턴스(Cp\_TX)가 형성되고, 수신 터치전극(RX\_TE)과 공통전극(CE) 사이에 기생 캐패시턴스(Cp\_RX)가 형성될 수 있다.

- [0271] 도 16을 참조하면, 데이터 전압(VDATA)이 인가되는 데이터 라인(DL)과 공통전압(VSS)이 인가되는 공통전국(CE) 사이에, 기생 캐패시턴스(Cdc)가 형성될 수 있다. 또한, 스캔신호(SCAN)가 인가되는 게이트 라인(GL)와 공통전압(VSS)이 인가되는 공통전극(CE) 사이에, 기생 캐패시턴스가 형성될 수도 있다.

- [0272] 다수의 데이터 라인(DL)에 인가되는 데이터 전압(VDATA)과 다수의 게이트 라인(GL)에 인가되는 스캔신호(SCAN)는 일정 전압을 갖는 것이 아니라, 전압 레벨이 변화하는 신호들이다.

- [0273] 특히, 다수의 데이터 라인(DL)에 인가되는 데이터 전압(VDATA)은 프레임 마다 업데이트 할 이미지에 따라 전압 레벨의 변동의 타이밍이나 수준은 예측하기가 어려운 랜덤성이 큰 신호이다. 랜덤성이 큰 데이터 전압(VDATA)에 의해, 데이터 라인(DL)은 예측하기 어려운 타이밍이나 수준을 갖는 전압 변동 특성을 가질 수 있다.

- [0274] 데이터 라인(DL)의 전압 변동은, 기생 캐패시턴스(Cdc)를 통해 데이터 라인(DL)과 커플링 된 공통전극(CE)에서 의 전압 상태를 변화시킬 수 있다. 더 구체적으로, 데이터 전압(VDATA)의 전압 레벨이 변하는 타이밍에, 기생 캐패시턴스(Cdc)를 통해 데이터 라인(DL)과 커플링 된 공통전극(CE)은 데이터 전압(VDATA)의 전압 레벨 변화에 따른 피크 전압이 발생할 수 있다.

- [0275] 따라서, 공통전극(CE)은, 인가된 DC 전압 형태의 공통전압(VSS)이 일정하게 유지되는 것이 아니라, 데이터 라인 (DL)의 전압 변동에 의해, 피크 전압이 발생하여, 원치 않는 전압 변동이 초래될 수 있다.

- [0276] 공통전극(CE)에서 발생하는 비정상적인 피크 전압은 커플링 노이즈(CE Coupling Noise)라고 하고, 디스플레이성능 및 터치 성능을 떨어뜨릴 수 있는 노이즈 전압(Vnoise)에 해당한다.

- [0277] 공통전극(CE)에서의 원하지 않는 전압 변동은, 공통전극(CE)과 중첩되는 터치센서에 해당하는 송신 터치전극 (TX\_TE)과 공통전극(CE)에서도 원치 않는 전압 변동을 야기시킬 수 있다.

- [0278] 또한, 도 15에 도시된 바와 같이, 공통전극(CE)에서의 원하지 않는 전압 변동은, 공통전극(CE)과 중첩되는 제1 터치 라우팅 배선(X-TRW) 및 제2 터치 라우팅 배선(Y-TRW)에서도 원치 않는 전압 변동을 야기시킬 수 있다. 이러한 현상에 의해, 디스플레이 성능은 물론, 터치 센싱(펜 센싱, 터치 센싱) 성능에도 악영향을 끼칠 수 있다.

- [0279] 따라서, 도 15와 같이, 제2 비-표시영역(NA2)에서, 다수의 제1 터치 라우팅 배선들(X-TRW) 및 다수의 제2 터치라우팅 배선(Y-TRW)이 공통전극(CE)과 중첩되어 배치되는 경우, 베젤이 증가할 뿐만 아니라, 공통전극(CE)에서유발되는 노이즈에 의해, 터치 센싱이 저하될 수 있다.

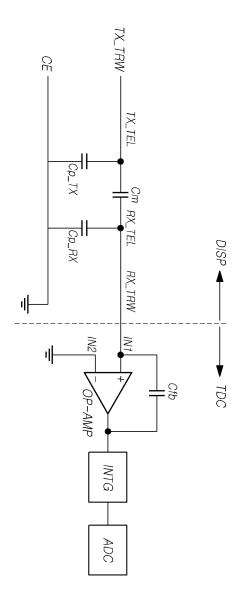

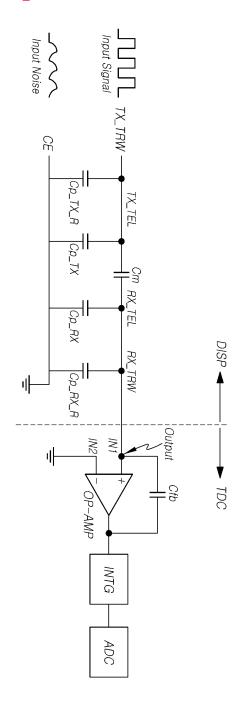

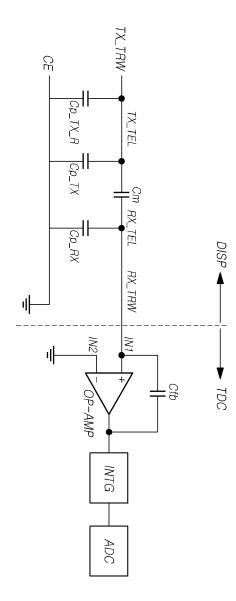

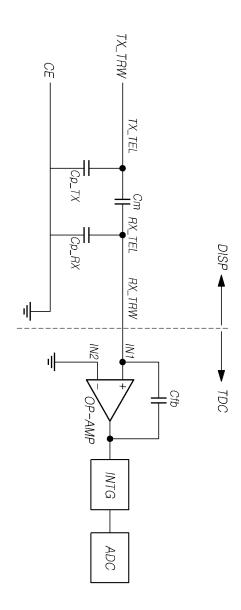

- [0280] 도 17은 본 발명의 실시예들에 따른 터치표시장치의 센싱 시스템의 등가회로를 나타낸 도면이다.

- [0281] 본 발명의 실시예들에 따른 터치표시장치의 센싱 시스템은, 표시패널(DISP) 내 터치센서, 공통전극(CE), 각종 캐패시턴스(Cm, Cp\_TX\_R, Cp\_TX, Cp\_RX, Cp\_RX\_R) 및 터치구동회로(TDC) 등을 모델링 될 수 있으며, 도 17과 같은 등가회로로 나타낼 수 있다.

- [0282] 터치센서는 송신 터치 라우팅 배선(TX\_TRW), 송신 터치 전극라인(TX\_TEL), 수신 터치 라우팅 배선(RX\_TRW) 및 수신 터치 전극라인(RX\_TEL) 등을 포함할 수 있다.

- [0283] 송신 터치 라우팅 배선(TX\_TRW)는 제1 터치 라우팅 배선(X-TRW) 또는 제2 터치 라우팅 배선(Y-TRW)일 수 있다. 수신 터치 라우팅 배선(RX\_TRW)은 제2 터치 라우팅 배선(Y-TRW) 또는 제1 터치 라우팅 배선(X-TRW) 일 수 있다.

- [0284] 송신 터치 전극라인(TX\_TEL)은 제1 터치전극 라인(X-TEL) 또는 제2 터치전극 라인(Y-TEL)일 수 있다. 수신 터치 전극라인(RX\_TEL)은 제2 터치전극 라인(Y-TEL) 또는 제1 터치전극 라인(X-TEL)일 수 있다.

- [0285] 표시영역(AA) 내에서는, 송신 터치 전극라인(TX\_TEL)과 수신 터치 전극라인(RX\_TEL) 사이에 터치 센싱에 필요한 뮤추얼-캐패시턴스(Cm)가 형성될 수 있다.

- [0286] 표시영역(AA) 내에서는, 송신 터치 전극라인(TX\_TEL)과 공통전극(CE) 사이에 송신 측 기생 캐패시턴스(Cp\_TX)가 형성되고, 수신 터치 전극라인(RX\_TEL) 과 공통전극(CE) 사이에 수신 측 제2 기생 캐패시턴스(Cp\_RX)가 형성될 수 있다.

- [0287] 비-표시영역(NA)에서는, 송신 터치 라우팅 배선(TX\_TRW)과 공통전극(CE) 사이에 송신 라우팅 측 기생 캐패시턴 스(Cp\_TX\_R)가 형성되고, 수신 터치 라우팅 배선(RX\_TRW)과 공통전극(CE) 사이에 수신 라우팅 측 제2 기생 캐패

시턴스(Cp\_RX\_R)가 형성될 수 있다.

- [0288] 터치구동회로(TDC)는, 제1 입력단(IN1), 제2 입력단(IN2) 및 출력단을 포함하는 연산 증폭기(OP-AMP)과, 연산 증폭기(OP-AMP)의 제1 입력단(IN1)과 출력단 사이에 연결된 피드백 캐패시터(Cfb)과, 연산 증폭기(OP-AMP)의 출력단에 연결되는 적분기(INTG)와, 적분기(INTG)의 출력단에 연결되는 아날로그-디지털 컨버터(ADC) 등을 포함할수 있다.

- [0289] 연산 증폭기(OP-AMP)의 제1 입력단(IN1)은 비 반전 입력단(+)이고, 연산 증폭기(OP-AMP)의 제2 입력단(IN2)은 반전 입력단(-)일 수 있다. 연산 증폭기(OP-AMP)의 제1 입력단(IN1)은 터치패드(X-TP 또는 Y-TP)를 통해 수신 터치 라우팅 배선(RX\_TRW)과 전기적으로 연결될 수 있다. 연산 증폭기(OP-AMP)의 제2 입력단(IN2)은 기준전압이 인가될 수 있다. 여기서, 예를 들어, 기준전압은 그라운드 전압 등의 DC 전압이 인가될 수 있으며, 경우에 따라서는, AC 전압일 수도 있다. 연산 증폭기(OP-AMP)과 피드백 캐패시터(Cfb)를 합하여 전하 증폭기(Charge Amplifier)라고도 한다.

- [0290] 도 17을 참조하면, 터치구동회로(TDC)는 터치패드(Y-TP 또는 X-TP)를 통해 송신 터치 라우팅 배선(TX\_TRW)으로 터치 센싱을 위한 구동 신호를 입력 신호(Input Signal)로서 입력한다. 이에 따라, 입력 신호가 송신 터치 전극라인(TX\_TEL)에 인가된다.

- [0291] 도 17을 참조하면, 터치구동회로(TDC)는 연산 증폭기(OP-AMP)의 제1 입력단(IN1)과 연결된 수신 터치 라우팅 배선(RX\_TRW)을 통해 수신 터치 전극라인(RX\_TEL)에서의 신호를 검출한다.

- [0292] 여기서, 신호 검출이 되는 노드를 출력노드라고 할 수 있다. 출력 노드는 연산 증폭기(OP-AMP)의 제1 입력단 (IN1)이거나, 연산 증폭기(OP-AMP)의 제1 입력단(IN1)과 연결된 터치패드(X-TP 또는 Y-TP)이거나, 터치패드(X-TP 또는 Y-TP)와 연결된 수신 터치 라우팅 배선(RX\_TRW)에 해당할 수 있다.

- [0293] 도 17을 참조하면, 도 16을 참조하여 전술한 바와 같이, 공통전극(CE)에 원치 않는 노이즈(Noise)가 발생할 수 있다.

- [0294] 공통전극(CE)에서 발생된 비정상적인 노이즈(Noise)에 의해, 공통전극(CE)과 용량 방식으로 커플링 된 송신 터치 라우팅 배선(TX\_TRW), 송신 터치 전극라인(TX\_TEL), 수신 터치 라우팅 배선(RX\_TRW) 및 수신 터치 전극라인 (RX\_TEL)에서, 원치 않는 전압 변동(노이즈)가 발생하여, 센싱 감도를 떨어뜨릴 수 있다.

- [0295] 이러한 문제는, 도 15와 같이, 다수의 제1 터치 라우팅 배선들(X-TRW) 및 다수의 제2 터치 라우팅 배선(Y-TRW)이 공통전극(CE)과 중첩되어 배치되는 경우에 더욱 심해질 수 있다.

- [0296] 아래에서는, 도 18 내지 도 42를 참조하면, 제2 비-표시영역(NA2) 및/또는 제3 비-표시영역(NA3)의 베젤을 감소 시킬 수 있고, 공통전극(CE)에서의 비정상적인 노이즈에도 강인한 구조에 대하여 상세하게 설명한다.

- [0297] 단, 아래에서는, 설명의 편의를 위하여, 제2 비-표시영역(NA2)와 제3 비-표시영역(NA3) 중 제2 비-표시영역 (NA2)에 대하여 예시적으로 설명한다. 또한, 아래에서 참조하게 되는 도면들(단면도들)은 개념적으로 나타낸 것으로서, 충들의 높이나 경사 등을 고려하지 않고 도시된 것이다. 이하에 참조되는 도면들은 도 8의 단면 구조에 적용될 것이다. 또한, 아래에서는, 이상에서 기재한 설명과의 차이점을 위주로 설명한다. 따라서, 아래에서 설명되지 않는 내용은 위의 내용이 적용될 수 있을 것이다.

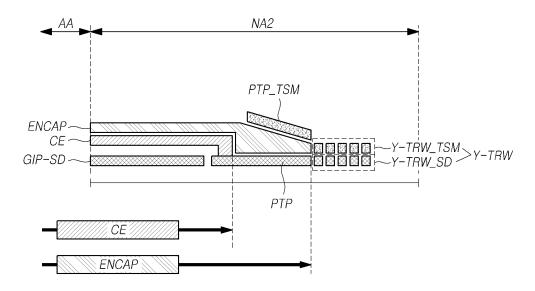

- [0298] 도 18 내지 도 27은 본 발명의 실시예들에 따른 터치표시장치가 더블 라우팅 구조를 갖는 경우, 네로우 베젤을 구현하기 위하여, 표시패널(DISP)의 제2 비-표시영역(NA2)에서의 제1 터치 라우팅 배선들(X-TRW)과 제2 터치 라우팅 배선들(Y-TRW) 중 제2 터치 라우팅 배선들(Y-TRW)이 공통전극(CE)과 중첩되지 않도록 하는 배치 구조들을 나타낸 도면들이다.

- [0299] 도 18 내지 도 27의 배치 구조들의 경우, 제1 터치 라우팅 배선들(X-TRW)과 제2 터치 라우팅 배선들(Y-TRW) 중 제2 터치 라우팅 배선들(Y-TRW)이 공통전극(CE)과 중첩되지 않는다. 이를 통해, 네로우 베젤 구현을 용이하게 하고, 공통전극(CE)과 제2 터치 라우팅 배선들(Y-TRW) 사이에 기생 캐패시턴스가 형성되는 것을 방지해주어 터치 감도를 향상시켜줄 수 있다. 아래에서 더욱 상세하게 설명한다.

- [0300] 본 발명의 실시예들에 따른 터치표시장치는, 기판(SUB), 기판(SUB) 상에 다수의 서브픽셀 영역마다 배치되는 다수의 픽셀전극(PE), 다수의 픽셀전극(PE) 상에 배치되며 공통전압(VSS)이 인가되는 공통전극(CE), 공통전극(CE)을 덮으면서 배치되는 봉지층(ENCAP), 표시영역(AA)에서 봉지층(ENCAP) 상에 배치되는 n개의 제1 터치전극 라인(X-TEL)과 m개의 제2 터치전극 라인(Y-TEL)을 포함하는 터치센서 등을 포함할 수 있다.

- [0301] 더블 라우팅 구조를 갖는 경우, 터치표시장치는, 표시영역(AA)의 외곽 영역인 비-표시영역(NA) 중 표시영역(A A)으로부터 제1 방향으로 외곽에 위치하는 제1 비-표시영역(NA1)에 배치되며, 2n개의 제1 터치패드(X-TP) 및 2m 개의 제2 터치패드(Y-TP)를 포함하는 터치패드 부(TPA)를 더 포함할 수 있다.

- [0302] 더블 라우팅 구조를 갖는 경우, 터치표시장치는, 봉지층(ENCAP)의 경사면을 따라 내려와, n개의 제1 터치전극라인(X-TEL) 각각의 일단과 타단을 제1 비-표시영역(NA1)에 배치된 2n개의 제1 터치패드(X-TP)와 전기적으로 연결해주는 2n개의 제1 터치 라우팅 배선(X-TRW)을 더 포함할 수 있다.

- [0303] 더블 라우팅 구조를 갖는 경우, 터치표시장치는, 봉지층(ENCAP)의 경사면을 따라 내려와, m개의 제2 터치전극라인(Y-TEL) 각각의 일단과 타단을 제1 비-표시영역(NA1)에 배치된 2m개의 제1 터치패드(X-TP)와 전기적으로 연결해주는 2m개의 제2 터치 라우팅 배선(Y-TRW)을 더 포함할 수 있다.

- [0304] 본 발명의 실시예들에 따른 터치표시장치에서, n개의 제1 터치전극 라인(X-TEL)과 m개의 제2 터치전극 라인(Y-TEL) 각각은 1가지 이상의 터치센서메탈을 포함할 수 있다.

- [0305] 더블 라우팅 구조를 갖는 경우, 2n개의 제1 터치 라우팅 배선(X-TRW) 중 일부(예를 들어, n개)의 제1 터치 라우팅 배선(X-TRW)과, 2m개의 제2 터치 라우팅 배선(Y-TRW) 중 일부(예를 들어, m개)의 제2 터치 라우팅 배선(Y-TRW)은, 표시영역(AA)으로부터 제2 방향으로 외곽에 위치하는 제2 비-표시영역(NA2)을 지나갈 수 있다.

- [0306] 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)은 터치센서메탈을 포함할 수 있다.

- [0307] 도 18 내지 도 27을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)은 표 시영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)과 중첩되어 배치될 수 있다.

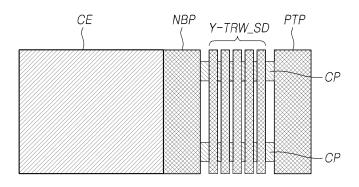

- [0308] 도 18 내지 도 27을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과, 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW SD)을 포함할 수 있다.

- [0309] 이와 같이, 제2 비-표시영역(NA2)에 배치되는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이 1개의 층에 나란히 배치되는 것이 아니라 2개 층 또는 그 이상의 층(예: 3개 층, 4개 층 등)에 나누어서 배치되므로, 제2 비-표시영역(NA2)에서 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이 차지하는 베젤 영역 크기를 줄일 수 있다.

- [0310] 제1 메탈은 터치센서메탈과 다른 메탈로서, 1가지 이상을 메탈을 포함할 수 있다. 예를 들어, 제1 메탈은, 표시영역(AA) 내 배치된 트랜지스터들(T1, T2 등)의 소스 및 드레인 전극이나 표시영역(AA) 내 데이터 라인(DL)에 포함되는 소스-드레인 메탈과, 표시영역(AA) 내 트랜지스터들(T1, T2 등)의 게이트 전극이나 게이트 라인(GL)에 포함되는 게이트 메탈 중 1 가지 이상을 포함할 수 있다.

- [0311] 전술한 바와 같이, 제1 메탈이 소스-드레인 메탈 또는 게이트 메탈을 포함하는 경우, 제1 메탈이 포함된 하나이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 1개의 층에 배치될 수 있다. 이와 다르게, 제1 메탈이 소스-드레인 메탈과 게이트 메탈을 모두 포함할 수도 있다. 이 경우, 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선 (Y-TRW\_SD)은 2개의 층에 나누어져 배치될 수 있다. 이러한 내용은 아래에서 설명되는 모든 구조들에서 적용될수 있다.

- [0312] 터치센서메탈은 전극 메탈과 브릿지 메탈 중 1 가지 이상을 포함할 수 있다. 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)은, 전극 메탈 및 브릿지 메탈 중 하나의 터치센서메탈을 포함하는 경우, 1 개의 층에 배치될 수 있다. 이와 다르게, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)은, 2가지 터치센서메탈(전극 메탈 및 브릿지 메탈)을 모두 포함하는 경우, 2개의 층에 나누어져 배치될 수 있다. 이러한 내용은 아래에서 설명되는 모든 구조들에서 적용될 수 있다.

- [0313] 도 18 내지 도 27을 참조하면, 터치표시장치에서 GIP 타입으로 구현된 게이트구동회로(GDC)는, 표시영역(AA) 내 배치된 다수의 게이트 라인(GL)과 전기적으로 연결되며, 제2 비-표시영역(NA2)에 배치되며, 표시영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)과 중첩되어 배치될 수 있다.

- [0314] 도 18 내지 도 27을 참조하면, 게이트구동회로(GDC)는, 제1 메탈과 동일한 메탈(GIP-SD)이 포함된 트랜지스터들 (예를 들어, 풀-업 트랜지스터, 풀-다운 트랜지스터 등)을 포함할 수 있다. 여기서, 제1 메탈은, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)에 포함된 메탈이다.

- [0315] 도 18 내지 도 27을 참조하면, 터치표시장치는, 공통전극(CE)으로 공통전압(VSS)을 전달하며 제2 비-표시영역

(NA2)에 배치된 전원전달패턴(PTP)을 더 포함할 수 있다.

- [0316] 도 18 내지 도 27을 참조하면, 전원전달패턴(PTP)은 제1 메탈을 포함할 수 있다. 여기서, 제1 메탈은, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)에 포함된 메탈이다.

- [0317] 전원전달패턴(PTPT)의 위치에 대한 일 예로서, 전원전달패턴(PTP)은, 도 18, 도 19 및 도 27에 도시된 바와 같이, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)과 게이트구동회로(GDC) 사이에 배치될 수 있다.

- [0318] 전원전달패턴(PTPT)의 위치에 대한 다른 예로서, 전원전달패턴(PTP)은, 도 20 내지 도 26에 도시된 바와 같이, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)보다 더 외곽에 배치될 수도 있다.

- [0319] 도 18 및 도 19를 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 표시 영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)과 중첩되지 않으면서 배치될 수 있다.

- [0320] 이에 따라, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 공통전극(CE)과 기생 캐패시턴스를 형성하지 않는다. 만약, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이 수신 터치 라우팅 배선(RX\_TRW)이라면, 수신 터치 라우팅 배선(RX\_TRW)과 공통전극(CE) 사이에 수신 라우팅 측 제2 기생 캐패시턴스(Cp\_RX\_R)가 형성되지 않는다. 이로 인해, 터치 감도가 향상될 수 있다.

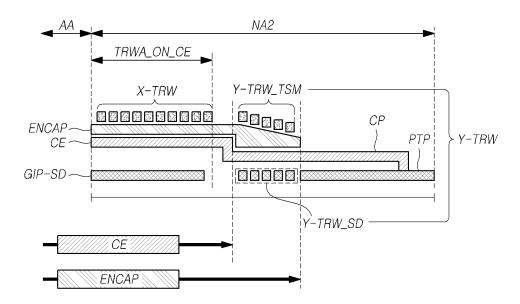

- [0321] 도 19를 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)에서, 터치센서메 탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 서로 다른 층에서 서로 엇갈리면서 배치될 수 있다.

- [0322] 도 19를 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)에서, 터치센서메 탈이 포함된 둘 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM) 사이의 공간은, 제1 메탈이 포함된 둘 이상의 제2 터치 라우팅 배선(Y-TRW\_SD) 각각에 중첩될 수 있다.

- [0323] 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 서로 다른 층에서 서로 엇갈리면서 배치되는 구조는, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과, 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)을 포함하는다른 모든 경우에도 적용될 수 있다.

- [0324] 도 20 내지 도 26을 참조하면, 터치표시장치는, 공통전극(CE)과 전원전달패턴(PTP)을 전기적으로 연결해주는 연결패턴(CP)을 더 포함할 수 있다.

- [0325] 연결패턴(CP)은 전원전달패턴(PTP)이 제2 터치 라우팅 배선(Y-TRW)보다 더 외곽에 배치된 경우에 유용할 수 있다.

- [0326] 제2 터치 라우팅 배선들(Y-TRW)이 공통전극(CE)과 전원전달패턴(PTP) 사이에 존재하는 경우, 연결패턴(CP)은 제 2 터치 라우팅 배선들(Y-TRW)과 중첩되어 배치되어, 공통전극(CE)과 전원전달패턴(PTP)을 전기적으로 연결해준다.

- [0327] 연결패턴(CP)의 형성 위치나 물질 종류 등은 다양할 수 있다. 연결패턴(CP)은, 공통전극(CE)과 동일한 물질과, 표시영역(AA) 내 픽셀전극(PE)과 동일한 물질과, 표시영역(AA) 내 트랜지스터(T1, T2)의 게이트 전극과 동일한 물질(게이트 메탈)과, 표시영역(AA) 내 트랜지스터(T1, T2)의 소스 전극 및 드레인 전극과 동일한 물질(소스-드레인 메탈) 등 중에서 1 가지 이상을 물질(메탈)을 포함하되, 제1 메탈과 다른 1가지 이상의 물질(메탈)을 포함할 수 있다. 이러한 내용은 도 34 내지 도 40 등의 연결패턴(CP)에 대해서도 적용될 수 있다.

- [0328] 예를 들어, 도 21 및 도 22(도 21의 일부분의 평면도)에 도시된 바와 같이, 연결패턴(CP)은 공통전극(CE)과 동일한 물질로 구성될 수 있다. 다른 예를 들어, 도 23 및 도 24(도 23의 일부분의 평면도)에 도시된 바와 같이, 연결패턴(CP)은 픽셀전극(PE)과 동일한 물질로 구성될 수 있다. 또 다른 예를 들어, 도 25 및 도 26(도 25의 일부분의 평면도)에 도시된 바와 같이, 연결패턴(CP)은 게이트 전극과 동일한 물질로 구성될 수 있다.

- [0329] 도 21 및 도 22를 참조하면, 연결패턴(CP)이 공통전극(CE)과 동일한 물질로 구성된 경우, 연결패턴(CP)은 표시 영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)에서 돌출된 부분일 수 있다.

- [0330] 도 21 및 도 22를 참조하면, 연결패턴(CP)은 봉지층(ENCAP)과 중첩될 수 있다. 연결패턴(CP)의 일부는 공통전극 (CE)과 연결되고 봉지층(ENCAP)의 경사면의 중첩되고, 연결패턴(CP)의 다른 부분은 제2 터치 라우팅 배선(Y-TRW)보다 더 외곽에 배치된 전원전달패턴(PTP)과 연결되고 중첩될 수 있다.

- [0331] 도 21 및 도 22를 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 연결 패턴(CP)과 중첩되어 배치될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 터치센서메탈을 포함하는 제2 터치 라우팅 배선(Y-TRW\_TSM)은 연결패턴(CP)의 위에서 연결패턴(CP)과 중첩된다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 제1 메탈을 포함하는 제2 터치 라우팅 배선(Y-TRW\_SD)은 연결패턴(CP)의 아래에서 연결패턴(CP)과 중첩된다.

- [0332] 도 23 및 도 24를 참조하면, 연결패턴(CP)이 표시영역(AA) 내 픽셀전극(PE)과 동일한 물질을 포함하는 경우, 연결패턴(CP)은 봉지층(ENCAP)과 중첩될 수 있다. 연결패턴(CP)의 일부는 공통전극(CE)과 연결되고 봉지층(ENCAP)의 경사면의 중첩되고, 연결패턴(CP)의 다른 부분은 제2 터치 라우팅 배선(Y-TRW)보다 더 외곽에 배치된 전원 전달패턴(PTP)과 연결되고 중첩될 수 있다.

- [0333] 도 23 및 도 24를 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 연결 패턴(CP)과 중첩되어 배치될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 터치센서메탈을 포함하는 제2 터치 라우팅 배선(Y-TRW\_TSM)은 연결패턴(CP)의 위에서 연결패턴(CP)과 중첩될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 제1 메탈을 포함하는 제2 터치 라우팅 배선(Y-TRW\_SD)은 연결패턴(CP)의 아래에서 연결패턴(CP)과 중첩될 수 있다.

- [0334] 도 25 및 도 26을 참조하면, 연결패턴(CP)이 표시영역(AA) 내 트랜지스터(T1, T2)의 게이트 전극과 동일한 물질을 포함하는 경우, 연결패턴(CP)은 봉지층(ENCAP)과 중첩될 수 있다. 연결패턴(CP)의 일부는 공통전극(CE)과 연결되고 봉지층(ENCAP)의 경사면의 중첩되고, 연결패턴(CP)의 다른 부분은 제2 터치 라우팅 배선(Y-TRW)보다 더외곽에 배치된 전원전달패턴(PTP)과 연결되고 중첩될 수 있다.

- [0335] 도 25 및 도 26을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 연결 패턴(CP)과 중첩되어 배치될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 터치센서메탈을 포함하는 제2 터치 라우팅 배선(Y-TRW\_TSM)은 연결패턴(CP)의 위에서 연결패턴(CP)과 중첩될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 제1 메탈을 포함하는 제2 터치 라우팅 배선(Y-TRW\_SD)은 연결패턴(CP)의 아래에서 연결패턴(CP)과 중첩될 수 있다.

- [0336] 도 23 내지 도 26을 참조하면, 터치표시장치는, 게이트구동회로(GDC)와 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 사이에 배치되며 공통전압(VSS)이 인가되는 노이즈 차단 패턴(NBP)을 더 포함할 수 있다.

- [0337] 노이즈 차단 패턴(NBP)의 형성에 따라, 제2 터치 라우팅 배선(Y-TRW)과 게이트구동회로(GDC) 사이에 불필요한 기생 캐패시턴스가 형성되는 것을 방지해줄 수 있다. 노이즈 차단 패턴(NBP)은 제2 터치 라우팅 배선(Y-TRW)이 게이트구동회로(GDC)의 영향을 받지 않도록 해줄 수 있다.

- [0338] 도 20 내지 도 26을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW) 중 적어도 하나는 제2 비-표시영역(NA2) 내에서 봉지층(ENCAP)의 경사면과 중첩될 수 있다.

- [0339] 도 27을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 표시영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)과 중첩되지 않으면서 배치될 수 있다.

- [0340] 이에 따라, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 공통전극(CE)과 기생 캐패시턴스를 형성하지 않는다. 만약, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이 수신 터치 라우팅 배선(RX\_TRW)이라면, 수신 터치 라우팅 배선(RX\_TRW)과 공통전극(CE) 사이에 수신 라우팅 측 제2 기생 캐패시턴스(Cp\_RX\_R)가 형성되지 않는다. 이로 인해, 터치 감도가 향상될 수 있다.

- [0341] 도 27를 참조하면, 터치표시장치는, 공통전극(CE)으로 공통전압(VSS)을 전달하기 위하여, 전원전달패턴(PTP)과 다른 추가적인 추가 전원전달패턴(PTP\_TSM)을 더 포함할 수 있다.

- [0342] 도 27를 참조하면, 전원전달패턴(PTP)은 제2 비-표시영역(NA2)에 배치되고, 터치센서메탈과 다른 제1 메탈(예를 들어, 소스-드레인 메탈)이 포함될 수 있다. 이에 비해, 추가 전원전달패턴(PTP\_TSM)은 제2 비-표시영역(NA2)에 배치되고, 터치센서메탈이 포함될 수 있다.

- [0343] 도 27를 참조하면, 터치표시장치는, 공통전극(CE)으로 공통전압(VSS)을 전달하기 위하여, 추가 전원전달패턴 (PTP\_TSM)를 더 구비함으로써, 전원전달패턴(PTP)의 폭을 줄일 수 있다.

- [0344] 도 27를 참조하면, 추가 전원전달패턴(PTP\_TSM)은 터치센서메탈을 포함하기 때문에, 추가 전원전달패턴 (PTP\_TSM)은 터치센서메탈로 이루어진 제1 터치 라우팅 배선(X-TRW) 및 터치센서메탈로 이루어진 제2 터치 라우팅 배선(Y-TRW\_TSM)과 함께 형성될 수 있다. 또한, 추가 전원전달패턴(PTP\_TSM)은 제1 및 제2 터치전극 라인들 (X-TEL, Y-TEL)과도 함께 형성될 수 있다.

- [0345] 도 27를 참조하면, 추가 전원전달패턴(PTP\_TSM)은 봉지층(ENCAP) 상에 배치될 수 있으며, 경우에 따라, 추가 전원전달패턴(PTP\_TSM)의 전체 또는 일부는 봉지층(ENCAP)의 경사면과 중첩될 수 있다.

- [0346] 도 28은 도 18 내지 도 27의 배치 구조들에 따른 센싱 시스템의 등가회로이다.

- [0347] 도 28을 참조하면, 도 18 내지 도 27의 배치 구조들에 따르면, 제2 터치 라우팅 배선들(Y-TRW)이 공통전극(CE)과 중첩되지 않는다. 따라서, 제2 터치 라우팅 배선들(Y-TRW)과 공통전극(CE) 사이에 기생 캐패시턴스가 형성되지 않는다. 만약, 제2 터치 라우팅 배선들(Y-TRW)이 수신 터치 라우팅 배선(RX\_TRW)이라면, 비-표시영역(NA)에서 수신 터치 라우팅 배선(RX\_TRW)과 공통전극(CE) 사이에 기생 캐패시턴스(Cp\_RX\_R)가 형성되지 않는다(도 17과 비교). 이로 인해, 터치 감도가 향상될 수 있다.

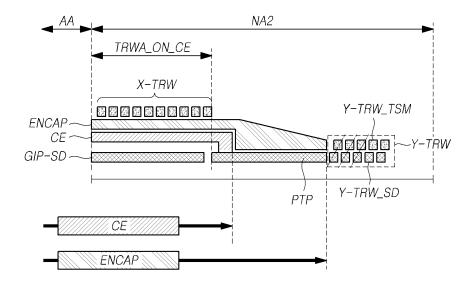

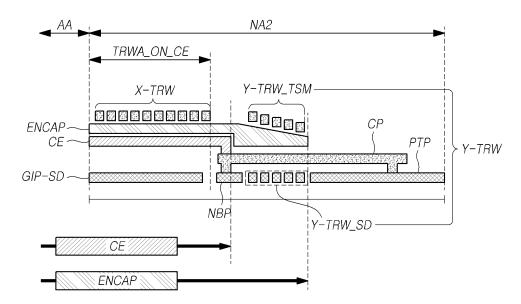

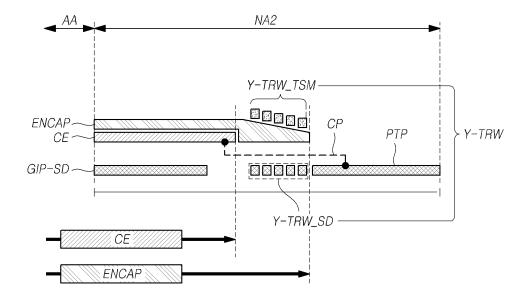

- [0348] 도 29 내지 도 31은 본 발명의 실시예들에 따른 터치표시장치가 더블 라우팅 구조를 갖는 경우, 네로우 베젤을 구현하기 위하여, 표시패널(DISP)의 제2 비-표시영역(NA2)에서의 제1 터치 라우팅 배선들(X-TRW)과 제2 터치 라우팅 배선들(Y-TRW)이 공통전극(CE)과 중첩되지 않도록 하는 배치 구조들을 나타낸 도면들이다. 도 4의 더블 라우팅 구조도 함께 참조된다.

- [0349] 도 29 내지 도 31의 배치 구조들의 경우, 도 18 내지 도 27의 배치 구조들과 다르게, 제1 터치 라우팅 배선들 (X-TRW)과 제2 터치 라우팅 배선들(Y-TRW) 모두가 공통전극(CE)과 중첩되지 않는다. 이를 통해, 네로우 베젤 구현을 용이하게 하고, 공통전극(CE)과 터치 라우팅 배선들(X-TRW, Y-TRW) 사이에 기생 캐패시턴스가 형성되는 것을 방지해주어 터치 감도를 향상시켜줄 수 있다. 아래에서 더욱 상세하게 설명한다.

- [0350] 전술한 바와 같이, 터치표시장치의 터치센서는 표시영역(AA)에서 봉지층(ENCAP) 상에 배치되는 n개의 제1 터치전극 라인(X-TEL)과 m개의 제2 터치전극 라인(Y-TEL)을 포함할 수 있다. n개의 제1 터치전극 라인(X-TEL)과 m개의 제2 터치전극 라인(Y-TEL) 각각은 1가지 이상의 터치센서메탈을 포함할 수 있다.

- [0351] 더블 라우팅 구조를 갖는 경우, 터치패드 부(TPA)는, 표시영역(AA)의 외곽 영역인 비-표시영역(NA) 중 표시영역 (AA)으로부터 제1 방향으로 외곽에 위치하는 제1 비-표시영역(NA1)에 배치되며, 2n개의 제1 터치패드(X-TP) 및 2m개의 제2 터치패드(Y-TP)를 포함할 수 있다.

- [0352] 더블 라우팅 구조를 갖는 경우, 터치표시장치는, 봉지층(ENCAP)의 경사면을 따라 내려와, n개의 제1 터치전극라인(X-TEL) 각각의 일단과 타단을 제1 비-표시영역(NA1)에 배치된 2n개의 제1 터치패드(X-TP)와 전기적으로 연결해주는 2n개의 제1 터치 라우팅 배선(X-TRW)을 포함할 수 있다.

- [0353] 더블 라우팅 구조를 갖는 경우, 터치표시장치는, 봉지층(ENCAP)의 경사면을 따라 내려와, m개의 제2 터치전극라인(Y-TEL) 각각의 일단과 타단을 제1 비-표시영역(NA1)에 배치된 2m개의 제2 터치패드(Y-TP)와 전기적으로 연결해주는 2m개의 제2 터치 라우팅 배선(Y-TRW)을 포함할 수 있다.

- [0354] 더블 라우팅 구조를 갖는 경우, 2n개의 제1 터치 라우팅 배선(X-TRW) 중 둘 이상의 제1 터치 라우팅 배선(X-TRW)과, 2m개의 제2 터치 라우팅 배선(Y-TRW) 중 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은, 표시영역(AA)으로 부터 제2 방향으로 외곽에 위치하는 제2 비-표시영역(NA2)을 지나갈 수 있다.

- [0355] 도 29 내지 도 31을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)은, 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_TSM)과, 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_SD)을 포함할 수 있다.

- [0356] 이와 같이, 제2 비-표시영역(NA2)에 배치되는 둘 이상의 제1 터치 라우팅 배선(X-TRW)이 1개의 층에 나란히 배치되는 것이 아니라 2개 층 또는 그 이상의 층(예: 3개 층, 4개 층 등)에 나누어서 배치되므로, 제2 비-표시영역(NA2)에서 둘 이상의 제1 터치 라우팅 배선(X-TRW)이 차지하는 베젤 영역 크기를 줄일 수 있다.

- [0357] 도 29 내지 도 31을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은, 터 치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과, 제1 메탈이 포함된 하나 이상의 제2 터

치 라우팅 배선(Y-TRW\_SD)을 포함할 수 있다.

- [0358] 이와 같이, 제2 비-표시영역(NA2)에 배치되는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이 1개의 층에 나란히 배치되는 것이 아니라 2개 층 또는 그 이상의 층(예: 3개 층, 4개 층 등)에 나누어서 배치되므로, 제2 비-표시영역(NA2)에서 둘 이상의 제2 터치 라우팅 배선(Y-TRW)이 차지하는 베젤 영역 크기를 줄일 수 있다.

- [0359] 도 29 내지 도 31을 참조하면, 예를 들어, 제1 메탈은, 터치센서에 포함되는 터치센서메탈과 다른 메탈로서, 1 가지 이상을 메탈을 포함할 수 있다. 예를 들어, 제1 메탈은, 표시영역(AA) 내 배치된 트랜지스터들(T1, T2 등)의 소스 및 드레인 전극이나 표시영역(AA) 내 데이터 라인(DL)에 포함되는 소스-드레인 메탈과, 표시영역(AA) 내 트랜지스터들(T1, T2 등)의 게이트 전극이나 게이트 라인(GL)에 포함되는 게이트 메탈 중 1 가지 이상을 포함할 수 있다.

- [0360] 전술한 바와 같이, 제1 메탈이 소스-드레인 메탈 또는 게이트 메탈을 포함하는 경우, 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_SD)과 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 1 개의 층에 배치될 수 있다. 이와 다르게, 제1 메탈이 소스-드레인 메탈과 게이트 메탈을 모두 포함할 수도 있다. 이 경우, 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_SD)은 2개의 층에 나누어져 배치되고, 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 2개의 층에 나누어져 배치될 수 있다.

- [0361] 터치센서메탈은 전극 메탈과 브릿지 메탈 중 1 가지 이상을 포함할 수 있다. 터치센서메탈이 포함된 하나 이상의 제 1 터치 라우팅 배선(X-TRW\_TSM)과 터치센서메탈이 포함된 하나 이상의 제 2 터치 라우팅 배선(Y-TRW\_TSM)은, 전극 메탈 및 브릿지 메탈 중 하나의 터치센서메탈을 포함하는 경우, 1개의 층에 배치될 수 있다. 이와 다르게, 터치센서메탈이 포함된 하나 이상의 제 1 터치 라우팅 배선(X-TRW\_TSM)은 2가지 터치센서메탈(전극 메탈 및 브릿지 메탈)을 모두 포함하는 경우, 2개의 층에 나누어져 배치될 수 있다. 그리고, 터치센서 메탈이 포함된 하나 이상의 제 2 터치 라우팅 배선(Y-TRW\_TSM)은, 2가지 터치센서메탈(전극 메탈 및 브릿지 메탈)을 모두 포함하는 경우 2개의 층에 나누어져 배치될 수 있다.

- [0362] 도 29 내지 도 31을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)에서, 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_TSM)과, 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_SD)은, 서로 다른 층에서 서로 중첩되게 배치될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)에서, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 서로 다른 층에서 서로 중첩되게 배치될 수 있다.

- [0363] 도 29 내지 도 31을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)에서, 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_TSM)과, 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_SD)은, 서로 다른 층에서 서로 엇갈리면서 배치될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)에서, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선 (Y-TRW\_TSM)과 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 서로 다른 층에서 서로 엇갈리면서 배치될 수 있다.

- [0364] 도 29 내지 도 31을 참조하면, 터치표시장치는, 표시영역(AA) 내 배치된 다수의 게이트 라인(GL)과 전기적으로 연결되며, 제2 비-표시영역(NA2)에 배치되며 제1 메탈이 포함된 트랜지스터들을 포함하는 GIP 타입의 게이트구 동회로(GDC)를 더 포함할 수 있다.

- [0365] 도 29 내지 도 31을 참조하면, 터치표시장치는, 공통전극(CE)으로 공통전압(VSS)을 전달하며 제2 비-표시영역 (NA2)에 배치된 전원전달패턴(PTP)을 더 포함할 수 있다. 전원전달패턴(PTP)은 터치센서메탈과 다른 제1 메탈을 포함할 수 있다.

- [0366] 도 29 내지 도 31을 참조하면, 전원전달패턴(PTP)은 게이트구동회로(GDC)보다 표시영역(AA)에 더 가깝게 배치될 수 있다

- [0367] 도 29를 참조하면, 표시영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)은 게이트구동회로(GDC)와 중첩될 수 있다.

- [0368] 도 31을 참조하면, 표시영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)은, 게이트구동회로(GDC)와 완전히 중첩되지 않고, 게이트구동회로(GDC)가 노출되도록 오픈 되어 있을 수 있다.

- [0369] 도 29 및 도 31을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)은 표시

영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)과 중첩되지 않고 배치될 수 있다. 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 표시영역(AA)에서 제2 비-표시영역(NA2)까지 확장된 공통전극(CE)과 중첩되지 않고 배치될 수 있다.

- [0370] 따라서, 제1 터치 라우팅 배선(X-TRW)과 공통전극(CE) 사이의 기생 캐패시턴스가 형성되지 않고, 제2 터치 라우팅 배선(Y-TRW)과 공통전극(CE) 사이의 기생 캐패시턴스가 형성되지 않을 수 있다.

- [0371] 도 29 내지 도 31을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)보다 더 외곽에 배치될 수 있다.

- [0372] 도 29 및 도 30을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW) 중 터치 센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_TSM)은 봉지층(ENCAP) 상에 배치될 수 있다.

- [0373] 이에 비해, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW) 중 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_SD)은 봉지층(ENCAP) 아래에 배치될 수 있다.

- [0374] 도 29 및 도 30을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW) 중 터치 센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW\_TSM)의 전체 또는 일부는 제2 비-표시영역(NA2) 내 에서 봉지층(ENCAP)의 경사면과 중첩될 수 있다.

- [0375] 도 30을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW) 각각은, 터치센서 메탈이 포함된 상부 배선(X-TRW\_UP)과 제1 메탈이 포함된 하부 배선(X-TRW\_DOWN)을 포함할 수 있다.

- [0376] 도 30을 참조하면, 상부 배선(X-TRW\_UP)의 일단과 하부 배선(X-TRW\_DOWN)의 일단은 봉지층(ENCAP)의 끝에서 제1 방향으로 외곽에 위치하는 제1 지점(P1)에서 컨택될 수 있다.

- [0377] 상부 배선(X-TRW\_UP)의 타단과 하부 배선(X-TRW\_DOWN)의 타단은 봉지층(ENCAP)의 반대 끝에서 제1 방향의 반대 방향으로 외곽에 위치한 제3 지점(P3)에서 컨택될 수 있다. 제1 지점(P1)과 제3 지점(P3)은 봉지층(ENCAP)이 없는 지점들로서, 봉지층(ENCAP)이 끝난 지점보다 더 외곽인 지점들이다.

- [0378] 도 30을 참조하면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW) 중에서 하나의 제 1 터치 라우팅 배선(X-TRW (B))은, 다른 제1 터치 라우팅 배선(X-TRW (A))의 위 또는 아래에 배치된 메탈(OCM)을 통해 해당 제1 터치전극 라인(X-TEL)과 연결될 수 있다.

- [0379] 도 32는 도 29 내지 도 31의 배치 구조들에 따른 센싱 시스템의 등가회로이다.

- [0380] 도 32를 참조하면, 도 29 내지 도 31의 배치 구조들에 따르면, 제2 비-표시영역(NA2)을 지나가는 둘 이상의 제1 터치 라우팅 배선(X-TRW)과 둘 이상의 제2 터치 라우팅 배선(Y-TRW)은 공통전극(CE)과 중첩되지 않고 배치될 수 있다. 따라서, 제1 터치 라우팅 배선(X-TRW)과 공통전극(CE) 사이의 기생 캐패시턴스가 형성되지 않고, 제2 터치 라우팅 배선(Y-TRW)과 공통전극(CE) 사이의 기생 캐패시턴스가 형성되지 않을 수 있다.

- [0381] 제1 터치 라우팅 배선(X-TRW)이 수신 터치 라우팅 배선(RX\_TRW)이고, 제2 터치 라우팅 배선(Y-TRW)이 송신 터치 라우팅 배선(TX\_TRW)인 경우, 비-표시영역(NA)에서, 수신 터치 라우팅 배선(RX\_TRW) 및 공통전극(CE) 간의 기생 캐패시턴스(Cp\_RX\_R)와 송신 터치 라우팅 배선(TX\_TRW) 및 공통전극(CE) 간의 기생 캐패시턴스(Cp\_TX\_R)이 형성 되지 않는다(도 17과 비교). 이에 따라, 터치 감도가 향상될 수 있다.

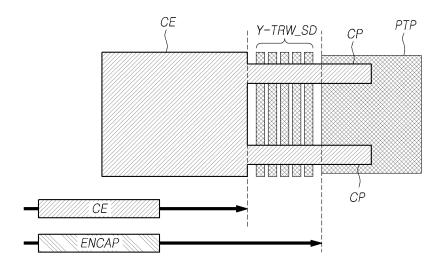

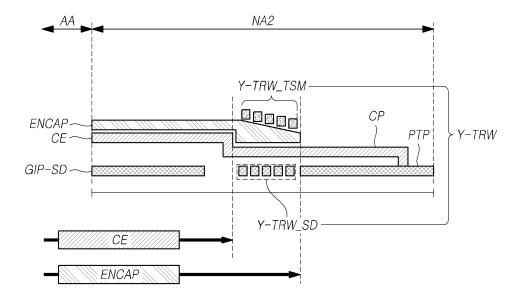

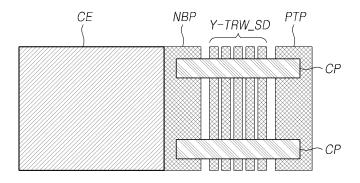

- [0382] 도 33 내지 도 40은 본 발명의 실시예들에 따른 터치표시장치가 싱글 라우팅 구조 또는 해프-싱글 라우팅 구조를 갖는 경우, 네로우 베젤을 구현하기 위하여, 표시패널(DISP)의 제2 비-표시영역(NA2)에서의 제1 터치 라우팅 배선들(X-TRW)과 제2 터치 라우팅 배선들(Y-TRW)이 공통전극(CE)과 중첩되지 않도록 하는 배치 구조들을 나타낸 도면들이다. 아래에서는, 싱글 라우팅 구조의 도 5와 해프-싱글 라우팅 구조의 도 6과, 다양한 비-표시영역들 (NA1, NA2, NA3, NA4)이 도시된 도 14가 함께 참조된다.

- [0383] 도 33 내지 도 40의 배치 구조들의 경우, 제1 터치 라우팅 배선들(X-TRW)과 제2 터치 라우팅 배선들(Y-TRW) 모두가 공통전극(CE)과 중첩되지 않는다. 이를 통해, 네로우 베젤 구현을 용이하게 하고, 공통전극(CE)과 터치 라우팅 배선들(X-TRW, Y-TRW) 사이에 기생 캐패시턴스가 형성되는 것을 방지해주어 터치 감도를 향상시켜줄 수 있다. 아래에서 더욱 상세하게 설명한다.

- [0384] 터치표시장치의 터치센서는, 표시영역(AA)에서 봉지층(ENCAP) 상에 배치되는 n개의 제1 터치전극 라인(X-TEL)과 m개의 제2 터치전극 라인(Y-TEL)을 포함할 수 있다. 여기서, n개의 제1 터치전극 라인(X-TEL)과 m개의 제2 터치

전극 라인(Y-TEL) 각각은 1가지 이상의 터치센서메탈을 포함할 수 있다.

- [0385] n개의 제1 터치전극 라인(X-TEL)에 대하여 싱글 라우팅 구조를 갖고, m개의 제2 터치전극 라인(Y-TEL)에 대하여 싱글 라우팅 구조를 갖는 경우, 터치표시장치의 터치패드 부(TPA)는, 표시영역(AA)의 외곽 영역인 비-표시영역(NA) 중 표시영역(AA)으로부터 제1 방향으로 외곽에 위치하는 제1 비-표시영역(NA1)에 배치되며, n개의 제1 터치패드(X-TP) 및 m개의 제2 터치패드(Y-TP)를 포함할 수 있다.

- [0386] 터치표시장치는, n개의 제1 터치전극 라인(X-TEL)에 대하여 성글 라우팅 구조를 갖는 경우, 봉지층(ENCAP)의 경 사면을 따라 내려와, n개의 제1 터치전극 라인(X-TEL)을 제1 비-표시영역(NA1)에 배치된 n개의 제1 터치패드(X-TP)와 전기적으로 연결해주는 n개의 제1 터치 라우팅 배선(X-TRW)를 포함할 수 있다.

- [0387] 터치표시장치는, m개의 제2 터치전극 라인(Y-TEL)에 대하여 싱글 라우팅 구조를 갖는 경우, 봉지층(ENCAP)의 경사면을 따라 내려와, m개의 제2 터치전극 라인(Y-TEL)을 제1 비-표시영역(NA1)에 배치된 m개의 제1 터치패드(X-TP)와 전기적으로 연결해주는 m개의 제2 터치 라우팅 배선(Y-TRW)을 포함할 수 있다.

- [0388] n개의 제1 터치 라우팅 배선(X-TRW)은 표시영역(AA)으로부터 제2 방향의 반대 방향으로 외곽에 위치하는 제3 비-표시영역(NA3)을 지나갈 수 있다. 제3 비-표시영역(NA3)을 지나가는 n개의 제1 터치 라우팅 배선(X-TRW)은, 터치센서메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW)과, 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제1 터치 라우팅 배선(X-TRW)을 포함할 수 있다.

- [0389] m개의 제2 터치 라우팅 배선(Y-TRW)은 표시영역(AA)으로부터 제2 방향으로 외곽에 위치하는 제2 비-표시영역 (NA2)을 지나갈 수 있다. 제2 비-표시영역(NA2)을 지나가는 m개의 제2 터치 라우팅 배선(Y-TRW)은, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)과, 터치센서메탈과 다른 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)을 포함할 수 있다.

- [0390] 제1 메탈은 터치센서메탈과 다른 메탈로서, 1가지 이상을 메탈을 포함할 수 있다. 예를 들어, 제1 메탈은, 표시 영역(AA) 내 배치된 트랜지스터들(T1, T2 등)의 소스 및 드레인 전국이나 표시영역(AA) 내 데이터 라인(DL)에 포함되는 소스-드레인 메탈과, 표시영역(AA) 내 트랜지스터들(T1, T2 등)의 게이트 전국이나 게이트 라인(GL)에 포함되는 게이트 메탈 중 1 가지 이상을 포함할 수 있다.

- [0391] 전술한 바와 같이, 제1 메탈이 소스-드레인 메탈 또는 게이트 메탈을 포함하는 경우, 제1 메탈이 포함된 하나이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 1개의 층에 배치될 수 있다. 이와 다르게, 제1 메탈이 소스-드레인 메탈과 게이트 메탈을 모두 포함할 수도 있다. 이 경우, 제1 메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_SD)은 2개의 층에 나누어져 배치될 수 있다.

- [0392] 터치센서메탈은 전극 메탈과 브릿지 메탈 중 1 가지 이상을 포함할 수 있다. 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)은, 전극 메탈 및 브릿지 메탈 중 하나의 터치센서메탈을 포함하는 경우, 1 개의 층에 배치될 수 있다. 이와 다르게, 터치센서메탈이 포함된 하나 이상의 제2 터치 라우팅 배선(Y-TRW\_TSM)은, 2가지 터치센서메탈(전극 메탈 및 브릿지 메탈)을 모두 포함하는 경우, 2개의 층에 나누어져 배치될 수 있다.