## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第6176869号 (P6176869)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日 (2017.7.21)

| (51) Int.Cl. |       |           | FΙ   |       |             |

|--------------|-------|-----------|------|-------|-------------|

| HO1P         | 11/00 | (2006.01) | HO1P | 11/00 | $1 \ 0 \ 1$ |

| HO1Q         | 21/06 | (2006.01) | HO1Q | 21/06 |             |

| HO1Q         | 13/02 | (2006.01) | HO1Q | 13/02 |             |

| HO1Q         | 23/00 | (2006.01) | HO1Q | 23/00 |             |

請求項の数 21 (全 23 頁)

(21) 出願番号 特願2015-561339 (P2015-561339) (86) (22) 出願日 平成26年1月8日 (2014.1.8) (65) 公表番号 特表2016-516327 (P2016-516327A)

(43) 公表日

平成28年6月2日 (2016.6.2)

(86) 国際出願番号

PCT/US2014/010618

(87) 国際公開番号 W02014/137484 (87) 国際公開日 平成26年9月12日 (2014.9.12) 審査請求日 平成27年12月2日 (2015.12.2)

(31) 優先権主張番号 61/775,451

(32) 優先日 平成25年3月8日(2013.3.8)

(33) 優先権主張国 米国 (US) (31) 優先権主張番号 61/775, 454

(32) 優先日 平成25年3月8日 (2013.3.8)

(33) 優先権主張国 米国(US)

||(73)特許権者 514145729

ノースロップ グルマン システムズ コ

ーポレーション

NORTHROP GRUMMAN SY STEMS CORPORATION アメリカ合衆国 バージニア州 2204 2-4511 フォールズ チャーチ フェアビュー パーク ドライブ 2980

|(74)代理人 100082072

弁理士 清原 義博

(72) 発明者 チャン,チュンボ

アメリカ合衆国 90266 カリフォル ニア州 マンハッタン・ビーチ アビエー

ション・プレイス 307

最終頁に続く

## (54) 【発明の名称】 導波路および半導体パッケージング

## (57)【特許請求の範囲】

## 【請求項1】

サブミリメートル波長(SMMW)デバイスを製造する方法であって、該方法は、

1 つ以上の D C スルーバイアスを含むように第 1 ウエハをバッチ処理する工程、

前記第1ウエハの上部表面に1つ以上の半田・バンプを堆積する工程、

前記半田・バンプと整列した 1 つ以上の空胴を作るために第 2 ウエハをバッチ処理する工程、

前記第2ウエハの下部表面を前記第1ウエハの上部表面と接合する工程、

モノリシックマイクロ波集積回路(MMIC)チップを形成するために半導体材料の1つ 以上の第3ウエハをバッチ処理する工程、及び

前記1以上の第3ウエハを個々のMMICチップへと方形切断する工程、及び

前記1以上のMMICチップを前記第2ウエハの空胴に設ける工程

## を含み、

<u>前記第2ウエハの1以上の空洞と整列した1以上のアンテナを形成するために第4ウエハ</u>をバッチ処理する工程、及び

前記第4ウエハを前記第2ウエハの上部表面と接合する工程を更に含む

ことを特徴とするサブミリメートル波長(SMMW)デバイスを製造する方法。

#### 【請求項2】

前記1以上のアンテナがホーンアンテナである請求項1に記載の方法。

#### 【請求項3】

前記第1、第2及び第4ウエハがウエハスケール・アセンブリ(WSA)技術を使用して 組み立てられる請求項1に記載の方法。

#### 【請求項4】

前記第2ウエハの空胴が導波路を含む請求項1に記載の方法。

## 【請求項5】

前記第1ウエハがGaAsであり、前記第2及び第4ウエハがシリコンであり、前記第3 ウエハがIII - V半導体材料である請求項1に記載の方法。

## 【請求項6】

前記MMICが動作可能性に関してテストされ、公知で良好なチップのみが前記第2ウエ 八の空洞に設けられる請求項1に記載の方法。

10

20

## 【請求項7】

前記MMICが能動的な回路類を含んでいる請求項1に記載の方法。

#### 【請求項8】

前記MMICが均質でない材料とプロセスを使用して製造される請求項6に記載の方法。

## 【請求項9】

前記MMICチップに電気的な相互連結を提供するために、半田・バンプが前記DCバイ アスに整列される請求項1に記載の方法。

## 【請求項10】

サブミリメートル波長(SMMW)焦点面配列(FPA)用の画素であって、

DCスルーバイアスと該DCスルーバイアスと整列する半田・バンプを含むチップ・イン ターフェース、

前記チップ・インターフェースの上部表面上の半田・バンプと整列する1つ以上の空胴を 含む導波路、

前記導波路の空胴に挿入された1つ以上のモノリシックマイクロ波集積回路(MMIC) チップ、及び

前記導波路の空胴の少なくとも1つと整列したアンテナを含み、

そこでは、SMMW信号はアンテナによって受け取られ、前記導波路の空胴を通して送信 され、前記MMICチップによって処理される画素。

## 【請求項11】

前記チップ・インターフェースがウエハと前記導波路から製造され、アンテナは1つ以上 のウエハから製造される請求項10に記載の画素。

30

## 【請求項12】

前記チップ・インターフェース・ウエハおよび前記1つ以上の導波路およびアンテナ・ウ エハがウエハスケール・パッケージング技術を用いて集積される請求項11に記載の画素

# 【請求項13】

前記アンテナがホーンアンテナである請求項10に記載の画素。

## 【請求項14】

前記MMICチップにおいて、1つ以上の低ノイズ増幅器(LNA)および1つ以上のダ イオードを含む請求項10に記載の画素。

40

50

## 【請求項15】

前記チップ・インターフェース、前記導波路、前記アンテナおよび前記MMICチップが 各々別々に製造される請求項10に記載の画素。

## 【請求項16】

前記MMICが動作可能性に関してテストされ、公知で良好なチップのみが前記導波路の 空胴に入れられる請求項10に記載の画素。

#### 【請求項17】

第1層であって、該第1層の一方の側から他方の側まで複数の電気的導通を含む第1層、 前記第1層の電気的導通と整列した複数の導波路空胴を含む第2層、

前記複数の導波路空胴に挿入され、前記第1層の電気的導通と動作可能に接続された複数

のモノリシックマイクロ波集積回路(MMIC)チップ、及び

複数のアンテナを含む第3層であって、該複数のアンテナが前記複数の導波路空胴に整列 する複数のアンテナを含むサブミリメートル波長(SMMW)焦点面配列(FPA)。

#### 【 請 求 項 1 8 】

前記MMICチップが低ノイズ増幅器(LNA)およびダイオードをさらに含む請求項1 7 に記載の F P A。

#### 【請求項19】

前記第1、第2、第3層および前記MMICチップが各々別々に作り上げられる請求項1 8 に記載の F P A。

#### 【請求項20】

前記MMICチップがIII-V半導体材料から製造され、前記第1、第2及び第3層が バッチ処理される請求項18に記載のFPA。

#### 【 請 求 項 2 1 】

前記第1、第2及び第3層がウエハスケール・アセンブリ(WSA)技術を用いて組み立 てられる請求項17に記載のFPA。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

<政府の権利の陳述>

この発明は、国防省高度研究プロジェクト庁によって与えられた契約番号W911QX-C - 0 0 6 6 の下で、政府支援でなされた。政府はこの発明における権利を有している。

この出願は、2013年3月8日に申請された「WAVEGUIDE AND SEMI CONDUCTOR PACKAGING」と題する米国仮出願第61/775,451 号、及び2013年3月8日に申請された「DEEP TRENCH WAFER TTERNING」と題する米国仮出願第61/775,454号の優先権を主張する。

## 【背景技術】

[0002]

昨今の電子をベースにした画像システムは、電波望遠鏡とディジタルカメラを含む広く様 々な用途を有している。これらのデバイスは、複合画像を形成するために非常にハイ・レ ベルで電磁放射の波長を処理する。そのような撮像デバイスで使用される共通機器は個々 のアンテナの焦点面配列(FPA)、あるいは画素である。画像を形成するために、FP Aは、電磁スペクトルの全体にわたって放射を組み合わせる。

#### [0003]

個々のアンテナ素子からの信号が所望のビーム又は画像を形成するために合成されるフェ イズドアレーとして、FPAはしばしば実装される。多数のビームの形成のような高度な フェイズドアレー・アプリケーション、より大きく距離が増加した分解能、及び画像シス テムのための縮小したサンプリング時間は、アンテナの数を増加させること、あるいはフ ロントエンド・エレメント計算により達成される。大きな配列が実現されるために、有利 な大きさの範囲内で全面的にデバイスを維持するように寸法、重量およびコストの低減に よるエレメント計算の増加を補うことは望ましい。より高い周波数(より小さな波長)で フェイズドアレーを操作することは、常に減少する波長をもつ素子のスケーリングの利用 によって寸法と重量の低減化が当然可能になる。これは高周波モノリシックマイクロ波集 積回路(MMIC)の相対的な寸法で実証されているが、この利益はフェイズドアレー・ システムには大部分は実現されなくなった;回路の寸法は減少しているが、分離したブロ ックの導波路ハウジングの固定された外観は総合システム寸法の低減化に結びついていな い。機械的なピン、フランジ結合および直流バイアスは、分離したブロックのパッケージ の寸法を 2 0 0 - 7 0 0 G H z からおよそ 1 i n 3 で、大雑把には周波数一定のままにさ せた。

[0004]

50

20

10

30

20

30

40

50

低いミリメートル波、サブミリ波およびTHz周波数で作動するソリッドステート集積回路の最近のデモンストレーションは、これらの周波数で作動する画像システムを予見することに向けた推進力を提供した。

#### [0005]

サブミリメートル波長(SMMW)画像システムにはスモーク、フォグおよびダストのような大気中の遮蔽物を介して画像を監視するために使用される可能性がある。SMMWデバイスは0.3~3テラヘルツ(THz)の周波数で作動する。その非常に短い波長により、テラヘルツ放射は、衣類、紙、ボール紙、木材、石細工、プラスチックおよびセラミックスを通り抜けることができる。これは、遠隔の隠された武器および改善された起爆装置(IED)の離散的な検波を提供する画像システムのためにそれを理想にする。

## [0006]

現在の S M M W 画像システムは寸法と電源消費により戦場か空中輸送される適応には役に立たない。一例では、 1 0 4 0 の素子を持ったWバンド( 7 5 - 1 1 0 ギガヘルツ) F P A を使用し、 1 4 , 0 0 0 m m  $^2$  の全ダイ領域の寸法と、 2 5 0 W の直流( D C )所要電力、 1 5 1 b s のパッケージ重量の 2 5 0 c m  $^2$  の寸法をもち得、水冷を要求し得る。 S M M W 画像システムは望ましいが、寸法は携帯用のシステムのような多くのアプリケーションには大きすぎる。

#### [00007]

システムオペレーションの周波数での波長のオーダーのアンテナ素子間隔は、高周波コンパクト・アンテナアレイには望ましい。標準的な導波路ブロックはこれらのターゲットを満たすのに不十分である。 S M M W アプリケーションに使用されるものなど高周波の小型化見込みを満たすことができる技術は、ウエハレベル・パッケージング(W L P)の技術それであり、異なるウエハ基板の全ウエハの接合により小さく稠密なパッケージのためにウエハ(例えばシリコン、ガラスあるいは水晶ウエハ)のエッチングされた導波路を備えるとともに異なる有効な技術をもたらす場合がある。従来のウエハレベル・パッケージングでは、有効な導波路ウエハ全体は3次元の集積構造を作成するためにともに接合される

#### [00008]

ウエハレベル・パッケージング(WLP)の以前の進歩は、小型で軽量で、低損失、かつ 高回路性能のために組み合わせられる、導波路ウエハおよびマイクロ波モノリシック集積 回路(MMIC)ウエハを可能にした。マイクロ波振動数からWバンドまで、およびTH z 周波数付近の成功にもかかわらず、堅牢で低価格のプロセスへのこの種の集積化を拡張 するいくつかの基本的な挑戦が残っている。最初に、導波路領域を提供するために、MM ICウエハ・領域は、MMIC回路に完全には使用されず、それゆえ、SI導波路への能 動回路を整列させるために主として充てん剤として使用される高価なIII-V半導体の 一部を浪費する。MMIC回路面積がWG面積より通常、はるかに小さいので、ウエハ中 の回路/細砕石の数は規則的なMMICウエハより著しく低い。次に、デバイスの歩留ま りは、各ウエハ層の歩留まりの製品に直接リンクされ、それゆえMMICの歩留まりが低 い場合に非常に影響される。機能的な低ノイズ増幅器(LNA)が機能を持たないダイオ ードと整合される場合、全回路は機能を持たない。回路の歩留まりがより困難になり、試 験がより高価になるより高い周波数でこの問題は厄介になる。第三に、WLPアプローチ において、デバイスが多数の技術がともに集積されることを必要とする場合、ウエハ層の 数が増加し、デバイスの歩留まりは、増加する層および集積化の複雑さを伴って急速に減 少する。

## [0009]

サブミリメートル波長のWLPのための追加のハードルは、必要なデバイス密度を達成するのに必要な半導体製造工程で見出だされる。半導体素子を製造する際に使用される共通の技術は、例えば、半導体ウエハの処理および(または)パターニング中のホトレジスト(PR)の使用を含む。ウエハは、当業者に知られたシリコン、III-V化合物、II-VI化合物などのような材料から形成され得る。湿ったホトレジスト(湿ったPR)は

20

30

40

50

一般に使用されるが、多くの場合ディープトレンチを含むウエハのパターニングに不適切である。例えば、トレンチ深さがおよそ30-50μmに増加すると、湿ったPRは許容可能な結果で処理するのがより難しくなる。

#### [0010]

湿った P R プロセスを使用する場合、様々な問題が存在するかもしれない。一例において、サイドウォールおよび(または)トレンチの底は完全に次工程にそれらを露出しておく湿った P R によってカバーされるのが難しい。いくつかの技術は、トレンチ深さが約30-80μmに近いか、或いは30-80μm未満であると、これらの問題を緩和するのを支援するかもしれない。これらの技術の例は多数の湿った P R 田 射線量および開発を含んでいる。しかしながら、これらの技術でさえ、正確なパターンおよび小さな特徴を定義するのは難しいかもしれない。

[0011]

湿ったPRを備えた別の問題は一様でないPR厚さである。湿ったPRは、回転コーティング工程で典型的に適用される。しかし、これは一般に特にトレンチのエッジの近くで一様でない厚さに帰着する。湿ったPR厚さは、カバー場所およびPR厚さの間の不規則か予測不能の関係をもつ他の領域において厚すぎる一方で、いくつかの領域において薄すぎるかもしれない。PRが薄すぎるところで、長い露光或いは多重露光の後にパターンは精度を容易に失う。PRが厚すぎると、完全にPRを現像するのは難しい。

[0012]

最後に、非常に厚い湿ったPRは「パイル・アップ(pile-up)」するかもしれない、特に多数の湿ったPRコーティングが使用される場合いくつかの領域で「パイル・アップ(pile-up)」し得る。このパイル・アップは、多数のPR照射および現像によってさえ湿ったPRを現像することを非常に困難にする。パイル・アップは、さらに正確で小さな特徴を定義することを困難にする。

【発明の概要】

【発明が解決しようとする課題】

[0013]

これらの問題に取り組むために、マイクロマシン(micromachin)処理された 導波路「パッケージ」へ個々のIII・V MMICを集積することに依存する新しい集 積化スキームが必要である。

【課題を解決するための手段】

[0014]

この方法を使用して、III・V MMICは集積化に先立ってDCスクリーニングされ得、既知の良好なダイだけを集積化することができ、増加した歩留まりへと導く。この集積化方法は、さらに多重ウエハWLP集積化でのような集積化と同じ技術レベルを達成する、マイクロマシン処理されたパッケージに集積される異なる技術のMMICを可能にする。

[0015]

330-350GHzのマイクロ集積される焦点面配列(mFPA)技術の様々な実装が、本明細書に記載され、それは戦場使用およびシステム増強のためのSMMWカメラの新しい世代を可能にする。開示された技術を使用する330-350GHzの実装は、コンパクトな携帯用の開口を可能にして、水冷の必要性の除去に加えてWバンドと比較して、13Xまで焦点面寸法の減少、および25XまでDC電力消費の減少を可能にする。さらに、この短い波長のためのフォトリソグラフィーおよびダイ寸法のスケーリングは、単位原価を下げるためにほぼ28Xのダイ領域の低減を可能にする。

[0016]

本明細書に記載された実装はマイクロ集積された焦点面配列と関係があるが、当該技術は他の多くのウエハ組立てアプリケーションに適用可能である。マイクロ集積化は、高周波システムの小型化を可能にする場合があり、小さく稠密なパッケージへ異なる技術およびアンテナを組み合わせることができる。これは、サブミリメートル波長周波数(焦点面配

列、有効な撮像、サブmmレーダー)用新製品を可能にする。画像システムに適用された時、マイクロ集積された画素は高周波撮像、通信およびセキュリティー・システムのための大きな2D配列を可能にする。

[0017]

高周波は全面的な光学系、カメラおよびエレクトロニクスの寸法を縮小する。SWaP低減(寸法、重量および電力低減)は、多数のプラットホーム上の劣悪な視環境の撮像を可能にする。狭いビーム幅と制限された検出器アベイラビリテイはLPI/LPD通信リンクを可能にする。マイクロ集積された画素の2D配列は、より遅い単一画素ラスタースキャンの代わりに動的な場面撮像、およびリアルタイム撮像を可能にする。縮小されたSWaPは、リアルタイム群衆監視および武器検波用のフィールド携帯撮像装置を可能にする

10

【図面の簡単な説明】

[0018]

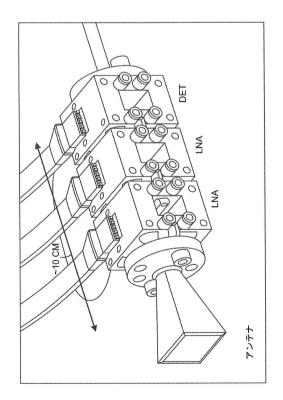

- 【図1】図1は、焦点面配列の単一画素についての先行技術の図を示している。

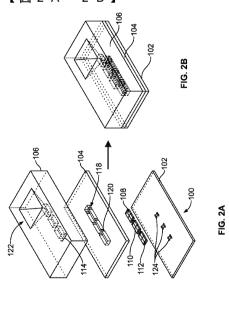

- 【図2A】図2Aは、焦点面配列の単一のマイクロ集積された画素を示している。

- 【図2B】図2Bは、図2Aの3つのウエハすべての合成図を示している。

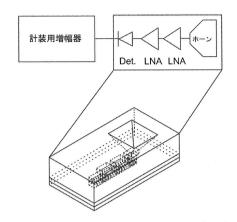

- 【図2C】図2Cは、図2Aの3つのウエハすべてについての別の図を示している。

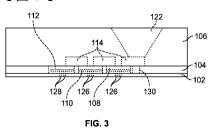

- 【図3】図3は、単一のマイクロ集積された画素の側面図を示す。

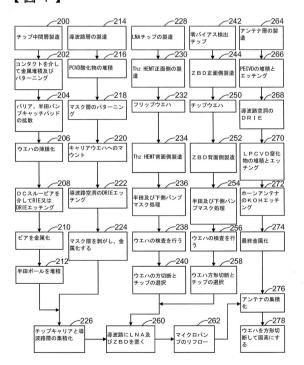

- 【図4】図4は、図2Aの単一のマイクロ集積された画素を製造することに含まれる工程を例証するフローチャートである。

20

30

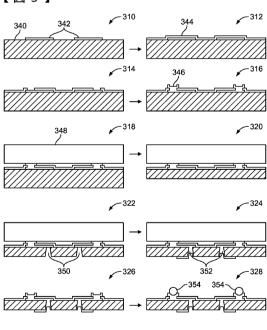

- 【図5】図5は、図4のフローチャートの様々な工程間に図2Aの画素のチップ・インターフェースを図式化して表している。

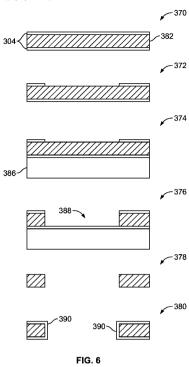

- 【図6】図6は、図4のフローチャートの様々な工程間に図2Aの画素の導波路層を図式化して表している。

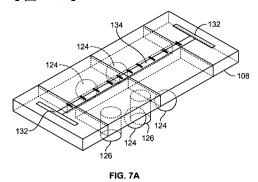

- 【図7A】図7AはLNAチップを示している。

- 【図7B】図7Bは、図2Aの画素中の導波路とLNA/ZBDチップの間の遷移状態を示している。

- 【図8】図8は、図4のフローチャートの様々な工程間にMMICチップとのチップ・インターフェースおよび導波路層の集積化を図式化して表している。

- 【図9】図9は、図4のフローチャートの様々な工程間に図2Aの画素のアンテナ層を図式化して表している。

- 【図10】図10は、図2Aの画素の全アセンブリを図式化して表している。

- 【図11】図11は図2Bの中で示されるような多くのmFPA画素を指名している。

- 【図12】図12は、基板への乾燥したホトレジストの適用のためのシステムを図式化して表している。

- 【図13】図13は、乾燥したホトレジストを使用して、ディープトレンチをパターニングすることに関与する工程を例証するフローチャートである。

- 【図14】図14は、乾燥したホトレジストを使用して処理されたウエハを示している。

- 【図15】図15は、さらなる処理後の図14のウエハを示している。

【発明を実施するための形態】

40

[0019]

マイクロ集積化の技術は、マイクロマシン処理(micromachined)されたホーンアンテナおよび導波路を含む  $3\,3\,0$  -  $3\,5\,0\,G\,H\,z$  の受信器・画素、  $1\,0$ 以上の  $I\,n\,P\,H\,E\,M\,T\,L\,N\,A$  チップおよび  $n\,I\,N$  ダイオード検波器を製造するために使用された。開示された技術は  $2\,D\,P\,U$  イと単一のマイクロ集積された画素の両方を製造するために使用することができる。比較については、図  $1\,U\,C\,C$  にごれるような分割ブロックパッケージに従来のやり方でパッケージにされた  $3\,3\,0$  -  $3\,5\,0\,G\,H\,z$  の画素は、大雑把には  $1\,0\,x\,3\,x\,3\,c\,m^3$  であり得、その一方で記載されているようなマイクロ集積された画素の一例はほぼ  $0\,.\,5\,x\,0\,.\,5\,x\,0\,.\,1\,4\,c\,m^3$  であり、容積縮小は  $2\,5\,0\,0$  の因数より大きい。更に、開示されたマイクロ集積された画素・ボリュームは、多数の設計に使用することが

20

30

40

50

できるマスクレイアウトを利用する。もっと最適化されたマスクレイアウトの使用により さらに3X容積縮小が達成されうる。

## [0020]

< 1. 概観 >

本明細書に記載されるように、シリコンあるいは他のウエハ(例えばグラス)は両方とも 、ウエハスケール・パッケージングによるパッケージとして使用されることができ、また さらに多数のチップのために相互に連結する導波路として使用され得る。多数のシリコン ウエハは受動的シリコン導波素子を形成するために組み合わせることができる。チップが 導波路とは別々に形成されるので、異なる組立て技術がチップとパッケージングに使用す ることができる。例えば、III・Vウエハから特定化されたチップは、シリコン・パッ ケージおよび導波路内で集積されうる。チップは、半田ボール、マイクロバンプ、半田マ イクロバンプあるいは銅のマイクロバンプを使用して、シリコン・パッケージと動作可能 に結合され得る。マイクロバンプはアメリカ合衆国オレゴン州、ポートランドにて201 0年5月17日 - 20日開催のCS MANTECHConferenceでのX.Ze ng氏の「Wafer Level Bump Technology For - V MMIC Manufacturing」に開示され、その内容が参照によって組 込まれる。半田ボールはスルー・ウエハ(thru-wafer)を使用して、パッケー ジの外部に電気的なDC接続を提供し得る。一実施例において、銅のマイクロバンプは半 田キャップを備えた 5 0 μ m の銅めっきを使用して形成される。半田ボールの様々な寸法 が可能であるが、本明細書に開示された実装は、3milの半田ボール、あるいは随意に 5 milの半田ボールに基づく。これらの特徴は、様々な活性技術の集積化およびさらに 既知の良好な活性を有するダイの使用を考慮に入れることを可能にする。

[0021]

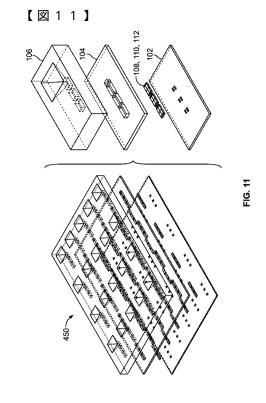

図2 A を参照すると、焦点面アレイの単一のマイクロ集積された画素の概観は、デバイス (100)として示される。デバイス (100)は複数のウエハ (102)、 (104) および (106)と、集積回路チップ (108)、 (110)、 (112)を含む。ウエハと集積回路チップは、その後、以下に述べられた技術を使用して、導波路スタックに個々に組み込まれ得る。単一の画素は図2 A に示されるが、適切なレイアウトで配列されれた多数の画素を含むウエハに層 (102)、 (104)および (106)のために以下に記載される製造プロセスが適用することが理解される。

[0022]

一実施例において、層(102)はチップ中間層として機能する。この層はDCスルーバイアスと出力(図示せず)を含んでいる。半田ボール、あるいはマイクロバンプ(124)は、チップ(108)、(110)および(112)のアタッチメントのためにチップ中間層(102)に置かれる。

[0023]

層(104)は導波路層として機能し、電磁気信号の進行用に導波路(114)を提供するのに適した空胴(118)および(120)を含んでいる。層(106)アンテナ層として機能する。図2Aに示される実装では、導波路(114)は、導波路層(104)および示されるようなアンテナ層(106)の両方の空胴によって形成される。代替の実装では、導波路(114)は、完全に導波路層(104)、内に形成されるか、あるいはチップ中間層(102)内に形成されるか若しくは両方に形成され得る。導波路(114)用の追加の中間の空胴は、チップ中間層(102)とキャップ層(106)の間に追加のウエハを加えることにより形成され得る。別の代替の実装では、導波路層(104)は省略され、導波路(114)はチップ中間層(102)からだけ、アンテナ層(106)からだけ、又はチップ中間層(102)とキャップ層106の両方の組合せから形成される

[0024]

一実施例において、集積回路チップ(108)、(110)および(112)は、モノリシックマイクロ波集積回路(MMIC)を含む。一実施例におけるチップは導波路(11

20

30

40

50

4)の内部に位置する個別化されたチップである。図2Aに示されるように、集積回路チップは2つの低ノイズ増幅器(LNA)チップ(108)、(110)および零バイアス検出器(ZBD)チップ(112)を含む。一実施例において、増幅器(108)および(110)は低ノイズ増幅器を含む。代替の実装では、増幅器(108)および(110)は単一のLNAあるいは他の増幅器構成として組み合わせられ得、そうでなければ形成され得る。増幅器(108)および(110)は検出器(112)あるいは追加の集積回路(図示せず)と組合せられ得る。チップも、例えば、追加チップ部品特徴あるいは能力を提供するために分割されるかもしれない。例えば、多数の低ノイズ増幅器は、デバイス(100)のために十分な利得を提供するために直列又は並列で設けられうる。別の実施例において、増幅器と検出器はシングルチップへ組み合わせられ得る。

[0025]

図2 B は、それらが単一の画素を形成するためにともに接合された後の3つのウエハすべてについての合成図を示す。寸法は1つの可能な実施例の代表であるが、他の寸法が達成され得る。

[0026]

図2 Bの構造の電気回路図は、図2 Cで示される。 S M M W 放射はホーンアンテナによって受け取られ、1組の低ノイズ増幅器によって増幅されて、次に、補足計装および処理装置に出力される前に例えばショットキー・零バイアス検出器によって検知される。 2 つの L N A チップおよび検出器の選択は、検出器が十分に高い応答を有する低減された利得をもつ L N A を使用するような所望の特性に基づき得る。代替的に、1 つ以上の高い利得の L N A がより低い応答を検出器に与えるために使用されてもよい。一つあるいは複数の L N A のいずれかがより高い利得ファクタを提供するために使用されるかもしれない。デバイス 1 0 0 の代替の実装は追加チップ部品を使用し得る。

[0027]

図3は、本発明の一実施形態の側面図を示す。チップ中間層(102)はDCスルーバイアス(126)を含み、LNAチップ(108)と(110)の後ろでDCパッドに結合される。ZBD(112)からの出力は128で示される。導波路層(104)はチップ(108)、(110)および(112)の保持するためにポケットを含んでいる。導波路層(104)は、さらにアンテナ(122)からLNA(108)に信号を伝えるために工程・トランジション(130)を含んでいる。アンテナ層(106)は導波路(114)およびアンテナ(122)を含んでいる。

[0028]

ついでウエハはそれぞれ、個々にウエハスケール・アセンブリ(WSA)技術を使用して組み合わせられる。各層の組立ては別々に処理され、ついで完全な画素・パッケージへのMMICチップによる集積化が説明される。完全な画素・パッケージの組立ての概観は図4に示される。

[0029]

< 2 . チップ中間層組立て>

図 2 Aのチップ中間層(102)の組立ては、図 5 と共に工程(200)で始まる図 4 のフローチャートの最初のカラムに関して記載される。それは、組立ての様々な工程の間にグラフでチップ中間層を表す。図 4 の工程(202)では、チップ中間層(102)の組立ては、図 5 において(310)で示されるように砒化ガリウム(GaAs)(340)の層から始まる。好ましい実施形態では、GaAs層(340)は厚さ500-600μmで、100μmの厚さまで薄くなる。工程(202)を継続し、DCルーティントレース(342)は GaAs 層 340の上部表面にパターニングされる。

[0030]

図4の工程(204)で、誘電体層(窒化ケイ素など)(344)は(312)で加えられ、例えば、(314)で・リアクティブイオンエッチング(-RIE)を使用してエッチングした。その後、半田ボールのための拡散バリアパッド(346)は(316)で加えられる。パッド(346)は金属で作られ、半田ボールとDCルーティントレース(3

42)間の接続を提供する。

## [0031]

図5の工程(206)を参照すると、(320)で描かれた、ウエハ薄化プロセスでチップ中間層を支援するために、サファイア・サポート層(348)は図5の(318)で描かれる。

## [0032]

図4の工程(208)で、DCスルーバイアス(350)は、図5の(322)で描かれた、GaAs層(340)の後部からエッチングされる。DCスルーバイアス(350)は、図2Aのチップ(108)、(110)および(112)のためのDCルーティントレースの背部に直流バイアスを供給する。図4の工程(210)で、バイアス(350)は、例えば図5の(324)に描かれるようなスパッタリングプロセスで金属化される。

[0033]

最後に、図4の工程(212)で、サファイア層(348)は除去された(326)で、 半田ボール(354)は、図5の(328)で示されるような上部表面に置かれる。好ま しい実施形態では、半田ボールは直径3milである。代替の実装では、半田ボールは、 中間層の代わりにMMICチップの背部に置かれる。

#### [0034]

< 3 . 導波路層組立て >

図2 A の導波路層(104)の組立ては、図6と共に工程(214)で始まる図4のフローチャートの第2のカラムに関して記載され、それは、組立ての様々な工程の間にグラフ的に導波路層を表す。図4の工程(216)で、プラズマ助長の化学蒸着法(PECVD)酸化物(384)は、図6の(370)で示されるシリコンウエハ(382)の両面に置かれる。好ましい実施形態において、シリコンウエハ(382)は、およそ300 $\mu$ mと350 $\mu$ mの間の厚さを有している。代替の厚さは当業者に明白であり、所望のパラメータに基づき得る。図6の(372)で、シリコン層(382)の上部の酸化物は、例えば、図4の工程(218)に述べられているようなRIEプロセスを使用してエッチングされる。導波路層(104)の組立てに関する特定の詳細は、図12~15に関して以下に与えられるだろう。

## [0035]

図4の工程(220)で、導波路層は図6の(374)で示されるようなキャリヤ・ウエハ(386)にマウントされ、一方で例えば(376)で示されるようなDRIEプロセスを使用して工程222で導波路空胴(388)がエッチングされる。導波路層は導波路、ステップ・トランジションおよび(または)チップ空胴の1つ以上を提供するのに適し得る。

## [0036]

最後に、図4の工程(224)で(380)で示されるように、マスキング層は図6の描かれているように除去され、導波路空胴が金属化される。導波路サイドウォールの金属化は、1ミリメートル当たり0.2dB未満の低損失波動を考慮に入れる。

## [0037]

< 4 . L N A および Z B D 組立て概観 >

一般に、図2Aのチップ(108)、(110)および(112)の1つ以上は、GaAsまたはInPのようなIII・V半導体から形成され得る。代替のウエハ材料は当業者に明白であり、デバイス(100)で使用される各チップに対して同じである必要がない。LNAと検出器のチップのための特定の処理詳細は以下に議論されるだろう。一般に、ウエハの「正面側」の処理中に複数のチップを作成するために、1以上の「ホットビア(hot via)」相互連結が、それらの背部からチップの正面側にDCをもたらすために加えられるか、あるいは映像信号を提供する。

## [0038]

H E M T デバイス技術は I n A s 複合チャネル( I A C C )を調整するためにサブ 5 0 n m のトランジスター・ゲート長を提供する。この構造は最大発振周波数 f  $_{\rm MAX}$  > 1 . 4

10

20

30

40

THzおよび最大臨界周波数 f  $_{T}$  > 7 0 0 G H  $_{Z}$  を達成した。そのプロセスは、 6 0 0 p F / m m  $_{Z}$  の金属・絶縁体・金属(M I M ) コンデンサー、 2 0 および 1 0 0 / の薄膜抵抗体(TFR)、エアーブリッジオプションによる相互連結およびデバイス・パッシベーションなどの増加した使用周波数を支援するために受動素子を有している。ウエハは基板モードを抑えるためにコンパクトな背部バイアスで 5 0  $_{L}$  m まで薄くなる。

[0039]

<a . 低ノイズ増幅器(LNA)>

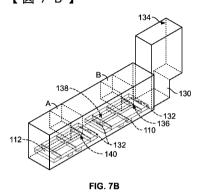

図2 AのLNAチップ(108)および(110)の組立ては、図7 Aおよび7 Bと共に工程(228)で始まる図4のフローチャートの第3カラムに関して記載されるだろう。図4の工程(230)では、組立ては、GaAsまたはInPのようなIII-V半導体の正面の横のTHz HEMTプロセスから始まる。その後、工程(232)では、背部THz HEMT組立てを行なうことができるように、ウエハはフリップ処理される。

[0040]

図7Aで示されるように、一実施例におけるLNAは共面の導波路134を使用し、導波路中に、および導波路から外に、トランジションエネルギーまでのオンチップの電磁気のダイポール(132)を使用する。好ましい実施形態は、空胴の内部で導波路層(104)に入るために、チップ・寸法は775μm×350μm未満に抑制される。それは、図7Aの(126)で示されたすべてのドレイン電圧およびゲート電圧のために単一のバイアス・パッドだけを各々許可する。330・350GHzの動作バンドを超える一方で、DC電力~15mWを消費している間、LNAは 15dBの利得と、<10dBのノイズ指数(NF)を達成する。

[0041]

本発明において実装されたLNAは例えば3段あるいは5段増幅器になりえる。3段増幅器は5段より少ない利得を提供する。しかしながら、特定の全利得は該システムに必要とされ、それゆえ2台の3段増幅器を必要とするが、この利得要求は1台の5段段増幅器だけにする。一般に、それがより少ないスペースを必要とするが、どんな構成も動作環境に会うために使用することができるので、単に1つの増幅器チップの使用は好ましい。一実施例におけるLNA(142)は5段の高利得LNAサブミリメートル波長モノリシックマイクロ波集積回路(S-MMIC)を含む。LNA寸法の主要な考察は、段数、所望の利得、インピーダンス・マッチング・ネットワークおよび振動抑制のためのバイパスコンデンサーである。半田ボールおよび(または)LNAの能動的な回路類へのダイシング損失を回避するために、スペーサー・ポストは使用されてもよい。さらに、十分なチップ個別化はスクライブ / 破壊条件を除去するために使用されてもよい。

[0042]

一実施例における L N A ( 1 4 2 )は 3 0 n m のリン化インジウム高電子移動度トランジスター ( H E M T ) を含む。 H E M T は一般に高い  $f_{max}$  を考慮に入れる。 L N A ( 1 4 2 )は導波路( 1 3 0 )への集積トランジションを提供するのに適している。 L N A ( 1 4 2 )の 1 つの実装のパッケージにされた性能を測定した。パッケージ利得は 3 2 0 から 3 5 0 G H z までで~ 1 7 d B であり、 N F < 8 . 8 d B であり、 L N A 直流電力 P  $_{d}$   $_{c}$  = 1 4 . 3 m W であり、トランジション毎の損失は~ 1 d B であった。

[0043]

さらに完成した 3 0 n m の I n P H E M T L N A が高い R F 収率 ( > 8 0 % ) と共に、3 3 0 G H z での利得およびノイズ指数 ( M M I C レベルで ~ 5 . 7 d B ) を示した。

[0044]

[0045]

10

20

30

5 つの利得段が単一のLNAに組み入れられる場合、所望の利得(例えば 3 0 d B ) は、 導波路および 2 つのオンチップ導波路トランジションの 5 0 の  $\mu$  mの長さを除去する間に 達成され得る。例えば、一実施例において、 5 つの利得段LNAは 4 3 0 × 2 7 5  $\mu$  m  $^2$  である。この寸法は 2 および 1 . 5 の間隔規則の両方を満たす。

## [0046]

一実施例において、LNA(108)、(110)の高い利得によって引き起こされた潜在的な振動を回避するために、損失のある抵抗性のフタ材は導波路(114)のフィードバックを最小限にするために導波路(114)の内表面に適用され得る。一実施例における損失のある抵抗性のフタ材はニッケル・クロミウムである。

## [0047]

図4の工程236では、その後、多くの背部処理工程はチップ中間層(102)までチップの粘着性を改善するために取ることができる。例えば、チップはそれらの背部にソルダマスクで置かれるか、あるいは拡散バリアを適用し得る。一実施例におけるソルダマスクは、図7Aにおいて124で示される半田材料(半田ボール)に封じ込めと画成を提供する。半田ボールの使用の1つの代わりとして、「マイクロバンプ」めっきが使用され得る。この場合、ソルダマスク堆積の後に続いて、アンダーバンプ・マスク(UBM)堆積が、2milのマイクロバンプめっきと共に行なわれ得る。一実施例におけるソルダマスクおよびUBM堆積はチップ中間層102上で行なわれる。使用され得る他のプロセスは、ビアエッチプロセス、背部金属化プロセスおよび半田パッドの準備のためのプロセスを含む。

#### [0048]

工程 2 3 8 では、製造されたウエハ上のチップが、それらの機能性を決定するために処理後にスクリーニング処理され得る。スクリーニング処理は「オンウエハ」あるいは方形切断の後に行われ得る。スクリーニング処理の後、チップは方形切断され、検査され、工程 2 4 0 でデバイス(1 0 0 ) との集積のために取られる。

## [0049]

< b . 導波路からチップまでの要素のつなぎ >

図7 Bに示されるように、LNAと検出器チップは集積された電磁遷移を使用して、DRIE形成された導波路に結合される。E-面プローブは、図1Aのホーンアンテナ(122)と図7 Bに示されるようなLNAチップ(110)との間に相互連結される。これは、稠密な集積化がコンポーネント同士の間隔を最小限にすることを可能にし、配列のスケーラビリティに不可欠である。MMIC間の距離は、コンパクトな画素寸法を実現し、かつ最小の相互連結損失を提供する。

## [0050]

一実施例における、ホーンアンテナ(122)とMMICチップとの間の相互連結は、導波路内の空胴を含む。代替の実装では、相互連結は導電接続を含み得る。図7Bの第1相互連結(130)は、90度の導波路曲りを含み、~1.2dBの挿入損失を有している。第2相互連結(132)は、~2.4dBの損失(導波路遷移までの2つのチップを含む)の損失を有している。一実施例における相互連結は、高い許容差の電磁的に結合された相互連結を含み、ボンド・ワイヤーおよび狭ピッチの相互連結の除去が増大した収率と一様性を可能にする。

# [0051]

高周波(>70GHz)では、電磁エネルギーを転送する方法としてワイヤボンドを使用する場合、MMIC増幅器は問題を示す。これらの周波数では、ワイヤボンドは、MMICを離調することができる重要な挿入損および非常に反応的なインピーダンスを与える。

## [0052]

相互連結(132)は能動的なMMICに直接集積される。したがって、それは、アセンブリの変化にそれほど敏感でなく、増加した収率および一様性に結びつく。相互連結(132)は、導波路へのMMICと電磁的に結合する。

## [0053]

10

20

30

< c . 零 - バイアス検波回路(ZBD))

図4の工程242乃至 258に示されるように、ZBDチップ(112)は同様にLN A チップに作り上げられる。好ましい実施形態では、 Z B D (112)は、マイクロ波及 びミリ波信号のバイアスされていないミクシング、逓倍及び直接の検波を提供するnIN 疑似ショットキーダイオードを使用する。一実施例において、検出器(112)は、検波 回路バイアスの必要をなくす「零バイアス・ダイオード」である。これは総合システムを 単純化し、システムノイズを低減する。ダイオードの一例はSawdaiらの(米国特許 第8,334,550号)に開示され、その内容は参照によって組込まれている。このア プローチでは、高濃度にドープした(InGaAsなどの)n+狭バンドギャップ層は、 標準的なショットキーダイオード中の陽極金属を交換する。したがって、有効なショット キーバリアは、 n + アノード層と最低値にドープしたカソード層の間のエピタキシアル成 長したヘテロ接合である。ヘテロ接合は所望のバリアの高さを生産するために調整するこ とができる、したがってダイオード・ターンオン電圧のチューニングを可能にする。最初 の結果は、n-I-N疑似ショットキーダイオードが、高周波に計量可能で、十分に零バ イアス検出器として使用のために0Vで整流して、容易に作り上げられることを実証した 。ダイオードは、520GHzまで、およびより好ましくは740GHzまでのしゃ断周 波数f~を提供する。これらのnINダイオードを使用するバイアスされていない直接の 検波回路は、195GHz(図20)で付帯的なRFのための> 3000V/Wの応答を 実証した。シミュレートされた検波応答は340GHzの入射RF信号のために~140 0 V / Wである。

[0054]

この n I N ユニポーラダイオードのエピタキシアル・スタックは、 n + 高濃度ドープ広バンドギャップ・サブカソード半導体膜、低濃度ドープ広バンドギャップ・カソード層及び n + 高濃度ドープ狭バンドギャップ・アノード層を含む。カソード層とアノード層の間の へテロ接合は導電バンドにおいて小さく、高品質の電子バリアを生成する。このバリアは 調整可能なターンオン電圧で電流の整流を生成する。一実施例において、 1 0 0 mmの I n P 基板上で格子整合した I n G a A s / I n A 1  $_{\times}$  G a  $_{1}$   $_{\times}$  A s 合金半導体が使用される。アノード層とカソード層中の材料の組成物は、低順方向のターンオン電圧を生成するように設計される。メサ型ダイオードは 1 乃至 1 0  $\mu$  m 2 の範囲の種々の領域で製造される。 L N A に似て、最終基板の厚さは 5 0  $\mu$  m  $\tau$  m  $\tau$  ある。

この n I N ダイオード技術はピーク ~ 2 7 V <sup>- 1</sup>、および 5 2 0 G H z までのしゃ断周波数を実証した。これらの新規な n I Nユニポーラ装置で達成される性能指数は、他の零バイアス・ショットキーダイオードと比較可能である。

[0055]

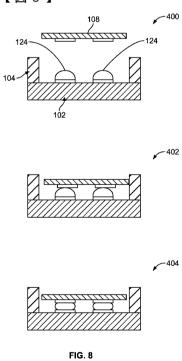

< 5 . チップキャリア/導波路組立>

図4の工程226で示されるように、マイクロ画素を組み立てる第1工程は、図8の400で示されるようなチップ中間層(102)に導波路層(104)を結合することを含んでいる。低温ボンディングプロセスは半田ボール(例えばインジウム・Auボンディング又はAu-Au熱圧着)への熱接触を最小限にするために使用される。

[0056]

ウエハのボンディング温度および表面の位相(topology)はマルチプルウエハ技術の集積のために適切なパラメータである。半田ボール・リフロー(後述する)温度は、ウエハボンディング間の半田リフローを防ぐ、ウエハボンディング温度より高くなければならない。一実施例において、インジウム・金のボンディング界面は、略183Cで溶融する半田を用いてウエハの接合のために使用される。インジウムは157Cで溶融し、インジウム・金ボンディングは180C(実際のボンディングでは170C)未満のボンディング温度を可能にする。代替の半田、ボンディング材およびボンディング方法は当業者には明らかである。層(102、104および106)の1つ以上は、ウエハボンディングを促進するために金および(または)インジウムでパターニングされる。

[0057]

10

20

30

40

ついで工程260で、個別化された公知のLNAチップとZBDチップが図8の402で示されたような導波路層(104)の空胴(388)(図6)に設けられる。チップ(108、110および112)は複数の半田ボール(124)によってチップ中間層102に結合される。一実施例における半田ボールは、取り付けられるチップに基づいて寸法が決められる。好ましい実施形態では、5mi1および3mi1の半田ボールが使用されるが、他の寸法も熟考される。チップ中間層(102)への全チップ列は空胴の境界によって画成され、およそ25μmである。空胴の寸法および(または)チップの形状は空胴内のチップ配置を促進するために調節され得る。例えば、形作られて、チップは長方形か、交差した形状、若しくは空胴の寸法はチップ配置を単純化するために増加され得る。ついで、マイクロバンプ・リフローは、約1乃至2μmの範囲までキャリヤパッドへのチップを自己整列し得る。

10

## [0058]

その後、図4の工程262では、チップが図8のうちの404で示されるような空胴内に マイクロバンプ自己整列のプロセスが半田リフローによって行なわれる。チップ中間層( 1 0 2 ) および導波路層(1 0 4 ) の第 1 ボンディング後のチップ・アタッチメントのた めの半田リフローは、損傷しないか、或いは中間層(102)および導波路層(104) のボンディングにずれを引き起こさない。一実施例において、第1ボンディングのIn‐ Au層は共融混合物 / 合金を形成し、再びリフローするだめにより高い温度を必要とする 。一実施例において半田リフローは所望の温度(例えばおよそ200C)で行なわれ、よ り低い温度が好ましい。一実施例における半田リフローは、ホールドタイム期間の間、所 望の温度で随意に保持して、所望の温度まで半田ボールを徐々に加熱(「ramp 」)し、その後、熱を下げる(「ramp down」)ことによって行なわれる。ラン プアップの期間、ホールドタイム期間、所望の温度、及びランプダウンは調節され得る。 一実施例において、ランプアップはおよそ1-2分である。2000はおよそ3秒間保持 される。また、ランプダウンはおよそ1・2分である。低い加熱発熱温度および短い加熱 期間は、一般に半田パッド中のバリア層を介して半田拡散を低減する。一例において、実 際のウエハ/チップボンディング時間はわずか2-10分であり、最大のランピングが使 用される。

20

## [0059]

30

チップ中間層102(表面上の高さ>50μm)の上の半田ボールのために、損害あるいは半田ボールへの変位を回避するために、最初のウエハボンディングはウエハアライメント中に十分な高さクリアランスを必要とする。ウエハアライメント中のより高い精度は、チップ108と110、112および導波路114の壁の間の間隔のリダクションを考慮に入れる。それは信号ロスを縮小する。一実施例において、SmartViewPライナー(85284アリゾナ州、テンペのEVGroup社)はほぼ1μmの整列精度を達成するために使用され得る。

[0060]

ந் - 40 3

半田は、容易に空気環境内で酸化され得る。酸化物は、液状の半田が別の要素(例えばチップ中間層(102)、チップ(108、110および112))によって湿り、接合部を形成するのを防ぐ。一実施例において、半田、ウエハあるいはチップは、半田リフロー直前に酸化物を除去するために液体フラックスを使用してすすがれる。一実施例におけるリフローは、例えばH2/Ar混合物で、抑制された空気環境中で行なわれる。

# [0061]

更なる実施形態において、マイクロバンプ自己整列は、銅スタッド上で増加した半田材料によって促進されるか、マイクロバンプ・寸法が増大する。キャリヤ・ウエハパッドに対する半田の湿潤性は、マイクロバンプ(MicroBump)のためにアンダーバンプ金属(UBM)の選択によって改善される。アンダーバンプ金属の例は、銅、金および半田キャップを備えた銅を含んでいる。アンダーバンプ金属(UBM)および半田マスク材料並びにボンディングパッド・寸法および間隔の選択は、半田リフロー中の自己整列の精度を決定する。上記の実装では、自己整列精度はおよそ1乃至2μmまでである。

20

30

40

50

#### [0062]

上述されるように導波路層を最初に接合する1つの利点は、それらが所定の位置に設けられるように、空胴サイドウォールがチップの粗い整列を提供することである。代替の実装では、LNAチップとZBDチップは、先ず中間層に置かれて接合され、ついで、導波路層が中間層に接合される。

#### [0063]

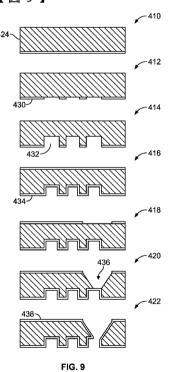

< 6 . アンテナ層の製造 >

図2 Aのアンテナ層(106)の製造は、図9と共に工程264で始まる図4のフローチャートの最後のカラムに関連して記載され、製造中の様々な工程の間にグラフ式にアンテナ層を表す。図4の工程266で、シリコンの1mmの厚さのウエハ(424)、例えばプラズマ強化化学蒸着法(PECVD)酸化物(430)は、図9の410で描かれるように、シリコンウエハ(424)の下側に成膜される。412で示されるように、酸化物(430)がエッチングされる。

## [0064]

図4の工程268で、導波路空胴は、例えば、図9の414で示されるようなDRIEプロセスを使用して、アンテナ層に形成される。図7の工程270で、低圧化学蒸着法(LPCVD)プロセスは、例えば、導波路サイドウォールを保護し、かつ図9の416および418で描かれるようなホーンアンテナ用のマスキング層を作成するように窒化物層(434)を設けるために使用される。さらに次の例において、熱酸化はLPCVD窒化物の代わりにホーンエッチングマスクに使用される。損失のあるカバー(例えばニッケル・クロミウム)は、例えば導波路(432)の内側表面上で、ニッケル・クロミウムの堆積およびパターニングによってアンテナ層106上に提供され得る。

## [0065]

工程272で、ホーンアンテナ(436)は、例えば図9のうちの420で示されるような水酸化カリウム(KOH)エッチングによって形成される。KOHエッチングはほぼ54度の傾斜を備えた滑らかな側壁表面に帰着する。ホーンアンテナ(436)はおよそ800μmの深さを持つためにエッチングされる。最後に、図7の工程274で、図9のうちの422で示されるように、窒化物層が除去され、アンテナ層は例えばスパッタリングプロセスによって金属化される。代替の実装では、ホーンアンテナ空胴を最初に形成するために、図4の工程270および272は工程266および268の前に行なわれる。

#### [0066]

有利には、アンテナ層へのホーンアンテナ(436)の集積化は、入力電磁気信号の信号パスを縮小する。ホーンアンテナが好ましい。なぜなら、平面アンテナ或いはパッチアンテナに比してホーンアンテナは非常に効率的なラジエータ(~80乃至 90%)を提供し、平面アンテナ或いはパッチアンテナの1乃至2%に比して優れたバンド幅(S11<-10dB 300乃至360GHz、18%)を有し、そして優れた利得を有しているからである。しかしながら、アンテナの代替の形態が熟考される。好ましい実施形態では、アンテナは12dBの利得、3dBのビーム幅および32×38度を有している。

#### [0067]

一実施形態では、アンテナ(436)の寸法の低減を可能にする誘電性を増大するために、アンテナ(436)はベンゾシクロブテン(BCB)で充填される。代替の充填材は当業者には明らかである。さらに、アンテナ(436)は、段付きホトレジスト・アプローチおよび(または)多重ウエハ・アプローチを使用して形成され得る。一実施例においてラフと後続するDRIEによって作成される。このリソグラフ・プロセスは、ホトレジストによって溶解しないサブマイクロンの画素の寸法およびピッチを変える使用を含んでいる。これは、傾斜したホトレジストプロファイルに変える勾配照射線量を作成する。DRIEエッチング中に、ホトレジストプロファイルはシリコンエッチングに変えられる。エッチング工程に続いて、アンテナ・サイドウォールは金(Au)で金属化される。代替的に、上述されるように、KOHエッチングはアンテナ(436)を形成するために使用さ

れ得る。

## [0068]

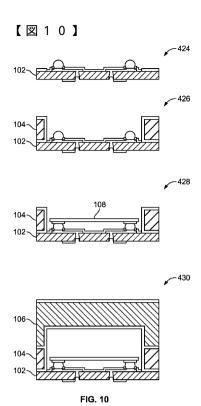

< 7. 最終組立工程 >

図4の工程276で、アンテナ層(106)は、In/Au接着剤あるいはAu/Au 熱-圧縮接着剤で導波路層(104)に接合される。追加の金属フィルム(インジウムなど)は、層(104または106)に追加される必要があり得、そのプロセスは、以下のセクション9で述べる。最後に、図4の工程278で、組み立てられた層は、個々の画素へと方形切断される。

[0069]

図10は、本発明による焦点面アライ画素の全アセンブリを図式化して表す。チップキャリア層(102)はDC バイアスおよび半田ボールと共に424で示される。426で、導波路層104は上述及び図4の工程226に示されるように、チップキャリア層(102)に接合される。428で、図4の工程260で示され、図8に関連して記載されるように、MMICチップ(108、110および112)は導波路層(104)の空胴に置かれ接合される。最後に、430で、アンテナ層(106)は導波路層(104)に接合される。

## [0070]

< 8 . 焦点面配列のウエハスケール処理 >

本明細書に記載された集積化アプローチおよび特徴は、異なるウエハ技術を備えたチップおよび導波路のバッチ組立てを可能にする。異なる半導体技術の中で作り上げられ、低損失のマイクロマシン処理された導波路トランジションを介して接続されたチップの集積化は、改善された素子性能を可能にする。本明細書に記載されたmFPA実装に適用されるように、公知の良好なチップとの三角形の格子の2-Dサブアレイの完全に積層された330~350GHzの焦点面配列が製造され得、高密度、LNA、検波器及びミクロスケール画素のミクロンの精度の集積化を提供する。図2Aに示されるmFPAは、およそ0.4cm×0.18cm×0.135cmの寸法で作り上げられた。

#### [0071]

導波路のためのマイクロマシニング処理の使用は層数を低減する。提供される利点は1024以上の要素の大きいプレナーアレイの計量を可能にし、いくつかのウエハレベル・パッケージング・アプローチに関連した化合物の収率の問題を低減し、かつマルチプルシリコン・パッケージング・ウエハ用の単一のIII・Vウエハの使用が延びる。LNA S- MMIC上の高度なパッケージングと抵抗性のカバーは、増加した安定性を提供する。電磁的に結合された十字形のチップは低損失の相互連結を可能にする。

[0072]

m F P A 画素の大きいプレナーアレイの一例は図11に示される。プレナーアレイは複数の画素を含むように450にて図11の左側に示され、各画素は層(102、104および106)とチップ(108、110および112)を有する。図11に示される画素の特定のレイアウトは必要ではなくもっとも好ましい数の画素数、部品間の信号損失及び他の要因を達成するために適切なレイアウトが選択され得る。大型のプレナー撮像アレイの使用は動的な場面撮像を可能にする。

[0073]

特定の画像システムのための、焦点面配アレイ(FPA)受信要素間隔の選択は、光学素子間のトレードオフである設計パラメータ、すなわちFナンバー(焦点距離/開口・寸法)、受信器対受信器のアンテナ結合 / クロストーク、受信器アンテナと光学素子のマッチングおよび像平面のサンプリングである分解能は受信器の画素間隔の低減により増加される。しかしながら、MMWカメラ中の広範囲な実験からの経験的なデータは、1.5 未満の間隔で近傍の画素のアンテナ間に連結することにより受け入れがたいレベルの受信器性能劣化を示す。有利には、本明細書に記載された特徴は、1.5 の間隔を備えている

[0074]

50

10

20

30

20

30

40

50

組立ての見地から、単一画素内の個々のチップ間の距離は画素対画素の距離よりはるかに短くすべく低減され得る。バッチ式に製造された受信器・アンテナでは、1.5 の受信器間隔を作り上げることは3 のものと同程度である。実際的見地から、間隔の上限は定義される。ナイキスト・サンプリングに達するために、1024もの素子を持った正方形のFPAを仮定して開口径未満にFPAの寸法を維持するために~2.5 の下で受信器間隔を維持しなければならない。しかしながら、撮像分解能を改善するために、1.5 の最も小さな間隔に一致する間隔より大きな開口が使用されるべきである。上述の(4.2 × 4.2 cm2)のFPAでは、光学の開口径は、ナイキスト・サンプリングのために~15cmに増加し、これは30cmの焦点距離のイメージャー用などコンパクトめに~15cmに増加し、これは30cmの焦点距離のイメージャー用などコンパクトをでの2.2cmの解像度に相当する。1人で持ち運べるイメージャー用などコンパクトをでステムについて、焦点距離はナイキスト・サンプリングのために6.5cmに低減され得る。他の目的のために、異なる撮像の必要条件が、異なる光学素子および結果的に異なる寸法のカメラを規定する。

#### [0075]

< 9.導波路層(104)あるいはアンテナ層(106)上の追加の金属の組立て。>マイクロマシン処理された導波路(WG)は、WGの空胴を形成するためにウエハにディープトレンチを使用する。WGトレンチを備えたトレンチ・ウエハは、WGを完成するために、しばしば1つ以上の追加のウエハに集積される。例えば、トレンチ・ウエハはWGの空胴を密閉するためにカバーウエハおよび(または)底ウエハに集積され得る。追加の処理および(または)パターニングはトレンチ・ウエハにおけるトレンチの形成後に必要とされ得る。例えば、トレンチ・ウエハは、さらにWG空胴の内部に置かれたチップで集積する必要があり得る。

#### [0076]

一実施例において、ウエハ集積化は、トレンチ・ウエハとカバーウエハの間でボンディング層(インジウムなど)の堆積のためにトレンチ・ウエハがパターニングされることを必要とする。ボンディング層はWGのための他の設計面の考慮を払うために選択され得る。しかしながら、トレンチ深さがほぼ30万至50μm以上である場合、湿ったホトレジスト(PR)は特にトレンチ・エッジの近くでトレンチの形成後にパターニングするのにふさわしくないかもしれない。例えば、湿ったPRは、ほぼ200μmの高さのトレンチ・サイドウォールを十分に被覆しないかもしれない。別の例において、追加処理は、トレンチの内部、例えば半田パッドおよび(または)ウエハ上面表面からトレンチ内に延びる金属ラインに必要とされ得る。実験は、これらのパターンは湿ったPRを使用して達成するのが難しいことを示した。

# [0077]

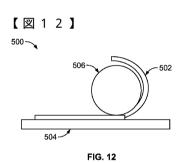

乾燥したホトレジスト(乾燥したPR)はウエハの処理に利用可能である。乾燥したPRはウエハ中のトレンチを閉鎖するためにキャップ材として使用された。図12を参照すると、システム(500)の一実装は、基板またはウエハ(504)への乾燥したホトレジスト(502)の塗布に適している。システム(500)は乾燥したPR(502)の塗布のためのローラー(506)を含む。一実施例におけるローラー(506)は熱および(または)ウエハ504への乾燥したPR(502)の塗布を促進する圧力を提供するのに適している。一実施例において、ローラー(506)は120°Cに加熱される。

# [0078]

一実施例におけるシステム(500)は乾燥したPRの模様をウエハの天面に直接パターニングするのに適している。システム(700)は、ウエハ・トレンチに隣接して、及びウエハ・トレンチ内をパターニングするために乾燥したPRを使用するのにさらに適している。湿ったPRのために使用されたスピン・コーティング・プロセスとは対照的に、乾燥したPRはい固体のフィルムであり、ウエハ表面上に積層され得、それ故、湿ったPRによって現れたPRの被覆および厚さの変化の問題を回避する。乾燥したPRの厚さは約

20

30

40

50

1 1 µ m から 1 0 0 µ m の間で変わり得る。

## [0079]

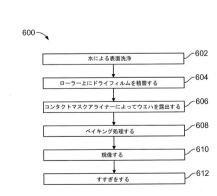

図13を参照すると、方法600は乾燥したPRを用いてディープトレンチの近くで乾燥したPRを使用してパターニングするために1つの実装を例証する。ウエハの表面は、例えば既知の溶剤を使用して洗浄される(工程602)。乾燥したPR(702)はローラー(506)(工程604)によってウエハ(504)上に積層される。一実施例における乾燥したPR(502)は例えばデュポン社のMM100レジストを含み、それは、ほぼ50μmの分解能を可能にする。乾燥したPRの他の例は当業者には明らかである。一実施例におけるローラー(506)は積層を促進するために120°Cに加熱される。ローラー(506)のための代替の温度は、例えば使用される乾燥したPRあるいはローラーの速度に基づいて選択され得る。

[0800]

ウエハはコンタクトマスクアライナーで露出される(工程606)。一例におけるコンタクトマスクアライナーは、365mmで150mWおよび露光ランプ波長の電力を有している。他のコンタクトマスクアライナーは、例えば、使用される乾燥したPR、パターンの複雑さあるいは他のデザイン面の配慮に基づいて選択され得る。露出後に、一実施例におけるウエハはパターン分解能を改善するためにベイキング処理がなされる(工程608)。ベイキング処理はホットプレートを使用して、およそ60秒間90°Cでなされる。ウエハを加熱する代替の方法、又は代替の温度および持続時間は当業者には明らかである。ついで、ウエハは現像される(工程 610)。一実施例において、ウエハは炭酸カリウム溶液で約90秒間スプレー現像される。一実施例における溶液は $K_2$ CO $_3$ (1.0 w t %)である。現像のための持続時間および溶液は設計面の配慮に基づいて調節され得る。ついで、ウエハは現像後の残渣を除去するために、例えば脱イオン水スプレーを使用してすすがれる(工程612)。

[0081]

一実施例における乾燥したPR(502)はネガ型レジストで、金属蒸着とリフトオフのためのサイドウォール輪郭を作成するのにより適している。乾燥したPR(502)の厚さはほぼ38 $\mu$ mであり、それは40-50 $\mu$ mといった小さな形体を解決することができる。より小さな形体については、より薄い乾燥したPRが使用され得る。ある表面への乾燥したPRの付着が増強される必要があり得る。例えば、シリコン表面に比して、Au表面への乾燥したPR付着は少なくなる。付着は、表面処理(例えば、表面を粗くする、あるいはいくつかの表面増強剤を使用して)で改善され得る。追加のマスクの形体はAu天面への乾燥したPR付着および支持を増強するために組込まれ得る。

[0082]

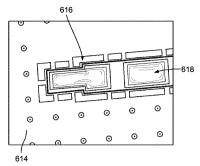

図14を参照すると、が図12の乾燥したホトレジスト・アプリケーションを使用して処理されたウエハ(614)の一実施例が示されている。この実施例において、不連続の開口列は乾燥したPR支持を増強するために使用された。乾燥したホトレジスト開口は616で示される。トレンチ(618)は乾燥したPRによって被覆されていることが示される。一実施例において、インジウム層は、ボンディング層を形成するために金層上の開口(616)内にパターニングされる。ついで、ボンディング層は当業者に認識されることであるが、別のウエハで接合され得る。

[0083]

図 1 5 を参照すると、領域(6 2 2 )においてインジウム蒸着とリフトアップ後のウエハ (6 2 0 )の一実施例が示される。

[0084]

代替の工程および組立て特徴は当業者には明らかである。例えば、当業者に認識されることであるが、ホーンアンテナはアンテナ層(106)の背部上で空胴の形成に先立って形成され得る。

[0085]

本明細書に記載された工程または動作はあくまでも一例にすぎない。発明の精神から逸脱

せずに、これらの工程又は動作に多くの変形があり得る。例えば、工程は異なる順に行なわれ得るか、あるいは、工程が加えられるか、削除されるか、若しくは修正され得る。

## [0086]

本発明の例示的な実装は本明細書に描かれ、詳細に記載されたが、当業者には発明の精神から逸脱することなく様々な変更、追加、置換がなし得るであろうことは明白であり、それゆえ、それらはつぎの特許請求の範囲に規定されるとおり、本発明の範囲内にあるものと考えられる。

【図1】

【図2A-2B】

# 【図2C】

# 【図3】

## 【図4】

# 【図5】

FIG. 5

# 【図6】

# 【図7A】

【図7B】

【図8】

【図9】

【図13】

# 【図14】

FIG. 14

# 【図15】

## フロントページの続き

(72)発明者 ヌゴ,ピーター

アメリカ合衆国 90630 カリフォルニア州 サイプレス ジーン・ストリート 9827

(72)発明者 アカーリング, ガーション

アメリカ合衆国 90230 カリフォルニア州 カルバー・シティー ディラー・アベニュー 5430

(72)発明者 レオン,ケビン エム.

アメリカ合衆国 90034 カリフォルニア州 ロサンゼルス アプト103 ベントレー・ア ベニュー 3724

(72)発明者 チャン - チエン, パティー

アメリカ合衆国 90277 カリフォルニア州 レドンド・ビーチ ナンバー・エー エメラル ド・ストリート 309

(72)発明者 ヘニグ,ケリー,ジェイ.

アメリカ合衆国 90505 カリフォルニア州 トランス グランド・サミット・ロード 27

(72)発明者 ディール,ウイリアム,アール.

アメリカ合衆国 90278 カリフォルニア州 レドンド・ビーチ スペース・パーク・ドライブ 1

## 審査官 赤穂 美香

(56)参考文献 米国特許出願公開第2011/0180917(US,A1)

特開2012-216714(JP,A)

特開平11-195731(JP,A)

特開2011-171498(JP,A)

特表2014-511623(JP,A)

国際公開第2012/119818(WO,A1)

特開2007-165638(JP,A)

(58)調査した分野(Int.CI., DB名)

H01P 11/00

H010 13/02

H01Q 21/06

H01Q 23/00