### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2016-219802 (P2016-219802A)

(43) 公開日 平成28年12月22日(2016, 12, 22)

(51) Int. Cl. F 1 テーマコード (参考)

**HO1L 29/786 (2006.01)**HO1L 29/78 617K 3K107 **HO1L 51/50 (2006.01)**HO5B 33/14 A 5F110

## 審査請求 有 講求項の数 19 OL (全 16 頁)

(21) 出願番号 特願2016-97712 (P2016-97712) (71)

(22) 出願日 平成28年5月16日 (2016. 5. 16)

(31) 優先権主張番号 10-2015-0067321

(32) 優先日 平成27年5月14日 (2015.5.14)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 501426046

エルジー ディスプレイ カンパニー リ

ミテッド

大韓民国 ソウル、ヨンドゥンポーグ、ヨ

ウィーテロ 128

(74) 代理人 100094112

弁理士 岡部 讓

(74)代理人 100106183

弁理士 吉澤 弘司

(74)代理人 100114915

弁理士 三村 治彦

(74) 代理人 100120363

弁理士 久保田 智樹

(74)代理人 100125139

弁理士 岡部 洋

最終頁に続く

## (54) 【発明の名称】薄膜トランジスタ及びそれを含む表示装置のバックプレーン基板

## (57)【要約】

【課題】アクティブ層の結晶化時に発生する断線を解決 しうる薄膜トランジスタ及びそれを含むバックプレーン 基板を提供する。

【解決手段】本発明の薄膜トランジスタは、基板と、基板上に設けられ、平坦部及び平坦部の側部に傾斜部を有し、傾斜部の横幅(a)と高さ(h)との比(h/a)が1.192以下であるゲート電極と、基板上に配置され、ゲート電極を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられ、ゲート電極の上方に位置する多結晶シリコンのアクティブ層と、アクティブ層の両端に接続されたソース電極及びドレイン電極とを含む。

## 【選択図】図7

#### 【特許請求の範囲】

### 【請求項1】

基板と、

前記基板上に設けられ、平坦部及び前記平坦部の側部に傾斜部を有し、前記傾斜部の横幅(a)と高さ(h)との比(h/a)が1.192以下であるゲート電極と、

前記基板上に配置され、前記ゲート電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜上に設けられ、前記ゲート電極の上方に位置する多結晶シリコンのアクティブ層と、

前記アクティブ層の両端に接続されたソース電極及びドレイン電極と を含む、薄膜トランジスタ。

【請求項2】

前記傾斜部の傾斜面の前記基板の面に対する角度は2°~50°の範囲である、請求項1に記載の薄膜トランジスタ。

## 【請求項3】

前記ゲート電極の前記平坦部の厚さは、前記傾斜部の高さ(h)と実質的に等しく、少なくとも1000 である、請求項1又は2に記載の薄膜トランジスタ。

### 【請求項4】

前記ゲート絶縁膜及び前記アクティブ層は、前記ゲート電極の前記平坦部及び前記傾斜部を覆うように形成されている、請求項1乃至3のいずれか1項に記載の薄膜トランジスタ。

【請求項5】

前記傾斜部は、前記基板に隣接して設けられ、前記基板の面に対して第1角度をなす傾斜面を有する第1傾斜部と、前記第1傾斜部の上に設けられ、前記基板の面に対して第2角度をなす傾斜面を有する第2傾斜部とを含む、請求項1乃至4のいずれか1項に記載の薄膜トランジスタ。

### 【請求項6】

前記第1角度は前記第2角度よりも大きい、請求項5に記載の薄膜トランジスタ。

#### 【請求項7】

前記第1傾斜部は、前記ゲート電極の前記平坦部の厚さの1/2以下である、請求項6に記載の薄膜トランジスタ。

【請求項8】

前記第2角度は2°~50°の範囲である、請求項7に記載の薄膜トランジスタ。

【請求項9】

マトリクス状に区分された複数の画素を有する基板を有し、

前記複数の画素のうちの少なくとも一つは、

前記基板上に設けられ、平坦部及び前記平坦部の側部に傾斜部を有し、前記傾斜部の 横幅(a)と高さ(h)との比(h/a)が1.192以下であるゲート電極と、

前記基板上に配置され、前記ゲート電極を覆うゲート絶縁膜と、

前記ゲート絶縁膜上に設けられ、前記ゲート電極の上方に位置する多結晶シリコンの アクティブ層と、

前記アクティブ層の両端に接続されたソース電極及びドレイン電極と、を含む、

表示装置のバックプレーン基板。

【請求項10】

前記傾斜部の傾斜面の前記基板の面に対する角度は2°~50°の範囲である、請求項9に記載のバックプレーン基板。

## 【請求項11】

前記ゲート電極の前記平坦部の厚さは、前記傾斜部の高さ(h)と実質的に等しく、少なくとも1000 である、請求項9又は10に記載のバックプレーン基板。

### 【請求項12】

前記ゲート絶縁膜及び前記アクティブ層は、前記ゲート電極の前記平坦部及び前記傾斜

10

20

30

40

部を覆うように形成されている、請求項 9 乃至 1 1 のいずれか 1 項に記載のバックプレーン基板。

### 【請求項13】

前記傾斜部は、前記基板に隣接して設けられ、前記基板の面に対して第1角度をなす傾斜面を有する第1傾斜部と、前記第1傾斜部の上に設けられ、前記基板の面に対して第2角度をなす傾斜面を有する第2傾斜部とを含む、請求項9乃至12のいずれか1項に記載のバックプレーン基板。

### 【請求項14】

前記第1角度は前記第2角度よりも大きい、請求項13に記載のバックプレーン基板。

#### 【 請 求 項 1 5 】

前記第1傾斜部は、前記ゲート電極の前記平坦部の厚さの1/2以下である、請求項1 4に記載のバックプレーン基板。

#### 【請求項16】

前記第2角度は2°~50°の範囲である、請求項15に記載のバックプレーン基板。

## 【請求項17】

請求項9乃至15のいずれか1項に記載のバックプレーン基板を備え、液晶表示装置又は有機発光表示装置である、表示装置。

#### 【請求項18】

前記表示装置は、液晶表示装置であり、前記画素は、前記ドレイン電極に接続された画素電極を更に有する、請求項17に記載の表示装置。

#### 【請求項19】

前記表示装置は、有機発光表示装置であり、前記画素は、有機発光ダイオードを有し、前記ドレイン電極は、前記有機発光ダイオードの第1の電極を構成する、請求項17に記載の表示装置。

## 【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、薄膜トランジスタに係り、特に、薄膜トランジスタ及びそれを含む表示装置のバックプレーン基板に関する。

### 【背景技術】

## [0002]

移動通信端末機、ノートパソコンのような各種携帯用電子機器の発展に伴い、これらに適用できる平板表示装置(Flat Panel Display Device)に対する要求が増大している。

## [0003]

平板表示装置としては、液晶表示装置(Liquid Crystal Display Device)、プラズマ表示装置(Plasma Display Panel Device)、電界放出表示装置(Field Emission Display Device)、有機又は無機発光表示装置(Organic or Inorganic Light Emitting Diode Display Device)などが研究されている。このような平板表示装置の中でも、液晶表示装置及び有機発光表示装置は、量産技術の発展、駆動手段の容易性、低電力消費、高画質及び大画面の実現の利点によって、適用分野が拡大されている。

## [0004]

平板表示装置は、複数個の画素をマトリクス状に備え、各画素を個別的に制御することができるTFT(Thin Film Transistor:薄膜トランジスタ)を画素内に1つ以上備える。薄膜トランジスタは、ゲート電極の位置によってトップゲート構造とボトムゲート構造とに分類することができる。

## [0005]

図1は、典型的なトップゲート構造のTFTのゲート電極の形成後の状態を示す断面図

10

20

30

40

である。典型的なトップゲート構造のTFT(Thin Film Transistor)では、まず、基板10上に、非晶質(amorphous)シリコン層を形成し、これをエキシマレーザー(excimer laser)を用いて結晶化して多結晶シリコン(poly-silicon)層を形成する。

[0006]

次いで、結晶化された多結晶シリコン層上に感光膜(図示せず)を塗布し、前記感光膜を露光及び現像して感光膜パターンを形成し、感光膜パターンをマスクとして前記多結晶シリコンをエッチングし、図1に示すように、各画素の所定の部位にアクティブ層20を残す。

[0007]

ところが、上述の結晶化は、通常は400 以上の温度で行われる。この過程で、アクティブ層20内で成長したグレインとグレインとが出会って突出する部位が発生することがあった。このような突出部位が形成されると、完成した薄膜トランジスタを動作する際、ターンオン時に電界(electric field)が集中してブレークダウン電圧が低下し、リーク電流が生じる原因になることがあった。また、薄膜トランジスタの製造工程中、前記突出部位は静電不良に対して脆弱であるため、製造歩留まりを低下させる要因になることがあった。今後、次世代の装置において低消費電力及びスリムネス(slimness)構造のためにゲート絶縁膜が薄くなることが要求される場合、このような弱点はさらに問題となる。

[ 0 0 0 8 ]

アクティブ層 2 0 を形成した後、トップゲート構造の薄膜トランジスタにおいては、ゲート絶縁膜 3 0 及びゲート電極 4 0 を順次形成する。このとき、ゲート絶縁膜 3 0 及びゲート電極 4 0 は、アクティブ層 2 0 の突出部位を覆うように形成される。したがって、ゲート絶縁膜 3 0 及びゲート電極 4 0 も下部のアクティブ層 2 0 の表面が有する突出部位の影響を受けてしまい、ゲート絶縁膜 3 0 及びゲート電極 4 0 の界面にも凹凸を有するようになる。

[0009]

また、チャネルは、アクティブ層20のゲート電極40と重なる部位に形成される。アクティブ層20とゲート電極40との間には、ゲート絶縁膜30が介在している。したがって、チャネルは、突出部位によってもたらされるアクティブ層20とゲート電極40との間の不均一な界面に形成されることになる。この結果、ホットキャリアストレス(HCS:Hot Carrier Stress)が高くなり、信頼性が低下することがあった。

【先行技術文献】

【特許文献】

[ 0 0 1 0 ]

【 特 許 文 献 1 】 特 開 2 0 1 5 - 1 2 5 3 4 7 号 公 報

【発明の概要】

【発明が解決しようとする課題】

[0011]

本発明は、上述した問題点を解決するために案出されたものであり、アクティブ層の結晶化時に発生する断線を防止或いは低減しうる薄膜トランジスタ及びそれを含む表示装置のバックプレーン基板を提供することに、その目的がある。

【課題を解決するための手段】

[0012]

上記のような目的を達成するために、本発明の一観点による薄膜トランジスタは、基板と、前記基板上に設けられ、平坦部及び前記平坦部の側部に傾斜部を有し、前記傾斜部の横幅(a)と高さ(h)との比(h/a)が1.192以下であるゲート電極と、前記基板上に配置され、前記ゲート電極を覆うゲート絶縁膜と、前記ゲート絶縁膜上に設けられ、前記ゲート電極の上方に位置対向する多結晶シリコンのアクティブ層と、前記アクティ

10

20

30

40

ブ層の両端に接続されたソース電極及びドレイン電極とを含む。

#### [0013]

前記傾斜部の傾斜面の前記基板の面に対する角度は2°~50°の範囲であることが好ましく、このとき、前記ゲート電極の前記平坦部の厚さは、前記傾斜部の高さ(h)と実質的に等しく、少なくとも1000 であってもよい。

#### [0014]

前記ゲート絶縁膜及び前記アクティブ層は、前記ゲート電極の前記平坦部及び前記傾斜部を覆うように形成される。

## [ 0 0 1 5 ]

場合によって、前記傾斜部は、前記基板に隣接して設けられ、前記基板の面に対して第1角度をなす傾斜面を有する第1傾斜部と、前記第1傾斜部の上に設けられ、前記基板の面に対して第2角度をなす傾斜面を有する第2傾斜部を含むことができる。そして、前記第1角度は前記第2角度よりも大きくてもよい。この場合、前記第1傾斜部は、前記ゲート電極の前記平坦部の厚さの1/2以下であってもよい。また、前記第2角度は2°~50°の範囲であることが好ましい。

#### [0016]

また、本発明の他の一観点による表示装置のバックプレーン基板は、マトリクス状に区分された複数の画素を有する基板を有し、前記複数の画素のうちの少なくとも1つは、前記基板上に設けられ、平坦部及び前記平坦部の側部に傾斜部を有し、前記傾斜部の横幅(a)と高さ(h)との比(h/a)が1.192以下であるゲート電極と、前記基板上に配置され、前記ゲート電極を覆うゲート絶縁膜と、前記ゲート絶縁膜上に設けられ、前記ゲート電極の情報に位置する多結晶シリコンのアクティブ層と、前記アクティブ層の両端に接続されたソース電極及びドレイン電極と、を含んでなることができる。

### 【発明の効果】

#### [0017]

本発明の薄膜トランジスタ及びそれを含む表示装置のバックプレーン基板には、次のような効果がある。

#### [0018]

第一に、ゲート電極の上部にチャネルを含むアクティブ層を形成することによって、たとえレーザー結晶化した後にアクティブ層を冷却する過程でアクティブ層の表面に突出部位が発生しても、チャネルはゲート電極に隣接するアクティブ層とゲート絶縁膜との界面側に形成されるため、ホットキャリアストレスが低く、BV(Breakdown Voltage)の低下が少ないため、素子の信頼性を確保することができる。したがって、このような構成を含む薄膜トランジスタを表示装置のバックプレーン基板の各画素に配置する場合、表示装置の全体的な性能向上を期待することができる。

#### [0019]

第二に、ゲート電極をアクティブ層の下部に配置することによって、光電流の発生を防止するために備えられる遮光層やボトム遮光金属層の省略が可能である。これによって、表示装置の製造に用いられるマスク数の低減が可能であり、製造歩留まりの向上を期待することができる。

# [ 0 0 2 0 ]

第三に、配線抵抗の低減のためにゲート電極に一定水準以上の厚さが要求される構造では、下側に形成されたゲート電極の傾斜に沿って上部のゲート絶縁膜及びアクティブ層を 形成し、ゲート電極の傾斜部を低い傾斜で形成することによって、傾斜部に対向するアクティブ層で多結晶シリコンの断線を防止することができる。

# [0021]

第四に、ゲート電極の低い傾斜の傾斜部を形成する際に、複数の金属層を形成したり別途のマスクを追加しなくても、エッチング工程において感光膜のアッシングの程度及びエッチング選択比を調節することによって低傾斜のテーパー及び傾斜部の二重テーパーの実現が可能であるので、工程上の負担が少ない。

10

20

30

40

【図面の簡単な説明】

[0022]

- 【図1】典型的なトップゲート構造のTFTのゲート電極の形成後の状態を示す断面図である。

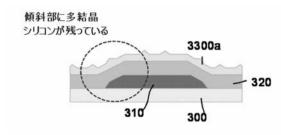

- 【図2】ボトムゲート構造のTFTのアクティブ層の結晶化後の状態を示す断面図である

- 【図3】ボトムゲート構造のTFTのアクティブ層の結晶化後の冷却時におけるアクティブ層の断線を示す断面図である。

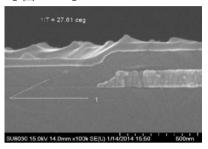

- 【図4】図3のアクティブ層の断線を撮影したSEM像である。

- 【図 5 A 】本発明の第 1 実施例に係る薄膜トランジスタのシリコン層を形成した直後の状態を示す平面図である。

- 【図5B】図5Aの平面図のI~I′線に沿って切断した断面図である。

- 【図 6 】本発明の第 1 実施例に係る薄膜トランジスタのシリコン層のレーザー結晶化後の 状態を示す断面図である。

- 【図7】本発明の第1実施例に係る薄膜トランジスタを示す断面図である。

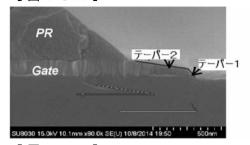

- 【図8A】ゲート電極の傾斜部の角度が45°である場合に、図6の結晶化後の状態を撮影したSEM像である。

- 【図8B】ゲート電極の傾斜部の角度が30°である場合に、図6の結晶化後の状態を撮影したSEM像である。

- 【図8C】ゲート電極の傾斜部の角度が10°である場合に、図6の結晶化後の状態を撮影したSEM像である。

- 【図9A】本発明の第1実施例に係る薄膜トランジスタのゲート電極の形成方法を示す工程断面図(その1)である。

- 【 図 9 B 】 本 発 明 の 第 1 実 施 例 に 係 る 薄 膜 ト ラン ジ ス タ の ゲ ー ト 電 極 の 形 成 方 法 を 示 す 工 程 断 面 図 ( そ の 2 ) で あ る 。

- 【図9C】本発明の第1実施例に係る薄膜トランジスタのゲート電極の形成方法を示す工程断面図(その3)である。

- 【図9D】本発明の第1実施例に係る薄膜トランジスタのゲート電極の形成方法を示す工程断面図(その4)である。

- 【図10A】本発明の第2実施例に係る薄膜トランジスタのシリコン層を形成した直後の 状態を示す平面図である。

- 【図10B】図10Aの平面図のII~II′線に沿って切断した断面図である。

- 【図 1 1 】本発明の第 2 実施例に係る薄膜トランジスタのシリコン層のレーザー結晶化後の状態を示す断面図である。

- 【図12】本発明の第2実施例に係る薄膜トランジスタを示す断面図である。

- 【図13A】本発明の第2実施例に係る薄膜トランジスタのゲート電極を形成した後の状態を示すSEM像である。

- 【図13B】本発明の第2実施例に係る薄膜トランジスタのゲート電極の上部にアクティブ層を形成した後の状態を示すSEM像である。

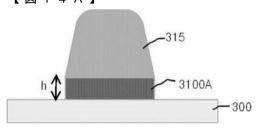

- 【図14A】本発明の第2実施例に係る薄膜トランジスタのゲート電極の形成方法を示す 工程断面図(その1)である。

- 【 図 1 4 B 】本発明の第 2 実施例に係る薄膜トランジスタのゲート電極の形成方法を示す 工程断面図(その 2 )である。

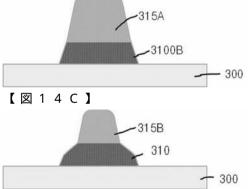

- 【図14C】本発明の第2実施例に係る薄膜トランジスタのゲート電極の形成方法を示す 工程断面図(その3)である。

【発明を実施するための形態】

[0023]

以下、添付の図面を参照して、本発明の実施形態による薄膜トランジスタ及びそれを含む表示装置のバックプレーン基板を詳細に説明する。

[0024]

50

40

10

20

上述のように、典型的なトップゲート構造の薄膜トランジスタにおいて、アクティブ層の表面に突出部位が発生すると、ホットキャリアストレスが高くなり、また、突出部位の近くのチャネル形成及び電界の集中によってBV(Breakdown voltage)特性が劣化するという問題が生じることがあった。

### [0025]

このような問題がトップゲート構造の構造的な問題点であることを考慮して、アクティブ層に多結晶シリコン(poly-silicon)を適用する構造において、最近、ボトムゲート方式についての研究開発が行われている。

#### [0026]

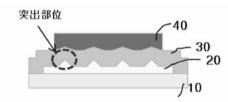

図2は、ボトムゲート構造のTFTのアクティブ層の結晶化後の状態を示す断面図である。図2に示すように、ボトムゲート構造の薄膜トランジスタ(TFT)では、基板100上にゲート電極110を形成し、次いで、ゲート絶縁膜120及び非晶質シリコン層をPECVD(Plasma Enhanced Chemical Vapor Deposition)で順次堆積し、その後、例えばエキシマレーザーの照射により非晶質シリコン層の結晶化を行って多結晶シリコン層130を形成する。

#### [0027]

ここで、結晶化過程は非晶質シリコン層の堆積の後に行われるので、ゲート絶縁膜120と非晶質シリコン層は、それらの間にその他のアニーリング(annealing)工程なしに直ちに連続して形成することができる。したがって、結晶化時にグレイン同士が出会う部位に対応して多結晶シリコン層130の表面に突出部位が発生しても、チャネルは、ゲート電極110の上側にある多結晶シリコン層130とゲート絶縁膜120との間の平坦な界面に形成されるため、トップゲート構造で発生したような電界集中現象は発生しない。

#### [0028]

また、チャネルはゲート電極110の上部に形成されるので、設計自由度はより高く、高解像度構造に有利である。また、液晶パネルのバックプレーン(backplane)においては、バックライトから入ってくる光を例えばゲート電極110により遮蔽できることによって、光電流(photo current)の防止のためにアクティブ層の下側に必要とされる遮光層を除去することができ、パッシブ方式の有機発光表示装置のバックプレーンにおいては、ボトム遮光金属層(Bottom Shield Metallayer)を省略できるので、表示装置の製造のために必要なマスクの数を低減することができる。

### [0029]

但し、ボトムゲート方式において、エキシマレーザーの照射によって多結晶シリコン層を形成する際、液状のシリコンが冷却され、重力及び表面張力によって結晶質の塊同士が凝集する凝集現象(agglomeration)が発生することがある。この過程で、平坦な表面は関係ないが、ゲート電極の両端上のようにテーパーを有する部位では、その両端に結晶質塊が移動し、結果的に、多結晶シリコンがゲート電極の端部上の傾斜部位で消失する現象が発生することがある。

### [0030]

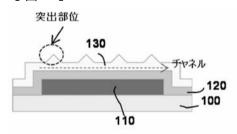

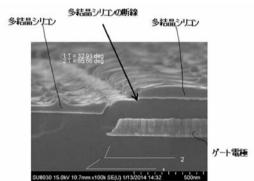

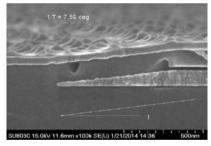

図3は、ボトムゲート構造のTFTの結晶化後の冷却時におけるアクティブ層の断線を示した断面図であり、図4は、図3のアクティブ層の断線を撮影したSEM像である。

## [0031]

図3では、冷却後、テーパーでの多結晶シリコンの消失によるアクティブ層130aの断線を断面で示しており、図4は、これをSEMで撮影したもので、ゲート電極110のテーパーに沿ったゲート絶縁膜の側面でアクティブ層の断線が発生することを示している。アクティブ層は、結晶化後に冷却化された多結晶シリコンである。

#### [0032]

本発明は、下記のように、レーザー結晶化で多結晶シリコンを形成するボトムゲート構造のテーパーに生じる欠陥を防止したものである。

10

20

30

40

10

20

30

40

50

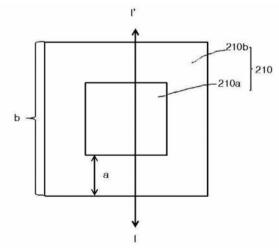

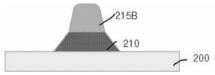

### [0033]

「第1実施例]

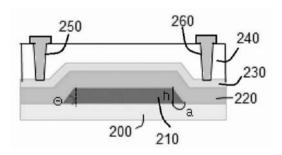

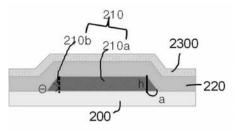

図 5 A は、本発明の第 1 実施例に係る薄膜トランジスタのシリコン層を形成した直後の状態を示す平面図である。図 5 B は、図 5 A の平面図のI-I '線に沿った断面図である。図 6 は、本発明の第 1 実施例に係る薄膜トランジスタのシリコン層のレーザー結晶化後の状態を示す断面図(図 5 A のI-I '線に沿った断面図)である。図 7 は、本発明の第 1 実施例に係る薄膜トランジスタを示す断面図(図 5 A のI-I '線に沿った断面図)である。

### [0034]

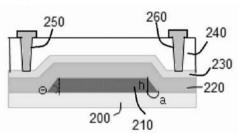

図5 B 及び図7に示すように、本発明の第1実施例に係る薄膜トランジスタは、基板200と、基板200上に設けられ、平坦部210a及び平坦部210aの側部に傾斜部210bを有し、傾斜部210bの横幅aと高さhとの比(h/a)が1.192以下(すなわち、角度が約50°以下)であるゲート電極210と、基板200上に配置され、ゲート電極210を覆うゲート絶縁膜220と、ゲート絶縁膜220上に設けられ、ゲート電極210の上方に位置する多結晶シリコンのアクティブ層230と、アクティブ層230の両端に接続されたソース電極250及びドレイン電極260とを含む。

### [0035]

傾斜部210bの横幅aと高さhとの比は、設計段階では約1以下(すなわち、角度が約45°以下)にすることが好ましいが、最終製品においては許容誤差10%程度を勘案して、約1.192まで許容可能である。これを傾斜部の角度に換算すると、設計段階では45°以下をターゲットとするが、許容誤差を勘案すると、最終製品では約50°までの傾斜が発生することを考慮し得る。

#### [0036]

アクティブ層 2 3 0 は、両端がドープされてソース領域 2 3 0 b 及びドレイン領域 2 3 0 c として定義される。ソース領域 2 3 0 b 及びドレイン領域 2 3 0 c は、ソース電極 2 5 0 及びドレイン電極 2 6 0 との接続領域となる。アクティブ層 2 3 0 のソース領域 2 3 0 b とドレイン領域 2 3 0 c との間は真性領域であって、薄膜トランジスタのチャネル領域として用いられる。

## [0037]

アクティブ層 2 3 0 とソース電極 2 5 0 及びドレイン電極 2 6 0 との層間には、接続部を除いて層間絶縁膜 2 4 0 が設けられる。ソース電極 2 5 0 及びドレイン電極 2 6 0 は、層間絶縁膜 2 4 0 に設けられたコンタクトホールを介してアクティブ層 2 3 0 のソース領域 2 3 0 b 及びドレイン領域 2 3 0 c に接続される。

## [0038]

本発明の第1実施例に係る薄膜トランジスタは、ゲート電極210の側部のテーパー(taper)を低くすることを特徴とするもので、図5A及び図5Bに示すように、傾斜部210bの斜面と基板200の表面とのなす角度 は2°~50°の範囲であることが好ましい。ここで、傾斜部210bの斜面が基板200の表面に対して有する角度 は、最終製品において工程許容誤差の範囲で変更されてもよい。傾斜部210bが低い傾斜を有する理由は、非晶質シリコン2300をゲート電極210の表面上に堆積するとき、ゲート電極210の平坦部210aでは平坦に、傾斜部210bでは低い傾斜に沿って緩やかな堆積が可能であるからである。また、図6に示すように、レーザー照射による約400 前後での結晶化によって多結晶シリコン層2300aの表面に突出部位が発生し、その後の冷却過程で結晶質化された成分同土で部分的な凝集現象が発生しても、傾斜部210bに対向する部分の多結晶シリコン層2300aは緩やかな傾斜に沿って堆積されているので、多結晶シリコン2300aの断線は発生しない。

#### [0039]

図6は、多結晶シリコン層2300aのレーザー照射後、冷却まで行われた状態であり、実際に薄膜トランジスタやそれを用いた表示装置のバックプレーン基板の場合、多結晶シリコン2300aは、パターニングして一定部分のみをアクティブ層230(例えば図

7を参照)として残す。

### [0040]

以下、ゲート電極 2 1 0 の傾斜部を低いテーパーにしたときに多結晶シリコンの傾斜部で断線が発生しない点を立証するために行った実験の結果について説明する。図 8 A 乃至図 8 C は、それぞれゲート電極 2 1 0 の傾斜部の角度 が 4 5 °、3 0°、1 0°である場合に、図 6 の結晶化後の状態を撮影した S E M 像である。

### [0041]

図8A乃至図8Cは、非晶質シリコンを結晶化するレーザーを照射し、次いで冷却まで行った後のゲート電極の上部を示したもので、ゲート電極の傾斜部のターゲット角度が45。以下である条件を維持したとき、多結晶シリコン層の傾斜部で断線が発生していない点を示したものである。実際に最終製品で残っているゲート電極の傾斜部の基板表面に対する角度は、工程許容誤差により約50。以下であり得る。

#### [0042]

従来のボトムゲート構造においては、段差部位を減らす趣旨から、側部の高テーパーは維持するもののゲート(電極)の厚さを1000 未満とする研究があった。しかしながら、この構造の場合、ゲート(電極)の厚さを1000 以上にすると、ゲート電極の傾斜部上の多結晶シリコン層で断線が発生する可能性が高かった。上述した図4は、ゲート電極の傾斜部に高テーパーを維持した場合であって、基板に対するゲート電極の傾斜部が約65°である場合であり、ゲート電極の傾斜部上に位置した多結晶シリコンの断線現象が観察されたことを示している。

#### [ 0 0 4 3 ]

本発明の一実施例による薄膜トランジスタは、ゲート電極の傾斜部の角度を低くすることによって、このような問題点を解決したものである。換言すると、本発明の一実施形態による薄膜トランジスタによれば、平坦部におけるゲート電極の厚さが1000 以上の場合にも、ゲート電極の傾斜部上における多結晶シリコンの断線を防止することができる

## [0044]

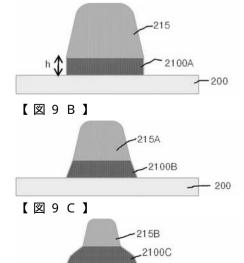

以下、本発明の第1実施例による薄膜トランジスタに適用するための低傾斜を有するゲート電極の形成方法を説明する。図9A乃至図9Dは、本発明の第1実施例に係る薄膜トランジスタのゲート電極の形成方法を示す工程断面図(図5AのI-I<sup>\*</sup>線に沿った断面図)である。

# [0045]

図9Aに示すように、まず、基板200上に金属を堆積し、第1感光膜パターン215を用いて堆積した金属をウェットエッチング又はドライエッチングして、第1ゲートパターン層2100Aを形成する。ここで、第1感光膜パターン215が有する幅は、形成しようとする平坦部とその周辺の傾斜部に対応する'b'の幅(図5A参照)を有する。そして、基板200上に堆積した金属の厚さ'h'は、1000 以上である。金属は、同一の金属又は同一の金属合金をスパッタリングなどの方式で形成した単一層である。

## [0046]

図9 Bに示すように、エッチング装置内の酸素( $O_2$ )の含有量を増加し、第 1 感光膜パターンをアッシング(a s h i n g)して幅を減少させて第 2 感光膜パターン 2 1 5 Aを形成し、同一の過程で、第 1 ゲートパターン層 2 1 0 0 A の側部のエッチングを行うことで、 1 次傾斜を有する第 2 ゲートパターン 2 1 0 0 B を形成する。

# [0047]

次いで、図9Cに示すように、エッチング装置内の酸素(〇₂)の含有量を増加し、第2感光膜パターンをアッシング(ashing)して再度幅を減少させて第3感光膜パターン215Bを形成し、同一の過程で、第2ゲートパターン層2100Bの側部のエッチングを行うことで、2次傾斜を有する第3ゲートパターン2100Cを形成する。この過程で用いられるドライエッチングプラズマは、感光膜成分のエッチング選択比がゲート電極形成用の金属のエッチング選択比よりも大きいので、相対的にアッシング及びエッチン

10

20

30

40

グ過程で第2感光膜パターン215Aの除去幅がさらに大きく、また、第3ゲートパターン2100Cの下端部の幅を、図9Aの過程で形成された幅'b'の水準に維持することができる。そして、形成された前記第3ゲートパターン2100Cは、下部と上部とで傾斜が異なるテーパーを有することができる。

## [0048]

次いで、図9 D に示すように、図9 C の条件と同じ条件で時間を増加させる場合、第3 感光膜パターン 2 1 5 B の下部でエッチングされて、最終的なゲート電極 2 1 0 の形状は、端部に、1 次テーパーよりも低い低傾斜の第2 テーパーで均一な傾斜部を有するようになる。

## [0049]

一方、図9A乃至図9Dの過程は、同一のプラズマエッチング装置で行うことができる。感光膜パターンのアッシングが必要な場合は、エッチング装置内の酸素量を増加すればよい。アッシングされた感光膜パターンの下部のゲートパターン層の金属のエッチングは、感光膜成分のエッチング選択比が金属のエッチング選択比よりも高いドライエッチングプラズマを用いて、直接ドライエッチングプラズマに当たる上側部からゆっくりエッチングされて、低傾斜のテーパーを有するようにエッチングが行われるようにする。ドライエッチングプラズマは、感光膜パターンの上側から基板200に供給されることが好ましい

### [0050]

上述した方法によって、ゲート電極 2 1 0 は、多層や異種の金属の部分に分けて形成せず、 1 回の堆積工程後、感光膜及びエッチング選択比などを調整することで、低段差の傾斜部を有する単一層で形成することができる。

### [0051]

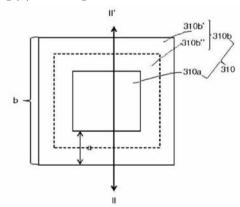

#### 「第2実施例]

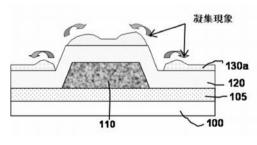

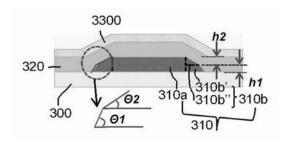

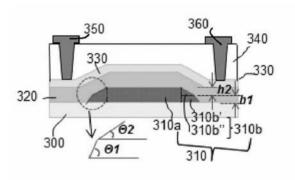

図10Aは、本発明の第2実施例に係る薄膜トランジスタのシリコン層を形成した直後の状態を示す平面図である。図10Bは、図10Aの平面図のII-II ′線に沿った断面図である。図11は、本発明の第2実施例に係る薄膜トランジスタのシリコン層のレーザー結晶化後の状態を示す断面図(II-II ′線に沿った断面図)である。図12は、本発明の第2実施例に係る薄膜トランジスタを示す断面図(II-II ′線に沿った断面図)である。

### [0052]

図12に示すように、本発明の第2実施例に係る薄膜トランジスタは、基板300上に設けられ、平坦部310a及び平坦部310aの側部に傾斜部310bを有し、傾斜部310bの横幅aと高さhとの比(h/a)が1.192以下であるゲート電極310(例えば、図10A参照)と、基板300上に配置され、ゲート電極を覆うゲート絶縁膜320と、ゲート絶縁膜320と、ゲート絶縁膜320と、ゲート絶縁膜320と、アクティブ層330の両端に接続されたソース電極350及びドレイン電極360とを含む。

## [0053]

ここで、第1実施例と異なる点は、図10A及び図10Bに示すように、ゲート電極310の傾斜部310bが二重テーパーを有することである。すなわち、傾斜部310bは、基板300に隣接して設けられ、基板300の面に対して第1角度 1をなす傾斜面を有する第1厚さh1の第1傾斜部310b′と、第1傾斜部310b′上に設けられ、基板300の面に対して第2角度 2をなす傾斜面を有する第2厚さh2の第2傾斜部310b″とを含む。そして、第1角度 1は第2角度 2よりも大きいことが好ましく、傾斜部310bの上側のエッチング度が高い。また、この場合、第2角度 2は約2°~約50°の範囲であり、第2角度 2を有する第2傾斜部310b″が、傾斜部310bの全厚さの半分以上を占める。したがって、第1傾斜部310b′は、傾斜部310bの全厚さの半分以下であり、また、ゲート電極310の平坦部の厚さhの1/2以下であってもよい。

10

20

30

40

### [0054]

説明していないアクティブ層 3 3 0 は、両端がドープされてソース領域 3 3 0 b 及びドレイン領域 3 3 0 c として定義され、ソース電極 3 5 0 及びドレイン電極 3 6 0 との接続領域となる。そして、アクティブ層 3 3 0 のソース領域 3 3 0 b とドレイン領域 3 3 0 c との間は真性領域であって、薄膜トランジスタのチャネル領域として用いられる。

#### [0055]

アクティブ層 3 3 0 とソース電極 3 5 0 及びドレイン電極 3 6 0 との層間には、接続部を除いて層間絶縁膜 3 4 0 が設けられる。ソース電極 3 5 0 及びドレイン電極 3 6 0 は、層間絶縁膜 3 4 0 に設けられたコンタクトホールを介してアクティブ層 3 3 0 のソース領域 3 3 0 b 及びドレイン領域 3 3 0 c に接続される。

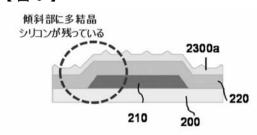

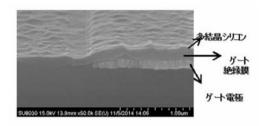

[0056]

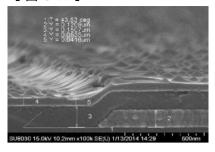

図13A及び図13Bは、それぞれゲート電極の傾斜部を二重段差で形成した直後、及びその上部にシリコン層を形成した後、結晶化した後の状態を示したSEM像である。

[ 0 0 5 7 ]

図 1 3 A 及び図 1 4 C に示すように、ゲート電極 3 1 0 を形成した直後には、ゲート電極 3 1 0 をパターニングするために用いられた感光膜パターン 3 1 5 B が残っており、ほぼゲート電極 3 1 0 の平坦部 3 1 0 a に相当する幅が残っている。また、図 1 0 A に示すように、ゲート電極 3 1 0 の平坦部 3 1 0 a の周辺の傾斜部 3 1 0 b が 'a'の幅で残っており、図 1 0 A、図 1 0 B 及び図 1 2 に示すように、傾斜部 3 1 0 b 内に高い傾斜の第 1 傾斜部 3 1 0 b ,及び相対的に低い傾斜の第 2 傾斜部 3 1 0 b "が備えられる。

[0058]

このようなゲート電極 3 1 0 の上側の感光膜パターン 3 1 5 B を現像で除去した後、基板 3 0 0 上に、ゲート電極 3 1 0 の上側を覆うようにゲート絶縁膜 3 2 0 及び非晶質シリコン層 3 3 0 0 を連続的に堆積する。その後、例えばレーザーを照射して非晶質シリコン層 3 3 0 0 を結晶化し、これを冷却して、図 1 1 のように、多結晶シリコン層 3 3 0 0 a を形成する。冷却過程で結晶質の多結晶シリコン同士が凝集する凝集現象があっても、傾斜部の主な低いテーパーによって、図 1 3 B に示すように、多結晶シリコン層 3 3 0 0 a の傾斜部でも多結晶シリコンの損失がほとんどなく、これによって多結晶シリコン層 3 3 0 0 a の断線が発生しなくなる。

[0059]

多結晶シリコン層 3 3 0 0 a は、その後、特定の形状にパターニングされ、パターニングされた両端にドーピングが行われる。これにより、図 1 2 のソース領域 3 3 0 b 及びドレイン領域 3 3 0 c とそれらの間に真性領域 3 3 0 a のチャネルを有するアクティブ層 3 0 を形成する。

[0060]

以下、本発明の第 2 例による薄膜トランジスタに適用するための傾斜部の二重段差を有するゲート電極の形成方法を説明する。図 1 4 A 乃至図 1 4 C は、本発明の第 2 実施例に係る薄膜トランジスタのゲート電極の形成方法を示す工程断面図(II-II <sup>'</sup>線に沿った断面図)である。

[0061]

図14Aに示すように、まず、基板300上に金属を堆積し、第1感光膜パターン315を用いて堆積した金属をウェットエッチング又はドライエッチングして、第1ゲートパターン層3100Aを形成する。ここで、第1感光膜パターン315が有する幅は、形成しようとするゲート電極310の平坦部とその周辺の傾斜部に対応する'b'の幅(例えば図10Aを参照)を有する。そして、基板300上に堆積した金属の厚さ'h'は1000 以上である。基板300上に堆積された金属は、同一の金属又は同一の金属合金をスパッタリングなどの方式で形成した単一層である。

[0062]

図 1 4 B に示すように、エッチング装置内の酸素( O  $_2$  )の含有量を増加し、第 1 感光膜パターンをアッシング( a s h i n g )して幅を減少させて第 2 感光膜パターン 3 1 5

10

20

30

40

10

20

30

40

50

A を形成し、同一の過程で、第 1 ゲートパターン層 3 1 0 0 A の側部のエッチングを行うことで、第 1 傾斜部 3 1 0 b 'の傾斜に相当する 1 次傾斜を有する第 2 ゲートパターン 3 1 0 0 B を形成する(例えば図 1 2 を参照)。

### [0063]

この工程において、第2ゲートパターン層3100Bを形成する過程で第1ゲートパターン3100Aの上側が下側よりもさらに除去された理由は、第1感光膜パターン315をアッシングして第2感光膜パターン315Aを形成する際にその幅が減少したためである。また、エッチング装置の上側から入ってくるドライエッチングプラズマの反応量が、第1感光膜パターン315が露出した上側のほうが大きいためである。

## [0064]

次いで、図14Cに示すように、エッチング装置内の酸素(〇₂)の含有量を増加し、第2感光膜パターンをアッシング(ashing)して再度幅を減少させて第3感光膜パターン315Bを形成し、同一の過程で、第2ゲートパターン層3100Bの側部のエッチングを行うことで、2次傾斜を有する第3ゲートパターンを形成する。第3ゲートパターンは、図12の最終的なゲート電極310となる。この過程で用いられるドライエッチングプラズマは、感光膜成分のエッチング選択比がゲート電極形成用の金属のエッチング選択比よりも大きいので、相対的にアッシング及びエッチング過程で第3感光膜パターンの315Bの除去幅がさらに大きく、また、ゲート電極310の下端部の幅を、図14Aの過程で形成された幅'b'の水準に維持することができる。そして、形成された前記ゲート電極310は、傾斜部の第1傾斜部310b'及びその上部の第2傾斜部310b"での傾斜が異なるテーパーを有することができる。そして、最終的に形成された第3ゲートの傾斜が異なるテーパーを有することができる。そして、最終的に形成された第3ゲートの傾斜が異なるテーパーを有することができる。そして、最終的に形成された第3ゲートの傾斜が異なるテーパーを有することができる。そして、最終的に形成された第3ゲートの傾斜が異なるテーパーを有することができる。そして、最終的に形成された第3ゲートの傾斜が異なるテーパーを有することができる。そして、最終的に形成された第3ゲートの傾斜が異なるテーパーを有することができる。

#### [0065]

図14A乃至図14Cの工程は、同一のプラズマエッチング装置で行うことができる。 感光膜パターンのアッシングが必要な場合は、エッチング装置内の酸素量を増加すればよい。アッシングされた感光膜パターンの下部のゲートパターン層の金属のエッチングは、 感光膜成分のエッチング選択比がゲート金属のエッチング選択比よりも高いドライエッチングプラズマを用いて、上側のエッチングがより良好に行われるようにする。

## [0066]

上述した方法によって、ゲート電極 3 1 0 は、多層や異種の金属の部分に分けて形成せず、1回のゲート金属の堆積工程の後、感光膜及びエッチング選択比などを調整することで、相対的に低い傾斜の第 2 傾斜部 3 1 0 b "及びこれよりも小さい厚さの第 1 傾斜部 3 1 0 b "を含む二段階の傾斜部がある単一層で形成することができる。

## [0067]

上述した第1実施例及び第2実施例によって形成された薄膜トランジスタを、基板上にマトリクス状に区分された画素にそれぞれ1つ以上配置することで、表示装置のバックプレーン基板を形成することができる。例えば、液晶パネルの場合、各画素において、上述した低段差の傾斜部を有するゲート電極上に、レーザー照射により結晶化した多結晶シリコンのアクティブ層を備えた形態で薄膜トランジスタが1つずつ備えられ、アクティブ層の両端に接続されたソース電極及びドレイン電極のうちドレイン電極と接続された画素電極をさらに備えて、各画素の薄膜トランジスタの選択駆動で画素別階調表現で表示を行うことができる。

# [0068]

また、有機発光表示パネルの場合は、各画素は、上述した低段差の傾斜部を有するゲート電極上に、レーザー照射により結晶化した多結晶シリコンのアクティブ層を有する薄膜トランジスタを2つ以上備えることができる。各画素は更に、薄膜トランジスタのアクティブ層の両端に接続されたソース電極及びドレイン電極のうちドレイン電極に接続され、2つの電極とそられの間に有機発光層が備えられた有機発光ダイオードを備えることができる。これにより、各画素の薄膜トランジスタの選択駆動で画素別階調表現で表示を行う

ことができる。この場合、ドレイン電極が、有機発光ダイオードの第 1 電極として機能することもできる。

## [0069]

一方、以上で説明した本発明は、上述した実施例及び添付の図面に限定されるものではなく、本発明の技術的思想を逸脱しない範囲内で様々な置換、変形及び変更が可能であるということは、本発明の属する技術分野における通常の知識を有する者にとって明らかである。

## 【符号の説明】

## [0070]

2 0 0 , 3 0 0 基板

2 1 0 , 3 1 0 ゲート電極

2 1 0 a , 3 1 0 a 平坦部

2 1 0 b , 3 1 0 b 傾斜部

2 2 0 , 3 2 0 ゲート絶縁膜

2 3 0 0 , 3 3 0 0 非晶質シリコン

2 3 0 , 3 3 0 アクティブ層

2 4 0 , 3 4 0 層間絶縁膜

250,350 ソース電極

2 6 0 , 3 6 0 ドレイン電極

# 【図1】

## 【図2】

【図3】

## 【図4】

【図5A】

【図5B】

【図6】

【図7】

【図8C】

【図9A】

【図8A】

【図8B】

【図9D】

【図10A】

【図10B】

【図11】

【図12】

【図13A】

【図13B】

【図14A】

【図14B】

## フロントページの続き

(72)発明者 呉 錦 美

大韓民国 ソウル特別市 西大門區 税務署二ガギル 47 (弘濟洞)

(72)発明者 オム 惠 先

大韓民国 大邱廣域市 西區 國債報償路七八ギル 20-1 (飛山洞)

(72)発明者 楊 仙 英

大韓民国 京畿道 富川市 遠美區 上洞路 57 2411棟 1201號 (上洞, ハンボクハン メウル ソハグランブル アパート)

(72)発明者 李 正 仁

大韓民国 ソウル特別市 九老區 九老中央路一八ギル 56 402號 (九老洞, スンサム ハイツ アパート)

F ターム(参考) 3K107 AA01 BB01 CC21 CC45 EE04

5F110 AA26 CC08 EE02 EE06 EE23 EE24 EE44 FF30 GG02 GG13 GG35 GG45 NN02 NN44 NN71 PP04 QQ02 QQ04 QQ09