(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4177097号 (P4177097)

(45) 発行日 平成20年11月5日(2008, 11.5)

(24) 登録日 平成20年8月29日(2008.8.29)

(51) Int. Cl.

HO1L 33/00 (2006.01)

HO1L 33/00

FL

請求項の数 15 (全 12 頁)

(21) 出願番号 特願2002-524235 (P2002-524235) (86) (22) 出願日 平成13年8月31日 (2001. 8. 31)

(65) 公表番号 特表2004-508720 (P2004-508720A) (43) 公表日 平成16年3月18日 (2004.3.18)

(86) 国際出願番号 PCT/DE2001/003348 (87) 国際公開番号 W02002/019439

(87) 国際公開日 平成14年3月7日 (2002.3.7) 審査請求日 平成15年3月25日 (2003.3.25)

(31) 優先権主張番号 100 42 947.5

(32) 優先日 平成12年8月31日 (2000.8.31)

(33) 優先権主張国 ドイツ (DE)

前置審査

(73)特許権者 599133716

オスラム オプト セミコンダクターズ ゲゼルシャフト ミット ベシュレンクテ

ル ハフツング

C

Osram Opto Semicond

uctors GmbH

ドイツ連邦共和国、93055 レーゲン スブルグ、ライプニッツシュトラーセ 4 Leibnizstrasse 4, D -93055 Regensburg,

Germanv

|(74)代理人 100061815

弁理士 矢野 敏雄

|(74)代理人 100094798

弁理士 山崎 利臣

最終頁に続く

(54) 【発明の名称】 1 1 1 - V 窒化物半導体ベースの放射線を発する半導体チップを製造する方法および放射線を発 する半導体チップ

## (57)【特許請求の範囲】

## 【請求項1】

薄層素子(11)の層系をエピタキシャル基板(100)上に析出させ、

薄層素子を支持体(5)に結合させ、

エピタキシャル基板(100)を薄層素子から除去する、III - V窒化物半導体材料をベースとした薄層素子(11)を有する放射線を発する半導体チップを製造する方法において、

エピタキシャル基板(100)が、固着層(3)によって、成長層(2)に結合されているポリSiC、ポリGaN、SiC、GaNまたはサファイアからなる基板ボディ(1)を有しており、前記成長層(2)はSi(111)層を有し、かつ前記固着層(3)は酸化ケイ素または窒化ケイ素からなり、

成長層(2)上に、薄層素子(11)の層系をエピタキシャル成長によって析出させることを特徴とする、III-V室化物半導体材料をベースとした薄層素子(11)を有する放射線を発する半導体チップを製造する方法。

#### 【請求項2】

支持体(5)を被着する前に、薄層素子(11)の層系を、互いに分離された多数の個別の薄層素子(11)に構造形成する、請求項1記載の方法。

#### 【請求項3】

エピタキシャル基板を剥離した後、薄層素子(11)を接触させる、請求項1<u>または2</u> 記載の方法。

## 【請求項4】

層系を被着した後、

介在支持体を層系上に被着する段階、

エピタキシャル基板を剥離する段階、

支持体(5)を、層系の、エピタキシャル基板を剥離した側に被着する段階、および 介在支持体を剥離する段階で方法を続行する、請求項1から<u>3</u>までのいずれか1項記載 の方法。

## 【請求項5】

介在支持体を被着する前に、多数のGaNベースの層(4)を構造形成する、請求項<u>4</u> 記載の方法。

【請求項6】

介在支持体を剥離した後に、薄層素子(11)を接触させる、請求項<u>4</u>または<u>5</u>記載の方法。

# 【請求項7】

第1の層として、成長層(2)の表面に、導電性の緩衝層(9)を形成する、請求項1から6までのいずれか1項記載の方法。

## 【請求項8】

緩衝層(9)を、A1GaNベースの多数の個別層から形成する、請求項<u>7</u>記載の方法

【請求項9】

緩衝層(9)の、成長層(2)に隣接する個別層が、成長層(2)の層から見て前記個別層に後に配置された個別層よりも高いA1含有量を有している、請求項<u>8</u>記載の方法。

## 【請求項10】

緩衝層(9)の、成長層(2)とは反対の側の個別層が、成長層(2)の層から見て前記個別層の前に配置された個別層よりも低いA1含有量を有している、請求項<u>8</u>または<u>9</u>記載の方法。

# 【請求項11】

互いに間隔をおいた多数の導電性の領域を、成長層(2)上に被着する段階、および 平坦化する充填層(7)を被着する段階によって緩衝層を形成する、請求項<u>7</u>から<u>10</u> までのいずれか1項記載の方法。

【請求項12】

多数の導電性の領域を、InGaN材料、GaN材料またはInN材料の使用によって 形成する、請求項11記載の方法。

【請求項13】

充填層(7)が、平坦な層を得られるように高いAl成分を有するAlGaNまたはA 1GaInNを有している、請求項11または12記載の方法。

【請求項14】

成長層の厚さが、約1~20 $\mu$ m、特に10 $\mu$ mより小さい、請求項1から<u>13</u>までのいずれか1項記載の方法。

【請求項15】

エピタキシャル基板が、薄層素子(11)の材料に適合した熱膨張係数またはこの材料よりも大きな熱膨張係数を有している、請求項1から<u>14</u>までのいずれか1項記載の方法

【発明の詳細な説明】

#### [00001]

本発明は、請求項1の上位概念に記載のIII-V窒化物半導体材料をベースとした放射線を発する半導体チップを製造する方法、および請求項19の上位概念に記載の放射線を発する半導体チップに関する。

## [00002]

GaNベースの放射線を発する半導体デバイスは、たとえばUS5874747により公

10

20

30

30

40

知である。このような半導体デバイスは、GaNまたはこれをベースとした材料からなる多数の層を有する半導体ボディを有している。上記の刊行物によれば、GaNをベースとした多数の層は、SiC基板上に被着されている。

#### [0003]

この場合、III - V窒化物半導体材料には、GaNから誘導されたまたはGaNに類する材料、およびその上に形成されるたとえば三成分または四成分の混晶が属する。特に、材料AIN、InN、AIGaN(AI  $_{1-x}$  Ga  $_x$  N、0 x 1)、InGaN(In  $_{1-x}$  Ga  $_x$  N、0 x 1)、InGaN(In  $_{1-x}$  Ga  $_x$  N、0 x 1)およびAIInGaN(Al  $_{1-x-y}$  In  $_x$  Ga  $_y$  N、0 x 1、0 y 1)がこれに属する。

[0004]

以下、「III - V窒化物半導体」という名称は、上に述べた材料のグループを指すものとする。さらに、この名称は、前述の材料系の層をエピタキシャル成長により製造する際に緩衝層を形成するために使用する材料を含んでいる。

[0005]

さらに、USS679152より、GaNベースの半導体ボディをエピタキシャル成長によって適当な基板、たとえばSi基板上に製造することが公知であり、この場合、GaN層をエピタキシャル成長によって析出させた後、インサイトゥ (in situ)で基板を除去する。

[0006]

また、US5786606より、本来のエピタキシャル基板上に形成された中間のSiC基板を有するGaNベースの半導体ボディが公知である。この本来の基板ボディは、製造の際に除去される。

[0007]

SiC基板を有する半導体ボディを使用するということは、半導体デバイスの製造のためにかかる付加的なコストが小さくはないことを意味する。それというのは、SiC基板自体に極めて大きなコストがかかるからである。III・V窒化物半導体材料をベースとしたそれぞれの半導体ボディと共に、SiC基板の部材を半導体デバイスに組付ける場合には、半導体デバイスのためのコストは直接的にSiC基板のコストに結びつく。そのため、半導体デバイスを安価に製造することは困難である。

[00008]

さらに、III-V窒化物半導体をベースとした半導体チップ中のSiC基板は発光効率の低下を招きうる。なぜならば、SiCは、III-V窒化物半導体から発せられた放射線を部分的に吸収するので、放出可能な放射線の割合を低下させてしまうからである。

[0009]

US5679152に記載されたSi基板を使用する製造方法では、極めて薄い基板しか使用することができず、これらの基板は、エピタキシャル成長後に直ちに除去しなくてはならない。通常、このような基板の許容厚さは、1μmより薄い。

[0010]

この基板の薄さは、ケイ素とIII - V窒化物半導体をベースとした材料との間で熱膨張 係数が異なるために起こるクラック形成を防ぐために必要である。

[0011]

本発明の課題は、技術的に簡単にかつこれにより安価に製造可能であって高い外部量子効率を有する、III - V 窒化物半導体材料をベースとした放射線を発する半導体チップを得ることである。

[0012]

さらに、本発明の課題は、上記の半導体チップのための製造方法を提供することである。

[0013]

これらの課題は、請求項1に記載の方法および請求項19に記載の半導体チップによってそれぞれ解決される。本発明の有利な実施態様は、引用形式請求項2~18および20~

10

20

30

40

25に記載されている。

# [0014]

本発明によれば、III - V室化物半導体材料ベースの放射線を発する半導体チップが薄層素子として形成されている。

# [0015]

この場合、薄層素子というのは主にもっぱら、III-V室化物半導体材料をベースとしたエピタキシャル層の積層体からなる半導体層系と解釈される。

#### [0016]

薄層素子は、多数のIII - V窒化物半導体エピタキシャル層からなっており、この場合、この半導体ボディは、一方の側で n 型のエピタキシャル層によって、これとは反対の側で p 型のエピタキシャル層によって区切られている。

[0017]

薄層素子は、p型の側で導電性の支持体の上に被着されていて、この支持体は、薄層素子のための取付け面を有していて、有利にはさらに薄層素子の接触のために使用することができる。

#### [0018]

薄層素子のn型の側には、対応する接触面が形成されている。以下、「接触面」という名称は、さらなる記載がない場合には、この接触面を指すものとする。

## [0019]

特に有利には、このようにして形成された半導体チップが、たとえばSiC基板のような通常の厚さ(>100μm)のエピタキシャル基板を有していないということであり、これによって、半導体デバイスのための材料コストは低減される。

## [0020]

この薄層構造の別の利点は、半導体ボディが、放射線を吸収する基板をわずかしか有していない、または放射線を吸収する基板をまったく有していないということである。

## [0021]

したがって、発光効率を、反射性の支持体を使用することによって増大させることができ る

## [0022]

本発明の有利な別の実施態様では、薄層素子においてn型の側で区切っているエピタキシャル層を、導電性の緩衝層として形成する。

# [0023]

GaNベースの半導体ボディの製造におけるこの緩衝層の形成は、エピキシャル基板と緩衝層に続くエピタキシャル層との間での格子不整合を補償するために一般に行われている

#### [0024]

導電性の緩衝層は、このように形成された半導体ボディにより縦方向に導電性の半導体デバイスが得られるという大きな利点を有する。

## [0025]

絶縁性の緩衝層に対して、この導電性の緩衝層は有利であり、それというのは、縦方向に 導電性の半導体チップはより低コストで接触を可能にするからである。さらに、活性層を 横方向へより大きく拡張することができる。

#### [0026]

本発明の特に有利な実施態様では、緩衝層は多層に形成されている。異なる組成を有する多数の層の連続体によって、有利には、緩衝層の導電性の最適化および緩衝層に続くGaNベースの層との整合の最適化が可能となる。

## [0027]

本発明の有利な実施態様では、緩衝層は、AlGaNベースの材料たとえばAl $_{1-x}$ Ga $_x$ N[式中、0 x < 1] およびAl $_{1-x-y}$ In $_x$ Ga $_y$ N[式中、0 x < 1、0 y < 1、x + y < 1] からなる。

10

20

30

40

#### [0028]

この場合、特に有利には、良好な導電性の緩衝層を得るために、緩衝層の、接触面の方を向いた側が、低いA1含有量で形成されている。

#### [0029]

このような低い A 1 含有量を有する層の表面品質および結晶の品質は低いので、緩衝層の、接触面とは反対の側を高い A 1 含有量で形成するとさらに有利である。この高い A 1 含有量によって、緩衝層の表面品質は高くなり、後続の I I I - V 室化物半導体ベースの層への良好な整合が得られる。

## [0030]

緩衝層が、接触面の側で低いA1含有量を有し、これとは反対の側で高いA1含有量を有することによって、同時に高い表面品質を備えた導電性の緩衝層が得られ、極めて有利である。

#### [0031]

本発明によれば、III-V室化物半導体材料をベースとした放射線を発する半導体素子の製造のために、III-V窒化物半導体ベースの層をエピタキシャル基板上に被着させる。この場合、このエピタキシャル基板の基板ボディは、III-V窒化物半導体材料に適合する熱膨張係数かまたはIII-V窒化物半導体材料と比較してより大きな熱膨張係数を有し、かつこのエピタキシャル基板は、エピタキシャル側で、有利にはSi(111)を有する薄い成長層によって区切られている。

## [0032]

したがって、有利には、III・V窒化物半導体ボディを製造する際、エピタキシャル基板の熱膨張が基板ボディによって決定されるので、これにより、基板は、被着すべき層と熱的に類似した挙動を有する。

#### [0033]

Si(111)表面は、六方晶構造を有しているので、III-V室化物半導体用のエピタキシャル表面として適している。

#### [0034]

さらに、Si(111)表面は、簡単に加工してエピタキシャル成長に備えることができる。Si(111)の加工技術は、この材料が極めてよく使用されているために半導体産業において極めて周知であり、実証済みである。

#### [0035]

したがって、有利には、市販のSiC基板の直径よりも著しく大きな直径を有するエピタキシャル基板を製造することも可能である。

# [0036]

Si(111)表面の達成可能な表面品質も、SiC基板の表面品質より著しく向上する

# [0037]

基板ボディとしては、有利には、GaNベースの層へ良好に熱的に適合するので、多結晶SiC(ポリSiC)、GaNまたは多結晶GaN(ポリGaN)を使用する。さらに、基板ボディは、サファイア( $Al_2O_3$ )を含有していてよい。サファイアは、II I-V 窒化物半導体材料よりも大きな熱膨張係数を有している。

#### [0038]

この基板ボディは、従来の技術で使用される基板よりも著しく低コストである。それというのは、半導体ボディが成長層の表面上に析出するので、有利には、基板ボディの結晶特性に対する要求が低減されるからである。このように要求が低減されることによって、特に低コストの多結晶材料を使用することができる。

#### [0039]

有利には、基板ボディは固着層によって成長層と結合されており、この固着層は、酸化ケイ素または窒化ケイ素からなる。

# [0040]

10

20

30

40

基板ボディと成長層との間の固着層の形成は簡単に行うことができ、この場合、上で述べた材料は、特に安定な結合を保証する。

#### [0041]

本発明による製造方法の特に有利な実施態様では、 I I I - V 室化物半導体ベースの層を被着させた後に続く次の段階で、 I I I - V 室化物半導体ベースの層の上に支持体を被着する。

#### [0042]

その後、III・V室化物半導体ベースの層からエピタキシャル基板を剥離する。

#### [0043]

これによって、有利には、エピタキシャル基板もしくは基板ボディの再使用または継続使 用が可能となる。

#### [0044]

Si(111)成長層をエピタキシャル表面として使用することは、エピタキシャル基板を剥離する場合に有利である。それというのは、半導体ボディは、たとえばエッチングによって簡単に基板ボディから分離できるからである。この場合、Si(111)成長層が犠牲層となる。

## [0045]

特に有利には、この製造方法では、単結晶SiC基板ボディを使用した半導体ボディの低コストの製造が可能となる。なぜならば、コストのかかるSiC基板ボディの再使用または継続使用ができるからである。

#### [0046]

本発明による製造方法の有利な実施態様では、エピタキシャル基板を剥離した後、半導体ボディの、エピタキシャル基板を剥離した面上に接触層を被着する。

#### [0047]

本発明による製造方法の有利な実施態様では、エピタキシャル基板を剥離する前に、多数のIII・V窒化物半導体層を構造形成する。

#### [0048]

この場合、構造形成というのは、エピタキシャル層を、エピタキシャル基板上で間隔を置いて互いに並んで配置された多数の個別のエピタキシャル層積層体に横方向で分割する手段であると解釈される。有利には、エッチングによってエピタキシャル層積層体を剥離する場合、この構造形成によって、エッチング攻撃にさらされる表面が拡大する。

# [0049]

本発明の有利な実施態様では、前述の製造方法において、支持体の代わりに、まず介在支持体を、III-V窒化物半導体材料をベースとしたエピタキシャル層上に被着する。その後、同様にエピタキシャル基板を剥離し、エピタキシャル層の、エピタキシャル基板が剥離した側に支持体を被着する。次の段階で、介在支持体を剥離する。

# [0050]

この実施態様によって、有利には、III-V室化物半導体材料をベースとした層の積層順序が、支持体に関して前述の製造方法と逆になっている。このような逆転は有利であり、これによって、後続の方法、特にこの逆転した積層順序を必要とするパッケージングでの使用も可能となる。

#### [0051]

本発明による製造方法の特に有利な実施態様では、第1の層として、エピタキシャル基板上に導電性の緩衝層を被着する。

#### [0052]

このような緩衝層は、これに続くエピタキシャル層に対して、最適に整合した格子構造を 有する表面を得るために特に有利であり、この格子構造は同時に、後続の層材料によって 良好に濡れ、これにより、後続の層の均一な成長が可能となる。

#### [0053]

緩衝層が導電性を有していることによって、上で述べたようなポジティブな性質を有する

20

10

30

40

縦方向に導電性の半導体素子を得ることができる。

## [0054]

有利には、緩衝層を、多数のAlGaNベースの個別層から形成する。

#### [0055]

このことは、高い A 1 含有量を有する緩衝層が、 I I I - V 室化物半導体材料をベースとした次なる層に対して格子整合しかつ良好に濡れることのできる表面を形成するので、有利である。しかし、高い A 1 含有量を有する緩衝層の導電性は低い。一方で、低い A 1 含有量を有する緩衝層は電気をよく通すが、結晶の品質および表面品質は低い。

## [0056]

このような多数の層を組み合わせて形成することにより、高い導電性と高い結晶の品質とを兼ね備えることが可能となる。

## [0057]

さらに、基板側に、比較的高いA1含有量を有する層を形成し、エピタキシャル層側に、 つまり緩衝層の、エピタキシャル基板とは反対の側に、比較的低いA1含有量を有する層 を析出させると有利である。

#### [0058]

本発明による製造方法の特に有利な別の実施態様では、緩衝層を2段階で形成する。

#### [0059]

第 1 の段階では、エピタキシャル基板の成長層の上に、多数の導電性の領域を被着する。この導電性の領域のための材料としては、特に、 $In_{1-x}Ga_xN[$ 式中、0x<1 ] および $In_{1-x-y}Al_xGa_yN[$ 式中、0x<1、0x<1 、0x<1 のようなInGaNベースの材料またはInGaNが適している。

## [0060]

この場合、SiおよびGaはドメインを形成する傾向があるので、導電性の領域の広範囲にわたる均一な配置が得られる。

## [0061]

第2段階で、これらの多数の導電性の領域を、プラナリゼーション加工する充填層でカバーし、導電性の領域間の間隙を充填する。

## [0062]

この場合、材料としては、特に、高いAl含有量を有するAlGaN化合物が適している。このようにして製造された緩衝層は、次のIII・V窒化物半導体材料をベースとした層の析出に極めてよく適していてかつ高い導電性を有している。

#### [0063]

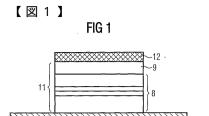

本発明のさらなる特徴、利点および合目的点は、以下に示す3つの実施例により図1~3に基づき説明する。

#### [0064]

図1は、本発明による構成素子の実施例の概略的な断面図であり、

図2は、本発明による製造方法の実施例を説明した概略図であり、

図3は、本発明による導電性の緩衝層のための製造方法を説明した概略図である。

#### [0065]

種々異なる実施例において、同様のまたは同様に作用する構成部分には、それぞれ同じ参 照符号を付与してある。

## [0066]

図1に示した放射線を発する半導体チップは、薄層素子の形の半導体ボディ11を有しており、この半導体ボディ11は、導電性の緩衝層9と、特にIII・V窒化物半導体材料をベースとしたエピタキシャル層を有している層系8とからなっている。緩衝層9上には接触面12が被着されていて、この接触面12は、図1に示したものとは異なって半導体ボディ11の上側の一部しか覆っていなくてもよい。また、接触面12は、たとえばA1を有しているまたはA1からなっていて、ボンドパッドとして形成されていてよい。

## [0067]

50

10

20

30

層系 8 の構造は、半導体ボディ 1 1 もしくはこれによって形成されるチップの機能性を規定する。この層系 8 は、放射線を発する役割を果たす活性層も含んでいる。

#### [0068]

半導体ボディ11は、エピタキシャル基板を有していない。

#### [0069]

半導体ボディ11は、緩衝層9の側ではn型に、これと反対の側ではp型に形成されている。

## [0070]

p型の側で、半導体ボディ11は、導電性の支持体5の主面に被着されている。

#### [0071]

支持体5は、半導体ボディ11とは反対の側で、第2の接触面10を有している。

#### [0072]

有利には、このようにして形成された半導体チップは、縦方向に、つまり層面に対して垂直に一貫して導電性である。これによって、横方向に広範囲にわたって均一に電流が構成素子を通って流れることができ、かつ簡単な接触が可能となる。

## [0073]

また、別の利点は、チップを側面方向に問題なくスケーリングできるということである。 この場合、横方向のスケーリングとは、チップの横方向の別の設定寸法への移行と理解されたい。この移行は、チップが横方向に構造形成されていない、つまりトポロジーを有していないので、簡単にできる。

#### [0074]

これに対して、たとえば主面上に異なる2つの接触面を有しているような横方向に構造形成された素子では、横方向のスケーリングの際には、横方向の構造の適合を考慮しなければならない。

#### [0075]

縦方向に導電性のチップのための条件は、導電性の緩衝層 9 である。この層は、たとえば 2 層にIII・V窒化物半導体材料から形成されている。緩衝層 9 のさらに詳しい性質は、図 3 に基づいて導電性の緩衝層の製造と共に説明する。

## [0076]

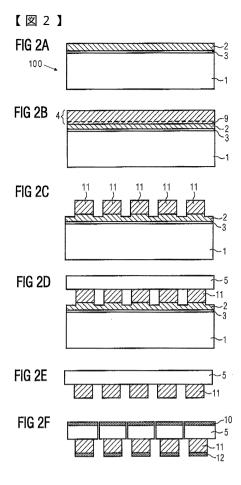

III - V窒化物半導体材料は、直接バンド遷移型でありかつバンドギャップが大きいので、本発明により形成された半導体ボディは、特に黄色、緑色、緑青色または紫色のスペクトル領域に中心波長を有する発光ダイオードチップ、特に高い光度を有する発光ダイオードおよび緑色から紫色のスペクトル領域に発光波長を有する半導体レーザーの実現のために適している。

# [0077]

図2に、6つの中間段階a~fで概略的に、本発明による製造方法の実施例を示す。

#### [0078]

出発点では、多層のエピタキシャル基板 1 0 0 が形成されている(図 2 a)。基板ボディ1 は、Si C、有利にはポリSi C からなる。

#### [0079]

基板ボディ1上には、有利には、酸化ケイ素からなる固着層3が形成されていて、この固着層3は、基板ボディを、たとえばSi(111)からなる薄い成長層2に結合している

# [0080]

この場合、成長層 2 の厚さは、この熱膨張がこの下に設けられた基板ボディ 1 によってほぼ規定されるように薄く選択されている。通常、成長層 2 の厚さは、ほぼ 0 . 1 ~ 2 0  $\mu$  mであり、有利には 1 0  $\mu$  mよりも小さく、特に有利には 0 . 1 ~ 2  $\mu$  mである。

#### [0081]

成長層2の表面には、次の段階で、III-V窒化物半導体材料からなる多数の層4を析出させる(図2)。

10

20

30

40

#### [0082]

この場合、有利には、まず、導電性のAIGaN緩衝層9を成長層2の表面に形成する。 それというのは、GaN自体およびInGaN化合物の、Si(111)‐またはSiC 表面への濡れ性が悪いからである。

# [0083]

緩衝層 9、 およびこの上に析出させる I I I - V 化合物半導体材料をベースとした隣接する層は、 n 型に形成する。

## [0084]

反対の側、つまりエピタキシャル基板 1 0 0 と反対の側では、エピタキシャル層積層体を、1 つまたは複数の p 型の層によって区切る。

# [0085]

n型層とp型層との間には、A  $1_{1-x-y}$  G  $a_x$  I  $n_y$  N [式中、 $0_x$  1、 $0_x$  1、x+y 1] ベースの多数の層を形成する。これらの層は、狭義には放射線を発する役割を果たしている。これには、当業者によく知られている放射線を発するすべての半導体構造が、特にシングル・またはダブルヘテロ構造および単一・または多重量子井戸構造を形成している  $p_x$  n接合が適している。

## [0086]

次の段階では、メサエッチングによって、Al $_{1-x-y}$ Ga $_x$ In $_y$ Nベースの層を横方向に構造形成する(図2c)。これによって、エピタキシャル基板 100上に互いに並んで配置された多数の個別の層積層体が形成される。これらの層積層体はほぼ、放射線を発するチップのまだ個別化されていない薄層素子 11である。

#### [0087]

メサエッチングは、エピタキシャル基板100の成長層2内にまでおよび、これによって、次の段階で、薄層素子11をエピタキシャル基板100から簡単に剥離することができる。

# [0088]

$A\ 1_{\ 1-x-y}\ G\ a_x\ I\ n_y\ N$ ベースの層 4 の構造形成後、薄層素子  $1\ 1$  の、エピタキシャル基板  $1\ 0\ 0$  とは反対の p 型の側に、支持体 5 または選択的には介在支持体  $1\ 3$  を被着する。支持体材料としては、たとえば  $G\ a\ A\ s$  または  $C\ u$  を使用することができる。

# [0089]

次の段階(図2e)で、エピタキシャル基板100を薄層素子11から剥離する。この剥離は、湿式化学式にエッチングによって行い、この際、成長層2を破壊する。この場合、成長層2をエッチングによって分離する湿式化学式の剥離に必要とされるコストは、たとえばSiC基板ボディの剥離よりもはるかに小さい。

## [0090]

選択的には、介在支持体13を使用して、エピタキシャル基板100を剥離した後にその位置に支持体5を被着して、その後、介在支持体13を剥離する。

## [0091]

この段階の最後に形成されている構造は、両方法で極めて類似しており、相違しているのは、介在支持体13を使用する場合には、緩衝層9が、半導体ボディの、支持体5の方を向いた側に設けられているという点だけである(図2e右)。もう1つの方法では、緩衝層9が、半導体ボディ11の、支持体5とは反対の側に形成される。

## [0092]

続いて、半導体ボディ11に接触面12を、支持体5に接触面10を設ける。さらに続いて、支持体5をそれぞれ半導体ボディ11間で分離し、これにより、多数の図1に示した 半導体チップが得られる(図2f)。

## [0093]

有利には、薄層素子11を支持体5もしくは介在支持体13への結合することによって、引き続き行うエピタキシャル基板100の剥離と関連して、エピタキシャル基板ボディ1の再使用が可能となり、これによって、SiCを基板ボディ材料として使用する場合には

10

20

30

40

、大幅なコスト低減が得られる。

# [0094]

さらに、SiC基板で起こるあらゆる吸収損失がなくなる。これによって、発光効率は著しく向上する。

# [0095]

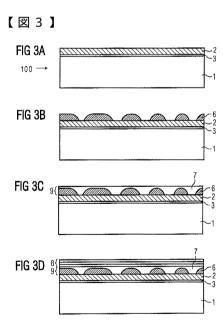

別の製造方法で、ポリSiCまたはポリGaNのような低コストの基板ボディを使用する場合には、その再使用に特に利点がない場合には、基板全体をエッチングで分離することもできる。

## [0096]

図3で、4つの中間段階に基づき概略的に、導電性の緩衝層9の製造を説明する。

## [0097]

エピタキシャル基板 1 0 0 としては、上で述べた製造方法のように、たとえばSi(111)を含むエピタキシャル側の成長層 2 を備えたSiC-またはポリSiC基板ボディ1を使用する(図3a)。

# [0098]

第 1 の段階では、成長層 2 上に、多数の量子点の形の核形成層 6 を析出させる(図 3 b)

#### [0099]

このための材料としては、低いA 1 含有量( < 5 0 %)を有するA 1 G a I n N、 I n G a N またはG a N を使用する。量子点は、高導電性であるが、閉じた層を形成していない。したがって、成長層の表面に、互いにつながっていない多数の導電性の領域が得られる。被覆度は、材料組成に応じて 1 ~ 9 9 % と変化させることができる。

## [0100]

量子点層 6 上に、高い A l 含有量を有する A l G a N ベースの、たとえば A l  $_{\rm x}$  G a  $_{\rm 1}$   $_{\rm x}$  N [式中、 x > 0 . 5 ] の平坦化する充填層 7 を析出させる(図 3 c )。これによって、平坦な構造 9 が得られる。

#### [0101]

導電性の領域 6 は、通路状の結合を緩衝層 9 を通して形成しており、緩衝層 9 の良好な導電性を保証する。

# [0102]

次の段階で、緩衝層 9 上に、特にIII - V化合物半導体材料をベースとしたエピタキシャル層を含む層系 8 を析出させる(図3 c)。このIII - V化合物半導体材料が主に半導体デバイスの機能性を規定する。

#### [0103]

薄層素子および個別の半導体チップを製造するためのさらなる段階は、たとえば図2A~ 2Cに基づき説明した相応の段階に相当する。

# [0104]

上に述べた実施例に基づく本発明の説明は、むろん、発明をこれらの実施例に制限するものではない。

## [0105]

特に、半導体材料は、その都度与えられる範囲内で、必要条件と構成素子のために設けられた使用領域とに適合させることができる。

# [0106]

さらに、半導体ボディの活性層の内部の半導体材料の組成によって、発生する放射線のセンター波長を設定することができる。

# 【図面の簡単な説明】

- 【図1】 本発明による構成素子の実施例の概略的な断面図

- 【図2】 本発明による製造方法の実施例を説明した概略図

- 【図3】 本発明による導電性の緩衝層のための製造方法を説明した概略図

20

10

30

#### フロントページの続き

(74)代理人 100099483

弁理士 久野 琢也

(74)代理人 100110593

弁理士 杉本 博司

(74)代理人 100128679

弁理士 星 公弘

(74)代理人 100135633

弁理士 二宮 浩康

(74)代理人 100114890

弁理士 アインゼル・フェリックス=ラインハルト

(72)発明者 シュテファン バーダー

ドイツ連邦共和国 レーゲンスブルク ドイチュヘルンヴェーク 2

(72)発明者 ミヒャエル フェーラー

ドイツ連邦共和国 バート アップバッハ リルケシュトラーセ 5ベー

(72)発明者 ベルトルト ハーン

ドイツ連邦共和国 ヘマウ アム プファネンシュティール 2

(72)発明者 フォルカー ヘルレ

ドイツ連邦共和国 ヴァルデッツェンベルク アイヒェンシュトラーセ 35

(72)発明者 ハンス - ユルゲン ルーガウアー

ドイツ連邦共和国 ヴェンツェンバッハ タンネンヴェーク 14

#### 審查官 道祖土 新吾

(56)参考文献 特開平11-284228 (JP,A)

特開平11-145515(JP,A)

特開平09-129927(JP,A)

特開2000-101139(JP,A)

特表平11-504764(JP,A)

国際公開第00/034989(WO,A1)

米国特許第05985687(US,A)

米国特許第05851905(US,A)

米国特許第06046464(US,A)

特開平11-145516 (JP,A)

特開昭 6 4 - 5 3 4 0 7 ( J P , A )

特表2002-532873(JP,A)

特開平09-223819(JP,A)

特開平03-296278(JP,A)

特開平10-2226(JP,A)

#### (58)調査した分野(Int.CI., DB名)

H01L 33/00