19 RÉPUBLIQUE FRANÇAISE

#### INSTITUT NATIONAL DE LA PROPRIÉTÉ INDUSTRIELLE

**COURBEVOIE**

11 No de publication :

3 091 389

(à n'utiliser que pour les commandes de reproduction)

21) No d'enregistrement national :

19 06119

(51) Int Cl<sup>8</sup>: **G 06 N 3/06** (2019.01), G 06 F 15/76, 9/30, 9/46, G 06 N 3/08

12)

#### **DEMANDE DE BREVET D'INVENTION**

**A1**

**Date de dépôt :** 07.06.19.

(30) **Priorité**: 31.12.18 GB 1821301.7.

Demandeur(s): Graphcore Limited Société régie par les lois de l'Angleterre et du Pays de Galles — GB.

Date de mise à la disposition du public de la demande : 03.07.20 Bulletin 20/27.

Liste des documents cités dans le rapport de recherche préliminaire : Ce dernier n'a pas été établi à la date de publication de la demande.

Références à d'autres documents nationaux apparentés :

Inventeur(s): ALEXANDER Alan Graham, KNOWLES Simon Christian et GORE Mrudula.

Titulaire(s): Graphcore Limited Société régie par les lois de l'Angleterre et du Pays de Galles.

Mandataire(s): CABINET BEAUMONT.

Demande(s) d'extension :

BANCS DE REGISTRES DANS UN PROCESSEUR À FILS D'EXÉCUTION MULTIPLES.

(57) BANCS DE REGISTRES DANS UN PROCES-SEUR À FILS D'EXÉCUTION MULTIPLES

Processeur comprenant une unité d'exécution à fils d'exécution en barillet pour exécuter des fils d'exécution simultanés, et un ou plusieurs bancs de registres comprenant un ensemble respectif de registres de contexte pour chaque fil simultané. L'un des bancs de registres comprend en outre un ensemble de registres de poids partagés commun à certains ou à la totalité des fils d'exécution simultanés. Les types d'instructions définis dans le jeu d'instructions du processeur comprennent une instruction arithmétique ayant des opérandes spécifiant une source et une destination parmi un ensemble respectif de registres arithmétiques du fil dans lequel l'instruction arithmétique est exécutée. L'unité d'exécution est agencée de manière à, en réponse au code opération de l'instruction arithmétique, réaliser une opération comprenant la multiplication d'une entrée provenant de la source par au moins l'un des poids provenant d'au moins l'un des registres de poids partagés, et placer un résultat dans la destination.

Figure pour l'abrégé: Fig. 4

# **Description**

# Titre de l'invention : BANCS DE REGISTRES DANS UN PROCESSEUR À FILS D'EXÉCUTION MULTIPLES

# Domaine technique

[0001] La présente description concerne un agencement de bancs de registres destiné à être utilisé par des instructions de code machine exécutées dans un processeur à fils d'exécution multiples.

# Technique antérieure

On a trouvé de plus en plus d'intérêt à développer des processeurs conçus pour des applications spécifiques, comme des unités de traitement graphique (GPU) et des processeurs de signal numérique (DSP). Un autre type de processeur spécifique à des applications auquel on a récemment porté de plus en plus d'intérêt est un type dédié à des applications d'intelligence artificielle, dénommé par la demanderesse "IPU" (de l'anglais Intelligence Processing Unit - unité de traitement pour intelligence). Ces processeurs peuvent être utilisés par exemple comme processeurs accélérateurs agencés pour réaliser des tâches allouées par un hôte, comme par exemple pour réaliser un apprentissage ou pour aider à l'apprentissage d'un modèle de connaissance comme un réseau neuronal, ou pour réaliser ou aider à réaliser des prédictions ou des inférences sur la base d'un tel modèle.

[0003] Un algorithme d'intelligence artificielle est basé sur la réalisation itérative de mises à jour d'un "modèle de connaissance", qui peut être représenté par un graphe de multiples nœuds interconnectés. Chaque nœud représente une fonction de ses entrées. Certains nœuds reçoivent les entrées du graphe et certains nœuds reçoivent des entrées provenant d'un ou plusieurs autres nœuds, tandis que les sorties de certains nœuds constituent les entrées d'autres nœuds, et les sorties de certains nœuds fournissent la sortie du graphe (et dans certains cas un nœud donné peut même comporter tout cela : des entrées du graphe, des sorties du graphe et des connexions à d'autres nœuds). En outre, la fonction au niveau de chaque nœud est paramétrée par un ou plusieurs paramètres respectifs, par exemple des poids. Pendant une étape d'apprentissage le but est, sur la base d'un ensemble de données d'entrée expérimentales, de trouver des valeurs pour les divers paramètres telles que le graphe dans son ensemble va générer une sortie souhaitée pour une plage d'entrées possibles. Divers algorithmes pour réaliser cela sont connus dans la technique, comme un algorithme à rétroprogrammation basé sur une descente de gradient stochastique. Sur de multiples itérations basées sur les données d'entrée, les paramètres sont progressivement ajustés pour diminuer leurs erreurs, et ainsi le graphe converge vers une solution. Dans une

étape ultérieure, le modèle appris peut alors être utilisé pour faire des prédictions de sorties étant donné un ensemble spécifié d'entrées ou pour réaliser des inférences quant aux entrées (causes) étant donné un ensemble spécifié de sorties.

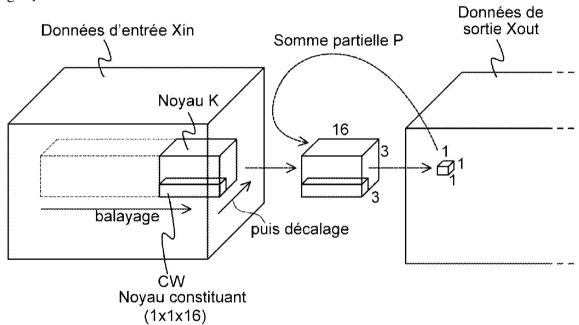

[0004] Un processeur conçu pour des applications d'intelligence artificielle peut inclure dans son jeu d'instructions des instructions dédiées pour réaliser des opérations arithmétiques utilisées communément dans les applications d'intelligence artificielle (le jeu d'instructions étant le jeu fondamental de types d'instructions de code machine que l'unité d'exécution du processeur peut reconnaitre, chaque type étant défini par un code opération respectif et par zéro, ou plus, opérandes). Par exemple, une opération courante nécessaire dans les applications d'intelligence artificielle comme les réseaux neuronaux est la convolution d'un noyau avec un ensemble de données d'entrée, le noyau représentant les poids d'un nœud dans le réseau neuronal. Pour réaliser la convolution d'un noyau d'une taille significative avec les données, la convolution peut être décomposée en multiples produits vectoriels ou matriciels produisant chacun en sortie une somme partielle à accumuler avec la sortie de produits ultérieurs. Il existe déjà des processeurs qui incluent dans leur jeu d'instructions des instructions arithmétiques dédiées à la réalisation d'opérations du type multiplication vectorielle et matricielle destinées à être utilisées dans la réalisation de convolutions.

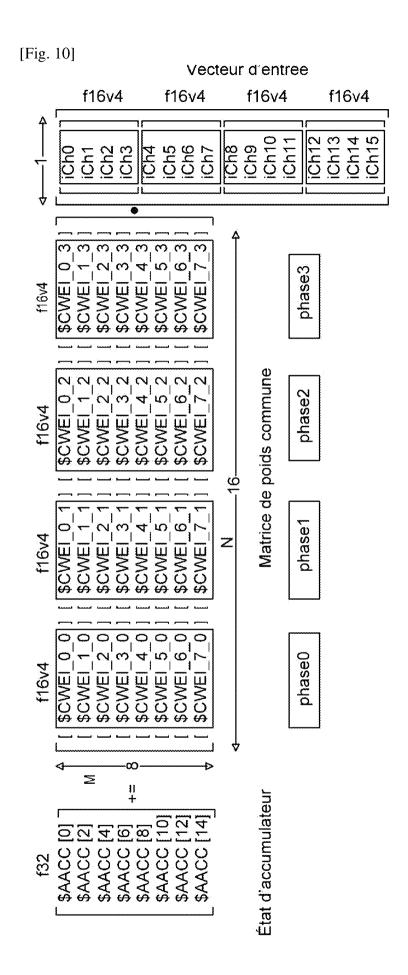

### Résumé de l'invention

[0005] Un processeur peut aussi assurer un soutien pour l'exécution simultanée de multiples fils d'exécution de programme. Ce soutien comprend typiquement un ensemble respectif de registres de contexte pour chaque fil d'exécution, chaque ensemble étant utilisé pour contenir l'état de programme (le "contexte") de l'un respectif d'une pluralité de fils devant être exécutés simultanément. L'état de programme contenu dans les registres de contexte d'un fil donné comprend typiquement un compteur de programme pour ce fil, un ou plusieurs registres d'état de commande enregistrant un état du fil (par exemple en pause, en exécution, etc.), et une pluralité de registres d'opérandes comprenant des registres d'opérandes arithmétiques destinés à contenir temporairement des valeurs sur lesquelles on doit opérer et qui sont fournies par des instructions arithmétiques du fil d'exécution respectif. Les différents fils simultanés sont entrelacés dans le temps par l'intermédiaire d'un pipeline d'exécution commun dans des créneaux temporels d'exécution respectifs différents, chaque créneau utilisant seulement les registres d'un ensemble respectif différent parmi les ensembles de registres de contexte.

[0006] Habituellement, chaque fil comprend son propre ensemble respectif de registres d'opérandes arithmétiques dans un banc de registres arithmétiques séparé pour chaque fil. Lorsqu'une instruction est exécutée en tant que partie d'un fil donné, il est implicite

qu'elle utilise toujours les registres d'opérandes arithmétiques se trouvant dans le banc de registres arithmétiques de ce fil particulier.

[0007] On a identifié ici qu'il peut se trouver des applications dans lesquelles des fils d'exécution peuvent en fait opérer sur certaines valeurs d'opérandes qui sont les mêmes et aussi sur certains autres opérandes qui sont spécifiques au fil individuel. Un exemple pourrait se trouver dans une multiplication vectorielle ou matricielle réalisée en tant que partie d'une convolution, dans laquelle l'instruction dans chaque fil multiplie un ensemble commun de poids (partagé entre des fils) par des données d'entrées qui sont spécifiques au fil individuel. Un exemple particulier de cela peut survenir dans un réseau neuronal à convolution où de nombreux nœuds comprennent en fait les mêmes poids mais avec des connexions différentes. Considérons par exemple un scénario dans lequel chaque fil d'exécution est agencé pour réaliser le traitement d'un nœud respectif différent dans le réseau neuronal, comme la convolution d'un noyau commun de poids avec des données d'entrée respectives pour détecter un certain élément caractéristique. Dans de tels scénarios, il serait avantageux de prévoir un mécanisme permettant à une instruction arithmétique donnée d'opérer sur une combinaison d'un ou plusieurs opérandes de poids communs partagés entre des fils et d'un ou plusieurs opérandes spécifiques aux fils respectifs individuels. Ce

problème n'est en aucun cas spécifique de réseaux neuronaux et pourrait apparaître dans toute application qui se retrouve à utiliser certaines valeurs d'opérandes partagées

et certains opérandes spécifiques à des fils.

[8000] Selon un aspect décrit ici, on prévoit un processeur comprenant : un ou plusieurs bancs de registres ; et une unité d'exécution agencée pour exécuter des instances de types d'instructions définis dans un jeu d'instructions, chaque instruction se trouvant dans le jeu d'instructions étant constituée d'un code opération et d'un ou plusieurs opérandes. L'unité d'exécution est une unité d'exécution à fils en barillet agencée pour exécuter une pluralité de fils simultanés chacun dans un créneau respectif différent d'une séquence répétitive de créneaux temporels entrelacés, et pour chacun des fils simultanés, lesdits un ou plusieurs bancs de registres comprennent un ensemble respectif de registres de contexte agencé pour contenir un état de programme du fil respectif, chaque ensemble de registres de contexte comprenant un ensemble respectif de registres d'opérandes arithmétiques destiné à être utilisés par le fil respectif. L'un desdits un ou plusieurs bancs de registres comprend en outre un ensemble de registres de poids partagés commun à certains ou à la totalité des fils simultanés. Les types d'instructions définis dans le jeu d'instructions comprennent une instruction arithmétique comportant des opérandes spécifiant une source et une destination dans l'ensemble respectif de registres arithmétiques du fil dans lequel l'instruction arithmétique est exécutée. L'unité d'exécution est agencée afin de, en réponse au code

opération de l'instruction arithmétique, réaliser une opération comprenant la multiplication d'une entrée provenant de ladite source par au moins l'un des poids provenant d'au moins l'un des registres de poids partagés, et placer un résultat dans la destination.

- [0009] Dans des modes de réalisation, ledit au moins l'un des registres de poids partagés peut être implicite d'après le code opération de l'instruction arithmétique, n'étant spécifié par aucun d'opérande de l'instruction arithmétique.

- [0010] Dans des modes de réalisation, l'instruction arithmétique peut prendre un autre opérande spécifiant ledit au moins l'un des registres de poids partagés parmi l'ensemble de registres de poids partagés.

- [0011] Dans des modes de réalisation, l'entrée peut comprendre un vecteur, et la multiplication peut comprendre un produit scalaire de l'entrée par un vecteur de poids provenant des registres de poids partagés.

- [0012] Dans des modes de réalisation, ledit au moins l'un des registres de poids partagés peut comprendre un sous-ensemble des registres de poids partagés parmi une pluralité de sous-ensembles, chaque sous-ensemble contenant un vecteur de poids respectif ; et l'autre opérande peut sélectionner à partir duquel sous-ensemble il faut prendre le vecteur de poids à utiliser dans la multiplication.

- [0013] Dans des modes de réalisation, l'instruction arithmétique peut comprendre l'une des instructions suivantes : une instruction de produit scalaire vectoriel, une instruction de produit scalaire vectoriel à accumulation, une instruction de produit matriciel, une instruction de produit matriciel à accumulation, ou une instruction de convolution.

- [0014] Dans des modes de réalisation, les fils simultanés peuvent comprendre une pluralité de fils de travail et l'unité d'exécution peut être en outre agencée pour exécuter, au moins à certains instants, un sous-programme superviseur comprenant au moins un fil superviseur agencé pour gérer les fils de travail.

- [0015] Dans des modes de réalisation, le sous-programme superviseur peut être agencé pour écrire les poids dans le banc de registres de poids partagés.

- [0016] Dans des modes de réalisation, les poids se trouvant dans les registres de poids partagés peuvent être écrits seulement par le sous-programme superviseur, et les fils de travail peuvent être seulement capables de lire les registres de poids partagés.

- [0017] Dans des modes de réalisation, les registres de contexte peuvent comprendre l'un respectif des ensembles de registres de contexte pour chacun des fils de travail qui peuvent être exécutés simultanément, et un ensemble additionnel de registres de contexte peut être agencé pour contenir un état de programme du sous-programme superviseur.

- [0018] Dans des modes de réalisation, le sous-programme superviseur peut être agencé pour commencer en s'exécutant initialement dans tous les créneaux, et pour écrire les poids

avant de lancer les fils de travail ; le sous-programme superviseur pouvant lancer chacun des fils de travail en abandonnant certains ou la totalité des créneaux dans lesquels le sous-programme superviseur s'exécute initialement à certains fils respectifs parmi les fils de travail.

- [0019] Dans des modes de réalisation, le jeu d'instructions peut inclure une instruction d'exécution qui, lorsqu'elle est exécutée en tant que partie du sous-programme superviseur, amène le créneau dans lequel l'instruction d'exécution est exécutée à être abandonné à l'un des fils de travail de sorte que le fil de travail est lancé dans ce créneau à la place du sous-programme superviseur.

- [0020] Dans des modes de réalisation, le jeu d'instructions peut inclure une instruction de sortie qui, lorsqu'elle est exécutée en tant que partie de l'un des fils de travail, amène le créneau dans lequel l'instruction de sortie est exécutée à être restitué au sousprogramme superviseur de sorte que le sous-programme superviseur continue à s'exécuter dans ce créneau de nouveau à la place du fil de travail.

- [0021] Dans des modes de réalisation, les bancs de registres comprennent un banc de registres arithmétiques séparé pour chaque fil de travail simultané, le banc de registres arithmétiques respectif comprenant les registres d'opérandes arithmétiques respectifs.

- [0022] Dans des modes de réalisation, les bancs de registres peuvent comprendre un banc de registres de poids séparé comprenant les registres de poids.

- [0023] Dans des modes de réalisation, le banc de registres de poids peut être agencé de telle sorte qu'il peut être écrit seulement par le sous-programme superviseur et les fils de travail peuvent seulement lire le banc de registres de poids.

- [0024] Selon un autre aspect de la présente invention, on prévoit un procédé d'actionnement d'un processeur agencé selon l'un quelconque des modes de réalisation mentionnés ciavant ou ailleurs ici, le procédé comprenant l'exécution d'un programme comprenant une ou plusieurs instances de l'instruction arithmétique sur le processeur par l'intermédiaire de l'unité d'exécution.

# Brève description des dessins

- [0025] Pour faciliter la compréhension de modes de réalisation de la présente description et pour montrer comment de tels modes de réalisation peuvent être mis en pratique, on va faire référence, seulement à titre d'exemple, aux dessins joints dans lesquels :

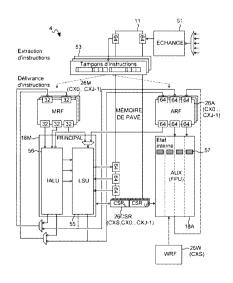

- [0026] [fig.1] la figure 1 est un schéma blocs d'un exemple de processeur à fils d'exécution multiples,

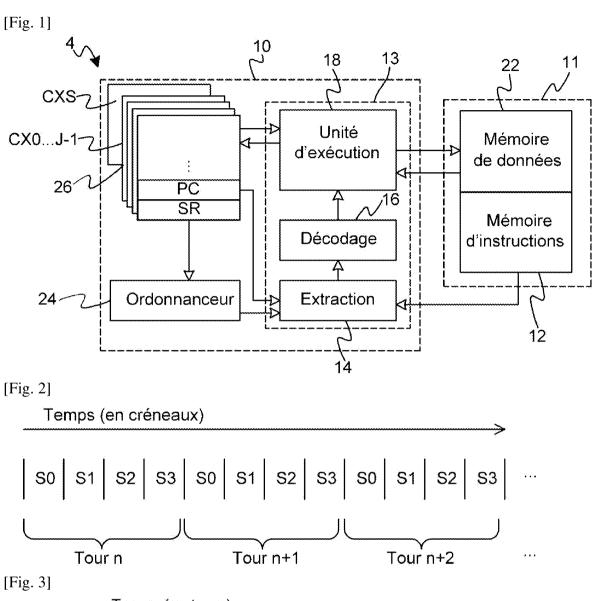

- [0027] [fig.2] la figure 2 représente schématiquement un schéma de créneaux temporels entrelacés,

- [0028] [fig.3] la figure 3 représente schématiquement un fil superviseur et une pluralité de fils de travail s'exécutant dans une pluralité de créneaux temporels entrelacés,

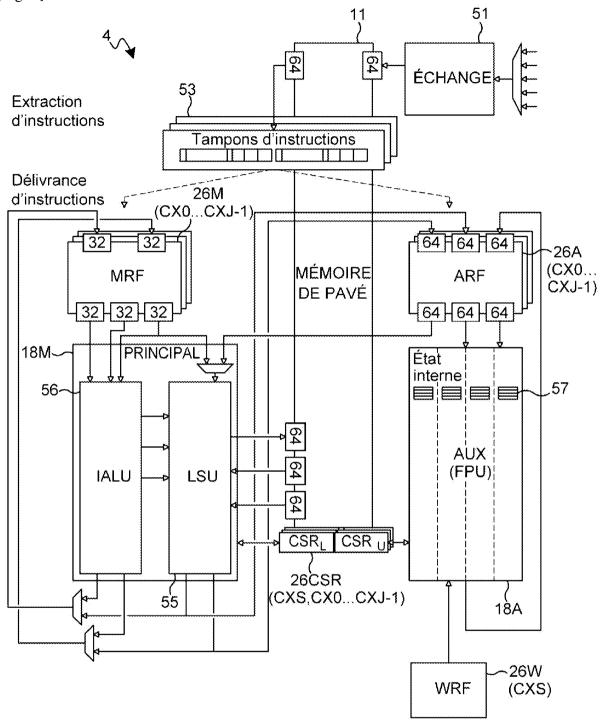

- [0029] [fig.4] la figure 4 représente schématiquement une structure de blocs logiques d'un exemple de processeur,

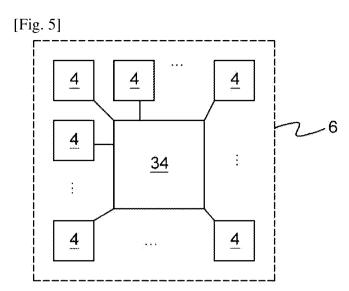

- [0030] [fig.5] la figure 5 est un schéma blocs d'un processeur comprenant une matrice de processeurs constituants,

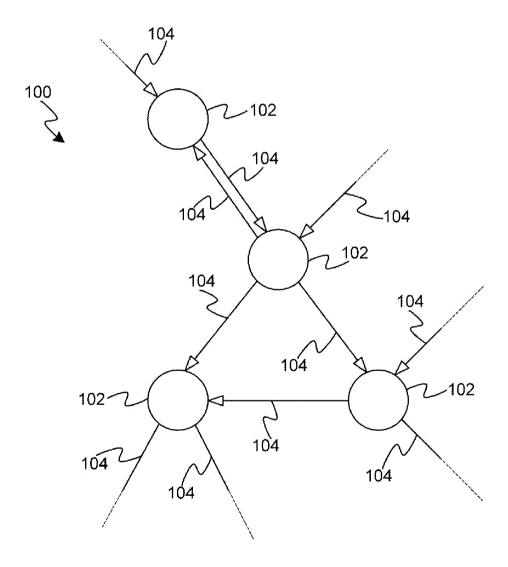

- [0031] [fig.6] la figure 6 représente schématiquement un graphe utilisé dans un algorithme d'intelligence artificielle,

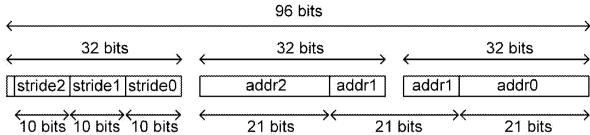

- [0032] [fig.7] la figure 7 représente schématiquement un schéma de disposition d'adresses destiné à être utilisé dans la mise en œuvre d'un type d'instruction de chargement-stockage,

- [0033] [fig.8] la figure 8 représente schématiquement un agencement de valeurs de pas de progression prédéterminées dans un ensemble de registres de pas,

- [0034] [fig.9] la figure 9 représente schématiquement une convolution d'un noyau 3D K avec un volume de données d'entrée,

- [0035] [fig.10] la figure 10 représente schématiquement une multiplication matricielle réalisée par une séquence de phases d'une instruction de produit matriciel à accumulation,

- [0036] [fig.11] la figure 11 représente plus précisément le fonctionnement des instructions de produit matriciel à accumulation,

- [0037] [fig.12] la figure 12 donne un exemple d'une série de boucles d'une séquence d'instructions de produit matriciel à accumulation agencée pour réaliser une convolution,

- [0038] [fig.13] la figure 13 représente schématiquement le fonctionnement d'une instruction de convolution, et

- [0039] [fig.14] la figure 14 donne un exemple d'une série d'instructions de convolution.

#### Description des modes de réalisation

[0040] La figure 1 illustre un exemple de processeur 4 selon des modes de réalisation de la présente description. Le processeur 4 comprend une unité de traitement à fils d'exécution multiples 10 prenant la forme d'une unité de traitement à fils en barillet, et une mémoire locale 11 (c'est-à-dire sur le même pavé dans le cas d'une matrice de pavés multiples, ou sur la même puce dans le cas d'une puce à un seul processeur). Une unité de traitement à fils d'en barillet est un type d'unité de traitement à fils d'exécution multiples dans lequel le temps d'exécution du pipeline est divisé en une séquence répétitive de créneaux temporels entrelacés, chacun d'eux pouvant être occupé par un fil d'exécution donné. On peut aussi appeler cela exécution simultanée, décrit plus en détail immédiatement dans la suite. La mémoire 11 comprend une mémoire d'instructions 12 et une mémoire de données 22 (qui peuvent être mises en œuvre dans des modules mémoire adressables différents ou dans des régions dif-

férentes du même module mémoire adressable). La mémoire d'instructions 12 mémorise du code machine à exécuter par l'unité de traitement 10, tandis que la mémoire de données 22 mémorise à la fois des données sur lesquelles va opérer le code exécuté et des données de sortie produites par le code exécuté (par exemple en résultat de telles opérations).

- [0041] La mémoire 12 mémorise une pluralité de fils d'exécution différents d'un programme, chaque fil d'exécution comprenant une séquence respective d'instructions pour réaliser une certaine tâche ou certaines tâches. On notera qu'une instruction telle que mentionnée ici désigne une instruction de code machine, c'est-à-dire une instance d'une des instructions fondamentales du jeu d'instructions du processeur, constituée d'un seul code opération et de zéro, ou plus, opérandes. Dans des modes de réalisation, le programme comprend une pluralité de fils de travail, et un sous-programme superviseur qui peut être structuré sous forme d'un ou plusieurs fils superviseurs. Cela va être décrit plus en détail immédiatement dans la suite.

- [0042] Un processeur à fils d'exécution multiples est un processeur capable d'exécuter de multiples fils de programme les uns à côté des autres, typiquement de manière simultanée. Une exécution simultanée signifie que les fils partagent un pipeline d'exécution commun (ou au moins une partie commune d'un pipeline) et que des fils différents sont entrelacés dans ce même pipeline à exécution partagée dans différents créneaux temporels entrelacés dans un cycle répétitif. Cela augmente les performances en raison de plus nombreuses opportunités pour cacher la latence du pipeline. Le processeur comprend du matériel qui est commun aux multiples fils d'exécution différents (par exemple une mémoire d'instructions, une mémoire de données et/ou une unité d'exécution en commun) ; mais pour prendre en charge le fonctionnement à fils multiples, le processeur comprend aussi du matériel dédié spécifique à chaque fil.

- [0043] Le matériel dédié comprend un ensemble séparé de registres de contexte 26 pour au moins chacun des fils qui peuvent être exécutés simultanément, c'est-à-dire un ensemble par créneau dans le cycle. Le mot "contexte", lorsqu'on parle de processeur à fils d'exécution multiples, fait référence à l'état de programme de l'un respectif des fils en cours d'exécution côte à côte (par exemple valeur de compteur de programme, valeurs de statut et d'opérandes courants). Les registres de contexte font référence aux registres respectifs destinés à représenter cet état de programme du fil respectif. Les registres se trouvant dans un banc de registres sont distincts de la mémoire générale en ce que les adresses des registres sont fixées sous forme de bits dans des mots d'instructions, alors que les adresses mémoire peuvent être calculées en exécutant des instructions.

- [0044] Dans l'unité de traitement 10, de multiples fils différents parmi les fils provenant de la mémoire d'instructions 12 peuvent être entrelacés dans un seul pipeline d'exécution

13 (bien que typiquement seul un sous-ensemble de la totalité des fils mémorisés dans la mémoire d'instructions peut être entrelacé à un point donné dans le programme global). L'unité de traitement à fils multiples 10 comprend une pluralité d'ensembles de registres de contexte 26, chaque ensemble 26 étant agencé pour représenter l'état (contexte) d'un fil respectif différent parmi les fils qui peuvent être exécutés simultanément. L'unité de traitement à fils d'exécution multiples 10 comprend aussi un pipeline d'exécution partagé 13, qui est commun aux fils exécutés simultanément, et un ordonnanceur 24 pour planifier les fils d'exécution simultanés pour une exécution à travers le pipeline partagé de manière entrelacée, par exemple à tour de rôle. L'unité de traitement 10 est connectée à une mémoire d'instructions partagée 12 commune à la pluralité de fils, et à une mémoire de données partagée 22 qui est ici encore commune à la pluralité de fils.

- [0045] Le pipeline d'exécution 13 comprend un étage d'extraction 14, un étage de décodage 16 et un étage d'exécution 18 comprenant une unité d'exécution qui peut réaliser des opérations arithmétiques et logiques, des calculs d'adresses, des opérations de chargement et de stockage, et d'autres opérations, comme définies par l'architecture du jeu d'instructions.

- [0046] Chaque ensemble de registres de contexte 26 comprend un ou plusieurs registres de commande respectifs comprenant au moins un compteur de programme (PC) pour le fil respectif (pour garder la trace de l'adresse d'instruction à laquelle le fils s'exécute actuellement), et dans des modes de réalisation aussi un ensemble d'un ou plusieurs registres d'état de commande (CSR) enregistrant un statut courant du fil respectif (comme par exemple s'il est actuellement en exécution ou en pause). Chaque ensemble de bancs de registres de contexte 26 comprend aussi un ensemble respectif de registres d'opérandes, pour contenir temporairement des opérandes des instructions exécutées par le fil respectif, c'est-à-dire des valeurs sur lesquelles on opère ou qui résultent d'opérations définies par les codes d'opération des instructions du fil respectif lorsqu'elles sont exécutées. Chaque ensemble de registres 26 peut être mis en œuvre dans un ou plusieurs bancs de registres.

- [0047] L'étage d'extraction 14 a accès au compteur de programme (PC) de chacun des contextes. Pour chaque fil respectif, l'étage d'extraction 14 extrait l'instruction suivante de ce fil de l'adresse suivante dans la mémoire de programme 12 comme indiqué par le compteur de programme. Le compteur de programme s'incrémente automatiquement à chaque cycle d'exécution à moins qu'il ne soit dérouté par une instruction de branchement. L'étage d'extraction 14 passe ensuite l'instruction extraite à l'étage de décodage 16 pour qu'elle soit décodée, et l'étage de décodage 16 passe ensuite une indication de l'instruction décodée à l'unité d'exécution 18 accompagnée des adresses décodées des éventuels registres d'opérandes qui sont spécifiés dans

l'instruction, afin que l'instruction soit exécutée. L'unité d'exécution 18 a accès aux registres d'opérandes et aux registres d'état de commande, qu'elle peut utiliser dans l'exécution de l'instruction sur la base des adresses de registres décodées, comme dans le cas d'une instruction arithmétique (par exemple en additionnant, en multipliant, en soustrayant ou en divisant les valeurs se trouvant dans deux registres d'opérandes et en fournissant le résultat à un autre registre d'opérande du fil respectif). Ou bien si l'instruction définit un accès à la mémoire (chargement ou stockage), la logique de chargement/stockage de l'unité d'exécution 18 charge une valeur à partir de la mémoire de données dans un registre d'opérande du fil respectif, ou mémorise une valeur provenant d'un registre d'opérande du fil respectif dans la mémoire de données 22, conformément à l'instruction.

L'étage d'extraction 14 est connecté de manière à extraire des instructions à exécuter à partir de la mémoire d'instructions 12, sous le contrôle de l'ordonnanceur 24.

L'ordonnanceur 24 est agencé pour contrôler l'étage d'extraction 14 pour extraire une instruction à partir de chacun d'un ensemble de fils s'exécutant simultanément tour à tour dans une séquence répétitive de créneaux temporels, divisant ainsi les ressources du pipeline 13 en une pluralité de créneaux temporels entrelacés dans le temps, comme on va le décrire plus en détail immédiatement dans la suite. Par exemple, le schéma d'ordonnancement pourrait être un tour de rôle ou un tour de rôle pondéré. Un autre terme pour désigner un processeur opérant de cette manière est processeur à fils d'exécution en barillet.

[0049] Un exemple du schéma d'entrelacement mis en œuvre par l'ordonnanceur 24 est illustré en figure 2. Ici, les fils simultanés sont entrelacés selon un schéma de tour de rôle dans lequel, dans chaque tour du schéma, le tour est divisé en une séquence de créneaux temporels S0, S1, S2...SJ-1 (par exemple J=4, ou J=6), chaque créneau étant destiné à exécuter un fil respectif. Typiquement chaque créneau a une longueur égale à un cycle d'exécution et les différents créneaux sont de taille égale, bien que cela ne soit pas nécessairement ainsi dans tous les modes de réalisation possibles, par exemple un schéma de tour de rôle pondéré est aussi possible, schéma dans lequel certains fils obtiennent plus de cycles que d'autres par tour d'exécution. En général l'exécution de fils en barillet peut utiliser un ordonnancement soit à tour de rôle régulier soit à tour de rôle pondéré, dans ce dernier cas la pondération pouvant être fixe ou adaptative.

[0050] Quelle que soit la séquence pour chaque tour d'exécution, ce motif se répète ensuite, chaque tour comprenant une instance respective de chacun des créneaux temporels. On notera par conséquent qu'un créneau temporel auquel on fait référence ici désigne l'emplacement alloué de manière répétitive dans la séquence, et non une instance particulière du créneau temporel dans une répétition donnée de la séquence. Dit d'une autre manière, l'ordonnanceur 24 répartit les cycles d'exécution du pipeline 13 dans

une pluralité de canaux d'exécution entrelacés dans le temps (multiplexés par séparation temporelle), chacun comprenant une récurrence d'un créneau temporel respectif dans une séquence répétitive de créneaux temporels. Dans le mode de réalisation illustré, il y a quatre créneaux temporels, mais cela n'est que dans un but illustratif et d'autres nombres sont possibles. Par exemple dans un mode de réalisation préféré, il y a en fait six créneaux temporels.

- [0051] Dans des modes de réalisation, les registres de contexte 26 comprennent un ensemble respectif de registres de contexte de travail CX0... CX(J-1) pour chacun des J fils qui peuvent être exécutés simultanément (J=3 dans l'exemple illustré mais cela n'est pas limitatif), et un banc de registres de contexte de superviseur additionnel, CXS. Les bancs de registres de contexte de travail contiennent les contextes de fils de travail, et le banc de registres de contexte de superviseur contient le contexte d'un fil superviseur. On notera que dans des modes de réalisation le contexte de superviseur comporte un nombre de registres différent de celui de chacun des fils de travail. L'unité de traitement 10 comprend ainsi un banc de registres de contexte 26 de plus qu'il y a de créneaux temporels, c'est-à-dire qu'elle supporte un contexte de plus que le nombre de créneaux temporels entrelacés qu'elle peut gérer pour des fils en barillet.

- [0052] Chacun des contextes de travail CX0...CXJ est utilisé pour représenter l'état de l'un respectif d'une pluralité de fils de travail affectés actuellement à l'un des quatre créneaux temporels d'exécution S0...SJ, pour réaliser n'importe quelles tâches de calcul spécifiques d'application que souhaite le programmeur (on notera de nouveau que cela peut seulement être un sous-ensemble du nombre total de fils de travail du programme mémorisé dans la mémoire d'instructions 12). Le contexte additionnel CXS est utilisé pour représenter l'état d'un "fil superviseur" (SV) dont le rôle est de coordonner l'exécution des fils de travail, au moins dans le sens de l'affectation de celui des fils de travail W qui doit être exécuté dans tel ou tel créneau des créneaux temporels S0, S1, S2... et à quel point dans le programme global. Optionnellement, le fil superviseur peut avoir d'autres responsabilités de "superviseur" ou de coordination, comme la réalisation d'échanges externes ou de synchronisations à barrières. On notera bien sûr que le cas illustré de J=4 n'est qu'un exemple de mise en œuvre dans un but illustratif. Par exemple, dans une autre mise en œuvre J=6 (six créneaux temporels, six contextes de travail et un contexte de superviseur).

- [0053] En référence à la figure 3, dans des modes de réalisation le fil superviseur SV ne possède pas son propre créneau par lui-même dans le schéma de créneaux temporels d'exécution entrelacés. Il en est de même pour les fils de travail puisque l'allocation de créneaux à des fils de travail est définie de manière flexible. Au lieu de cela, chaque créneau temporel possède son propre ensemble de registres de contexte pour mémoriser un contexte de travail, qui est utilisé par le fil de travail lorsque le créneau

est alloué au fil de travail, mais pas utilisé lorsque le créneau est alloué au superviseur. Quand un créneau donné est alloué au superviseur, ce créneau utilise à la place le banc de registres de contexte CXS du superviseur. Le superviseur a toujours accès à son propre contexte et aucun des fils de travail ne peut occuper le banc de registres de contexte de superviseur CXS.

- [0054] Le fil superviseur SV a la capacité de s'exécuter dans n'importe lequel et dans tous les créneaux temporels S0....S3 (ou plus généralement S0...SJ-1). L'ordonnanceur 24 est agencé de manière à, lorsque le programme dans son ensemble démarre, commencer par allouer le fil superviseur à la totalité des créneaux temporels, c'est-à-dire qu'ainsi le superviseur SV démarre en s'exécutant dans tous les créneaux S0...SJ-1. Toutefois, le fil superviseur est muni d'un mécanisme pour, à un certain point ultérieur (soit immédiatement soit après avoir réalisé une ou plusieurs tâches de superviseur), abandonner temporairement chacun des créneaux dans lequel il s'exécute à l'un respectif des fils de travail, par exemple initialement les fils de travail W0...W3 dans l'exemple représenté en figure 3 (ou plus généralement W0...WJ-1). Cela est obtenu en faisant exécuter une instruction d'exécution par le fil superviseur, qui prend au moins l'adresse d'un fil de travail dans la mémoire d'instructions 12 comme opérande. Les fils de travail sont des portions de code qui peuvent s'exécuter simultanément entre elles, chacune représentant une ou plusieurs tâches de calcul respectives à réaliser.

- [0055] L'instruction d'exécution agit sur l'ordonnanceur 24 de manière à abandonner le créneau temporel courant, dans lequel cette instruction est elle-même exécutée, au fil de travail spécifié par l'opérande. On notera qu'il est implicite dans l'instruction d'exécution que c'est le créneau temporel dans lequel cette instruction est exécutée qui est abandonné (implicite dans le contexte d'instructions de code machine signifie qu'il n'y a pas besoin d'opérande pour spécifier cela c'est sous-entendu de manière implicite d'après le code opération lui-même). Ainsi le créneau temporel qui est abandonné est le créneau temporel dans lequel le superviseur exécute l'instruction d'exécution.

- [0056] Le fil superviseur SV réalise une opération similaire dans chacun d'un ou plusieurs autres des créneaux temporels, pour abandonner certains ou la totalité de ses créneaux temporels à des fils respectifs différents parmi les fils de travail W0...WJ-1 (sélectionnés dans un ensemble plus grand de fils de travail possibles dans la mémoire d'instructions 12). Une fois qu'il a réalisé cela pour le dernier créneau, le superviseur est suspendu (puis plus tard il va reprendre là où il avait quitté lorsque l'un des créneaux est rendu par un fil de travail W). Le fil superviseur SV est ainsi capable d'allouer des fils de travail différents, chacun réalisant une ou plusieurs tâches, à différents créneaux des créneaux temporels d'exécution entrelacés S0...SJ-1 (par

exemple J=4 comme cela est illustré, ou J=6). Lorsque le fil superviseur détermine qu'il est temps d'exécuter un fil de travail, il utilise l'instruction d'exécution pour allouer ce fil de travail au créneau temporel dans lequel l'instruction d'exécution a été exécutée.

- [0057] Dans certains modes de réalisation, le jeu d'instructions comprend aussi une variante de l'instruction d'exécution, "exécuter tous", ou exécution générale. Cette instruction est utilisée pour lancer un ensemble de plusieurs fils de travail ensemble, tous exécutant le même code. Dans des modes de réalisation cela lance un fil de travail dans chacun des créneaux de l'unité de traitement S0...S3 (ou plus généralement S0....S(J-1)).

- Une fois lancé, chacun des fils de travail alloués actuellement W0...WJ-1 se déroule pour réaliser lesdites une ou plusieurs tâches de calcul définies dans le code spécifié par l'instruction d'exécution respective. À la fin de cela, le fil de travail respectif rend le créneau temporel dans lequel il s'exécute au fil superviseur. Cela est obtenu en exécutant une instruction de sortie dans le fil de travail respectif. L'instruction de sortie agit sur l'ordonnanceur 24 de façon à repasser le créneau temporel courant, dans lequel cette instruction est elle-même exécutée, au fil superviseur. En réponse l'ordonnanceur 24 continue ensuite à exécuter le superviseur dans ce créneau.

- [0059] La figure 4 illustre en outre d'autres exemples du détail du processeur 4, comprenant le détail de l'unité d'exécution 18 et des registres de contexte 26. Le processeur comprend un tampon d'instructions 53 respectif pour chacun des M fils pouvant être exécutés simultanément. Les registres de contexte 26 comprennent un banc de registres principal (MRF) respectif 26M pour chacun des M contextes de travail et pour le contexte de superviseur. Les registres de contexte comprennent en outre un banc de registres auxiliaire (ARF) 26A respectif pour au moins chacun des contextes de travail. Les registres de contexte 26 comprennent en outre un banc de registres de poids commun (WRF) 26W, auquel tous les fils de travail s'exécutant actuellement peuvent accéder en lecture. Le WRF peut être associé au contexte de superviseur en ce que le fil superviseur est le seul fil qui peut écrire dans le WRF. Les registres de contexte 26 peuvent aussi comprendre un groupe respectif de registres d'état de commande 26CSR pour chacun des contextes de superviseur et de travail. L'unité d'exécution 18 comprend une unité d'exécution principale 18M et une unité d'exécution auxiliaire 18A. L'unité d'exécution principale 18M comprend une unité de chargement-stockage (LSU) 55 et une unité logique et arithmétique en entiers (IALU) 56. L'unité d'exécution auxiliaire 18A comprend au moins une unité arithmétique en virgule flottante (FPU).

- [0060] Dans chacun des J créneaux temporels entrelacés S0...SJ-1, l'ordonnanceur 24 contrôle l'étage d'extraction 14 pour extraire au moins une instruction d'un fil respectif

à partir de la mémoire d'instructions 11, pour la mettre dans l'un respectif des J tampons d'instructions 53 correspondant au créneau temporel courant. Dans des modes de réalisation, chaque créneau temporel est un cycle d'exécution du processeur, bien que d'autres schémas ne soient pas exclus (par exemple un tour de rôle pondéré). Dans chaque cycle d'exécution du processeur 4 (c'est-à-dire chaque cycle de l'horloge du processeur qui fournit l'horloge au compteur programme) l'étage d'extraction 14 extrait soit une seule instruction soit un petit "groupe d'instructions" (par exemple, un groupe de deux instructions ou un groupe de quatre instructions), en fonction de la mise en œuvre. Chaque instruction est ensuite délivrée, via l'étage de décodage 16, à l'un du LSU 55 ou de l'IALU 56 de l'unité d'exécution principale 18M ou au FPU de l'unité d'exécution auxiliaire 18A, en fonction du fait que l'instruction (selon son code opération) est une instruction d'accès à la mémoire, une instruction arithmétique en entiers ou une instruction arithmétique en virgule flottante, respectivement. Le LSU 55 et l'IALU 56 de l'unité d'exécution principale 18M exécutent leurs instructions en utilisant des registres du MRF 26M, les registres particuliers à l'intérieur du MRF 26M étant spécifiés par des opérandes des instructions. Le FPU de l'unité d'exécution auxiliaire 18A réalise des opérations utilisant des registres se trouvant dans les bancs ARF 26A et WRF 26W, où les registres particuliers dans le banc ARF sont spécifiés par des opérandes des instructions. Dans des modes de réalisation, les registres se trouvant dans le WRF peuvent être implicites dans le type d'instruction (c'est-à-dire prédéterminés pour ce type d'instruction). L'unité d'exécution auxiliaire 18A peut aussi contenir des circuits prenant la forme de bascules logiques internes à l'unité d'exécution auxiliaire 18A pour contenir certains états internes 57 destinés à être utilisés pour réaliser les opérations d'un ou plusieurs des types d'instructions arithmétiques en virgule flottante.

Dans des modes de réalisation qui extraient et exécutent des instructions en groupes, les instructions individuelles se trouvant dans un groupe d'instructions donné sont exécutées simultanément, en parallèle en suivant des pipelines indépendants 18M, 18A (représentés en figure 4). Dans des modes de réalisation qui exécutent des groupes de deux instructions, les deux instructions peuvent être exécutées simultanément en suivant les pipelines auxiliaire et principal. Dans ce cas, le pipeline principal est agencé pour exécuter des types d'instructions qui utilisent le banc MRF et le pipeline auxiliaire est utilisé pour exécuter des types d'instructions qui utilisent le banc ARF. Le fait d'appairer des instructions en groupes complémentaires appropriés peut être géré par le compilateur.

[0062] Chaque contexte de fil de travail possède sa propre instance du banc de registres principal (MRF) 26M et du banc de registres auxiliaire (ARF) 26A (c'est-à-dire un MRF et un ARF pour chacun des créneaux de fils en barillet). La fonctionnalité décrite

ici en relation avec le MRF ou l'ARF doit être comprise comme fonctionnant sur la base d'un contexte. Toutefois il y a un seul banc de registres de poids partagé (WRF), partagé entre les fils. Chaque fil peut accéder aux bancs MRF et ARF de seulement son propre contexte 26. Toutefois, tous les fils de travail s'exécutant actuellement peuvent accéder au WRF commun. Le WRF fournit ainsi un ensemble commun de poids destiné à être utilisé par tous les fils de travail. Dans des modes de réalisation, seul le superviseur peut écrire dans le WRF, et les fils de travail peuvent seulement lire dans le WRF.

[0063] Le jeu d'instructions du processeur 4 comprend au moins un type d'instruction de chargement dont le code opération, lorsqu'il est exécuté, amène le LSU 55 à charger des données à partir de la mémoire de données 22 dans le banc ARF, 26A, respectif du fil dans lequel les instructions de chargement ont été exécutées. L'emplacement de la destination dans le banc ARF est spécifié par un opérande de l'instruction de chargement. Un autre opérande de l'instruction de chargement spécifie un registre d'adresse dans le MRF, 26M, respectif qui contient un pointeur vers une adresse dans la mémoire de données 22 à partir de laquelle il faut charger les données. Le jeu d'instructions du processeur 4 comprend aussi au moins un type d'instruction de stockage dont le code opération, lorsqu'il est exécuté, amène le LSU 55 à stocker des données dans la mémoire de données 22 à partir du banc ARF respectif du fil dans lequel l'instruction de stockage a été exécutée. L'emplacement de la source du stockage dans le banc ARF est spécifié par un opérande de l'instruction de chargement. Un autre opérande de l'instruction de chargement spécifie un registre d'adresse dans le MRF, qui contient un pointeur vers une adresse dans la mémoire de données 22, à laquelle il faut stocker la donnée. En général, le jeu d'instructions peut comprendre des types d'instructions de chargement et de stockage séparés, et/ou au moins un type d'instruction de chargement-stockage qui combine les opérations de chargement et de stockage dans une seule instruction. Comme on va le décrire plus en détail dans la suite, le jeu d'instructions peut inclure un type particulier d'instruction de chargementstockage qui réalise deux chargements et une opération de stockage, le tout en une seule instruction. On notera que le jeu d'instructions d'un processeur 4 donné peut inclure de multiples variétés différentes de types d'instructions de chargement, de stockage et/ou de chargement-stockage.

[0064] Le jeu d'instructions du processeur comprend aussi un ou plusieurs types d'instructions arithmétiques pour réaliser des opérations arithmétiques. Selon des modes de réalisation décrits ici, cela peut inclure au moins un type d'instruction arithmétique qui fait usage du banc de registres de poids commun, WRF, 26W. Ce type d'instruction prend au moins un opérande qui spécifie au moins une source de l'opération arithmétique correspondante dans le banc ARF, 26A, respectif du fil dans

lequel l'instruction arithmétique a été exécutée. Toutefois, au moins une autre source de l'instruction arithmétique est le WRF commun, commun à tous les fils de travail. Dans des modes de réalisation, cette source est implicite dans l'instruction arithmétique en question (c'est-à-dire implicite pour ce type d'instruction arithmétique). Implicite dans le sens d'une instruction de code machine signifie qu'il n'y a pas besoin de spécifier un opérande. C'est-à-dire que dans ce cas, l'emplacement de la source dans le WRF est inhérent d'après le code opération (prédéterminé pour ce code opération particulier). En variante dans d'autres modes de réalisation, l'instruction arithmétique peut prendre un opérande spécifiant dans quel ensemble de registres de poids on doit prendre les poids, parmi quelques ensembles différents se trouvant dans le WRF. Toutefois, le fait que la source des poids se trouve dans le banc WRF (par opposition disons au banc MRF ou au banc ARF d'usage général) est encore implicite.

[0065] En réponse au code opération du type concerné d'instruction arithmétique, l'unité arithmétique (par exemple le FPU) dans l'unité d'exécution auxiliaire 18A réalise une opération arithmétique, comme spécifié par le code opération, qui comprend d'opérer sur les valeurs se trouvant dans le ou les registres de source spécifiés dans le banc ARF respectif du fil, et dans le ou les registres de source dans le WRF. Elle fournit aussi en sortie un résultat de l'opération arithmétique à un registre de destination dans le banc ARF respectif du fil comme spécifié explicitement par un opérande de destination de l'instruction arithmétique.

[0066] Des exemples de types d'instructions arithmétiques qui peuvent utiliser une source dans le WRF commun, 26W, peuvent inclure : un ou plusieurs types d'instructions de multiplication vectorielle, un ou plusieurs types d'instructions de multiplication matricielle, un ou plusieurs types d'instructions de multiplication vectorielle à accumulation et/ou types d'instructions de multiplication matricielle à accumulation (qui accumulent un résultat de la multiplication entre une instance donnée de l'instruction et la suivante), et/ou un ou plusieurs types d'instructions de convolution. Par exemple, un type d'instruction de multiplication vectorielle peut multiplier un vecteur d'entrée explicite provenant du banc ARF, 26A, par un vecteur prédéterminé de poids provenant du WRF; ou un type d'instruction de multiplication matricielle peut multiplier un vecteur d'entrée explicite provenant du banc ARF par une matrice prédéterminée de poids provenant du WRF. Dans un autre exemple, un type d'instruction de convolution peut faire une convolution d'une matrice d'entrée provenant du banc ARF avec une matrice prédéterminée provenant du WRF. Le fait d'avoir un banc de registres de poids partagés, WRF, commun à une pluralité de fils, permet à chaque fil de multiplier ou faire une convolution entre un noyau commun et ses propres données respectives. Cela est utile puisque c'est d'un scénario qui survient souvent dans

beaucoup d'applications d'apprentissage automatique, par exemple là où chaque fil représente un nœud différent dans un réseau neuronal et où le noyau commun représente une caractéristique qui est recherchée ou pour laquelle on réalise un apprentissage (par exemple une arête ou une forme particulière dans une région ou un volume de données graphiques).

[0067] Dans des modes de réalisation, les valeurs se trouvant dans le WRF, 26W, peuvent être écrites par le fil superviseur. Le superviseur (qui dans un mode de réalisation commence par s'exécuter dans tous les créneaux S0...SM) exécute en premier une série d'instructions de mise en place pour écrire les valeurs de certains poids commun dans l'emplacement prédéterminé dans le WRF. Il exécute ensuite des instructions d'exécution (ou une instruction d'exécution générale) pour lancer un fil de travail respectif dans certains ou la totalité des créneaux S0...SJ-1. Chaque fil de travail comprend ensuite une ou plusieurs instances d'une ou plusieurs instructions arithmétiques du ou des types décrits précédemment, de manière à réaliser la ou les opérations arithmétiques correspondantes sur ses propres données d'entrée respectives, chargées dans son banc ARF, 26A, respectif, mais en utilisant les poids communs écrits par le superviseur dans le WRF, 26W. Lorsque chaque fil termine sa tâche respective, il exécute une instruction de sortie pour rendre son créneau au superviseur. Lorsque tous les fils lancés ont terminé leurs tâches respectives, le superviseur peut écrire de nouvelles valeurs dans le WRF et lancer un nouvel ensemble de fils (ou lancer un nouvel ensemble pour continuer à utiliser les valeurs existantes dans le WRF).

On notera que les appellations "principal", "auxiliaire" et "poids" ne sont pas néces-[8900] sairement limitatives. Dans des modes de réalisation il peut y avoir un premier banc de registres (par contexte de travail), un deuxième banc de registres (par contexte de travail) et un troisième banc de registres partagé (par exemple faisant partie du contexte de superviseur mais accessible à tous les fils de travail). Le banc ARF 26A et l'unité d'exécution auxiliaire 18 peuvent aussi être appelés banc de registres arithmétiques et unité d'exécution arithmétique puisqu'ils sont utilisés pour des instructions arithmétiques (ou au moins l'arithmétique en virgule flottante). Le MRF 26M et l'unité d'exécution auxiliaire 18 peuvent aussi être appelés banc de registres d'adresses mémoire et unité d'exécution arithmétique puisque l'une de leurs utilisations consiste à accéder à la mémoire. Le banc de registres de poids (WRF) 26W est appelé ainsi car il est utilisé pour contenir des poids multiplicateurs utilisés dans un certain type ou dans certains types d'instructions arithmétiques, qui seront décrits bientôt dans la suite. Par exemple cela pourrait être utilisé pour représenter les poids de nœuds dans un réseau neuronal. Dit d'une autre manière, le banc MRF pourrait être appelé banc de registres d'entiers puisqu'il est utilisé pour contenir des opérandes entiers, tandis que le banc

ARF pourrait être appelé banc de registres de virgule flottante puisqu'il est utilisé pour contenir des opérandes en virgule flottante. Dans des modes de réalisation qui exécutent des instructions en groupes de deux, le MRF est le banc de registre utilisé par le pipeline principal et le banc ARF est le registre utilisé par le pipeline auxiliaire.

[0069] Cependant, dans des variantes de réalisation, on notera que l'espace de registres 26 n'est pas nécessairement divisé en ces bancs de registres séparés pour ces différents buts. Au lieu de cela, des instructions exécutées dans les unités d'exécution principale et auxiliaire peuvent être capables de spécifier des registres dans le même banc de registres partagé (un banc de registres par contexte dans le cas d'un processeur à fils d'exécution multiples). Aussi, le pipeline 13 ne comporte pas nécessairement des pipelines constituants parallèles (par exemple des pipelines auxiliaire et principal) pour exécuter simultanément des groupes d'instructions.

[0070] Le processeur 4 peut aussi comprendre une interface d'échange 51 pour échanger des données entre la mémoire 11 et une ou plusieurs autres ressources, par exemple d'autres instances de processeurs et/ou des dispositifs externes comme une interface réseau ou un dispositif de stockage attaché à un réseau (NAS). Comme cela est illustré en figure 5, dans des modes de réalisation le processeur 4 peut constituer l'un des pavés d'une matrice 6 de pavés processeurs interconnectés, chaque pavé exécutant une partie d'un programme plus large. Les processeurs individuels 4 (pavés) constituent ainsi une partie d'un processeur ou d'un système de traitement plus large 6. Les pavés 4 peuvent être interconnectés entre eux via un sous-système d'interconnexion 34, auquel ils sont connectés via leur interface d'échange 51 respective. Les pavés 4 peuvent être mis en œuvre sur la même puce (c'est-à-dire la même puce élémentaire) ou sur des puces différentes, ou dans une combinaison (c'est-à-dire que la matrice peut être constituée de multiples puces comprenant chacune de multiples pavés 4). Le système d'interconnexion 34 et l'interface d'échange 51 peuvent par conséquent comprendre un mécanisme d'interconnexion interne (sur la puce) et/ou un mécanisme d'échange externe (entre puces), en conséquence.

Dans un exemple d'application d'un processeur ou système à fils d'exécution multiples et/ou à pavés multiples, le programme exécuté à travers les multiples fils et/ou pavés 4 comprend un algorithme d'intelligence artificielle, comme un algorithme agencé pour réaliser l'apprentissage d'un réseau neuronal et/ou pour réaliser des inférences sur la base d'un réseau neuronal. Dans de tels modes de réalisation chaque fil de travail, ou la partie du programme exécutée sur chaque pavé, ou chaque fil de travail sur chaque pavé, est utilisé pour représenter un nœud 102 différent dans un réseau neuronal (un type de graphe) ; et des communications entre fils et/ou pavés, en conséquence, représentent des arêtes 104 entre des nœuds 102 dans le graphe. Cela est illustré en figure 6.

[0072] L'intelligence artificielle commence par une étape d'apprentissage dans laquelle l'algorithme d'intelligence artificielle apprend un modèle de connaissance. Le modèle comprend un graphe de nœuds interconnectés (c'est-à-dire des sommets) 102 et d'arêtes (c'est-à-dire des liaisons) 104. Chaque nœud 102 du graphe comporte une ou plusieurs arêtes d'entrée et une ou plusieurs arêtes de sortie. Certaines des arêtes d'entrée de certains des nœuds 102 sont les arêtes de sortie de certains autres nœuds, connectant ainsi entre eux les nœuds pour former le graphe. En outre, une ou plusieurs des arêtes d'entrée d'un ou plusieurs des nœuds 102 constituent les entrées du graphe dans son ensemble, et une ou plusieurs des arêtes de sortie d'un ou plusieurs des nœuds 102 constituent les sorties du graphe dans son ensemble. Parfois, un nœud donné peut même comporter tous ces éléments : des entrées du graphe, des sorties du graphe et des connexions à d'autres nœuds. Chaque arrête 104 communique une valeur ou plus souvent un tenseur (une matrice à n dimensions), cela constituant les entrées et les sorties fournies aux nœuds et reçues des nœuds 102 sur leur arrêtes d'entrée et de sortie respectivement.

[0073] Chaque nœud 102 représente une fonction de son ou de ses entrées reçues sur son arrête ou ses arrêtes d'entrée, le résultat de cette fonction étant la ou les sorties fournies sur l'arrête ou les arrêtes de sortie. Chaque fonction est paramétrée par un ou plusieurs paramètres respectifs (parfois appelés poids, bien qu'ils n'aient pas besoin nécessairement d'être des poids multiplicateurs). En général, les fonctions représentées par les différents nœuds 102 peuvent prendre différentes formes de fonctions et/ou peuvent être paramétrées par différents paramètres.

[0074] En outre, chacun desdits un ou plusieurs paramètres de chaque fonction d'un nœud est caractérisé par une valeur d'erreur respective. En outre, une condition respective peut être associée à l'erreur ou aux erreurs dans le ou les paramètres de chaque nœud 102. Pour un nœud 102 représentant une fonction paramétrée par un seul paramètre, la condition peut être un simple seuil, c'est-à-dire que la condition est satisfaite si l'erreur se trouve dans les limites du seuil spécifié mais n'est pas satisfaite si l'erreur est audelà du seuil. Pour un nœud 102 paramétré par plus qu'un seul paramètre respectif, la condition pour que ce nœud 102 ait atteint un niveau d'erreur acceptable peut être plus complexe. Par exemple, la condition peut être satisfaite seulement si chacun des paramètres de ce nœud 102 se trouve dans les limites du seuil respectif. Dans un autre exemple, une métrique combinée peut être définie comme combinant les erreurs dans les différents paramètres pour le même nœud 102, et la condition peut être satisfaite à condition que la valeur de la métrique combinée se trouve dans les limites d'un seuil spécifié, mais autrement la condition n'est pas satisfaite si la valeur de la métrique combinée est au-delà du seuil (ou vice versa en fonction de la définition de la métrique). Quelle que soit la condition, cela donne une mesure indiquant si l'erreur

dans le ou les paramètres du nœud descend en dessous d'un certain niveau ou degré d'acceptabilité. En général on peut utiliser toute métrique appropriée. La condition ou la métrique peut être la même pour tous les nœuds, ou peut être différente pour certains nœuds respectifs différents parmi les nœuds.

[0075] Dans l'étape d'apprentissage l'algorithme reçoit des données expérimentales, c'est-à-dire de multiples points de données représentant différentes combinaisons possibles d'entrées dans le graphe. Au fur et à mesure que des données expérimentales sont reçues, l'algorithme ajuste progressivement les paramètres des divers nœuds 102 du graphe sur la base des données expérimentales de manière à essayer de minimiser les erreurs dans les paramètres. Le but est de trouver des valeurs des paramètres telles que la sortie du graphe soit aussi proche que possible d'une sortie souhaitée pour une entrée donnée. Lorsque le graphe dans son ensemble tend vers un tel état, on dit que le graphe converge. Après l'obtention d'un degré de convergence approprié, le graphe peut être utilisé pour réaliser des prédictions ou des inférences, c'est-à-dire pour prédire un résultat pour certaines entrées données ou pour inférer une cause pour une sortie donnée.

[0076] L'étape d'apprentissage peut prendre un certain nombre de formes possibles différentes. Par exemple, dans une approche supervisée, les données expérimentales d'entrée prennent la forme de données d'apprentissage, c'est-à-dire d'entrées qui correspondent à des sorties connues. Avec chaque point de données, l'algorithme peut ajuster les paramètres de telle sorte que la sortie concorde le plus précisément possible avec la sortie connue pour l'entrée donnée. Dans l'étape de prédiction ultérieure, le graphe peut alors être utilisé pour mapper une interrogation d'entrée sur une sortie prédite approximative (ou vice versa si on réalise une inférence). D'autres approches sont aussi possibles. Par exemple, dans une approche non supervisée, il n'y a pas de concept de résultat de référence pour chaque donnée d'entrée, et au lieu de cela on laisse l'algorithme d'intelligence artificielle identifier sa propre structure dans les données de sortie. Ou dans une approche par renforcement, l'algorithme essaye au moins une sortie possible pour chaque point de données dans les données expérimentales, et on lui indique si sa sortie est positive ou négative (et potentiellement un degré avec lequel elle est positive ou négative), par exemple gagné ou perdu, ou récompense ou cout, ou similaire. Sur de nombreux essais, l'algorithme peut progressivement ajuster les paramètres du graphe pour être capable de prédire des entrées qui vont conduire à un résultat positif. Les diverses approches et divers algorithmes pour l'apprentissage d'un graphe sont connus de l'homme de l'art de l'apprentissage automatique.

[0077] Selon un exemple d'application des techniques décrites ici, chaque fil du travail est programmé pour réaliser les calculs associés à un nœud individuel respectif des nœuds

102 dans un graphe d'intelligence artificielle comme un réseau neuronal. Dans ce cas, au moins certaines des arêtes 104 entre les nœuds 102 correspondent aux échanges de données entre des fils, et certaines peuvent impliquer des échanges entre des pavés. Dans le cas d'un agencement multi-pavé 6 avec plusieurs fils par pavé 4, chaque pavé 4 exécute un sous-graphe du graphe. Chaque sous-graphe comprend un sous-programme superviseur comprenant un ou plusieurs fils superviseurs, et un ensemble de fils de travail représentant les nœuds 102 du sous-graphe respectif.

Dans des applications comme l'intelligence artificielle, il serait souhaitable de pouvoir acheminer un flux de données de manière efficace vers et à partir de la mémoire de données 22 du processeur 4 (par exemple un pavé). Par exemple cela serait particulièrement utile (mais pas exclusivement) pour accompagner une séquence d'instructions arithmétiques complexes comme des instructions de produits scalaires vectoriels, de produits matriciels, de produits scalaires vectoriels à accumulation, de produits matriciels à accumulation ou des instructions de convolution dédiées, qui englobent un fort degré de complexité arithmétique dans une seule instruction arithmétique.

[0079] Pour répondre à ces problèmes, des modes de réalisation prévoient un type d'instruction de chargement-stockage, dans le jeu d'instructions du processeur 4, qui réalise deux opérations de chargement et une opération de stockage, puis applique ensuite automatiquement un pas de progression indépendant à chacune des adresses de chargement et de stockage, tout cela en réponse à une seule instance du code opération de l'instruction. En outre, l'instruction utilise un empaquetage efficace d'adresses dans le banc de registres approprié (par exemple le banc MRF 26M), d'où il résulte que les trois adresses (les deux adresses de chargement et l'adresse de stockage) sont empaquetées dans l'espace de deux registres. Cela permet aux trois adresses mémoire et au registre de pas d'être accédés en une seule instruction avec seulement trois ports d'accès à partir du MRF 26M, vers le LSU (un port respectif pour accéder à chacun des trois registres).

[0080] L'instruction peut être appelée ici "ld2xst64pace", en faisant référence au fait qu'elle charge deux valeurs de 64 bits et stocke une valeur de 64 bits, le terme "pace" étant synonyme de pas de progression. Toutefois cette étiquette ou les largeurs de bits particulières ne doivent pas être considérées comme étant nécessairement limitatives. L'instruction peut de manière plus générale être appelée simplement instruction de chargement-stockage (bien que cela n'implique pas qu'elle soit nécessairement la seule sorte d'instructions de chargement-stockage dans le jeu d'instructions du processeur), ou "ldx2st" (chargement fois deux et stockage). Sa syntaxe est la suivante :

[0081] ld2xst \$aDst, \$aSrc, \$mAddr, \$mStride, Strimm

[0082] \$aDst fait référence à un ou plusieurs opérandes identifiant une destination dans le

banc de registres auxiliaire (ou arithmétique) (ARF) 26A, la destination comprenant un ou plusieurs des registres se trouvant dans le banc ARF. Dans des modes de réalisation, chacun des registres se trouvant dans le banc ARF a une largeur de 32 bits, et la destination \$aDst peut être constituée de quatre registres de 32 bits de la sorte : \$aDst0:Dst0+3. L'opérande de destination du ld2xst64pace peut spécifier l'emplacement de seulement l'un de ces registres de destination dans le banc ARF (par exemple le plus bas \$aDst0) et les emplacements de l'autre ou des autres peuvent être implicites par rapport à celui-ci (par exemple, les trois registres contigus suivants dans le banc ARF). En variante dans d'autres mises en œuvre, il n'est pas exclu que chacun des multiples opérandes de destination puisse être identifié explicitement ou indépendamment par des opérandes séparés (bien que cela nécessite une largeur d'instruction augmentée).

- \$aSrc fait référence à un ou plusieurs opérandes identifiant une source dans le banc ARF, 26A, la source comprenant un ou plusieurs des registres se trouvant dans le banc ARF. Dans des modes de réalisation chacun des registres se trouvant dans le banc ARF a une largeur de 32 bits, et la source \$aSrc peut être constituée de deux registres de 32 bits de la sorte : \$aSrc0:Src+1. L'opérande de source du ld2xst64pace peut spécifier l'emplacement de seulement l'un de ces trois registres de source dans le banc ARF (par exemple le plus bas \$aSrc0) et l'emplacement de l'autre ou des autres peut être implicite par rapport à celui-ci (par exemple le registre contigu suivant dans le banc ARF). En variante dans d'autres mise en œuvre, il n'est pas exclu que chacun des multiples opérandes de source puisse être identifié explicitement et indépendamment par des opérandes séparés (bien que cela nécessite une largeur d'instruction augmentée).

- [0084] \$mAddr fait référence à un ou plusieurs opérandes spécifiant l'emplacement de deux registres \$mAddr0:Addr0+1 dans le banc de registres principal (MRF) 25M, qui entre eux contiennent trois adresses : deux adresses de chargement et une adresse de stockage. Dans des modes de réalisation chacun des registres se trouvant dans le MRF a une largeur de 32 bits. L'opérande d'adresse mémoire peut spécifier l'emplacement de seulement l'un de ces registres dans le MRF (par exemple le plus bas \$mAddr0), l'emplacement de l'autre étant implicite par rapport à celui-ci (par exemple le registre contigu suivant dans le MRF). En variante, dans d'autres mises en œuvre, il n'est pas exclu que chacun des registres d'adresses mémoire puisse être identifié explicitement et indépendamment par des opérandes séparés (bien que cela nécessite une largeur d'instruction augmentée).

- [0085] Strimm est un ensemble d'opérandes immédiats, un opérande respectif pour chacune des adresses des deux chargements et du stockage. Dans le MRF, 26M, on prévoit un registre de pas qui comprend une pluralité de champs. Chaque champ contient une

valeur respective différente d'un ensemble prédéterminé de valeurs de pas possibles différentes. Une valeur de pas est une valeur de laquelle on incrémente une adresse mémoire, c'est-à-dire un pas d'adresse mémoire, typiquement destiné à une utilisation dans une série de tels pas. Pour chacun des deux chargements et du stockage, l'opérande de pas immédiat respectif spécifie à partir de quel champ dans le registre de pas il faut prendre la valeur de pas à appliquer à l'adresse respective de chargement ou de stockage, après avoir réalisé l'opération de chargement ou de stockage respective de la présente instance de l'instruction. Cela réalise un déplacement le long de l'adresse dans le MRF, 26M, au bénéfice d'une instance suivante de l'instruction de chargement-stockage.

- [0086] Dans des modes de réalisation, l'unité de chargement-stockage 55 supporte une fonctionnalité par laquelle une valeur spéciale de l'opérande de pas immédiat peut directement spécifier une valeur de pas de 1 (c'est-à-dire une augmentation d'une unité d'adresse dans l'espace d'adresses utilisé), plutôt que de pointer vers un champ de registre. C'est-à-dire qu'en dehors de la plage de valeurs que l'opérande de pas immédiat peut prendre, l'une des valeurs spécifie un pas de un, et certaines ou la totalité des autres spécifient des champs possibles différents dans le registre de pas contenant des valeurs de pas programmables. Une unité désigne ici la taille atomique de l'accès aux données. Par exemple, si l'opérande est un vecteur à 4 éléments de valeurs en virgule flottante de 16 bits, l'incrément est de 1 atome/unité, ce qui est équivalent à 8 multiplets (64 bits).

- [0087] Le registre de pas est un registre dans le banc MRF, 26M. Dans des modes de réalisation le fil de travail lui-même est responsable de l'écriture des valeurs de pas dans les champs de son propre registre de pas (dans son propre banc MRF). En variante, il n'est pas exclu que dans d'autres mises en œuvre les valeurs de pas se trouvant dans les champs du registre de pas puissent être écrites par le fil superviseur SV, ou bien qu'une combinaison d'approches soit utilisée.

- L'obligation d'avoir un opérande spécifiant \$mStride est une fonctionnalité optionnelle du processeur 4 dépendant de la mise en œuvre. Dans des modes de réalisation, l'instruction de chargement-stockage prend un opérande spécifiant l'emplacement du registre de pas \$mStride dans le MRF, 26M. Ainsi le programme peut sélectionner le registre de pas parmi une pluralité de registres de pas possibles, assurant encore davantage de flexibilité dans la sélection du pas. Toutefois, dans des variantes de réalisation il n'est pas exclu que l'emplacement de \$mStride puissent être fixe ou implicite et ne nécessite pas d'opérande dans l'instruction de chargement-stockage.

- [0089] La figure 7 illustre un exemple de l'empaquetage de trois adresses dans deux registres de 32 bits dans le MRF, 26M, chaque adresse étant sur 21 bits. La figure 7

illustre aussi un exemple de l'empaquetage de trois valeurs de pas dans un registre de 32 bits dans le MRF, chaque valeur de pas étant sur 10 bits (dans ce cas deux bits du registre restent inutilisés). Ainsi l'instruction de chargement-stockage peut accéder à trois adresses mémoire via seulement deux ports larges de 32 bits du MRF en une seule instruction. Un troisième port large de 32 bits peut être utilisé par la même instruction pour accéder au registre de pas, contenant par exemple trois valeurs de pas de 10 bits (deltas d'adresse) dans trois champs larges de 10 bits disposés dans un registre de pas large de 32 bits dans le MRF (laissant 2 bits de ce registre inutilisés). On notera que la disposition particulière représentée en figure 7 n'est qu'un exemple. Par exemple, dans une autre mise en œuvre addr2 peut être à cheval sur les deux registres, plutôt que addr1.

- [0090] La figure 8 illustre un agencement de multiples registres de pas \$mStrideA, \$mStrideB, \$mStrideC ... dans le MRF, 26M. L'un quelconque de ces registres pourrait être spécifié comme étant le registre de pas \$mStride par l'opérande correspondant de l'instruction de chargement-stockage. Chaque registre de pas possible comprend une pluralité de champs, par exemple dans des modes de réalisation au nombre de trois (bien que cela dépende de la mise en œuvre il n'y a pas nécessairement le même nombre de champs ni de registres de pas qu'il n'y a d'adresses de chargement et de stockage). Pour chacune des adresses des deux chargements et du stockage, l'opérande immédiat respectif dans l'ensemble de valeurs immédiates Strimm peut spécifier l'un des champs possibles dans le registre de pas \$mStride à partir duquel il faut prendre une valeur de pas respective (un delta d'adresse à appliquer à la suite du chargement ou du stockage respectif). Par exemple, dans des modes de réalisation, si l'opérande de pas est de 2 bits pour chacun des deux chargements et du stockage, alors trois des valeurs possibles spécifient des champs différents parmi les trois champs de pas, et l'autre valeur possible spécifie simplement un pas de un sans faire référence à une valeur contenue dans un registre. Par exemple 00 va spécifier un pas de 1 (atome), tandis que le 01 va spécifier un premier champ dans le registre de pas, 10 va spécifier un deuxième champ dans le registre de pas et 11 va spécifier un troisième champ dans le registre de pas.

- [0091] On notera que dans des modes de réalisation, l'une des valeurs possibles de la valeur immédiate de pas spécifie un incrément par défaut de 1, au lieu d'un champ dans le registre de pas \$mStride.

- [0092] En fonctionnement, lorsqu'il est exécuté par l'unité d'exécution 18, le code opération de l'instruction de chargement-stockage (après décodage par l'étage de décodage 16) déclenche le LSU 55 pour réaliser les opérations suivantes. Il charge les valeurs à partir des deux adresses de chargement dans la mémoire 22, comme spécifié par l'adresse contenue dans \$mAddr dans le MRF, 26M, dans la destination dans le banc

ARF, 26A, spécifié par \$aDsc. En outre, il mémorise la ou les valeurs provenant de \$aSrc dans le banc ARF dans l'adresse de stockage en mémoire 22 spécifiée par l'adresse contenue dans \$mAddr dans le banc MRF. Le LSU 55 post-incrémente ensuite indépendamment chacune des deux adresses de chargement et l'adresse de stockage de la valeur de pas respective provenant du champ respectif du registre de pas \$mStride dans le MRF, spécifié par l'opérande respectif parmi les trois opérandes immédiats Strimm.

[0093] On notera que pour chacune des adresses des deux chargements et du stockage de l'instance courante de l'instruction de chargement-stockage, l'opération de pas de progression de l'instruction courante incrémente l'adresse respective du pas respectif à la suite de chacune des opérations de chargement et de stockage de l'opération de chargement-stockage courante, respectivement. En fonction de la mise en œuvre, cela peut signifier que tous les incréments sont appliqués ensemble après les deux chargements et le stockage, par exemple, chargement, chargement, stockage, incrément, incrément, incrément. En variante, l'opération de pas peut incrémenter l'adresse respective immédiatement à la suite de chaque chargement et du stockage, par exemple chargement, incrément, chargement, incrément, stockage, incrément. En effet le stockage pourrait aussi venir avant l'un des chargements ou avant les deux. Ce qui importe c'est simplement que l'incrément de chaque adresse de chargement soit fait après son chargement respectif, et l'incrément de l'adresse de stockage soit fait après le stockage. L'essentiel est de se déplacer suivant les adresses de chargement et de stockage dans le MRF pour être prêt pour une instance suivante de l'instruction de chargement-stockage.

[0094] Dans des modes de réalisation, la mémoire 11 (ou au moins la mémoire de données 22) comporte seulement deux ports d'accès de 64 bits pour charger des données à partir de la mémoire, et seulement un port d'accès d'une largeur de 64 bits pour stocker des données dans la mémoire. Dans des modes de réalisation, le MRF, 26M (d'un contexte donné) comporte seulement trois ports d'une largeur de 32 bits vers l'unité de chargement-stockage 55 ; et le banc ARF, 26A (d'un contexte donné) comporte seulement un port d'une largeur de 64 bits vers l'unité de chargement-stockage 55. (On notera que dans l'exemple illustré, l'IALU 56 est utilisé pour récupérer les pointeurs dans le MRF 26M et pour calculer les adresses à partir de ceux-ci afin de les passer au LSU 55, et ainsi en effet l'IALU 56 agit comme partie du LSU 55. Par conséquent dans cet exemple les trois ports allant du MRF 26M vers le LSU 55 comprennent les trois ports allant du MRF 26M vers l'IALU 56. Aussi il n'est pas exclu que dans d'autres mises en œuvre le LSU 55 puisse récupérer les pointeurs dans le MRF 26M directement et calculer ses propres adresses sur la base de ceux-ci).

[0095] Dans des modes de réalisation, les quatre registres de destination de 32 bits

\$aDst0:Dst0+3 dans le banc ARF (128 bits au total) peuvent être utilisés pour charger, à partir de la mémoire 22, par exemple un vecteur de quatre éléments de valeurs en virgule flottante de 16 bits (f16) et un vecteur de deux éléments de valeurs en virgule flottante de 32 bits (f32). Les deux registres de source de 32 bits \$aSrc0:Src+1 se trouvant dans le banc ARF (64 bits au total) peuvent être utilisés pour mémoriser, dans la mémoire 22, par exemple un vecteur de deux éléments de 32 bits de valeurs f32.

[0096] Pour être utilisée dans un programme, l'instruction de chargement-stockage est intercalée parmi d'autres types d'instructions comme des instructions arithmétiques qui prennent des entrées à partir des destinations des instructions de chargement, réalisent des opérations sur la base de celles-ci, et fournissent des résultats aux sources de l'instruction de chargement-stockage. C'est-à-dire que le programme comprend des instances de l'instruction de chargement-stockage et des instances d'au moins une instruction arithmétique, comme l'instruction de produit scalaire vectoriel, l'instruction de produit matriciel, l'instruction de produit scalaire vectoriel à accumulation, l'instruction de produit matriciel à accumulation ou l'instruction de convolution mentionnées précédemment ; les destinations d'au moins certaines des instructions de chargement-stockage étant les sources d'au moins certaines des instructions arithmétiques, et les destinations d'au moins certaines des instructions arithmétiques étant les sources d'au moins certaines des instructions de chargement-stockage. Grâce à la forte densité sémantique de l'instruction de chargement-stockage, avec ses deux chargements et sa fonctionnalité de pas, cela permet au programme de travailler efficacement à travers les données avec une faible charge de code dépensée pour les opérations de chargement et de stockage.

[0097] Par exemple, le programme peut comprendre une série de paires d'instructions, chaque paire d'instructions étant constituée d'une instance de l'instruction de chargement-stockage, suivie d'une instance correspondante d'une instruction arithmétique. Dans chaque paire d'instructions, la source de l'instruction de chargement-stockage est définie comme étant la destination de l'instruction arithmétique provenant d'une paire précédente, et les destinations de l'instruction de chargement-stockage sont définies comme étant les sources de l'instruction arithmétique correspondante dans la paire courante ou une paire ultérieure. Par exemple, considérons une instruction arithmétique "arith" ayant comme syntaxe :

[0098] arith \$aDst, \$aSrcA, \$aSrcB

[0099] où \$aDst désigne un opérande spécifiant une destination dans le banc ARF, 26A; et \$aSrcA, \$aSrcB désignent des opérandes spécifiant deux sources dans le banc ARF (on notera que "arith" est un nom générique utilisé ici pour toute instruction arithmétique ayant au moins cette syntaxe). Le programme peut ensuite être programmé avec une série de paires d'instructions, par exemple :

```

[0100]

[0101]

ldx2st Xin-Pin, Pout, Tripacked, Strides; arith Pout, Xin, Pin;

[0102]

ldx2st Xin-Pin, Pout, Tripacked, Strides; arith Pout, Xin, Pin;

[0103]

ldx2st Xin-Pin, Pout, Tripacked, Strides; arith Pout, Xin, Pin;

[0104]

ldx2st Xin-Pin, Pout, Tripacked, Strides; arith Pout, Xin, Pin;

[0105]

[0106]

ou:

[0107]

[0108]

ldx2st Xin-Pin, Pout_A, Tripacked, Strides; arith Pout_A, Xin, Pin;

[0109]

ldx2st Xin-Pin, Pout B, Tripacked, Strides; arith Pout B, Xin, Pin;

[0110]

ldx2st Xin-Pin, Pout_A, Tripacked, Strides; arith Pout_A, Xin, Pin;

[0111]

ldx2st Xin-Pin, Pout B, Tripacked, Strides; arith Pout B, Xin, Pin;

[0112]

[0113]

etc.

```

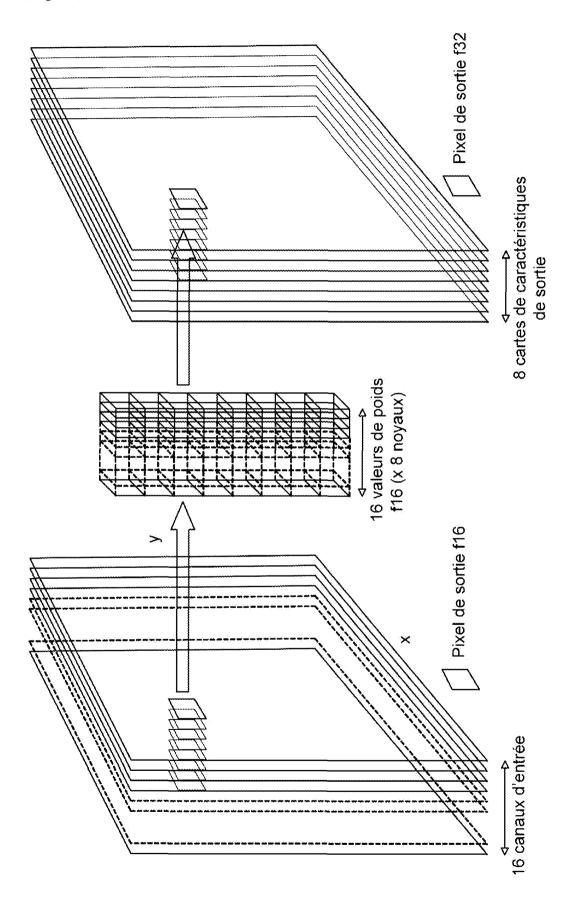

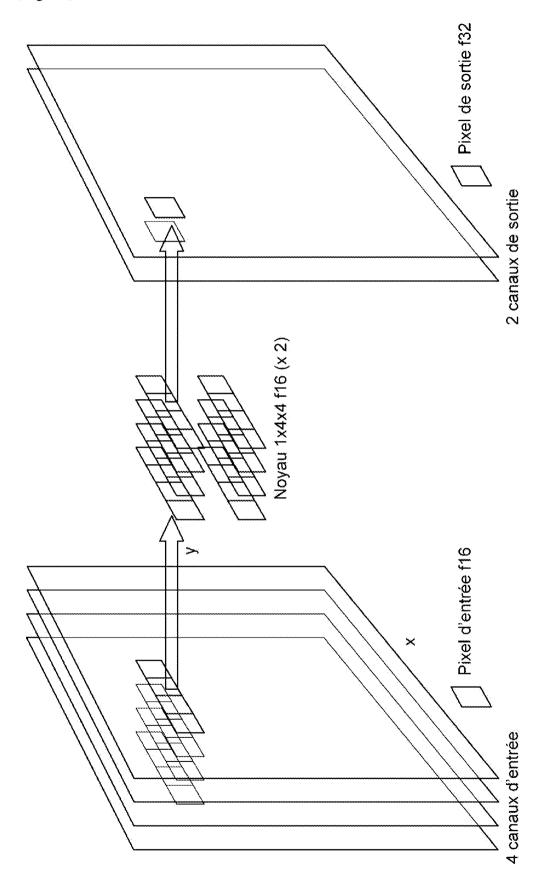

- Dans des modes de réalisation, chaque paire est un groupe d'instructions, c'est-à-dire des instructions exécutées simultanément en suivant des pipelines respectifs. Par exemple, dans des modes de réalisation l'instruction de chargement-stockage est exécutée par le pipeline principal en utilisant le banc MRF, 26M, et l'instruction arithmétique est exécutée en parallèle par le pipeline auxiliaire en utilisant le banc ARF, 26A. Toutefois, dans des variantes de réalisation il n'est pas exclu que l'instruction de chargement-stockage et l'instruction arithmétique puissent être exécutées l'une après l'autre par l'intermédiaire d'une seule unité de traitement en pipeline.