US 20070216000A1

### (19) United States (12) Patent Application Publication (10) Pub. No.: US 2007/0216000 A1

### Sep. 20, 2007 (43) **Pub. Date:**

### Sasamura et al.

### (54) COVER TAPE FOR PACKAGING SEMICONDUCTOR DEVICE AND PACKAGE FOR SEMICONDUCTOR DEVICE

(75) Inventors: Keiichi Sasamura, Kawasaki (JP); Kenichi Yazaki, Kawasaki (JP); Yuuzou Hamanaka, Kawasaki (JP); Yukio Ando, Kawasaki (JP); Hideyasu Hashiba, Kawasaki (JP)

> Correspondence Address: WESTERMAN, HATTORI, DANIELS & ADRIAN, LLP 1250 CONNECTICUT AVENUE, NW, SUITE 700 WASHINGTON, DC 20036

- FUJITSU LIMITED, Kawasaki (73) Assignee: (JP)

- 11/541,727 (21) Appl. No.:

- (22)Filed: Oct. 3, 2006

- (30) **Foreign Application Priority Data**

- Mar. 16, 2006 (JP) ..... 2006-073586

### **Publication Classification**

- (51) Int. Cl. (2006.01)H01L 23/02

- (52) U.S. Cl. ..... 257/678

#### ABSTRACT (57)

The purpose of the present invention is to provide a cover tape for packaging semiconductor device which protects the outer shape of the semiconductor device, and is capable of improving the mounting speed of the semiconductor device by shipment in tape, and a package for semiconductor device using the cover tape for packaging semiconductor device. The cover tape for packaging semiconductor device of the present invention has a net-like structure 20 at least in a portion, and the cover tape for packaging semiconductor device is pasted onto an embossed tape which has a number of pockets containing semiconductor devices so as to cover the pockets. The package for semiconductor device of the present invention contains an embossed tape which has a number of pockets which contain semiconductor devices, and the cover tape for packaging semiconductor device of the present invention.

FIG. 1A

FIG. 1B

FIG. 1C

# FIG. 1D

## FIG. 1E

# FIG. 1F

FIG. 1H

FIG. 1I

FIG. 2A

FIG. 2B

### COVER TAPE FOR PACKAGING SEMICONDUCTOR DEVICE AND PACKAGE FOR SEMICONDUCTOR DEVICE

### CROSS-REFERENCE TO RELATED APPLICATIONS

**[0001]** This application is based upon and claims the benefits of the priority from the prior Japanese Patent Application No. 2006-073586, filed on Mar. 16, 2006, the entire contents of which are incorporated herein by reference.

### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

**[0003]** The present invention relates to a cover tape for packaging semiconductor device which ensures quality and reliability of a semiconductor device by protecting the outer shape of the semiconductor device, and is capable of improving the mounting speed of the semiconductor device by shipment in tape, and a package for semiconductor device.

[0004] 2. Description of the Related Art

[0005] The shipment in embossed tape has been employed as a delivering embodiment of a semiconductor device for mounting the semiconductor device on a substrate. In the shipment in embossed tape, the semiconductor device is delivered packaged in a package which contains an embossed tape on which pockets for containing the semiconductor device are formed in accordance with the shape of the semiconductor device such as LSIs, etc. and a cover tape which packs the embossed tape. The semiconductor device contained in the package is taken out after the cover tape is peeled off and mounted on a surface of the substrate automatically. Because the embossed tape is advantageous in being able to transport the semiconductor device such as LSIs, etc. in large quantity and in enabling high-speed mounting of the semiconductor device on a substrate by users, the demand for shipment in embossed tape is growing in recent years.

**[0006]** However, with a progress of polarization (grow in size and downsizing) of semiconductor devices, small, thin and light electronic components such as CSP/CHIP, etc. are being shipped or mounted in tray because shipment in embossed tape is difficult due to manufacturing of the embossed tape which makes the high-precision processing impossible.

**[0007]** The shipment in tray has a problem in mounting speed which is two to three times slower compared to that of the shipment in tape because of the delay caused by the use of intermediate table when a general-purpose mounting device is used. Moreover, there are two types of mounting device: general-purpose type which is applicable for both shipments in tray and tape and high-speed type which is applicable only for shipment in tape. The mounting device of high-speed type has a problem that it is not applicable for shipment in tray.

**[0008]** Therefore, it is necessary to improve the embossed tape and to realize the use of the high-speed mounting device by shipment in embossed tape in order to realize high-speed mounting of the semiconductor device.

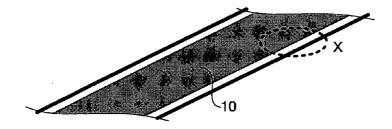

**[0009]** For example, a tape wound on a reel as shown in FIG. 1A is known as the embossed tape. An enlarged view of the embossed tape in X portion surrounded by dashed line

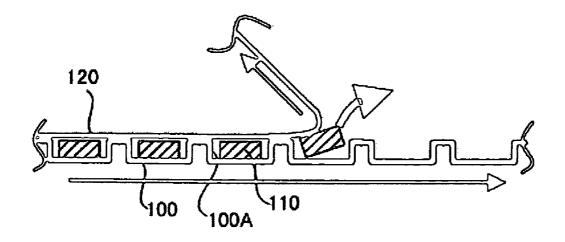

in FIG. 1A is shown in FIG. 1B and a cross-sectional view is shown in FIG. 1C. As shown in FIG. 1C, semiconductor devices, IC chips 110 are packed in a package containing an embossed tape 100 on which pockets 100A which contain the IC chips 110 are formed and a cover tape 120 which packs the embossed tape 100. The IC chips 110 contained in the pockets 100A are transported in high speed, and taken out after the cover tape 120 is peeled off in high speed during mounting on the substrate. During this time, there has been a problem with conventional cover tape 120 that the IC chips 110 pop out from the pockets 100A due to absorption at low-pressure and static electricity, etc.

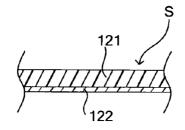

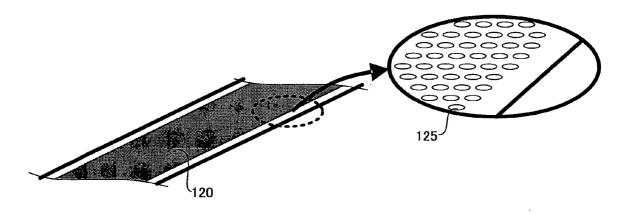

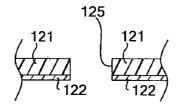

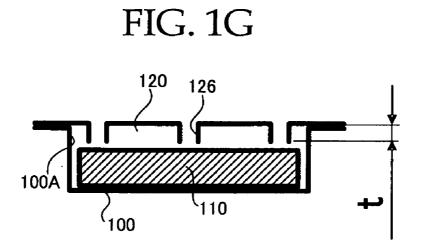

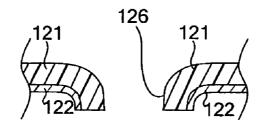

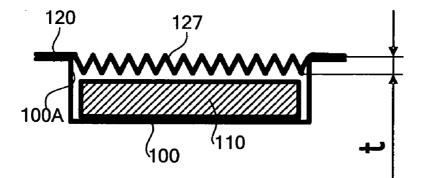

[0010] For this reason, cover tapes on which openings 125 or openings 126 are formed as shown in FIGS. 1E and 1G (Japanese Patent Application Laid-Open (JP-A) No. 4-031215 and 2005-132421) and a cover tape on which projections 127 are formed as shown in FIG. 1I (JP-A No. 2005-35636) have been proposed. These cover tapes 120 inhibit popping out, etc. of the semiconductor devices (IC chips 110) which occurs during peeling off of the cover tapes 120 by decreasing the contact area between upper surface of the semiconductor devices (IC chips 110) and the cover tapes 120 with the openings 125, the openings 126 or the projections 127. However, when forming the projections 127, exclusive cover tape is needed for every pockets 100A pitch. Furthermore, it becomes necessary to make the depth of the pockets 100A as much deeper as the height "t" of the projections on the cover tape 120 on which the projections 127 are formed as shown in FIG. 1I and the cover tape 120 on which the openings 126 are formed in form of projection as shown in FIG. 1G. Further, when the openings 125 shown in FIG. 1E and the openings 126 shown in FIG. 1G are formed, an insulating layer 122 is in contact with or adjacent to the semiconductor device because end faces of the openings 125 and 126 of the cover tapes 120 are exposed as shown in cross-sectional views in FIGS. 1F and 1H. Generally, a sheet S prior to forming of cover tape 120 has a two-layer structure containing an insulating layer 121 and an antistatic layer 122 for material cost reduction as shown in FIG. 1D. Because the insulating layer 121, which takes over the most part of the sheet S, does not have conductive and antistatic functions, a problem of circuit destruction due to charged semiconductor device or dust generated from the end faces of the openings 125 and 126 which attaches to the semiconductor device during mounting on the substrate occurs as shown in FIGS. 1F and 1H.

**[0011]** In consequence, a cover tape for packaging semiconductor device which prevents generation of powder dust by inhibiting static electricity, ensures quality and reliability of a semiconductor device and is capable of improving the mounting speed of the semiconductor device by shipment in tape have not yet been provided and further development is desired.

**[0012]** It is an object of the present invention to solve foregoing problems and to fulfill the following purposes.

**[0013]** The purpose of the present invention is to provide a cover tape for packaging semiconductor device which ensures quality and reliability of a semiconductor device by protecting the outer shape of the semiconductor device, and is capable of improving the mounting speed of the semiconductor device by shipment in tape, and a package for semiconductor device using the cover tape for packaging semiconductor device.

#### SUMMARY OF THE INVENTION

**[0014]** The measures to solve above problems are as follows.

**[0015]** The cover tape for packaging semiconductor device of the present invention has a net-like structure at least in a portion and is pasted onto an embossed tape which contains a number of pockets containing semiconductor devices so as to cover the pockets.

**[0016]** Since the cover tape for packaging semiconductor device has the net-like structure at least in a portion, the contact area with the semiconductor device is decreased because of the multiple airspaces provided by the net-like structure and the airspaces exhibit ventilation function enabling to inhibit the popping out of the semiconductor devices caused by absorption at low pressure and static electricity, etc. which occurs during high-speed transportation and high-speed peeling. Therefore, the cover tape for packaging semiconductor device, is capable of improving the mounting speed of the semiconductor device by shipment in tape and can be suitably used for shipment in tape of small-size package, particularly small, thin and light electronic components such as CSP/CHIP.

**[0017]** The package for semiconductor device of the present invention contains an embossed tape which has a number of pockets containing semiconductor devices and a cover tape for packaging semiconductor device of the present invention.

**[0018]** Since the package for semiconductor device uses the cover tape for packaging semiconductor device of the present invention, it is possible to transport the semiconductor device while ensuring its quality and reliability and the package for semiconductor device can be suitably used for high-speed transportation of the electronic components such as the semiconductor device by shipment in tape.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0019]** FIG. **1**A is a photograph showing an overall view of an exemplary embossed tape and cover tape wound on a reel.

**[0020]** FIG. 1B is a photograph showing a plain view of the embossed tape and the cover tape of FIG. 1A.

**[0021]** FIG. 1C is a schematic cross-sectional view showing the embossed tape and the cover tape shown in FIGS. 1A and 1B.

**[0022]** FIG. 1D is a schematic cross-sectional view showing an exemplary layer composition of the conventional cover tape.

**[0023]** FIG. 1E is a perspective view showing an example (first view) of the conventional cover tape of an aspect in which openings are disposed on the cover tape.

**[0024]** FIG. 1F is a schematic cross-sectional view showing the cover tape shown in FIG. 1E.

**[0025]** FIG. 1G is a cross-sectional view showing an example (second view) of the conventional cover tape of an aspect in which openings in form of projection are disposed on the cover tape.

**[0026]** FIG. 1H is a schematic cross-sectional view showing the cover tape shown in FIG. 1G.

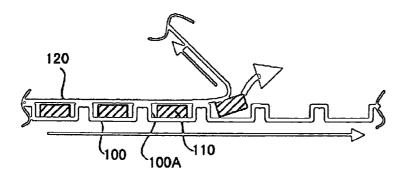

**[0027]** FIG. 1I is a cross-sectional view showing an example (third view) of the conventional cover tape of an aspect in which projections are disposed on the cover tape. **[0028]** FIG. 2A is a perspective view showing the cover tape for packaging semiconductor device of the present invention in the first embodiment.

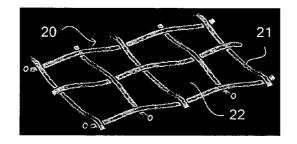

**[0029]** FIG. **2**B is a schematic diagram showing a net-like structure of the cover tape for packaging semiconductor device of the present invention in the first embodiment.

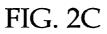

**[0030]** FIG. **2**C is a schematic cross-sectional view showing the cover tape for packaging semiconductor device of the present invention in the first embodiment.

### DESCRIPTION OF THE PREFERRED EMBODIMENTS

**[0031]** The cover tape for packaging semiconductor device of the present invention will be explained in detail referring to figures below.

### First Embodiment

**[0032]** The first embodiment of the cover tape for packaging semiconductor device of the present invention will be explained referring to figures below.

**[0033]** FIG. **2**A is a perspective view showing the cover tape for packaging semiconductor device of the present invention in the first embodiment.

[0034] A cover tape 10 as shown in FIG. 2A is pasted on the embossed tape for use. The embossed tape is not particularly limited and may be selected from known embossed tapes accordingly. Examples include an embossed tape 100 as shown in FIG. 1C on which pockets (concave portions) 100A are formed at regular intervals in a length direction for containing semiconductor devices (IC chips 110, for example). The cover tape 10 prevents dropout of semiconductor devices (IC chips 110, for example) contained in the pockets 100A on the embossed tape 100 when pasted on the embossed tape 100. Furthermore, the cover tape 10 is shipped and transported as wound on reels with the embossed tape 100 (FIG. 1A). The semiconductor device mentioned here is not particularly limited and may be selected accordingly. It is preferably small, thin and light electronic components such as CSP/CHIP, etc. and examples include LSIs and condensers.

**[0035]** FIG. **2B** is a partially enlarged view showing the X portion surrounded by dotted lines in the cover tape **10** of FIG. **2A**. The cover tape **10** has a net-like structure **20** as shown in FIG. **2B**, and the net-like structure **20** is formed of a string-like member **21** woven in a grid pattern.

**[0036]** The shape, size, thickness and constituent material of the cover tape **10** are not particularly limited and may be selected accordingly. Because of the net-like structure **20** contained in the cover tape **10**, the contact area with semiconductor device is decreased and absorption at low pressure and static electricity can be prevented.

**[0037]** The net-like structure **20** is not particularly limited and may be selected accordingly as long as it has multiple airspaces for ventilation function and examples include a structure formed of the string-like member **21** woven in a grid pattern. The net roughness of the net-like structure **20** is not particularly limited and may be adjusted accordingly. The net-like structure preferably has a roughness to some degree without causing peeling off in terms of decreasing the contact area with the semiconductor device. **[0038]** The location of formation of the net-like structure **20** in the cover tape **10** is not particularly limited and may be selected accordingly. The net-like structure **20** may be formed in the entire cover tape **10** or formed locally so as to be located only above the pockets where semiconductor devices are contained when pasted on the embossed tape.

**[0039]** The width of the string-like member **21** is not particularly limited and may be selected accordingly. Further, method for weaving the string-like member **21** to form net-like structure **20** is not particularly limited and may be selected accordingly and examples include plain weaving.

**[0040]** The shape of the cover tape **10** is not particularly limited and may be selected accordingly. It is preferably in form of strips and the vertical cross section preferably has irregularity relative to the horizontal plane. If the vertical cross section has irregularity, it is possible to decrease the contact area between the cover tape **10** and the semiconductor device.

**[0041]** The size of the cover tape **10** is not particularly limited and may be adjusted corresponding to the size of the embossed tapes and the pockets.

**[0042]** The thickness of the cover tape **10** is not particularly limited and may be adjusted accordingly. It is preferably thin because it eliminates the need for designing the pocket depth deeper.

**[0043]** The constituent material for the cover tape **10** is not particularly limited and may be selected accordingly. The cover tape **10** is preferably made of an insulating layer and an antistatic layer which covers the insulating layer.

**[0044]** The material (insulating material) for the insulating layer is not particularly limited and may be selected accordingly and examples include PET (polyethylene terephthalate).

**[0045]** The material (antistatic material) for the antistatic layer is not particularly limited and may be selected accordingly. Examples include PE (polyethylene) to which antistatic agent is applied or kneaded in.

[0046] The cover tape 10 may have a net-like structure 20 made of an insulating layer formed of woven string-like member 21 made of the insulating material and the net-like structure 20 may be coated with an antistatic layer made of the antistatic material. For example, the cover tape 10 may have a net-like structure 20 formed of a woven fibrous (string-like) member (hereinafter, may be referred to as "cover tape material") 21 having a core-shell structure containing an inner layer (insulating layer) 21A formed of the insulating material and an outer layer (antistatic layer) 21B formed of the antistatic material as shown in the cross-sectional view of FIG. 2C. In these cases, since the cover tape 10 formed of the woven string-like member 21 is in woven form, and small irregularity (the crossings of the string-like member 21 corresponds to the convex portions) and openings 22 are formed naturally by crossings of the string-like member 21, it is possible to omit forming of projections 127 or openings 125 and 126 which are required for conventional cover tape 120 as shown in FIGS. 1E to 1I, allowing simplification of manufacturing process.

**[0047]** Moreover, the insulating layer is not exposed as in the case of conventional cover tape **120** shown in FIGS. 1E to **1**H because the insulating layer is coated with the antistatic layer. Therefore, the insulating layer does not come near and/or in contact with the semiconductor device and the

cover tape 10 excels in protection for outer shapes and circuits of the semiconductor devices compared to the conventional cover tape 120.

**[0048]** Furthermore, it is necessary to make the depth of the pockets **100**A as much deeper as the height "t" of the projections in the conventional cover tape **120** shown in FIGS. 1G to **11** and the number of semiconductor device contained per **1** reel is decreased. However, because irregularity of the vertical cross section relative to the horizontal plane in the cover tape for packaging semiconductor device of the present invention is small, designing the pocket depth deeper is not necessary and in addition, the cover tape for packaging semiconductor device of the present invention is applicable for any pocket pitch.

**[0049]** Since the cover tape for packaging semiconductor device in the first embodiment has the net-like structure, the contact area with the semiconductor device is small and ventilation function is exhibited, thereby inhibiting popping out of semiconductor devices caused by absorption at low pressure and static electricity, etc. which occurs during high-speed transportation and high-speed peeling.

**[0050]** Moreover, because the insulating layer does not come near and/or in contact with the semiconductor device, it is possible to ensure quality and reliability of a semiconductor device by preventing circuit destruction caused by frictional electrification with the semiconductor device. And it is also possible to prevent dust generated from end faces of openings from attaching to the lead terminals of the semiconductor device and the substrate during mounting, as in the case of the conventional cover tapes.

**[0051]** Furthermore, height of the irregularity forming the net-like structure is small, thereby eliminating the need for designing pockets deeper and allowing the number of semiconductor devices contained per 1 reel to increase.

**[0052]** Further, the cover tape for packaging semiconductor device in the first embodiment can be suitably used as a package for semiconductor device by pasting onto the embossed tape which has been selected accordingly.

**[0053]** By the present invention, it is possible to solve foregoing problems and to provide a cover tape for packaging semiconductor device which ensures quality and reliability of a semiconductor device by protecting the outer shape of the semiconductor device, and is capable of improving the mounting speed of the semiconductor device by shipment in tape, and a package for semiconductor device.

**[0054]** The cover tape for packaging semiconductor device of the present invention can ensure quality and reliability of a semiconductor device by protecting the outer shape of the semiconductor device, and improve the mounting speed of the semiconductor device by shipment in tape. Therefore, the cover tape for packaging semiconductor device of the present invention can be suitably used for shipment in tape of small-size package, particularly small, thin and light electronic components such as CSP/CHIP, etc. of the semiconductor device of the present invention in particular.

**[0055]** The package for semiconductor device of the present invention can transport the semiconductor device while ensuring quality and reliability of the electronic components of the semiconductor device and can be suitably used for high-speed transportation of the semiconductor device by shipment in tape.

What is claimed is:

1. A cover tape for packaging semiconductor device comprising:

- a net-like structure,

- wherein the cover tape for packaging semiconductor device comprises the net-like structure at least in a portion, and

- the cover tape for packaging semiconductor device is pasted onto an embossed tape which comprises a number of pockets containing semiconductor devices so as to cover the pockets.

2. The cover tape for packaging semiconductor device according to claim 1, wherein the cover tape for packaging semiconductor device is in woven form.

3. The cover tape for packaging semiconductor device according to claim 1, wherein the net-like structure is formed of a woven string-like member.

4. The cover tape for packaging semiconductor device according to claim 3, wherein the string-like member comprises an insulating material which is coated with an anti-static material.

5. The cover tape for packaging semiconductor device according to claim 3, wherein the string-like member comprises the insulating material, and a grid insulating layer, which is formed of the woven string-like member, is coated with an antistatic layer comprising the antistatic material.

6. The cover tape for packaging semiconductor device according to claim 1, wherein the net-like structure is located only in an area corresponding to the pocket of the embossed tape.

7. The cover tape for packaging semiconductor device according to claim 3, wherein the net-like structure is located only in an area corresponding to the pocket of the embossed tape.

8. A package for semiconductor device, comprising:

an embossed tape; and

a cover tape for packaging semiconductor device,

- wherein the embossed tape comprises a number of pockets which contain semiconductor devices, and

- the cover tape for packaging semiconductor device comprises:

a net-like structure,

- wherein the cover tape for packaging semiconductor device comprises the net-like structure at least in a portion, and

- the cover tape for packaging semiconductor device is pasted onto an embossed tape which comprises a number of pockets containing semiconductor devices so as to cover the pockets.

9. The package for semiconductor device according to claim 8, wherein the cover tape for packaging semiconductor device is in woven form.

**10**. The package for semiconductor device according to claim **8**, wherein the net-like structure is formed of a woven string-like member.

11. The package for semiconductor device according to claim 10, wherein the string-like member comprises an insulating material which is coated with an antistatic material.

12. The package for semiconductor device according to claim 10, wherein the string-like member comprises the insulating material, and a grid insulating layer, which is formed of the woven string-like member, is coated with an antistatic layer comprising the antistatic material.

**13**. The package for semiconductor device according to claim **8**, wherein the net-like structure is located only in an area corresponding to the pocket of the embossed tape.

14. The package for semiconductor device according to claim 10, wherein the net-like structure is located only in an area corresponding to the pocket of the embossed tape.

\* \* \* \* \*