## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111524794 A (43)申请公布日 2020.08.11

(21)申请号 201910107844.9

H01L 23/528(2006.01)

(22)申请日 2019.02.02

(71)申请人 中芯国际集成电路制造(上海)有限 公司

地址 201203 上海市浦东新区中国(上海) 自由贸易试验区张江路18号

申请人 中芯国际集成电路制造(北京)有限 公司

(72)发明人 陈卓凡 张海洋

(74)专利代理机构 上海知锦知识产权代理事务 所(特殊普通合伙) 31327

代理人 高静 李丽

(51) Int.CI.

H01L 21/033(2006.01)

**H01L 21/768**(2006.01)

权利要求书4页 说明书18页 附图10页

#### (54)发明名称

半导体结构及其形成方法

#### (57)摘要

一种半导体结构及其形成方法,方法包括:提供基底;在基底上形成待刻蚀材料层;在待刻蚀材料层上形成掩膜材料层;对部分区域的掩膜材料层进行第一掺杂处理,在第一掺杂处理后,掩膜材料层包括掩膜材料层第一部分和待去除的掩膜材料层第二部分,掩膜材料层第一部分为经第一掺杂处理的部分或者掩膜材料层第一部分为经第一掺杂处理的部分;在掩膜材料层第二部分为经第一掺杂处理的部分;在掩膜材料层第二部分为经第一沟槽,至少位于掩膜材料层第一部分内;去除掩膜材料层第二部分,在剩余掩膜材料层为形成第二沟槽;去除第一沟槽和第二沟槽露出的待刻蚀材料层,形成目标图形层;形成目标图形层,大成目标图形层,大成目标图形层,大成目标图形层,大成目标图形层,大成目标图形层,大路剩余掩膜材料层。本发明提高了第一沟槽和第二沟槽的图形精度,相应提高了目标图形层中的图形精度。

CN 111524794 A

1.一种半导体结构的形成方法,其特征在于,包括:

提供基底:

在所述基底上形成待刻蚀材料层:

在所述待刻蚀材料层上形成掩膜材料层:

对部分区域的所述掩膜材料层进行第一掺杂处理,适于增大未经所述第一掺杂处理的掩膜材料层与经所述第一掺杂处理的掩膜材料层之间的去除选择比,其中,在所述第一掺杂处理后,所述掩膜材料层包括掩膜材料层第一部分和待去除的掩膜材料层第二部分,所述掩膜材料层第一部分为所述掩膜材料层中经所述第一掺杂处理的部分,或者,所述掩膜材料层第二部分为所述掩膜材料层中经所述第一掺杂处理的部分;

在所述第一掺杂处理之后,在所述掩膜材料层内形成露出部分所述待刻蚀材料层的第一沟槽,所述第一沟槽至少位于所述掩膜材料层第一部分内;

形成所述第一沟槽后,去除所述掩膜材料层第二部分,在剩余所述掩膜材料层内形成露出部分所述待刻蚀材料层的第二沟槽;

去除所述第一沟槽和第二沟槽露出的所述待刻蚀材料层,形成目标图形层:

形成所述目标图形层后,去除剩余所述掩膜材料层。

2.权利要求1所述的半导体结构的形成方法,其特征在于,形成所述第一沟槽的步骤中,所述第一沟槽的延伸方向与所述掩膜材料层第二部分的延伸方向相同,且在与所述掩膜材料层第二部分延伸方向相垂直的方向上,所述第一沟槽位于所述掩膜材料层第一部分和掩膜材料层第二部分的交界处;

去除所述掩膜材料层第二部分之前,还包括:在所述第一沟槽的侧壁上形成侧壁层;

形成所述第二沟槽的步骤中,以所述侧壁层为掩膜,去除所述掩膜材料层第二部分;

形成所述目标图形层的步骤中,以所述侧壁层为掩膜,去除所述第一沟槽和第二沟槽露出的所述待刻蚀材料层。

3. 如权利要求1所述的半导体结构的形成方法,其特征在于,在所述第一掺杂处理后, 所述掩膜材料层第一部分为所述掩膜材料层中经所述第一掺杂处理的部分;

在所述待刻蚀材料层上形成掩膜材料层的步骤中,所述掩膜材料层的材料为无定形硅:

或者,

在所述第一掺杂处理后,所述掩膜材料层第二部分为所述掩膜材料层中经所述第一掺杂处理的部分:

在所述待刻蚀材料层上形成掩膜材料层的步骤中,所述掩膜材料层的材料为氧化硅或氮化硅。

4.权利要求1所述的半导体结构的形成方法,其特征在于,所述掩膜材料层的材料为无定形硅,所述第一掺杂处理的掺杂离子为B离子;

或者,所述掩膜材料层的材料为氧化硅,所述第一掺杂处理的掺杂离子为Ar离子;

或者,所述掩膜材料层的材料为氮化硅,所述第一掺杂处理的掺杂离子为H离子或He离子。

5.如权利要求1所述的半导体结构的形成方法,其特征在于,采用离子注入工艺进行所述第一掺杂处理,所述第一掺杂处理的参数包括:注入能量为1Kev至10Kev,注入剂量为

1E14原子每平方厘米至1E16原子每平方厘米,注入方向与所述基底表面法线的夹角为0度至45度。

- 6.如权利要求1所述的半导体结构的形成方法,其特征在于,采用湿法刻蚀工艺或者灰化工艺,去除所述掩膜材料层第二部分。

- 7.如权利要求1所述的半导体结构的形成方法,其特征在于,在所述第一掺杂处理后, 所述掩膜材料层第一部分为所述掩膜材料层中经所述第一掺杂处理的部分;

形成所述第一沟槽之前,所述形成方法还包括:对部分区域的所述掩膜材料层进行第二掺杂处理,适于增大未经所述第二掺杂处理的掩膜材料层与经所述第二掺杂处理的掩膜材料层之间的去除选择比,其中,经所述第二掺杂处理的掩膜材料层作为掩膜材料层第三部分:

在所述第一掺杂处理和第二掺杂处理之后,所述掩膜材料层第一部分和所述掩膜材料层第三部分相连,且所述掩膜材料层第一部分和所述掩膜材料层第三部分围成的区域所对应的掩膜材料层为所述掩膜材料层第二部分。

- 8. 如权利要求7所述的半导体结构的形成方法,其特征在于,在进行所述第一掺杂处理之前,进行所述第二掺杂处理;或者,在进行所述第二掺杂处理之前,进行所述第一掺杂处理。

- 9.如权利要求7所述的半导体结构的形成方法,其特征在于,所述第二掺杂处理的掺杂离子与所述第一掺杂处理的掺杂离子相同。

- 10.如权利要求7所述的半导体结构的形成方法,其特征在于,所述第二掺杂处理的掺杂离子为B离子。

- 11.如权利要求7所述的半导体结构的形成方法,其特征在于,采用离子注入工艺进行所述第二掺杂处理,所述第二掺杂处理的参数包括:注入能量为1Kev至10Kev,注入剂量为1E14原子每平方厘米至1E16原子每平方厘米,注入方向与所述基底表面法线的夹角为0度至45度。

- 12.如权利要求7所述的半导体结构的形成方法,其特征在于,在进行所述第一掺杂处理之前,进行所述第二掺杂处理:

对部分区域的所述掩膜材料层进行第一掺杂处理的步骤包括:在所述掩膜材料层上形成图形层,所述图形层横跨所述掩膜材料层第三部分,且在所述掩膜材料层第三部分的延伸方向上,所述图形层露出所述掩膜材料层第三部分的边界,或者,靠近所述掩膜材料层第三部分边界一侧的图形层侧壁与所述掩膜材料层第三部分的边界相齐平;对所述图形层露出的掩膜材料层进行所述第一掺杂处理;去除所述图形层。

13.如权利要求1所述的半导体结构的形成方法,其特征在于,在所述第一掺杂处理后, 所述掩膜材料层第一部分为所述掩膜材料层中经所述第一掺杂处理的部分;

对部分区域的所述掩膜材料层进行第一掺杂处理的步骤包括:通过光刻工艺或自对准 双重图形化工艺,在所述掩膜材料层上形成图形层;对所述图形层露出的掩膜材料层进行 所述第一掺杂处理;去除所述图形层。

- 14. 如权利要求1所述的半导体结构的形成方法,其特征在于,采用干法刻蚀工艺刻蚀所述掩膜材料层,在所述掩膜材料层内形成所述第一沟槽。

- 15.如权利要求2所述的半导体结构的形成方法,其特征在于,所述侧壁层的材料为氧

化钛、氮化钛、氧化硅、氮化硅、氮氧化硅或碳化硅。

16.如权利要求2所述的半导体结构的形成方法,其特征在于,形成所述侧壁层的工艺包括原子层沉积工艺。

17. 如权利要求1所述的半导体结构的形成方法,其特征在于,形成所述第一沟槽之后, 形成所述第二沟槽之前,还包括:至少在一个所述第一沟槽中形成保护层,且在所述第一沟槽的延伸方向上,所述保护层两侧露出相对应的所述第一沟槽底部的剩余待刻蚀材料层;

形成所述目标图形层的步骤中,以所述保护层为掩膜,去除所述第一沟槽和第二沟槽 露出的所述待刻蚀材料层。

18. 如权利要求17所述的半导体结构的形成方法,其特征在于,形成所述保护层的步骤包括:在剩余所述掩膜材料层露出的待刻蚀材料层上形成牺牲层,所述牺牲层覆盖剩余所述掩膜材料层的顶部:

在所述第一沟槽部分区域上方的牺牲层内形成通槽,在与所述第一沟槽延伸方向相垂直的方向上,所述通槽至少露出相对应的所述第一沟槽底部的待刻蚀材料层;

形成填充所述通槽的保护层:

形成所述保护层后,去除所述牺牲层。

- 19. 如权利要求17所述的半导体结构的形成方法,其特征在于,所述保护层的材料为LTO或SiOC。

- 20. 如权利要求1所述的半导体结构的形成方法,其特征在于,在所述基底上形成所述 待刻蚀材料层的步骤中,所述待刻蚀材料层包括硬掩膜材料层;

在所述基底上形成所述待刻蚀材料层之前,还包括:在所述基底上形成介质层;

去除剩余所述掩膜材料层之后,还包括:以所述目标图形层为掩膜,图形化所述介质层,在所述介质层内形成互连开口;在所述互连开口内填充导电材料,形成互连结构。

- 21.如权利要求20所述的半导体结构的形成方法,其特征在于,所述互连结构为金属互连线或接触孔插塞。

- 22.一种半导体结构,其特征在于,包括:

基底:

待刻蚀材料层,位于所述基底上:

掩膜材料层,位于所述待刻蚀材料层上,所述掩膜材料层包括掩膜材料层第一部分和 待去除的掩膜材料层第二部分,所述掩膜材料层第一部分中具有掺杂离子,或者,所述掩膜 材料层第二部分中具有掺杂离子;

位于所述掩膜材料层内的沟槽,所述沟槽至少位于所述掩膜材料层第一部分内。

23. 如权利要求22所述的半导体结构,其特征在于,所述沟槽的延伸方向与所述掩膜材料层第二部分的延伸方向相同,且在与所述掩膜材料层第二部分延伸方向相垂直的方向上,所述沟槽位于所述掩膜材料层第一部分和掩膜材料层第二部分的交界处;

所述半导体结构还包括:侧壁层,位于所述沟槽的侧壁上。

24. 如权利要求22所述的半导体结构,其特征在于,所述掩膜材料层第一部分中具有掺杂离子;所述掩膜材料层的材料为无定形硅;

或者,

所述掩膜材料层第二部分中具有掺杂离子;所述掩膜材料层的材料为氧化硅或氮化

硅。

25. 如权利要求22所述的半导体结构,其特征在于,所述掩膜材料层的材料为无定形硅;所述掩膜材料层第一部分中具有掺杂离子,且所述掺杂离子为B离子;

或者,

所述掩膜材料层的材料为氧化硅;所述掩膜材料层第二部分中具有掺杂离子,且所述 掺杂离子为Ar离子;

或者,

所述掩膜材料层的材料为氮化硅,所述掩膜材料层第二部分中具有掺杂离子,且所述掺杂离子为H离子或He离子。

26. 如权利要求22所述的半导体结构,其特征在于,所述掩膜材料层第一部分中具有掺杂离子:

所述掩膜材料层还包括:掩膜材料层第三部分,在与所述掩膜材料层第二部分延伸方向相垂直的方向上,所述掩膜材料层第三部分贯穿所述掩膜材料层第二部分,且所述掩膜材料层第三部分中具有掺杂离子。

- 27. 如权利要求26所述的半导体结构,其特征在于,所述掩膜材料层第三部分和掩膜材料层第一部分中的掺杂离子相同。

- 28. 如权利要求26所述的半导体结构,其特征在于,所述掩膜材料层第三部分中的掺杂离子为B离子。

- 29. 如权利要求22所述的半导体结构,其特征在于,所述半导体结构还包括:保护层,至少位于一个所述沟槽中,且在所述沟槽的延伸方向上,所述保护层两侧露出相对应的所述沟槽底部的剩余待刻蚀材料层。

- 30.如权利要求22所述的半导体结构,其特征在于,所述待刻蚀材料层包括硬掩膜材料层:

所述半导体结构还包括:介质层,位于所述基底和待刻蚀材料层之间。

31.如权利要求30所述的半导体结构,其特征在于,所述介质层为层间介质层或金属层间介质层。

# 半导体结构及其形成方法

#### 技术领域

[0001] 本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

## 背景技术

[0002] 随着半导体集成电路(integrated circuit,IC)产业的快速成长,半导体技术在摩尔定律的驱动下持续地朝更小的工艺节点迈进,使得集成电路朝着体积更小、电路精密度更高、电路复杂度更高的方向发展。

[0003] 在集成电路发展过程中,通常功能密度(即每一芯片的内连线结构的数量)逐渐增加的同时,几何尺寸(即利用工艺步骤可以产生的最小元件尺寸)逐渐减小,这相应增加了集成电路制造的难度和复杂度。

[0004] 目前,在技术节点不断缩小的情况下,如何提高形成于晶圆上的图形与目标图形的匹配度成为了一种挑战。

### 发明内容

[0005] 本发明实施例解决的问题是提供一种半导体结构及其形成方法,提高图形精度。

[0006] 为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基底;在所述基底上形成待刻蚀材料层;在所述待刻蚀材料层上形成掩膜材料层;对部分区域的所述掩膜材料层进行第一掺杂处理,适于增大未经所述第一掺杂处理的掩膜材料层与经所述第一掺杂处理的掩膜材料层之间的去除选择比,其中,在所述第一掺杂处理后,所述掩膜材料层包括掩膜材料层第一部分和待去除的掩膜材料层第二部分,所述掩膜材料层第一部分为所述掩膜材料层中经所述第一掺杂处理的部分,或者,所述掩膜材料层第二部分为所述掩膜材料层中经所述第一掺杂处理的部分;在所述第一掺杂处理之后,在所述掩膜材料层内形成露出部分所述待刻蚀材料层的第一沟槽,所述第一沟槽至少位于所述掩膜材料层第一部分内;形成所述第一沟槽后,去除所述掩膜材料层第二部分,在剩余所述掩膜材料层内形成露出部分所述待刻蚀材料层的第二沟槽;去除所述第一沟槽和第二沟槽露出的所述待刻蚀材料层,形成目标图形层;形成所述目标图形层后,去除剩余所述掩膜材料层。

[0007] 相应的,本发明实施例还提供一种半导体结构,包括:基底;待刻蚀材料层,位于所述基底上;掩膜材料层,位于所述待刻蚀材料层上,所述掩膜材料层包括掩膜材料层第一部分和待去除的掩膜材料层第二部分,所述掩膜材料层第一部分中具有掺杂离子,或者,所述掩膜材料层第二部分中具有掺杂离子;位于所述掩膜材料层内的沟槽,所述沟槽至少位于所述掩膜材料层第一部分内。

[0008] 与现有技术相比,本发明实施例的技术方案具有以下优点:

[0009] 本发明实施例通过第一掺杂处理,将掩膜材料层区分为具有较大去除选择比的掩膜材料层第一部分和掩膜材料层第二部分,在所述第一掺杂处理之后,在所述掩膜材料层内形成第一沟槽,所述第一沟槽至少位于掩膜材料层第一部分内,并在形成所述第一沟槽后,去除所述掩膜材料层第二部分,在剩余所述掩膜材料层内形成第二沟槽;与在同一步骤

中形成第一沟槽和第二沟槽的方案相比,本发明实施例通过分别形成第一沟槽和第二沟槽的方式,一方面,这有利于提高形成所述第一沟槽和第二沟槽的工艺窗口(例如:改善光学邻近效应),使得第一沟槽和第二沟槽的图形精度得到保障,另一方面,所述掩膜材料层第二部分和掩膜材料层第一部分之间具有较大的去除选择比,这进一步提高了形成所述第二沟槽的工艺窗口(例如:可采用无掩膜刻蚀的方式去除所述掩膜材料层第二部分),使得第二沟槽的图形精度得到保障;综上,本发明实施例提高了所述第一沟槽和第二沟槽的图形精度,相应的,去除所述第一沟槽和第二沟槽露出的所述待刻蚀材料层以形成目标图形层后,所述目标图形层中的图形精度相应得到提高。

#### 附图说明

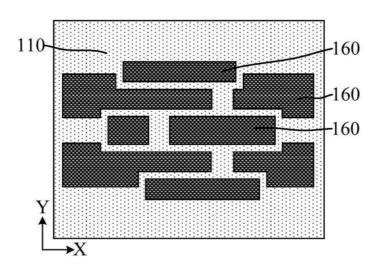

[0010] 图1至图24是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图;

[0011] 图25至图26是本发明半导体结构一实施例的结构示意图。

## 具体实施方式

[0012] 由背景技术可知,在技术节点不断缩小的情况下,如何提高形成于晶圆上的图形与目标图形的匹配度成为了一种挑战。

[0013] 经研究发现,随着技术节点的不断缩小,光刻胶图形的间距也不断减小。然而,在光刻工艺的影响下,当相邻光刻图形的间距小于光刻工艺的临界距离(threshold distance)时,光刻胶图形容易出现变形、失真等问题。当所述光刻胶图形转移至待图形化膜层内以形成目标图形(例如:沟槽)时,相应会降低所述目标图形的图形精度。

[0014] 为了解决所述技术问题,本发明实施例通过第一掺杂处理,将掩膜材料层区分为具有较大去除选择比的掩膜材料层第一部分和掩膜材料层第二部分,在所述第一掺杂处理之后,在所述掩膜材料层内形成第一沟槽,所述第一沟槽至少位于掩膜材料层第一部分内,并在形成所述第一沟槽后,去除所述掩膜材料层第二部分,在剩余所述掩膜材料层内形成第二沟槽;与在同一步骤中形成第一沟槽和第二沟槽的方案相比,本发明实施例通过分别形成第一沟槽和第二沟槽的方式,一方面,这有利于提高形成所述第一沟槽和第二沟槽的工艺窗口,使得第一沟槽和第二沟槽的图形精度得到保障,另一方面,所述掩膜材料层第二部分和掩膜材料层第一部分之间具有较大的去除选择比,这进一步提高了形成所述第二沟槽的工艺窗口,使得第二沟槽的图形精度得到保障;综上,本发明实施例提高了所述第一沟槽和第二沟槽的图形精度,相应的,去除所述第一沟槽和第二沟槽露出的所述待刻蚀材料层以形成目标图形层后,所述目标图形层中的图形精度相应得到提高。

[0015] 为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

[0016] 图1至图24是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意图。

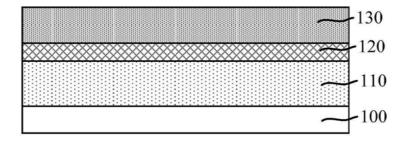

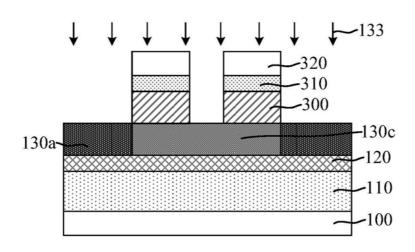

[0017] 参考图1,提供基底100。

[0018] 所述基底100用于为后续制程提供工艺平台。本实施例中,以所形成的半导体结构为平面晶体管为例,所述基底100包括衬底。

[0019] 具体地,所述衬底为硅衬底。在其他实施例中,所述衬底的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟等其他材料,所述衬底还可以为绝缘体上的硅衬底或者绝缘体上的锗衬底等其他类型的衬底。

[0020] 在其他实施例中,当所形成的半导体结构为鳍式场效应晶体管时,所述基底相应可以包括衬底以及凸出于所述衬底的鳍部。

[0021] 所述基底100还可以包括其他结构,例如,栅极结构、掺杂区、浅沟槽隔离结构 (shallow trench isolation,STI)和介电层等。其中,所述栅极结构可以为金属栅结构或 多晶硅栅结构。

[0022] 本实施例中,所述基底100还包括形成于所述衬底上的层间介质层(图未示)以及形成于所述层间介质层中的接触孔插塞(contact,CT)(图未示)。

[0023] 继续参考图1,所述形成方法还包括:在所述基底100上介质层110。

[0024] 所述介质层110用于实现后续所形成互连结构之间的电隔离。

[0025] 本实施例中,所述介质层110为金属层间介质(inter metal dielectric,IMD)层,所述介质层110用于实现后段(back end of line,BEOL)制程中金属互连结构之间的电隔离。

[0026] 具体地,所述介质层110为第一金属层间介质,用于实现第一金属互连线(即M1layer)之间的电隔离。其中,所述第一金属互连线指的是最靠近接触孔插塞的金属互连结构。

[0027] 在其他实施例中,所述介质层还可以为位于第一金属互连线上的其他金属层间介质,用于实现其他互连结构之间的电隔离。例如,所述介质层为第二金属层间介质,用于实现第二金属互连线、以及位于第二金属互连线和第一金属互连线之间的通孔(via)结构之间的电隔离。

[0028] 为此,所述介质层110的材料为低k介质材料(低k介质材料指相对介电常数大于或等于2.6且小于等于3.9的介质材料)、超低k介质材料(超低k介质材料指相对介电常数小于2.6的介质材料)、氧化硅、氮化硅或氮氧化硅等。

[0029] 本实施例中,所述介质层110的材料为超低k介质材料,从而降低后段金属互连结构之间的寄生电容,进而减小后段RC延迟。具体地,所述超低k介质材料可以为SiOCH。

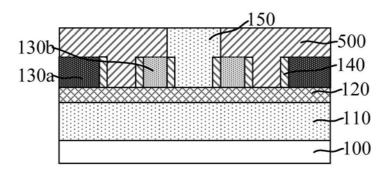

[0030] 继续参考图1,在所述基底100上形成待刻蚀材料层120。

[0031] 所述待刻蚀材料层120经后续的图形化工艺后,其内部形成有贯穿其厚度的目标图形,从而为所述目标图形的转移做好工艺准备。

[0032] 本实施例中,所述待刻蚀材料层120形成于所述介质层110上,所述待刻蚀材料层120为硬掩膜(hard mask,HM)材料层,即所述待刻蚀材料层的材料为硬掩膜材料。后续图形化所述待刻蚀材料层120以形成目标图形层后,所述目标图形层用于作为图形化所述介质层110的掩膜。

[0033] 为此,所述待刻蚀材料层120的材料可以包括氧化硅、氮化硅、氮氧化硅、碳化硅、钛、氧化钛、氮化钛、钽、氧化钽、氮化钽、氮化硼、氮化铜、氮化铝和氮化钨中的一种或多种。

[0034] 本实施例中,所述介质层110为金属层间介质层,因此,所述待刻蚀材料层120为金属硬掩膜(metal hard mask,MHM)材料层。具体地,所述待刻蚀材料层120的材料为氮化钛。氮化钛是后段制程中常用的金属硬掩膜层材料。

[0035] 在其他实施例中,所述待刻蚀材料层还可以为叠层结构,包括底部刻蚀停止材料层、位于所述底部刻蚀停止材料层上的硬掩膜材料层、以及位于所述硬掩膜材料层上的顶部刻蚀停止材料层。其中,所述底部刻蚀停止材料层和顶部刻蚀停止材料层的材料通常为氧化硅,所述底部刻蚀停止材料层用于在图形化所述硬掩膜材料层的过程中,降低所述介质层发生过刻蚀问题的概率;所述顶部刻蚀停止材料层用于对所述硬掩膜材料层起到保护作用,在图形化位于所述硬掩膜材料层上方的膜层时,降低所述硬掩膜材料层发生过刻蚀的概率,通过该顶部刻蚀停止材料层和底部刻蚀停止材料层,有利于提高刻蚀工艺的工艺窗口和轮廓控制。

[0036] 继续参考图1,在所述待刻蚀材料层120上形成掩膜材料层130。

[0037] 后续制程包括图形化所述掩膜材料层130,图形化后的掩膜材料层130用于作为图形化所述待刻蚀材料层120的掩膜。

[0038] 因此,所述掩膜材料层130与所述待刻蚀材料层120之间具有较高的刻蚀选择比,从而在后续刻蚀工艺中实现选择性刻蚀。本实施例中,所述掩膜材料层130与所述待刻蚀材料层120的材料不同。

[0039] 本实施例中,所述掩膜材料层130为无定形硅(a-Si)。无定形硅是后段制程中用于图形化金属硬掩膜材料层的常用掩膜材料。在其他实施例中,根据所述待刻蚀材料层的材料选取,所述掩膜材料层的材料还可以为氧化硅或氮化硅。

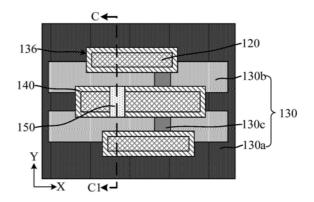

[0040] 结合参考图2至图9,对部分区域的所述掩膜材料层130进行第一掺杂处理133(如图8所示),适于增大未经所述第一掺杂处理133的掩膜材料层130与经所述第一掺杂处理133的掩膜材料层130之间的去除选择比,其中,在所述第一掺杂处理133后,所述掩膜材料层130包括掩膜材料层第一部分130a和待去除的掩膜材料层第二部分130b,所述掩膜材料层第一部分130a为所述掩膜材料层130中经所述第一掺杂处理133的部分。

[0041] 后续制程还包括:在所述掩膜材料层130内形成露出部分所述待刻蚀材料层120的第一沟槽,所述第一沟槽至少位于所述掩膜材料层第一部分130a内,且在形成所述第一沟槽后,去除所述掩膜材料层第二部分130b,在剩余所述掩膜材料层130内形成露出部分所述待刻蚀材料层120的第二沟槽。所述掩膜材料层第二部分130b和掩膜材料层第一部分130a之间具有较大的去除选择比,这显著提高了形成所述第二沟槽的工艺窗口(例如:可采用无掩膜刻蚀的方式去除所述掩膜材料层第二部分130b),使得所形成第二沟槽的图形精度得到保障。

[0042] 其中,未经所述第一掺杂处理133的掩膜材料层130与经所述第一掺杂处理133的掩膜材料层130之间的去除选择比指的是:所述掩膜材料层第二部分130b和掩膜材料层第一部分130a的去除速率的比值。

[0043] 本实施例中,经所述第一掺杂处理133的掩膜材料层130作为掩膜材料层第一部分130a,未经所述第一掺杂处理133的掩膜材料层130作为掩膜材料层第二部分130b。通过所述第一掺杂处理133,向部分区域的掩膜材料层130内掺杂杂质离子,使掩膜材料层第一部分130a和掩膜材料层第二部分130b的材料中的微观结构产生差别。具体地,所述杂质离子使得所述掩膜材料层第一部分130a材料中硅的晶界间隙减小,从而提高所述掩膜材料层第一部分130a的热稳定性和化学稳定性,稳定性的提高相应有利于提高所述掩膜材料层第部分130a的抗腐蚀能力,进而增大这两者之间的去除选择比,使得后续去除掩膜材料层第

二部分130b的工艺对所述掩膜材料层第一部分130a的影响小。

[0044] 本实施例中,在所述第一掺杂处理133后,使得所述掩膜材料层第二部分130b和掩膜材料层第一部分130a之间的去除选择比大于或等于6,从而降低掩膜材料层第一部分130a在后续形成第二沟槽的制程中受到刻蚀损耗的概率。

[0045] 本实施例中,所述掩膜材料层130的材料为无定形硅,因此,所述第一掺杂处理133的掺杂离子为B离子。通过向部分无定形硅中掺杂B离子,使掩膜材料层第一部分130a的材料变为硼掺杂的硅,从而显著提高掩膜材料层第二部分130b和掩膜材料层第一部分130a之间的去除选择比,而且,B原子的稳定性较高,有利于提高掩膜材料层第一部分130a的热稳定性和化学稳定性,此外,B离子是半导体领域中常用的掺杂离子,工艺兼容性较高。

[0046] 本实施例中,采用离子注入工艺进行所述第一掺杂处理133。离子注入工艺较为简单,且通过调整注入剂量,易于对所述掩膜材料层第二部分130b和掩膜材料层第一部分130a之间的去除选择比进行调整。

[0047] 具体地,所述第一掺杂处理133的步骤包括:

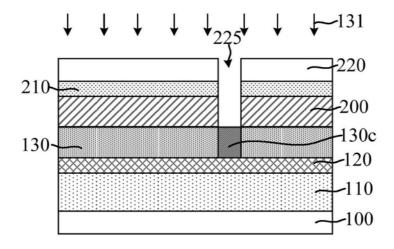

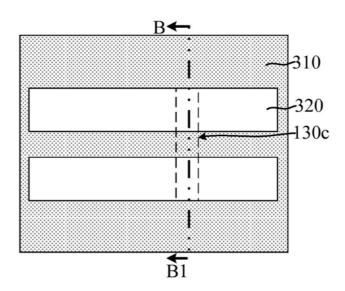

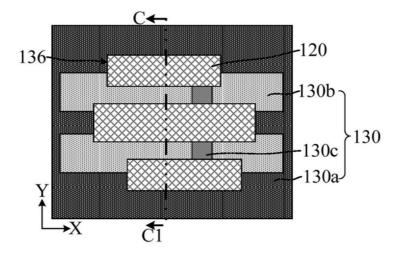

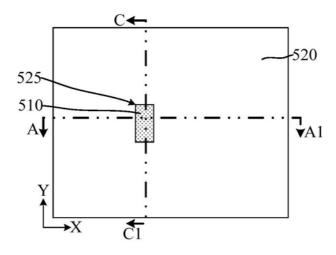

[0048] 结合参考图6和图7,图6是俯视图,图7是图6沿BB1割线的剖视图,在所述掩膜材料层130(如图1所示)上形成第一图形层320。

[0049] 所述第一图形层320遮挡部分区域的掩膜材料层130,防止后续第一掺杂处理的杂质离子掺杂至该区域内。本实施例中,所述第一图形层320的材料为光刻胶。通过光刻工艺形成所述第一图形层320。

[0050] 需要说明的是,在形成所述第一图形层320之前,还包括:在所述掩膜材料层130上形成第一平坦化层300;在所述第一平坦化层300上形成第一抗反射涂层310。所述第一图形层320相应形成于所述第一抗反射涂层310上。

[0051] 所述第一平坦化层300用于为第一图形层320的形成提供平坦表面,从而提高所述第一图形层320的图形精度,使得第一图形层320的形貌、尺寸以及形成位置满足工艺需求。本实施例中,所述第一平坦化层300的材料为旋涂碳(spin on carbon,SOC)材料。在其他实施例中,所述第一平坦化层的材料还可以为0DL(organic dielectric layer,有机介电层)材料或DUO(deep UV light absorbing oxide,深紫外光吸收氧化层)材料。

[0052] 所述第一抗反射涂层310用于减小曝光时的反射效应,从而提高图形的转移精度。本实施例中,所述第一抗反射涂层310为Si-ARC层,Si-ARC层有利于增加光刻工艺过程中的曝光景深(DOF),有利于提高曝光均匀性,而且,Si-ARC层中富含硅,因此还有利于提高所述第一抗反射涂层310的硬度,从而有利于进一步提高图形的转移精度。

[0053] 为此,所述形成方法还包括:以所述第一图形层320为掩膜,依次刻蚀所述第一抗反射涂层310和第一平坦化层300,从而露出待掺杂的掩膜材料层130。

[0054] 在其他实施例中,还可以采用自对准双重图形化(self-aligned double patterning,SADP)工艺形成所述第一图形层。SADP工艺能够在不改变目前光刻技术的前提下(即光刻窗口大小不变),使得所形成图形的密度是利用光刻工艺所形成图形的密度的两倍,即可以获得1/2最小间距(1/2pitch),从而在图形特征尺寸(critical dimension,CD)不断缩小的情况下,使光刻工艺克服光刻分辨率的极限的问题,从而降低形成所述第一图形层的工艺难度、提高所述第一图形层的图形精度。

[0055] 参考图8,采用离子注入工艺,对所述第一图形层320露出的掩膜材料层130(如图7

所示) 进行第一掺杂处理133。

[0056] 在所述第一掺杂处理133后,所述第一图形层320露出的掩膜材料层130中掺杂有杂质离子,用于作为掩膜材料层第一部分130a,未掺杂杂质离子的掩膜材料层130作为掩膜材料层第二部分130b。

[0057] 所述第一掺杂处理133的注入剂量不宜过低,也不宜过高。注入剂量越低,所述掩膜材料层第一部分130a中的杂质离子的掺杂浓度相应越低,所述掩膜材料层第二部分130b和掩膜材料层第一部分130a之间的去除选择比难以满足工艺需求;如果注入剂量过高,所述掩膜材料层第一部分130a中的杂质离子的掺杂浓度相应过高,所述掩膜材料层第一部分130a中的杂质离子容易扩散至掩膜材料层第一部分130a中,从而影响所述掩膜材料层第二部分130b和掩膜材料层第一部分130a之间的去除选择比,相应会影响后续第二沟槽的形貌质量。为此,本实施例中,所述第一掺杂处理133的注入剂量为1E14原子每平方厘米至1E16原子每平方厘米。

[0058] 所述第一掺杂处理133的注入能量不宜过小,也不宜过大。如果注入能量过小,则难以保证整个厚度范围内的掩膜材料层130中均掺杂有该杂质离子,在后续去除掩膜材料层第二部分130b时,所述掩膜材料层第一部分130a所对应区域的掩膜材料层130容易发生损耗;如果注入能量过大,该杂质离子容易被注入至所述掩膜材料层130下方的待刻蚀材料层120中,从而对所述待刻蚀材料层120产生不良影响,相应影响后续制程的正常进行。为此,本实施例中,所述第一掺杂处理133的注入能量为1Kev至10Kev。

[0059] 所述第一掺杂处理133的注入方向与所述基底100表面法线的夹角不宜过大。如果夹角过大,则该杂质离子容易被误掺杂至所述第一图形层320下方的掩膜材料层130中,从而影响后续后续对掩膜材料层第二部分130b的去除效果。为此,本实施例中,所述第一掺杂处理133的注入方向与所述基底100表面法线的夹角为0度至45度。具体地,当所述第一掺杂处理133的掺杂离子为B离子时,所述夹角可以为0度,即注入方向垂直于所述基底100表面。[0060] 结合参考图9,图9是俯视图,在所述第一掺杂处理133后,去除所述第一图形层320

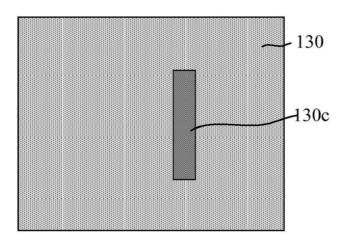

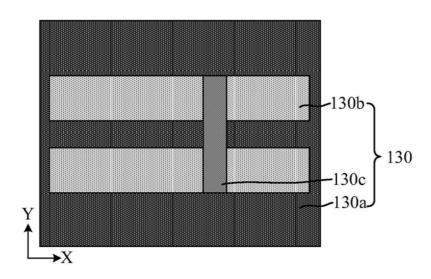

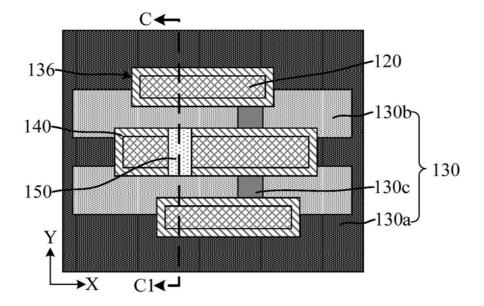

[0060] 结合参考图9,图9是俯视图,在所述第一掺杂处理133后,去除所述第一图形层320(如图8所示)、第一抗反射涂层310(如图8所示)和第一平坦化层300(如图8所示)。

[0061] 需要说明的是,在其他实施例中,以所述第一图形层为掩膜依次刻蚀所述第一抗反射涂层和第一平坦化层的过程中,所述第一图形层会发生损耗,当露出待掺杂的掩膜材料层后,所述第一图形层已被完全消耗,此时,仅需去除所述第一抗反射涂层和第一平坦化层。

[0062] 还需要说明的是,本实施例中,在所述第一掺杂处理133后,所述掩膜材料层第二部分130b的横截面形状为条形,所述掩膜材料层第二部分130b的延伸方向为X方向,与其延伸方向相垂直的方向为Y方向。

[0063] 结合参考图2至图5,在所述第一掺杂处理133(如图8所示)之前,还包括:对部分区域的掩膜材料层130(如图3所示)进行第二掺杂处理131(如图4所示),适于增大未经所述第二掺杂处理131的掩膜材料层130与经所述第二掺杂处理131的掩膜材料层130之间的去除选择比,其中,经所述第二掺杂处理131的掩膜材料层130作为掩膜材料层第三部分130c(如图5所示)。

[0064] 所述掩膜材料层第三部分130c用于作为后续所形成第二沟槽的剪切部件(cut feature)。在后续完成所述第一掺杂处理133后,所述掩膜材料层第三部分130c用于对所述

掩膜材料层第二部分130b(如图9所示)进行分割,从而在后续去除所述掩膜材料层第二部分130b后,在剩余掩膜材料层130内形成多个相隔离的第二沟槽。

[0065] 所述掩膜材料层第三部分130c与未掺杂有离子的剩余掩膜材料层130之间具有较大的刻蚀选择比,因此,在后续去除所述掩膜材料层第二部分130b时,所述掩膜材料层第三部分130c能够被保留,相应提高了形成所述第二沟槽的工艺窗口,使得所形成第二沟槽的图形精度得到保障。其中,未经所述第二掺杂处理131的掩膜材料层130与经所述第二掺杂处理131的掩膜材料层130之间的去除选择比指的是:未经所述第二掺杂处理131的掩膜材料层第三部分130c的去除速率的比值。

[0066] 本实施例中,第二掺杂处理131使得未掺杂杂质离子的剩余掩膜材料层130和掩膜材料层第三部分130c之间的去除选择比大于或等于6,从而降低所述掩膜材料层第三部分130c在后续形成第二沟槽的制程中受到刻蚀损耗的概率。

[0067] 后续制程还包括去除所述掩膜材料层第一部分130a (如图9所示) 和掩膜材料层第三部分130c,因此,在实际制造过程中,通过合理设定第一掺杂处理133和第二掺杂处理131的参数,在保证去除选择比满足工艺需求的同时,使得后续在去除剩余掩膜材料层130的步骤中,掩膜材料层第一部分130a和掩膜材料层第三部分130c的去除选择比可以接近为1(例如:0.8至1.2),从而便于在同一步骤中去除所述掩膜材料层第一部分130a和掩膜材料层第三部分130c,以简化工艺步骤。

[0068] 本实施例中,所述第二掺杂处理131的掺杂离子与第一掺杂处理133的掺杂离子相同,在后续在去除剩余掩膜材料层130的步骤中,有利于减小所述掩膜材料层第一部分130a和掩膜材料层第三部分130c的去除速率的差值,以便于在同一步骤中去除所述掩膜材料层第一部分130a和掩膜材料层第三部分130c。

[0069] 本实施例中,所述第二掺杂处理131的掺杂离子为B离子。

[0070] 本实施例中,采用离子注入工艺进行所述第二掺杂处理131。离子注入工艺较为简单,且可以通过调整注入剂量,对未掺杂杂质离子的剩余掩膜材料层130和掩膜材料层第三部分130c之间的去除选择比进行调整。

[0071] 具体地,所述第二掺杂处理131的步骤包括:

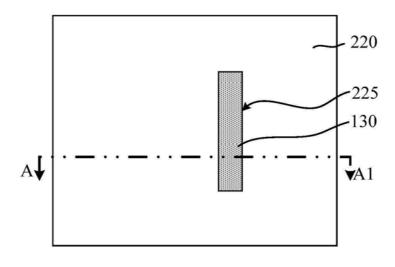

[0072] 结合参考图2和图3,图2是俯视图,图3是图2沿AA1割线的剖视图,在所述掩膜材料层130(如图3所示)上形成第二图形层220。

[0073] 所述第二图形层220内形成有第一图形开口225(如图3所示),所述第一图形开口225露出部分区域的掩膜材料层130,用于定义后续向掩膜材料层130内掺杂杂质离子的区域。本实施例中,所述第二图形层220的材料为光刻胶。

[0074] 因此,如图3所示,在形成所述第二图形层220之前,还包括:在所述掩膜材料层130上形成第二平坦化层200;在所述第二平坦化层200上形成第二抗反射涂层210。所述第二图形层220相应形成于所述第二抗反射涂层210上。

[0075] 本实施例中,所述第二平坦化层200的材料为旋涂碳,所述第二抗反射涂层210为Si-ARC层。对所述第二平坦化层200和第二抗反射涂层210的具体描述,可分别参考前述对所述第一平坦化层300(如图8所示)和第一抗反射涂层310(如图8所示)的具体描述,在此不再赘述。

[0076] 为此,所述形成方法还包括:以所述第二图形层220为掩膜,依次刻蚀所述第二抗

反射涂层210和第二平坦化层200,从而露出待掺杂的掩膜材料层130。

[0077] 参考图4,采用离子注入工艺,对所述第一图形开口225露出的掩膜材料层130进行第二掺杂处理131。

[0078] 在所述第二掺杂处理131后,所述第一图形开口225露出的掩膜材料层130作为掩膜材料层第三部分130c。

[0079] 本实施例中,综合考虑所述掩膜材料层第三部分130c和后续掩膜材料层第二部分130b之间的去除选择比、以及所述掩膜材料层第三部分130c和后续掩膜材料层第一部分130a之间的去除选择比,并防止杂质离子向不期望掺杂的区域扩散,所述第二掺杂处理131的注入剂量为1E14原子每平方厘米至1E16原子每平方厘米。对注入剂量的分析可参考前述对第二掺杂处理133的相应描述,在此不再赘述。

[0080] 本实施例中,为了保证待掺杂区域的整个厚度内的掩膜材料层130中均掺杂有该杂质离子,并降低该杂质离子被注入至所述待刻蚀材料层120中的概率,所述第二掺杂处理131的注入能量为1Kev至10Kev。对注入能量的分析可参考前述对第二掺杂处理133的相应描述,在此不再赘述。

[0081] 所述第一图形开口225的开口尺寸通常较小,如果夹角过大,则容易受到遮蔽效应 (shadow effect)的影响,从而降低掺杂效果。为此,本实施例中,所述第二掺杂处理131的 注入方向与基底100表面法线的夹角为0度至45度。具体地,所述夹角可以为0度,即注入方向垂直于所述基底100表面。对夹角的分析可参考前述对第二掺杂处理133的相应描述,在此不再赘述。

[0082] 对所述第二掺杂处理131的具体描述,可参考前述对第一掺杂处理133(如图8所示)

[0083] 结合参考图5,图5是俯视图,在所述第二掺杂处理131(如图4所示)后,去除所述第二图形层220(如图4所示)、第二抗反射涂层210(如图4所示)和第二平坦化层200(如图4所示)。

[0084] 为此,继续参考图9,本实施例中,在进行所述第一掺杂处理133之后,所述掩膜材料层第一部分130a和掩膜材料层第三部分130c相连,且所述掩膜材料层第一部分130a和掩膜材料层第三部分130c围成的区域所对应的掩膜材料层130为所述掩膜材料层第二部分130b,也就是说,所述掩膜材料层第三部分130c贯穿所述掩膜材料层第二部分130b。

[0085] 为此,通过所述第一掺杂处理133和所述第二掺杂处理131,从而获得多个相隔离的掩膜材料层第二部分130b,进而为后续形成多个相隔离的第二沟槽提供工艺基础。

[0086] 相应的,继续参考图6,形成所述第一图形层320的步骤中,所述第一图形层320横跨所述掩膜材料层第三部分130c,且在所述掩膜材料层第三部分130c的延伸方向上,靠近所述掩膜材料层第三部分130c边界一侧的第一图形层320侧壁与所述掩膜材料层第三部分130c的边界相齐平。

[0087] 由于所述掩膜材料层第三部分130c中已掺杂有杂质离子,因此,沿所述第一图形层320的延伸方向上,所述第一图形层320无需露出所述掩膜材料层第三部分130c所对应区域的掩膜材料层130,这相应降低了形成所述第一图形层320的工艺难度、提高了形成所述第一图形层320的工艺窗口,有利于提高所述第一图形层320的图形精度。

[0088] 本实施例中,在所述掩膜材料层第三部分130c的延伸方向上,靠近所述掩膜材料

层第三部分130c边界一侧的第一图形层320侧壁与所述掩膜材料层第三部分130c的边界相齐平,从而保证所述掩膜材料层第三部分130c能够与所述掩膜材料层第一部分130a相连,进而实现所述掩膜材料层第三部分130c对掩膜材料层第二部分130b的隔离。

[0089] 其中,所述第一图形层320露出部分掩膜材料层第三部分130c,但由于所述第一掺杂处理133用于增大未经所述第一掺杂处理133的掩膜材料层130与经所述第一掺杂处理133的掩膜材料层130之间的去除选择比,因此,即使所述第一掺杂处理133对部分掩膜材料层第三部分130c中掺杂了杂质离子,在后续去除掩膜材料层第二部分130b的步骤中,所述掩膜材料层第三部分130c仍能够被保留。

[0090] 在另一些实施例中,所述第一图形层也可以露出所述掩膜材料层第三部分的边界,即所述掩膜材料层第三部分和所述掩膜材料层第一部分具有重叠部分,这仍能实现所述掩膜材料层第三部分对掩膜材料层第二部分的隔离,且在后续去除掩膜材料层第二部分130b的步骤中,所述掩膜材料层第三部分130c仍能够被保留。

[0091] 需要说明的是,在其他实施例中,也可以先进行所述第一掺杂处理,再进行所述第二掺杂处理。

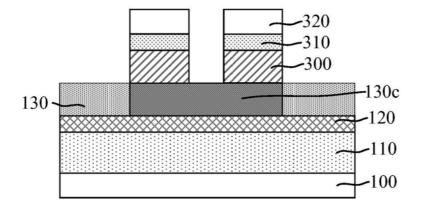

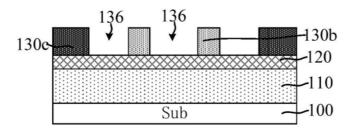

[0092] 结合参考图10至图13,在所述第一掺杂处理133(如图8所示)之后,在所述掩膜材料层130(如图12所示)内形成露出部分所述待刻蚀材料层120的第一沟槽136(如图12所示),所述第一沟槽136至少位于所述掩膜材料层第一部分130a内。

[0093] 所述第一沟槽136用于定义所述待刻蚀材料层120中的部分待去除区域。

[0094] 后续制程还会去除所述掩膜材料层第二部分130b,在剩余所述掩膜材料层130内形成露出部分待刻蚀材料层120的第二沟槽,与在同一步骤中形成第一沟槽和第二沟槽的方案相比,本实施例通过分别形成第一沟槽136和第二沟槽的方式,有利于提高形成所述第一沟槽136和第二沟槽的工艺窗口(例如:改善光学邻近效应),使得第一沟槽136和第二沟槽的图形精度得到保障。

[0095] 其中,在形成所述第一沟槽136之前,还未对所述掩膜材料层130进行图形化,从而为所述第一沟槽136的形成提供了平坦面,相应降低了形成所述第一沟槽136的工艺复杂度。

[0096] 具体地,形成所述第一沟槽136的步骤包括:

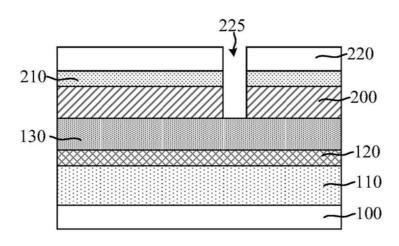

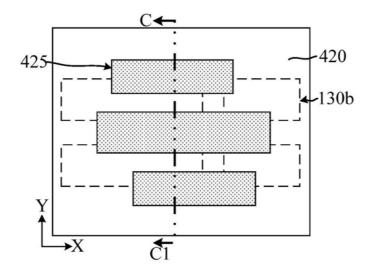

[0097] 结合参考图10至图11,图10是俯视图,图11是图10沿CC1割线的剖视图,在所述掩膜材料层130上形成第三图形层420。

[0098] 所述第三图形层420内形成有第二图形开口425,所述第二图形开口425露出部分区域的掩膜材料层130,所述第二图形开口425用于定义后续第一沟槽的形成区域。本实施例中,所述第三图形层420的材料为光刻胶。

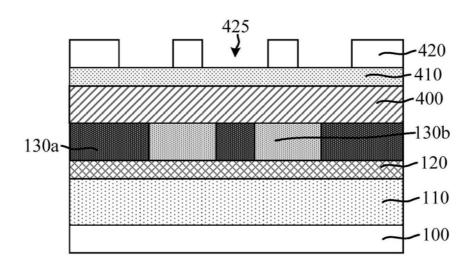

[0099] 因此,如图11所示,在形成所述第三图形层420之前,还包括:在所述掩膜材料层130上形成第三平坦化层400;在所述第三平坦化层400上形成第三抗反射涂层410。所述第三图形层420相应形成于所述第三抗反射涂层410上。

[0100] 本实施例中,所述第三平坦化层400的材料为旋涂碳,所述第三抗反射涂层410为Si-ARC层。对所述第三平坦化层400和第三抗反射涂层410的具体描述,可分别参考前述对所述第一平坦化层300(如图7所示)和第一抗反射涂层310(如图7所示)的具体描述,在此不再赘述。

[0101] 相应的,所述形成方法还包括:以所述第三图形层420为掩膜,依次刻蚀第三抗反射涂层410和第三平坦化层400,从而露出待刻蚀的掩膜材料层130。

[0102] 其中,所述掩膜材料层130具有平坦面,因此,降低了所述第三图形层420、第三抗反射涂层410和第三平坦化层400的形成工艺以及图形化工艺的复杂度。

[0103] 本实施例中,第二图形开口425横跨掩膜材料层第三部分130c,同一个第二图形开口425不仅露出所述掩膜材料层第二部分130b一侧的掩膜材料层第一部分130,还露出部分掩膜材料层第三部分130c以及位于所述掩膜材料层第三部分130c两侧的部分掩膜材料层第二部分130b,从而减小后续相邻第一沟槽和第二沟槽的间距,并满足集成电路的设计复杂度要求。

[0104] 在其他实施例中,根据集成电路的设计要求,同一个第二图形开口可以仅露出掩膜材料层第二部分一侧的掩膜材料层第一部分,或者,当掩膜材料层第三部分和掩膜材料层第一部分具有重叠部分时,同一个第二图形开口也可以仅露出掩膜材料层第二部分一侧的掩膜材料层第一部分和掩膜材料层第三部分。

[0105] 结合参考图12至图13,图12是俯视图,图13是图12沿CC1割线的剖视图,刻蚀所述第二图形开口425(如图11所示)露出的掩膜材料层130,在所述掩膜材料层130内形成第一沟槽136。

[0106] 本实施例中,采用干法刻蚀工艺刻蚀所述第二图形开口425露出的掩膜材料层130。干法刻蚀工艺具有各向异性刻蚀的特性,有利于提高所述第一沟槽136的形貌质量;而且,通过选用干法刻蚀工艺,易于控制刻蚀停止位置,以降低对所述待刻蚀材料层120的损伤;此外,通过合理调节所述干法刻蚀工艺的参数,易于在同一刻蚀步骤中刻蚀所述掩膜材料层第一部分130a、掩膜材料层第二部分130b和掩膜材料层第三部分130c。

[0107] 本实施例中,形成第一沟槽136后,第一沟槽136的延伸方向与掩膜材料层第二部分130b的延伸方向(如图12中X方向所示)相同,且在与掩膜材料层第二部分130b延伸方向相垂直的方向上(如图12中Y方向所示),第一沟槽136位于掩膜材料层第一部分130a和掩膜材料层第二部分130b的交界处。

[0108] 具体地,所述第一沟槽136还贯穿所述掩膜材料层第三部分130c。

[0109] 本实施例中,形成第一沟槽136后,去除所述第三图形层420(如图11所示)、第三抗反射涂层410(如图11所示)和第三平坦化层400(如图11所示)。

[0110] 结合参考图14至图15,图14是俯视图,图15是图14沿CC1割线的剖视图,所述形成方法还包括:在所述第一沟槽136的侧壁上形成侧壁层140。

[0111] 后续去除剩余掩膜材料层第二部分130b后,在剩余掩膜材料层130内形成第二沟槽,通过所述侧壁层140,以实现所述第二沟槽与第一沟槽136的隔离,防止所述第二沟槽与第一沟槽136出现贯通的问题,而且,使得相邻第二沟槽与第一沟槽136的间距满足设计最小间隔(designed minimum space)。

[0112] 为此,所述侧壁层140和掩膜材料层第二部分130b之间具有较高的去除选择比,使得侧壁层140能够作为后续去除剩余掩膜材料层第二部分130b时的掩膜。本实施例中,所述侧壁层140和掩膜材料层第二部分130b的材料不同,所述侧壁层140的材料为氧化钛。氧化钛与无定形硅以及氮化钛之间的去除选择比较高。在其他实施例中,根据所述待刻蚀材料层和掩膜材料层的材料设定,所述侧壁层的材料还可以为氮化钛、氧化硅、氮化硅、氮氧化

硅或碳化硅。

[0113] 具体地,形成所述侧壁层140的步骤包括:形成侧壁材料层,所述侧壁材料层保形覆盖所述第一沟槽136的侧壁和底部,且还覆盖所述掩膜材料层130的顶部;去除所述第一沟槽136底部和掩膜材料层130顶部的侧壁材料层,保留所述第一沟槽136侧壁的侧壁材料层作为所述侧壁层140。

[0114] 通过选用保形覆盖的方式形成侧壁材料层,从而能够通过无掩膜刻蚀的方式刻蚀该侧壁材料层,降低了工艺复杂度和成本。本实施例中,选用原子层沉积工艺形成所述侧壁材料层。原子层沉积工艺具有良好的台阶覆盖能力,且能够形成厚度均一性较好的膜层材料,有利于提高所述侧壁层140的形成质量以及厚度均一性。

[0115] 在其他实施例中,当所述第一沟槽仅形成于所述掩膜材料层第二部分一侧的掩膜材料层第一部分内时,或者,仅形成于所述掩膜材料层第二部分一侧的掩膜材料层第一部分内和掩膜材料层第三部分内时,也可以不形成所述侧壁层。

[0116] 结合参考图16至图21,形成所述侧壁层140后,还包括:至少在一个第一沟槽136 (如图21所示)中形成保护层150 (如图21所示),且在所述第一沟槽136的延伸方向上(如图21中X方向所示),所述保护层150两侧露出相对应的所述第一沟槽136底部的剩余待刻蚀材料层130。

[0117] 所述保护层150用于作为所述第一沟槽136的剪切部件。在所述第一沟槽136的延伸方向上,所述保护层150覆盖部分区域的待刻蚀材料层120,从而使得所述保护层150下方的待刻蚀材料层120在后续刻蚀工艺中被保留;相应的,将所述第一沟槽136的图形传递至待刻蚀材料层120中时,能够在所述待刻蚀材料层120中形成相隔离的图形。与通过光刻制程将所述第一沟槽136在其延伸方向上进行分割的方案相比,本实施例有利于提高形成所述第一沟槽136的工艺窗口,从而提高图形传递的精度。

[0118] 具体地,形成所述保护层150的步骤包括:

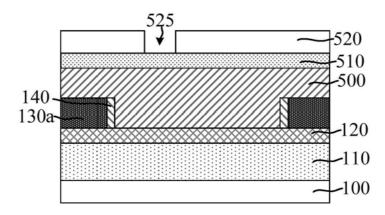

[0119] 结合参考图16至图18,图16是俯视图,图17是图16沿AA1割线的剖视图,图18是图16沿CC1割线的剖视图,在剩余掩膜材料层130露出的待刻蚀材料层120上形成牺牲层500,牺牲层500还覆盖剩余掩膜材料层130顶部。

[0120] 所述牺牲层500用于为后续形成保护层提供工艺平台。

[0121] 后续形成所述保护层后,还需去除所述牺牲层500,因此,所述牺牲层500的材料为 易于去除的材料。本实施例中,所述牺牲层500为S0C材料。

[0122] 图形化所述牺牲层500的制程通常包括光刻胶层的形成,通过选用SOC材料,还有利于提高光刻胶层的图形精度,从而提高后续形成于该牺牲层500中的通槽的图形精度。对所述牺牲层500的具体描述,可参考前述对所述第一平坦化层300(如图7所示)的具体描述,在此不再赘述

[0123] 在其他实施例中,所述牺牲层的材料还可以为0DL材料或BARC(Bottom Anti-Reflective Coating,底部抗反射涂层)材料。

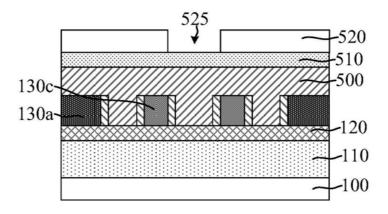

[0124] 继续参考图16至图18,并结合参考图19,图19是基于图18的剖视图,在第一沟槽136(如图14所示)部分区域上方的牺牲层500内形成通槽550(如图19所示),在与第一沟槽136延伸方向相垂直的方向上(如图16中Y方向所示),所述通槽550至少露出相对应的第一沟槽136底部的待刻蚀材料层120。

[0125] 具体地,在所述牺牲层500上形成第四抗反射涂层510;在所述第四抗反射涂层510上形成第四图形层520,所述第四图形层520内形成有第三图形开口525,用于定义所述牺牲层500中待刻蚀的区域;沿所述第三图形开口525,依次刻蚀第四抗反射涂层510和牺牲层500,在所述牺牲层500内形成所述通槽550。

[0126] 本实施例中,所述第四抗反射涂层510为Si-ARC层,所述第四图形层520的材料为光刻胶。

[0127] 本实施例中,形成所述通槽550后,在与所述第一沟槽136延伸方向相垂直的方向上,所述通槽550还露出所述侧壁层140,这相应增大了所述第三图形开口525的开口尺寸,从而增大了形成所述第三图形开口525的工艺窗口,例如,缓解光刻工艺解析度的限制。在其他实施例中,所述通槽也可以仅露出所述侧壁层之间的待刻蚀材料层。

[0128] 如图19所示,本实施例中,形成所述通槽550后,去除所述第四图形层520(如图18 所示)和第四抗反射涂层510(如图18所示)。

[0129] 需要说明的是,在其他实施例中,沿所述第三图形开口依次刻蚀第四抗反射涂层和牺牲层后,所述第四图形层和第四抗反射涂层也可以完全被消耗。相应无需采用额外的步骤以去除所述第四图形层和第四抗反射涂层。

[0130] 结合参考图20,图20是基于图19的剖视图,形成填充所述通槽550的保护层150。

[0131] 具体地,向所述通槽550内填充保护材料层,所述保护材料层还覆盖所述牺牲层500顶部;通过回刻(etch back)的方式,去除高于所述牺牲层500顶部的保护材料层,保留所述通槽550内的保护材料层作为所述保护层150。

[0132] 本实施例中,所述保护层150的材料为LT0(low temperature oxide,低温氧化物)。该材料的填充性较好,有利于提高保护层150在通槽550内的填充质量,而且,该材料为易于被去除的材料,降低了后续去除所述保护层150的工艺难度。具体地,选用低压化学气相淀积(LPCVD)工艺形成所述保护层150.

[0133] 在另一些实施例中,所述保护层的材料还可以为SiOC。在其他实施例中,所述保护层的材料还可以为采用流动性化学气相沉积 (FCVD) 工艺形成的氧化硅或者其他可采用ALD工艺形成的适宜材料。

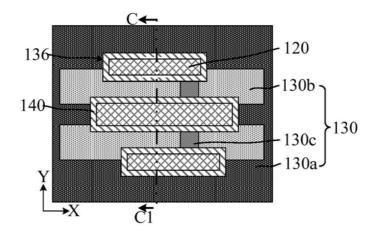

[0134] 参考图21,图21是俯视图,形成所述保护层150后,去除所述牺牲层500(如图20所示)。

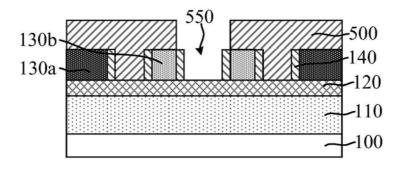

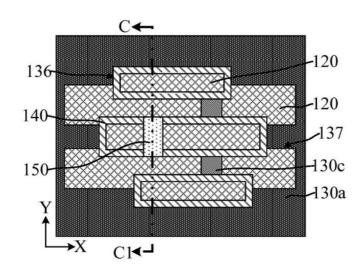

[0135] 参考图22,图22是基于图21的俯视图,去除所述掩膜材料层第二部分130b(如图21 所示),在剩余所述掩膜材料层130内形成露出部分待刻蚀材料层120的第二沟槽137。

[0136] 所述第二沟槽137用于定义后续待刻蚀材料层120中剩余待去除的区域。

[0137] 所述掩膜材料层第二部分130b和掩膜材料层第一部分130a之间具有较大的去除选择比,所述掩膜材料层第二部分130b和掩膜材料层第三部分130c之间也具有较大的去除选择比,这显著提高了形成所述第二沟槽137的工艺窗口,使得所形成第二沟槽137的图形精度得到保障;而且,与在同一步骤中形成所述第一沟槽和第二沟槽的方案相比,通过在另一步骤中形成所述第一沟槽136,提高了光刻工艺的工艺窗口,例如,缓解光刻工艺解析度的限制,从而使得所述第一沟槽136和第二沟槽137的图形精度均能得到提高,相应的,后续去除所述第一沟槽136和第二沟槽137露出的待刻蚀材料层120以形成目标图形层后,所述目标图形层中的图形精度相应得到了提高。

[0138] 本实施例中,所述第一沟槽136的侧壁上形成有侧壁层140,因此,以所述侧壁层140为掩膜,去除所述掩膜材料层第二部分130b,从而实现所述第二沟槽137和第一沟槽136的隔离。

[0139] 本实施例中,采用湿法刻蚀工艺,去除所述掩膜材料层第二部分130b。湿法刻蚀工艺是通过化学反应的方式,去除所述掩膜材料层第二部分130b,有利于减小所述第一沟槽136露出的待刻蚀材料层120受到的损伤。

[0140] 在其他实施例中,也可以选用灰化工艺,去除所述掩膜材料层第二部分。

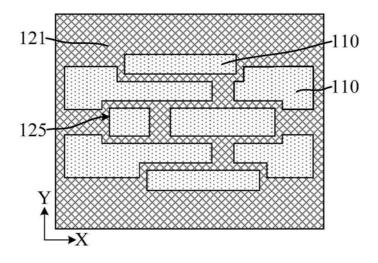

[0141] 参考图23,图23是基于图22的俯视图,去除所述第一沟槽136(如图22所示)和第二 沟槽137(如图22所示)露出的所述待刻蚀材料层120(如图22所示),剩余待刻蚀材料层120 用于作为目标图形层121。

[0142] 本实施例中,待刻蚀材料层120为硬掩膜材料层,相应的,所述目标图形层121为硬掩膜层,所述硬掩膜层用于作为后续图形化所述介质层110的掩膜。

[0143] 在去除所述第一沟槽136和第二沟槽137露出的待刻蚀材料层120后,所述第一沟槽136和第二沟槽137的图形传递至所述目标图形层121中,在所述目标图形层121中形成多个掩膜开口125。其中,所述第一沟槽136和第二沟槽137的图形精度较高,相应提高了所述掩膜开口125的图形精度。

[0144] 本实施例中,所述第一沟槽136的侧壁上形成有侧壁层140,且至少一个第一沟槽136中形成有保护层150,因此,形成所述目标图形层121的步骤中,以所述侧壁层140和保护层150为掩膜,去除所述第一沟槽136和第二沟槽137露出的所述待刻蚀材料层120。

[0145] 本实施例中,形成所述目标图形层121后,还包括:去除所述侧壁层140、保护层150和剩余所述掩膜材料层130。

[0146] 具体地,采用干法刻蚀工艺,去除所述侧壁层140、保护层150和剩余所述掩膜材料层130。其中,通过调整所述干法刻蚀工艺的参数,从而能够在同一刻蚀机台中去除所述侧壁层140、保护层150和剩余所述掩膜材料层130。

[0147] 结合图24,图24是基于图23的俯视图,所述形成方法还包括:以所述目标图形层121(如图23所示)为掩膜,图形化所述介质层110,在所述介质层内110形成互连开口(图未示);在所述互连开口内填充导电材料,形成互连结构160。

[0148] 所述掩膜开口125 (如图23所示) 的图形精度较高,从而提高了所述互连开口的图形精度,使得所述互连结构160的形貌和布局满足设计需求,相应提高了所述互连结构160的性能。

[0149] 本实施例中,所述互连结构160为后段制程中的金属互连线。

[0150] 其中,形成所述互连结构160的制程通常包括平坦化处理,所述目标图形层121在 所述平坦化处理的过程中被去除。

[0151] 随着电路集成度的增加,后段金属布线的设计复杂度越来越高,相邻金属互连线的间距也越来越小,通过前述形成所述第一沟槽136和第二沟槽137的方式,显著提高了所述金属互连线的形成质量以及性能,从而提高半导体结构的性能和可靠性。例如,所述金属互连线为第一金属(M1)互连线。

[0152] 在另一些实施例中,当所述介质层还可以为层间介质层时,所述互连结构相应为接触孔插塞。

[0153] 需要说明的是,在其他实施例中,在上述形成方法中,还可以为:在所述第一掺杂处理后,所述掩膜材料层第二部分为所述掩膜材料层中经所述第一掺杂处理的部分。

[0154] 在该实施例中,在第一掺杂处理的过程中,杂质离子破坏所述掩膜材料层第二部分的晶格,降低其材料致密度,从而使所述掩膜材料层第二部分易于被去除,相应也能提高掩膜材料层第二部分和掩膜材料层第一部分之间的去除选择比。

[0155] 为此,在该实施例中,在所述待刻蚀材料层上形成掩膜材料层的步骤中,所述掩膜材料层的材料为氧化硅或氮化硅。

[0156] 其中,当所述掩膜材料层的材料为氧化硅时,前述第一掺杂处理的掺杂离子为Ar离子;当所述掩膜材料层的材料为氮化硅时,前述第一掺杂处理的掺杂离子为H离子或He离子。

[0157] 需要说明的是,在这种情况下,相应无需进行前述的第二掺杂处理,在进行前述第一掺杂处理的步骤中,使图形层(例如:光刻胶层)仅露出待去除的掩膜材料层第二部分所对应区域的掩膜材料层即可。

[0158] 对该实施例的具体描述,可参考前述实施例中的相应描述,在此不再赘述。

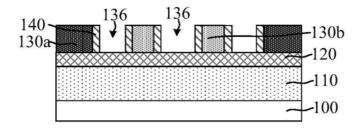

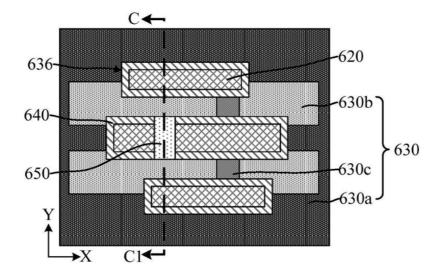

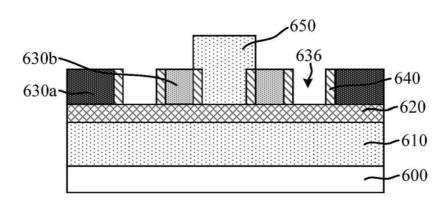

[0159] 相应的,本发明实施例还提供一种半导体结构。参考图25至图26,示出了本发明半导体结构一实施例的结构示意图,图25是俯视图,图26是图25沿CC1割线的剖视图。

[0160] 所述半导体结构包括:基底600;待刻蚀材料层620,位于所述基底600上;掩膜材料层630(如图25所示),位于所述待刻蚀材料层620上,所述掩膜材料层630包括掩膜材料层第一部分630a和待去除的掩膜材料层第二部分630b,所述掩膜材料层第一部分630a中具有掺杂离子,或者,所述掩膜材料层第二部分630b中具有掺杂离子;位于所述掩膜材料层630内的沟槽636,所述沟槽636至少位于所述掩膜材料层第一部分630a内。

[0161] 本实施例中,以所述半导体结构为平面晶体管为例,所述基底600包括衬底。具体地,所述衬底为硅衬底。在其他实施例中,所述衬底的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟等其他材料,所述衬底还可以为绝缘体上的硅衬底或者绝缘体上的锗衬底等其他类型的衬底。

[0162] 在其他实施例中,当所述半导体结构为鳍式场效应晶体管时,所述基底相应可以包括衬底以及凸出于所述衬底的鳍部。

[0163] 所述基底600还可以包括其他结构,例如,栅极结构、掺杂区、浅沟槽隔离结构和介电层等。本实施例中,所述基底600还包括位于所述衬底上的层间介质层(图未示)以及形成于所述层间介质层中的接触孔插塞(图未示)。

[0164] 本实施例中,所述半导体结构还包括:位于所述基底610上的介质层610。

[0165] 所述介质层610用于实现互连结构之间的电隔离。本实施例中,所述介质层610为金属层间介质层,用于实现后段制程中金属互连结构之间的电隔离。

[0166] 具体地,所述介质层610为第一金属层间介质,用于实现第一金属互连线之间的电隔离。其中,所述第一金属互连线指的是最靠近接触孔插塞的金属互连结构。在其他实施例中,所述介质层还可以为位于第一金属互连线上的金属层间介质,用于实现其他互连结构之间的电隔离。例如,所述介质层为第二金属层间介质,用于实现第二金属互连线、以及位于第二金属互连线和第一金属互连线之间的通孔结构之间的电隔离。

[0167] 为此,所述介质层610的材料为低k介质材料、超低k介质材料、氧化硅、氮化硅或氮

氧化硅等。本实施例中,所述介质层610的材料为超低k介质材料。具体地,所述超低k介质材料可以为SiOCH。

[0168] 在其他实施例中,所述介质层还可以为层间介质层,用于实现接触孔插塞之间的电隔离。

[0169] 所述待刻蚀材料层620经图形化工艺后,会在其内部形成贯穿其厚度的目标图形。本实施例中,所述待刻蚀材料层630位于所述介质层610上,所述待刻蚀材料层620为硬掩膜材料层,即所述待刻蚀材料层的材料为硬掩膜材料。图形化所述待刻蚀材料层620以形成目标图形层后,所述目标图形层用于作为图形化所述介质层610的掩膜。

[0170] 为此,所述待刻蚀材料层620的材料可以包括氧化硅、氮化硅、氮氧化硅、碳化硅、钛、氧化钛、氮化钛、钽、氧化钽、氮化钽、氮化硼、氮化铜和氮化铝和氮化钨中的一种或多种。

[0171] 本实施例中,所述介质层610为金属层间介质层,因此,所述待刻蚀材料层620的材料为氮化钛。在其他实施例中,所述待刻蚀材料层还可以为叠层结构,包括底部刻蚀停止材料层、位于所述底部刻蚀停止材料层上的硬掩膜材料层、以及位于所述硬掩膜材料层上的顶部刻蚀停止材料层。其中,所述底部刻蚀停止材料层和顶部刻蚀停止材料层的材料通常为氧化硅。

[0172] 实现图形化的掩膜材料层630用于作为图形化待刻蚀材料层620的掩膜。

[0173] 因此,所述掩膜材料层630与所述待刻蚀材料层620之间具有较高的刻蚀选择比,从而在后续刻蚀工艺中实现选择性刻蚀。本实施例中,所述掩膜材料层630与所述待刻蚀材料层620的材料不同。

[0174] 本实施例中,所述掩膜材料层630为无定形硅。无定形硅是后段制程中用于图形化 金属硬掩膜材料层的常用掩膜材料。在其他实施例中,根据所述待刻蚀材料层的材料设定,所述掩膜材料层的材料还可以为氧化硅或氮化硅。

[0175] 本实施例中,所述掩膜材料层630内形成有沟槽,所述沟槽至少位于所述掩膜材料层第一部分630a内。具体地,定义所述沟槽为第一沟槽636,所述第一沟槽630用于定义所述特刻蚀材料层620中待刻蚀的部分区域。在后续制程中,通过去除所述掩膜材料层第二部分630b,即可在所述掩膜材料层630内形成露出部分所述待刻蚀材料层620的第二沟槽,所述第二沟槽用于定义所述待刻蚀材料层620中待刻蚀的剩余区域。

[0176] 本实施例中,所述掩膜材料层第一部分630a中掺杂有离子,使得所述掩膜材料层第一部分630a材料的晶界间隙减小,从而提高所述掩膜材料层第一部分630a的热稳定性和化学稳定性,稳定性的提高相应有利于提高所述掩膜材料层第一部分630a的抗腐蚀能力,这使得所述掩膜材料层第二部分630b和掩膜材料层第一部分630a之间具有较大的去除选择比,从而显著提高了形成所述第二沟槽的工艺窗口(例如:可采用无掩膜刻蚀的方式去除所述掩膜材料层第二部分630b),进而使得所形成第二沟槽的图形精度得到保障。

[0177] 而且,所述第一沟槽636和第二沟槽在不同步骤中形成,与在同一步骤中形成所述第一沟槽和第二沟槽的方案相比,本实施例提高了光刻工艺的工艺窗口,例如,缓解光刻工艺解析度的限制,从而使得所述第一沟槽636和第二沟槽的图形精度均能得到提高,相应的,后续去除所述第一沟槽636和第二沟槽露出的待刻蚀材料层620以形成目标图形层后,所述目标图形层中的图形精度相应得到了提高。

[0178] 本实施例中,所述掩膜材料层630的材料为无定形硅,因此,所述掩膜材料层第一部分630a中的掺杂离子为B离子。相应的,所述掩膜材料层第一部分630a的材料变为硼掺杂的硅,从而显著提高掩膜材料层第二部分630b和掩膜材料层第一部分630a之间的去除选择比,而且,B原子的稳定性较高,有利于提高掩膜材料层第一部分630a的热稳定性和化学稳定性,此外,B离子是半导体领域中常用的掺杂离子,工艺兼容性较高。

[0179] 本实施例中,通过合理设定所述掩膜材料层第一部分630a中的掺杂离子浓度,使 所述掩膜材料层第二部分630b和掩膜材料层第一部分630a之间的去除选择比满足工艺需 求,并防止所述掩膜材料层第一部分630a中的杂质离子向掩膜材料层第一部分630a中扩 散,以保证后续第二沟槽的形貌质量。

[0180] 需要说明的是,本实施例中,所述第一沟槽636的延伸方向(如图25中X方向所示)与所述掩膜材料层第二部分630b的延伸方向相同,且在与所述掩膜材料层第二部分630b延伸方向相垂直的方向上(如图25中Y方向所示),所述第一沟槽636位于掩膜材料层第一部分630a和掩膜材料层第二部分630b的交界处。

[0181] 通过使第一沟槽636位于掩膜材料层第一部分630a和掩膜材料层第二部分630b的 交界处,从而减小后续相邻第一沟槽636和第二沟槽的间距,并满足集成电路的设计复杂度 要求。在其他实施例中,根据集成电路的设计要求,所述第一沟槽也可以位于所述掩膜材料层第二部分一侧的掩膜材料层第一部分内。

[0182] 为此,本实施例中,所述半导体结构还包括:侧壁层640,位于所述第一沟槽636的侧壁上。

[0183] 第二沟槽通过去除掩膜材料层第二部分630b的方式形成,通过侧壁层640,以实现第二沟槽与第一沟槽636的隔离,防止第二沟槽与第一沟槽636出现贯通的问题,并使得相邻第二沟槽与第一沟槽636的间距满足设计最小间隔。

[0184] 为此,所述侧壁层640和掩膜材料层第二部分630b之间具有较高的去除选择比,使得侧壁层640能够作为后续去除掩膜材料层第二部分630b时的掩膜。本实施例中,所述侧壁层640和掩膜材料层第二部分630b的材料不同,所述侧壁层640的材料为氧化钛。氧化钛与无定形硅以及氮化钛之间的去除选择比较高。在其他实施例中,根据所述待刻蚀材料层和掩膜材料层的材料设定,所述侧壁层的材料还可以为氮化钛、氧化硅、氮化硅、氮氧化硅或碳化硅。

[0185] 在其他实施例中,当所述第一沟槽位于所述掩膜材料层第二部分一侧的掩膜材料层第一部分内时,所述半导体结构中也可以不包含所述侧壁层。

[0186] 本实施例中,所述掩膜材料层630还包括:掩膜材料层第三部分630c,在与所述掩膜材料层第二部分630b延伸方向相垂直的方向上,所述掩膜材料层第三部分630c贯穿所述掩膜材料层第二部分630b,且所述掩膜材料层第三部分630c中具有掺杂离子。

[0187] 所述掩膜材料层第三部分630c用于作为后续第二沟槽的剪切部件。所述掩膜材料层第三部分630c用于对所述掩膜材料层第二部分630b进行分割,从而在去除所述掩膜材料层第二部分630b后,即可在掩膜材料层630内形成多个相隔离的第二沟槽。

[0188] 所述掩膜材料层第三部分630c与掩膜材料层第二部分630b之间具有较大的刻蚀选择比,因此,在去除所述掩膜材料层第二部分630b时,所述掩膜材料层第三部分630c能够被保留,从而形成多个相隔离的第二沟槽,相应提高了形成所述第二沟槽的工艺窗口,使得

所形成第二沟槽的图形精度得到保障。

[0189] 本实施例中,所述掩膜材料层第三部分630c和掩膜材料层第一部分630a中的掺杂离子相同,这有利于降低后续在去除所述掩膜材料层第三部分630c和掩膜材料层第一部分630a的步骤中,所述掩膜材料层第一部分630a和掩膜材料层第三部分630c之间去除速率的差值,以便于在同一步骤中去除所述掩膜材料层第一部分630a和掩膜材料层第三部分630c。

[0190] 本实施例中,通过合理设定所述掩膜材料层第三部分630c中的掺杂离子浓度,使得所述掩膜材料层第三部分630c和掩膜材料层第二部分630b之间的去除选择比、以及所述掩膜材料层第三部分630c和掩膜材料层第一部分630a之间的去除选择比满足工艺需求,并防止所述掩膜材料层第一部分630c中的杂质离子向其他区域中扩散。

[0191] 本实施例中,根据前述分析可知,所述掩膜材料层第三部分630c中的掺杂离子为B离子。

[0192] 其中,根据所述掩膜材料层第三部分630c和后续掩膜材料层第一部分630a中的掺杂离子类型,合理设定所述掩膜材料层第三部分630c和后续掩膜材料层第一部分630a中的掺杂离子浓度,使得所述掩膜材料层第一部分630a和掩膜材料层第三部分630c的去除选择比为可以接近为1(例如:0.8至1.2),从而便于在同一步骤中去除所述掩膜材料层第一部分630a和掩膜材料层第三部分630c,以简化工艺步骤。

[0193] 需要说明的是,所述半导体结构还包括:保护层650,至少位于一个所述第一沟槽636中,且在所述第一沟槽636的延伸方向上,所述保护层650两侧露出相对应的所述第一沟槽636底部的剩余待刻蚀材料层620。

[0194] 所述保护层650用于作为第一沟槽的剪切部件。在所述第一沟槽636的延伸方向上,所述保护层650覆盖部分区域的待刻蚀材料层620,从而使得所述保护层650下方的待刻蚀材料层620在后续刻蚀工艺中被保留。相应的,将所述第一沟槽636的图形传递至待刻蚀材料层620中时,能够在所述待刻蚀材料层620中形成相隔离的图形。与通过光刻制程将所述第一沟槽636在其延伸方向上进行分割的方案相比,本实施例有利于提高形成所述第一沟槽636的工艺窗口,从而提高图形传递的精度。

[0195] 本实施例中,所述保护层650的材料为LTO。该材料的填充性较好,有利于提高保护层150在第一沟槽636内的填充质量,而且,该材料为易于被去除的材料,降低了后续去除所述保护层650的工艺难度。在另一些实施例中,所述保护层的材料还可以为SiOC。

[0196] 本实施例中,在与所述第一沟槽636延伸方向相垂直的方向上,所述保护层650还覆盖相对应的第一沟槽636侧壁上的侧壁层640。形成所述保护层650的制程通过包括光刻工艺,通过增大所述保护层650的长度,相应增大了形成该光刻工艺的工艺窗口,例如,缓解光刻工艺解析度的限制。其中,所述保护层650的长度指的是:在与所述第一沟槽636延伸方向相垂直的方向上,所述保护层650的尺寸。

[0197] 在其他实施例中,所述保护层也可以仅覆盖所述侧壁层之间的待刻蚀材料层。

[0198] 需要说明的是,本实施例以所述掩膜材料层第一部分630a中具有掺杂离子为例进行说明。在其他实施例中,还可以为:所述掩膜材料层第二部分中具有掺杂离子,所述掩膜材料层第一部分中相应不具有掺杂离子。

[0199] 在半导体领域中,通常通过离子掺杂的方式,使得所述掩膜材料层第二部分中具

有掺杂离子,在离子掺杂的过程中,掺杂离子破坏所述掩膜材料层第二部分的晶格,降低其材料致密度,从而使所述掩膜材料层第二部分易于被去除,相应也能提高掩膜材料层第二部分和掩膜材料层第一部分之间的去除选择比。

[0200] 为此,在该实施例中,所述掩膜材料层的材料相应为氧化硅或氮化硅。

[0201] 其中,当所述掩膜材料层的材料为氧化硅时,所述掩膜材料层第二部分中具有掺杂离子,且所述掺杂离子为Ar离子;或者,当所述掩膜材料层的材料为氮化硅时,所述掩膜材料层第二部分中具有掺杂离子,且所述掺杂离子为H离子或He离子。

[0202] 需要说明的是,在这种情况下,所述半导体结构相应不含有所述掩膜材料层第三部分,除所述掩膜材料层第二部分之外,所述掩膜材料层中的剩余部分均均用于作为所述掩膜材料层第一部分。

[0203] 对该实施例的具体描述,可参考前述实施例中的相应描述,在此不再赘述。

[0204] 本实施例所述半导体结构可以采用前述实施例所述的形成方法所形成,也可以采用其他形成方法所形成。对本实施例所述半导体结构的具体描述,可参考前述实施例中的相应描述,本实施例在此不再赘述。

[0205] 虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

图17

图18

图19

图20

图21

图22

图23

图24

图25

图26