## (10) **DE 10 2011 116 442 A1** 2013.04.25

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2011 116 442.5

(22) Anmeldetag: 20.10.2011(43) Offenlegungstag: 25.04.2013

(51) Int Cl.: **G05B 19/045** (2011.01)

**G05B 19/05** (2011.01) **G05B 19/042** (2011.01) **G06F 15/76** (2011.01) **B25J 9/18** (2011.01)

(71) Anmelder:

Robert Bosch GmbH, 70469, Stuttgart, DE

(72) Erfinder:

May, Gunther, Dr., 97753, Karlstadt, DE; Hielscher, Frank, 97816, Lohr, DE

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

(54) Bezeichnung: Steuervorrichtung und Verfahren zur Steuerung einer Bewegung eines Elements einer Anlage

(57) Zusammenfassung: Die vorliegende Erfindung betrifft eine Steuervorrichtung (100) zur Steuerung einer Bewegung eines Elementes (175) einer Anlage (177), wobei die Steuervorrichtung (100) einen Hauptprozessor (120) und einen Hilfsprozessor (140) aufweist, wobei der Hilfsprozessor (140) mit den Hauptprozessor (120) verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors (120) unterscheidet, insbesondere wobei die Rechnerarchitektur des Hilfsprozessors (140) eine schnellere Verarbeitung von vorbestimmten Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors (120). Der Hilfsprozessor (140) ist ausgebildet, um ein Hilfsprozessoreingangssignal (150) von dem Hauptprozessor (120) einzulesen und unter Verwendung des Hilfsprozessoreingangssignals (150) ein Hilfsprozessorausgangssignal (160) zu ermitteln und an den Hauptprozessor (120) auszugeben. Der Hauptprozessor (120) ist ausgebildet, um ein Eingangssignal (130) einzulesen, unter Verwendung des Eingangssignals (130) das Hilfsprozessoreingangssignal (150) zu ermitteln und an den Hilfsprozessor (140) zu übermitteln, das von dem Hilfsprozessor (140) ermittelte Hilfsprozessorausgangssignal (160) einzulesen und unter Verwendung des Hilfsprozessorausgangssignal (160) ein Steuersignal (170) zur Steuerung der Bewegung des Elementes (175) der Anlage (177) zu ermitteln.

### **Beschreibung**

**[0001]** Die vorliegende Erfindung bezieht sich auf eine Steuervorrichtung und ein Verfahren zur Steuerung einer Bewegung eines Elementes einer Anlage gemäß den Hauptansprüchen.

[0002] In vielen Automatisierungsanlagen werden heutzutage speicherprogrammierbare Steuerungen (SPS) eingesetzt. Diese können mit einem Programm versehen werden, um verschiedenste Abläufe etwa in Fabrikanlagen zu automatisieren. Viele SPS-Systeme werden mit so genannter , Motion'-Funktionalität kombiniert, die es ermöglich, auch komplexe Bewegungsabläufe, wie sie etwa bei Werkzeugmaschinen oder in der Robotik auftreten, genau zu steuern. Solche Steuerprogramme können, insbesondere im Motion-Bereich, sehr hohe Rechenleistungen erfordern. Aus diesem Grund werden dafür im Allgemeinen leistungsfähige Controller oder Industrie-PCs auf der Basis von Universalprozessoren, wie etwa PC-Hauptprozessoren oder Mikrocontroller, eingesetzt. Stellvertretend für solche Systeme soll hier der Begriff ,Automatisierungscontroller' verwendet werden. Man spricht bei kompakten Steuerungen, die Merkmale von PC-basierten Steuerungssystemen und speicherprogrammierbaren Steuerungen kombinieren, von Programmable Automation Controller, kurz PAC.

[0003] Im Bereich der Simulationstechnik werden seit einiger Zeit die Grafikprozessoren etwa von PCs dazu eingesetzt, um Berechnungen für Simulationen durchzuführen (siehe beispielsweise Marco Di Sarno: "Atomistische Simulationen auf neuartigen Prozessorarchitekturen - Simulationen auf Grafikprozessoren"; Hauptseminar , Moderne Simulationsmethoden in der Physik' an der Universität Stuttgart, 2010), entgegen ihrem ursprünglichen Zweck, nämlich dem Rendern von Grafiken zur Darstellung auf Bildschirmen. In vielen Fällen, insbesondere wenn es sich um einfache, reguläre Programmstrukturen handelt, können durch die Nutzung von Grafikprozessoren erhebliche Leistungssteigerungen gegenüber der alleinigen Berechnung auf Universalprozessoren, wie etwa PC-Hauptprozessoren erreicht werden. Auch weitere Spezialprozessoren, wie etwa Audio- oder Netzwerkprozessoren, können für ähnliche Zwecke genutzt werden.

[0004] Weiterhin können dynamisch konfigurierbare Logikbausteine, wie etwa Field Programmable Gate Arrays (FPGAs), als Ergänzung von Universalprozessoren zum Einsatz kommen. Dabei wird in Ihnen eine Konfiguration abgelegt, die spezifisch auf den jeweiligen Anwendungszweck ausgelegt ist und auch dynamisch generiert werden kann, und bei geeigneter Auslegung durch die Spezialisierung eine erhebliche Beschleunigung im Vergleich zur Nutzung eines Universalprozessors ermöglicht (siehe beispielswei-

se Gerhard Lienhart: "Beschleunigung hydrodynamischer astrophysikalischer Simulationen mit FPGAbasierten rekonfigurierbaren Koprozessoren", Dissertation an der Universität Heidelberg, 2004).

**[0005]** Vor diesem Hintergrund ist es die Aufgabe der vorliegenden Erfindung, eine verbesserte Steuervorrichtung und ein verbessertes Verfahren zur Steuerung einer Bewegung eines Elementes einer Anlage zu schaffen.

**[0006]** Diese Aufgabe wird durch den Gegenstand der unabhängigen Ansprüche gelöst. Vorteilhafte Ausgestaltungen ergeben sich aus den Unteransprüchen.

**[0007]** Die vorliegende Erfindung schafft eine Steuervorrichtung zur Steuerung einer Bewegung eines Elementes einer Anlage, wobei die Steuervorrichtung die folgenden Merkmale aufweist:

- einen Hauptprozessor, und

- einen Hilfsprozessor, wobei der Hilfsprozessor mit den Hauptprozessor verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors unterscheidet, insbesondere wobei die Rechnerarchitektur des Hilfsprozessors eine schnellere Verarbeitung von vorbestimmten zeitveränderlichen Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors und wobei der Hilfsprozessor ausgebildet ist, um ein Hilfsprozessoreingangssignal von dem Hauptprozessor einzulesen und unter Verwendung des Hilfsprozessoreingangssignal ein Hilfsprozessorausgangssignal zu ermitteln und an den Hauptprozessor auszugeben,

wobei der Hauptprozessor ausgebildet ist, um ein Eingangssignal einzulesen, unter Verwendung des Eingangssignals das Hilfsprozessoreingangssignal zu ermitteln und an den Hilfsprozessor zu übermitteln, das von dem Hilfsprozessor ermittelte Hilfsprozessorausgangssignal einzulesen und unter Verwendung des Hilfsprozessorausgangssignal ein Steuersignal zur Steuerung der Bewegung des Elementes der Anlage zu ermitteln.

[0008] Ferner schafft die vorliegende Erfindung ein Verfahren zur Steuerung einer Bewegung eines Elementes einer Anlage, wobei eine Steuervorrichtung einen Hauptprozessor und einen Hilfsprozessor aufweist, wobei der Hilfsprozessor mit dem Hauptprozessor verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors unterscheidet, insbesondere wobei die Rechnerarchitektur des Hilfsprozessors eine schnellere Verarbeitung von vorbestimmten zeitveränderlichen Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors, wobei das Verfahren die folgenden Schritte aufweist:

- Einlesen eines Eingangssignals durch den Hauptprozessor;

- Ausgeben eines Hilfsprozessoreingangssignals durch den Hauptprozessor an den Hilfsprozessor ansprechend auf das Eingangssignal;

- Empfangen eines von dem Hilfsprozessor ausgegebenen Hilfsprozessorausgangssignals an dem Hauptprozessor, wobei der Hilfsprozessor das Hilfsprozessorausgangssignal ansprechend auf das Hilfsprozessoreingangssignal bereitstellt; und

- Bestimmen eines Steuersignals zur Steuerung der Bewegung des Elementes der Anlage durch den Hauptprozessor, wobei das Steuersignal ansprechend auf das vom Hauptprozessor bereitgestellte Hilfsprozessorausgangssignal bereitgestellt wird.

**[0009]** Von Vorteil ist auch ein Computerprogrammprodukt mit Programmcode, der auf einem maschinenlesbaren Träger wie einem Halbleiterspeicher, einem Festplattenspeicher oder einem optischen Speicher gespeichert sein kann und zur Durchführung des Verfahrens nach einer der vorstehend beschriebenen Ausführungsformen verwendet wird, wenn das Programm auf einem Computer oder einer Vorrichtung ausgeführt wird.

**[0010]** Somit schafft die vorliegende Erfindung ein Computerprogramm mit Programmcode zur Durchführung oder Ansteuerung der Schritte des oben genannten Verfahrens, wenn das Computerprogramm auf einem Steuergerät ausgeführt wird.

[0011] Unter einer Anlage kann beispielsweise eine Vorrichtung der Automatisierungstechnik wie beispielsweise eine Schweißanlage, eine Förderanlage oder dergleichen verstanden werden, in der einzelne Elemente wie beispielsweise ein Greifarm mit einer Schweißzange in Bewegung gesetzt werden. Unter einer Rechnerarchitektur kann eine Verschaltung verstanden werden, wie die einzelnen Schalteinheiten der betreffenden Prozessoren miteinander verbunden sind. Beispielsweise kann durch die Rechnerarchitektur eine (zumindest teilweise) veränderbare (d. h. flüchtig programmierbare) oder feste (d. h. nicht-flüchtig programmierbare) Verdrahtung oder Verbindung der einzelnen Komponenten des Prozessors festgelegt sein. Dabei kann die Rechnerarchitektur des Hauptprozessors in Bezug auf andere Parameter optimiert sein, als die Rechnerarchitektur des Hilfsprozessors. Insbesondere kann der Hilfsprozessor eine Rechnerarchitektur aufweisen, die dazu ausgelegt ist, um eine schnellere Verarbeitung von vorbestimmten (zeitveränderlichen) Signalen zu ermöglichen. Diese vorbestimmten (zeitveränderlichen) Signale können beispielsweise Signale sein, wie sie in Graphikanwendungen oder Audioanwendungen oft auftreten. Beispielsweise können vorbestimmten Signale solche sein, die eine Verschiebung eines Bildpunktes in eine vorbestimmte Richtung und Strecke repräsentieren. Ein solches Signal tritt in der Bildverarbeitung auf, aber auch bei der Berechnung einer Bewegung eines Elementes einer Anlage von einem Startpunkt zu einem Zielpunkt. Auf diese Weise kann zur Berechnung des von dem Element abzufahrenden Weges von dem Start- zu dem Zielpunkt auch ein Prozessor verwendet werden, der speziell für derartige Berechnungen in Bezug auf eine Verarbeitungsgeschwindigkeit optimiert ist, beispielsweise aus dem Bereich der Bildverarbeitung mit bestimmten Graphikprozessoren.

[0012] Der vorliegenden Erfindung liegt die Erkenntnis zu Grunde, dass eine Steuerung einer Bewegung eines Elementes einer Anlage durch die Auslagerung zumindest eines Teil der numerischen Last bei der Berechnung von Steuerungsdaten für das sich bewegende Element einer Anlage in einen speziell für dynamische Berechnungsvorgänge ausgelegten oder optimierten Prozessor, nämlich den Hilfsprozessor, sehr effizient durchgeführt werden kann. Ein solcher (Hilfs-)Prozessor kann beispielsweise ein Graphikprozessor und/oder ein Audioprozessor sein, der Signale für eine graphische Ausgabe aufbereitet bzw. Audiosignale für einen Ausgabe aufbereitet. Dieser Hilfsprozessor kann durch einen Hauptprozessor mit übergeordneten Informationen oder Daten versorgt werden, so dass sich die Funktionalität des Hilfsprozessors im Wesentlichen nur auf einen Teil, d. h. bestimmte Berechnungsaufgaben bei der Abarbeitung einer Signal-Verarbeitungsvorschrift beschränken kann, für die der Hilfsprozessor besonders optimiert wurde. Auf diese Weise kann die besondere Leistungsfähigkeit des Hilfsprozessors im Bereich der Verarbeitung von dynamischen Signalen unterstützend verwendet werden, wobei die übergeordnete Steuerung (d. h. die Bestimmung der Steuersignale für die Bewegung eines Elementes) der Anlage durch den einfach und flexibel zu programmierenden Hauptprozessor geleistet wird.

[0013] Die vorliegende Erfindung bietet den Vorteil, dass durch die Kombination des Hauptprozessors mit dem für bestimmte Funktionalitäten optimierten Hilfsprozessor eine wesentliche Beschleunigung der Ermittlung des Steuersignals des Elementes der Anlage möglich ist. Dabei kann auf bereits verfügbare Komponenten zurückgegriffen werden, so dass auch im Bereich der Anlagensteuerung, der keinen derartig großen Markt darstellt, wie der Bereich der Unterhaltungselektronik, dennoch von Innovationen im Bereich der Unterhaltungstechnik profitieren kann und zur Verbesserung der Leistungsfähigkeit der Anlagensteuerungen genutzt werden kann. Insofern kann ein Zusatznutzen in dem technischen Feld der Anlagensteuerung durch die Ausnutzung von technischen Innovationen beispielsweise aus dem Bereich der Unterhaltungselektronik realisiert werden.

[0014] Gemäß einer Ausführungsform der vorliegenden Erfindung kann der Hauptprozessor derart ausgestaltet sein, dass eine Verarbeitungsvorschrift zur Verarbeitung von Signalen zumindest teilweise flüchtig in dem Hauptprozessor einprogrammiert ist und/oder dass der Hilfsprozessor derart ausgebildet ist, dass eine Verarbeitungsvorschrift zur Verarbeitung von Signalen zumindest teilweise nichtflüchtig in den Hilfsprozessor einprogrammiert ist. Eine derartige Ausführungsform der vorliegenden Erfindung bietet den Vorteil einer besonders guten Einstellungsmöglichkeit zwischen einer möglichst flexible programmierbaren übergeordneten Hauptprozessoreinheit, die das Steuersignal für die Bewegung des Elementes der Anlage berechnet und einer möglichst schnellen Berechnung von einzelnen Verarbeitungsschritten der gesamten Verarbeitungsvorschrift zur Ermittlung des Steuersignals für die Bewegung des Elementes der Anlage.

[0015] Vorteilhaft ist es ferner, wenn gemäß einer Ausführungsform der vorliegenden Erfindung der Hauptprozessor ausgebildet ist, um einen Teil eines Codes einer Verarbeitungsvorschrift als Verarbeitungsvorschrift in den Hilfsprozessor zu laden, wobei der Hilfsprozessor ausgebildet ist, um unter Anwendung des Codes der Verarbeitungsvorschrift auf das Hilfsprozessoreingangssignal das Hilfsprozessorausgangssignal zu ermitteln. Eine derartige Ausführungsform der vorliegenden Erfindung bietet den Vorteil einer guten Auslastbarkeit des Hilfsprozessors, da dem Hilfsprozessor auch vom Hauptprozessor durch das Laden von bestimmtem Code die in dem Code codierten Aufgaben übertragen werden können, die dann der Hauptprozessor nicht mehr abarbeiten braucht.

[0016] Um eine besonders schnelle Ermittlung des Steuersignals für die Bewegung des Elementes der Anlage zu erlangen, kann eine Parallelisierung von bestimmten Verarbeitungsschritten durchgeführt werden. Gemäß einer Ausführungsform der vorliegenden Erfindung kann dazu beispielsweise zumindest ein weiterer Hilfsprozessor vorgesehen sein, wobei der weitere Hilfsprozessor mit den Hauptprozessor verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors unterscheidet, insbesondere wobei die Rechnerarchitektur des weiteren Hilfsprozessors eine schnellere Verarbeitung von vorbestimmten zeitveränderlichen Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors und wobei der weitere Hilfsprozessor ausgebildet ist, um ein weiteres Hilfsprozessoreingangssignal von dem Hauptprozessor und/oder dem Hilfsprozessor einzulesen und unter Verwendung des weiteren Hilfsprozessoreingangssignal ein weiteres Hilfsprozessorausgangssignal zu ermitteln und an den Hauptprozessor und/ oder den Hilfsprozessor auszugeben, insbesondere wobei der Hauptprozessor ausgebildet ist, um unter

Verwendung des weiteren Hilfsprozessorausgangssignals das Steuersignal zur Steuerung der Bewegung des Elementes der Anlage zu ermitteln.

[0017] Besonders vorteilhaft kann gemäß einer Ausführungsform der vorliegenden Erfindung als Hilfsprozessor ein Prozessor vorgesehen sein, dessen Rechnerarchitektur für eine Verarbeitung von Signalen zur Anzeige einer Grafik, eine Verarbeitung von Audiodaten oder zur Einprogrammierung von dynamisch konfigurierbaren Logikschaltungen optimiert wurde. Die Verwendung dieser Art von Prozessor als Hilfsprozessor erweist sich für eine schnelle Ermittlung des Steuersignals als sehr hilfreich.

[0018] Auch kann gemäß einer weiteren Ausführungsform der vorliegenden Erfindung der Hauptprozessor ausgebildet sein, um zeitversetzt mehrere Hilfsprozessoreingangssignale (zyklisch) an den Hilfsprozessor zu übersenden und ansprechend auf jedes an den Hilfsprozessor übersandte Hilfsprozessoreingangssignal ein Hilfsprozessorausgangssignal zu empfangen und wobei der Hauptprozessor ausgebildet ist, um das Steuersignal unter Verwendung der vom Hilfsprozessor empfangenen Hilfsprozessorausgangssignale zu ermitteln. Eine solche Ausführungsform der vorliegenden Erfindung bietet den Vorteil, dass einzelne zyklisch zu wiederholende Arbeitsschritte bei der Ermittlung des Steuersignals wiederholt in dem Hilfsprozessor ausgeführt werden können, wobei der Hauptprozessor immer wieder für die Ermittlung von Teilergebnissen (in der Form der Hilfsprozessorausgangssignale) auf die besondere Leistungsfähigkeit des Hilfsprozessors zurückgreifen kann.

[0019] Um eine besonders einfache Implementierung der Steuervorrichtung zu erreichen, kann gemäß einer Ausführungsform der vorliegenden Erfindung der Hilfsprozessor als Teileinheit in eine integrierte Schaltung mit dem Hauptprozessor eingebettet sein. Dabei kann ein Kern (beispielsweise von mehreren Kernen) einer integrierten Schaltung den Hauptprozessor und ein anderer Bereich der integrierten Schaltung den Hilfsprozessor bilden. Dabei können sowohl der Haupt- als auch der Hilfsprozessors in einem gemeinsamen Gehäuse der integrierten Schaltung angeordnet sein.

[0020] Die Erfindung wird nachstehend anhand der beigefügten Zeichnungen beispielhaft näher erläutert. Es zeigen:

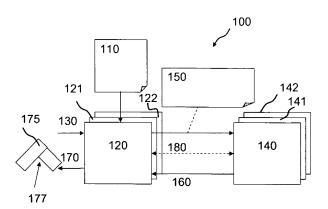

**[0021]** Fig. 1 ein Blockschaltbild eines ersten Ausführungsbeispiels der vorliegenden Erfindung als Steuervorrichtung;

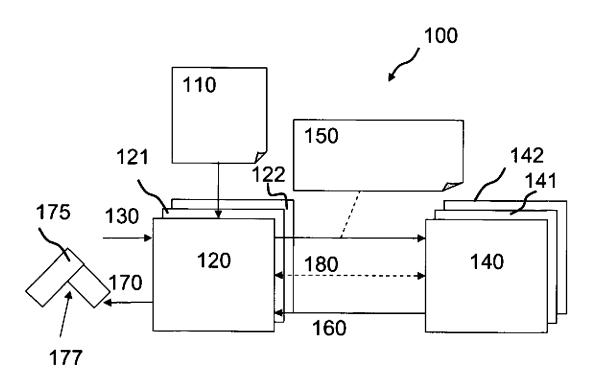

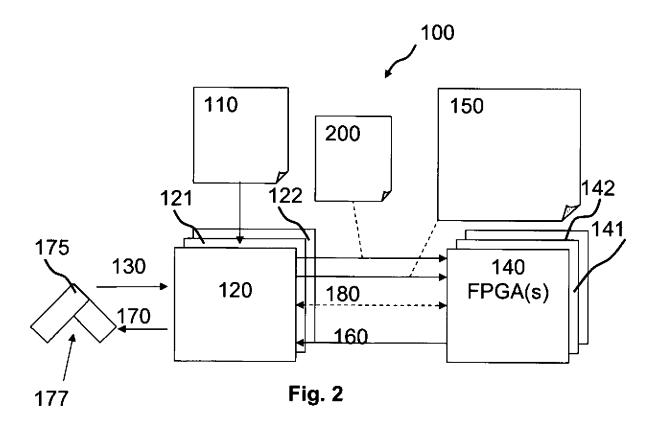

**[0022]** Fig. 2 ein Blockschaltbild eines zweiten Ausführungsbeispiels der vorliegenden Erfindung als Steuervorrichtung; und

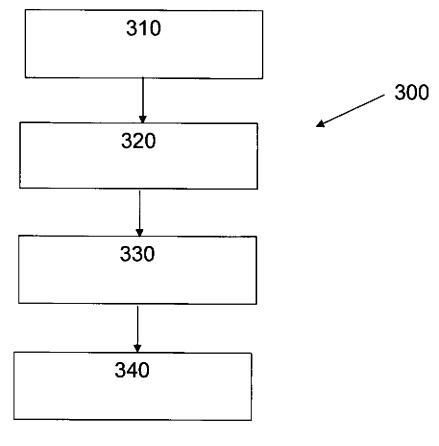

[0023] Fig. 3 ein Ablaufdiagramm eines Ausführungsbeispiels der vorliegenden Erfindung als Verfahren.

**[0024]** Gleiche oder ähnliche Elemente können in den nachfolgenden Figuren durch gleiche oder ähnliche Bezugszeichen versehen sein. Ferner enthalten die Figuren der Zeichnungen, deren Beschreibung sowie die Ansprüche zahlreiche Merkmale in Kombination. Einem Fachmann ist dabei klar, dass diese Merkmale auch einzeln betrachtet werden oder sie zu weiteren, hier nicht explizit beschriebenen Kombinationen zusammengefasst werden können.

[0025] Ein erster Aspekt, der dem hier beschriebenen Ansatz zugrunde liegt ist, dass beispielsweise Grafikprozessoren auch eingesetzt werden können, um SPS- und/oder Motion-Programmcode, teilweise als Ergänzung zu einem Universalprozessor, oder ganz und autark, ablaufen zu lassen. Es ist davon auszugehen, dass sich Anwendungen ergeben werden, bei denen dadurch eine erhebliche Steigerung der Verarbeitungsgeschwindigkeit erzielen lässt, da sich sowohl in SPS- als auch in Motion-Programmcode typisch sehr reguläre Strukturen befinden, die sich für die Verarbeitung auf Grafikprozessoren gut eignen. An diesem Ansatz ist weiterhin vorteilhaft, dass Grafikprozessoren je nach verwendeter Systemarchitektur häufig autark bzw. hinsichtlich Zugriffsprioritäten bevorzugt an den Hauptprozessor angebunden sind und nicht mit weiteren Systemkomponenten um den Zugriff auf Systembusse konkurrieren.

**[0026]** Auch andere Spezialprozessoren, wie etwa Audioprozessoren, können für eine Anwendung bei der Beschleunigung von SPS- und/oder Motion-Programmcode geeignet sein.

**[0027]** Ein zweiter Aspekt des hier vorgestellten Ansatzes ist beispielsweise die Nutzung von dynamisch konfigurierbaren Logikbausteine zur Beschleunigung des Ablaufs von SPS- und/oder Motion-Programm-codes.

[0028] Fig. 1 zeigt ein Blockschaltbild eines ersten Ausführungsbeispiels der vorliegenden Erfindung als Steuervorrichtung 100 als erstes Umsetzungsbeispiel der vorliegenden Erfindung. Das in der Fig. 1 gezeigte Blockschaltbild des ersten Umsetzungsbeispiels der beschriebenen Grundidee zeigt eine Steuervorrichtung 100, in dem ein SPS-/Motion-Programm-Code 110 (d. h. ein Programmcode, durch den eine speicherprogrammierbare Steuerung für eine Bewegung (= Motion) eines Elementes einer Anlage gesteuert werden soll) in einen (von mehreren) Hauptprozessor(en) 120 (bzw. 121, 122) gespeichert werden soll. Dabei wird ein Eingangssignal 130 dem Hauptprozessor 120 zugeführt, das beispielsweise einen Start eines durchzuführenden

Programmablaufs in dem Hauptprozessor 120 repräsentiert. Weiterhin umfasst die Steuervorrichtung 100 zumindest einen Grafikprozessor 140, gemäß dem in Fig. 1 dargestellten Ausführungsbeispiel drei Grafikprozessoren 140, 141 und 142, die als Hilfsprozessor(en) 140 arbeiten. Dabei wird durch ein Hilfsprozessoreingangssignal 150, welches vom Hauptprozessor 120 an dem Hilfsprozessor 140 ausgegeben wird, ein selektierter Anteil eines für den Grafikprozessor 140 aufbereiteten Teils des SPS-/Motion-Programmcodes übertragen, so dass im Hilfsprozessor 140 Operationen entsprechend der Signal-Verarbeitungsvorschrift ausgeführt werden, die in dem im Hilfsprozessoreingangssignal 150 übertragenen Code codiert sind. Ferner können in dem Hilfsprozessoreingangssignal 150 auch konkrete Werte als Variablen übergeben werden, die die Basis für die in dem Hilfsprozessor 140 unter Verwendung des vom Hauptprozessor 120 an den Hilfsprozessor 140 übertragenen Codes ermittelten Berechnungsergebnisse darstellen. Diese Berechnungsergebnisse werden dann in einem Hilfsprozessorausgangssignal 160 vom Hilfsprozessor 140 an den Hauptprozessor 120 übertragen, in dem dann unter Verwendung der in dem Hilfsprozessorausgangssignal 160 übertragenen Berechnungsergebnisse das Steuersignal 170 für die Ansteuerung der Bewegung des Elementes 175 der Anlage 177 bestimmt wird. Das Element 175 kann dabei beispielsweise ein Greifarm einer Fertigungsmaschine als Anlage 177 sein, beispielsweise um unter Verwendung des Greifarmes 175 Schweißnähte an einem Werkstück anzubringen. Um eine Berechnung der Werte der Berechnungsergebnisse im Hilfsprozessor 140 zu beschleunigen, können optional noch weitere Signale 180 zur Kommunikation zwischen dem Hauptprozessor 120 und dem Hilfsprozessor 140 ausgetauscht werden, beispielsweise zur Synchronisation der Signalübermittlung oder Steuerung der Signalverarbeitung zwischen dem Hauptprozessor 120 und Hilfsprozessor 140.

[0029] In der Fig. 1 wird somit ein Teil eines Automatisierungscontrollers 100 als Ausführungsbeispiel der vorliegenden Erfindung dargestellt. Der Hauptprozessor 120, bei denen es sich hier um einen Universalprozessor handelt, erhält das Anwenderprogramm, z. B. um einen Automatisierungsvorgang in einer Fabrik zu steuern. Ein Teil des Programms, der sich besonders zur Verarbeitung auf dem Grafikprozessor 140 eignet, wird gegebenenfalls in eine für den Grafikprozessor 140 besonders geeignete Form aufbereitet, an den Grafikprozessor 140 weitergegeben (beispielsweise mittels des Signals 150). Nach der Berechnung liefert der Grafikprozessor 140 die Ergebnisse 160 an den Hauptprozessor 120 zurück. Zwischendurch kann gegebenenfalls zusätzliche Kommunikation 180 stattfinden. In der Regel ist Programmcode in der Automatisierungstechnik zyklischer Natur, so dass sich dieser gesamte Vorgang, oder Teile davon, entsprechend wiederholen können.

[0030] Fig. 2 zeigt ein Blockschaltbild eines zweiten Ausführungsbeispiels der vorliegenden Erfindung als Steuervorrichtung 100. Entgegen der Darstellung aus Fig. 1 ist dabei jedoch der bzw. die Hilfsprozessor(en) 140 als FPGA(s) (FPGA = field programmable gate array = (Anwendungs-)Feld programmierbare (Logik-)Gatter-Anordnung) ausgestaltet. Somit ist in der Fig. 2 ein weiteres Umsetzungsbeispiel der beschriebenen Grundidee abgebildet. In der Darstellung aus Fig. 2 ist wiederum ein Teil eines Automatisierungscontrollers 100 dargestellt. Dabei wird der auf dem FPGA 140 auszuführende Programmcode gegebenenfalls in eine für den FPGA 140 in der vorliegenden Konfiguration nutzbare Form gebracht. Anschließend wird der bzw. werden die FPGAs 140 vom Hauptprozessor 120 mittels eines Konfigurationssignals 200 derart konfiguriert, dass sie den vorliegenden Programmcode bzw. Teile davon möglichst effizient ausführen können. Das Konfigurationssignal 200 enthält somit eine Logik-Konfigurationsinformation wie die einzelnen Schaltungs- bzw. Logikeinheiten des FPGAs 140 miteinander zu verschalten sind. damit sie möglichst schnell und effizient die vom FP-GA als Hilfsprozessor 140 auszuführenden Arbeitsschritte ausführen können. Ab dann läuft das weitere Vorgehen (d. h. die Übertragung von Information zwischen dem Haupt- und Hilfsprozessor) ähnlich wie im Ausführungsbeispiel ab, welches in der Fig. 1 dargestellt und näher beschrieben wurde. Die über das Konfigurationssignal 200 bereitgestellte FPGA-Konfiguration kann für die Laufzeit der Steuerungsvorrichtung 100 statisch sein. Alternativ kann der FP-GA 140 während der Laufzeit der Steuerungsvorrichtung 100 über das Konfigurationssignal 200 umkonfiguriert werden.

[0031] Die vorliegende Erfindung ermöglicht somit eine Implementierung von SPS- und Motion-Funktionalität auf Spezialprozessoren und/oder FPGAs als Ergänzung oder Ersatz für Universalprozessoren. Wichtige Aspekte der vorliegenden Erfindung beziehen sich somit beispielsweise auf die Nutzung eines oder mehrerer Hilfs- bzw. Grafikprozessoren zum Beschleunigen durch partielle Ausführung oder zur exklusiven Ausführung von SPS-Programmcode einerseits und Motion-Programmcode andererseits, wobei der Motion-Programmcode, der speziell Berechnungsschritte für Bewegungen der Elemente betrifft, auf dem besonders ausgestalteten Hilfsprozessor ausgeführt wird. Ein weiterer Aspekt der Erfindung bezieht sich auf eine Nutzung eines oder mehrerer anderer Spezialprozessoren, etwa Audioprozessoren zum Beschleunigen durch partielle Ausführung oder zur exklusiven Ausführung von SPS-Programmcode (insbesondere auf dem Hauptprozessor) einerseits und einem Motion-Programmcode (insbesondere auf dem Hilfsprozessor) andererseits. Auch ist ein weiterer Aspekt der vorliegenden Erfindung darin zu sehen, dass eine Nutzung eines oder mehrerer dynamisch konfigurierbarer Logikbausteine wie etwa

Field Programmable Gate Arrays (FPGAs) zum Beschleunigen durch partielle Ausführung oder zur exklusiven Ausführung von SPS-Programmcode einerseits und einem Motion-Programmcode andererseits verwendet wird. Zugleich können auch der oder die Hilfsprozessoren, d. h. der jeweilige Zusatzbaustein bzw. die jeweiligen Zusatzbausteine (Grafik-/Spezialprozessor oder FPGA) ganz oder teilweise in den bzw. in die Hauptprozessoren integriert sind. Ein weiterer Aspekt der Erfindung betrifft ferner eine automatische Selektierung (die teilweise auch als "Mapping bezeichnet wird) der durch den oder die vorstehend genannten Grafikprozessoren, den oder die anderen vorstehend genannten Spezialprozessoren, oder den oder die vorstehend beschrieben dynamisch konfigurierbaren Logikbaustein(e) zu beschleunigenden. Dabei werden Anteile des Programmcodes zur Berechnung des Steuersignals durch den Compiler, den Hauptprozessor zur Laufzeit oder durch manuelle Selektierung durch den Benutzer bei der Programmerstellung abgespalten und in den Hilfsprozessor eingeschrieben, damit die Teile der Verarbeitungsvorschrift, die in den abgespaltenen Anteilen enthalten sind, in dem Hilfsprozessor ausgeführt werden.

[0032] Fig. 3 zeigt ein Ablaufdiagramm eines Ausführungsbeispiels der vorliegenden Erfindung als Verfahren 300 zur Steuerung einer Bewegung eines Elementes einer Anlage. Die Steuervorrichtung weist einen Hauptprozessor und einen Hilfsprozessor auf, wobei der Hilfsprozessor mit dem Hauptprozessor verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors unterscheidet, insbesondere wobei die Rechnerarchitektur des Hilfsprozessors eine schnellere Verarbeitung von (zeitveränderlichen) Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors. Das Verfahren umfasst ferner einen Schritt des Einlesens 310 eines Eingangssignals durch den Hauptprozessor. Weiterhin umfasst das Verfahren 300 einen Schritt des Ausgebens 320 eines Hilfsprozessoreingangssignals durch den Hauptprozessor an den Hilfsprozessor ansprechend auf das Eingangssignal. Ferner umfasst das Verfahren 300 einen Schritt des Empfangens 330 eines von dem Hilfsprozessor ausgegebenen Hilfsprozessorausgangssignals an dem Hauptprozessor, wobei der Hilfsprozessor das Hilfsprozessorausgangssignal ansprechend auf das Hilfsprozessoreingangssignal bereitgestellt hat. Schließlich umfasst das Verfahren 300 einen Schritt des Bestimmens 340 eines Steuersignals zur Steuerung der Bewegung des Elementes der Anlage durch den Hauptprozessor, wobei das Steuersignal ansprechend auf das vom Hilfsprozessorprozessor bereitgestellte Hilfsprozessorausgangssignal bereitgestellt wird.

**[0033]** Die gezeigten Ausführungsbeispiele sind nur beispielhaft gewählt und können miteinander kombiniert werden.

### Bezugszeichenliste

| 100 | Steuervorrichtung                       |

|-----|-----------------------------------------|

| 110 | SPS-/Motion-Programm-Code               |

| 120 | Hauptprozessor                          |

| 121 | weiterer Hauptprozessor                 |

| 122 | weiterer Hauptprozessor                 |

| 130 | Eingangssignal                          |

| 140 | Hilfsprozessor                          |

| 141 | weiterer Hilfsprozessor                 |

| 142 | weiterer Hilfsprozessor                 |

| 150 | Hilfsprozessoreingangssignal            |

| 160 | Hilfsprozessorausgangssignal            |

| 170 | Steuersignal                            |

| 175 | Element, Greifarm                       |

| 177 | Anlage, Fertigungsmaschine, Schweißan-  |

|     | lage                                    |

| 180 | Signale zur weiteren Kommunikation zwi- |

|     | schen dem Haupt- und dem Hilfsprozessor |

| 200 | FPGA-Konfigurationssignal               |

|     |                                         |

#### **Patentansprüche**

- 1. Steuervorrichtung (100) zur Steuerung einer Bewegung eines Elementes (175) einer Anlage (177), wobei die Steuervorrichtung (100) die folgenden Merkmale aufweist:

- einen Hauptprozessor (120), und

- einen Hilfsprozessor (140), wobei der Hilfsprozessor (140) mit dem Hauptprozessor (120) verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors (120) unterscheidet, insbesondere wobei die Rechnerarchitektur des Hilfsprozessors (140) eine schnellere Verarbeitung von vorbestimmten Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors (120) und wobei der Hilfsprozessor (140) ausgebildet ist, um ein Hilfsprozessoreingangssignal (150) von dem Hauptprozessor (120) einzulesen und unter Verwendung des Hilfsprozessoreingangssignals (150) ein Hilfsprozessorausgangssignal (160) zu ermitteln und an den Hauptprozessor (120) auszugeben,

wobei der Hauptprozessor (120) ausgebildet ist, um ein Eingangssignal (130) einzulesen, unter Verwendung des Eingangssignals (130) das Hilfsprozessoreingangssignal (150) zu ermitteln und an den Hilfsprozessor (140) zu übermitteln und das von dem Hilfsprozessor (140) ermittelte Hilfsprozessorausgangssignal (160) einzulesen und unter Verwendung des Hilfsprozessorausgangssignal (160) ein Steuersignal (170) zur Steuerung der Bewegung des Elementes (175) der Anlage (177) zu ermitteln.

2. Steuervorrichtung gemäß Anspruch 1, dadurch gekennzeichnet, dass der Hauptprozessor (120) derart ausgestaltet ist, dass eine Verarbeitungsvorschrift zur Verarbeitung von Signalen zumindest teilweise flüchtig in dem Hauptprozessor (120) einprogrammiert ist und/oder dass der Hilfsprozessor (140) der-

art ausgebildet ist, dass eine Verarbeitungsvorschrift zur Verarbeitung von Signalen zumindest teilweise nicht-flüchtig in den Hilfsprozessor (140) einprogrammiert ist.

- 3. Steuervorrichtung gemäß einem der vorangegangenen Ansprüche, dadurch gekennzeichnet, dass der Hauptprozessor (120) ausgebildet ist, um einen Teil eines Codes einer Verarbeitungsvorschrift als Verarbeitungsvorschrift in den Hilfsprozessor (140) zu laden, wobei der Hilfsprozessor (140) ausgebildet ist, um unter Anwendung des Codes der Verarbeitungsvorschrift auf das Hilfsprozessoreingangssignal (150) das Hilfsprozessorausgangssignal (160) zu ermitteln.

- 4. Steuervorrichtung gemäß einem der vorangegangenen Ansprüche, gekennzeichnet durch zumindest einen weiteren Hilfsprozessor (141) wobei der weitere Hilfsprozessor (141) mit den Hauptprozessor (120) verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors (120) unterscheidet, insbesondere wobei die Rechnerarchitektur des weiteren Hilfsprozessors (141) eine schnellere Verarbeitung von vorbestimmten Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors (120) und wobei der weitere Hilfsprozessor (141) ausgebildet ist, um ein weiteres Hilfsprozessoreingangssignal von dem Hauptprozessor (120) und/oder dem Hilfsprozessor (140) einzulesen und unter Verwendung des weiteren Hilfsprozessoreingangssignal ein weiteres Hilfsprozessorausgangssignal zu ermitteln und an den Hauptprozessor (120) und/oder den Hilfsprozessor (140) auszugeben, insbesondere wobei der Hauptprozessor (120) ausgebildet ist, um unter Verwendung des weiteren Hilfsprozessorausgangssignals das Steuersignal (170) zur Steuerung der Bewegung des Elementes (175) der Anlage (177) zu ermitteln.

- 5. Steuervorrichtung gemäß einem der vorangegangenen Ansprüche, dadurch gekennzeichnet, dass als Hilfsprozessor (140) ein Prozessor vorgesehen ist, dessen Rechnerarchitektur für eine Verarbeitung von Signalen zur Anzeige einer Grafik, eine Verarbeitung von Audiodaten oder zur Einprogrammierung von dynamisch konfigurierbaren Logikschaltungen optimiert wurde.

- 6. Steuervorrichtung gemäß einem der vorangegangenen Ansprüche, dadurch gekennzeichnet, dass der Hauptprozessor (120) ausgebildet ist, um zeitversetzt mehrere Hilfsprozessoreingangssignale (150) zyklisch an den Hilfsprozessor (140) zu übersenden und ansprechend auf jedes an den Hilfsprozessor (140) übersandte Hilfsprozessoreingangssignal (150) ein Hilfsprozessorausgangssignal (160) zu empfangen und wobei der Hauptprozessor (120) ausgebildet ist, um das Steuersignal (170) unter Ver-

wendung der vom Hilfsprozessor (140) empfangenen Hilfsprozessorausgangssignale (160) zu ermitteln.

- 7. Steuervorrichtung gemäß einem der vorangegangenen Ansprüche, dadurch gekennzeichnet, dass der Hilfsprozessor (140) als Teileinheit in eine integrierte Schaltung mit dem Hauptprozessor (120) eingebettet ist.

- 8. Steuervorrichtung gemäß einem der vorangegangenen Ansprüche, dadurch gekennzeichnet, dass der Hilfsprozessor (140) als Teileinheit einer elektronische Schaltung mit dem Hauptprozessor (120) verbunden ist.

- 9. Verfahren (300) zur Steuerung einer Bewegung eines Elementes (175) einer Anlage (177), wobei eine Steuervorrichtung (100) einen Hauptprozessor (120) und einen Hilfsprozessor (140) aufweist, wobei der Hilfsprozessor (140) mit den Hauptprozessor (120) verbunden ist und eine Rechnerarchitektur aufweist, die sich von einer Rechnerarchitektur des Hauptprozessors (120) unterscheidet, insbesondere wobei die Rechnerarchitektur des Hilfsprozessors (140) eine schnellere Verarbeitung von vorbestimmten Signalen ermöglicht, als die Rechnerarchitektur des Hauptprozessors (120), wobei das Verfahren (300) die folgenden Schritte aufweist:

- Einlesen (**310**) eines Eingangssignals (**130**) durch den Hauptprozessor (**120**);

- Ausgeben (320) eines Hilfsprozessoreingangssignals (150) durch den Hauptprozessor (120) an den Hilfsprozessor (140) ansprechend auf das Eingangssignal (130);

- Empfangen (330) eines von dem Hilfsprozessor (140) ausgegebenes Hilfsprozessorausgangssignals (160) an dem Hauptprozessor (120), wobei der Hilfsprozessor (140) das Hilfsprozessorausgangssignal (160) ansprechend auf das Hilfsprozessoreingangssignal (150) bereitgestellt hat; und

- Bestimmen (340) eines Steuersignals (170) zur Steuerung der Bewegung des Elementes (175) der Anlage (177) durch den Hauptprozessor (120), wobei das Steuersignal (175) ansprechend auf das vom Hilfsprozessor (140) bereitgestellte Hilfsprozessorausgangssignal (160) bereitgestellt wird.

- 10. Computerprogramm mit Programmcode zur Durchführung oder Ansteuerung der Schritte des Verfahrens (300) gemäß Anspruch 9, wenn das Computerprogramm auf einer Steuervorrichtung (100) ausgeführt wird.

Es folgen 2 Blatt Zeichnungen

## Anhängende Zeichnungen

Fig. 1

Fig. 3