(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4582078号 (P4582078)

(45) 発行日 平成22年11月17日(2010.11.17)

(24) 登録日 平成22年9月10日(2010.9.10)

(51) Int. Cl.

FL

GO6F 12/16

(2006, 01)

GO6F 12/16 320F

> 請求項の数 6 (全 12 頁)

(21) 出願番号

特願2006-284003 (P2006-284003)

(22) 出願日 (65) 公開番号 平成18年10月18日 (2006.10.18) 特開2008-102693 (P2008-102693A)

(43) 公開日

平成20年5月1日(2008.5.1)

審查請求日

平成19年5月30日 (2007.5.30)

||(73)特許権者 000003067

TDK株式会社

東京都中央区日本橋一丁目13番1号

(74)代理人 100094983

弁理士 北澤 一浩

(74)代理人 100095946

弁理士 小泉 伸

(74)代理人 100099829

弁理士 市川 朗子

(72) 発明者 長谷川 英知

東京都中央区日本橋一丁目13番1号 T

DK株式会社内

審査官 堀江 義隆

最終頁に続く

(54) 【発明の名称】メモリコントローラ及びフラッシュメモリシステム、並びにフラッシュメモリの制御方法

### (57)【特許請求の範囲】

### 【請求項1】

ホストシステムから与えられる指示情報に応じて、複数個のフラッシュメモリに対する 並行したアクセスを制御するメモリコントローラであって、

前記フラッシュメモリから読み出したデータに含まれる誤りの有無を判断する誤り検出 手段と、

前記フラッシュメモリから読み出したデータに含まれる誤りを訂正する誤り訂正手段と

前記誤り検出手段で誤りが含まれていると判断されたデータだけが、前記誤り訂正手段 で誤り訂正が行われるように制御する制御手段とを備え、

前記誤り検出手段の個数が並行してアクセスされる前記フラッシュメモリの個数と同数 であり、前記誤り訂正手段の個数が並行してアクセスされる前記フラッシュメモリの個数 より少ないことを特徴とするメモリコントローラ。

### 【請求項2】

前記誤り訂正手段には2個以上の前記誤り検出手段が割り当てられ、いずれかの前記誤 り検出手段で誤りが含まれていると判断されたデータは、該誤り検出手段に割り当てられ ている前記誤り訂正手段で誤り訂正が行われることを特徴とする請求項1に記載のメモリ コントローラ。

### 【請求項3】

前記制御手段は、前記ホストシステムから読み出される順番が先のデータの誤り訂正が

先に行われるように制御することを特徴とする請求項1又は2に記載のメモリコントロー ラ。

### 【請求項4】

請求項1乃至3のいずれか1項記載のメモリコントローラと、

複数個のフラッシュメモリとを備えるフラッシュメモリシステム。

### 【請求項5】

ホストシステムから与えられる指示情報に応じて、複数個のフラッシュメモリに対する 並行したアクセスを制御するフラッシュメモリの制御方法であって、

前記フラッシュメモリから読み出したデータに含まれる誤りの有無を判断する誤り検出 ステップと、

前記フラッシュメモリから読み出したデータに含まれる誤りを訂正する誤り訂正ステッ プとを有し、

前記誤り検出ステップは、並行してアクセスされる前記フラッシュメモリから読み出し たデータに対して並行して行われ、

前記誤り訂正ステップは、並行してアクセスされる前記フラッシュメモリから読み出し たデータに対して予め設定された順番で行われることを特徴とするフラッシュメモリの制 御方法。

### 【請求項6】

前記順番は、前記ホストシステムから読み出される順番が先のデータの誤り訂正が先に 行われるように設定されていることを特徴とする請求項5に記載のフラッシュメモリの制 御方法。

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は、メモリコントローラ及び当該メモリコントローラを備えるフラッシュメモリ システム、並びにフラッシュメモリの制御方法に関する。

### 【背景技術】

### [0002]

従来、フラッシュメモリから読み出したデータに含まれる誤りを検出、訂正する方法と して、誤り訂正符号(エラーコレクションコード)に基づいて誤りを検出、訂正する方法 が知られている。この誤り訂正符号としては、リードソロモン符号、ハミング符号、BC H符号等がある。リードソロモン符号を用いたエラー訂正では、ハミング符号を用いたエ ラー訂正よりエラー訂正処理能力が高く、効率的なエラー訂正が可能であった。(例えば 特許文献1参照)。また、複数のフラッシュメモリを有する半導体ディスク装置では、 複数のフラッシュメモリに並行してアクセスすることにより、アクセス速度の高速化がな されていた。(例えば、特許文献2参照)。

【特許文献1】特開2006-127441

【特許文献2】特開2004-240993

### 【発明の開示】

### 【発明が解決しようとする課題】

### [0003]

複数個のフラッシュメモリに並行してアクセスする場合、並行してアクセスされるフラ ッシュメモリと同数のエラー訂正回路が必要になる。従って、複数個のフラッシュメモリ に並行してアクセスする半導体ディスク装置では、エラー訂正回路の回路規模が大きくな ってしまっていた。

## [0004]

本発明は、かかる実情に鑑み、複数個のフラッシュメモリに並行してアクセスする場合 に、エラー訂正回路の回路規模が増大するのを抑制することができるメモリコントローラ 、当該メモリコントローラを備えるフラッシュメモリシステム、並びにフラッシュメモリ の制御方法を提供しようとするものである。

10

20

30

40

#### 【課題を解決するための手段】

### [0005]

上記目的を達成するために、本発明によるメモリコントローラは、ホストシステムから与えられる指示情報に応じて、複数個のフラッシュメモリに対する並行したアクセスを制御するメモリコントローラであって、前記フラッシュメモリから読み出したデータに含まれる誤りの有無を判断する誤り検出手段と、前記誤り検出手段で誤りが含まれていると判断されたデータだけが、前記誤り訂正手段で誤り訂正が行われるように制御する制御手段とを備え、前記誤り検出手段の個数が並行してアクセスされる前記フラッシュメモリの個数と同数であり、前記誤り訂正手段の個数が並行してアクセスされる前記フラッシュメモリの個数より少ないことを特徴とする。

[0006]

このような構成にすることにより、誤り訂正手段に対応する回路の回路規模が増大するのを抑制することができる。また、本発明は、リードソロモン符号、BCH符号等の符号化方式で生成された誤り訂正符号に基づいて誤り検出と誤り訂正を行う回路のように、誤り検出手段に対応する回路と誤り訂正手段に対応する回路を分離して形成することができれば、誤り訂正符号の符号化方式に限定されることなく実施することができる。

#### [00007]

尚、前記誤り訂正手段には2個以上の前記誤り検出手段が割り当てられ、いずれかの前記誤り検出手段で誤りが含まれていると判断されたデータは、該誤り検出手段に割り当てられている前記誤り訂正手段で誤り訂正が行われることが好ましい。また、前記制御手段は、前記ホストシステムから読み出される順番が先のデータの誤り訂正が先に行われるように制御することが好ましい。

[0008]

本発明によるフラッシュメモリシステムは、上記いずれかのメモリコントローラと複数 個のフラッシュメモリとを備えることを特徴としている。

#### [0009]

本発明によるフラッシュメモリの制御方法は、ホストシステムから与えられる指示情報に応じて、複数個のフラッシュメモリに対する並行したアクセスを制御するフラッシュメモリの制御方法であって、前記フラッシュメモリから読み出したデータに含まれる誤りの有無を判断する誤り検出ステップと、前記フラッシュメモリから読み出したデータに含まれる誤りを訂正する誤り訂正ステップとを有し、前記誤り検出ステップは、並行してアクセスされる前記フラッシュメモリから読み出したデータに対して並行して行われ、前記誤り訂正ステップは、並行してアクセスされる前記フラッシュメモリから読み出したデータに対して予め設定された順番で行われることを特徴とする。

[0010]

尚、前記順番は、前記ホストシステムから読み出される順番が先のデータの誤り訂正が 先に行われるように設定されていることが好ましい。

### 【発明の効果】

### [0011]

本発明のメモリコントローラ及びフラッシュメモリシステムによれば、誤り訂正するための回路の個数を並行してアクセスされる前記フラッシュメモリの個数より少なくしたので、複数個のフラッシュメモリに並行してアクセスする構成で、エラー訂正回路の回路規模が増大するのを抑制することができる。

#### [0012]

また、本発明のフラッシュメモリの制御方法によれば、誤りを検出する処理は、並行してアクセスされる複数個のフラッシュメモリから読み出したデータに対して並行して行われ、誤りを訂正する処理は、並行してアクセスされる複数個のフラッシュメモリから読み出したデータに対して予め設定された順番で行われる。従って、誤りを検出する処理で読み出したデータに誤りが含まれていた場合は、予め設定された順番で効率的に誤りの訂正

10

20

30

40

を行うことができる。

【発明を実施するための最良の形態】

#### [0013]

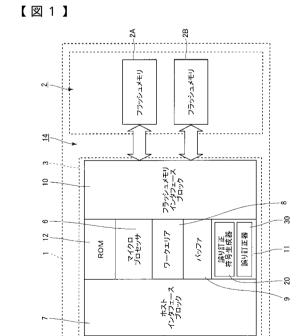

以下、本発明の実施の形態を、図面を参照して説明する。図1は、本発明に係るフラッシュメモリシステム1を概略的に示すブロック図である。図1に示すように、フラッシュメモリシステム1は、フラッシュメモリ2と、それを制御するメモリコントローラ3で構成されている。

### [0014]

なお、フラッシュメモリシステム 1 は、外部バス 1 3 を介してホストシステム 4 と接続される。ホストシステム 4 は、ホストシステム 4 の全体の動作を制御するための C P U (Central Processing Unit)、フラッシュメモリシステム 1 との情報の授受を担うコンパニオンチップ等から構成される。ホストシステム 4 は、例えば、文字、音声、あるいは画像情報等の種々の情報を処理するパーソナルコンピュータやデジタルスチルカメラをはじめとする各種情報処理装置であってもよい。

#### [0015]

フラッシュメモリ 2 は複数チップのNAND型フラッシュメモリからなり、本実施の形態ではフラッシュメモリ 2 Aとフラッシュメモリ 2 Bの 2 チップからなる。NAND型フラッシュメモリは、不揮発性メモリであり、レジスタとメモリセルとの間でデータの複写を行って、データの書き込み又は読み出しを行う。

### [0016]

メモリセルアレイは、複数のメモリセル群と、ワード線とを備える。各メモリセル群は、複数のメモリセルが直列に接続されたものである。ワード線は、メモリセル群の特定のメモリセルを選択するためのものである。このワード線を介して選択されたメモリセルとレジスタとの間で、データの複写、即ち、レジスタから選択されたメモリセルへの複写又は選択されたメモリセルからレジスタへのデータの複写が行われる。

### [0017]

メモリセルアレイを構成するメモリセルは、2つのゲートを備えたMOSトランジスタによって構成される。ここで、一方のゲートが、コントロールゲートと呼ばれ、他方のゲートがフローティングゲートと呼ばれている。このフローティングゲートに電荷(電子)を注入若しくはこのフローティングゲートから電荷(電子)を排出することによって、データの書き込み若しくはデータの消去が行われる。

### [0018]

又、このフローティングゲートは、周囲を絶縁体で囲まれているので、注入された電子は長期間にわたって保持される。なお、フローティングゲートに電子を注入するときは、コントロールゲートが高電位側となる高電圧をコントロールゲートとフローティングゲート間に印加する。また、フローティングゲートから電子を排出するときは、コントロールゲートが低電位側となる高電圧をコントロールゲートとフローティングゲート間に印加する。

### [0019]

ここで、フローティングゲートに電子が注入されている状態が書き込み状態であり、論理値「0」に対応する。また、フローティングゲートから電子が排出されている状態が消去状態であり、論理値「1」に対応する。

### [0020]

NAND型フラッシュメモリでは、データ読み出し動作及びデータ書き込み動作はページ単位で行われ、データ消去動作はブロック(物理ブロック)単位でおこなわれる。尚、物理ブロックは複数のページで構成され、大ブロックの場合は、1個のページが4セクタ(2048バイト)のユーザ領域と64バイトの冗長領域とで構成され、1個の物理ブロックが64個のページで構成されている。又、小ブロックの場合は、1個のページが1セクタ(512バイト)のユーザ領域と16バイトの冗長領域とで構成され、1個の物理ブロックが32個のページで構成されている。又、大ブロックの場合は、ユーザ領域を4分

10

20

30

40

割した 5 1 2 バイトの領域をサブページといい、各サブページに冗長領域内の一部の領域 を割り当てて使用する。従って、大ブロックの場合は、 1 個の物理ブロックに 2 5 6 個の サブページが含まれている。

### [0021]

一方、ホストシステム 4 側のアドレス空間は、セクタ(5 1 2 バイト)単位で分割した 領域に付けた通番である L B A (Logical Block Address)で管理されている。メモリコントローラ 3 内では、複数個のセクタをまとめたものを論理ブロックとし、この論理ブロックと物理ブロックの対応関係を管理することにより、ホストシステム 4 側の論理アドレスをフラッシュメモリ 2 側の物理アドレスに変換している。

### [0022]

ユーザ領域はホストシステム 4 から与えられるデータを記憶するための領域である。冗長領域は、誤り訂正符号(ECC: Error Correcting Code)、論理アドレス情報、ブロックステータス(フラグ)等の付加データを記憶するための領域である。誤り訂正符号は、ユーザ領域に記憶されているデータに含まれる誤りを検出、訂正するためのデータであり、誤り訂正符号生成器 2 0 の詳細については後述する。

### [0023]

論理アドレス情報は、ユーザ領域に有効なデータが格納されている物理ブロックと対応関係にある論理ブロックを特定するための情報である。なお、ユーザ領域に有効なデータが格納されていない物理ブロックについては、そのブロックの冗長領域に、論理アドレス情報は格納されていない。したがって、冗長領域に論理アドレス情報が格納されているか否かを判定することにより、その冗長領域が含まれている物理ブロックに有効なデータが格納されているか否かを判定することができる。つまり、冗長領域に論理アドレス情報が格納されていないとき、その物理ブロックには、有効なデータが格納されていないと判断する。

### [0024]

尚、論理ブロックと物理ブロックとの対応関係は通常、アドレス変換テーブルによって管理される。このアドレス変換テーブルは、各物理ブロックの冗長領域に記憶されている論理アドレス情報に基づいて作成される。

### [0025]

ブロックステータス (フラグ) は、ブロックの良否を示すフラグである。正常にデータの書き込み等を行うことができないブロックは、不良ブロックと判別され、冗長領域には、不良ブロックであることを示すブロックステータス (フラグ)が書き込まれる。

### [0026]

このようなフラッシュメモリ2A、2Bは、それぞれメモリコントローラ3から、データ、アドレス情報、内部コマンド等を受信して、データの読み出し処理、書き込み処理、 ブロック消去処理、転送処理等の各処理を行う。

### [0027]

ここで、内部コマンドとは、メモリコントローラ 3 がフラッシュメモリ 2 A、 2 B に処理の実行を指示するためのコマンドであり、フラッシュメモリ 2 A、 2 B は、メモリコントローラ 3 から与えられる内部コマンドに従って動作する。これに対して、外部コマンドとは、ホストシステム 4 がフラッシュメモリシステム 1 に対して処理の実行を指示するためのコマンドである。

# [0028]

メモリコントローラ 3 は、図 1 に示すように、マイクロプロセッサ 6 と、ホストインタフェースブロック 7 と、ワークエリア 8 と、バッファ 9 と、フラッシュメモリインタフェースブロック 1 0 と、ECCブロック 1 1 と、ROM (Read Only Memory) 1 2 と、から構成される。これら機能ブロックによって構成されるメモリコントローラ 3 は、一つの半導体チップ上に集積される。以下に各機能ブロックについて説明する。

### [0029]

50

10

20

30

10

20

30

40

50

マイクロプロセッサ 6 は、 R O M 1 2 に記憶されているプログラムに従って、メモリコントローラ 3 の全体の動作を制御する。例えば、マイクロプロセッサ 6 は、各種処理等を定義したコマンドセットを R O M 1 2 から読み出してフラッシュメモリインタフェースプロック 1 0 に処理を実行させる

[0030]

ホストインタフェースブロック 7 は、ホストシステム 4 との間の、データ、アドレス情報、ステータス情報、外部コマンド等の授受を行なう。ホストシステム 4 よりフラッシュメモリシステム 1 に供給されるデータ等は、ホストインタフェースブロック 7 を入口としてフラッシュメモリシステム 1 の内部(例えば、バッファ 9 )に取り込まれる。また、フラッシュメモリシステム 1 からホストシステム 4 に供給されるデータ等は、ホストインタフェースプロック 7 を出口としてホストシステム 4 に供給される。

[0031]

ワークエリア 8 は、フラッシュメモリ 2 の制御に必要なデータが一時的に格納される作業領域であり、複数の S R A M (Static Random Access Memory) セルによって構成される。

[0032]

バッファ9は、フラッシュメモリ2A、2Bから読み出されたデータ及びフラッシュメモリ2A、2Bに書き込むべきデータを一時的に蓄積する。フラッシュメモリ2A、2Bから読み出されたデータは、ホストシステム4が受け取り可能な状態となるまでバッファ9に保持される。フラッシュメモリ2A、2Bに書き込むべきデータは、それぞれフラッシュメモリ2A、2Bが書き込み可能な状態となるまでバッファ9に保持される。

[0033]

フラッシュメモリインタフェースブロック10は、内部バス14を介して、フラッシュメモリ2とデータ、アドレス情報、ステータス情報、内部コマンド等の授受を行う。

[0034]

ECCブロック11は、フラッシュメモリ2A、2Bに書き込むデータ(ユーザデータ)に付加される誤り訂正符号(ECC)を生成するとともに、フラッシュメモリ2から読み出したデータに付加された誤り訂正符号(ECC)に基づいて、読み出したデータに含まれる誤りを検出・訂正する。本実施の形態では、リードソロモン符号方式で符号化された誤り訂正符号(以下、リードソロモン符号の誤り訂正符号と言う)を用いて、誤りの検出と訂正を行っている。

[0035]

ROM12は、マイクロプロセッサ6による処理の手順を定義するプログラムを格納する不揮発性の記憶素子である。例えば、アドレス変換テーブルの作成等の処理手順を定義するプログラムが格納される。

[0036]

ここで、ECCブロック11の詳細について説明する。ECCブロック11は、データを書き込む際に用いられる誤り訂正符号生成器20と、データを読み出す際に用いられる誤り訂正器30とを有する。誤り訂正符号生成器20は、入力されたデータに基づいて、リードソロモン符号の誤り訂正符号(ECC)を生成する。誤り訂正器30は、フラッシュメモリ2A、2Bから読み出した誤り訂正符号(ECC)に基づいてエラー訂正処理を行う。

[0037]

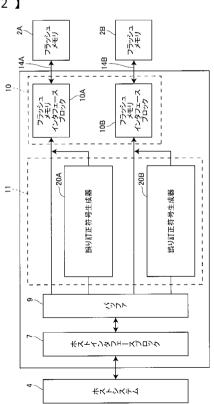

誤り訂正符号生成器20の動作を、図2を参照して説明する。図2は、ECCブロック11の構成のうち誤り訂正符号生成器20(20A、20B)のみを記載している。誤り訂正符号生成器20A、20Bは受け取ったユーザデータからエラー訂正のための誤り訂正符号(ECC)を生成する。ここで、バッファ9からフラッシュメモリ2Aに転送されるユーザデータは、誤り訂正符号生成器20Aに入力される。一方、バッファ9からフラッシュメモリ2Bに転送されるユーザデータは、誤り訂正符号生成器20Bに入力される

10

20

30

40

50

。つまり、フラッシュメモリ2Aに書き込まれるユーザデータの誤り訂正符号(ECC)は誤り訂正符号生成器20Aで生成され、フラッシュメモリ2Bに書き込まれるユーザデータの誤り訂正符号(ECC)は誤り訂正符号生成器20Bで生成される。尚、誤り訂正符号生成器20Aで生成された誤り訂正符号(ECC)は、フラッシュメモリ2Aの冗長領域に書き込まれ、誤り訂正符号生成器20Bで生成された誤り訂正符号(ECC)は、フラッシュメモリ2Bの冗長領域に書き込まれる。

#### [0038]

尚、バッファ9からフラッシュメモリ2Aへのユーザデータの転送とバッファ9からフラッシュメモリ2Bへのユーザデータの転送は並行して行われる。フラッシュメモリ2Aに接続されている内部バス14Aとフラッシュメモリ2Bに接続されている内部バス14Bは独立していることが好ましいが、双方に接続されている内部バス14を時分割で使用してもよい。時分割で共用する場合は、例えば、フラッシュメモリ2Aに転送する1セクタのデータに含まれるデータと、フラッシュメモリ2Bに転送する1セクタのデータに含まれるデータを、1バイト単位で交互に転送する。

#### [0039]

誤り符号生成器 2 0 A、 2 0 Bに入力されたユーザデータは、リードソロモン符号の所定のシンボル長に変換される。この所定のシンボル長に変換されたシンボルデータに基づいてリードソロモン符号の誤り訂正符号(ECC)が生成される。更に、消去状態のときの不整合を回避するため、ユーザ領域に書き込まれる 1 セクタのユーザデータの全ビットが消去状態(論理値の"1")になるような変換処理が施される。従って、フラッシュメモリ 2 A、 2 Bの冗長領域には、この変換処理が施された誤り訂正符号(ECC)が書き込まれる。又、この変換処理が施された誤り訂正符号(ECC)が書き込まれる。又、この変換処理が施された誤り訂正符号(ECC)は、所定のシンボルデータからバイト単位のデータに変換されてフラッシュメモリ 2 A、 2 Bの冗長領域に書き込まれる。

### [0040]

本実施の形態では、ユーザデータを10ビットのシンボルデータに変換して誤り訂正符号(ECC)を生成している。この変換では、1セクタ(4096ビット)のユーザデータを順次連結した後、10ビット単位で切り出している。又、1セクタ(4096ビット)のユーザデータの末尾に4ビットのダミーデータを付加することにより、1セクタ(4096ビット)のユーザデータを410シンボルのシンボルデータに変換している。又、誤り訂正符号生成器20A、20Bでは、8シンボルの誤り訂正符号(ECC)が生成されるように設定されている。この8シンボルの誤り訂正符号(ECC)に基づいて、5シンボルの誤り検出と4シンボルの誤り訂正をすることができる。

### [0041]

以上に説明したように、ホストシステムから与えられたユーザデータは、バッファ9に保持された後、フラッシュメモリ2A又はフラッシュメモリ2Bに転送される。フラッシュメモリ2Aに書き込まれるユーザデータについては、フラッシュメモリインタフェースプロック10A及び内部バス14Aを介してフラッシュメモリ2Aに転送されると共に、誤り訂正符号生成器20Aに入力される。誤り訂正符号生成器20Aは、入力されたユーザデータに基づいて8シンボルの誤り訂正符号(ECC)を生成する。この8シンボルの誤り訂正符号(ECC)は、上述の変換処理が施された後、10バイトのデータとしてフラッシュメモリ2Aに転送される。

# [0042]

一方、フラッシュメモリ2Bに書き込まれるユーザデータについては、フラッシュメモリインタフェースプロック10B及び内部バス14Bを介してフラッシュメモリ2Bに転送されると共に、誤り訂正符号生成器20Bに入力される。誤り訂正符号生成器20Bは、入力されたユーザデータに基づいて8シンボルの誤り訂正符号(ECC)を生成する。この8シンボルの誤り訂正符号(ECC)は、上述の変換処理が施された後、10バイトのデータとしてフラッシュメモリ2Bに転送される。

#### [0043]

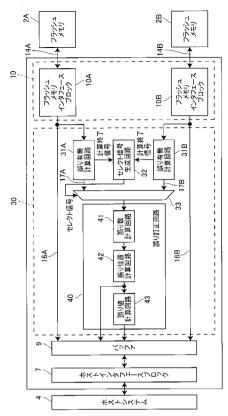

次に、誤り訂正器 3 0 の動作を、図 3 を参照して説明する。図 3 は、ECCブロック 1 1 の構成のうち誤り訂正器 3 0 のみが記載されている。この誤り訂正器 3 0 は、誤り有無計算回路 3 1 A、 3 1 B、セレクト信号生成回路 3 2、インタフェースセレクタ 3 3 及び誤り訂正回路 4 0 で構成されている。更に、誤り訂正回路 4 0 は、誤り数計算回路 4 1、誤り位置計算回路 4 2 及び誤り値計算回路 4 3 で構成されている。

#### [0044]

フラッシュメモリ2A、2Bからユーザデータを読み出すときには、変換処理が施されている誤り訂正符号(ECC)も読み出される。フラッシュメモリ2Aのユーザ領域から読み出されたユーザデータは、内部バス14A及びフラッシュメモリインタフェースプロック10Aを介してバッファ9に転送されると共に、誤り有無計算回路31Aに入力される。更に、読み出したユーザデータが記憶されていたユーザ領域と対応する冗長領域から変換処理が施されている誤り訂正符号(ECC)が読み出され、誤り有無計算回路31Aに入力される。一方、フラッシュメモリ2Bのユーザ領域から読み出されたユーザデータは、内部バス14B及びフラッシュメモリインタフェースプロック10Bを介してバッファ9に転送されると共に、誤り有無計算回路31Bに入力される。更に、読み出したユーザデータが記憶されていたユーザ領域と対応する冗長領域から変換処理が施されている誤り訂正符号(ECC)が読み出され、誤り有無計算回路31Bに入力される。

### [0045]

誤り有無計算回路31A、31Bでは、入力されたユーザデータが10ビットのシンボルデータに変換される。つまり、入力された1セクタ(4096ビット)のユーザデータは、順次連結された後、10ビット単位で切り出される。又、1セクタ(4096ビット)のユーザデータの末尾には4ビットのダミーデータが付加され、1セクタ(4096ビット)のユーザデータは410シンボルのシンボルデータに変換される。同様に変換処理が施されている誤り訂正符号(ECC)は、10ビットのシンボルデータに変換される。又、変換処理が施されている誤り訂正符号(ECC)については、変換処理が施される前の誤り訂正符号(ECC)に戻す逆変換処理も施される。

#### [0046]

誤り有無計算回路31A、31Bは、この410シンボルのシンボルデータと8シンボルの誤り訂正符号(ECC)に基づいて誤り有無を判断する計算処理を実行する。この誤り有無を判断する計算処理も、誤り有無計算回路31A、31Bで並行して行われる。

### [0047]

ユーザデータ又は誤り訂正符号(ECC)に対応する418シンボルに誤りが含まれているときは、誤り有無計算回路31A、31Bから出力される計算結果を示す情報が、インタフェースセレクタ33を介して誤り数計算回路41に入力される。尚、セレクト信号生成回路32は、ホストシステム4から読み出される順番が先のユーザデータの誤り訂正が先に行われるように誤り数計算回路41に入力する順番を制御する。例えば、フラッシュメモリ2A、2Bから並行して読み出されたユーザデータの双方に誤りが含まれていたときに、フラッシュメモリ2Aから読み出されたユーザデータが先にホストシステム4から読み出される場合は、誤り有無計算回路31Aから出力される情報が先に誤り数計算回路41に入力されるように順番を制御する。

#### [0048]

誤り数計算回路 4 1 は、誤り有無計算回路 3 1 A から与えられた情報に基づいて誤りの有るシンボルデータの数を求める計算処理を実行する。この計算処理で、誤りの有るシンボルデータの数が 5 シンボル以上であると判断された場合は、ここで誤り訂正の処理が中止される。誤りの有るシンボルデータの数が 4 シンボル以下であると判断された場合は、誤り数計算回路 4 1 から出力される計算結果を示す情報が誤り位置計算回路 4 2 に入力される。

### [0049]

誤り位置計算回路42は、誤り数計算回路41から与えられた情報に基づいて、ユーザ

10

20

30

40

データ又は誤り訂正符号(ECC)に対応する418シンボルのうちのどのシンボルデータ(何番目のシンボルデータ)に誤りが有るかを求める計算処理を実行する。誤り位置計算回路42から出力される計算結果を示す情報は、誤り値計算回路43に入力される。

### [0050]

誤り値計算回路43は、誤り位置計算回路42から与えられた情報に基づいて、誤りが有るシンボルデータの正しい値を求める計算処理を実行する。誤りが有るシンボルデータの正しい値が求められると、バッファ9に保持されているユーザデータの誤り訂正が行われる。ここでは、誤り位置計算回路42で求められた誤りが有るシンボルデータに対応する部分のユーザデータの値が、誤り値計算回路43で求めた正しい値に訂正される。つまり、誤りが有るシンボルデータがn(1~410)番目のときに、n番目のシンボルデータに対応するビットが正しい値に訂正される。

#### [0051]

以上詳細に説明したように、本実施の形態によるメモリコントローラ3によれば、並行して読み出されるユーザデータ(フラッシュメモリ2 A とフラッシュメモリ2 B から読み出されるユーザデータ)に誤りが含まれているか否かを判断する処理が誤り検出手段である誤り有無計算回路3 1 B で並行して実行される。誤り訂正手段である誤り訂正回路40は、誤り数計算回路41、誤り位置計算回路42及び誤り値計算回路43で構成されている。フラッシュメモリ2 A から読み出されるユーザデータの誤り訂正とフラッシュメモリ2 B から読み出されるユーザデータの誤り訂正は、いずれも誤り訂正回路40で実行される。つまり、誤り検出手段は、並行してアクセスされるフラッシュメモリと同数設けられているが、誤り訂正手段の数は並行してアクセスされるフラッシュメモリの数より少なくなっている。従って、誤り検出手段と誤り訂正手段とで構成される誤り訂正器の回路規模を削減することができる。

#### [0052]

尚、並行して読み出されたユーザデータの双方、つまり、フラッシュメモリ2Aから読み出されるユーザデータとフラッシュメモリ2Bから読み出されるユーザデータの双方に誤りが含まれていた場合、ホストシステム4から読み出される順番で誤り訂正が行われる。並行して読み出されたユーザデータのいずれか一方にだけ誤りが含まれていた場合、誤りが含まれていた側のユーザデータの誤り訂正だけが実行される。

### [0053]

本発明によるメモリコントローラ及びフラッシュメモリシステム、並びにフラッシュメモリの制御方法は上述した実施の形態に限定されず、特許請求の範囲に記載した範囲で種々の変形や改良が可能である。例えば、誤り検出手段(誤り有無計算回路31A、誤り有無計算回路31Bに相当する回路)と誤り訂正手段(誤り訂正回路40に相当する回路)の個数は特に限定されず、誤り訂正手段の数が誤り検出手段の数より少ない構成であればよい。又、誤り訂正符号の方式はリードソロモン符号に限定されず、誤り検出手段と誤り訂正手段とを分離して構成できるBCH符号等の符号化方式であってもよい。

### [0054]

尚、誤り訂正手段で誤り訂正を行う順番は、ホストシステム4から読み出される順番であることが好ましいが、誤り検出手段で先に誤りが検出された側、又は、誤りが含まれているか否かを判断する処理が先に終了した側から順番に誤り訂正を行ってもよい。

#### 【図面の簡単な説明】

### [0055]

【図1】本発明の一実施の形態によるフラッシュメモリシステムの概略構成を示すプロック図である。

【図2】本発明の一実施の形態による誤り訂正符号生成器の動作を説明するためのブロッ ク図である。

【図3】本発明の一実施の形態による誤り訂正器の動作を説明するためのブロック図である。

### 【符号の説明】

10

20

30

40

# [0056]

1 フラッシュメモリシステム

2 A 、 2 B フラッシュメモリ

3 メモリコントローラ

20 誤り訂正符号生成器

3 0 誤り訂正器

ホストシステム

【図2】

# 【図3】

# フロントページの続き

(56)参考文献 特開昭 5 8 - 1 4 3 5 0 0 (JP, A)

特開昭57-127998(JP,A)

特開平09-091206(JP,A)

特開昭62-119800(JP,A)

(58)調査した分野(Int.CI., DB名)

G06F 12/16

G11C 29/42