# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2021-150511 (P2021-150511A)

(43) 公開日 令和3年9月27日(2021.9.27)

| (51) Int.Cl. |                 |           | FΙ      |          |          | テーマコート     | (参考)   |

|--------------|-----------------|-----------|---------|----------|----------|------------|--------|

| HO1L         | 27/11582        | (2017.01) | HO1L    | 27/11582 |          | 5F033      |        |

| HO1L         | <i>2</i> 7/00   | (2006.01) | HO1L    | 27/00    | 3 O 1 C  | 5F048      |        |

| HO1L         | <i>27/11575</i> | (2017.01) | HO1L    | 27/11575 |          | 5F083      |        |

| HO1L         | <i>27/11573</i> | (2017.01) | HO1L    | 27/11573 |          | 5 F 1 O 1  |        |

| HO1L         | 21/336          | (2006.01) | HO1L    | 29/78    | 371      |            |        |

|              |                 |           | 審査請求 未請 | 家 請求項    | の数 12 01 | 」 (全 25 頁) | 最終頁に続く |

(21) 出願番号 (22) 出願日 特願2020-49532 (P2020-49532) 令和2年3月19日 (2020.3.19) (71) 出願人 318010018

キオクシア株式会社

東京都港区芝浦三丁目1番21号

(74)代理人 100119035

弁理士 池上 徹真

(74)代理人 100141036

弁理士 須藤 章

(74)代理人 100178984

弁理士 高下 雅弘

(72)発明者 佐貫 朋也

東京都港区芝浦三丁目1番21号 キオク

シア株式会社内

(72) 発明者 中塚 圭祐

東京都港区芝浦三丁目1番21号 キオク

シア株式会社内

最終頁に続く

# (54) 【発明の名称】半導体記憶装置

# (57)【要約】 (修正有)

【課題】それぞれに集積回路が形成された2枚のウェハを貼り合わせることにより高い機能を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置であるフラッシュメモリ100は、制御チップ101と、メモリチップ102を含む。制御チップ101は、第1の半導体基板10、第1の層間領域12、複数の第1の金属パッド14a~14 f及び制御回路16を含む。制御回路16は、第1~第4のセンスアンプ回路18a~18dを含む。メモリチップ102は、第2の半導体基板20、第2の層間領域22、複数の第2の金属パッド24a~24f、メモリセルアレイ26、素子分離絶縁層28、裏面絶縁層30、貫通電極32、ターミナルパッド34、パッシベーション膜36、第1~第4のビット線BL1~BL4、第1~第8のプレーン、ワード線コンタクト領域及びターミナルパッド領域を含む。

【選択図】図1

#### 【特許請求の範囲】

# 【請求項1】

第1の半導体基板と、

第1のパッドと、

第2のパッドと、

半導体回路と、

#### を含む第1のチップと、

第2の半導体基板と、

前記第1のパッドに接する第3のパッドと、

前記第2のパッドに接する第4のパッドと、

前記第2の半導体基板と前記第1のチップとの間に設けられたメモリセルアレイであっ て、

第1の方向に、互いに離間して繰り返し配置された複数のゲート電極層を含み、前記第 1の方向に垂直な第2の方向に第1の幅を有し、前記第2の方向に第1の間隔で離間して 繰り返し配置された複数の積層体と、

前記積層体の中に設けられ、前記第1の方向に延び、前記第1の方向に垂直な面内にお いて、規則的に配置された複数の半導体層と、

前 記 複 数 の 半 導 体 層 の 内 の 少 な く と も 一 つ と 、 前 記 複 数 の ゲ ー ト 電 極 層 の 内 の 少 な く と も一つとの間に設けられた電荷蓄積層と、

を含むメモリセルアレイと、

前 記 メ モ リ セ ル ア レ イ と 前 記 第 1 の チ ッ プ と の 間 に 設 け ら れ 、 前 記 第 2 の 方 向 に 延 び 、 前記複数の半導体層の内の一つである第1の半導体層に電気的に接続された第1の配線と

前 記 メ モ リ セ ル ア レ イ と 前 記 第 1 の チ ッ プ と の 間 に 設 け ら れ 、 前 記 第 2 の 方 向 に 延 び 、 前記第1の配線の延長線上に位置し、前記第1の配線と離間し、前記複数の半導体層の内 の別の一つである第2の半導体層に電気的に接続された第2の配線と、

を含む第2のチップと、

を備える半導体記憶装置。

# 【請求項2】

前記第1の配線と前記第2の配線の間の部分と、前記第2の半導体基板との間に、前記 複数の積層体の内の少なくとも一つが位置する請求項1記載の半導体記憶装置。

# 【請求項3】

前記第1の配線と前記第2の配線の間の距離は、前記第1の幅の3倍よりも小さい請求 項2記載の半導体記憶装置。

# 【請求項4】

前記第1の配線と前記第2の配線の間の部分と、前記第2の半導体基板との間に、前記 複 数 の 積 層 体 の 内 の 隣 り 合 う 2 つ の 積 層 体 の 間 の 部 分 が 位 置 し 、 前 記 第 1 の 配 線 と 前 記 第 2の配線の間の距離は、前記第1の幅よりも小さい請求項1記載の半導体記憶装置。

前記第1の配線と前記第2の配線の間の距離は、前記第1の間隔よりも小さい請求項4 記載の半導体記憶装置。

#### 【請求項6】

前記第1の配線は前記第3のパッドに電気的に接続され、前記第2の配線は前記第4の パッドに電気的に接続される請求項1ないし請求項5いずれか一項記載の半導体記憶装置

# 【請求項7】

前 記 第 1 の パ ッ ド 及 び 前 記 第 2 の パ ッ ド は 前 記 半 導 体 回 路 に 電 気 的 に 接 続 さ れ る 請 求 項 1ないし請求項6いずれか一項記載の半導体記憶装置。

# 【請求項8】

前記第2の半導体基板は、第1の半導体領域と、前記第1の半導体領域と離間した第2

10

20

30

40

の半導体領域を有し、前記第1の半導体層は、前記第1の半導体領域に電気的に接続され、前記第2の半導体層は前記第2の半導体領域に電気的に接続される請求項1ないし請求項7いずれか一項記載の半導体記憶装置。

#### 【請求項9】

前記第1の半導体領域は、前記第2の半導体基板の前記メモリセルアレイの側の第1の面から、前記第2の半導体基板の前記メモリセルアレイの反対側の第2の面まで連続する第1の絶縁層で囲まれる請求項8記載の半導体記憶装置。

## 【請求項10】

前記第2の半導体領域は、前記第1の面から、前記第2の面まで連続する第2の絶縁層で囲まれ、前記第1の絶縁層と前記第2の絶縁層は離間する請求項9記載の半導体記憶装置。

10

#### 【請求項11】

前記第1の半導体領域に電気的に接続される前記半導体層を含む前記メモリセルアレイの第1の領域は、メモリ動作上、第1のプレーンに含まれ、

前記第2の半導体領域に電気的に接続される前記半導体層を含む前記メモリセルアレイの第2の領域は、メモリ動作上、前記第1のプレーンと異なる第2のプレーンに含まれる請求項8記載の半導体記憶装置。

#### 【請求項12】

前記半導体回路は、第1のセンスアンプ回路と第2のセンスアンプ回路とを、更に含み

20

30

前記第1のセンスアンプ回路は、前記第1のパッドに電気的に接続され、

前記第2のセンスアンプ回路は、前記第2のパッドに電気的に接続される請求項1ない し請求項11いずれか一項記載の半導体記憶装置。

【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明の実施形態は、半導体記憶装置に関する。

# 【背景技術】

#### [0002]

貼合技術は、それぞれに集積回路が形成された2枚のウェハを貼り合わせることにより、高機能又は高集積の半導体デバイスを実現する。例えば、メモリセルアレイが形成された半導体ウェハと、メモリセルアレイを制御する制御回路が形成された半導体ウェハを貼り合わせる。その後、貼り合わされた半導体ウェハを、ダイシングにより複数のチップに分割することで、高機能又は高集積の半導体メモリが実現できる。

【先行技術文献】

#### 【特許文献】

# [ 0 0 0 3 ]

【 特 許 文 献 1 】 特 開 2 0 1 9 - 1 4 0 1 7 8 号 明 細 書

# 【発明の概要】

【発明が解決しようとする課題】

40

# [0004]

本発明が解決しようとする課題は、高い機能を実現する半導体記憶装置を提供することにある。

# 【課題を解決するための手段】

#### [00005]

実施形態の半導体記憶装置は、第1の半導体基板と、第1のパッドと、第2のパッドと、半導体回路と、を含む第1のチップと、第2の半導体基板と、前記第1のパッドに接する第3のパッドと、前記第2の半導体基板と前記第1のチップとの間に設けられたメモリセルアレイであって、第1の方向に、互いに離間して繰り返し配置された複数のゲート電極層を含み、前記第1の方向に垂直な第2の

方向に第1の幅を有し、前記第2の方向に第1の間隔で離間して繰り返し配置された複数の積層体と、前記積層体の中に設けられ、前記第1の方向に延び、前記第1の方向に垂直な面内において、規則的に配置された複数の半導体層と、前記複数の半導体層の内の少なくとも一つとの間に設けられた電荷蓄積層と、を含むメモリセルアレイと、前記メモリセルアレイと前記第1のチップとの間に設けられ、前記第2の方向に延び、前記メモリセルアレイと前記第1のチップとの間に電気的に接続された第1の配線と、前記メモリセルアレイと前記第1のチップとの間に設けられ、前記第2の方向に延び、前記第1の配線の延長線上に位置し、前記第1の配線と離間し、前記複数の半導体層の内の別の一つである第2の半導体層に電気的に接続された第2の配線と、を含む第2のチップと、を備える。

【図面の簡単な説明】

- [0006]

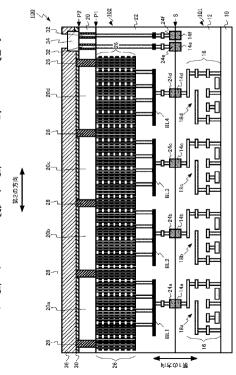

- 【図1】第1の実施形態の半導体記憶装置の模式断面図。

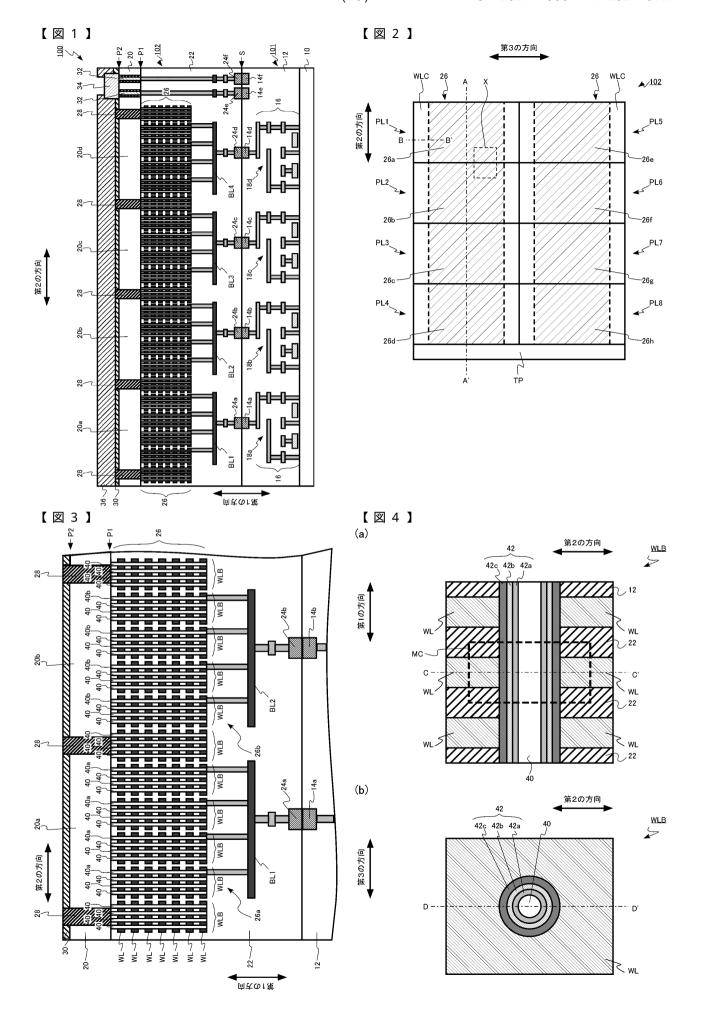

- 【図2】第1の実施形態の半導体記憶装置の配置図。

- 【図3】第1の実施形態の半導体記憶装置の模式断面図。

- 【図4】第1の実施形態の半導体記憶装置の模式断面図。

- 【図5】第1の実施形態の半導体記憶装置の模式図。

- 【図6】第1の実施形態の半導体記憶装置の配置図。

- 【図7】第1の実施形態の半導体記憶装置の模式断面図。

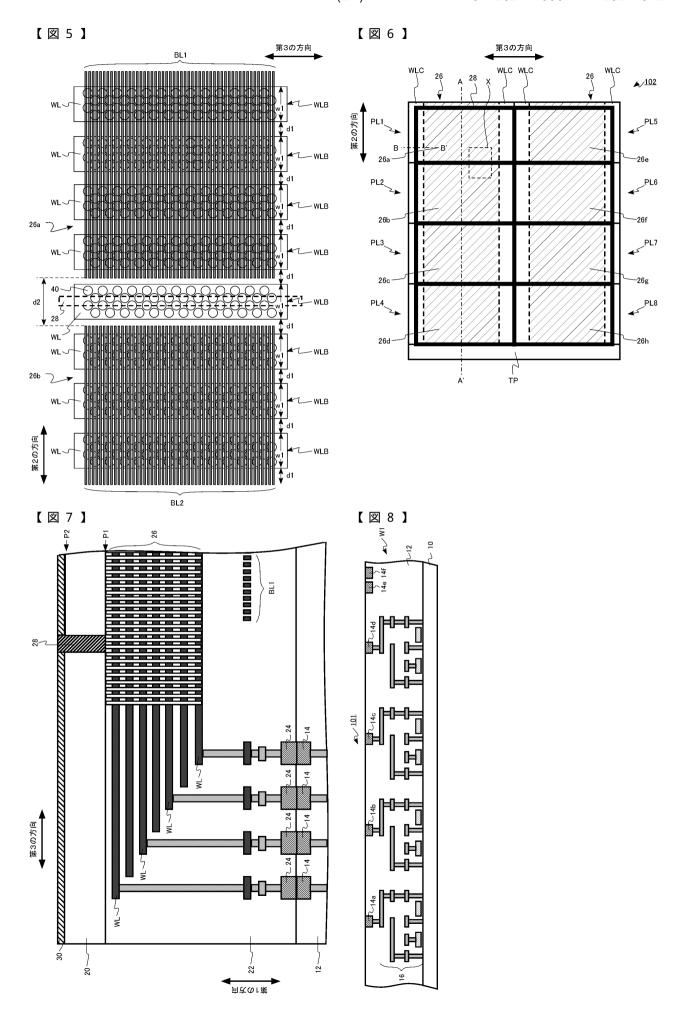

- 【図8】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

- 【 図 9 】 第 1 の 実 施 形 態 の 半 導 体 記 憶 装 置 の 製 造 方 法 を 示 す 模 式 断 面 図 。

- 【図10】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

- 【図11】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

- 【図12】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

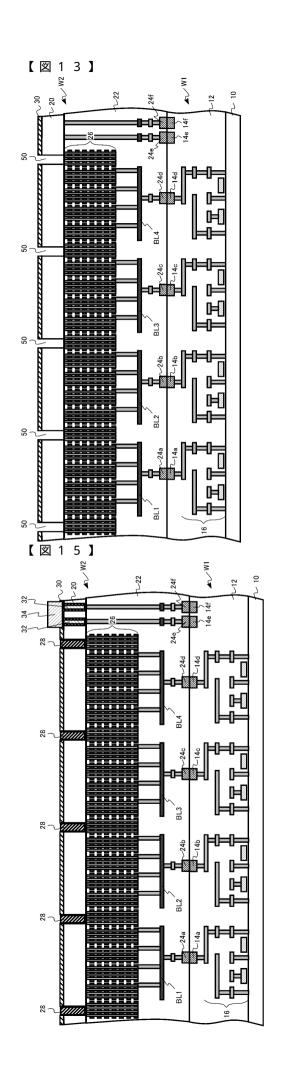

- 【図13】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

- 【図14】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

- 【図15】第1の実施形態の半導体記憶装置の製造方法を示す模式断面図。

- 【図16】第2の実施形態の半導体記憶装置の模式図。

- 【図17】第2の実施形態の半導体記憶装置の配置図。

- 【図18】第3の実施形態の半導体記憶装置の模式図。

- 【図19】第4の実施形態の半導体記憶装置の配置図。

- 【図20】第4の実施形態の半導体記憶装置の変形例の配置図。

- 【発明を実施するための形態】

- [0007]

以下、図面を参照しつつ本発明の実施形態を説明する。なお、以下の説明では、同一又は類似の部材などには同一の符号を付し、一度説明した部材などについては適宜その説明を省略する。

[0008]

また、本明細書中、便宜上「上」、又は、「下」という用語を用いる場合がある。「上」、又は、「下」とは、例えば、図面内での相対的位置関係を示す用語である。「上」、又は、「下」という用語は、必ずしも、重力に対する位置関係を規定する用語ではない。 【 0 0 0 9 】

本明細書中の半導体記憶装置を構成する部材の化学組成の定性分析及び定量分析は、例えば、二次イオン質量分析法(Secondary Ion Mass Spectrometry:SIMS)、エネルギー分散型 X 線分光法(Energy Dispersive X-ray Spectroscopy:EDX)により行うことが可能である。また、半導体記憶装置を構成する部材の厚さ、部材間の距離等の測定には、例えば、透過型電子顕微鏡(Transmission Electron Microscope:TEM)又は走査型電子顕微鏡(Scanning Electron Microscope:SEM)を用いることが可能である。

10

20

30

40

## [0010]

# (第1の実施形態)

## [0011]

第 1 の実施形態の半導体記憶装置は、フラッシュメモリ 1 0 0 である。フラッシュメモリ 1 0 0 は、メモリセルを 3 次元的に配置した 3 次元 N A N D フラッシュメモリである。

# [ 0 0 1 2 ]

図1は、第1の実施形態の半導体記憶装置の模式断面図である。図2は、第1の実施形態の半導体記憶装置の配置図である。図2には、フラッシュメモリ100のメモリチップ102のプレーン、メモリセルアレイ、ワード線コンタクト領域、及び、ターミナルパッド領域の配置が示される。図1は、図2のAA、断面である。

#### [ 0 0 1 3 ]

第1の実施形態のフラッシュメモリ100は、制御チップ101と、メモリチップ10 2を含む。制御チップ101は、第1のチップの一例である。メモリチップ102は、第 2のチップの一例である。

# [0014]

制御チップ101は、第1の半導体基板10、第1の層間領域12、複数の第1の金属パッド14a、14b、14c、14d、14e、14f、及び、制御回路16を含む。制御回路16は、第1のセンスアンプ回路18a、第2のセンスアンプ回路18b、第3のセンスアンプ回路18c、及び、第4のセンスアンプ回路18dを含む。

### [0015]

第1の金属パッド14aは、第1のパッドの一例である。第1の金属パッド14bは、 第2のパッドの一例である。制御回路16は、半導体回路の一例である。

#### [0016]

以下、第1の金属パッド14a、14b、14c、14d、14e、14fを簡略化のため、単に、第1の金属パッド14a~14fと記述する場合がある。また、第1の金属パッド14a~14f、及び、これらと同様の機能を有する金属パッドを、総称して、単に、第1の金属パッド14と記述する場合がある。

#### [0017]

メモリチップ102は、第2の半導体基板20、第2の層間領域22、複数の第2の金属パッド24a、24b、24c、24d、24e、24f、メモリセルアレイ26、素子分離絶縁層28、裏面絶縁層30、貫通電極32、ターミナルパッド34、パッシベーション膜36、第1のビット線BL1、第2のビット線BL2、第3のビット線BL3、第4のビット線BL4、第1のプレーンPL1、第2のプレーンPL2、第3のプレーンPL3、第4のプレーンPL4、第5のプレーンPL5、第6のプレーンPL6、第7のプレーンPL7、第8のプレーンPL8、ワード線コンタクト領域WLC、及び、ターミナルパッド領域TPを含む。

10

20

30

40

#### [ 0 0 1 8 ]

第2の金属パッド24aは、第3のパッドの一例である。第2の金属パッド24bは、 第 4 のパッドの一例である。第 1 のビット線 B L 1 は、第 1 の配線の一例である。第 2 の ビット線BL2は、第2の配線の一例である。

## [0019]

以下、第2の金属パッド24a、24b、24c、24d、24e、24fを簡略化の ため、単に、第2の金属パッド24a~24fと記述する場合がある。また、第2の金属 パッド24a~24f、及び、これらと同様の機能を有する金属パッドを、総称して、単 に、第2の金属パッド24と記述する場合がある。

# [0020]

また、 第 1 のビット線 B L 1 、 第 2 のビット線 B L 2 、 第 3 のビット線 B L 3 、 及び、 第4のビット線BL4、及び、これらと同様の機能を有するビット線を、総称して、単に 、ビット線BLと記述する場合がある。

# [0021]

第 2 の 半 導 体 基 板 2 0 は 、 第 1 の プレート 領 域 2 0 a 、 第 2 の プレート 領 域 2 0 b 、 第 3 のプレート領域 2 0 c 、 及び、 第 4 のプレート領域 2 0 d を有する。 第 1 のプレート領 域 2 0 a は、第 1 の半導体領域の一例である。第 2 のプレート領域 2 0 b は、第 2 の半導 体領域の一例である。

# [0022]

メモリセルアレイ26は、複数のワード線ブロックWLB、複数のチャネル層40、及 び、図1、2には、図示しない電荷蓄積層42を含む。複数のワード線ブロックWLBは 、それぞれ、複数のワード線WLを含む。

## [0023]

メモリセルアレイ 2 6 は、第 1 の領域 2 6 a 、第 2 の領域 2 6 b 、第 3 の領域 2 6 c 、 第 4 の 領 域 2 6 d 、 第 5 の 領 域 2 6 e 、 第 6 の 領 域 2 6 f 、 第 7 の 領 域 2 6 g 、 及 び、 第 8の領域26hを含む。

### [0024]

素子分離絶縁層28は、第1の絶縁層の一例である。

# [0025]

ワード線ブロックWLBは、積層体の一例である。チャネル層40は、半導体層の一例 である。ワード線WLは、ゲート電極層の一例である。

# [0026]

複数のチャネル層 4 0 は、第 1 のチャネル層 4 0 a 、第 2 のチャネル層 4 0 b を含む。 複数 の チャ ネ ル 層 4 0 は 、 半 導 体 層 の 一 例 で あ る 。 第 1 の チャ ネ ル 層 4 0 a は 、 第 1 の 半 導 体 層 の 一 例 で あ る 。 第 2 の チ ャ ネ ル 層 4 0 b は 、 第 2 の 半 導 体 層 の 一 例 で あ る 。

#### [0027]

図 1 に示すように、制御チップ 1 0 1 とメモリチップ 1 0 2 は、貼合面 S ( s t i c k ing interface)で接合している。

制御チップ101は、メモリチップ102を制御する機能を有する。

# [0029]

第 1 の 半 導 体 基 板 1 0 は 、 例 え ば 、 単 結 晶 シ リ コ ン で あ る 。

#### [0030]

第 1 の半導体基板 1 0 とメモリチップ 1 0 2 との間に、制御回路 1 6 が設けられる。制 御回路16は、複数のトランジスタ等の半導体素子、及び、半導体素子間を電気的に接続 する多層配線層を含む。

#### [0031]

制御回路16には、第1のセンスアンプ回路18a、第2のセンスアンプ回路18b、 第 3 のセンスアンプ回路 1 8 c 、及び、第 4 のセンスアンプ回路 1 8 d が含まれる。第 1 のセンスアンプ回路18a、第2のセンスアンプ回路18b、第3のセンスアンプ回路1 10

20

30

40

8 c 、 及 び 、 第 4 の セ ン ス ア ン プ 回 路 1 8 d は 、 メ モ リ チ ッ プ 1 0 2 の メ モ リ セ ル か ら 読 み出されるデータを増幅し、メモリセルのデータを検出する機能を有する。

## [0032]

第1の層間領域12は、第1の半導体基板10のメモリチップ102側に設けられる。 第 1 の層間領域 1 2 は、制御回路 1 6 の複数のトランジスタ等の半導体素子、及び、多層 配線層の電気的絶縁を確保する機能を有する。第1の層間領域12は、例えば、酸化シリ コンを含む。

## [0033]

第 1 の 金 属 パ ッ ド 1 4 a ~ 1 4 f は 、 第 1 の 層 間 領 域 1 2 の メ モ リ チ ッ プ 1 0 2 側 に 設 けられる。 第 1 の金属パッド 1 4 a ~ 1 4 f は、第 1 の層間領域 1 2 の中に設けられる。 [0034]

第 1 の 半 導 体 基 板 1 0 と 第 1 の 金 属 パ ッ ド 1 4 a ~ 1 4 f と の 間 に 、 制 御 回 路 1 6 が 設 けられる。

# [0035]

第 1 の金属パッド 1 4 a ~ 1 4 f は、制御回路 1 6 に電気的に接続される。第 1 の金属 パッド14aは、第1のセンスアンプ回路18aに電気的に接続される。第1の金属パッ ド 1 4 b は、 第 2 のセンスアンプ回路 1 8 b に電気的に接続される。第 1 の金属パッド 1 4 c は、第 3 のセンスアンプ回路 1 8 c に電気的に接続される。第 1 の金属パッド 1 4 d は、第4のセンスアンプ回路18日に電気的に接続される。

# [0036]

第 1 の 金属 パッド 1 4 a ~ 1 4 f は、第 2 の 金属 パッド 2 4 a ~ 2 4 f に 接 する。第 1 の金属パッド14a~14fは、制御チップ101とメモリチップ102とを電気的に接 続する機能を有する。

#### [0037]

第 1 の金属パッド 1 4 a ~ 1 4 f は、例えば、銅(Cu)を含む。第 1 の金属パッド 1 4 a ~ 1 4 f は、例えば、銅(Cu)である。

# [0038]

図 1 に示すように、メモリチップ 1 0 2 は、第 2 の半導体基板 2 0 と制御チップ 1 0 1 との間にメモリセルアレイ26を有する。メモリセルアレイ26には、複数のメモリセル が 3 次 元 的 に 積 層 さ れ て い る 。 複 数 の メ モ リ セ ル が 3 次 元 的 に 配 置 さ れ る こ と に よ り 、 大 容量のフラッシュメモリ100が実現できる。

# [0039]

第2の半導体基板20は、第1の面P1と第2の面P2とを有する。第1の面P1は、 メモリセルアレイ26側の面であり、第2の面P2は、メモリセルアレイ26と反対側の 面である。

# [0040]

第2の半導体基板20は、例えば、単結晶シリコンである。

## [0041]

図1に示すように、メモリセルアレイ26と制御チップ101との間に、第1のビット 線 B L 1 、 第 2 の ビット線 B L 2 、 第 3 の ビット線 B L 3 、 及 び 、 第 4 の ビット 線 B L 4 が設けられる。第1のビット線BL1~BL4は、第2の方向に延びる。第1のビット線 BL1~BL4は、それぞれ離間している。

# [0042]

ビット線BLは、メモリセルアレイ26のメモリセルからデータを読み出す機能を有す る。ビット線BLは、例えば、金属である。ビット線BLは、例えば、タングステンや銅 である。

## [0043]

図2に示すように、メモリチップ102は、8個のプレーンを備える。メモリチップ1 0 2 は、第 1 のプレーンPL1、第 2 のプレーンPL2、第 3 のプレーンPL3、第 4 の プレーンPL4、第5のプレーンPL5、第6のプレーンPL6、第7のプレーンPL7

10

20

30

40

、及び、第8のプレーンPL8を備える。

# [0044]

プレーンは、メモリ動作上、同一のプレーンに属する異なるメモリセルに対して、異なるコマンドの同時実行が制限される範囲である。同一のプレーンに属する異なるメモリセルに対しては、同時に異なるコマンドを実行することができない。例えば、同一のプレーンに属する異なるメモリセルに対しては、書き込みコマンド、読み出しコマンド、及び、消去コマンドの中の異なる2つのコマンドを同時に実行することができない。

## [0045]

例えば、第1のプレーンPL1に属する異なるメモリセルに対して、同時に異なるコマンドを実行することができない。一方、第1のプレーンPL1に属するメモリセルと、第2のプレーンPL2に属するメモリセルに対しては、異なるコマンドを実行することができる。したがって、プレーンの数を増やすことで、フラッシュメモリのバンド幅を広げることが可能となる。

# [0046]

第1のプレーンPL1、第2のプレーンPL2、第3のプレーンPL3、及び、第4のプレーンPL4は、第2の方向に並んで配置される。メモリセルアレイ26は、第1のプレーンPL1と第2のプレーンPL2との境界、第2のプレーンPL2と第3のプレーンPL3と第4のプレーンPL4との境界を跨いで、配置される。メモリセルアレイ26の中で、第1のプレーンPL1、第2のプレーンPL2、第3のプレーンPL3、及び、第4のプレーンPL4に属する領域が、それぞれ、第1の領域26a、第2の領域26b、第3の領域26c、及び、第4の領域26dである。

## [0047]

第5のプレーンPL5、第6のプレーンPL6、第7のプレーンPL7、及び、第8のプレーンPL8は、第2の方向に並んで配置される。メモリセルアレイ26は、第5のプレーンPL5と第6のプレーンPL6との境界、第6のプレーンPL6と第7のプレーンPL7との境界、及び、第7のプレーンPL7と第8のプレーンPL8との境界を跨いで、配置される。メモリセルアレイ26の中で、第5のプレーンPL5、第6のプレーンPL6、第7のプレーンPL7、及び、第8のプレーンPL8に属する領域が、それぞれ、第5の領域26e、第6の領域26f、第7の領域26g、及び、第8の領域26hである。

# [0048]

メモリセルアレイ 2 6 の第 3 の方向には、ワード線コンタクト領域W L C が設けられる。第 3 の方向は、第 1 の方向及び第 2 の方向に垂直な方向である。ワード線コンタクト領域W L C には、ワード線W L への電気的接続を得るための構造が形成される。

# [0049]

第1のプレーンPL1、第2のプレーンPL2、第3のプレーンPL3、第4のプレーンPL4、第5のプレーンPL5、第6のプレーンPL6、第7のプレーンPL7、及び、第8のプレーンPL8の第2の方向に、ターミナルパッド領域TPを含む。ターミナルパッド領域TPには、制御チップ101への電気的接続を得るための構造が形成される。

# [0050]

図 1 に示す、貫通電極 3 2 、及び、ターミナルパッド 3 4 が、ターミナルパッド領域 T P に設けられる。

# [0051]

図3は、第1の実施形態の半導体記憶装置の模式断面図である。図3は、図1の一部を拡大した図である。

#### [0052]

メモリセルアレイ26は、複数のワード線ブロックWLBを含む。ワード線ブロックWLBは、第1の方向に互いに離間して繰り返し配置された複数のワード線WLを含む。第1の方向は、第2の半導体基板20の第1の面P1の法線方向である。

10

20

30

40

. .

#### [0053]

1個のワード線ブロックWLBは、例えば、メモリ動作上の消去単位であるブロックを構成するが、それに限らず、ブロックは、複数のワード線ブロックWBLによって構成されても良い。

# [0054]

ワード線WLは、メモリセルアレイ26に含まれるメモリセルトランジスタのゲート電極層として機能する。ワード線WLとワード線WLとの間は、第2の層間領域22で電気的に分離される。ワード線プロックWLBとワード線プロックWLBとの間でワード線WLは分割されている。

# [0055]

ワード線 W L は、 導電層である。 ワード線 W L は、 例えば、 金属である。 ワード線 W L は、 例えば、 タングステンである。

#### [0056]

ワード線ブロックWLBは、第1の方向に垂直な第2の方向に、一定の間隔で繰り返し配置される。

## [0057]

なお、ワード線ブロックWLBとワード線ブロックWLBとの間に、図示しない板状の 導電層を設けることも可能である。例えば、導電層を第2の半導体基板20に電気的に接 続させることで、メモリセルアレイ26の制御チップ101側から、第2の半導体基板2 0への電気的導通を得ることが可能になる。

#### [0058]

メモリセルアレイ 2 6 は、複数のチャネル層 4 0 を含む。チャネル層 4 0 は、ワード線ブロックW L B の中に設けられる。チャネル層 4 0 は、第 1 の方向に延びる。チャネル層 4 0 は、第 1 の方向に垂直な面内において、規則的に配置される。

#### [0059]

チャネル層 4 0 の一端は、第 2 の半導体基板 2 0 に電気的に接続される。チャネル層 4 0 の他端は、ビット線 B L に電気的に接続される。チャネル層 4 0 は、メモリセルアレイ 2 6 に含まれるメモリセルトランジスタのチャネル領域として機能する。

# [0060]

チャネル層40は、半導体である。チャネル層40は、例えば、多結晶シリコンである

# [0061]

第1のビット線BL1は、第2の方向に延びる。第1のビット線BL1は、複数のチャネル層40の内の少なくとも一つである第1のチャネル層40aに電気的に接続される。第1のチャネル層40aは、第1のプレート領域20aに電気的に接続される。

#### [0062]

また、第2のビット線BL2は、第2の方向に延びる。第2のビット線BL2は、複数のチャネル層40の内の少なくとも一つである第2のチャネル層40bに電気的に接続される。第2のチャネル層40bは、第2のプレート領域20bに電気的に接続される。

## [0063]

図4は、第1の実施形態の半導体記憶装置の模式断面図である。図4は、メモリセルアレイ26の一部の模式断面図である。図4は、一つのワード線ブロックWLBの一部の模式断面図である。図4(a)は図4(b)のDD′断面、図4(b)は図4(a)のCC′断面である。図4(a)中、点線枠で囲まれる領域が、1個のメモリセルMCである。

#### [0064]

電荷蓄積層42は、ワード線WLとチャネル層40との間に設けられる。電荷蓄積層42は、例えば、トンネル絶縁膜42a、電荷トラップ膜42b、及び、ブロック絶縁膜42cを有する。トンネル絶縁膜42a、電荷トラップ膜42b、及び、ブロック絶縁膜42cは、例えば、それぞれ酸化シリコン膜、窒化シリコン膜、酸化シリコン膜である。

# [0065]

50

10

20

30

10

20

30

40

50

電荷蓄積層42に蓄積される電荷の量に応じて、メモリセルMCのトランジスタの閾値電圧が変化する。この閾値電圧の変化を利用することで、1個のメモリセルMCがデータを記憶することが可能となる。

[0066]

チャネル層40は、例えば、円柱状である。チャネル層40は、例えば、内側に絶縁層が設けられた円筒状であっても構わない。

[0067]

図5は、第1の実施形態の半導体記憶装置の模式図である。図5は、第1の方向に垂直な面から見た、ワード線WL、ワード線ブロックWLB、チャネル層40、素子分離絶縁層28、第1のビット線BL1、及び、第2のビット線BL2の位置関係を示す。

[0068]

図 5 は、図 2 中の領域 X の拡大図である。図 5 は、第 1 のプレーン P L 1 と第 2 のプレーン P L 2 との境界を含む図である。

[0069]

ワード線ブロックWLBは、第2の方向に第1の幅(図5中のw1)を有する。ワード線ブロックWLBは、第2の方向に第1の間隔(図5中のd1)で離間して、繰り返し配置される。ワード線ブロックWLBは、第2の方向に一定の周期、すなわち、w1+d1の周期で配置される。

[0070]

ワード線ブロックWLBの周期的な配置は、メモリセルアレイ26の第2の方向の一方の端部から、他方の端部まで、保たれる。例えば、第1のプレーンPL1の端部から、第4のプレーンPL4の端部まで、各プレーンの間で途切れることなく、ワード線ブロックWLBの周期的な配置が保たれる。

[0071]

チャネル層40は、第1の方向に垂直な面内において、規則的に配置される。チャネル層40は、ワード線ブロックWLBの中にある。

[0072]

第1のビット線 B L 1 及び第2のビット線 B L 2 は、第2の方向に延びる。第2のビット線 B L 2 は、第1のビット線 B L 2 と、第1のビット線 B L 1 は離間する。第2のビット線 B L 2 と、第1のビット線 B L 1 は、物理的にも電気的にも分割されている。

[0073]

分割された第1のビット線 B L 1 と第 2 のビット線 B L 2 との間の部分には、複数のワード線ブロックW L B の内の一つが位置する。第1のビット線 B L 1 と第 2 のビット線 B L 2 との間の部分と、第 2 の半導体基板 2 0 との間には、ワード線ブロックW L B が一つ存在する。

[0074]

第1のビット線BL1と第2のビット線BL2との間の部分に位置するワード線ブロックWLBの中のチャネル層40は、第1のビット線BL1及び第2のビット線BL2のいずれにも電気的に接続されない。第1のビット線BL1と第2のビット線BL2との間の部分に位置するワード線ブロックWLBの中のメモリセルは、メモリセルとして動作しない、いわゆるダミーセルである。

[0075]

第1のビット線 B L 1 と第2のビット線 B L 2 との間の距離(図5 中の d 2 )は、例えば、ワード線ブロックW L B の第1の幅w 1 の 3 倍よりも小さい。第1のビット線 B L 1 と第2のビット線 B L 2 との間の距離(図5 中の d 2 )は、例えば、ワード線ブロックW L B の第1の幅w 1 の 2 倍よりも小さい。

[0076]

第1のビット線 B L 1 は、第1のプレーン P L 1 に属する。第2のビット線 B L 2 は、第2のプレーン P L 2 に属する。

#### [0077]

第1のビット線 B L 1 は、制御チップ 1 0 1 の第 1 のセンスアンプ回路 1 8 a に電気的に接続される。第2のビット線 B L 2 は、制御チップ 1 0 1 の第2のセンスアンプ回路 1 8 b に電気的に接続される。

## [0078]

第1のビット線 B L 1 と第2のビット線 B L 2 との間の部分に位置するワード線ブロックW L B の第2の半導体基板 2 0 の側に、素子分離絶縁層 2 8 が設けられる。例えば、第1のビット線 B L 1 と第2のビット線 B L 2 との間の部分に位置するワード線ブロックW L B の中の、少なくとも一部のチャネル層 4 0 が、素子分離絶縁層 2 8 に接する。

# [0079]

図 6 は、第 1 の実施形態の半導体記憶装置の配置図である。図 6 には、フラッシュメモリ 1 0 0 のメモリチップ 1 0 2 の素子分離絶縁層の配置が示される。

#### [0800]

素子分離絶縁層28は、メモリセルアレイ26の、第1の領域26a、第2の領域26b、第3の領域26c、第4の領域26d、第5の領域26e、第6の領域26f、第7の領域26g、及び、第8の領域26hを囲むように設けられる。素子分離絶縁層28は、格子状に設けられる。

#### [ 0 0 8 1 ]

図1に示すように、メモリチップ102の第2の半導体基板20は、第1のプレート領域20a、第2のプレート領域20b、第3のプレート領域20c、及び、第4のプレート領域20dを有する。第1のプレート領域20aと第2のプレート領域20bとの間、第2のプレート領域20bと第3のプレート領域20cとの間、第3のプレート領域20cと第4のプレート領域20dとの間は、素子分離絶縁層28で分離される。第1のプレート領域20aと第2のプレート領域20bと第3のプレート領域20cとの間、第3のプレート領域20cと第4のプレート領域20dとの間は、素子分離絶縁層28で物理的及び電気的に分離される。

### [0082]

素子分離絶縁層28は、第2の半導体基板20のメモリセルアレイ26側の第1の面P1から、第2の半導体基板20のメモリセルアレイ26の反対側の第2の面P2まで連続して設けられる。素子分離絶縁層28は、第2の半導体基板20を貫通する。

### [0083]

素子分離絶縁層28は、絶縁体である。素子分離絶縁層28は、例えば、酸化シリコンである。

# [0084]

第 1 のプレート領域 2 0 a 、第 2 のプレート領域 2 0 b 、第 3 のプレート領域 2 0 c 、及び、第 4 のプレート領域 2 0 d は、メモリ動作上、それぞれ、第 1 のプレーン P L 1、第 2 のプレーン P L 2 、第 3 のプレーン P L 3 、及び、第 4 のプレーン P L 4 に属する。

図3に示すように、メモリセルアレイ26の第1の領域26aに含まれるチャネル層40は、第1のプレート領域20aに電気的に接続される。第1のプレート領域20aに電気的に接続されるチャネル層40に、第1のチャネル層40aが含まれる。

# [0086]

[0085]

また、メモリセルアレイ 2 6 の第 2 の領域 2 6 b に含まれるチャネル層 4 0 は、第 2 のプレート領域 2 0 b に電気的に接続される。第 2 のプレート領域 2 0 b に電気的に接続されるチャネル層 4 0 に、第 2 のチャネル層 4 0 b が含まれる。

# [0087]

図 1 に示すように、第 2 の金属パッド 2 4 a ~ 2 4 f は、第 2 の層間領域 2 2 のメモリチップ 1 0 2 側に設けられる。第 2 の金属パッド 2 4 a ~ 2 4 f は、第 2 の層間領域 2 2 の中に設けられる。

# [ 0 0 8 8 ]

10

20

30

第 2 の半導体基板 2 0 と第 2 の金属パッド 2 4 a ~ 2 4 f との間に、メモリセルアレイ 2 6 が設けられる。

[0089]

第2の層間領域22は、第2の半導体基板20の制御チップ101側に設けられる。第 2の半導体基板20は、制御チップ101との間に、第2の層間領域22を挟む。

[0090]

第2の層間領域22は、メモリセルアレイ26の電気的絶縁を確保する機能を有する。 第2の層間領域22は、例えば、酸化シリコンを含む。

[0091]

第2の金属パッド24a~24fは、メモリセルアレイ26に電気的に接続される。第2の金属パッド24aは、第1のビット線BL1に電気的に接続される。第2の金属パッド24bは、第2のビット線BL2に電気的に接続される。第2の金属パッド24cは、第3のビット線BL3に電気的に接続される。第2の金属パッド24dは、第4のビット線BL4に電気的に接続される。

[0092]

第2の金属パッド24a~24fは、第1の金属パッド14a~14fに接する。第2の金属パッド24aは、第1の金属パッド14aに接する。第2の金属パッド24bは、第1の金属パッド14bに接する。第2の金属パッド24cは、第1の金属パッド14cに接する。第2の金属パッド24dは、第1の金属パッド14dに接する。

[0093]

第2の金属パッド24a~24fは、第1の金属パッド14a~14fに電気的に接続される。第2の金属パッド24aは、第1の金属パッド14aに電気的に接続される。第2の金属パッド24bは、第1の金属パッド14bに電気的に接続される。第2の金属パッド24cは、第1の金属パッド14dに電気的に接続される。第2の金属パッド24dは、第1の金属パッド14dに電気的に接続される。

[0094]

第 2 の金属パッド 2 4 a ~ 2 4 f は、メモリチップ 1 0 2 と制御チップ 1 0 1 とを電気的に接続する機能を有する。

[0095]

第 2 の 金属 パッド 2 4 a ~ 2 4 f は、 例えば、銅( C u )を含む。 第 2 の 金属 パッド 2 4 a ~ 2 4 f は、 例えば、銅( C u )である。

[0096]

図7は、第1の実施形態の半導体記憶装置の模式断面図である。図7は、図2のBB′ 断面である。図7は、ワード線コンタクト領域WLCの断面図である。

[0097]

ワード線コンタクト領域WLCでは、メモリセルアレイ26から第3の方向に延びるワード線WLが、階段構造を形成している。第2の金属パッド24から延びる導電層により、第2の金属パッド24とワード線WLとが電気的に接続される。第2の金属パッド24は、それぞれ、第1の金属パッド14に接する。

[0098]

メモリセルアレイ26の第2の半導体基板20側に、素子分離絶縁層28が設けられる。なお、素子分離絶縁層28が設けられる位置は、ビット線BLが接続されるチャネル層40よりチップ端部側であれば、特に、限定されない。例えば、素子分離絶縁層28が設けられる位置は、ワード線WLの階段構造の第2の半導体基板20側であっても構わない

[0099]

裏面絶縁層30は、第2の半導体基板20の上に設けられる。裏面絶縁層30は、第2の半導体基板20の第2の面P2に接して設けられる。裏面絶縁層30は、例えば、酸化シリコンである。

[0100]

50

10

20

30

パッシベーション膜36は、裏面絶縁層30の上に設けられる。パッシベーション膜36は、裏面絶縁層30に接して設けられる。パッシベーション膜36は、例えば、ポリイミドである。

## [0101]

次に、第1の実施形態の半導体記憶装置の製造方法の一例について説明する。図8、図9、図10、図11、図12、図13、図14、図15は、第1の実施形態の半導体記憶装置の製造方法を示す模式断面図である。

# [0102]

最初に、第1の半導体基板10の上に、複数の制御チップ101となる領域を有する第1のウェハW1を製造する(図8)。制御チップ101となる領域には、制御回路16が形成される。第1のウェハW1の表面には、第1の金属パッド14a~14fが露出する

# [0103]

次に、第2の半導体基板20の上に、複数のメモリチップ102となる領域を有する第2のウェハW2を製造する(図9)。メモリチップ102となる領域には、メモリセルアレイ26が形成される。第2のウェハW2の表面には、第2の金属パッド24a~24fが露出する。

# [0104]

次に、第1のウェハW1と第2のウェハW2を、機械的圧力により貼り合わせる(図10、図11)。第1のウェハW1と第2のウェハW2を、第1の金属パッド14a~14fと第2の金属パッド24a~24fが接するように貼り合わせる。次に、第1のウェハW1と第2のウェハW2をアニールする。アニールの温度は、例えば、400 である。アニールにより、第1のウェハW1と第2のウェハW2とが接合する。

#### [0105]

次に、第2の半導体基板20を薄膜化した後、裏面絶縁層30を形成する(図12)。 第2の半導体基板20の薄膜化は、例えば、Chemical Mechanical Polishing法(CMP法)を用いて行う。裏面絶縁層30の形成は、例えば、Chemical Vapor Deposition法(CVD法)による膜の堆積を用いて行う。

# [0106]

次に、第2の半導体基板20に開口部50を形成する(図13)。開口部50は、例えば、リソグラフィ法によるパターニングと、Reactive Ion Etching法(RIE法)によるエッチングを用いて行う。

# [0107]

次に、開口部50に素子分離絶縁層28を形成する(図14)。素子分離絶縁層28は、例えば、CVD法による膜の堆積と、CMP法による膜の平坦化により形成する。

# [0108]

次に、公知のプロセス技術を用いて、貫通電極32、及び、ターミナルパッド34を形成する(図15)。貫通電極32の形成では、図13の半導体基板20に形成する開口部50と同時にRIEなどで開口部を形成することもできる。また、貫通電極32の中の伝導体材料は、図15のPad電極34と同じ材料を同時に埋め込んで形成することもでき、伝導体材料は例えばA1などである。

# [0109]

次に、裏面絶縁層30及びターミナルパッド34の上に、パッシベーション膜を形成する。その後、接合された第1のウェハW1と第2のウェハW2を、例えば、ブレードダイシングにより切断する。第1のウェハW1と第2のウェハW2とを切断することにより、図1に示す、制御チップ101とメモリチップ102とが接合されたフラッシュメモリ100のチップが、複数個製造される。

# [0110]

次に、第1の実施形態の半導体記憶装置の作用及び効果について説明する。

20

10

30

50

#### [0111]

フラッシュメモリは、メモリセルアレイを多数のプレーンに分割することによりバンド幅を大きくすることが可能となる。しかし、プレーンの数が増えると、各プレーンを制御するセンスアンプ回路等の制御回路の数も増え、制御回路のチップ占有率が高くなる。したがって、メモリセルアレイのチップ占有率が低下し、メモリの大容量化が困難となる。

[0112]

第1の実施形態のフラッシュメモリ100は、製造に貼合技術を用いる。制御回路16とメモリセルアレイ26を、異なる2枚のウェハ上に製造した後、2枚のウェハを貼り合わせ、接合させる。接合された2枚のウェハをダイシングすることで、制御回路16を有する制御チップ101と、メモリセルアレイ26を有するメモリチップ102が上下に接合されたチップが製造される。

[0113]

メモリチップ102には、メモリセルアレイ26のみが形成される。したがって、プレーンの数が増えても、メモリセルアレイのチップ占有率の低下が抑制される。よって、バンド幅が広く、大容量のフラッシュメモリが実現できる。

[0114]

また、制御回路16をメモリセルアレイ26と異なるウェハ上に製造するため、熱工程の短いプロセスで制御回路16を形成することができる。このため、制御回路16を構成するトランジスタの微細化が可能になる。したがって、制御回路16の面積の縮小が容易になる。よって、プレーンの数が増え、各プレーンを制御するセンスアンプ回路等の制御回路の数が増えた場合でも、制御チップ101のサイズが増大することを抑制できる。

[0115]

メモリセルアレイを多数のプレーンに分割する場合、プレーン毎にビット線 B L を分割することが必要となる。すなわち、プレーンを構成するメモリセルアレイと、別のプレーンを構成するメモリセルアレイとの境界で、ビット線 B L を分割することが必要となる。

[0116]

例えば、メモリセルアレイを2つのプレーンの間の境界領域で分割する場合を考える。 メモリセルアレイを境界領域で分割すると、境界領域の近傍でパターンの周期性が乱れる。このため、境界領域に隣り合うメモリセルアレイのパターン、例えば、チャネル層形成のためのメモリホールのパターンの形状異常が生じやすくなる。したがって、境界領域に隣り合うメモリセルアレイに、メモリセルとして機能させないダミーセル領域を設ける必要が生じる。ダミーセル領域を設けることは、メモリとして機能するメモリセルアレイのチップ占有率を低下させるため、プレーンの数を多くする上での阻害要因となる。

[ 0 1 1 7 ]

第1の実施形態のフラッシュメモリ100では、2つのプレーンの間の境界領域でメモリセルアレイを分割しない。言い換えれば、2つのプレーンの間で、メモリセルアレイの周期性を変化させない。

[0118]

具体的には、図5に示すように、第1のプレーンPL1と第2のプレーンPL2との境界で、メモリセルアレイ26の周期性が変化しない。第1のプレーンPL1に属するメモリセルアレイ26の第1の領域26aと、第2のプレーンPL2に属するメモリセルアレイ26の第2の領域26bとの間で、メモリセルアレイ26の周期性は変化しない。

[0119]

第1の領域26aから第2の領域26bの間で、ワード線ブロックWLBは、第1の方向に垂直な第2の方向に、一定の第1の幅w1を有し、一定の第1の間隔d1で繰り返し配置される。すなわち、ワード線ブロックWLBは、第2の方向に一定の周期、すなわち、w1+d1の周期で配置される。

[0120]

第 1 のプレーン P L 1 に属する第 1 のビット線 B L 1 と、第 2 のプレーン P L 2 に属する第 2 のビット線 B L 2 は、パターンの周期性に変化がないメモリセルアレイ 2 6 の上で

10

20

30

40

分割される。

# [0121]

第1のプレーンPL1と第2のプレーンPL2との境界で、メモリセルアレイ26は分割されず、メモリセルアレイ26の周期性は変化しない。このため、メモリセルアレイ26にダミーセル領域を設ける必要はない。したがって、プレーンの分割数を多くしても、メモリとして機能するメモリセルアレイ26のチップ占有率が低下することを抑制できる。よって、プレーンの数を多くすることが容易となる。

# [0122]

第1の実施形態のフラッシュメモリ100は、第2の半導体基板20を貫通する素子分離絶縁層28を備える。第2の半導体基板20を貫通する素子分離絶縁層28を備えることで、第1のプレート領域20aと第2のプレート領域20bを短い距離で電気的に分離することが可能となる。このため、第1のプレート領域20aと第2のプレート領域20bとの間の距離が小さくできる。したがって、プレーンとプレーンとの間の素子分離のために、メモリとして機能するメモリセルアレイ26のチップ占有率が低下することを抑制できる。よって、プレーンの数を多くすることが容易となる。

#### [ 0 1 2 3 ]

以上、第1の実施形態によれば、プレーンの数を多くすることで、バンド幅が大きくなり、高い機能を実現する半導体記憶装置が提供できる。

#### [ 0 1 2 4 ]

## (第2の実施形態)

第2の実施形態の半導体記憶装置は、第1の配線と第2の配線の間の部分と、第2の半導体基板との間に、複数の積層体の内の二つが位置し、第1の半導体領域は、第2の半導体基板のメモリセルアレイの反対側の第2の面まで連続する第1の絶縁層で囲まれ、第2の半導体領域は、第1の面から、第2の面まで連続する第2の絶縁層で囲まれ、第1の絶縁層と第2の絶縁層は離間する点で、第1の実施形態の半導体記憶装置と異なっている。以下、第1の実施形態と重複する内容については、一部記述を省略する。

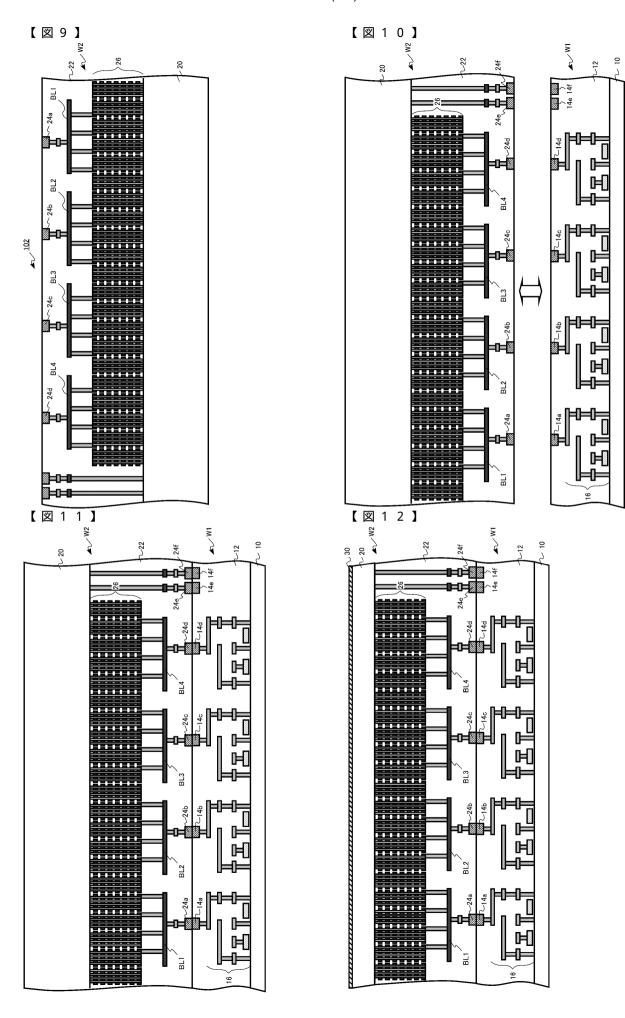

#### [0125]

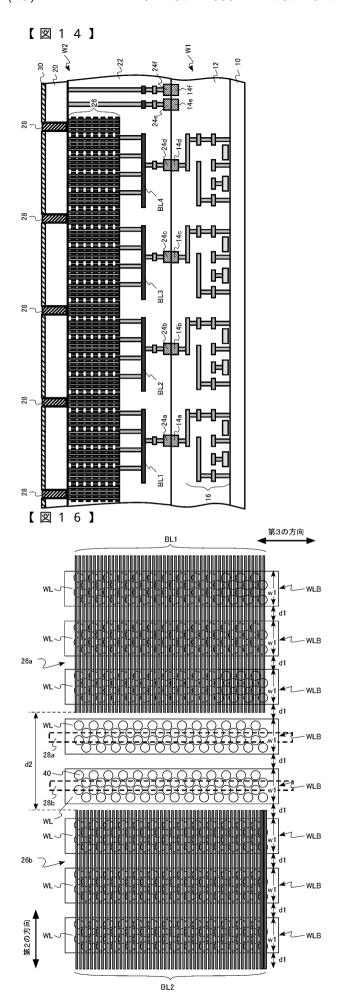

図16は、第2の実施形態の半導体記憶装置の模式図である。

# [0126]

図16は、第1の方向に垂直な面から見た、ワード線WL、ワード線ブロックWLB、チャネル層40、素子分離絶縁層28、第1のビット線BL1、及び、第2のビット線BL2の位置関係を示す。図16は、第1の実施形態の図5に対応する図である。

# [0127]

図 1 7 は、第 2 の実施形態の半導体記憶装置の配置図である。図 1 7 には、メモリチップ 1 0 2 のプレーン、メモリセルアレイ、ワード線コンタクト領域、ターミナルパッド領域、及び、素子分離絶縁層の配置が示される。図 1 7 は、第 1 の実施形態の図 6 に対応する図である。

# [0128]

図 1 6 は、図 1 7 中の領域 Y の拡大図である。図 1 6 は、第 1 のプレーン P L 1 と第 2 のプレーン P L 2 との境界を含む図である。

# [0129]

分割された第1のビット線BL1と第2のビット線BL2との間の部分には、複数のワード線プロックWLBの内の二つが位置する。第1のビット線BL1と第2のビット線BL2との間の部分と、第2の半導体基板20との間には、ワード線プロックWLBが二つ存在する。

#### [0130]

第1のビット線 B L 1 と第 2 のビット線 B L 2 との間の部分に位置する二つのワード線プロックW L B の中のチャネル層 4 0 は、第1のビット線 B L 1 及び第 2 のビット線 B L 2 と 2 のいずれにも電気的に接続されない。第1のビット線 B L 1 と第 2 のビット線 B L 2 と

10

20

30

40

の間の部分に位置する二つのワード線ブロックWLBの中のメモリセルは、メモリセルとして動作しない、いわゆるダミーセルである。

## [0131]

第 1 のビット線 B L 1 と第 2 のビット線 B L 2 との間の距離(図 1 6 中の d 2 )は、例えば、ワード線ブロックW L B の第 1 の幅 w 1 の 3 倍よりも小さい。

#### [0132]

第1のビット線BL1と第2のビット線BL2との間の部分に位置する二つのワード線ブロックWLBの第2の半導体基板20の側に、第1の素子分離絶縁層28aと第2の素子分離絶縁層28bが設けられる。例えば、第1のビット線BL1と第2のビット線BL2との間の部分に位置するワード線ブロックWLBの中の、少なくとも一部のチャネル層40が、第1の素子分離絶縁層28bに接する。

[ 0 1 3 3 ]

図 1 7 に示すように、第 1 の素子分離絶縁層 2 8 a は、メモリセルアレイ 2 6 の、第 1 の領域 2 6 a を囲むように設けられる。第 1 の素子分離絶縁層 2 8 a は、枠状である。

[0134]

第 2 の素子分離 絶 縁 層 2 8 b は、メモリセルアレイ 2 6 の、第 2 の領域 2 6 b を囲むように設けられる。第 2 の素子分離 絶 縁 層 2 8 b は、枠状である。

[0135]

第1の素子分離絶縁層28aと第2の素子分離絶縁層28bは離間する。第1の素子分離絶縁層28aと第2の素子分離絶縁層28bは、分離されている。

[0136]

第1の実施形態の素子分離絶縁層28は、格子状である。素子分離絶縁層28が格子状の場合、3重点又は4重点が形状の特異箇所として存在する。このような、特異箇所では、素子分離絶縁層28の形状不良が生じやすい。

[0137]

第2の実施形態の第1の素子分離絶縁層28a及び第2の素子分離絶縁層28bは枠状であることにより、3重点又は4重点のような形状の特異箇所が存在しない。したがって、第1の素子分離絶縁層28bの形状不良は生じにくい

[0138]

第3の素子分離絶縁層28c、第4の素子分離絶縁層28d、第5の素子分離絶縁層28e、第6の素子分離絶縁層28f、第7の素子分離絶縁層28g、及び、第8の素子分離絶縁層28hは、第1の素子分離絶縁層28a及び第2の素子分離絶縁層28bと同様の構成を備える。したがって、第1の素子分離絶縁層28a及び第2の素子分離絶縁層28bと同様の作用及び効果を有する。

[0139]

以上、第2の実施形態によれば、プレーンの数を多くすることで、バンド幅が大きくなり、高い機能を実現する半導体記憶装置が提供できる。また、形状不良の生じにくい半導体記憶装置が提供できる。

[0140]

(第3の実施形態)

第3の実施形態の半導体記憶装置は、第1の配線と第2の配線の間の部分と、第2の半導体基板との間に、複数の積層体の内の隣り合う2つの積層体の間の部分が位置し、第1の配線と第2の配線の間の距離は、第1の幅よりも小さい点で、第1の実施形態の半導体記憶装置と異なっている。以下、第1の実施形態と重複する内容については、一部記述を省略する。

[0141]

図18は、第3の実施形態の半導体記憶装置の模式図である。

[ 0 1 4 2 ]

図18は、第1の方向に垂直な面から見た、ワード線WL、ワード線ブロックWLB、

10

20

30

40

チャネル層 4 0 、素子分離 絶縁層 2 8 、第 1 のビット線 B L 1 、及び、第 2 のビット線 B L 2 の位置関係を示す。図 1 8 は、第 1 の実施形態の図 5 に対応する図である。

## [0143]

分割された第1のビット線BL1と第2のビット線BL2との間の部分には、複数のワード線ブロックWLBの内の隣り合う2つのワード線ブロックWLBの間の部分が位置する。第1のビット線BL1と第2のビット線BL2との間の部分と、第2の半導体基板20との間には、複数のワード線ブロックWLBの内の隣り合う2つのワード線ブロックWLBの間の部分が位置する。

# [0144]

第1のビット線 B L 1 と第 2 のビット線 B L 2 との間の距離(図 1 8 中の d 2 )は、例えば、ワード線プロックW L B の第 2 の方向の第 1 の間隔(図 1 8 中の d 1 )よりも小さい。

#### [0145]

第1のビット線BL1と第2のビット線BL2との間の部分の第2の半導体基板20の側に、素子分離絶縁層28が設けられる。隣り合う2つのワード線ブロックWLBの間の部分の第2の半導体基板20の側に、素子分離絶縁層28が設けられる。

## [0146]

第3の実施形態では、第1のビット線BL1と第2のビット線BL2を分割する領域、言い換えれば、第1のプレーンPL1と第2のプレーンPL2の境界に、メモリセルとして動作しない、いわゆるダミーセルを設ける必要がない。したがって、メモリとして機能するメモリセルアレイ26のチップ占有率が低下することを抑制できる。よって、プレーンの数を多くすることが容易となる。

## [0147]

以上、第3の実施形態によれば、プレーンの数を多くすることで、バンド幅が大きくなり、高い機能を実現する半導体記憶装置が提供できる。

# [0148]

# (第4の実施形態)

第4の実施形態の半導体記憶装置は、プレーンの数が異なる点で、第1ないし第3の半導体記憶装置と異なっている。以下、第1の実施形態と重複する内容については、一部記述を省略する。

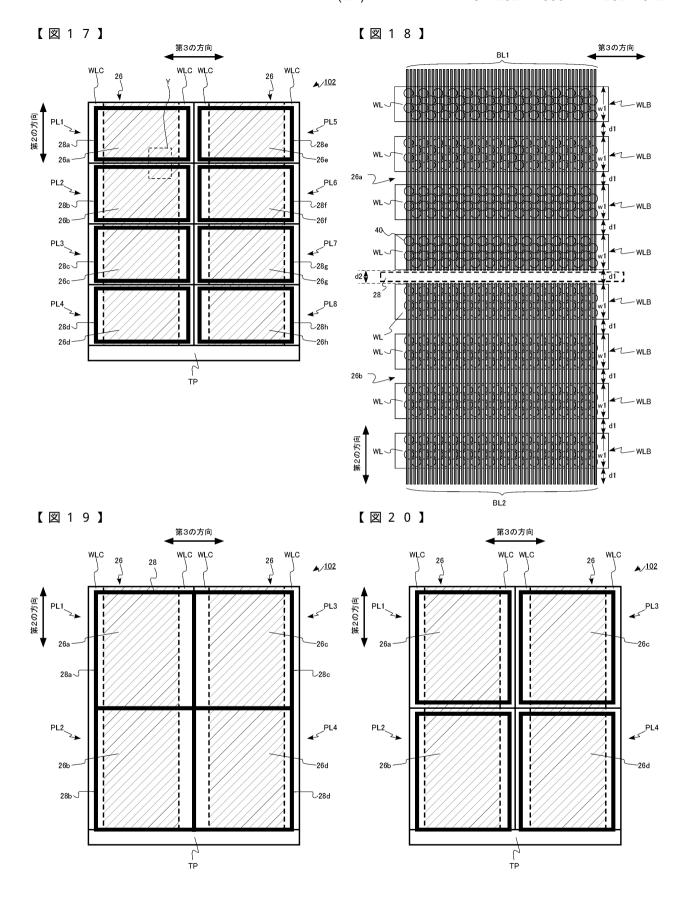

## [0149]

図 1 9 は、第 4 の実施形態の半導体記憶装置の配置図である。図 1 9 には、メモリチップ 1 0 2 のプレーン、メモリセルアレイ、ワード線コンタクト領域、ターミナルパッド領域、及び、素子分離絶縁層の配置が示される。図 1 9 は、第 1 の実施形態の図 6 に対応する図である。

# [0150]

図 1 9 に示すように、メモリチップ 1 0 2 は、 4 個のプレーンを備える。メモリチップ 1 0 2 は、第 1 のプレーンPL1、第 2 のプレーンPL2、第 3 のプレーンPL3、及び 、第 4 のプレーンPL4を備える。

## [0151]

第1のプレーンPL1、第2のプレーンPL2は、第2の方向に並んで配置される。メモリセルアレイ26は、第1のプレーンPL1と第2のプレーンPL2との境界を跨いで、配置される。メモリセルアレイ26の中で、第1のプレーンPL1、及び、第2のプレーンPL2に属する領域が、それぞれ、第1の領域26a、及び、第2の領域26bである。

# [0152]

第3のプレーン P L 3、及び、第4のプレーン P L 4 は、第2の方向に並んで配置される。メモリセルアレイ26は、第3のプレーン P L 3と第4のプレーン P L 4 との境界を跨いで、配置される。メモリセルアレイ26の中で、第3のプレーン P L 3、及び、第4のプレーン P L 4 に属する領域が、それぞれ、第3の領域26 c、及び、第4の領域26

10

20

30

40

dである。

# [0153]

図20は、第4の実施形態の半導体記憶装置の変形例の配置図である。図20は、図1 9に対応する図である。

# [0154]

第 1 の素子分離絶縁層 2 8 a は、メモリセルアレイ 2 6 の、第 1 の領域 2 6 a を囲むように設けられる。第 1 の素子分離絶縁層 2 8 a は、枠状である。

## [0155]

第2の素子分離絶縁層28bは、メモリセルアレイ26の、第2の領域26bを囲むように設けられる。第2の素子分離絶縁層28bは、枠状である。

[0156]

第1の素子分離絶縁層28aと第2の素子分離絶縁層28bは離間する。第1の素子分離絶縁層28aと第2の素子分離絶縁層28bは、分断されている。

## [ 0 1 5 7 ]

第 3 の素子分離 絶縁層 2 8 c は、メモリセルアレイ 2 6 の、第 3 の領域 2 6 c を囲むように設けられる。第 3 の素子分離 絶縁層 2 8 c は、枠状である。

#### [0158]

第4の素子分離絶縁層28dは、メモリセルアレイ26の、第4の領域26dを囲むように設けられる。第4の素子分離絶縁層28dは、枠状である。

## [0159]

第3の素子分離絶縁層28cと第4の素子分離絶縁層28dは離間する。第3の素子分離絶縁層28cと第4の素子分離絶縁層28dは、分断されている。

## [0160]

以上、第4の実施形態及びその変形例によれば、プレーンの数を多くすることで、バンド幅が大きくなり、高い機能を実現する半導体記憶装置が提供できる。

# [0161]

第1の実施形態ないし第4の実施形態において、メモリチップ102のプレーンの数が 8個又は4個の場合を例に説明したが、プレーンの数は2個以上であれば、8個又は4個 に限定されるものではない。

# [0162]

第1の実施形態ないし第4の実施形態において、素子分離絶縁層28が、第2の半導体基板20を貫通する形態を例に説明したが、素子分離絶縁層が第2の半導体基板20を貫通しない形態とすることも可能である。

# [0163]

第1の実施形態ないし第4の実施形態において、貼合面Sを定義している。フラッシュメモリの最終製品では、制御チップ101及びメモリチップ102の貼合面Sの位置が、明瞭に認識できない場合がある。しかし、例えば、第1の金属パッド14と第2の金属パッド24との位置ずれ等から、貼合面Sの位置は確定できる。

# [0164]

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。例えば、一実施形態の構成要素を他の実施形態の構成要素と置き換え又は変更してもよい。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

## 【符号の説明】

# [0165]

10 第1の半導体基板

1 4 a 第 1 の 金属 パッド (第 1 の パッド )

20

10

30

40

```

1 4 b

第1の金属パッド(第2のパッド)

1 6

制御回路(半導体回路)

1 8 a

第1のセンスアンプ回路

1 8 b

第2のセンスアンプ回路

2 0

第2の半導体基板

2 0 a

第1のプレート領域(第1の半導体領域)

2 0 b

第2のプレート領域(第2の半導体領域)

2 4 a

第2の金属パッド(第3のパッド)

2 4 b

第2の金属パッド(第4のパッド)

10

2 6

メモリセルアレイ

2 6 a

第1の領域

2 6 b

第2の領域

2 8

素子分離絶縁層(第1の絶縁層)

2 8 a

第1の素子分離絶縁層(第1の絶縁層)

2 8 b

第2の素子分離絶縁層(第2の絶縁層)

4 0

チャネル層(半導体層)

4 0 a

第1のチャネル層(第1の半導体層)

4 0 b

第2のチャネル層(第2の半導体層)

4 2

電荷蓄積層

20

1 0 0

フラッシュメモリ (半導体記憶装置)

制御チップ(第1のチップ)

1 0 1

1 0 2

メモリチップ(第2のチップ)

B L 1

第1のビット線(第1の配線)

B L 2

第2のビット線(第2の配線)

P 1

第1の面

P 2

第2の面

第1のプレーン

P L 1

P L 2

第2のプレーン

W L

ワード線(ゲート電極層)

30

WLB

ワード線ブロック(積層体)

w 1

第1の幅

d 1

第1の間隔

```

d 2

距離

## フロントページの続き

(51) Int.CI. FΙ テーマコード(参考) H 0 1 L 29/788 (2006.01) H 0 1 L 27/088 Ε H 0 1 L 29/792 H 0 1 L 21/88 Т (2006.01)H 0 1 L 21/8234 (2006.01)H 0 1 L 27/088 (2006.01)H 0 1 L 21/3205 (2006.01)H 0 1 L 21/768 (2006.01) H 0 1 L 23/522 (2006.01)(72) 発明者 前嶋 洋 東京都港区芝浦三丁目1番21号 キオクシア株式会社内 (72)発明者 吉井 謙一郎 東京都港区芝浦三丁目1番21号 キオクシア株式会社内 (72)発明者 前田 高志 東京都港区芝浦三丁目1番21号 キオクシア株式会社内 (72)発明者 和田 秀雄 東京都港区芝浦三丁目1番21号 キオクシア株式会社内 F ターム(参考) 5F033 HH08 HH11 MM30 QQ13 VV07 VV16 5F048 AA01 AB01 AC01 BA01 BA19 BA20 BB09 BB11 BC03 BC18 BD07 BF07 BF12 BF15 BF16 CB01 CB03 **CB04** 5F083 EP18 EP22 EP76 ER23 GA10 JA04 JA19 JA37 JA39 KA01 KA05 KA11 LA03 LA10 LA21 LA25 MA06 MA16 MA19 MA20 ZA28 5F101 BA45 BB02 BD16 BD30 BD34 BE02