### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-246378 (P2009-246378A)

(43) 公開日 平成21年10月22日(2009.10.22)

| (51) Int.Cl. |               |           | FΙ   |       |         | テーマ            | コード (参考)  |

|--------------|---------------|-----------|------|-------|---------|----------------|-----------|

| HO1L         | 27/14         | (2006.01) | HO1L | 27/14 | D       | 2G0            | 88        |

| HO1L         | <i>27/146</i> | (2006.01) | HO1L | 27/14 | C       | $4\mathrm{M}1$ | 18        |

| GO 1 T       | 1/20          | (2006.01) | GO1T | 1/20  | G       | 5 C O :        | 24        |

| GO 1 T       | 1/24          | (2006.01) | GO1T | 1/20  | E       |                |           |

| HO4N         | <i>5/33</i> 5 | (2006.01) | GO1T | 1/24  |         |                |           |

|              |               |           | 審査請求 | 有 請求  | マ項の数 16 | O L (全 26 ]    | 頁) 最終頁に続く |

(71) 出願人 000001007 特願2009-164698 (P2009-164698) (21) 出願番号 (22) 出願日 平成21年7月13日 (2009.7.13) (62) 分割の表示 特願2005-79431 (P2005-79431) (74)代理人 100090273 の分割 原出願日 平成8年9月3日(1996.9.3) 特願平7-227851 (31) 優先権主張番号 (72) 発明者 小林 功 平成7年9月5日(1995.9.5) (32) 優先日 (33) 優先権主張国 日本国(JP) (31) 優先権主張番号 特願平7-227852 (72) 発明者 海部 紀之 (32) 優先日 平成7年9月5日(1995.9.5) (33) 優先権主張国 日本国(JP) (72) 発明者 田代 和昭

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

弁理士 國分 孝悦

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

# (54) 【発明の名称】光電変換装置及び放射線撮像装置

# (57)【要約】

【課題】大面積の光電変換装置のコストを低減すること 、及び、信号処理を簡単にし、性能を向上させること、 及び、一種のICを光電変換素子アレイの上下又は左右 のいずれの側にも簡単に実装できるようにする。

【解決手段】複数の光電変換素子を有する基板100、 150を複数隣接して配置した光電変換装置において、 検出用回路IC-1~10は、アレイの対向する2辺の うちの一方の辺に配置された複数の第1の集積回路と、 他方の辺に配置された複数の第2の集積回路とを含み、 複数の第1及び第2の集積回路は双方向の動作が可能な 同じ構成の集積回路であり、複数の第1の集積回路に第 1の共通入力信号が入力され、複数の第2の集積回路に 第2の共通入力信号が入力されることにより、複数の第 1及び第2の集積回路がアレイから同一の方向で信号を 検出するように、複数の第1及び第2の集積回路の動作 方向を決定する。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

基板上に2次元状に配された複数の光電変換素子からなるアレイと、

当該アレイから出力される信号を検出するための検出回路と、を備えた光電変換装置であって、

前記検出回路は、前記アレイの対向する2辺のうちの一方の辺に配置された複数の第1の集積回路と、前記アレイの対向する2辺のうちの他方の辺に配置された複数の第2の集積回路と、を含み、前記複数の第1及び第2の集積回路は、双方向の動作が可能な同じ構成の集積回路であり、

前記複数の第1の集積回路に第1の共通入力信号が入力され、前記複数の第2の集積回路に第2の共通入力信号が入力されることにより、前記複数の第1及び第2の集積回路が前記アレイから同一の方向で信号を検出するように、前記複数の第1及び第2の集積回路の動作方向を決定することを特徴とする光電変換装置。

### 【請求項2】

前記集積回路はマルチプレクサを含み、前記検出回路の動作方向はマルチプレクサの切り換え順序により定められることを特徴とする請求項1記載の光電変換装置。

### 【請求項3】

前記集積回路はシフトレジスタを含み、前記検出回路の動作方向は前記シフトレジスタのシフト方向により定められることを特徴とする請求項1又は2記載の光電変換装置。

# 【請求項4】

前記集積回路はデコーダを含み、前記検出回路の動作方向は前記デコーダにアドレス情報を供給するコントローラにより定められることを特徴とする請求項1又は2記載の光電変換装置。

#### 【請求項5】

前記集積回路は、前記基板、当該基板を支持するマザーボード、及びフレキシブル配線 基板のいずれかに実装されていることを特徴とする請求項1から4のいずれか1項記載の 光電変換装置。

#### 【請求項6】

前記アレイの上部に蛍光体を有することを特徴とする請求項1から5のいずれか1項記載の光電変換装置。

### 【請求項7】

前記光電変換素子は、第1の電極層、半導体層、及び第2の電極層を積層した素子であり、前記半導体層は非単結晶半導体層であることを特徴とする請求項1から6のいずれか 1項記載の光電変換装置。

### 【請求項8】

前記光電変換素子は、前記第1の電極層と前記半導体層との間に絶縁層を、前記半導体層と前記第2の電極層との間に第1導電型のキャリアの注入を阻止する半導体層を、更に有することを特徴とする請求項7に記載の光電変換装置。

## 【請求項9】

入射される放射線を受けて当該放射線に応じた電気信号を発生する変換素子が基板上に 2次元状に複数配されたアレイと、

当該アレイから出力される信号を検出するための検出回路と、を備えた放射線撮像装置であって、

前記検出回路は、前記アレイの対向する2辺のうちの一方の辺に配置された複数の第1の集積回路と、前記アレイの対向する2辺のうちの他方の辺に配置された複数の第2の集積回路と、を含み、前記複数の第1及び第2の集積回路は、双方向の動作が可能な同じ構成の集積回路であり、

前記複数の第1の集積回路に第1の共通入力信号が入力され、前記複数の第2の集積回路に第2の共通入力信号が入力されることにより、前記複数の第1及び第2の集積回路が前記アレイから同一の方向で信号を検出するように、前記複数の第1及び第2の集積回路

10

20

30

40

の動作方向を決定することを特徴とする放射線撮像装置。

#### 【請求項10】

前記集積回路はマルチプレクサを含み、前記検出回路の動作方向はマルチプレクサの切り換え順序により定められることを特徴とする請求項9記載の放射線撮像装置。

## 【請求項11】

前記集積回路はシフトレジスタを含み、前記検出回路の動作方向は前記シフトレジスタのシフト方向により定められることを特徴とする請求項9又は10記載の放射線撮像装置

### 【請求項12】

前記集積回路はデコーダを含み、前記検出回路の動作方向は前記デコーダにアドレス情報を供給するコントローラにより定められることを特徴とする請求項9又は10記載の放射線撮像装置。

#### 【請求項13】

前記集積回路は、前記基板、当該基板を支持するマザーボード、及びフレキシブル配線基板のいずれかに実装されていることを特徴とする請求項9から12のいずれか1項記載の放射線撮像装置。

### 【請求項14】

前記変換素子は、前記放射線を可視光に変換する蛍光体と、前記可視光を前記電気信号に変換する光電変換素子と、を含むことを特徴とする請求項9から13のいずれか1項記載の放射線撮像装置。

#### 【請求項15】

前記光電変換素子は、第1の電極層、半導体層、及び第2の電極層を積層した素子であり、前記半導体層は非単結晶半導体層であることを特徴とする請求項14記載の放射線撮像装置。

#### 【請求項16】

前記光電変換素子は、前記第1の電極層と前記半導体層との間に絶縁層を、前記半導体層と前記第2の電極層との間に第1導電型のキャリアの注入を阻止する半導体層を、更に有することを特徴とする請求項15記載の放射線撮像装置。

【発明の詳細な説明】

# 【技術分野】

### [0001]

本発明は、光電変換装置、それを用いた撮像装置及び製造方法に係わり、特に大面積の 光電変換装置、例えばファクシミリ、デジタル複写機あるいはX線撮像装置等に用いられ る二次元の光電変換装置、それを用いた撮像装置及び製造方法に関するものである。

# 【背景技術】

# [0002]

従来、ファクシミリ、デジタル複写機等の読み取り系としては、縮小光学系とCCD型センサを用いた読み取り系が用いられていたが、近年、アモルファスシリコン(以下、a‐Siと記す)に代表される光電変換半導体材料の開発により、光電変換素子及び信号処理部を大面積の基板に形成し、情報源と等倍の光学系で読み取るいわゆる密着型センサの開発がめざましい。特にa‐Siは光電変換材料としてだけでなく、薄膜電界効果型トランジスタ(以下TFTと記す)としても用いることができるので光電変換半導体層とTFTの半導体層とを同時に形成することができる利点を有している。

# [0003]

a - S i を用いた光電変換装置は、その基体構造が特許文献 1 、 2 、又は 3 に記載されている。

### [0004]

a - S i 光センサと a - S i T F T を一体的に形成する為の具体例は、特許文献 4 、 5 、又は 6 の各明細書に記載されている。

# [0005]

10

20

30

(4)

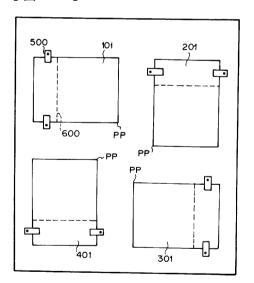

本発明者らは、これら明細書に開示の技術を基に、画素数を大巾に増大させた 2 次元エリア型の光電変換装置を試作した。その光電変換装置の概略を図 2 、図 3 を参照して説明する。

[0006]

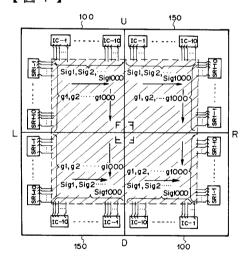

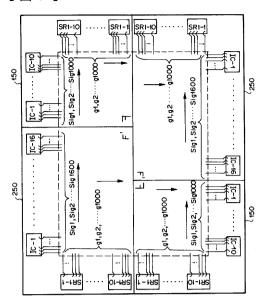

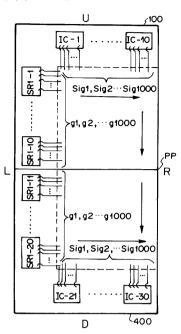

図 2 、図 3 に 2 0 0 0 0 × 2 0 0 0 個の画素を持つ光電変換装置を示す平面図を示す。 2 0 0 0 × 2 0 0 0 個の検出器を構成する場合、光電変換素子を縦・横方向にそれぞれ数を増やせばよいが、この場合、制御配線(走査線)もg 1 ~g 2 0 0 0 に示すように 2 0 0 0 本になり信号配線(データ線)もsig 1 ~sig 2 0 0 0 に示すように 2 0 0 0 本になり信号配線(データ線)もsig 1 ~sig 2 0 0 0 本の制御・処理をしなければならず大規模となる。これをそれぞれ 1 チップの I C で行うことは 1 チップが非常に大きくなり製造時の歩留まりや価格等で不利である。そこで、図に示すように走査回路は例えば 1 0 0 段のシフトレジスタを 1 個のチップに形成し、 2 0 個の走査回路チップ( S R 1 - 1 ~ S R 1 - 2 0 )を使用すれば良い。また検出用集積回路も 1 0 0 個の処理回路を 1 個のチップに形成し、 2 0 個の検出用集積回路チップ( I C 1 ~ I C 2 0 )を使用する。

[0007]

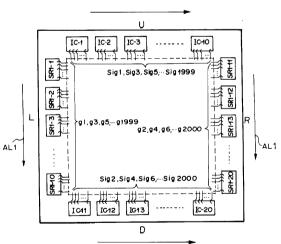

図3には左側(L)に20チップ(SR1-1~SR1-20)と下側(D)に20チップ実装し、1チップあたり100本の制御配線、信号配線をおのおのワイヤーボンディングでチップと接線している。図3中で破線で囲まれる部分は2次元エリア状に配列された光電変換素子アレイ部分に相当する。また検出用集積回路の外部への接続は省略している。

[ 0 0 0 8 ]

図2には別の例が示されており、ここでは、左側(L)に10チップ(SR1-1~SR1-20)と右側(R)に10チップ(SR1-11~SR1-20)と上側(U)に10チップ(IC1~10)、下側(D)に10チップ(IC11~20)を実装している。この構成は上・下・左・右側(U、D、L、R)にそれぞれ各配線を1000本ずつに振り分けているため、各辺の配線の密度が小さくなり、また各辺のワイヤーボンディングの密度も小さく、製造歩留まりが向上する。配線の振り分けは左側(L)にg1、g3、g5、…、g1999、右側(R)にg2、g4、g6、…、g2000とし、つまり奇数番目の制御配線を左側(L)、偶数番目の制御配線を右側(R)に振り分ける。こうすると各配線は等間隔に引き出され配線されるので密度の集中がなく歩留まりが向上する。また、上側(U)下側(D)への配線も同様に振り分ければよい。

[0009]

また、図示していないが、別の例として、配線の振り分けは左側(L)にg1~g100、g201~g300、…、g1801~g1900、右側(R)にg101~g200、g301~g400、…、g1901~g2000を振り分け、つまり、1チップごとに連続な制御線を振り分け、これを左・右側(L・R)交互に振り分けることも考えられる。こうすると、1チップ内は連続に制御でき、駆動タイミングの調整や設定が容易で回路を複雑にしなくてよく、安価なICが使用できる上・下側(U・D)についても同様で、連続な処理が可能で安価なICが使用できる。

【先行技術文献】

【特許文献】

[0010]

【特許文献1】米国特許第437688号明細書

【特許文献 2 】特公昭 6 2 - 2 3 9 4 4 号公報

【特許文献3】特公昭63-66117号公報

【特許文献4】米国特許第4931661号明細書

【特許文献5】米国特許第5338690号明細書

【特許文献 6 】米国特許第 5 3 0 6 6 4 8 号明細書

【発明の概要】

10

20

30

40

#### 【発明が解決しようとする課題】

### [0011]

しかしながら、大面積の光電変換装置では、製造時の微小なちり、特にアモルファスシリコンなどの半導体層を基板に堆積する時に薄膜堆積装置の壁から剥れ出るゴミ、及びメタル層を基板に堆積する時に基板上に残っているほこりを完全になくすことが困難であっため、配線の不具合、即ち配線のショートまたはオープンをゼロにすることは困難であった。

# [0012]

また、大面積の光電変換装置では、制御配線または信号配線がショートまたはオープンになると、その配線に接続されている光電変換素子の全ての出力信号が不正確なものとなり、光電変換装置としては使用不可能となるのである。

[0013]

つまり、大面積の光電変換装置を作製する時の1枚の基板が大きくなればなるほど基板1枚あたりの歩留まりは低くなり、同時に基板1枚あたりの不具合による損失額も大きくなるのである。

[ 0 0 1 4 ]

しかも、制御配線の選択順序(走査順序)を図2の矢印AL1に示す方向に設計しようとすると、図2の左側Lに配される各走査回路SR1-1~SR1-10の出力端子の配置順序と、図2の右側Rに配される各走査回路SR-11~SR1-20の出力端子の配列順序とが、互いに逆になる。従って、左右両側に配される走査回路を同じ構造のICチップで作るとすると、左又は右側いずれか一方の接続線(制御配線と走査回路の出力端子とを接続する線)を多層配線等で構成しなければならない。こうなると、接続線の構造が複雑且つ高コストなものになり、又走査回路の高密度実装を妨げる。

[0015]

又、出力端子の配置順序を変えた2種類のICを用意して一方を左側に、他方を右側に配することもできるが、基本動作が同じであるにもかかわらず2種のICを製造することは高コスト化の原因になる。

[0016]

このような問題は走査回路だけの問題ではなく検出用IC(IC1~IC20)においても同様に生じる。

[0017]

よって、本発明の第1の目的は、大面積の光電変換装置を作製する時の基板1枚あたりの歩留まりを向上させ、かつ基板1枚あたりの不具合による損失額を小さくすることにより、結果的に大面積の光電変換装置のコストを低減することにある。

[0018]

また、本発明の第2の目的は、大面積の光電変換装置を作製する時の検査工程の効率の向上およびそれに伴うスループット向上および部品点数の削減に伴う総合的なコストを低減することにある。

[ 0 0 1 9 ]

またさらに、本発明の第3の目的は、大面積の光電変換装置において、すべての光電変換素子を同一方向に走査し、信号処理を簡単にすることにより、光電変換装置の性能を向上させることである。

[0020]

本発明の第4の目的は、一種のICを光電変換素子アレイの上下又は左右のいずれの側にも簡単に実装できる光電変換装置を提供することにある。

# 【課題を解決するための手段】

### [0021]

上記目的を達成するため、本発明に係る光電変換装置は、基板上に2次元状に配された複数の光電変換素子からなるアレイと、当該アレイから出力される信号を検出するための検出回路と、を備えた光電変換装置であって、前記検出回路は、前記アレイの対向する2

10

20

30

40

辺のうちの一方の辺に配置された複数の第1の集積回路と、前記アレイの対向する2辺のうちの他方の辺に配置された複数の第2の集積回路と、を含み、前記複数の第1及び第2の集積回路は、双方向の動作が可能な同じ構成の集積回路であり、前記複数の第1の集積回路に第1の共通入力信号が入力され、前記複数の第1及び第2の集積回路に第2の共通入力信号が入力されることにより、前記複数の第1及び第2の集積回路が前記アレイから同一の方向で信号を検出するように、前記複数の第1及び第2の集積回路の動作方向を決定することを特徴とする。

## [0022]

本発明に係る光電変換装置の他の態様は、前記集積回路はマルチプレクサを含み、前記検出回路の動作方向はマルチプレクサの切り換え順序により定められることを特徴とする

スタを

また、本発明に係る光電変換装置のその他の態様は、前記集積回路はシフトレジスタを含み、前記検出回路の動作方向は前記シフトレジスタのシフト方向により定められることを特徴とする。

また、本発明に係る光電変換装置のその他の態様は、前記集積回路はデコーダを含み、前記検出回路の動作方向は前記デコーダにアドレス情報を供給するコントローラにより定められることを特徴とする。

また、本発明に係る光電変換装置のその他の態様は、前記集積回路は、前記基板、当該 基板を支持するマザーボード、及びフレキシブル配線基板のいずれかに実装されていることを特徴とする。

20

10

また、本発明に係る光電変換装置のその他の態様は、前記アレイの上部に蛍光体を有することを特徴とする。

また、本発明に係る光電変換装置のその他の態様は、前記光電変換素子は、第1の電極層、半導体層、及び第2の電極層を積層した素子であり、前記半導体層は非単結晶半導体層であることを特徴とする。

また、本発明に係る光電変換装置のその他の態様は、前記光電変換素子は、前記第1の電極層と前記半導体層との間に絶縁層を、前記半導体層と前記第2の電極層との間に第1 導電型のキャリアの注入を阻止する半導体層を、更に有することを特徴とする。

## [0023]

30

本発明に係る放射線撮像装置は、入射される放射線を受けて当該放射線に応じた電気信号を発生する変換素子が基板上に2次元状に複数配されたアレイと、当該アレイから出力される信号を検出するための検出回路と、を備えた放射線撮像装置であって、前記検出回路は、前記アレイの対向する2辺のうちの一方の辺に配置された複数の第1の集積回路と、を含み、前記複数の第1及び第2の集積回路は、双方向の動作が可能な同じ構成の集積回路であり、前記複数の第1及び第2の集積回路に第1の共通入力信号が入力され、前記複数の第2の集積回路に第2の共通入力信号が入力されることにより、前記複数の第1及び第2の集積回路が前記アレイから同一の方向で信号を検出するように、前記複数の第1及び第2の集積回路の動作方向を決定することを特徴とする。

### [0024]

40

本発明に係る放射線撮像装置の他の態様は、前記集積回路はマルチプレクサを含み、前記検出回路の動作方向はマルチプレクサの切り換え順序により定められることを特徴とする。

また、本発明に係る放射線撮像装置のその他の態様は、前記集積回路はシフトレジスタ を含み、前記検出回路の動作方向は前記シフトレジスタのシフト方向により定められることを特徴とする。

また、本発明に係る放射線撮像装置のその他の態様は、前記集積回路はデコーダを含み、前記検出回路の動作方向は前記デコーダにアドレス情報を供給するコントローラにより 定められることを特徴とする。

また、本発明に係る放射線撮像装置のその他の態様は、前記集積回路は、前記基板、当

該基板を支持するマザーボード、及びフレキシブル配線基板のいずれかに実装されている ことを特徴とする。

また、本発明に係る放射線撮像装置のその他の態様は、前記変換素子は、前記放射線を可視光に変換する蛍光体と、前記可視光を前記電気信号に変換する光電変換素子と、を含むことを特徴とする。

また、本発明に係る放射線撮像装置のその他の態様は、前記光電変換素子は、第 1 の電極層、半導体層、及び第 2 の電極層を積層した素子であり、前記半導体層は非単結晶半導体層であることを特徴とする。

また、本発明に係る放射線撮像装置のその他の態様は、前記光電変換素子は、前記第1の電極層と前記半導体層との間に絶縁層を、前記半導体層と前記第2の電極層との間に第1導電型のキャリアの注入を阻止する半導体層を、更に有することを特徴とする。

【発明の効果】

[0025]

以上説明した様に、本発明によれば、大面積の光電変換装置を作製する時の基板 1 枚あたりの歩留まりを向上させ、かつ基板 1 枚あたりの不具合による損失額を小さくすることにより、結果的に大面積の光電変換装置のコストを低減することが可能となる。

[0026]

また、本発明によれば、大面積の光電変換装置を作製する時の検査工程の効率の向上及びそれに伴うスループットの向上及び部品点数の削減が可能となり、結果的に大面積の光電変換装置のコストをさらに低減することが可能となる。

[0027]

また、本発明によれば、大面積の光電変換装置において、すべての光電変換素子を同一方向に走査し、信号処理を簡単な装置で高速に行うことが可能となり、その結果、光電変換装置のコスト低減と性能の向上をさせることが可能となる。

【図面の簡単な説明】

[0028]

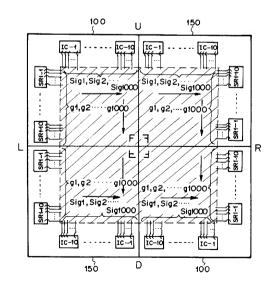

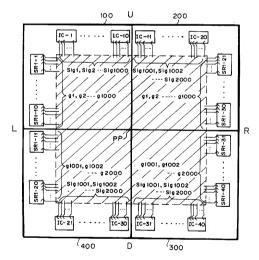

- 【図1】本発明の第1の実施形態に係る光電変換装置の全体平面図である。

- 【図2】2000×2000個の画素を持つ光電変換装置の別の例を示す平面図である。

- 【図3】2000×2000個の画素を持つ光電変換装置を示す平面図である。

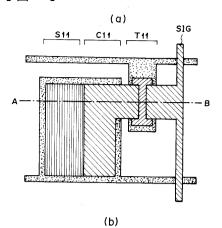

- 【図4】本発明の第1の実施形態の基板上の構成を示す平面図(a)及び断面図(b)である。

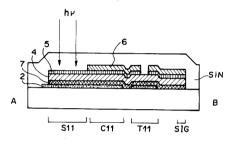

- 【図5】本発明の第1の実施形態に係る走査回路の構成を示す図である。

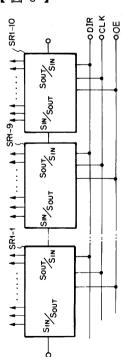

- 【図 6 】 1 0 個の走査回路チップSR1-1~SR1-10 を直列に接続し1 つの光電変換装置の走査回路を構成した例を示す図である。

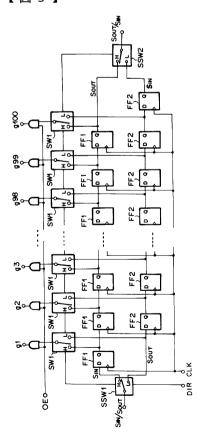

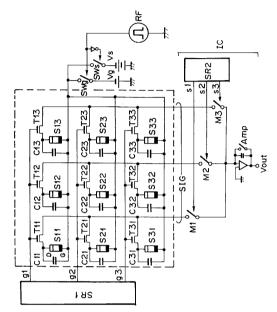

- 【図7】1つの検出用集積回路チップの構成を示す図である。

- 【図8】10個の検出用集積回路チップIC-1~IC-10を直列に接続した例を示す図である。

- 【図9】本発明の第2の実施形態に係る光電変換装置の平面図である。

- 【図10】本発明の第3の実施形態に係る光電変換装置の全体平面図である。

- 【図11】本発明の第3の実施形態に係る光電変換装置を作製するプラズマCVD装置内での基板配置図である。

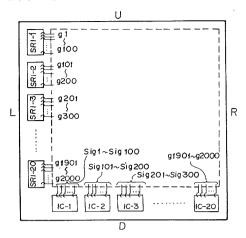

- 【 図 1 2 】 本 発 明 の 第 4 の 実 施 形 態 に 係 る 光 電 変 換 装 置 の 全 体 平 面 図 で あ る 。

- 【図13】本発明の第5の実施形態として、各実施形態の光電変換素子の上部に蛍光体層を配置し、X線レントゲン装置を構成したものである。

- 【図14】本発明の光電変換装置の駆動方法を説明する為の回路図である。

- 【図15】図14の動作を示すタイミングチャートである。

- 【 図 1 6 】 受 光 素 子 と し て の 光 セ ン サ の 構 成 及 び 駆 動 方 法 を 示 す 図 で あ る 。

- 【図17】薄膜の半導体膜で形成した電界効果型トランジスタ(TFT)の層構成を示す図である。

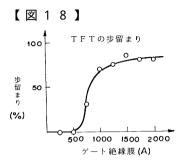

- 【図18】ゲート絶縁膜とTFTの歩留まりについて、実験した結果を示す図である。

10

20

30

40

【図19】4つの基板上に形成された光電変換素子アレイを示す図である。

【発明を実施するための形態】

[0029]

(第1の実施形態)

図1は、本発明の第1の実施形態に係る光電変換装置の全体平面図である。なお図2及び図3と同一機能の部分には同一符号を付してあり、説明を省略する場合がある。

[0030]

図1に示す光電変換装置において特徴的な点は、4枚の基板100、150、100、150を各々2枚ずつ180。回転した状態で4枚の光電変換素子部(図中点線で囲まれた斜線部)を実質的に隙間なく隣り合うように隣接して配列し、互いに貼り合わせることによって1つの大きな光電変換装置を構成している点である。

【 0 0 3 1 】

また、対角線上にある2つの基板はそれぞれ同一構成の基板である。

[0032]

さらに、図1中に矢印で示した走査方向において4枚の基板上の光電変換素子アレイの 走査回路の走査方向と、検出用集積回路の走査方向即ち、検出信号のパラ・シリ変換の方 向を双方向可能とすることにより、4枚の光電変換素子部を装置全体でみた時にすべて同 一方向に走査することが大きな特徴である。

[0033]

基板100の上には、光電変換素子が1000×1000個配置され、1000本の制御配線g1~g1000と1000本の信号配線sig1~sig1000の計2000本の配線と接続されている。走査回路SR1は100段ごとに1個のチップに形成してあり、基板100の上には、SR1・1~SR1・10の計10個のICチップが配置され制御配線g1~g1000とICチップの各端子とが接続されている。

[0034]

また、検出用集積回路も100個の処理回路ごとに1個のチップに形成し、IC1~IC10の計10個の検出用集積回路チップが配置され信号配線sig1~sig1000と目様であり、光電変換素子は1000×1000個配置されており、1000本の制御配線と1000本の信号配線により接続されている。また走査回路及び検出用集積回路も同様に10個ずつ配置されている。これらの走査回路及び検出用集積回路は各基板毎に同じものを用いて異なるものを用いてもよいが、後述するようにそれぞれ一種のICを用いたほうが好ましいものである。また、4枚の基板上の光電変換素子アレイにおいて4つ同時に走査することも可能であり、そのような場合は図2に示した例と比較すると1/4の走査時間に短縮することが可能となる。

[0035]

図1に示すように4枚の基板上に光電変換素子アレイを作製し、その4枚の基板をすき間が出来るだけ小さくなるように貼り合わせて大面積の光電変換装置を構成することにより、基板1枚あたりの歩留まりは高くなり、同時に基板1枚あたりの不具合による損失額を小さくすることができる。

[0036]

具体的には、図1の大面積光電変換装置における光電変換素子が配置してある面積と図3の光電変換装置における光電変換素子が配置してある面積が同じ場合には、図1に示す各基板内のすべての制御配線とすべての信号配線の合計の長さは図3に示す光電変換装置内のすべての制御配線とすべての信号配線の合計の長さの約1/4となる。

[0037]

このような光電変換装置において、制御配線及び信号配線のショートまたはオープンはその配線に接続されている光電変換素子のすべての出力信号が不正確なものとなるため、 光電変換装置としては使用不可能となってしまう。そのため、すべての制御配線及びすべての信号配線の合計の長さにほぼ比例して上記のような不具合が生じる確率が増大し、歩 10

20

30

40

留まりを下げるのである。

### [0038]

よって図1に示す基板1枚あたりの配線の不具合による歩留まりは、図3に示す光電変換装置の約4倍となる。また、図1に示す基板1枚が不具合となり、使用不可能になった場合の損失額は、基板の面積にほぼ比例するため、図3に示す光電変換装置において不具合が発生し使用不可能になった場合の損失額の約1/4となるのである。

#### [0039]

図1に示すように4枚の基板を用いて第1のパターンの光電変換素子アレイの基板100を2枚と、第2のパターンの光電変換素子アレイの基板150とを形成し、同一の走査回路及び検出用集積回路を実装し、その2枚の基板を各々180°ずつ回転させ対角線上に配し貼り合わせて大面積の光電変換装置を構成する。こうすることにより、部品点数の削減が可能となる。また、検査工程も2種類の装置で行うことが可能となり、検査工程の効率の向上及びそれに伴うスループットの向上が可能となる。その結果大面積の光電変換装置のコストを低減することが可能となる。

### [0040]

また、4枚の基板上に実装する走査回路及び検出用集積回路を双方向で駆動可能なものとし、シフト方向を定める信号の入力によってシフト方向が決定される回路を用いることにより、図3の様に配置された4枚の光電変換装置すべて同一の方向で走査することが可能となる。その結果、読み取られた全光電変換素子の信号を処理する回路が簡単なものとなり、高速で信号を処理することが可能となる。

#### [0041]

よって、低コストで高性能な大面積の光電変換装置が可能となる。

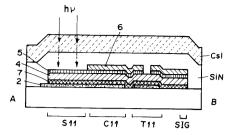

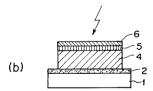

#### [0042]

また、基板上の構成は、図4(a)、(b)に示すように、前記基板上には、第1の電極層2、絶縁層7、光電変換を行いうる半導体層4、第1導電型のキャリアの注入を阻止する半導体層5、及び第2の電極層6を積層した光電変換素子が設けられている。そして、この光電変換装置は前記半導体層5に入射した信号光により発生した第1導電型のキャリアを前記半導体装置5に蓄積させ、前記第1導電型と異なる第2導電型のキャリアを前記第2の電極層6に導く方向に前記受光素子に電界を与える光電変換手段と、前記受光素子に電界を与えて、前記第1導電型のキャリアを前記半導体層から前記第2の電極層に募ま子に電界を与えるリフレッシュ手段と、前記光電変換手段による光電変換動作中に前記半導体層に蓄積された前記第1導電型のキャリアもしくは前記第2の電極層に導かれた前記第2導電型のキャリアを検出する為の信号検出部と、を有している。

# [ 0 0 4 3 ]

図4(a)、(b)において、S11は受光素子、T11はTFT、C11はコンデンサ、およびSIGは信号配線である。コンデンサC11と受光素子S11とを分離せず、受光素子S11とコンデンサC11とを一体的に形成している。これは受光素子とコンデンサとTFTとがほぼ同じ層構成であるから可能なことである。また、画素上部にはパッシベーション膜として窒化シリコン膜SiNが形成されている。上方より光が光電変換素子に入射すると電気信号(蓄積電荷量)に変換される。

#### [0044]

次に図1に示した走査回路の構成について図5を参照して説明する。

# [0045]

走査回路は、出力線の数に対応して設けられたアンドゲート及び選択スイッチSW1と、2段の遅延型フリップフロップ(Dフリップフロップ)FF1、FF2と、選択スイッチSSW1、SSW2と、を有している。

# [0046]

シフト方向を定める為の信号として、端子DIRにハイレベルの電圧が入力されると、選択スイッチSSW1、SSW2、SW1がハイ(H)側に切換えられる。図中左側の入

10

20

30

40

10

20

30

40

50

出力端子はSIN/SOUTから入力されるシフトパルス及びクロック入力端子から入力されるクロックに応じて、DフリップフロップFF1は順次選択スイッチSW1を介してアンドゲートに、ゲート線を選択する意味をもつ"1"を出力する。この時、制御端子OEにアウトプットイネーブルのパルス"1"が入力されるとアンドゲートの出力は"1"となり出力線が選択される。こうして、出力線はg1、g2、g3…g98、g99、g100の順に選択される。

[0047]

次に逆方向のシフト動作について説明する。シフト方向制御端子DIRにローレベルの電圧が入力されると、各選択スイッチSSW2、SW1、SSW1がロー(L)側に切換えられる。

[0048]

図 5 中、右側の入出力端子SOUT/SINからシフトパルスが入力されると、DフリップフロップFF2が順次、選択スイッチSW1を介してアンドゲートに"1"を出力する。この時制御端子OEにアウトプットイネーブルパルス"1"が入力されるとアンドゲートの出力は"1"となり出力線が選択される。こうして出力線はg100、g99、g98、...g3、g2、g1の順で選択される。

[0049]

図 6 は、 1 0 個の走査回路チップ S R 1 - 1 ~ S R 1 - 1 0 を直列に接続し1つの光電変換装置の走査回路を構成した例を示している。

[0050]

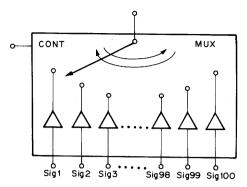

図 7 は、 1 つの検出用集積回路チップの構成を示している。 I C チップはマルチプレクサを有しており、入力された信号の出力順(又は信号の入力順)を選択する電気的ロータリースイッチを制御端子 C O N T への入力制御信号により制御する構成が採用されている。 つまり、 I C チップは、入力端子からパラレルに入力した信号を、いったん不図示のサンプルホールド回路に保持した後、シリアルに出力してもよいし、シリアルに入力してシリアルに出力してもよい。

[0051]

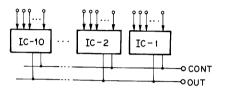

図 8 は、 1 0 個の検出用集積回路チップIC - 1 ~ IC - 1 0 を直列に接続した例を示している。

[0052]

図1の装置に図5~図8の走査回路及び検出用集積回路を採用した場合の動作について述べる。

[0053]

各チップからみれば、光電変換素子部のゲート配線又は信号配線に接続される各チップの端子の物理的配置順序とシフト方向との関係は装置100に搭載されるか、装置150に搭載されるかにより、互に逆になる。

[0054]

しかし、図5~図8の各ICチップはシフト方向が制御端子DIR、CONTへの入力信号によって選択的に定められる為、1種類のICチップが100又は150のいずれにも搭載できる。

[ 0 0 5 5 ]

例えば、図1中、左上の装置100と左下の装置150に搭載される走査回路は、端子DIRにハイレベルの電圧を入力し、シフト方向がg1、g2、...g100となるように定められる。

[0056]

一方、図1中右上の装置150と右下の装置100とに搭載される走査回路は端子DIRにローレベルの電圧を入力し、シフト方向がg100、g99、...g1となるように定められる。

[0057]

又、各チップからの走査選択信号は左上、左下の装置ではSR1-1からSR1-10

(11)

の順に出力され、逆に右上、右下の装置ではSR1-10からSR1-1の順に出力される。

[0058]

同様にして、図1の右上及び左上にある装置に搭載される検出用ICチップには端子CONTにハイレベルのパルスが入力され、端子Sig1、Sig2、…Sig100の順に検出信号を時系列に並べ変えて出力する。

[0059]

一方、図1の右下及び左下にある装置に搭載される検出用ICチップには端子CONTにローレベルのパルスが入力され端子Sig100、Sig99、…Sig1の順に検出信号を時系列に並べ変えて出力する。

[0060]

各チップからの出力は右上、左上の装置ではIC-1からIC-10の順まで時系列に出力され、右下、左下の装置では逆にIC-10からIC-1の順で時系列に出力される

[0061]

本発明の光電変換装置に用いることができるICチップの実装法は大別して4つある。各チップを4つの基板上にフリップチップ方式で直接搭載するチップオングラス法(COG法)、各チップをフレキシブルプリント配線基板に接続し搭載するテープキャリアパッケージICを用いる方法(TAB法)、4つの基板上にICチップを配してワイヤーボンディングする方法、或いは走査回路と検出用回路を光電変換素子を構成する薄膜半導体を用いて同一基板上に作製するモノリシック集積化法である。ICチップの大きさが無視できない場合であって光電変換素子アレイの外側の領域(枠部)の大きさを小さくしたい場合には、基板を折り曲げることが出来るTAB法が好ましい。TAB法の場合、制御配線又は信号配線と、テープキャリアパッケージされたICの端子との接続は、異方性導電性接着剤を用いて接続することが望ましい。

[0062]

又、 4 つの基板は、ガラス、セラミックス、金属、樹脂などからなる大面積の基体(マザーボード)に積層して貼り合わせるとよい。

[0063]

(第2の実施形態)

図9は、本発明の第2の実施形態に係る光電変換装置の平面図である。なお図1、図2 及び図3と同一機能の部分には同一符号を付してあり、説明を適宜省略している。

[0064]

図9に示す光電変換装置において特徴的な点は、4枚の基板の中の少なくとも1組が互いに異なる外形を有している点である。図9ではこうして4枚の基板を貼り合わせた時の大面積の光電変換装置における光電変換部の平面形状が長方形の装置を提供する。つまり、符号150で示す互いに対角線上にある1組の基板の装置は同一構成のものが使用でき、符号250で示す、対角線上にある1組の基板の装置は同一構成の装置である。もちろん、1組の基板の平面形状が互いに異なる場合においても、4枚の基板を貼り合わせた時の大面積の光電変換装置における光電変換部の平面形状が正方形になる場合もあるが、作製のしやすさ及びコストを考えると図9に示す装置がより好ましい。

[0065]

本発明による大面積の光電変換装置を人体の胸部用X線撮像装置に用いる場合は、光電変換部の平面形状は本第2の実施例のような長方形になる場合がある。

[0066]

このような場合においても、同一パターンの基板を2枚ずつ形成し、同一の走査回路及び検出用集積回路を実装し、その2枚の基板を各々180°ずつ回転させ、すき間をできるだけなくすように貼り合わせて大面積の光電変換装置を構成することにより、部品点数の削減が可能となる。また、検査工程も2種類の装置で行うことが可能となり、検査工程の効率の向上及びそれに伴うスループットの向上が可能となる。その結果大面積の光電変

10

20

30

40

換装置のコストを低減することが可能となる。

### [0067]

また、4枚の基板上に実装するシフトレジスタ及び検出用集積回路を双方向で駆動可能なものとすることにより、図3の様に配置された4枚の光電変換装置すべて同一の方向で走査することが可能となる。その結果、読み取られた全光電変換素子の信号を処理する回路が簡単なものとなり、高速で信号を処理することが可能となる。よって、低コストで高性能な大面積の光電変換装置が可能となる。

### [0068]

(第3の実施形態)

図10は、本発明の第3の実施形態に係る光電変換装置の全体平面図である。なお従来例の項で説明した図2、3と同一機能の部分には同一符号を付してあり、説明を省略する場合がある。

#### [0069]

図10に示す光電変換装置においては、4枚の基板100、200、300、400上に構成されている光電変換素子アレイ(図中、点線で囲まれる斜線部)を互いに接近させて配列して貼り合わせることによって1つの大きな光電変換装置を構成している。

### [0070]

基板100の上には、光電変換素子が1000×1000個配置され、制御配線g1~g1000と1000本の信号配線sig1~sig1000の計2000本の配線と接続されている。走査回路SR1のシフトレジスタは100段ごとに1個のチップに形成してあり、基板100の上には、SR1・1~SR1・10の計10個のICチップが配置され制御配線g1~g1000と接続されている。

#### [0071]

また、検出用集積回路は100個の処理回路ごとに1個のチップに集積化され、IC1~IC10の計10個のチップが配置され信号配線sig1~sig1000と接続されている。他の基板200、300、400においても基板100と同様であり、光電変換素子は1000×1000個配置されており、1000本の制御配線と1000本の信号配線により接続されている。またシフトレジスタ及び検出用集積回路も同様に10個ずつ配置されている。これらのシフトレジスタ及び検出用集積回路は各基板毎に同じものを用いても異なるものを用いてもよいが、前述した双方向に駆動可能なICを用いることが望ましいものである。また、4枚の光電変換装置において同時に走査することも可能であり、そのような場合は図9に示す例と比較すると1/4の走査時間に短縮することが可能となる。

# [0072]

図11は、本発明の第3の実施形態に係る光電変換装置を作製するプラズマCVD装置内での基板配置図である。図11に示す光電変換装置において更なる特徴的な点は、図10に示した光電変換装置100、200、300、400をそれぞれ構成する基板101、201、301、401のプラズマCVD内での配置される向きと、光電変換装置100、200、300、400の配置されている向きが同じことである。つまり、角部PPが中心になるように配置される。

# [0073]

図 1 1 において符号 5 0 0 は基板を押える治具であり、 6 0 0 は薄膜堆積後切断される 仮想の切断線である。

# [0074]

通常、プラズマCVD装置として、平行平板型で、一方の電極の孔からガスを噴出させる装置が用いられる為、基板又は電極の中心と周辺とに堆積速度に差が生じ易い。

#### [0075]

これに対して、図11のように配置された基板上に非晶質シリコン等の非単結晶半導体層を堆積し、そのままの向きで図1のように4枚を貼り合わせ大面積の光電変換装置を作製することにより、4枚の光電変換装置の継ぎ目の光電変換素子の特性が連続的に等しく

10

20

30

40

なり、結果的に高性能な大面積の光電変換装置を提供することが可能となる。

#### [0076]

基板上には、前述した、図4及び図5に示されるように、前記基板上には、第1の電極層2、絶縁層7、半導体層4、第1導電型のキャリアの注入を阻止する半導体層5、及び第2の電極層6を積層した光電変換素子を配列した光電変換部が設けられている。

## [0077]

(第4の実施形態)

図12は、本発明の第4の実施形態に係る光電変換装置の全体平面図である。なお前述した各実施例と同一機能の部分には同一符号を付してあり、適宜説明を省略する。

## [0078]

図12に示す光電変換装置において特徴的な点は、光電変換装置100、400をすき間が小さくなるように貼り合わせることによって1つの大きな光電変換装置を構成している点である。光電変換装置100、400は実施例3と同様に図11に示す配置でプラズマCVD内で非晶質シリコンが堆積される。よって、図11のように配置された基板上に非晶質シリコンを堆積し、そのうち基板101と基板401を用いて角部PPが一致するようにそのままの向きで図12のように2枚を貼り合わせて大面積の光電変換装置を作製することにより、2枚の光電変換装置の継ぎ目の光電変換素子の特性が連続的に等しくなり、結果的に高性能な大面積の光電変換装置を提供することが可能となる。

### [0079]

又、更に実施例1~3と同様に、2枚の基板上に実装するシフトレジスタ及び検出用集積回路を双方向で駆動可能なものとすることにより、図12の様に配置された2枚の光電変換装置を図12中、矢印に示す方向で走査することが可能となる。

## [0800]

(第5の実施形態)

第 5 の実施形態としては、上記した第 1 乃至第 4 の各実施形態の光電変換素子の上部に 蛍光体を配置し、 X 線レントゲン装置を構成したものである。

#### [0081]

基板上の構成は、前述した図5の光入射側にX線等の高エネルギー線を吸収し可視光を発生する発光体の層を設けたものである。それを図13に示す。パッシベーション膜SiN上に発光体としての蛍光体を配している。この蛍光体としてはヨウ化セシウム(CsI)が挙げられ、X線を受光すると蛍光を発生する。この蛍光を受光素子S11で光電変換する。例えば縦横1mmあたり5×5個の画素を2000×2000個の画素として二次元的に配置すれば40cm×40cmのX線検出器が得られる。

# [0082]

これを X 線フィルムの代わりに X 線発生器と組み合わせて X 線レントゲン装置を構成すれば胸部レントゲン検診や乳ガン検診に使用できる。するとフィルムと異なり瞬時にその出力を C R T で映し出すことが可能で、さらに出力をデジタルに変換しコンピュータで画像処理して目的に合わせた出力に変換することも可能である。また光磁気ディスクに保管もでき、過去の画像を瞬時に検索することもできる。また感度もフィルムよりも良く人体に影響の少ない微弱な X 線で鮮明な画像を得ることもできる。

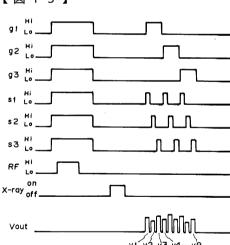

# [ 0 0 8 3 ]

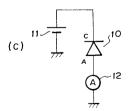

次に、図14、図15を参照して本発明に用いられる光電変換素子アレイの駆動法について説明する。ここでは1チップの走査回路による走査線数を3、1チップの検出用ICによるデータ線数を3として、3×3マトリクスの光電変換素子アレイの駆動する場合を例に挙げるが、走査線を1000本、データ線を1000本、光電変換素子を1000×1000マトリクスとすれば、図3の1つの基板の走査・検出が行えることは明らかである。

# [0084]

図 1 4 は、本発明の光電変換装置の駆動方法を説明する為の回路図である。各光電変換素子(画素)の構成としては図 4 、 5 、 1 3 に示したものと同じ構造を採用できる。

10

20

30

40

[0085]

図14において、S11~S33は受光素子で下部電極側をG、上部電極側をDで示している。C11~C33は蓄積用コンデンサ、T11~T33は転送TFTである。Vsは読み出し用電源、Vgはリフレッシュ用電源であり、それぞれスイッチSWs、SWgを介して全光電変換素子S11~S33のG電極に接続されている。スイッチSWsはインバータを介して、スイッチSWgは直接にリフレッシュ制御回路RFに接続されており、リフレッシュ期間はスイッチSWgがonするよう制御されている。1画素は1個の受光素子とコンデンサ、およびTFTで構成され、その出力信号は信号配線SIGを介して検出用集積回路ICに出力される。

[0086]

図14中の破線で囲んだ部分は大面積の同一絶縁基板上に形成されている。

【 0 0 8 7 】

図15は図14の動作を示すタイミングチャートである。

[ 0 0 8 8 ]

[0089]

しかし、この時点では光線は入射されていないため、全受光素子S11~S33には光は入射されずに光電流は流れない。この状態で光線がパルス的に出射され被写体を介して受光素子S11~S33に入射する。この光により流れた光電流は電荷としてそれぞれのコンデンサC11~C33に蓄積され光線の入射終了後も保持される。

[0090]

つぎに、走査回路SR1により制御配線g1にハイレベルの制御パルスが印加され、走査回路SR2の制御配線s1~s3への制御パルス印加によって転送用TFT・T11~T33のスイッチM1~M3を通してv1~v3が順次出力される。同様に走査回路SR1、SR2の制御により他の光信号も順次出力される。二次元の光情報が電気信号に変換されてv1~v9として得られる。静止画像を得る場合はここまでの動作であるが動画像を得る場合はここまでの動作を繰り返す。

[ 0 0 9 1 ]

この光電変換装置では受光素子のG電極が共通に接続され、この共通の配線をスイッチSWgとスイッチSWsを介してリフレッシュ用電源Vgと読み取り用電源Vsに接続して、G電極の電位に制御している為、全光電変換素子を同時にリフレッシュモードと光電変換モードとに切り換えることができる。このため複雑な制御なくして1画素あたり1個のTFTで光出力を得ることができる。

[0092]

以前我々が提案した光電変換装置では9個の画素を3×3に二次元配置し3画素ずつ同時に、3回に分割して転送・出力したが、これに限らず、例えば縦横1mmあたり5×5個の画素を2000×2000個の画素として二次元的に配置すれば40cm×40cm

10

20

30

40

の X 線 検 出 器 が 得 ら れ る。

### [0093]

従来のX線レントゲン装置におけるX線フィルムに代えて本発明の光電変換装置をX線発生器と組み合わせて用いれば新規なX線レントゲン装置となる。これは胸部レントゲン検診や乳ガン検診に使用できる。するとフィルムと異なり瞬時にその出力をCRTで映し出すことが可能で、さらに出力をデジタルに変換しコンピュータで画像処理して目的に合わせた出力に変換することも可能である。また光磁気ディスクに保管もでき、過去の画像を瞬時に検索することもできる。また感度もフィルムより良く人体に影響の少ない微弱なX線で鮮明な画像を得ることもできる。

## [0094]

又、本発明の光電変換装置に用いられる受光素子としては、光導電素子や光起電力素子が用いられるが、以下に述べる理由により、図 4 、 5 、 1 3 に示したような光電変換素子が好ましく用いられる。

# [0095]

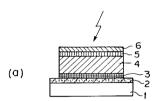

図16(a)~(c)は受光素子としての光センサの構成を示す図であり、図16(a)、(b)は二種類の光センサの層構成を示し、図16(c)は共通した代表的な駆動方法を示している。図16(a)、(b)共にフォト・ダイオード型の光センサであり、図16(a)はPIN型、図16(b)はショットキー型と称されている。

# [0096]

図16(a)、(b)中、1は絶縁基板、2は下部電極、3はp型半導体層(以下p層と記す)、4は真性半導体層(以下、i層と記す)、5はn型半導体層(以下n層と記す)6は透明電極である。図16(b)のショットキー型では下部電極2の材料を適当に選び、下部電極2からi層4に電子が注入されないようショットキーバリア層が形成されている。図16(c)において、10は上記光センサを記号化して表わした光センサを示し、11は電源、12は電流アンプ等の検出部を示している。光センサ10中Cで示された方向は図16(a)、(b)中の透明電極6側、Aで示された方向が下部電極2側であり、電源11はA側に対しC側に正の電圧が加わる様に設定されている。

#### [0097]

ここで動作を簡単に説明する。図16(a)、(b)に示されるように、矢印で示された方向から光が入射され、i層4に達すると、光は吸収され電子とホールが発生する。i層4には電源11により電界が印加されているため電子はC側、つまりn層5を通過して透明電極6に移動し、ホールはA側つまり下部電圧2に移動する。よって、光センサ10に光電流が流れたことになる。また、光が入射しない場合i層4で電子もホールも発生せず、また、透明電極内6のホールはn層5がホールの注入阻止層として働き、下部電極2内の電子は図16(a)のPIN型ではp層3が、図16(b)のショットキー型ではショットキーバリア層が、電子の注入阻止層として働き、電子、ホール共に移動できず、電流は流れない。したがって光の入射の有無で電流が変化し、これを図16(c)の検出部12で検出すれば光センサとして動作する。

# [0098]

しかしながら、上記光センサでSN比が高く、低コストの光電変換装置を生産するのは 困難であった。以下その理由について説明する。

#### [0099]

第1の理由は、図16(a)のPIN型、図16(b)のショットキー型は共に2カ所に注入阻止層が必要なところにある。図16(a)のPIN型において注入阻止層である n層 5 は電子を透明電極6に導くと同時にホールが i 層4に注入するのを阻止する特性が必要である。どちらかの特性を逸すれば光電流が低下したり、光が入射しない時の電流(以下暗電流と記す)が発生、増加することになりSN比の低下の原因になる。この暗電流はそれ自信がノイズと考えられると同時にショットノイズと呼ばれるゆらぎ、いわゆる量子ノイズを含んでおり、たとえば検出部12で暗電流を差し引く処理をしても、暗電流に伴う量子ノイズを小さくすることはできない。通常この特性を向上させるため i 層4や n

10

20

30

40

10

20

30

40

50

層 5 の成膜の条件や、作成後のアニールの条件の最適化を図る必要がある。しかし、もう一つの注入阻止層であるp層 3 についても電子、ホールが逆であるが同等の特性が必要であり、同様に各条件の最適化が必要である。通常、前者n層の最適化と後者p層の最適化の条件は同一でなく、両者の条件を同時に満足させるのは困難である。つまり、同一光センサ内に二カ所の注入阻止層が必要なことは高SN比の光センサの形成を困難にする。

[ 0 1 0 0 ]

これは図16(b)のショットキー型においても同様である。また図16(b)のショットキー型においては片方の注入阻止層にショットキーバリア層を用いているが、これは下部電極2とi層4の仕事関数の差を利用するもので、下部電極2の材料が限定されたり、界面の局在準位の影響が特性に大きく影響したりして、条件を満足させるのはさらに困難である。また、さらにショットキーバリア層の特性を向上させるために、下部電極2とi層4の間に100オングストローム前後の薄いシリコンや金属の酸化膜、窒化膜を形成することも報告されているが、これは、トンネル効果を利用し、ホールを下部電極2に導き、電子のi層4への注入を阻止する効果を向上させるもので、やはり仕事関数の差を利用しているため下部電極2の材料の限定は必要であるし、電子の注入の阻止とトンネル効果によるホールの移動という逆の性質を利用するため酸化膜や窒化膜は100オングストローム前後と非常に薄いところに限定され、かつ、厚さや膜質の制御は難しく生産性を低下させられる。

[0101]

また、注入阻止層が2カ所必要なことは生産性を低下させコストもアップする。これは注入阻止層が特性上重要な為2カ所中1カ所でもゴミ等で欠陥が生じた場合、光センサとしての特性が得られないからである。

[0102]

第2の理由を図17を用いて説明する。図17は薄膜の半導体膜で形成した電界効果型トランジスタ(TFT)の層構成を示している。TFTは光電変換装置を形成するうえで制御部の一部として利用することがある。図中、図16と同一なものは同番号で示してある。図17において、7はゲート絶縁膜であり、60は上部電極である。形成法を順を追って説明する。絶縁基板1上にゲート電極(G)として働く下部電極2、ゲート絶縁膜7、1層4、n層5、ソース、ドレイン電極(S、D)として働く上部電極60を順次成膜し、上部電極60をエッチングしてソース、ドレイン電極を形成し、その後n層5をエッチングしてチャネル部を構成している。TFTの特性はゲート絶縁膜7と1層4の界面の状態に敏感で通常その汚染を防ぐために同一真空内で連続に堆積する。

[0103]

従来の光センサをこのTFTと同一基板上に形成する場合、この層構成が問題となりコストアップや特性の低下を招く。この理由は図16に示した光センサの構成が、図16(a)のPIN型が電極/p層/i層/n層/電極、図16(b)のショットキー型が電極/i層/n層/電極という構成であるのに対し、TFTは電極/絶縁膜/i層/n層/電極という構成で両者が異なるからである。これは同一プロセスで形成できないことを示し、プロセスの複雑化による歩留まりの低下、コストアップを招く。また、i層/n層を共通化するにはゲート絶縁膜7やp層3のエッチング工程が必要となり、先に述べた光センサの重要な層である注入阻止層のp層3とi層4が同一真空内で成膜できなかったり、TFTの重要なゲート絶縁膜7とi層4の界面がゲート絶縁膜のエッチングにより汚染されたりして、特性の劣化やSN比の低下の原因になる。

[0104]

また、前述した図16(b)のショットキー型の特性を改善するため下部電極2とi層4の間に酸化膜や窒化膜を形成したものは膜構成の順は同一であるが先に述べたように酸化膜や窒化膜は100オングストローム前後である必要がありゲート絶縁膜と共用することは困難である。

[0105]

図18に、ゲート絶縁膜とTFTの歩留まりについて、我々が実験した結果を示す。ゲ

ート絶縁膜厚が1000オングストローム以下で歩留まりは急激に低下し、800オングストロームで歩留まりは約30%、500オングストロームで歩留まりは0%、250オングストロームではTFTの動作すら確認できなかった。トンネル効果を利用した光センサの酸化膜や窒化膜と、電子やホールを絶縁しなければならないTFTのゲート絶縁膜を共用化することは明らかに困難であり、これをデータが示している。

[0106]

またさらに、図示していないが電荷や電流の積分値を得るのに必要となる素子である容量素子(以下コンデンサと記す)を光センサと同一の構成でリークが少ない良好な特性のものを作るのは難しい。コンデンサは2つの電極間に電荷を蓄積するのが目的なため電極間の中間層には必ず電子とホールの移動を阻止する層が必要であるのに対し、従来の光センサは電極間に半導体層のみ利用しているため熱的にリークの少ない良好な特性の中間層を得るのは難しいからである。

10

[0107]

このように光電変換装置を構成するうえで重要な素子であるTFTやコンデンサとプロセス的にまたは特性的にマッチングが良くないことは複数の光センサを二次元に多数配置し、この光信号を順次検出するようなシステム全体を構成するうえで工程が多くかつ複雑になるため歩留まりが非常に悪く、低コストで高性能多機能な装置を作る上で問題になる

[0108]

これに対して、図4、5、13、14、15を参照して前述した光電変換素子を用いれば、上述した課題は解決できる。

20

[0109]

前出の図1に係る実施形態では、例えば右上の基板上の素子アレイのみを走査・検出し、他の3板の基板の素子アレイは走査検出を行わないように駆動することも出来る。

[0110]

しかしながら、右上の基板150の素子アレイのうち、例えば100本の制御配線g1、g2、…g100および100本の信号配線Sig1、Sig2、…Sig100の交点にある素子のみから信号検出を行うことはできない。よって、その交点にある素子の信号のみを再生する場合には、右上の基板150の全素子から信号を読み出した後、必要な信号のみを再生処理する方法が採られる。

30

[0111]

次に述べる実施形態では、走査回路チップ及び検出用チップがデコーダを有しており、コントローラーからのアドレス情報を基に選択すべき制御配線と信号配線とが定められ、 それに接続された端子のみが選択される構成の装置である。

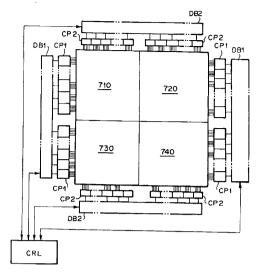

[0112]

図19において、光電変換素子アレイは4つの基板710、720、730、740上に形成されており、制御配線は左右にそれぞれ10個設けられた走査選択回路チップCP1に接続され、信号配線は上下にそれぞれ10個設けられた検出用ICチップCP2に接続されている。

[ 0 1 1 3 ]

40

コントローラーCRLは走査選択すべき光電変換素子のアドレス情報を配線回路DB1、DB2を介してそのアドレス情報に対応した端子をもつチップCP1、CP2に選択的にアドレス情報を供給する。アドレス情報が供給されたチップCP1、CP2はアドレス情報をデコードして選択すべき端子をイネーブルとする。こうして必要な領域の光電変換素子からの信号のみを処理再生するマスキング処理が容易に行われる。

[0114]

以上のように各チップがデコーダを有しているので、同じ構成の走査選択回路チップを 左右いずれにも配することができる。これは検出用ICチップについても同じである。

[ 0 1 1 5 ]

又、デコーダを有することにより、必要に応じて複数本の制御配線を同時に選択したり

、 所 定 数 本 飛 び 越 し て 走 査 選 択 し た り す る こ と も で き る 。 こ れ は 検 出 用 I C チ ッ プ に つ い ても同じことがいえる。

#### [0116]

勿論、全制御配線と全信号配線を特定するアドレス情報を時系列に各回路に入力すれば 図3と同様に走査方向を定めることができる。

#### [ 0 1 1 7 ]

以上本発明の実施形態について説明したが、本発明の他の好適な実施の態様を以下のと おり列挙する。

### [0118]

2 次元状に配された複数の光電変換素子を有する基板を複数隣接して配置した光電変換 装置において、走査回路又は検出用回路の少なくともいずれか一方が該光電変換装置の対 向する2辺に配され、該2辺に配された回路の走査方向が同じ方向に設定可能であること を特徴とする光電変換装置。

# [0119]

また、該走査方向は、シフトレジスタのシフト方向により定められることを特徴とする 光電変換装置。

### [0120]

また、該走査方向は、マルチプレクサの切換え順序により定められることを特徴とする 光電変換装置。

# [0121]

また、該走査回路は、デコーダを有し、入力されるアドレス情報により走査方向が定め られることを特徴とする光電変換装置。

### [0122]

また、該検出用回路は、デコーダを有し、入力されるアドレス情報により走査方向が定 められることを特徴とする光電変換装置。

# [0123]

また、該検出用回路は、光電変換素子からの信号をパラレルに入力し、走査方向に応じ てシリアルに出力することを特徴とする光電変換装置。

#### [ 0 1 2 4 ]

また、該検出用回路は、光電変換素子からの信号を走査方向に応じてシリアルに入力し シリアルに出力することを特徴とする光電変換装置。

# [ 0 1 2 5 ]

また、該走査回路と該検出用回路は、複数のICチップでそれぞれ構成されていること を特徴とする光電変換装置。

# [0126]

また、該走査回路又は該検出用回路の少なくともいずれか一方に走査方向を定める為の 信号が入力されることを特徴とする光電変換装置。

### [0127]

また、前記基板は4つであり、前記光電変換装置の対向する2辺に該走査回路が、別の 対向する2辺に検出用回路が設けられていることを特徴とする光電変換装置。

# [0128]

また、該走査回路及び検出用回路は、フレキシブル配線基板に実装されたICチップか らなることを特徴とする光電変換装置。

# [0129]

また、該走査回路及び検出用回路は、該基板又は該基板を支持するマザーボード上に実 装されたICチップであることを特徴とする光電変換装置。

#### [ 0 1 3 0 ]

また、該光電変換素子上に光変換体が配されていることを特徴とする光電変換装置。

#### [ 0 1 3 1 ]

また、該光変換体は、蛍光体であることを特徴とする光電変換装置。

10

20

30

40

### [ 0 1 3 2 ]

また、2次元的に配列された複数の光電変換素子を搭載した基板を、2次元的に縦横2枚ずつ4枚、前記光電変換素子部が平面的に隣り合うように配列して貼り合わせて構成され、かつ、前記貼り合わせた4枚の基板の中で、隣り合わない2枚の基板はそれぞれ同一構成の基板を平面上で180°回転した位置関係で配置されており、かつ、前記基板は、それぞれ同一方向に走査されることを特徴とする光電変換装置。

#### [ 0 1 3 3 ]

また、前記基板は、複数の光電変換素子が平面的に配列された光電変換素子部が形成された辺と、該光電変換素子部に接続される回路部が形成された辺とを有し、該基板の、それぞれの前記光電変換素子部が平面的に近接して隣り合うように配列して貼り合わせて構成したことを特徴とする光電変換装置。

[0134]

また、前記光電変換素子は、第一の電極層、絶縁層、半導体層、第1導電型のキャリアの注入を阻止する半導体層、及び第二の電極層を積層した素子であることを特徴とする光電変換装置。

[ 0 1 3 5 ]

また、2次元的に配列された光電変換素子を搭載した複数の基板を、それぞれの前記光電変換素子部が平面的に隣り合うように配置して貼り合わせて構成した光電変換装置であり、前記貼り合わせる複数の基板の配置を、それぞれの基板の光電変換部となる半導体層を堆積させた時の基板配置と同じ配置として、前記複数の基板を貼り合わせて構成したことを特徴とする光電変換装置。

[0136]

また、前記光電変換素子の半導体層は、非単結晶半導体層であることを特徴とする光電変換装置。

[0137]

また、前記基板は、複数の光電変換素子が平面的に配列された光電変換素子部が形成された辺と、該光電変換素子部に接続される回路部が形成された辺とを有し、該基板の複数枚を、それぞれの前記光電変換素子部が平面的に近接して隣り合うように配置して貼り合わせて構成したことを特徴とする光電変換装置。

[0138]

また、前記基板上には、第1の電極層、絶縁層、半導体層、第1導電型のキャリアの注入を阻止する半導体層、及び第2の電極層を積層した光電変換素子と、前記半導体層に入射した信号光により発生した第1導電型のキャリアを前記半導体層に蓄積し、前記第1導電型と異なる第2導電型のキャリアを前記第2の電極層に導く方向に前記光電変換素子に電界を与える手段と、前記光電変換素子に電界を与えて、前記第1導電型のキャリアを前記半導体層から前記第2の電極層に導く方向に前記光電変換素子に電界を与えるリフレッシュ手段と、前記手段による光電変換動作中に前記半導体層に蓄積された前記第1導電型のキャリアもしくは前記第2の電極層に導かれた前記第2導電型のキャリアを検出する為の信号検出部と、を有することを特徴とする光電変換装置。

[0139]

また、前記光電変換素子の上部に光変換体を配置し、 X 線レントゲン装置を構成したことを特徴とする光電変換装置。

[0140]

また、該光変換体は、蛍光体であることを特徴とする光電変換装置。

[ 0 1 4 1 ]

また、上記光電変換装置と、高エネルギー線照射装置とを有することを特徴とする撮像 装置。

[0142]

また、前記高エネルギー線は、X線であることを特徴とする撮像装置。

[0143]

20

10

30

40

さらに、2次元的に配列された光電変換素子を搭載した複数の基板を、それぞれの前記 光電変換素子が平面的に隣り合うように配置して貼り合わせた光電変換装置の製造方法に おいて、共通のCVD装置内において、共通の治具の表面上に、前記複数の基板を所定の 向きで平面的に配置して、前記光電変換素子となる半導体層を堆積させる堆積工程と、該 半導体層が堆積された複数の基板を前記堆積工程における前記基板の向きと同じ向きとな るように共通のマザーボード上に貼り合わせる工程とを含むことを特徴とする光電変換装 置の製造方法。

[0144]

特に、前記光電変換素子の半導体層は、非単結晶半導体層とするとよい。

[0145]

また、前記各基板の隣接する2辺に偏って前記複数の光電変換素子が平面的に配列されており、前記各基板の別の隣接する2辺に偏って前記各光電変換素子を走査する走査回路と、前記走査回路の走査により各光電変換素子から出力される信号を検出する検出用回路とが形成されており、前記各基板を、それぞれ、前記光電変換素子部が偏って形成された隣接する2辺のうち少なくともいずれか1辺が隣り合うように貼り合わせている。

[0146]

また更に、本発明の他の好適な実施の態様は、以下の手段を提供する。

[0147]

[1] 2次元的に配列された複数の光電変換素子を搭載した基板を、2次元的に縦横2枚ずつ4枚、前記光電変換素子部が平面的に隙間無く隣り合うように配列して貼り合わせて構成され、かつ、前記貼り合わせた4枚の基板の中で、隣合わない2枚の基板はそれぞれ同一構成の基板を平面上で180°回転した位置関係で配置されており、かつ、前記基板は、それぞれ同一方向に走査されることを特徴とする光電変換装置。

[ 0 1 4 8 ]

[2]前記基板は、複数の光電変換素子が平面的に配列された光電変換素子部が形成された辺と、該光電変換素子部に接続される回路部が形成された辺とを有し、該基板の、それぞれの前記光電変換素子部が平面的に隣り合うように配列して貼り合わせて構成した[1]記載の光電変換装置。

[0149]

[3]前記基板上には、第1の電極層、絶縁層、光電変換半導体層、第1導電型のキャリアの注入を阻止する半導体層、及び第2の電極層を積層した光電変換素子と、前記光電変換半導体層に入射した信号光により発生した第1導電型のキャリアを前記光電変換半導体層に留まらせ、前記第1導電型と異なる第2導電型のキャリアを前記第2の電極層に導く方向に前記光電変換素子に電界を与える光電変換手段と、前記光電変換素子に電界を与えて、前記第1導電型のキャリアを前記光電変換半導体層から前記第2の電極層に導く方向に前記光電変換素子に電界を与えるリフレッシュ手段と、前記光電変換手段による光電変換動作中に前記光電変換半導体層に蓄積された前記第1導電型のキャリアもしくは前記第2の電極層に導かれた前記第2導電型のキャリアを検出する為の信号検出部と、を有する[1]又は[2]に記載の光電変換装置。

[0150]

[4]前記光電変換素子の上部に蛍光体を配置し、X線レントゲン装置を構成した上記 [1]~[3]のいずれかに記載の光電変換装置。

[0151]

上記[1]、[2]の手段によれば、作製する時の基板1枚あたりの歩留まりを向上させ、かつ基板1枚あたりの不具合による損失額は小さくすることにより、結果的に大面積の光電変換装置のコストを低減できるという作用が得られる。

[0152]

また、検査工程の効率の向上、及びそれに伴うスループットの向上、及び部品点数の削減が可能となり、結果的に大面積の光電変換装置のコストをさらに低減することができるという作用が得られる。

10

20

30

40

#### [ 0 1 5 3 ]

さらに、すべての光電変換素子を同一方向に走査し、信号処理を簡単な装置で高速に行うことが可能となり、その結果、光電変換装置のコスト低減と性能の向上をさせることができる。

# [0154]

また、上記[3]の手段によれば、上記[1]、[2]で説明した作用に加えて、光電変換素子の注入阻止層が一か所のみで光の入射量を検出することができ、プロセスの最適化が容易で歩留まりの向上が図れ、製造コストの低減が可能で、SN比の高い低コストの光電変換装置を供給することができるという作用が得られる。

## [0155]

また、上記 [4] の手段によれば、上記 [1] ~ [3] で説明した作用に加えて、従来の X 線フィルムと異なり、出力を瞬時に映し出すことが可能となり、更に画像処理及びデータの保管も可能となる。又、感度もフィルムに比べて良く、人体に影響の少ない微弱な X 線で鮮明な画像を得ることができるという作用が得られる。

## [0156]

成膜時の基板の配置に応じて、基板を貼り合わせれば、少なくとも、異なる基板上の隣り合う位置に存在する光電変換素子の特性を連続的に等しくすることができるという作用が得られる。

### 【符号の説明】

# [0157]

1 0 0 、 1 5 0 : 基板、 g 1 ~ g 1 0 0 0 : 制御配線、 s i g 1 ~ s i g 1 0 0 0 : 信号配線、 S R 1 - 1 ~ S R 1 - 1 0 : 走査回路チップ、 I C 1 ~ I C 1 0 : 検出用集積回路チップ

# 【図1】

# 【図2】

10

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

# 【図12】

【図15】

【図13】

【図14】

【図16】

S D 60 5 6 7

【図19】

# フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 4 N 5/335 W H 0 4 N 5/335 E

(72)発明者 亀島 登志男

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 遠藤 忠夫

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 竹田 慎市

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 2G088 EE03 FF02 GG19 GG20 GG21 JJ05 JJ33 JJ37

4M118 AB01 BA05 CA14 CA32 CB06 CB11 CB14 FB03 FB13 FB16

FB24 HA24 HA25 HA27 HA29 5C024 AX01 AX11 CY47 GX09 GY31