#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4265575号 (P4265575)

(45) 発行日 平成21年5月20日(2009.5.20)

(24) 登録日 平成21年2月27日(2009.2.27)

| (51) Int.Cl. |        |           | FΙ   |       |      |

|--------------|--------|-----------|------|-------|------|

| HO1L         | 23/12  | (2006.01) | HO1L | 23/12 | 501P |

| HO1L         | 21/822 | (2006.01) | HO1L | 27/04 | С    |

| HO1L         | 27/04  | (2006.01) | H05K | 1/02  | J    |

| H05K         | 1/02   | (2006.01) |      |       |      |

請求項の数 7 (全 12 頁)

(21) 出願番号 特願2005-180400 (P2005-180400) (22) 出願日 平成17年6月21日 (2005.6.21) (65) 公開番号 特開2007-5350 (P2007-5350A) (43) 公開日 平成19年1月11日 (2007.1.11) 審査請求日 平成18年5月12日 (2006.5.12) ||(73)特許権者 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

||(74)代理人 100107836

弁理士 西 和哉

(74)代理人 100064908

弁理士 志賀 正武

(74)代理人 100101465

弁理士 青山 正和

|(72)発明者 橋元 伸晃

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

審査官 石野 忠志

最終頁に続く

## (54) 【発明の名称】半導体チップおよび電子機器

#### (57)【特許請求の範囲】

### 【請求項1】

電子回路が形成された半導体チップの表面に応力緩和層が形成され、前記応力緩和層の 表面に前記電子回路の接続端子の再配置配線が形成されてなる半導体チップであって、

前記応力緩和層の前記電子回路側に形成された第1電極と、前記応力緩和層を挟んで前記電子回路の反対側に形成された第2電極との間に、前記応力緩和層が配置されて、キャパシタが形成され、

前記電子回路と前記応力緩和層との間に、前記半導体チップのパッシベーション膜が形成され。

前記第1電極は、前記パッシベーション膜の前記電子回路側に形成されていることを特徴とする半導体チップ。

## 【請求項2】

前記第1電極は、前記電子回路の前記接続端子であることを特徴とする請求項1に記載の半導体チップ。

#### 【請求項3】

前記第1電極と前記第2電極との間に、複数の前記応力緩和層が配置されていることを特徴とする請求項1または請求項2に記載の半導体チップ。

#### 【請求項4】

前記第2電極の表面に、突起電極が形成されていることを特徴とする請求項1ないし請求項3のいずれかに記載の半導体チップ。

20

#### 【請求項5】

前記応力緩和層は、誘電体材料にセラミクスの粉末を分散させた材料からなることを特徴とする請求項1ないし請求項4のいずれかに記載の半導体チップ。

#### 【請求項6】

前記誘電体材料は、感光性を有する樹脂材料であることを特徴とする請求項 5 に記載の 半導体チップ。

#### 【請求項7】

<u>請</u>求項1ないし請求項6のいずれかに記載の半導体チップを備えたことを特徴とする電子機器。

【発明の詳細な説明】

10

## 【技術分野】

#### [0001]

本発明は、電子基板、電子基板の製造方法および電子機器に関するものである。

#### 【背景技術】

## [0002]

携帯電話やパーソナルコンピュータ等の電子機器には、電子回路が形成された半導体チップ(電子基板)が搭載されている。この半導体チップは、抵抗やコイル、キャパシタ等の受動素子とともに利用される場合がある。そこで、半導体チップを実装する基板にキャパシタを製造する技術が提案されている(例えば、特許文献1ないし特許文献3参照)。また半導体チップ上にMOSキャパシタを製造する技術が提案されている(例えば、特許文献4参照)。

20

【特許文献 1 】特開 2 0 0 0 - 3 4 0 9 5 5 号公報

【特許文献 2 】特開 2 0 0 0 - 3 5 3 8 7 5 号公報

【特許文献3】特開2001-156456号公報

【特許文献4】特開平2-162820号公報

# 【発明の開示】

【発明が解決しようとする課題】

## [0003]

しかしながら、半導体チップを実装する基板にキャパシタを製造する技術では、半導体チップ上のトランジスタから離れてキャパシタが配置されるため、応答特性や高周波特性を確保することが困難である。また、半導体チップ上にMOSキャパシタを製造する技術では、ゲート膜を誘電層として利用するので、キャパシタの容量値を確保することが困難である。さらに、キャパシタ形成領域にはトランジスタが形成できないため、キャパシタ形成領域の占有面積が必要で、キャパシタ形成した半導体チップはチップサイズが大きくなってしまう課題があった。

#### [0004]

本発明は、上記課題を解決するためになされたものであって、電気特性に優れ、キャパシタ形成してもチップサイズが大きくならない電子基板およびその製造方法の提供を目的とする。また電気特性に優れた電子機器の提供を目的とする。

#### 【課題を解決するための手段】

40

#### [0005]

上記目的を達成するため、本発明に係る電子基板は、電子回路が形成された電子基板の表面に応力緩和層が形成され、前記応力緩和層の表面に前記電子回路の接続端子の再配置配線が形成されてなる電子基板であって、前記応力緩和層の裏面側に形成された第1電極と、前記応力緩和層の表面側に形成された第2電極との間に、誘電体材料が配置されて、キャパシタが形成されていることを特徴とする。また前記誘電体材料は、前記応力緩和層であることが望ましい。

この構成によれば、再配置配線の形成工程において、メッキやフォトリソグラフィ等を 利用して、第2電極を正確に形成することが可能になる。よって、所望の特性を備えたキャパシタを形成することができる。また電子基板の電子回路に近接してキャパシタが配置

されるので、キャパシタの応答特性や高周波特性を確保することができる。さらに応力緩和層を誘電層として利用するので、キャパシタの容量値を自在に設定することができる。したがって、電気特性に優れた電子基板を提供することができる。さらに、キャパシタ形成領域にもトランジスタが形成できるため、キャパシタ形成領域の占有面積が必要なく、キャパシタ形成した半導体チップはチップサイズが大きくならない効果がある。

#### [0006]

また、前記第1電極と前記第2電極との間に、複数の前記応力緩和層が配置されていて もよい。

この構成によれば、キャパシタの容量値をより自在に設定することができるので、電気 特性に優れた電子基板を提供することができる。

## [0007]

また、前記第2電極の表面に、突起電極が形成されていることが望ましい。

この構成によれば、キャパシタから突起電極までの配線長が最短となり、インピーダンスマッチングに有利となる。したがって、電気特性に優れた電子基板を提供することができる。

#### [00008]

また、前記電子基板と前記応力緩和層との間に、前記電子基板のパッシベーション膜が 形成され、前記第1電極は、前記パッシベーション膜の裏面側に形成されていることが望ましい。

また、前記第1電極は、前記電子回路の前記接続端子であってもよい。

これらの構成によれば、電子回路からキャパシタまでの配線長が最短となり、配線による寄生容量やスタブ等を最小にすることができる。したがって、電気特性に優れた電子基板を提供することができる。

## [0009]

また、前記応力緩和層は、前記誘電体材料にセラミクスの粉末を分散させた材料からなることが望ましい。

高誘電体材料であるセラミクスの粉末を分散させることにより、キャパシタの誘電率を向上させることが可能になる。したがって、電気特性に優れた電子基板を提供することができる。

## [0010]

また、前記誘電体材料は、感光性を有する樹脂材料であることが望ましい。

この構成によれば、フォトリソグラフィを用いて応力緩和層を正確に形成することが可能になり、所望の特性を備えたキャパシタを形成することができる。したがって、電気特性に優れた電子基板を提供することができる。

## [0011]

一方、本発明に係る電子基板の製造方法は、電子回路が形成された電子基板の表面に応力緩和層が形成され、前記応力緩和層の表面に前記電子回路の接続端子の再配置配線が形成され、前記応力緩和層の裏面側に形成された第1電極と、前記応力緩和層の表面側に形成された第2電極との間に、誘電体材料が配置されて、キャパシタが形成されてなる電子基板の製造方法であって、前記応力緩和層の形成工程において、前記誘電体材料として前記応力緩和層を配置することを特徴とする。また前記再配置配線の形成工程において、前記第2電極を形成することを特徴とする。

この構成によれば、再配置配線の形成工程において、メッキやフォトリソグラフィ等を利用して、第2電極を正確に形成することが可能になる。また応力緩和層を誘電層として利用するので、キャパシタの容量値を自在に設定することができる。したがって、所望の特性を備えたキャパシタを形成することが可能になり、電気特性に優れた電子基板を提供することができる。また、低コストでキャパシタを形成することができる。さらに、キャパシタ形成領域にもトランジスタが形成できるため、キャパシタ形成領域の占有面積が必要なく、キャパシタ形成した半導体チップはチップサイズが大きくならない効果がある。

## [0012]

30

10

20

40

また、本発明に係る他の電子基板の製造方法は、電子回路が形成された電子基板の表面に応力緩和層が形成され、前記応力緩和層の表面に前記電子回路の接続端子の再配置配線が形成され、前記応力緩和層の裏面側に形成された第1電極と、前記応力緩和層の表面側に形成された第2電極との間に、誘電体材料からなる前記応力緩和層が配置されて、キャパシタが形成されてなる電子基板の製造方法であって、前記第2電極をトリミングして、前記キャパシタの特性を調整する工程を有することを特徴とする。

この構成によれば、所望の特性を備えたキャパシタを形成することが可能になり、電気 特性に優れた電子基板を提供することができる。

## [0013]

一方、本発明に係る電子機器は、上述した電子基板を備えたことを特徴とする。 この構成によれば、電気特性に優れた電子機器を提供することができる。

【発明を実施するための最良の形態】

### [0014]

以下、本発明の実施形態につき、図面を参照して説明する。なお、以下の説明に用いる 各図面では、各部材を認識可能な大きさとするため、各部材の縮尺を適宜変更している。

#### (第1実施形態)

本実施形態に係る半導体チップ(電子基板)は、電子回路が形成された半導体チップの表面に応力緩和層が形成され、その応力緩和層の表面に電子回路の接続端子の再配置配線が形成されたものである。そこで最初に、接続端子の再配置配線および応力緩和層について説明する。

[0015]

### (再配置配線)

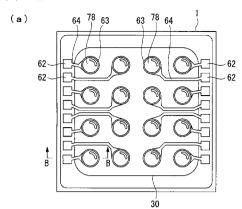

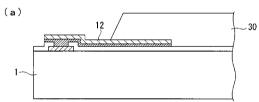

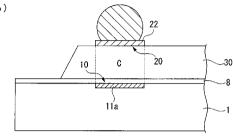

図1は再配置配線の説明図であり、図1(a)は半導体チップの平面図であり、図1(b)は図1(a)のB-B線における側面断面図である。図1(b)に示すように、電子回路が形成された半導体チップの表面には、電子回路を保護するためのパッシベーション膜8が形成されている。また半導体チップの表面には、電子回路を外部に電気的接続するための接続端子62が形成されている。なお接続端子62の表面には、パッシベーション膜8の開口部が形成されている。

### [0016]

図1(a)に示すように、半導体チップ1の周縁部に沿って、複数の接続端子62が整列配置されている。なお半導体チップの小型化により、隣接する接続端子62間のピッチは非常に狭くなっている。この半導体チップ1を相手側基板に実装すると、隣接する接続端子62間に短絡が発生するおそれがある。そこで接続端子62間のピッチを広げるため、接続端子62の再配置配線64が形成されている。

## [0017]

具体的には、半導体チップ1の表面中央部に、複数のパッド63がマトリクス状に配列形成されている。そのパッド63に対して、接続端子62の再配置配線64が接続されている。これにより、狭ピッチの接続端子62が中央部に引き出されて広ピッチ化されている。このような半導体チップの形成には、ウェハの状態において一括して再配置配線および樹脂封止を行なってから個々の半導体チップに分離する、W-CSP(Wafer level Chip Scale Package)技術が利用されている。

[0018]

このW - CSP技術を用いて半導体チップを形成する場合には、半導体チップを実装する相手側基板と半導体チップとの熱膨張係数の差によって生ずる応力を緩和する必要がある。そこで図1(b)に示すように、感光性ポリイミドやBCB(ベンゾシクロブテン)、フェノールノボラック樹脂等の感光性樹脂からなる応力緩和層30が、半導体チップの表面中央部に形成されている。そして、その応力緩和層30の表面に、上述したパッド63が形成されている。

#### [0019]

パッド63の表面にはバンプ78が形成されている。このバンプ78は、例えばハンダ

10

20

30

40

バンプであり、印刷法等によって形成されている。そしてこのバンプ78が、相手側基板の接続端子に対して、リフローやFCB(Flip Chip Bonding)等により実装される。なお異方導電性フィルム等を介して、半導体チップ1のパッド63を相手側基板の接続端子に実装することも可能である。

## [0020]

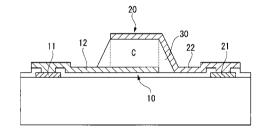

(キャパシタを備えた電子基板)

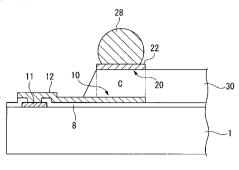

図2は、第1実施形態に係る半導体チップの側面断面図である。第1実施形態に係る半導体チップ(電子基板)は、応力緩和層30の裏面に形成された第1電極10と、応力緩和層の表面に形成された第2電極20との間に、誘電体材料からなる応力緩和層30が配置されて、キャパシタCが形成されたものである。

## [0021]

接続端子11の表面から半導体チップ1の表面中央部に向かって、Cu等の導電性材料からなる第1層配線12が延設されている。この第1層配線12の先端部は、応力緩和層30を挟んで第2層配線22と対向するように配置されている。なお第1層配線12は後述する下地層の表面に形成されているが、図2では下地層の記載を省略している。

#### [0022]

その第1層配線12の先端部を覆うように、応力緩和層30が形成されている。応力緩和層30は、上記のように感光性ポリイミドやBCB(ベンゾシクロブテン)、フェノールノボラック樹脂等の誘電体材料で構成されている。

### [0023]

その応力緩和層30の表面に、Cu等の導電性材料からなる第2層配線22が形成されている。この第2層配線22は上述したパッド状に形成され、応力緩和層30を挟んで第1層配線12の先端部と対向するように配置されている。なお第2層配線22は後述する下地層の表面に形成されているが、図2では下地層の記載を省略している。

#### [0024]

そして、半導体チップ1の表面に垂直な方向から見た場合(平面視)において、第1層配線12と第2層配線22とが重なる領域(重畳領域)に、キャパシタCが形成されている。すなわち、重畳領域における第1層配線12が第1電極10として機能し、重畳領域における第2層配線22が第2電極20として機能する。その第1電極10と第2電極20との間に、誘電体材料からなる応力緩和層30が配置されて、キャパシタCが形成されている。

## [0025]

なおパッド状に形成された第2層配線22の表面には、上述したバンプ(突起電極)28が形成されている。これにより、半導体チップの電子回路と相手側基板との間に、キャパシタCが配置されることになる。そして、第2電極20の表面にバンプ28が形成されているので、キャパシタCからバンプ28までの配線長が最短になり、インピーダンスマッチングに有利となる。

#### [0026]

なお、第1電極10と第2電極20との間に、応力緩和層30とは別の誘電体材料層を 形成してもよい。その誘電体材料層として、例えばゾルゲル法により高誘電率のセラミク 10

20

30

40

ス材料層を形成することが望ましい。この構成によれば、キャパシタの誘電率をさらに向上させることができる。

#### [0027]

(電子基板の製造方法)

次に、上述した半導体チップの製造方法につき、図3および図4を用いて説明する。

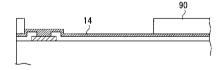

図3および図4は、本実施形態に係る半導体チップの製造方法の工程図である。ここでは、図3(a)に示すように、電子回路が形成された半導体チップの表面に、電子回路を保護するためのパッシベーション膜8と、電子回路を外部に電気的接続するための接続端子11とが形成され、接続端子11の表面にパッシベーション膜8の開口部が形成された状態から説明する。

[0028]

[0029]

次に図3(b)に示すように、下地膜14の表面にレジスト90を塗布し、フォトリソグラフィを行って、第1層配線の形成領域にレジスト90の開口部を形成する。

次に図3 (c)に示すように、下地膜14のシード層を電極として電解Cuメッキを行い、レジスト90の開口部にCuを埋め込んで第1層配線12を形成する。

[0030]

次に図3(d)に示すように、レジストを剥離する。

次に図3(e)に示すように、第1層配線12をマスクとして、下地膜14をエッチングする。このエッチングには、反応性イオンエッチング(RIE:Reactive Ion Etching)等を利用することが可能である。なお第1層配線12および下地膜14のシード層は共にCuで構成されているが、第1層配線12は下地膜14のシード層より十分に厚いので、エッチングによりシード層を完全に除去することができる。

[0031]

次に図4(a)に示すように、第1層配線12の先端部を覆うように応力緩和層30を 形成する。応力緩和層30は、印刷法やフォトリソグラフィを用いて半導体チップ1の表 面中央部に形成する。なお応力緩和層30を構成する誘電体材料として、感光性を有する 樹脂材料を採用すれば、フォトリソグラフィを用いて簡単かつ正確に応力緩和層30をパ ターニングすることができる。

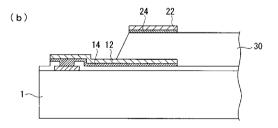

[0032]

次に図4(b)に示すように、応力緩和層30の表面に第2層配線22およびその下地層24を形成する。その具体的な方法は、上述した第1層配線12およびその下地膜14の形成方法と同様である。なお形成された第2層配線22をレーザ等でトリミングすることにより、キャパシタ特性のチューニングを行うことも可能である。

次に図4(c)に示すように、第2層配線22の表面にハンダボールを搭載してバンプ28を形成する。

[0033]

ところで第2層配線22は、図1に示す再配置配線64の形成工程において、再配置配線64と同時に形成することができる。すなわち、メッキやフォトリソグラフィ等を利用して、図4(c)に示す第2電極20を正確に形成することが可能になる。よって、所望の特性を備えたキャパシタCを形成することができる。また半導体チップ1の電子回路に近接してキャパシタCが配置されるので、キャパシタCの応答特性や高周波特性を確保す

10

20

30

40

ることができる。さらに応力緩和層30を誘電層として利用するので、キャパシタCの容量値を自在に設定することができる。したがって、電気特性に優れた半導体チップ1を提供することができる。

また再配置配線と同時に第2電極20を形成し、さらに応力緩和層30を誘電層として利用するので、低コストでキャパシタCを形成することができる。加えて、キャパシタ形成領域にもトランジスタが形成できるため、キャパシタ形成領域の占有面積が必要なく、キャパシタ形成した半導体チップはチップサイズが大きくならない効果がある。

### [0034]

(第2実施形態)

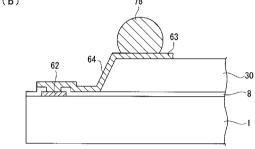

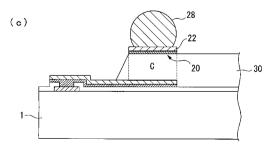

図5(a)は、第2実施形態に係る半導体チップの側面断面図である。第2実施形態では、接続端子11がキャパシタCの第1電極10として機能する点で、接続端子から延設された第1層配線が第1電極として機能する第1実施形態とは異なっている。なお第1実施形態と同様の構成となる部分については、その説明を省略する。

## [0035]

第2実施形態では、接続端子11を覆うように応力緩和層30が形成されている。そのため、応力緩和層30の一部を半導体チップ1の表面周縁部に延設するか、または予め接続端子11を半導体チップ1の表面中央部寄りに形成しておく。その応力緩和層30の表面に、第1実施形態と同様に第2層配線22が形成されている。

#### [0036]

そして、平面視において接続端子11と第2層配線22とが重なる領域(重畳領域)に、キャパシタCが形成されている。すなわち、重畳領域における接続端子11が第1電極10として機能し、重畳領域における第2層配線22が第2電極20として機能する。その第1電極10と第2電極20との間に、誘電体材料からなる応力緩和層30が配置されて、キャパシタCが形成されている。

#### [0037]

第2実施形態では、接続端子11がキャパシタCの第1電極10として機能するので、 半導体チップの電子回路に含まれるトランジスタの直近にキャパシタCを形成することが 可能になる。そのため、トランジスタからキャパシタまでの配線長が最短となり、配線に よる寄生容量やスタブ等を最小にすることができる。特に、高周波領域での電気特性(ロ ス、ノイズ輻射)が向上するので、キャパシタの放充電特性が向上し、キャパシタを小型 化することが可能になる。したがって、システム全体の電気特性の向上および小型化を実 現することができる。

#### [0038]

図5(b)は、第2実施形態に係る半導体チップの変形例である。この変形例では、半導体チップの電子回路の内部配線11aが、パッシベーション膜8の裏面側に形成されている。そして、平面視において内部配線11aと第2層配線22とが重なる領域(重畳領域)に、キャパシタCが形成されている。すなわち、重畳領域における内部配線11aが第1電極10として機能し、重畳領域における第2層配線22が第2電極20として機能する。その第1電極10と第2電極20との間に、応力緩和層30およびパッシベーション膜8が配置されて、キャパシタCが形成されている。

この変形例では、内部配線11aの表面におけるパッシベーション膜8を開口する必要がないので、製造コストを低減することができる。

### [0039]

# (第3実施形態)

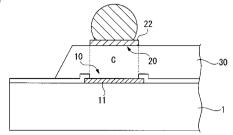

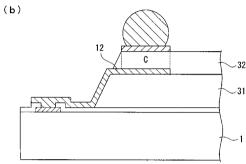

図 6 (a)は、第 3 実施形態に係る半導体チップの側面断面図である。第 3 実施形態では、複数の応力緩和層を誘電層に利用してキャパシタ C が形成されている点で、一つの応力緩和層を誘電層に利用してキャパシタ C が形成されている第 1 実施形態とは異なっている。なお第 1 実施形態と同様の構成となる部分については、その説明を省略する。

#### [0040]

第3実施形態では、半導体チップ1の表面中央部に第1応力緩和層31が形成され、そ

10

20

30

40

の第1応力緩和層31の表面に第2応力緩和層32が形成されている。そして、第1応力緩和層31の裏面に第1層配線12が形成され、第2応力緩和層32の表面に第2層配線22が形成されている。

#### [0041]

そして、平面視において第1層配線12と第2層配線22とが重なる領域(重畳領域)に、キャパシタCが形成されている。すなわち、重畳領域における第1層配線12が第1電極10として機能し、重畳領域における第2層配線22が第2電極20として機能する。その第1電極10と第2電極との間に、誘電体材料からなる第1応力緩和層31および誘電体材料からなる第2応力緩和層32が配置されて、キャパシタCが形成されている。

#### [0042]

このように、複数の応力緩和層を形成すれば、キャパシタの容量値を自在に設定することができる。例えば、第1応力緩和層31および第2応力緩和層32を誘電層に利用した第3実施形態では、第1応力緩和層31のみを誘電層に利用した第1実施形態と比べて、容量値の小さなキャパシタを形成することができる。

また、誘電率の異なる複数の応力緩和層を形成すれば、キャパシタの容量をより自在に設定することができる。例えば、図 6 ( b ) に示すように薄肉の第 2 応力緩和層 3 2 のみを誘電層に利用すれば、厚肉の第 1 応力緩和層 3 1 のみを誘電層に利用した第 1 実施形態と比べて、容量値の大きなキャパシタを形成することができる。

#### [0043]

なお図6(a)の第1層配線12に代えて、図5(a)に示すように、接続端子11を 第1電極10として機能させてもよい。また図5(b)に示すように、内部配線11aを 第1電極10として機能させてもよい。

## [0044]

#### (第4実施形態)

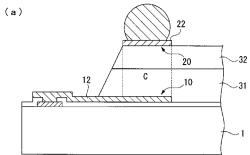

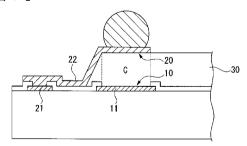

図7は、第4実施形態に係る半導体チップの側面断面図である。第4実施形態では、半導体チップの電子回路の内部にキャパシタが配置されている点で、半導体チップの電子回路と相手側基板との間にキャパシタが配置されている第1実施形態とは異なっている。なお第1実施形態と同様の構成となる部分については、その説明を省略する。

### [0045]

第4実施形態では、第1接続端子11の表面から第1層配線12が延設されている。その第1層配線12の先端部を覆うように、応力緩和層30が形成されている。そして、第1接続端子11とは別の第2接続端子21から、応力緩和層30の表面にかけて、第2層配線22が延設されている。

#### [0046]

そして、平面視において第1層配線12と第2層配線22とが重なる領域(重畳領域)に、キャパシタCが形成されている。すなわち、重畳領域における第1層配線12が第1電極10として機能し、重畳領域における第2層配線22が第2電極20として機能する。その第1電極10と第2電極との間に、誘電体材料からなる応力緩和層30が配置されて、キャパシタCが形成されている。これにより、いずれも電子回路から引き出された第1接続端子11と第2接続端子21との間に、キャパシタCが配置された状態となっている。このように、電子回路と相手側基板との間だけでなく、電子回路の内部にもキャパシタCを配置することができる。

### [0047]

なお第1層配線12に代えて、図5(a)に示すように、接続端子11を第1電極10として機能させてもよい。また図5(b)に示すように、内部配線11aを第1電極10として機能させてもよい。また図6(a)に示すように、複数の応力緩和層31,32を誘電層に利用してもよい。

## [0048]

#### (第5実施形態)

図8は、第5実施形態に係る半導体チップの側面断面図である。

10

20

30

第5実施形態に係る半導体チップは、図1に示す再配置配線構造に対して、図5(a)に示すキャパシタ構造を付加したものである。これにより、図8に示すように、半導体チップ1の第1接続端子11および第2接続端子21が、相手側基板の一つの実装端子(不図示)に接続されるようになっている。そして、その実装端子と第1接続端子11との間に、キャパシタCが配置された状態となっている。

このように、上記各実施形態の構造を組み合わせることにより、様々な態様でキャパシタを配置することができる。

## [0049]

(電子機器)

次に、上述した半導体チップ(電子基板)を備えた電子機器の例につき、図9を用いて説明する。

図9は、携帯電話の斜視図である。上述した半導体チップは、携帯電話300の筐体内部に配置されている。

#### [0050]

なお、上述した半導体装置は、携帯電話以外にも種々の電子機器に適用することができる。例えば、液晶プロジェクタ、マルチメディア対応のパーソナルコンピュータ(PC)およびエンジニアリング・ワークステーション(EWS)、ページャ、ワードプロセッサ、テレビ、ビューファインダ型またはモニタ直視型のビデオテープレコーダ、電子手帳、電子卓上計算機、カーナビゲーション装置、POS端末、タッチパネルを備えた装置などの電子機器に適用することが可能である。

[0051]

なお、本発明の技術範囲は、上述した実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において、上述した実施形態に種々の変更を加えたものを含む。すなわち、実施形態で挙げた具体的な材料や層構成などはほんの一例に過ぎず、適宜変更が可能である。

## [0052]

例えば、上記各実施形態では半導体チップの表面にキャパシタを形成したが、半導体チップの裏面にキャパシタを形成して、貫通電極により表面との導通を確保してもよい。また上記各実施形態では、電子回路が形成された半導体チップにキャパシタを形成したが、 絶縁材料からなる電子基板にキャパシタを形成してもよい。

【図面の簡単な説明】

[0053]

- 【図1】再配置配線の説明図である。

- 【図2】第1実施形態に係る半導体チップの側面断面図である。

- 【図3】第1実施形態に係る半導体チップの製造方法の工程図である。

- 【図4】第1実施形態に係る半導体チップの製造方法の工程図である。

- 【図5】第2実施形態に係る半導体チップの側面断面図である。

- 【図6】第3実施形態に係る半導体チップの側面断面図である。

- 【図7】第4実施形態に係る半導体チップの側面断面図である。

- 【図8】第5実施形態に係る半導体チップの側面断面図である。

- 【図9】携帯電話の斜視図である。

【符号の説明】

[0054]

C キャパシタ 10 第1電極 20 第2電極 30 応力緩和層

20

10

30

【図1】

【図2】

(b)

【図3】

(b)

(d)

(e)

【図4】

# 【図5】

(a)

# 【図6】

【図7】

【図9】

【図8】

# フロントページの続き

# (56)参考文献 特開平08-330313(JP,A)

特開2002-083893(JP,A)

特開2005-116715(JP,A)

特開2002-057291(JP,A)

特開2003-133476(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 23/12

H01L 21/60