# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**H01L 23/12** (2006.01)

(21) 출원번호 10-2007-0083607

(22) 출원일자 2007년08월20일 심사청구일자 2011년02월11일

(65) 공개번호 10-2009-0019297 (43) 공개일자 2009년02월25일

(56) 선행기술조사문헌

KR100541130 B1

US7122892 B2 US6874107 B2

JP2002164507 A

(24) 등록일자

(45) 공고일자

10-1213175

(11) 등록번호 2012년12월11일

(73) 특허권자

#### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

2012년12월18일

(72) 발명자

#### 강욱성

경기도 용인시 수지구 대지로15번길 60, 현대홈타 운3차2단지아파트 502동 801호 (죽전동)

(74) 대리인

박상수

전체 청구항 수 : 총 10 항

심사관 : 오순영

## (54) 발명의 명칭 로직 칩에 충충이 쌓인 메모리장치들을 구비하는반도체패키지

#### (57) 요 약

반도체장치를 제공한다. 베이스기판 상에 로직 칩이 배치된다. 상기 로직 칩은 서로 마주보는 제 1 표면 및 제 2 표면을 구비한다. 또한, 상기 로직 칩은 다수의 제 1 신호 단자, 상기 제 1 신호 단자와 떨어진 다수의 제 2 신 호 단자, 및 상기 제 1 및 제 2 신호 단자들에 전기적으로 접속된 직병렬변환기(SerDes)를 구비한다. 상기 제 1 표면에 제 1 반도체칩이 배치된다. 상기 제 1 반도체칩은 상기 제 1 신호 단자들에 전기적으로 접속된다. 상기 제 2 표면에 제 2 반도체칩이 배치된다. 상기 제 2 반도체칩은 상기 제 2 신호 단자들에 전기적으로 접속된다.

#### 대 표 도 - 도5

#### 특허청구의 범위

#### 청구항 1

베이스 기판;

상기 베이스 기판 상에 배치되고, 제1 표면, 제2 표면, 다수의 제1 신호 단자들, 다수의 제2 신호 단자들, 및 직병렬변환기(SerDes)를 갖는 로직 칩;

상기 로직 칩 상에 배치된 제 1 반도체 칩; 및

상기 베이스 기판 및 상기 로직 칩 사이에 배치된 제 2 반도체 칩을 포함하되,

상기 제2 표면은 상기 제1 표면에 대향하고, 상기 다수의 제2 신호 단자들은 상기 다수의 제1 신호 단자들과 떨어지고, 상기 제1 및 제2 신호 단자들은 상기 직병렬변환기에 전기적으로 접속되며,

상기 제1 반도체 칩은 상기 제1 표면에 부착되고 상기 제1 신호 단자들에 전기적으로 접속되며,

상기 제2 반도체 칩은 상기 제2 표면에 부착되고 상기 제2 신호 단자들에 전기적으로 접속된 반도체장치.

#### 청구항 2

제 1 항에 있어서,

상기 로직 칩은

기판 영역; 및

상기 기판 영역 상에 제공된 회로 영역을 포함하되, 상기 제 1 표면은 상기 회로 영역에 제공되고, 상기 제 2 표면은 상기 기판 영역에 제공되며, 상기 제 1 신호 단자들은 상기 회로 영역에 배치되고, 상기 제 2 신호 단자들은 상기 기판 영역에 배치된 반도체장치.

### 청구항 3

제 2 항에 있어서,

상기 제 2 신호 단자들은 상기 기판 영역을 관통하는 관통 전극을 포함하는 반도체장치.

## 청구항 4

제 2 항에 있어서,

상기 로직 칩은

상기 직병렬변환기에 전기적으로 접속된 다수의 입출력 단자를 더 포함하는 반도체장치.

## 청구항 5

제 4 항에 있어서,

상기 입출력 단자 및 상기 베이스기판 사이에 제공된 연결수단을 더 포함하되, 상기 연결수단은 도전성 볼 (conductive ball), 도전성 범프(conductive bump), 도전성 와이어(conductive wire), 및 도전성 스페이서 (conductive spacer)로 이루어진 일군에서 선택된 하나인 반도체장치.

## 청구항 6

제 1 항에 있어서,

상기 제 1 신호 단자 및 상기 제 1 반도체칩 사이에 배치된 제 1 도전성 범프; 및

상기 제 2 신호 단자 및 상기 제 2 반도체칩 사이에 배치된 제 2 도전성 범프를 더 포함하는 반도체장치.

## 청구항 7

제 1 항에 있어서,

상기 제 1 반도체칩 및 상기 제 2 반도체칩은 서로 다른 크기를 갖는 것을 특징으로 하는 반도체장치.

#### 청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

### 청구항 15

제 1 항에 있어서,

상기 로직 칩 및 상기 제1 반도체 칩 사이에 배치된 제 1 인터포저(first interposer); 및

상기 로직 칩 및 상기 제2 반도체 칩 사이에 배치된 제 2 인터포저(second interposer)를 더 포함하는 반도체장치.

## 청구항 16

제 15 항에 있어서,

상기 제 1 인터포저는 다수의 제 1 재배선 단자를 포함하되, 상기 제 1 재배선 단자는 상기 제 1 신호 단자에 대응하는 크기 및 간격을 갖는 관통 전극인 반도체장치.

## 청구항 17

제 15 항에 있어서,

상기 제 2 인터포저는

다수의 제 2 재배선 단자; 및

상기 제 2 재배선 단자에 전기적으로 접속된 다수의 제 3 재배선 단자를 포함하되, 상기 제 2 재배선 단자는 상기 제 2 신호 단자에 대응하는 크기 및 간격을 갖는 반도체장치.

## 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

## 명 세 서

#### 발명의 상세한 설명

## 기술분야

[0001] 본 발명은 반도체장치에 관한 것으로, 특히 로직 칩에 충충이 쌓인 메모리장치들을 구비하는 반도체패키지에 관한 것이다.

#### 배경기술

- [0002] 전자시스템의 경박단소화 및 다기능화에 따라 대용량, 고속동작, 및 저전력소모 특성을 갖는 메모리장치의 수요 가 증가하고 있다. 이에 따라, 복수의 메모리장치들을 하나의 반도체패키지 내에 적층 하는 기술이 시도되고 있다. 상기 메모리장치들을 적층 하는 기술은 대용량 메모리장치를 낮은 비용으로 구현할 수 있으며, 신호전달경로의 단축에 따른 동작속도의 증가와 전력소모의 감소에 유리하다.

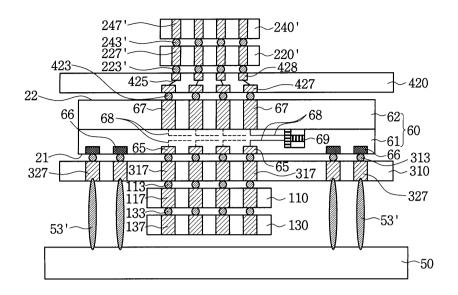

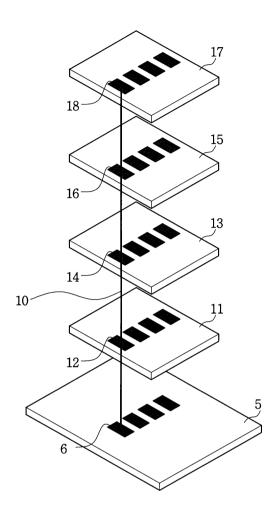

- [0003] 도 1은 종래기술에 의한 복수의 메모리칩들을 구비하는 반도체패키지를 보여주는 개략도이다.

- [0004] 도 1을 참조하면, 종래의 반도체패키지는 로직 칩(5) 상에 층층이 쌓인 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)을 구비한다. 상기 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)의 각각은 복수의 메모리 신호 단자들(12, 14, 16, 18)을 구비한다. 상기 메모리 신호 단자들(12, 14, 16, 18)은 상기 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)에 제공된 메모리 셀들(도시하지 않음)에 전기적으로 접속된다. 상기 로직 칩(5)은 복수의 로직 신호 단자들(6)을 구비한다. 상기 메모리 신호 단자들(12, 14, 16, 18)은 관통 전극(through silicon via; TSV)과 같은 데이터버스(10)를 통하여 상기 로직 신호 단자들(6) 중 대응하는 하나에 직렬접속된다.

- [0005] 상기 로직 칩(5)은 상기 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)에 데이터를 입출력하는 역할을 한다. 즉, 상기 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)에 저장된 데이터는 상기 데이터버스(10)를 통하여 읽어내고, 외부로부터 입력되는 데이터는 상기 데이터버스(10)를 통하여 상기 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)에 분배된다.

- [0006] 그런데 상기 제 1 메모리칩(11)에 상기 데이터버스(10)를 통하여 데이터를 입출력하는 동안 상기 제 2 내지 제 4 메모리칩들(13, 15, 17)은 대기하여야 한다. 이와 마찬가지로 상기 제 2 메모리칩(13)에 상기 데이터버스(10)를 통하여 데이터를 입출력하는 동안 상기 제 1, 제 3 및 제 4 메모리칩들(11 15, 17)은 대기하여야 한다. 즉, 상기 제 1 내지 제 4 메모리칩들(11, 13, 15, 17)에 데이터를 입출력하는 것은 직렬접속에 따른 신호지연이 발생한다.

- [0007] 한편. 복수의 메모리칩들을 구비하는 반도체패키지에 관한 기술이 미국공개특허 US2005/0170600 호에 "삼차원 반도체패키지 및 그에 채택되는 스페이서 칩(Three-dimensional semiconductor package, and spacer chip used therein)"이라는 제목으로 후쿠조(Fukuzo)에 의해 개시된 바 있다.

## 발명의 내용

## 해결 하고자하는 과제

- [0008] 본 발명이 이루고자 하는 기술적 과제는 상술한 종래기술의 문제점을 개선하기 위한 것으로서, 고속 입출력특성을 갖는 반도체장치를 제공하는 데 있다.

- [0009] 본 발명이 이루고자 하는 다른 기술적 과제는, 고속 입출력특성을 갖는 반도체메모리장치를 제공하는 데 있다.

#### 과제 해결수단

[0010] 상기 기술적 과제를 달성하기 위하여 본 발명은, 반도체장치를 제공한다. 베이스기판 상에 로직 칩이 배치된다. 상기 로직 칩은 서로 마주보는 제 1 표면 및 제 2 표면을 구비한다. 또한, 상기 로직 칩은 다수의 제 1 신호 단 자, 상기 제 1 신호 단자와 떨어진 다수의 제 2 신호 단자, 및 상기 제 1 및 제 2 신호 단자들에 전기적으로 접속된 직병렬변환기(SerDes)를 구비한다. 상기 제 1 표면에 제 1 반도체칩이 배치된다. 상기 제 1 반도체칩은 상기 제 1 신호 단자들에 전기적으로 접속된다. 상기 제 2 표면에 제 2 반도체칩이 배치된다. 상기 제 2 반도체칩은 상기 제 2 신호 단자들에 전기적으로 접속된다.

- [0011] 본 발명의 몇몇 실시 예에 있어서, 상기 로직 칩은 기판영역 및 상기 기판영역 상에 제공된 회로영역을 구비할 수 있다. 여기서, 상기 제 1 표면은 상기 회로영역에 제공될 수 있으며, 상기 제 2 표면은 상기 기판영역에 제공될 수 있다. 상기 제 1 신호 단자는 상기 회로영역에 배치될 수 있으며, 상기 제 2 신호 단자는 상기 기판영역에 배치될 수 있다. 상기 제 2 신호 단자는 상기 기판영역을 관통하는 관통 전극일 수 있다. 또한, 상기 로직 칩은 상기 직병렬변환기에 전기적으로 접속된 다수의 입출력 단자를 구비할 수 있다.

- [0012] 다른 실시 예에 있어서, 상기 입출력 단자 및 상기 베이스기판 사이에 연결수단이 제공될 수 있다. 상기 연결수단은 도전성 볼(conductive ball), 도전성 범프(conductive bump), 도전성 와이어(conductive wire), 및 도전성 스페이서(conductive spacer)로 이루어진 일군에서 선택된 하나일 수 있다.

- [0013] 또 다른 실시 예에 있어서, 상기 제 1 신호 단자 및 상기 제 1 반도체칩 사이에 제 1 도전성 범프가 배치될 수 있다. 상기 제 2 신호 단자 및 상기 제 2 반도체칩 사이에 제 2 도전성 범프가 배치될 수 있다.

- [0014] 또 다른 실시 예에 있어서, 상기 제 1 반도체칩 및 상기 제 2 반도체칩은 서로 다른 크기를 갖는 것일 수 있다.

- [0015] 또한, 본 발명은, 반도체메모리장치를 제공한다. 베이스기판 상에 로직 칩이 배치된다. 상기 로직 칩은 서로 마주보는 제 1 표면 및 제 2 표면을 구비한다. 상기 로직 칩은 다수의 제 1 신호 단자, 상기 제 1 신호 단자와 떨어진 다수의 제 2 신호 단자, 및 상기 제 1 및 제 2 신호 단자들에 전기적으로 접속된 직병렬변환기(SerDes)를 구비한다. 상기 제 1 표면 상에 배치되고 상기 제 1 신호 단자에 전기적으로 접속된 하나 또는 다수의 메모리장치가 제공된다. 상기 제 2 표면 상에 배치되고 상기 제 2 신호 단자에 전기적으로 접속된 하나 또는 다수의 다른 메모리장치가 제공된다.

- [0016] 몇몇 실시 예에 있어서, 상기 로직 칩은 기판영역 및 상기 기판영역 상에 제공된 회로영역을 구비할 수 있다. 상기 제 1 표면은 상기 회로영역에 제공될 수 있으며, 상기 제 2 표면은 상기 기판영역에 제공될 수 있다. 상기 제 1 신호 단자는 상기 회로영역에 배치될 수 있으며, 상기 제 2 신호 단자는 상기 기판영역에 배치될 수 있다. 상기 제 2 신호 단자는 상기 기판영역을 관통하는 관통 전극일 수 있다.

- [0017] 다른 실시 예에 있어서, 상기 다수의 메모리장치는 상기 제 1 신호 단자에 직렬연결될 수 있으며, 상기 다수의 다른 메모리장치는 상기 제 2 신호 단자에 직렬연결될 수 있다. 상기 메모리장치 및 상기 다른 메모리장치는 다수의 메모리 신호 단자를 구비할 수 있다. 상기 메모리 신호 단자는 관통 전극일 수 있다. 상기 제 1 및 제 2 신호 단자들과 상기 메모리 신호 단자 사이에 도전성 범프가 배치될 수 있다.

- [0018] 또 다른 실시 예에 있어서, 상기 로직 칩 및 상기 메모리장치 사이에 제 1 인터포저(first interposer)가 배치될 수 있다. 상기 로직 칩 및 상기 다른 메모리장치 사이에 배치된 제 2 인터포저(second interposer)가 배치될 수 있다. 상기 제 1 인터포저는 다수의 제 1 재배선 단자를 구비할 수 있다. 상기 제 1 재배선 단자는 상기 제 1 신호 단자에 대응하는 크기 및 간격을 갖는 관통 전극일 수 있다. 상기 제 2 인터포저는 다수의 제 2 재배선 단자 및 상기 제 2 재배선 단자에 전기적으로 접속된 다수의 제 3 재배선 단자를 구비할 수 있다. 상기 제 2 재배선 단자는 상기 제 2 신호 단자에 대응하는 크기 및 간격을 갖는 것일 수 있다.

- [0019] 또 다른 실시 예에 있어서, 상기 다른 메모리장치는 상기 메모리장치와 다른 크기를 갖는 것일 수 있다. 상기 다른 메모리장치는 상기 메모리장치의 축소판(shrink version)일 수 있다. 상기 다른 메모리장치는 상기 제 3 재배선 단자에 대응하는 크기 및 간격을 갖는 다수의 메모리 신호 단자를 구비할 수 있다.

## 直 과

[0020] 본 발명에 따르면, 로직 칩의 양측에 메모리장치들이 배치될 수 있다. 상기 메모리장치들은 상기 로직 칩에 내 장된 직병렬변환기(SerDes)에 병렬접속된다. 따라서 고속 입출력특성을 갖는 반도체장치를 구현할 수 있다.

## 발명의 실시를 위한 구체적인 내용

- [0021] 첨부한 도면들을 참조하여 본 발명의 바람직한 실시 예들을 상세히 설명하기로 한다. 그러나 본 발명은 여기서 설명되는 실시 예들에 한정되지 않고 다른 형태로 구체화될 수도 있다. 오히려, 여기서 소개되는 실시 예들은 개시된 내용이 철저하고 완전해질 수 있도록 그리고 당업자에게 본 발명의 사상이 충분히 전달될 수 있도록 하기 위해 제공되는 것이다. 도면들에 있어서, 층 및 영역들의 두께는 명확성을 기하기 위하여 과장된 것이다. 또한, 층이 다른 층 또는 기판 "상"에 있다고 언급되는 경우에 그것은 다른 층 또는 기판 상에 직접 형성될 수 있거나 또는 그들 사이에 제 3의 층이 개재될 수도 있다. 명세서 전체에 걸쳐서 동일한 참조번호로 표시된 부분들은 동일한 구성요소들을 의미한다.

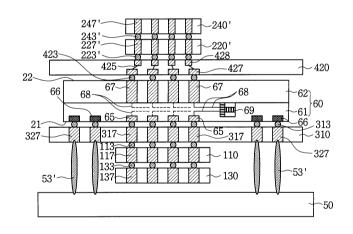

- [0022] 도 2 내지 도 5는 본 발명의 제 1 내지 제 4 실시 예들에 따른 로직 칩에 충충이 쌓인 메모리칩들을 구비하는 반도체패키지를 설명하기 위한 단면도들이다.

- [0023] 도 2를 참조하면, 본 발명의 제 1 실시 예에 따른 반도체패키지는 베이스기판(50), 로직 칩(60), 제 1 메모리칩(110), 제 2 메모리칩(220), 제 3 메모리칩(130), 및 제 4 메모리칩(240)을 포함할 수 있다.

- [0024] 상기 베이스기판(50)은 외부입출력단자들을 포함하는 인쇄회로기판 또는 반도체기판일 수 있다. 상기 로직 칩 (60)은 상기 베이스기판(50) 상에 배치될 수 있다. 상기 로직 칩(60)은 제 1 표면(21) 및 상기 제 1 표면(21)과 대향하는 제 2 표면(22)을 포함할 수 있다. 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)은 상기 제 1 표면(21) 상에 순차적으로 부착될 수 있다. 상기 제 2 메모리칩(220) 및 상기 제 4 메모리칩(240)은 상기 제 2 표면(22) 상에 순차적으로 부착될 수 있다. 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)은 상기 베이스기판(50) 및 상기 로직 칩(60) 사이에 배치될 수 있다.

- [0025] 상기 로직 칩(60)은 회로영역(61) 및 기판영역(62)으로 분류될 수 있다. 상기 회로영역(61)은 상기 기판영역(62)에 (62) 상에 배치될 수 있다. 상기 회로영역(61)에 상기 제 1 표면(21)이 제공될 수 있다. 상기 기판영역(62)에 상기 제 2 표면(22)이 제공될 수 있다. 상기 제 1 표면(21)은 상기 로직 칩(60)의 전면(front surface)일 수 있으며 상기 제 2 표면(22)은 상기 로직 칩(60)의 후면(back surface)일 수 있다. 상기 제 1 표면(21)은 상기 로직 칩(60)의 상면일 수 있으며 상기 제 2 표면(22)은 상기 로직 칩(60)의 하면일 수 있다. 상기 제 1 표면(21) 및 상기 제 2 표면(22)은 서로 평행할 수 있다.

- [0026] 상기 로직 칩(60)은 다수의 제 1 신호 단자(65), 다수의 제 2 신호 단자(67), 다수의 입출력 단자(66), 직병렬 변환기(serializer/deserializer; SerDes; 69), 및 다수의 상호연결배선(interconnection; 68)을 포함할 수 있다. 상기 제 1 신호 단자(65), 상기 입출력 단자(66), 상기 직병렬변환기(69), 및 상기 상호연결배선(68)은 상기 회로영역(61)에 형성될 수 있다. 상기 제 2 신호 단자(67)는 상기 기판영역(62)을 관통하는 티에스브이 (through silicon via; TSV)와 같은 관통 전극일 수 있다.

- [0027] 상기 제 1 신호 단자(65) 및 상기 제 2 신호 단자(67)는 서로 떨어지도록 형성될 수 있다. 상기 제 1 신호 단자 (65) 및 상기 제 2 신호 단자(67)는 각각 상기 상호연결배선(68)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 입출력 단자(66) 또한 다른 배선(도시하지 않음)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 제 1 신호 단자(65) 및 상기 입출력 단자(66)는 상기 제 1 표면(21)에 노출될 수 있다.

- [0028] 상기 입출력 단자(66)는 도전성 볼(conductive ball), 도전성 범프(conductive bump), 도전성 와이어 (conductive wire), 또는 도전성 스페이서(conductive spacer)와 같은 연결수단(53)에 의하여 상기 베이스기판 (50)에 전기적으로 접속될 수 있다. 예를 들면, 상기 도전성 볼은 솔더 볼(solder ball), 골드 볼(gold ball), 실버 볼(silver ball), 또는 이들의 조합일 수 있다. 상기 도전성 범프는 솔더 범프(solder bump), 골드 범프 (gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다. 상기 도전성 와이어는 골드 와이어(gold wire), 실버 와이어(silver wire), 알루미늄 와이어(aluminum wire), 또는 이들의 조합일수 있다. 상기 도전성 스페이서는 구리 스페이서(copper spacer), 알루미늄 스페이서(aluminum spacer), 질화타타늄 스페이서(TiN spacer), 질화타탈룸 스페이서(TaN spacer), 골드 스페이서(gold spacer), 실버 스페이서 (silver spacer), 백금 스페이서(Pt spacer), 니켈 스페이서(Ni spacer), 텅스텐 스페이서(W spacer), 또는 이들의 조합일수 있다.

- [0029] 상기 제 1 메모리칩(110)은 서로 떨어지도록 배치된 다수의 제 1 메모리 신호 단자(117)를 포함할 수 있으며, 상기 제 2 메모리칩(220)은 서로 떨어지도록 배치된 다수의 제 2 메모리 신호 단자(227)를 포함할 수 있고, 상 기 제 3 메모리칩(130)은 서로 떨어지도록 배치된 다수의 제 3 메모리 신호 단자(137)를 포함할 수 있으며, 상 기 제 4 메모리칩(240)은 서로 떨어지도록 배치된 다수의 제 4 메모리 신호 단자(247)를 포함할 수 있다. 상기

제 1 내지 제 4 메모리칩들(110, 220, 130, 240)의 각각은 다수의 메모리 셀(도시하지 않음), 상기 메모리 셀에 전기적으로 접속된 비트라인(도시하지 않음) 및 워드라인(도시하지 않음)을 포함할 수 있으나, 간략한 설명을 위하여 생략하기로 한다. 상기 메모리 셀은 상기 제 1 내지 제 4 메모리 신호 단자(117, 227, 137, 247) 중 대응하는 하나에 전기적으로 접속될 수 있다.

- [0030] 상기 제 1 내지 제 4 메모리 신호 단자(117, 227, 137, 247)는 티에스브이(through silicon via; TSV)와 같은 관통 전극일 수 있다. 상기 제 1 내지 제 4 메모리 신호 단자(117, 227, 137, 247)는 구리(Cu), 티타늄(Ti), 탄탈룸(Ta), 질화티타늄(TiN), 질화탄탈룸(TaN), 니켈(Ni), 텅스텐(W), 및 이들의 조합으로 이루어진 일군에게 서 선택된 하나일 수 있다. 예를 들면, 상기 제 1 내지 제 4 메모리 신호 단자(117, 227, 137, 247)는 Ti/TiN 막일 수 있다.

- [0031] 상기 제 1 메모리 신호 단자(117) 및 상기 제 1 신호 단자(65) 사이에 제 1 도전성 범프(113)가 배치될 수 있다. 상기 제 2 메모리 신호 단자(227) 및 상기 제 2 신호 단자(67) 사이에 제 2 도전성 범프(223)가 배치될 수 있다. 상기 제 3 메모리 신호 단자(137) 및 상기 제 1 메모리 신호 단자(117) 사이에 제 3 도전성 범프(133)가 배치될 수 있다. 상기 제 4 메모리 신호 단자(247) 및 상기 제 2 메모리 신호 단자(227) 사이에 제 4 도전성 범프(243)가 배치될 수 있다. 상기 제 1 내지 제 4 도전성 범프(113, 223, 133, 243)는 솔더 범프(solder bump), 골드 범프(gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다.

- [0032] 다른 실시 예들에서 상기 제 1 내지 제 4 도전성 범프(113, 223, 133, 243)는 도전성 볼(conductive ball), 도 전성 와이어(conductive wire), 또는 도전성 스페이서(conductive spacer)로 대체될 수 있다.

- [0033] 이제 도 2를 다시 참조하여 본 발명의 제 1 실시 예에 따른 반도체패키지의 동작을 설명하기로 한다.

- [0034] 도 2를 다시 참조하면, 상기 직병렬변환기(69)는 병렬신호를 입력받아 직렬신호 또는 병렬신호를 출력할 수 있으며, 이와 반대로, 직렬신호를 입력받아 병렬신호 또는 직렬신호를 출력하는 역할을 할 수 있다.

- [0035] 상술한 바와 같이, 상기 직병렬변환기(69)는 상기 상호연결배선(68), 상기 제 1 신호 단자(65), 상기 제 1 도전 성 범프(113) 및 상기 제 1 메모리 신호 단자(117)를 통하여 상기 제 1 메모리칩(110)에 내장된 메모리 셀과 전기적으로 접속될 수 있다. 또한, 상기 직병렬변환기(69)는 상기 상호연결배선(68), 상기 제 2 신호 단자(67), 상기 제 2 도전성 범프(223) 및 상기 제 2 메모리 신호 단자(227)를 통하여 상기 제 2 메모리칩(220)에 내장된 메모리 셀과 전기적으로 접속될 수 있다. 즉, 상기 제 1 메모리칩(110)에 내장된 메모리 셀 및 상기 제 2 메모리칩(220)에 내장된 메모리 셀은 상기 직병렬변환기(69)에 병렬접속될 수 있다.

- [0036] 이에 따라, 상기 제 1 메모리칩(110)에 저장된 데이터 및 상기 제 2 메모리칩(220)에 저장된 데이터는 상기 직병렬변환기(69)에 병렬접속될 수 있다. 이 경우에, 상기 직병렬변환기(69)는 상기 제 1 메모리칩(110) 및 상기제 2 메모리칩(220)에 저장된 데이터들을 동시에 읽어내고 상기 입출력 단자들(66) 및 상기 베이스기판(50)을 경유하여 외부로 출력할 수 있다. 이와 마찬가지로, 상기 직병렬변환기(69)는 상기 입출력 단자들(66)을 통하여 외부로부터 입력된 데이터들을 상기 제 1 메모리칩(110) 및 상기 제 2 메모리칩(220)에 분배하는 역할을 병렬수행할 수 있다. 즉, 상기 제 1 메모리칩(110) 및 상기 제 2 메모리칩(220)이 상기 직병렬변환기(69)에 직렬접속된 경우에 비하여 상대적으로 빠른 입출력특성을 보일 수 있다.

- [0037] 이에 더하여, 상기 직병렬변환기(69)는 상기 상호연결배선(68), 상기 제 1 신호 단자(65), 상기 제 1 도전성 범 프(113), 상기 제 1 메모리 신호 단자(117), 상기 제 3 도전성 범프(133), 및 상기 제 3 메모리 신호 단자(13 7)를 통하여 상기 제 3 메모리칩(130)에 내장된 메모리 셀과 전기적으로 접속될 수 있다. 이 경우에, 상기 제 1 메모리 신호 단자(117) 및 상기 제 3 메모리 신호 단자(137)는 직렬접속될 수 있다. 또한, 상기 직병렬변환기(69)는 상기 상호연결배선(68), 상기 제 2 신호 단자(67), 상기 제 2 도전성 범프(223), 상기 제 2 메모리 신호 단자(227), 상기 제 4 도전성 범들(243), 및 상기 제 4 메모리 신호 단자(247)를 통하여 상기 제 4 메모리칩(240)에 내장된 메모리 셀과 전기적으로 접속될 수 있다.

- [0038] 즉, 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)에 내장된 메모리 셀들은 상기 제 1 신호 단자(65)를 통하여 상기 직병렬변환기(69)에 직렬접속될 수 있으며, 상기 제 2 메모리칩(220) 및 상기 제 4 메모리칩(240)에 내장된 메모리 셀들은 상기 제 2 신호 단자(67)를 통하여 상기 직병렬변환기(69)에 직렬접속될 수 있다. 이에 따라, 상기 제 1 내지 제 4 메모리칩들(110, 220, 130, 240)이 모두 상기 직병렬변환기(69)에 직렬접속된 경우에 비하여 상대적으로 빠른 입출력특성을 보일 수 있다.

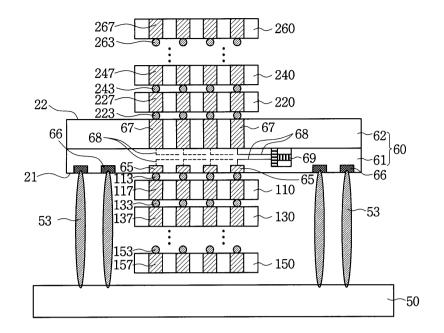

- [0039] 도 3을 참조하면, 본 발명의 제 2 실시 예에 따른 반도체패키지는 베이스기판(50), 로직 칩(60), 제 1 메모리칩(110), 제 2 메모리칩(220), 제 3 메모리칩(130), 제 4 메모리칩(240), 제 5 메모리칩(150), 및 제 6 메모리칩(

(260)을 구비할 수 있다. 이에 더하여, 상기 제 3 메모리칩(130) 및 상기 제 5 메모리칩(150) 사이에 하나 이상의 다른 메모리칩들이 배치될 수 있다. 더 나아가서, 상기 제 4 메모리칩(240) 및 상기 제 6 메모리칩(260) 사이에 하나 이상의 또 다른 메모리칩들이 배치될 수 있다. 이하에서는 본 발명의 제 1 실시 예와의 차이점만 간략하게 설명하기로 한다.

- [0040] 상기 베이스기판(50)은 외부입출력단자들을 구비하는 인쇄회로기판 또는 반도체기판일 수 있다. 상기 로직 칩 (60)은 상기 베이스기판(50) 상에 배치될 수 있다. 상기 로직 칩(60)은 제 1 표면(21) 및 상기 제 1 표면(21)과 마주보는 제 2 표면(22)을 구비할 수 있다. 상기 제 1 메모리칩(110), 상기 제 3 메모리칩(130), 및 상기 제 5 메모리칩(150)은 상기 제 1 표면(21) 상에 순차적으로 부착될 수 있다. 상기 제 2 메모리칩(220), 상기 제 4 메모리칩(240), 및 상기 제 6 메모리칩(260)은 상기 제 2 표면(22) 상에 순차적으로 부착될 수 있다. 상기 제 1 메모리칩(110), 상기 제 3 메모리칩(130), 및 상기 제 5 메모리칩(150)은 상기 베이스기판(50) 및 상기 로직 칩 (60) 사이에 배치될 수 있다.

- [0041] 상기 로직 칩(60)은 회로영역(61) 및 기판영역(62)으로 분류될 수 있다. 상기 회로영역(61)에 상기 제 1 표면 (21)이 제공될 수 있다. 상기 기판영역(62)에 상기 제 2 표면(22)이 제공될 수 있다.

- [0042] 상기 로직 칩(60)은 다수의 제 1 신호 단자(65), 다수의 제 2 신호 단자(67), 다수의 입출력 단자(66), 직병렬 변환기(serializer/deserializer; SerDes; 69), 및 다수의 상호연결배선(interconnection; 68)을 구비할 수 있다. 상기 제 1 신호 단자(65), 상기 입출력 단자(66), 상기 직병렬변환기(69), 및 상기 상호연결배선(68)은 상기 회로영역(61)에 배치될 수 있다. 상기 제 2 신호 단자(67)는 상기 기판영역(62)을 관통하는 티에스브이 (through silicon via; TSV)와 같은 관통 전극일 수 있다.

- [0043] 상기 제 1 신호 단자(65) 및 상기 제 2 신호 단자(67)는 서로 떨어지도록 배치될 수 있다. 상기 제 1 신호 단자 (65) 및 상기 제 2 신호 단자(67)는 각각 상기 상호연결배선(68)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 입출력 단자(66) 또한 다른 배선(도시하지 않음)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 제 1 신호 단자(65) 및 상기 입출력 단자(66)는 상기 제 1 표면(21)에 노출될 수 있다.

- [0044] 상기 제 5 메모리칩(150)은 서로 떨어지도록 배치된 다수의 제 5 메모리 신호 단자(157)를 구비할 수 있으며, 상기 제 6 메모리칩(260)은 서로 떨어지도록 배치된 다수의 제 6 메모리 신호 단자(267)를 구비할 수 있다. 상기 제 1 내지 제 6 메모리칩(110, 220, 130, 240, 150, 260)은 다수의 메모리 셀(도시하지 않음), 상기 메모리셀에 전기적으로 접속된 비트라인(도시하지 않음) 및 워드라인(도시하지 않음)을 구비할 수 있으나, 간략한 설명을 위하여 생략하기로 한다. 상기 메모리셀은 상기 제 1 내지 제 6 메모리 신호 단자(117, 227, 137, 247, 157, 267) 중 대응하는 하나에 전기적으로 접속될 수 있다.

- [0045] 상기 제 1 내지 제 6 메모리 신호 단자(117, 227, 137, 247, 157, 267)는 티에스브이(through silicon via; TSV)와 같은 관통 전극일 수 있다. 상기 제 1 내지 제 6 메모리 신호 단자(117, 227, 137, 247, 157, 267)는 구리(Cu), 티타늄(Ti), 탄탈룸(Ta), 질화티타늄(TiN), 질화탄탈룸(TaN), 니켈(Ni), 텅스텐(W), 및 이들의 조합으로 이루어진 일군에게서 선택된 하나일 수 있다. 예를 들면, 상기 제 1 내지 제 6 메모리 신호 단자(117, 227, 137, 247, 157, 267)는 Ti/TiN 막일 수 있다.

- [0046] 상기 제 3 메모리 신호 단자(137) 및 상기 제 5 메모리 신호 단자(137) 사이에 제 5 도전성 범프(153)가 배치될 수 있다. 상기 제 4 메모리 신호 단자(247) 및 상기 제 6 메모리 신호 단자(267) 사이에 제 6 도전성 범프(26 3)가 배치될 수 있다. 상기 제 1 내지 제 6 도전성 범프(113, 223, 133, 243, 153, 263)는 솔더 범프(solder bump), 골드 범프(gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다.

- [0047] 다른 실시 예들에서, 상기 제 1 내지 제 6 도전성 범프(113, 223, 133, 243, 153, 263)는 도전성 볼 (conductive ball), 도전성 와이어(conductive wire), 또는 도전성 스페이서(conductive spacer)로 대체될 수 있다.

- [0048] 도 4를 참조하면, 본 발명의 제 3 실시 예에 따른 반도체패키지는 베이스기판(50), 로직 칩(60), 제 1 메모리칩 (110), 제 2 메모리칩(220), 제 3 메모리칩(130), 및 제 4 메모리칩(240)을 구비할 수 있다. 이하에서는 본 발명의 제 1 실시 예와의 차이점만 간략하게 설명하기로 한다.

- [0049] 상기 베이스기판(50)은 외부입출력단자들을 구비하는 인쇄회로기판 또는 반도체기판일 수 있다. 상기 로직 칩(60)은 상기 베이스기판(50) 상에 배치될 수 있다. 상기 로직 칩(60)은 제 1 표면(21) 및 상기 제 1 표면(21)과 마주보는 제 2 표면(22)을 구비할 수 있다. 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)은 상기 제 1

표면(21) 상에 순차적으로 부착될 수 있다. 상기 제 2 메모리칩(220) 및 상기 제 4 메모리칩(240)은 상기 제 2 표면(22) 상에 순차적으로 부착될 수 있다. 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)은 상기 베이스기판(50) 및 상기 로직 칩(60) 사이에 배치될 수 있다.

- [0050] 상기 로직 칩(60)은 회로영역(61) 및 기판영역(62)으로 분류될 수 있다. 상기 회로영역(61)은 상기 기판영역(62) 상에 배치될 수 있다. 상기 회로영역(61)에 상기 제 1 표면(21)이 제공될 수 있다. 상기 기판영역(62)에 상기 제 2 표면(22)이 제공될 수 있다. 상기 제 1 표면(21)은 상기 로직 칩(60)의 전면(front surface)일 수 있으며 상기 제 2 표면(22)은 상기 로직 칩(60)의 후면(back surface)일 수 있다.

- [0051] 상기 로직 칩(60)은 다수의 제 1 신호 단자(65'), 다수의 제 2 신호 단자(67'), 다수의 입출력 단자(66), 직병 렬변환기(serializer/deserializer; SerDes; 69), 및 다수의 상호연결배선(interconnection; 68)을 구비할 수 있다. 상기 제 1 신호 단자(65'), 상기 입출력 단자(66), 상기 직병렬변환기(69), 및 상기 상호연결배선(68)은 상기 회로영역(61)에 배치될 수 있다. 상기 제 2 신호 단자(67')는 상기 기판영역(62) 및 상기 회로영역(61)을 관통하는 티에스브이(through silicon via; TSV)와 같은 관통 전극일 수 있다.

- [0052] 상기 제 1 신호 단자(65') 및 상기 제 2 신호 단자(67')는 서로 떨어지도록 배치될 수 있다. 상기 제 1 신호 단자(65') 및 상기 제 2 신호 단자(67')는 각각 상기 상호연결배선(68)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 입출력 단자(66) 또한 다른 배선(도시하지 않음)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 제 1 신호 단자(65') 및 상기 입출력 단자(66)는 상기 제 1 표면(21)에 노출될 수 있다.

- [0053] 상기 입출력 단자들(66)의 각각은 도전성 볼(conductive ball), 도전성 범프(conductive bump), 도전성 와이어 (conductive wire), 또는 도전성 스페이서(conductive spacer)와 같은 연결수단들(53)에 의하여 상기 베이스기 판(50)에 전기적으로 접속될 수 있다.

- [0054] 상기 제 1 메모리칩(110)은 서로 떨어지도록 배치된 다수의 제 1 메모리 신호 단자(117)를 구비할 수 있으며, 상기 제 2 메모리칩(220)은 서로 떨어지도록 배치된 다수의 제 2 메모리 신호 단자(227)를 구비할 수 있고, 상기 제 3 메모리칩(130)은 서로 떨어지도록 배치된 다수의 제 3 메모리 신호 단자(137)를 구비할 수 있으며, 상기 제 4 메모리칩(240)은 서로 떨어지도록 배치된 다수의 제 4 메모리 신호 단자(247)를 구비할 수 있다. 상기 제 1 내지 제 4 메모리칩(110, 220, 130, 240)은 다수의 메모리 셀(도시하지 않음), 상기 메모리 셀에 전기적으로 접속된 비트라인(도시하지 않음) 및 워드라인(도시하지 않음)을 구비할 수 있으나, 간략한 설명을 위하여 생략하기로 한다. 상기 메모리 셀은 상기 제 1 내지 제 4 메모리 신호 단자(117, 227, 137, 247) 중 대응하는 하나에 전기적으로 접속될 수 있다.

- [0055] 상기 제 1 메모리 신호 단자(117) 및 상기 제 1 신호 단자(65') 사이에 제 1 도전성 범프(113)가 배치될 수 있다. 상기 제 2 메모리 신호 단자(227) 및 상기 제 2 신호 단자(67') 사이에 제 2 도전성 범프(223)가 배치될 수 있다. 이 경우에, 상기 제 1 메모리칩(110) 및 상기 제 2 메모리칩(220)은 서로 어긋나게 배치될 수 있다. 상기 제 3 메모리 신호 단자(137) 및 상기 제 1 메모리 신호 단자(117) 사이에 제 3 도전성 범프(133)가 배치될 수 있다. 상기 제 4 메모리 신호 단자(247) 및 상기 제 2 메모리 신호 단자(227) 사이에 제 4 도전성 범프(243)가 배치될 수 있다. 상기 제 1 내지 제 4 도전성 범프(113, 223, 133, 243)는 솔더 범프(solder bump), 골드 범프(gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다.

- [0056] 다른 실시 예들에서 상기 제 1 내지 제 4 도전성 범프(113, 223, 133, 243)는 도전성 볼(conductive ball), 도 전성 와이어(conductive wire), 또는 도전성 스페이서(conductive spacer)로 대체될 수 있다.

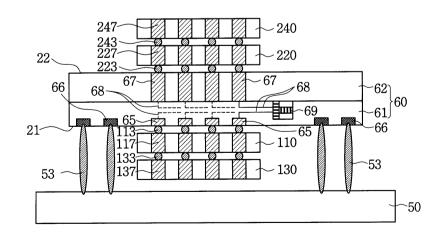

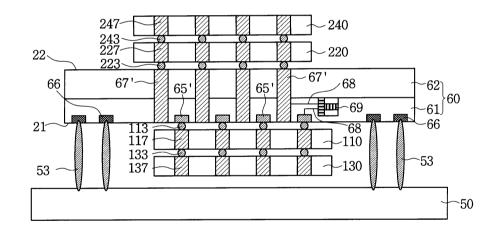

- [0057] 도 5를 참조하면, 본 발명의 제 4 실시 예에 따른 반도체패키지는 베이스기판(50), 로직 칩(60), 제 1 메모리칩 (110), 제 2 메모리칩(220), 제 3 메모리칩(130), 제 4 메모리칩(240), 제 1 인터포저(first interposer; 310) 및 제 2 인터포저(second interposer; 420)를 구비할 수 있다.

- [0058] 상기 베이스기판(50)은 외부입출력단자들을 구비하는 인쇄회로기판 또는 반도체기판일 수 있다. 상기 로직 칩 (60)은 상기 베이스기판(50) 상에 배치될 수 있다. 상기 로직 칩(60)은 제 1 표면(21) 및 상기 제 1 표면(21)과 마주보는 제 2 표면(22)을 구비할 수 있다. 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)은 상기 제 1 표면(21) 상에 순차적으로 부착될 수 있다. 상기 제 2 메모리칩(220) 및 상기 제 4 메모리칩(240)은 상기 제 2 표면(22) 상에 순차적으로 부착될 수 있다. 상기 제 1 메모리칩(110) 및 상기 제 3 메모리칩(130)은 상기 베이스기판(50) 및 상기 로직 칩(60) 사이에 배치될 수 있다.

- [0059] 상기 제 1 인터포저(310)는 상기 로직 칩(60) 및 상기 제 1 메모리칩(110) 사이에 배치될 수 있다. 즉, 상기 제

1 인터포저(310)는 상기 제 1 표면(21) 상에 부착될 수 있다. 상기 제 2 인터포저(420)는 상기 로직 칩(60) 및 상기 제 2 메모리칩(220) 사이에 배치될 수 있다. 즉, 상기 제 2 인터포저(420)는 상기 제 2 표면(22) 상에 부착될 수 있다.

- [0060] 상기 로직 칩(60)은 회로영역(61) 및 기판영역(62)으로 분류될 수 있다. 상기 회로영역(61)은 상기 기판영역(62) 상에 배치될 수 있다. 상기 회로영역(61)에 상기 제 1 표면(21)이 제공될 수 있다. 상기 기판영역(62)에 상기 제 2 표면(22)이 제공될 수 있다. 상기 제 1 표면(21)은 상기 로직 칩(60)의 전면(front surface)일 수 있으며 상기 제 2 표면(22)은 상기 로직 칩(60)의 후면(back surface)일 수 있다.

- [0061] 상기 로직 칩(60)은 다수의 제 1 신호 단자(65), 다수의 제 2 신호 단자(67), 다수의 입출력 단자(66), 직병렬 변환기(serializer/deserializer; SerDes; 69), 및 다수의 상호연결배선(interconnection; 68)을 구비할 수 있다. 상기 제 1 신호 단자(65), 상기 입출력 단자(66), 상기 직병렬변환기(69), 및 상기 상호연결배선(68)은 상기 회로영역(61)에 배치될 수 있다. 상기 제 2 신호 단자(67)는 상기 기판영역(62)을 관통하는 티에스브이 (through silicon via; TSV)와 같은 관통 전극일 수 있다.

- [0062] 상기 제 1 신호 단자(65) 및 상기 제 2 신호 단자(67)는 서로 떨어지도록 배치될 수 있다. 상기 제 1 신호 단자 (65) 및 상기 제 2 신호 단자(67)는 각각 상기 상호연결배선(68)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 입출력 단자(66) 또한 다른 배선(도시하지 않음)을 통하여 상기 직병렬변환기(69)에 전기적으로 접속될 수 있다. 상기 제 1 신호 단자(65) 및 상기 입출력 단자(66)는 상기 제 1 표면(21)에 노출될 수 있다.

- [0063] 상기 제 1 인터포저(310) 및 상기 제 2 인터포저(420)는 재배선 층의 역할을 할 수 있다. 상기 제 1 인터포저 (310)는 다수의 제 1 재배선 단자(317) 및 다수의 입출력 관통 전극(327)을 구비할 수 있다. 상기 제 1 재배선 단자들(317)은 터에스브이(through silicon via; TSV)와 같은 관통 전극일 수 있다. 상기 제 1 재배선 단자들 (317)은 상기 제 1 신호 단자들(65)에 대응하는 크기 및 간격을 구비하도록 배치된 것일 수 있다. 상기 입출력 관통 전극(327)은 상기 입출력 단자(66)에 대응하는 크기 및 간격을 구비하도록 배치된 것일 수 있다.

- [0064] 상기 제 2 인터포저(420)의 일면에 다수의 제 2 재배선 단자(427)가 제공될 수 있다. 상기 제 2 재배선 단자 (427)는 상기 제 2 신호 단자(67)에 대응하는 크기 및 간격을 구비하도록 배치된 것일 수 있다. 상기 제 2 인터 포저(420)의 다른 일면에 다수의 제 3 재배선 단자(428)가 제공될 수 있다. 상기 제 3 재배선 단자(428)는 인터 포저 배선(425)을 통하여 상기 제 2 재배선 단자(427) 중 대응하는 하나에 전기적으로 접속될 수 있다.

- [0065] 상기 제 1 재배선 단자(317), 상기 입출력 관통 전극(327), 상기 제 2 재배선 단자(427), 상기 제 3 재배선 단자(428) 및 상기 인터포저 배선(425)은 구리(Cu), 티타늄(Ti), 탄탈룸(Ta), 질화티타늄(TiN), 질화탄탈룸 (TaN), 니켈(Ni), 텅스텐(W), 및 이들의 조합으로 이루어진 일군에게서 선택된 하나일 수 있다.

- [0066] 상기 제 1 재배선 단자(317) 및 상기 제 1 신호 단자(65) 사이에 제 1 재배선 범프(313)가 배치될 수 있다. 또한, 상기 입출력 관통 전극(327) 및 상기 입출력 단자(66) 사이에도 상기 제 1 재배선 범프(313)가 배치될 수 있다. 상기 제 2 재배선 단자(427) 및 상기 제 2 신호 단자(67) 사이에 제 2 재배선 범프(423)가 배치될 수 있다. 상기 제 1 재배선 범프(313) 및 상기 제 2 재배선 범프(423)는 솔더 범프(solder bump), 골드 범프(gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다.

- [0067] 다른 실시 예들에서 상기 제 1 재배선 범프(313) 및 상기 제 2 재배선 범프(423)는 도전성 볼(conductive ball), 도전성 와이어(conductive wire), 또는 도전성 스페이서(conductive spacer)로 대체될 수 있다.

- [0068] 상기 입출력 관통 전극(327)은 도전성 볼(conductive ball), 도전성 범프(conductive bump), 도전성 와이어 (conductive wire), 또는 도전성 스페이서(conductive spacer)와 같은 연결수단들(53')에 의하여 상기 베이스 기판(50)에 전기적으로 접속될 수 있다. 예를 들면, 상기 도전성 볼은 솔더 볼(solder ball), 골드 볼(gold ball), 실버 볼(silver ball), 또는 이들의 조합일 수 있다. 상기 도전성 범프는 솔더 범프(solder bump), 골드 범프(gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다. 상기 도전성 와이어는 골드 와이어(gold wire), 실버 와이어(silver wire), 알루미늄 와이어(aluminum wire), 또는 이들의 조합일 수 있다. 상기 도전성 스페이서는 구리 스페이서(copper spacer), 알루미늄 스페이서(aluminum spacer), 질화티타늄 스페이서(TiN spacer), 질화탄탈룸 스페이서(TaN spacer), 골드 스페이서(gold spacer), 실버 스페이서(silver spacer), 백금 스페이서(Pt spacer), 니켈 스페이서(Ni spacer), 텅스텐 스페이서(W spacer), 또는 이들의 조합일 수 있다.

- [0069] 상기 제 1 메모리칩(110)은 서로 떨어지도록 배치된 다수의 제 1 메모리 신호 단자(117)를 구비할 수 있으며,

상기 제 2 메모리칩(220')은 서로 떨어지도록 배치된 다수의 제 2 메모리 신호 단자(227')를 구비할 수 있고, 상기 제 3 메모리칩(130)은 서로 떨어지도록 배치된 다수의 제 3 메모리 신호 단자(137)를 구비할 수 있으며, 상기 제 4 메모리칩(240')은 서로 떨어지도록 배치된 다수의 제 4 메모리 신호 단자(247')를 구비할 수 있다.

- [0070] 상기 제 1 메모리칩(110) 및 상기 제 2 메모리칩(220')은 서로 다른 규격을 갖는 것일 수 있다. 예를 들면, 상기 제 2 메모리칩(220')은 상기 제 1 메모리칩(110)의 축소판(shrink version)일 수 있다. 상기 제 3 메모리칩(130)은 상기 제 1 메모리칩(110)과 동일한 규격을 갖는 것일 수 있다. 또한, 상기 제 4 메모리칩(240')은 상기 제 2 메모리칩(220')과 동일한 규격을 갖는 것일 수 있다.

- [0071] 상기 제 1 내지 제 4 메모리칩들(110, 220', 130, 240')의 각각은 다수의 메모리 셀(도시하지 않음), 상기 메모리 셀에 전기적으로 접속된 비트라인(도시하지 않음) 및 워드라인(도시하지 않음)을 구비할 수 있으나, 간략한 설명을 위하여 생략하기로 한다. 상기 메모리 셀은 상기 제 1 내지 제 4 메모리 신호 단자(117, 227', 137, 247')중 대응하는 하나에 전기적으로 접속될 수 있다.

- [0072] 상기 제 1 내지 제 4 메모리 신호 단자(117, 227', 137, 247')는 티에스브이(through silicon via; TSV)와 같은 관통 전극일 수 있다. 상기 제 1 내지 제 4 메모리 신호 단자(117, 227', 137, 247')는 구리(Cu), 티타늄 (Ti), 탄탈룸(Ta), 질화티타늄(TiN), 질화탄탈룸(TaN), 니켈(Ni), 텅스텐(W), 및 이들의 조합으로 이루어진 일 군에게서 선택된 하나일 수 있다. 예를 들면, 상기 제 1 내지 제 4 메모리 신호 단자(117, 227', 137, 247')는 Ti/TiN 막일 수 있다.

- [0073] 상기 제 1 메모리 신호 단자(117)은 상기 제 1 재배선 단자(317)에 대응하는 크기 및 간격을 구비하도록 배치된 것일 수 있다. 상기 제 1 메모리 신호 단자(117) 및 상기 제 1 재배선 단자(317) 사이에 제 1 도전성 범프(113)가 배치될 수 있다. 상기 제 2 메모리 신호 단자(227')는 상기 제 3 재배선 단자(428)에 대응하는 크기 및 간격을 구비하도록 배치된 것일 수 있다. 상기 제 2 메모리 신호 단자(227') 및 상기 제 3 재배선 단자(428) 사이에 제 2 도전성 범프(223')가 배치될 수 있다. 상기 제 3 메모리 신호 단자(137) 및 상기 제 1 메모리 신호 단자(117) 사이에 제 3 도전성 범프(133)가 배치될 수 있다. 상기 제 4 메모리 신호 단자(247') 및 상기 제 2 메모리 신호 단자(227') 사이에 제 4 도전성 범프(243')가 배치될 수 있다. 상기 제 1 내지 제 4 도전성 범프(113, 223', 133, 243')는 솔더 범프(solder bump), 골드 범프(gold bump), 실버 범프(silver bump), 니켈 범프(Ni bump), 또는 이들의 조합일 수 있다.

- [0074] 다른 실시 예들에서 상기 제 1 내지 제 4 도전성 범프(113, 223', 133, 243')는 도전성 볼(conductive ball), 도전성 와이어(conductive wire), 또는 도전성 스페이서(conductive spacer)로 대체될 수 있다.

- [0075] 도 4에 도시된 바와 같이, 상기 제 1 인터포저(310) 및 상기 제 2 인터포저(420)를 이용하여 서로 다른 크기를 갖는 상기 제 1 메모리칩(110) 및 상기 제 2 메모리칩(220')을 상기 로직 칩(60)에 병렬접속할 수 있다.

- [0076] 본 발명은 상술한 실시 예들에 한정되지 않고 본 발명의 사상 내에서 여러 가지의 다른 형태로 변형될 수 있다. 예를 들면, 상기 메모리칩들(110, 220, 130, 240, 150, 260)은 반도체칩(semiconductor chip), 반도체 메모리코아(semiconductor memory core), 반도체 메모리패키지(semiconductor memory package), 또는 이들의 조합과 같은 다른 반도체장치로 대체될 수 있다.

### 도면의 간단한 설명

- [0077] 도 1은 종래기술에 의한 복수의 메모리칩들을 구비하는 반도체패키지를 보여주는 개략도이다.

- [0078] 도 2 내지 도 5는 본 발명의 제 1 내지 제 4 실시 예들에 따른 로직 칩에 층층이 쌓인 메모리칩들을 구비하는 반도체패키지를 설명하기 위한 단면도들이다.

# 도면

# 도면1

# 도면2

## 도면3

## 도면4

## 도면5