## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**GOIR 1/073** (2006.01) **GOIR 31/26** (2006.01) **HOIL 21/66** (2006.01)

(21) 출원번호 10-2013-7011041

(22) 출원일자(국제) **2011년09월28일** 심사청구일자 **없음**

(85) 번역문제출일자 2013년04월29일

(86) 국제출원번호 PCT/US2011/053775

(87) 국제공개번호 **WO 2012/054201** 국제공개일자 **2012년04월26일**

(30) 우선권주장

61/404,234 2010년09월28일 미국(US)

(11) 공개번호 10-2013-0138793

(43) 공개일자 2013년12월19일

(71) 출원인

어드밴스드 인쿼리 시스템즈, 인크,

미국 97006 오레건주 비버톤 메일 코드 오지아이 504 엔 더블유 워커 로드 20000

(72) 발명자

더빈 아론

미국 97124 오레건주 힐스버러 스위트 100 노스웨 스트 에버그린 파크스 20520 어드밴스드 인쿼리 시스템즈, 인크. 내

키이스 데이비드

미국 97124 오레건주 힐스버러 스위트 100 노스웨 스트 에버그린 파크웨이 20520 어드밴스드 인쿼리 시스템즈, 인크. 내

존슨 모건 티.

미국 97124 오레건주 힐스버러 스위트 100 노스웨 스트 에버그린 파크웨이 20520 어드밴스드 인쿼리 시스템즈, 인크, 내

(74) 대리인

안국찬, 양영준

전체 청구항 수 : 총 24 항

## (54) 발명의 명칭 웨이퍼 테스팅 시스템들 및 사용 및 제조의 연관된 방법들

#### (57) 요 약

웨이퍼 테스팅이 개시된다. 웨이퍼 테스팅 시스템은 개별적으로 동작가능한 진공들, 또는 압력 차이들에 의해 웨이퍼 트랜스레이터에 웨이퍼를 및 인터포저에 상기 웨이터 트랜스레이터를 해제 가능하게 부착하기 위한 어셈블리를 포함한다. 상기 어셈블리는 상기 웨이퍼 트랜스레이터에 결합된 웨이퍼 트랜스레이터 지지 링을 포함하며, 여기에서 공간이 하나 이상의 제 1 배출 경로들을 통해 제 1 진공까지 배출될 수 있도록 상기 웨이퍼 트랜스레이터 및 상기 인터포저 사이의 공간을 에워싸도록 상기 웨이퍼 트랜스레이터 지지 링으로부터 제 1 가요성 재료가 연장된다. 상기 어셈블리는 상기 웨이퍼 및 척에 결합된 웨이퍼 지지 링을 더 포함할 수 있으며, 여기에서 공간이 하나 이상의 제 2 배출 경로들을 통해 제 2 진공까지 배출될 수 있도록 상기 웨이퍼 및 상기 웨이퍼 트랜스레이터 사이에서의 공간을 에워싸도록 웨이퍼 지지 링으로부터 제 2 가요성 재료가 연장된다.

## 대 표 도 - 도2

## 특허청구의 범위

### 청구항 1

웨이퍼 테스팅 시스템(wafer testing system)에 있어서,

테스터(tester);

프로버(prober);

상기 테스터 및 상기 프로버 사이에 케이블을 포함하고,

상기 프로버는,

인터포저(interposer);

상기 인터포저에 근접한 웨이퍼 트랜스레이터(wafer translator); 및

상기 웨이퍼 트랜스레이터를 수취하도록 구성된 트랜스레이터 지지대(translator support);를 포함하고.

상기 트랜스레이터 지지대는 상기 웨이퍼 트랜스레이터 및 상기 인터포저 사이의 공간을 적어도 부분적으로 밀폐하여(hermetically) 밀봉하도록 구성된 시일(seal)을 갖는, 웨이퍼 테스팅 시스템.

#### 청구항 2

청구항 1 에 있어서.

상기 인터포저는 상기 웨이퍼 트랜스레이터에 근접한 컨택 핀(contact pin)을 포함하며;

상기 웨이퍼 트랜스레이터는 상기 인터포저에 근접한 제 1 측 상에서의 제 1 단자, 제 2 측에서의 제 2 단자, 및 상기 제 1 및 제 2 단자들 사이에 전기적 경로(electrical pathway)를 포함하며;

상기 컨택 핀은 상기 공간이 적어도 부분적으로 진공 하에 있을 때 상기 제 1 단자를 컨택하도록 구성되는, 웨이퍼 테스팅 시스템.

## 청구항 3

청구항 1 에 있어서.

상기 트랜스레이터 지지대는 상기 웨이퍼 트랜스레이터 및 상기 인터포저 사이에서의 상기 공간으로 및 그로부터 기체를 전달하도록 구성된 경로를 포함하는, 웨이퍼 테스팅 시스템.

## 청구항 4

청구항 1 에 있어서,

상기 트랜스레이터 지지대는 상기 시일(seal)을 수취하도록 구성된 홈(groove)을 가진 링(ring)을 포함하며;

상기 시일은 상기 링의 상기 홈에 적어도 부분적으로 수취되는 일반적인 가요성 재료(flexible material)를 포함하는, 웨이퍼 테스팅 시스템.

## 청구항 5

청구항 1 에 있어서,

상기 트랜스레이터 지지대는 홈을 가진 링을 포함하며,

상기 시일은 베이스 부분(base portion) 및 상기 베이스 부분으로부터 연장된 상부 부분(upper portion)을 포함하고, 상기 베이스 부분은 상기 링의 상기 홈에 수취되는, 웨이퍼 테스팅 시스템.

## 청구항 6

청구항 1 에 있어서.

상기 트랜스레이터 지지대는 플랜지(flange)가 달린 홈을 가진 링을 포함하고; 및

상기 시일은 베이스 부분 및 상기 베이스 부분으로부터 연장된 상부 부분을 포함하며,

상기 베이스 부분은 상기 링의 상기 홈에 수취되고 상기 홈의 상기 플랜지에 의해 유지되는, 웨이퍼 테스팅 시스템.

## 청구항 7

청구항 1 에 있어서,

상기 트랜스레이터 지지대는 플랜지가 달린 홈을 가진 링을 포함하고;

상기 시일은 베이스 부분 및 상기 베이스 부분으로부터 연장된 상부 부분을 포함하고;

상기 베이스 부분은 상기 링의 상기 홈에 수취되고 상기 홈의 상기 플랜지에 의해 유지되며; 및

상기 상부 부분은 상기 트랜스레이터 지지대에 대하여 원주 둘레에서(circumferentially) 바깥쪽으로 비스듬히 놓이는, 웨이퍼 테스팅 시스템.

#### 청구항 8

청구항 1 에 있어서,

상기 시일은 제 1 시일(seal)이고;

상기 웨이퍼 테스팅 시스템은,

상기 웨이퍼 트랜스레이터의 상기 제 2 측 상에 근접하여 웨이퍼를 유지하도록 구성된 척(chuck);

상기 척을 수취하도록 구성된 척 지지대(chuck support)로서, 상기 척 지지대는 상기 웨이퍼 및 상기웨이퍼 트랜스레이터 사이의 공간을 적어도 부분적으로 밀폐형 밀봉하도록 구성된 제 2 시일(seal)을 갖는, 상기 척 지지대를 더 포함하는, 웨이퍼 테스팅 시스템.

## 청구항 9

웨이퍼 트랜스레이터(wafer translator)에 있어서,

제 1 측 및 제 2 측을 가진 기판(substrate);

상기 제 1 측에서의 제 1 단자(terminal);

상기 제 1 측의 맞은편에 있는 상기 제 2 측에서의 제 2 단자;

상기 제 1 및 제 2 단자들 사이의 전기적 경로(electrical pathway); 및

상기 기판을 수취하도록 구성된 트랜스레이터 지지대(translator support)로서, 상기 트랜스레이터 지지대는 상기 웨이퍼 트랜스레이터 및 상기 웨이퍼 트랜스레이터의 상기 제 1 측에 근접한 인터포저(interposer) 사이의 공간을 적어도 부분적으로 밀폐형 밀봉하도록 구성된 시일을 갖는, 상기 트랜스레이터 지지대를 포함하는, 웨이퍼 트랜스레이터.

### 청구항 10

청구항 9 에 있어서,

상기 트랜스레이터 지지대는 상기 웨이퍼 트랜스레이터 및 상기 인터포저 사이의 공간으로 및 상기 웨이퍼 트랜스레이터 및 상기 인터포저 사이의 공간으로부터 기체가 통과하도록 구성된 경로(pathway)를 포함하는, 웨이퍼트랜스레이터.

#### 청구항 11

청구항 9 에 있어서,

상기 트랜스레이터 지지대는 상기 시일을 수취하도록 구성된 홈을 가진 링을 포함하며;

상기 시일은 상기 링의 상기 홈에 적어도 부분적으로 수취되는 일반적인 가요성 재료(flexible material)를 포함하는, 웨이퍼 트랜스레이터.

#### 청구항 12

청구항 9 에 있어서,

상기 트랜스레이터 지지대는 홈을 가진 링을 포함하며;

상기 시일은 베이스 부분 및 상기 베이스 부분으로부터 연장된 상부 부분을 포함하고, 상기 베이스 부분은 상기 링의 상기 홈에 수취되는, 웨이퍼 트랜스레이터.

#### 청구항 13

청구항 9 에 있어서,

상기 트랜스레이터 지지대는 플랜지가 달린 홈을 가진 링을 포함하고;

상기 시일은 베이스 부분 및 상기 베이스 부분으로부터 연장된 상부 부분을 포함하며;

상기 베이스 부분은 상기 링의 상기 홈에 수취되고 상기 홈의 상기 플랜지에 의해 유지되는, 웨이퍼 트랜스레이터.

## 청구항 14

청구항 9 에 있어서,

상기 트랜스레이터 지지대는 플랜지가 달린 홈을 가진 링을 포함하고;

상기 시일은 베이스 부분 및 상기 베이스 부분으로부터 연장된 상부 부분을 포함하고;

상기 베이스 부분은 상기 링의 상기 홈에 수취되고 상기 홈의 상기 플랜지에 의해 유지되며;

상기 상부 부분은 상기 트랜스레이터 지지대에 대하여 원주 둘레에서(circumferentially) 바깥쪽으로 비스듬히 놓이는, 웨이퍼 트랜스레이터.

#### 청구항 15

본드 패드(bond pad)를 가진 웨이퍼와의 컨택을 수립하기 위한 방법에 있어서,

인터포저(interposer) 및 상기 웨이퍼에 근접한 웨이퍼 트랜스레이터(wafer translator)를 배치하는 단계로서, 상기 웨이퍼 트랜스레이터는 상기 웨이퍼의 상기 본드 패드를 마주보는 단자를 가진, 상기 배치 단계;

상기 인터포저와 상기 웨이퍼 트랜스레이터 사이의 제 1 공간 및 상기 웨이퍼와 상기 웨이퍼 트랜스레이터 사이의 제 2 공간을 적어도 부분적으로 밀폐하여 밀봉하는 단계;

상기 제 1 공간에서 제 1 진공을 및 상기 제 2 공간에서 제 2 진공을 수립하는 단계; 및

상기 제 1 및 제 2 진공들에서 상기 웨이퍼의 상기 본드 패드(bond pad)와 상기 웨이퍼 트랜스레이터의 상기 단자(terminal)를 컨택(contact)하는 단계를 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 방법.

#### 청구항 16

청구항 15 에 있어서,

상기 단자 및 상기 본드 패드 사이에서의 컨택의 타겟 정도(target degree)에 기반하여 상기 제 1 및 제 2 진공 들 중 적어도 하나를 조정하는 단계를 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 방법.

#### 청구항 17

청구항 15 에 있어서,

상기 단자 및 상기 본드 패드가 서로와 전기적 및 물리적 컨택하도록 상기 제 1 및 제 2 진공들 중 적어도 하나

를 조정하는 단계를 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 방법.

#### 청구항 18

청구항 15 에 있어서.

척(chuck) 상에 상기 웨이퍼를 유지하는 단계로서, 상기 웨이퍼는 상기 웨이퍼 트랜스레이터를 마주보는 제 1 측 및 상기 척을 마주보는 제 2 측을 갖는, 상기 유지 단계;

상기 웨이퍼의 상기 제 2 측 및 상기 척 사이에 제 3 진공을 수립하는 단계; 및

상기 단자 및 상기 본드 패드 사이에서의 컨택의 타겟 정도에 기반하여 상기 제 1, 제 2, 및 제 3 진공들 중 적어도 하나를 조정하는 단계를 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 방법.

#### 청구항 19

청구항 15 에 있어서,

상기 본드 패드(bond pad)는 제 1 본드 패드이고;

상기 단자는 제 1 단자이고;

상기 웨이퍼는 또한 복수의 부가적인 본드 패드들을 포함하고;

상기 웨이퍼 트랜스레이터는 또한 상기 웨이퍼의 상기 본드 패드들에 대응하는 복수의 부가적인 단자들을 포함 하며; 및

상기 방법은 상기 복수의 단자들 및 상기 대응하는 본드 패드들 사이의 컨택의 타켓 정도에 기초하여 상기 제 1 및 제 2 진공들 중 적어도 하나를 조정하는 단계를 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 방법.

#### 청구항 20

청구항 15 에 있어서,

상기 제 1 공간에 제 1 압력 및 상기 제 2 공간에 제 2 압력 중 적어도 하나를 다른 것과 상이하도록 제어함으로써 상기 웨이퍼 트랜스레이터 상에서의 힘(force)들을 제어하는 단계를 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 방법.

## 청구항 21

본드 패드(bond pad)를 가진 웨이퍼와의 컨택을 수립하기 위한 장치에 있어서,

인터포저(interposer);

상기 인터포저에 근접한 제 1 측 및 상기 웨이퍼에 근접한 제 2 측을 가진 웨이퍼 트랜스레이터(wafer translator)로서, 상기 웨이퍼 트랜스레이터는 상기 웨이퍼의 상기 본드 패드를 마주보는 단자(terminal)를 갖는, 상기 웨이퍼 트랜스레이터;

상기 인터포저 및 상기 웨이퍼 트랜스레이터 사이의 제 1 공간을 적어도 부분적으로 밀폐하여 밀봉하기 위한 수단; 및

상기 웨이퍼 및 상기 웨이퍼 트랜스레이터 사이의 제 2 공간을 적어도 부분적으로 밀폐하여 밀봉하기 위한 수단을 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 장치.

## 청구항 22

청구항 21 에 있어서,

상기 제 1 공간에 제 1 진공을 수립하기 위한 수단;

상기 제 2 공간에 제 2 진공을 수립하기 위한 수단을 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 장치.

## 청구항 23

청구항 21 에 있어서,

상기 제 1 공간에 제 1 진공을 수립하기 위한 수단;

상기 제 2 공간에 제 2 진공을 수립하기 위한 수단; 및

상기 단자 및 상기 본드 패드 사이의 컨택의 타겟 정도에 기반하여 상기 제 1 및 제 2 진공들 중 적어도 하나를 조정하기 위한 수단을 더 포함하는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 장치.

#### 청구항 24

청구항 21 에 있어서.

상기 조정 수단은 상기 제 1 및 제 2 진공들 중 적어도 하나가 다른 하나와 상이하도록 조정하도록 구성되는, 본드 패드를 가진 웨이퍼와의 컨택을 수립하기 위한 장치.

## 명 세 서

## 기술분야

- [0001] 관련 출원에 대한 상호 참조

- [0002] 본 출원은 2010년 9월 28일에 출원된, "스택 내에서 접지압을 이용 및 관리하기 위한 3개의 독립적인 진공 구획들을 가진 웨이퍼 척, 웨이퍼, 웨이퍼 트랜스레이터, 및 테스터 DIB 보드의 배열 또는 스택; 부가적으로 특정웨이퍼에 대한 맞춤 트랜스레이터들을 생성하기 위해 리드 시간 및 비용을 최소화하도록 상기 웨이퍼 트랜스레이터의 테스터 측에 걸쳐 표준화된 컨택 패턴들을 생성하기 위한 시스템(ARRANGEMENT OR STACK OF A WAFER CHUCK, WAFER, WAFER TRANSLATOR, AND TESTER DIB BOARD WITH THREE INDEPENDENT VACUUM COMPARTMENTS TO APPLY AND MANAGE CONTACT PRESSURE WITHIN THE STACK; ADDITIONALLY A SYSTEM TO CREATE STANDARDIZED CONTACT PATTERNS ACROSS THE TESTER SIDE OF THE WAFER TRANSLATOR TO MINIMIZE LEAD TIME AND COST TO CREATE CUSTOM TRANSLATORS FOR SPECIFIC WAFER)"명칭의, 미국 가 출원 번호 제61/404,234호에 대한 우선권을 주장하고, 그것의 전체가 참조로서 본 출원에 통합된다.

- [0003] 기술 분야

- [0004] 본 기술은 일반적으로 반도체 제조 장비에 관한 것으로, 보다 상세하게는 해제 가능하게 부착된 상태에 척 (chuck), 웨이퍼, 웨이퍼 트랜스레이터(wafer translator), 및 인터포저(interposer)를 유지하기 위한 시스템 들 및 방법들에 관한 것이다.

#### 배경기술

- [0005] 반도체들은 디지털 카메라들, 휴대 전화기들, 컴퓨터들, 및 다수의 다른 기술 애플리케이션들에 사용된다. 반도 체들은 통상적으로 각각 따로 복수개의 반도체 웨이퍼들을 수용하는 여러 묶음으로 통상적으로 제조되고 웨이퍼들내에 그리고 웨이퍼들 위에 집적회로들을 갖는 다이(die)들이 다양한 반도체 제조 공정들을 통하여 형성되게 된다. 완성된 웨이퍼들은 상기 웨이퍼 상에서의 다이들이 미리 결정된 규격들에 따라 동작할 수 있는지를 결정하기 위해 전기적으로 테스트된다. 이러한 방식으로, 결함이 있는 다이들은 패키징되지 않거나 또는 그 외 완제품들로 통합되지 않는다.

- [0006] 전기적 테스팅 동안, 상기 반도체 웨이퍼의 표면상에서의 도전 영역들은 보통 프로브 카드(probe card)와 컨택된다. 상기 웨이퍼는 통상적으로 이동가능한 척(chuck) 상에 마운트되며, 그것은 프로브 카드에 관련하여 상기웨이퍼를 배치하고, 테스팅 동안 상기 웨이퍼를 제자리에 유지하기 위해 사용된다. 프로브 카드들을 이용한 종래의 테스팅 시스템들은 값이 비싸며 특정 크기 이상 소형화될 수 없다. 따라서, 반도체 웨이퍼들위에 개개의다이들을 저렴하고, 빠르며, 효과적으로 테스트하기 위해 사용될 수 있는 개선된 웨이퍼 테스팅 시스템을 갖는 것이 원하여질 것이다.

#### 발명의 내용

## 도면의 간단한 설명

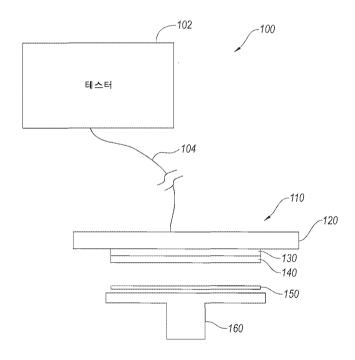

[0007] 도 1은 현재 개시된 기술의 일 실시예에 따라 구성된 테스트 환경의 개략적인 블록도이다.

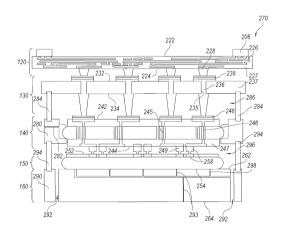

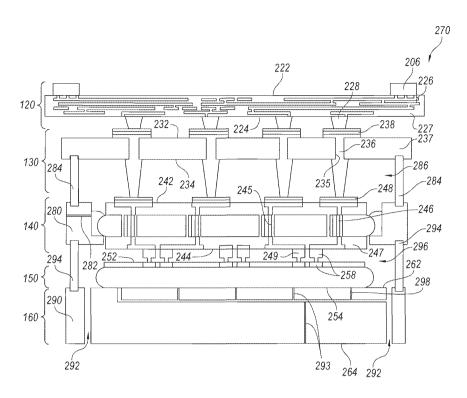

도 2는 현재 개시된 기술의 일 실시예에 따라 구성된 웨이퍼 테스팅 스택의 부분 개략도이다.

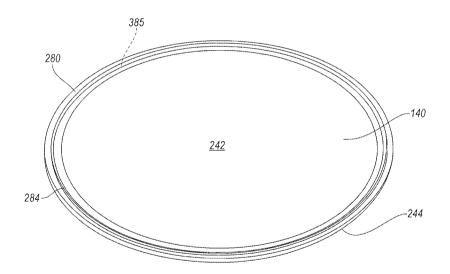

도 3a는 현재 개시된 기술의 일 실시예에 따라 구성된 웨이퍼 트랜스레이터의 부분 개략적 등각 투상도이다.

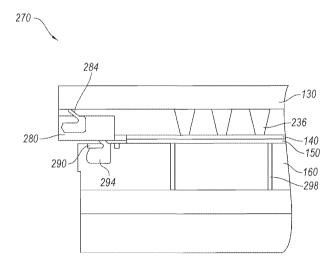

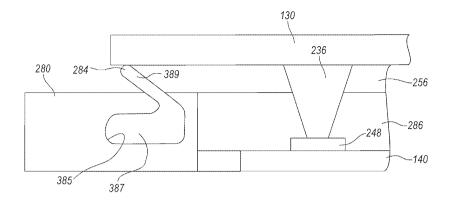

도 3b는 현재 개시된 기술의 일 실시예에 따른 인터포저에 동작가능하게 결합된 웨이퍼 트랜스레이터의 부분 개략적 단면 측면도이다.

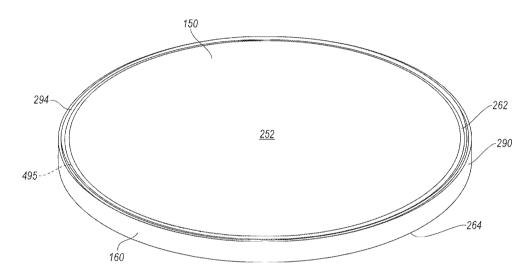

도 4a는 현재 개시된 기술의 일 실시예에 따른 웨이퍼 척에 결합된 웨이퍼의 부분 개략적 등각 투상도이다.

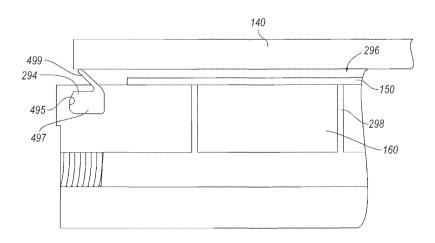

도 4b는 현재 개시된 기술의 일 실시예에 따른 웨이퍼 트랜스레이터에 동작가능하게 결합된 웨이퍼 및 웨이퍼 척의 부분 개략적 단면 측면도이다.

도 5는 현재 개시된 기술의 일 실시예에 따른 부착 공정 동안 도 2의 웨이퍼 테스팅 스택의 일부에 대한 부분 개략적 측면도이다.

도 6은 웨이퍼 척, 웨이퍼, 웨이퍼 트랜스레이터, 및 인터포저가 적충 구성으로 해제 가능하게 부착된 후 도 5 의 웨이퍼 테스팅 스택의 일부의 부분 개략적 측면도이다.

## 발명을 실시하기 위한 구체적인 내용

- [0008] 현재 개시된 기술의 실시예들은 일반적으로 웨이퍼 테스팅 시스템들 및 사용 및 제조의 연관된 방법들에 관한 것이다. 여기에서 "일 실시예", "실시예", 또는 유사한 공식 표시들에 대한 참조는 상기 실시예와 관련하여 설명된 특정한 특징, 구조, 동작, 또는 특성이 본 기술의 적어도 일 실시예에 포함된다는 것을 의미한다. 따라서, 여기에서의 이러한 구들 또는 공식 표시들의 외형들은 반드시 모두가 동일한 실시예를 참조하는 것은 아니다. 더욱이, 다양한 특정 특징들, 구조들, 동작들, 또는 특성들은 하나 이상의 실시예들에서 임의의 적절한 방식으로 조합될 수 있다.

- [0009] 여기에 사용된 바와 같이, 용어들("패드, "컨택들", 및 "전기 단자")은 일반적으로 하나의 구성요소 및 또 다른 것 사이에서의 물리적 및 전기적 연결이 이루어지는 도전 영역을 나타낸다. 집적 회로들의 문맥에서, "패드"는 통상적으로 보통 집적 회로로 및/또는 그로부터 신호들을 전달하기 위한 물리적 연결 단자를 형성하기 위해 사용되는, 상기 집적 회로의 표면에서 또는 그 가까이에서의 금속화된 영역을 나타낸다. 이러한 집적 회로 패드들은 금속, 금속 합금, 또는 통상적으로 집적 회로의 도전 재료의 최상층에 존재하는 금속들 및/또는 금속 합금들의 여러 계층들을 포함한 적층 구조로 형성될 수 있다.

- [0010] 표현("웨이퍼 트랜스레이터")은 싱귤레이션되지 않은 집적 회로들의 I/O 패드들(때때로 단자들, 패드들, 컨택패드들, 본드 패드들, 칩 패드들, 또는 테스트 패드들로서 불리우는)의 다른 전기 구성요소들로의 연결을 용이하게 하는 장치를 나타낸다. "I/O 패드들"은 일반적인 용어이며, 본 기술은 집적 회로의 특정 패드가 입력, 출력, 또는 입력/출력 회로의 일부인지 여부에 관하여 제한되지 않는다는 것이 이해될 것이다.

- [0011] 웨이퍼 트랜스레이터는 웨이퍼 및 다른 전기적 구성요소들 사이에 배치될 수 있다. 상기 웨이퍼 트랜스레이터는 각각의 표면이 그것 상에 배치된 단자들을 갖는, 두 개의 주요 표면들을 가진 기판, 및 제 1 표면상에서의 적어도 하나의 단자 및 제 2 표면상에서의 적어도 하나의 단자 사이에서 전기적 연속성을 위해 제공하기 위해 상기 기판을 통해 배치된 전기적 경로들을 포함할 수 있다. 웨이퍼를 향해 배치되도록 설계된 주요 표면은 상기 웨이퍼 트랜스레이터의 웨이퍼-측(wafer-side)으로서 불리울 수 있다. 상기 웨이퍼 트랜스레이터의 웨이퍼-측은 상기 웨이퍼 상에서의 집적 회로들의 I/O 패드들의 적어도 일부의 레이아웃에 일치하는 단자들의 패턴을 가질 수 있다. 상기 웨이퍼 트랜스레이터는, 웨이퍼 및 다른 전기적 구성요소들 사이에 배치될 때, 웨이퍼 상에서의 복수의 집적 회로들의 하나 이상의 I/O 패드들과 전기적으로 컨택하여, 그것을 통해 다른 전기적 구성요소들에 전기적 경로를 제공한다.

- [0012] 상기 웨이퍼 트랜스레이터는 제 1 규모(scale), 또는 치수(dimension)로 제조된 하나 이상의 전기 단자들, 및 제 2 규모, 또는 치수로 제조된 대응하는 세트의 전기 단자들 사이에 전기적 연결들을 달성하기 위해 사용될 수 있는 구조이다. 상기 웨이퍼 트랜스레이터는 하나의 기술(예로서, 프로브 카드의 핀들)에서 최소 특징들 및 또 다른 기술(예로서, 집적 회로의 본딩 패드들)에서의 최대 특징들 사이에 전기적 브리지를 제공할 수 있다. 편리함을 위해, 웨이퍼 트랜스레이터는 그것의 의도된 의미에 대해 애매성이 없는 트랜스레이터(translator)로서 간

단히 불리울 수 있다.

- [0013] 표현("트랜스레이트된 웨이퍼")은 부착된 상태에 있는 웨이퍼/웨이퍼 트랜스레이터 쌍, 및 상기 트랜스레이터의 웨이퍼-측 상에 배치된 집적 회로들의 컨택 패드들의 미리 결정된 부분, 또는 그 모두를 나타낸다. 착탈 가능한 부착은 예를 들면, 진공, 또는 다른 압력 차이 부착을 통해 달성될 수 있다. 즉, 공간 외부의 압력(통상적으로 대기압)에 관하여 상기 웨이퍼 및 상기 웨이퍼 트랜스레이터 사이에서의 공간에서의 압력을 감소시킴으로써, 상기 웨이퍼 및 웨이퍼 트랜스레이터는 부착 상태에 위치된다.

- [0014] 여기에 사용된 바와 같은 용어("테스터(tester)")는 장비, 통상적으로 전기적 장비를 나타내며, 이것은 집적 회로가 미리 결정된 규격에 따라 수행하는지 여부를 결정하기 위해 사용된다. 용어들("칩", "집적 회로", "반도체디바이스" 및 "마이크로전자 디바이스")은 때때로 이 분야에서 상호교환가능하게 사용된다. 본 기술은 이들 용어들이 보통 이 분야에 이해되는 바와 같이, 칩들, 집적 회로들, 반도체 디바이스들 및 마이크로전자 디바이스들의 제조 및 테스트에 관한 것이다.

- [0015] 웨이퍼 테스팅 시스템들 및 사용 및 제조의 연관된 방법들의 여러 실시예들이 이하에 설명된다. 일 실시예에서 상기 웨이퍼 테스팅 시스템은 개별적으로 동작가능한 진공들, 또는 압력 차이들에 의해 웨이퍼를 웨이퍼 트랜스 레이터에 및 상기 웨이퍼 트랜스레이터를 인터포저에 해제 가능하게 부착하기 위한 어셈블리를 포함한다. 상기 어셈블리는 웨이퍼 트랜스레이터에 결합된 웨이퍼 트랜스레이터 지지 링을 포함할 수 있으며, 여기에서 공간이 하나 이상의 제 1 배출 경로들을 통해 제 1 진공까지 배출될 수 있도록 웨이퍼 트랜스레이터 및 인터포저 사이에서의 공간을 에워싸기 위해 상기 웨이퍼 트랜스레이터 지지 링으로부터 제 1 가요성 재료가 연장된다. 상기 어셈블리는 웨이퍼 및 척에 결합된 웨이퍼 지지 링을 더 포함할 수 있으며, 여기에서 공간이 하나 이상의 제 2 배출 경로들을 통해 제 2 진공에 의해 배출될 수 있도록 상기 웨이퍼 및 웨이퍼 트랜스레이터 사이에서의 공간을 에워싸기 위해 상기 웨이퍼 지지 링으로부터 제 2 가요성 재료가 연장된다.

- [0016] 본 기술의 또 다른 양상에서, 부착 상태에서의 웨이퍼/웨이퍼 트랜스레이터/인터포저의 사용은 패드들이 이들 전기적 연결들을 이루는 공정에서 실질적으로 손상되지 않는 방식으로 웨이퍼 상에 싱귤레이션(unsingulated)되지 않은 집적 회로들의 패드들에 전기적 연결을 제공한다. 본 기술의 다양한 실시예들은 상기 웨이퍼/웨이퍼 트랜스레이터 쌍 및/또는 상기 웨이퍼 트랜스레이터/인터포저 쌍의 진공 부착을 용이하게 하기 위한 밀봉 장치 (sealing arrangement)를 제공한다. 공기 모두 또는 그것의 몇몇 부분, 또는 임의의 기체 또는 기체들의 조합은 하나 이상의 배출 경로들을 통해 웨이퍼 및 웨이퍼 트랜스레이터 사이로부터 배출된다.

- [0017] 도 1은 본 기술의 일 실시예에 따른 테스트 환경(100)의 개략적인 블록도이다. 도 1의 예에서, 상기 테스트 환경(100)은 테스터(102) 및 프로버(prober)(110)를 포함한다. 테스터(102)는 케이블(104)을 통해 프로버(110)에 전기적으로 결합된다. 프로버(110)는 디바이스 인터페이스 보드(Device Interface Board; "DIB")(120), 인터포 저(interposer)(130), 및 웨이퍼 트랜스레이터(wafer translator)(140)를 포함할 수 있다. 이하에 추가로 상세히 논의될 바와 같이, 상기 웨이퍼 트랜스레이터(140)는 웨이퍼(150)에 착탈 가능한 전기적 연결을 제공한다. 상기 웨이퍼(150)는 복수의 반도체 다이들을 포함하며, 각각의 다이는 하나 이상의 컨택들을 가진다. 상기 웨이퍼(150)는 프로브 척(160)에 의해 지지된다.

- [0018] 대표적인 웨이퍼 테스트 동안, 상기 웨이퍼 트랜스레이터(140) 및 웨이퍼(150)는 상기 웨이퍼 트랜스레이터 (140) 상에서의 하나 이상의 프로브들이 상기 웨이퍼(150) 상에서 본드 패드들에 컨택하도록 위치된다. 이것은 테스터(102)가 케이블(104), DIB(120), 인터포저(130), 및 웨이퍼 트랜스레이터(140)를 포함하는 경로를 통해 상기 웨이퍼(150)에 자극 신호(stimulus signal)들을 전송하는 것을 허용한다. 유사하게, 상기 테스터(102)는 동일한 경로를 통해 상기 웨이퍼(150)로부터 응답 신호들을 수신할 수 있다. 예를 들면, 테스터(102)는 개개의 패드들로부터 진단들을 획득할 수 있다(예로서, 테스터(102)는 패드에 신호를 공급하고 동일한 패드 또는 상이한 패드에서 응답을 분석할 수 있다).

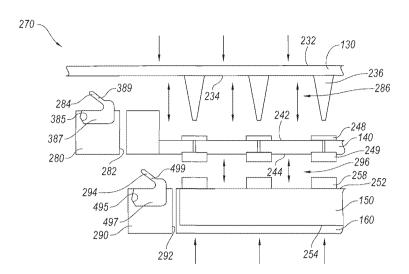

- [0019] 도 2는 본 기술의 일 실시예에 따른 웨이퍼 테스팅 스택(270)의 부분 개략도이다. 상기 테스팅 스택(270)은 DIB(120), 인터포저(130), 웨이퍼 트랜스레이터(140), 웨이퍼(150), 및 척(160)를 포함하여, 도 1을 참조하여 상기 논의된 특징들 중 여러 개를 포함한다. 상기 테스팅 스택(270)은 부착 장치에서의 이들 특징들을 도시하며, 따라서 테스터(예로서, 도 1에서의 테스터(102))는 전기적 브리지, 링크, 또는 DIB(120), 인터포저 (130), 및 웨이퍼 트랜스레이터(140)를 통과하여 계속되는 경로를 통해 상기 웨이퍼(150)에 동작가능하게 연결될 수 있다.

- [0020] 상기 DIB(120)는 제 1 표면(222) 및 상기 제 1 표면(222)의 맞은편에 제 2 표면(224)을 가진 기판(227)을 포함

한 인쇄 회로 보드일 수 있다. 하나 이상의 케이블 커넥터들(206)이 상기 제 1 표면(222)에 결합될 수 있다. 상기 케이블 커넥터들(206)은 케이블 또는 테스터(도 1에 도시된 케이블(104) 및 테스터(102)와 같은)와 동작가능하게 인터페이스하도록 구성될 수 있다. 하나 이상의 DIB 컨택들(228)은 상기 DIB(120)의 제 2 표면(224) 상에 배치될 수 있다. 상기 컨택들(228)은 상기 기판(227)을 통과하여 계속되는 전기적 경로들(226)을 통해 케이블 커넥터들(206)에 동작가능하게 연결될 수 있다.

- [0021] 상기 인터포저(130)는 DIB(120)의 제 2 표면(224)을 마주보는 제 1 표면(232) 및 상기 제 1 표면(232)의 맞은편에 제 2 표면(234)을 가진 인터포저 기판(237)을 포함한, 다-층 인쇄 회로 보드(multi-layer printed circuit board)일 수 있다. 상기 인터포저(130)는 인터포저 기판(237)내 비아(vias)(235)에 위치된 하나 이상의 컨택 핀(contact pin)들(236)을 포함할 수 있다. 상기 비아(235)는 제 1 표면(232)에서 제 2 표면(234)으로인터포저 기판(237)을 가로지를 수 있다. 상기 컨택 핀들(236)은 상기 인터포저의 제 1 표면(232)에서 또는 그가까이에서 컨택 패드들(238)에 동작가능하게 결합될 수 있다. 상기 컨택 패드들(238)은 상기 컨택 핀들(236)보다 큰 표면 면적을 가질 수 있으며, 그에 따라 상기 DIB 컨택들(228)과의 전기적 연결을 개선할 수 있다. 상기컨택 핀들(236) 및 컨택 패드들(238)은 니켈/금과 같은 도전 재료로 만들어질 수 있다. 도시된 실시예에서, 상기컨택 핀들(236)은 웨이퍼-트랜스레이터(140)를 향해 인터포저(130)의 제 2 표면(234)을 넘어 연장된다. 다른실시예들에서, 상기컨택 핀들(236)은 상기 인터포저(130)의 제 2 표면(234)에 관련하여 및 다른 개개의 컨택 핀들(236)에 관련하여 높이가 변할 수 있다.

- [0022] 웨이퍼 트랜스레이터(140)는 인터포저(130)를 마주보는 제 1 표면(242)을 가진 기판(247)을 포함할 수 있다. 제 1 전기 단자들(248)은 제 1 표면(242)에 또는 그 가까이에 위치되며 인터포저 컨택 핀들(236)과 인터페이스하도록 구성된다. 제 2 전기 단자들(249)은 웨이퍼(150)의 제 1 표면(252) 상에서의 본드 패드들(258)과 인터페이스하기 위해 제 1 표면(242)의 맞은편에 있는 웨이퍼 트랜스레이터(140)의 제 2 표면(244)에 또는 그 가까이에 위치된다. 상기 웨이퍼 트랜스레이터 기판(247)을 가로지르는 비아(245)에 배치된 전기적 경로들(246)은 제 1 표면(242)에서의 적어도 하나의 전기 단자(248) 및 제 2 표면(244)에서의 적어도 하나의 전기 단자(249) 사이에서전기적 연속성을 허용한다. 상기 웨이퍼 트랜스레이터(140)는 그에 따라 인터포저(130) 상에서의 핀들(236) 및웨이퍼(150) 상에서의 본드 패드(258)들 사이에 전기적 브리지, 링크 또는 경로를 제공한다. 상기 본드 패드들 (258)은 상기 테스터 및 상기 웨이퍼(150)의 내부 회로 사이의 최종 전기적 연결을 달성한다.

- [0023] 웨이퍼 트랜스레이터(140)의 제 2 표면(244)에서의 전기 단자들(249)의 패턴은 웨이퍼(150)위의 상기 패드들 (258)의 적어도 일부의 레이아웃에 일치하거나 또는 그것에 대응할 수 있다. 상기 웨이퍼(150) 및/또는 웨이퍼 트랜스레이터(140)는 기술의 다양한 실시예들에서 패드들(258) 및 전기단자들(249)의 상이한 패턴들 또는 배열들을 가질 수 있다. 예를 들면, 특정 실시예들에서, 상기 본드 패드들(258) 및 트랜스레이터 전기 단자들(249)은 다각형(예로서, 6각형) 또는 벌집-형 매트릭스(honeycomb-type matrix)로 배열된다. 상기 6각형 배열의 이점은 그것이 단자들 및 본드 패드들에 대한 폐쇄-패킹(close-packing)을 용이하게 한다는 것이다. 추가 실시예들에서, 상기 본드 패드들(258)은 그리드(grid)로 배열된다. 상기 전기 단자들(249)은 적어도 부분적으로 니켈, 백금, 니켈-백금 또는 다른 전기적-도전 재료들로 만들어질 수 있으며 상기 본드 패드들(258)은 적어도 부분적으로 알루미늄 또는 다른 전기적-도전 재료로 만들어질 수 있다. 특정 실시예들에서, 상기 전기 단자들(249)은 상기 본드 패드들(258)의 것보다 단단한 재료로 만들어질 수 있다. 특정 실시예들에서, 상기 전기 단자들(249)은 물리적 또는 화학적 기상 증착(vapor deposition), 스크린 프린팅(screen printing), 또는 다른 방법들에 의해 상기 웨이퍼 트랜스레이터(140) 상에 증착되거나 또는 형성될 수 있다.

- [0024] 몇몇 실시예들에서, 상기 웨이퍼-트랜스레이터(140)는 일반적으로 상기 웨이퍼(150)와 동일한 크기 및/또는 형상일 수 있으며 단일 터치(예로서, 상기 웨이퍼(150)와 상기 트랜스레이터(140)를 컨택하는 단일 인스턴스)를 갖고 상기 웨이퍼(150) 상에서 상기 패드들(258)의 모두를 컨택 및 테스트하기 위해 충분한 양의 전기 단자들(249)을 포함할 수 있다. 특정 실시예들에서, 상기 웨이퍼-트랜스레이터(140)의 전기 단자들(249)은 단일 터치에서 상기 웨이퍼(150) 상에서 130,000개 이상의 패드들(258)을 컨택한다. 특정 실시예에서, 상기 웨이퍼(150) 상에서의 100만 개 이상의 패드들(258)이 상기 웨이퍼 트랜스레이터(140)의 단일 터치에 의해 컨택된다. 특정 실시예들에서, 상기 웨이퍼 트랜스레이터(140)는 상기 웨이퍼(150)에 관하여 상이한 크기 및/또는 형상을 가지며 한 번에 상기 웨이퍼(150) 상에서의 상기 패드들(258)의 일부만을 테스트한다. 이러한 후자의 배열에서, 상기 웨이퍼 테스팅은 연속하여 상기 웨이퍼(150)의 다수의 부분들에 걸쳐 상기 테스터를 타일링(tiling)함으로써수행될 수 있다. 예를 들면, 특정 실시예에서, 40,000개의 패드들(258)을 가진 웨이퍼의 두 개의 영역들 각각은 상기 웨이퍼 트랜스레이터(140)에 의해 연속하여 컨택된다.

- [0025] 상기 웨이퍼(150) 및/또는 웨이퍼 트랜스레이터(140)의 구조는 이들 구성요소들 사이에 컨택을 개선하기 위해

맞춤(tailored)될 수 있다. 예를 들면, 상기 웨이퍼 트랜스레이터(140)의 경도(stiffness)는 서로 부합되도록하기 위해 상기 패드들 (258) 및 전기 단자들(249)에 대한 요구사항을 감소시키기 위해 기술의 다양한 실시예들에서 변경될 수 있다. 특정 실시예들에서, 가요성 웨이퍼 트랜스레이터(flexible wafer translator)(140)는 강성 지지대(rigid support) 상에 마운트된 웨이퍼(150)의 표면에 대한 유연성(compliance)을 제공하지만, 다른 실시예들에서, 상기 웨이퍼 트랜스레이터(150)는 보다 강성(rigid)이다. 특정 실시예들에서, 상기 웨이퍼-트랜스레이터(140)는 하나 이상의 보강재 보드들 또는 다른 보강 특징부(feature)들을 포함한다. 특정 실시예들에서, 상기 웨이퍼 트랜스레이터(140)는 적어도 부분적으로 실리콘 또는 세라믹으로 만들어지며 상기 웨이퍼는 적어도 부분적으로 실리콘으로 만들어진다.

- [0026] 상기 웨이퍼(150) 및 상기 웨이퍼 트랜스레이터(140) 사이에서의 컨택은 상기 웨이퍼(150)의 에지들을 향해 더미 기계적 컨택(dummy mechanical contact)들 또는 다른 표고(elevation)들을 부가함으로써 상기 웨이퍼(150)의 에지들에서 구부러짐/캔틸레버링(cantilevering)을 감소시킴으로써 추가로 개선될 수 있다. 더욱이, 패드들(258) 및/또는 전기 단자들(249)의 높이는 전기적 컨택을 개선하기 위해 웨이퍼(150) 및/또는 웨이퍼 트랜스레이터(140)에 걸쳐 정적으로 또는 동적으로(예로서, 스프링 또는 유사한 힘에 의해) 변경될 수 있다.

- [0027] 특정 실시예들에서, 상기 웨이퍼 트랜스레이터(140)는 트랜스레이터 지지 링(280)에 착탈 가능하게 또는 고정되게 결합된다. 상기 트랜스레이터 지지 링(280)은 그로부터 연장된 하나 이상의 시일(seal)들(284)을 포함할 수있다. 상기 시일들(284)은 상기 웨이퍼 트랜스레이터(140) 및 인터포저(130) 사이에서 기밀 또는 일반적으로 기밀 시일(airtight seal)을 제공하도록 구성될 수 있다. 상기 트랜스레이터 지지 링(280)은 상기 지지 링(280)을 가로지르는 하나 이상의 배출 경로(evacuation pathway)들, 또는 포트(port)들(282)을 포함할 수 있다. 몇몇 실시예들에서, 상기 배출 경로들(282)은 배출 경로들(282)을 개방 및 폐쇄하기 위한 밸브들이 설치될 수 있다. 도3a, 도3b, 및 도5를 참조하여 이하에 보다 상세히 논의될 바와 같이, 제 1 진공은 상기 배출 경로들(282)을 통해 공기를 배출시키기 위해 상기 인터포저(130) 및 상기 웨이퍼 트랜스레이터(140) 사이의 공간(286)을 빨아들일 수 있고, 그렇게 함으로써 상기 인터포저(130) 및 웨이퍼 트랜스레이터(140)를 함께 끌어 당길 수 있고 그리고 해제 가능하게 부착할 수 있는 압력 차이(pressure differential)을 생성할 수 있다. 특정 실시예들에서, 상기 트랜스레이터 지지 링(280)은 상기 트랜스레이터 지지 링 배출 경로(282)가 상기 인터포저(130)의 원주 내부에 있도록 상기 인터포저(130)의 직경보다 작은 직경을 가진다. 추가 실시예들에서, 상기 트랜스레이터 지지 링(290)은 상기 인터포저(130)의 직경과 동일하거나 또는 그보다 큰 직경을 가지며, 상기 배출 경로들(282)은 상기 인터포저(130)에 대하여 동일하거나 또는 상이한 위치들에 있을 수 있다.

- [0028] 상기 웨이퍼(150)는 상기 트랜스레이터 지지 링(280)을 참고로 하여 상기 설명된 것과 유사한 방식으로 상기 웨 이퍼(150)를 주변에서 둘러싸거나 또는 적어도 부분적으로 둘러싸는 척 지지 링(290)에 또는 그것 상에 위치될 수 있다. 상기 척 지지 링(290)은 상기 척(160)와 함께 필수적일 수 있거나 또는 별개의 구성요소를 포함할 수 있다. 상기 척 지지 링(290)은 그로부터 연장된 하나 이상의 시일들(294)을 포함할 수 있다. 상기 시일들(294) 은 상기 웨이퍼(150) 및 상기 웨이퍼 트랜스레이터(140) 사이에 기밀 또는 일반적으로 기밀 시일을 제공하도록 구성될 수 있다. 상기 척 지지 링(290)은 상기 웨이퍼 트랜스레이터(140) 및 상기 웨이퍼(150) 사이에서의 공간 (296)에 접근하는 하나 이상의 배출 경로들, 또는 포트들(292)을 포함할 수 있다. 예를 들면, 상기 포트들(29 2)은 상기 척(160)의 제 1 표면(262)으로부터 상기 제 1 표면(262)의 맞은편에 있는 척의 제 2 표면(264)으로 상기 척(160)를 가로지를 수 있다. 특정 실시예들에서, 상기 배출 경로들(292)은 상기 배출 경로들(292)을 개방 및 폐쇄하기 위해 밸브들이 설치될 수 있다. 도 4a, 도 4b, 및 도 5를 참조하여 이하에 추가로 상세히 논의될 바와 같이, 제 2 진공은 상기 웨이퍼 트랜스레이터(140) 및 상기 웨이퍼(150) 사이에서의 공간(296)에서 동작할 수 있으며, 그렇게 함으로써 상기 웨이퍼 트랜스레이터(140) 및 상기 웨이퍼(150)를 함께 끌어 당길 수 있고 그 리고 해제 가능하게 부착하는 압력 차이를 생성할 수 있다. 몇몇 실시예들에서, 공기 또는 다른 기체가 상기 배 출 경로들(292)을 통해 상기 공기 공간(296)으로부터 배출될 수 있다. 배출 경로들(292)을 진공 소스에 결합하 기 위한 다른 적절한 구성들이 다른 실시예들에서 사용될 수 있다는 것이 이해될 것이다. 특정 실시예들에서, 상기 웨이퍼(150) 및 상기 웨이퍼 트랜스레이터(140)는 2009년 8월 25일에 출원된, "그 사이에 배치된 가스켓이 없는 부착 상태에서 웨이퍼/웨이퍼 트랜스레이터 쌍을 유지하는 방법(MAINTAINING A WAFER/WAFER TRANSLATOR PAIR IN AN ATTACHED STATE FREE OF A GASKET DISPOSED THEREBETWEEN)" 명칭의, 본 출원의 양수인에게 양도된, 미국 특허 출원 번호 제12/547,418호에 설명된 시스템들 및 방법들에 의해 착탈 가능하게 부착될 수 있고, 그것 의 전체가 참조로서 본 출원에 통합된다.

- [0029] 몇몇 실시예들에서, 상기 웨이퍼(150)는 제 3 진공으로 척(160)에 해제 가능하게 결합될 수 있다. 상기 웨이퍼 (150)는 상기 척(160)의 제 1 표면(262)을 컨택하는 웨이퍼(150)의 제 2 표면(254)을 갖고, 척(160)를 향해 당

겨지고 그것 상에서 착탈 가능하게 유지될 수 있다. 상기 척(160)는 상기 척(160) 및 상기 웨이퍼(150) 사이에서 흡착(suction)을 실시하기 위해 진공 홀들(298)을 포함할 수 있다. 특정 실시예에서, 상기 척은 약 317 ㎜의 직경을 가지며 상기 웨이퍼는 약 300 ㎜의 직경을 가진다. 다른 실시예들에서, 상기 척 및/또는 웨이퍼는 다른 치수들을 가질 수 있다. 특정 실시예들에서, 상기 척 지지 링(290)은 상기 트랜스레이터 지지 링 배출 경로(282)가 상기 척 지지 링(290)의 원주 외부에 있도록 상기 트랜스레이터 지지 링(280)의 직경보다 작은 직경을 가진다. 추가 실시예들에서, 상기 척 지지 링(290)은 상기 트랜스레이터 지지 링(280)과 동일하거나 또는 그보다 큰 직경을 가진다. 상기 웨이퍼(150)는 웨이퍼 로봇 또는 유사하게 잘-알려진 웨이퍼 수송 장비에 의해 상기 척(160)로 전달될 수 있다. 몇몇 실시예들에서, 상기 척(160)는 상기 웨이퍼(150)의 제 2 표면(254)을 지지하기 위해 복수의 리프트 핀(lift pin)들을 포함할 수 있다.

- [0030] 도 3a는 본 기술의 일 실시예에 따라 구성된 웨이퍼 트랜스레이터(140)의 부분 개략적 등각 투상도이다. 도 3b는 본 기술의 일 실시예에 따른 상기 인터포저(130)에 동작가능하게 결합된 웨이퍼 트랜스레이터(140)의 부분 개략적 단면 측면도이다. 먼저 도 3a를 참조하면, 상기 웨이퍼 트랜스레이터(140)는 상기 트랜스레이터 지지 링 (280)에 결합되고 그것에 의해 주변이 둘러싸여진다. 특정 실시예들에서, 상기 지지 링(280)은 금속으로 제조되지만, 다른 실시예들에서 다른 재료들을 포함할 수 있다. 상기 지지 링(280)은 상기 시일(284)을 수취하도록 구성된 홈(groove)(385)을 포함한다. 다양한 실시예들에서, 상기 시일(284)은 보다 강성이거나 또는 보다 덜 강성 (rigid)일 수 있다. 도시된 예에서, 상기 홈(385)은 상기 지지 링(280)의 제 1 표면(242) 주변에서 연속하여 이어인다. 상기 지지 링(280)은 상기 홈(385)의 주변에서 안쪽으로 하나 이상의 배출 경로들을 포함할 수 있다. 도 2를 참조하여 상기 설명된 바와 같이, 상기 배출 경로들은 상기 트랜스레이터 지지 링(280)을 통해 가로지를 수 있으며 상기 배출 경로들을 개방 및 폐쇄하기 위해 밸브들이 설치될 수 있다.

- [0031] 이제 도 3b를 참조하면, 상기 시일(284)은 상기 홈(385)에 고정된 베이스 부분(387) 및 상기 지지 링(280)으로 부터 겉으로 연장된 상부 부분(389)을 포함한다. 상기 홈(385)은 상기 시일(284)의 베이스 부분(387)을 유지하기 위해 플랜지(flange)될 수 있다. 도시된 실시예에서, 상기 상부 부분(389)은 상기 지지 링(280)의 최상부 측에 대하여 원주 둘레에서 바깥쪽로 비스듬히 놓이지만, 다른 실시예들에서, 상기 상부 부분(389)은 상기 지지링(280)의 최상부 측에 대하여 수직 또는 거의 수직일 수 있다. 상기 상부 부분(389)은 웨이퍼 트랜스레이터(140) 및 인터포저(130) 사이에서의 공간(286)에 진공 또는 부분 진공을 유지하기 위해 시일로서 동작하도록 구성된다. 상기 진공은 착탈 가능하게 부착된 상태에서 상기 웨이퍼 트랜스레이터(140) 및 인터포저(130)를 유지한다. 상기 웨이퍼 트랜스레이터(140) 및 상기 인터포저(130)는 상기 배출 경로들을 개방하기 위해 상기 시일(284)을 해제함으로써 또는 밸브를 개방함으로써 서로로부터 해제될 수 있다.

- [0032] 도 4a는 본 기술의 일 실시예에 따른 웨이퍼 척(160) 상에 위치된 웨이퍼(150)의 부분 개략적 등각 투상도이다. 도 4b는 본 기술의 일 실시예에 따른 웨이퍼 트랜스레이터(140)에 동작가능하게 결합된 웨이퍼(150) 및 웨이퍼 척(160)의 부분 개략적 단면 측면도이다. 먼저 도 4a를 참조하면, 상기 웨이퍼(150)는 상기 척 지지 링(290)에 결합되며 그것에 의해 주변에 둘러싸여진다. 상기 척 지지 링(290)은 시일(294)을 수취하도록 구성된 홈(495)을 포함한다. 도시된 실시예에서, 상기 홈(495)은 상기 지지 링(290)의 최상부측 주변에서 연속하여 이어진다. 상기 척 지지 링(290)은 상기 홈(495)의 주변 안쪽에 하나 이상의 배출 경로들(도 4a에서 가시적이지 않음)을 포함할 수 있다. 상기 배출 경로들은 상기 척의 제 1 표면(262)으로부터 제 2 표면(264)으로 가로지를 수 있다. 상기 링(290)에서의 배출 경로들은 상기 배출 경로들을 개방 및 폐쇄하기 위해 밸브들이 설치될 수 있다. 몇몇 실시예들에서, 상기 척 지지 링(290)은 상기 척(160)에 필수적이며, 상기 척(160)는 상기 웨이퍼(150)에 해제 가능하게 결합된다(예로서, 상기 척(160)는 상기 척 진공 홀들(298)을 통해 상기 웨이퍼(150)에 대한 진공 유지 디바이스(vacuum hold-down device)로서 작용할 수 있다).

- [0033] 이제 도 4b를 참조하면, 상기 시일(294)은 홈(495)에 고정된 베이스 부분(497) 및 상기 지지 링(290)으로부터 겉으로 연장된 상부 부분(499)을 포함한다. 상기 홈(495)은 상기 시일(294)의 베이스 부분(497)을 유지하기 위해 플랜지될 수 있다. 도시된 실시예에서, 상기 상부 부분(499)은 상기 지지 링(290)의 최상부 측에 대하여 비스듬히 놓이지만, 다른 실시예들에서, 상기 상부 부분(499)은 수직 또는 거의 수직일 수 있다. 상기 상부 부분(499)은 웨이퍼 트랜스레이터(140) 및 웨이퍼(150) 사이에서의 공간(296)에 진공 또는 부분 진공을 유지하기 위해 시일로서 동작하도록 구성된다. 상기 진공은 착탈 가능하게 부착된 상태에서 상기 웨이퍼 트랜스레이터(140) 및 웨이퍼(150)를 유지한다. 상기 웨이퍼 트랜스레이터(140) 및 상기 웨이퍼(150)는 하나 이상의 배출 경로들을 개방하기 위해 상기 시일(294)을 해제함으로써 또는 밸브를 개방함으로써 서로로부터 해제될 수 있다.

- [0034] 도 5는 본 기술의 일 실시예에 따른 부착 공정 동안 도 2의 웨이퍼 테스팅 스택(270)의 일부의 부분 개략적 측면도이다. 도 2 내지 도 4b를 참조하여 상술된 바와 같이, 복수의 진공들은 (a) 상기 웨이퍼 트랜스레이터(14

0)에 인터포저(130)를 착탈 가능하게 부착하고, (b) 상기 웨이퍼(150)에 상기 웨이퍼 트랜스레이터(140)를 착탈 가능하게 부착하고, 및/또는 (c) 상기 척(160)에 상기 웨이퍼(150)를 착탈 가능하게 부착하기 위해 독립적으로 동작할 수 있다. 도시된 실시예에서, 상기 인터포저(130)가 상기 웨이퍼 트랜스레이터(140)를 향해 아래쪽으로 이동하는 동안 상기 척(160) 및 웨이퍼(150)는 착탈 가능하게 부착되고 상기 웨이퍼 트랜스레이터(140)를 향해 위쪽으로 함께 이동한다. 특정 실시예들에서, 상기 인터포저(130) 및 상기 척(160) 중 단지 하나만이 이들 요소들 중 하나가 정지된 채로 있는 동안 다른 것을 향해 이동한다. 통상적으로, 상기 웨이퍼 트랜스레이터(140) 및 웨이퍼(150)는 상기 웨이퍼 트랜스레이터(140)의 제 2 표면(244)에 배치된 전기 단자들(249) 및 상기 웨이퍼(150)의 제 1 표면(252)에서의 패드들(258)이 상기 웨이퍼(150) 및 웨이퍼 트랜스레이터(140) 사이에서의 공간(296)이 배출될 때 서로와 전기적 컨택을 하도록 서로에 대하여 정렬된다. 상기 인터포저(130) 및 웨이퍼 트랜스레이터(140)는 마찬가지로 상기 웨이퍼 트랜스레이터(140)의 제 1 표면(242) 상에 배치된 전기 단자들(248) 및 인터포저 컨택 핀들(236)이 상기 웨이퍼 트랜스레이터(130) 및 상기 인터포저(130) 사이에서의 공간(286)이 배출될 때 서로 전기적 컨택을 하도록 서로에 대하여 정렬된다.

- [0035] 웨이퍼(150)가 상기 웨이퍼 트랜스레이터(140)에 다가감에 따라, 상기 척 시일(294)은 상기 웨이퍼 트랜스레이 터(140) 또는 상기 웨이퍼 트랜스레이터 지지 링(280)의 제 2 표면(244)을 컨택하며 상기 웨이퍼(150) 및 상기 웨이퍼 트랜스레이터(140) 사이에서의 공간(296)을 밀봉한다. 공기 또는 다른 기체가 진공에 의하여 상기 척 지 지 링 배출 경로들(292)을 통해 빨아내기 때문에, 대기의 공기 압력은 웨이퍼 트랜스레이터(140) 및 웨이퍼 (150)를 착탈 가능하게 부착된 상태에 배치하며, 상기 웨이퍼 트랜스레이터(140)의 제 2 표면(244) 상에서의 전 기 단자들(249)은 상기 웨이퍼(150)의 제 1 측(252)의 패드들(258)과 전기적 컨택을 이룬다. 마찬가지로, 상기 인터포저(130)가 상기 웨이퍼 트랜스레이터(140)에 다가감에 따라, 상기 웨이퍼 트랜스레이터 시일(284)은 상기 인터포저(130)의 제 2 표면(234)의 주변 고리 모양 부분을 컨택하고 상기 인터포저(130) 및 상기 웨이퍼 트랜스 레이터(140) 사이에서의 공간(286)을 밀봉한다. 상기 웨이퍼 트랜스레이터(140) 및 상기 인터포저(130) 사이에 서의 공기 또는 다른 기체는 배출 경로들(282)을 통해 상기 공간(286)으로부터 빨아내어진다. 상기 웨이퍼 트랜 스레이터(140) 및 상기 인터포저(130) 밖에서의 기압은 착탈 가능하게 부착된 상태로 이들 구성요소들을 배치할 수 있으며, 여기에서 상기 웨이퍼 트랜스레이터(140)의 제 1 측(242) 상에서의 전기 단자들(248)은 상기 인터포 저(130)의 제 2 측(234) 상에서의 컨택 핀들(236)과 전기적 컨택을 이룬다. 도시된 실시예는 웨이퍼 테스팅 스 택을 형성하기 위해 동시에 부착한 인터포저(130), 웨이퍼 트랜스레이터(140), 및 웨이퍼(150)/척(160)를 도시 하지만, 특정 실시예들에서, 구성요소들은 순차적으로 서로에 부착할 수 있다(예로서, 상기 인터포저(130) 및 웨이퍼 트랜스레이터(140)는 상기 웨이퍼 트랜스레이터(140)가 상기 웨이퍼(150)에 부착되기 전에 서로에 부착 할 수 있다).

- [0036] 도 6은 상기 척(160), 웨이퍼(150), 웨이퍼 트랜스레이터(140) 및 인터포저(130)가 스택 구성으로 해제 가능하게 부착된 후 도 5의 웨이퍼 테스팅 스택(270)의 일부의 부분 개략적 측면도이다. 상기 웨이퍼 트랜스레이터 지지 링(280)으로부터 연장된 시일(284)은 이들 구성요소들이 제 1 진공을 통해 함께 당겨진 후, 상기 인터포저(130) 및 상기 웨이퍼 트랜스레이터(140) 사이에서 기밀 또는 일반적으로 기밀 시일을 생성하기 위해 상기 인터포저(130)를 끌어들인다. 상기 척 지지 링(290)으로부터 연장된 시일(294)은 마찬가지로 이들 구성요소들이 제2 진공을 통해 함께 당겨진 후, 상기 웨이퍼(150) 및 상기 웨이퍼 트랜스레이터(140) 사이에 제2 기밀 또는 일반적으로 기밀 시일을 생성한다. 상기 척(160) 및 웨이퍼(150)는 척 진공 홀들(298)을 통해 동작하는 제3 진공에 의하여 해제 가능하게 부착되었다.

- [0037] 제 1, 제 2, 및 제 3 진공들은 독립적으로 동작가능할 수 있어서, 상기 척(160) 및 웨이퍼(150)사이에서, 상기 웨이퍼(150) 및 웨이퍼 트랜스레이터(140) 사이에서, 및 상기 웨이퍼 트랜스레이터(140) 및 상기 인터포저(13 0)사이에서 상이한 기압 경도력들(pressure forces)을 제공할 수 있다. 이들 구성요소들 사이에서의 기압 경도력들은 그에 따라 상기 디바이스들의 컨택들 또는 다른 구성요소들을 손상시킬 수 있는 과도한 기압 경도력들 없이 컨택 및 테스팅 성능을 개선하기 위해 독립적으로 변경될 수 있다. 추가 실시예들에서, 상기 구성요소들 중 둘 이상 사이에서의 공기 공간은 서로와 유체 소통할 수 있으며 공통 진공에 의해 밀봉될 수 있다.

- [0038] 본 기술의 실시예들은 웨이퍼 테스팅 기술들에서의 많은 이점들을 제공할 수 있다. 예를 들면, 여기에 개시된 상기 웨이퍼 테스팅 시스템들은 테스팅을 위한 웨이퍼들의 유형들을 변경할 필요가 있을 때 쉽게 적응가능할 수 있다. 보다 구체적으로, 패드들의 대안적인 교대 배열을 가진, 새로운 유형의 웨이퍼가 테스팅될 준비가 될 때, 단지 상기 웨이퍼 트랜스레이터(또는 단지 상기 웨이퍼 트랜스레이터의 웨이퍼-측)만이 새로운 웨이퍼의 본드 패드 배열에 일치하도록 교체될 필요가 있다. 상기 DIB 및 인터포저는 보편적으로 다수의 유형들의 웨이퍼들을 수용할 수 있다. 이러한 배열은 새로운 구성을 가진 웨이퍼가 사용될 때 전체 프로버가 교체되는 종래의 시스템

들에 비해 상당한 비용 절감들로 이어질 수 있다.

[0039] 상이한 유형들의 웨이퍼들을 수용하기 위한 능력은 개별적으로-제어가능한 진공들에 의해 부가적으로 지원될 수 있다. 보다 구체적으로, 상기 진공들은 효과적인 전기적 컨택을 제공하기 위해 구성요소들 사이에서 기압 경도력들을 제어할 수 있으며 새로운 웨이퍼 상에서 본드 패드들의 수 및 특정 배열을 맞추기 위해 상기 웨이퍼 및 상기 웨이퍼 트랜스레이터 사이에서의 압력 차이를 조정할 수 있다. 상기 다중-진공 시스템은 또한 상기 웨이퍼 트랜스레이터가 컨택력들을 미세-조정하고 전체 웨이퍼를 보다 효과적으로 컨택할 수 있게 하며, 그에 의해 단일 터치로 상기 웨이퍼 상에서의 패드들 모두를 테스팅할 수 있다. 이것은 테스팅 시간을 감소시킬 수 있으며 반복되거나 또는 엄격한 테스팅으로부터 개개의 패드들 상에서의 마모를 감소시킬 수 있다.

더욱이, 여기에 개시된 시스템들은 통상적인 테스팅 시스템들에서의 것들보다 작은 컨택들을 가진 웨이퍼 트랜스레이터를 제공한다. 보다 작은 컨택들 사이에서 보다 적은 안테나 효과가 존재하기 때문에 상기 트랜스레이터 상에서의 보다 작은 컨택들은 웨이퍼의 테스팅 속도를 증가시킬 수 있다. 특정 실시예들에서, 상기 테스팅 속도는 초당 약 500 메가 비트(Mbits)들일 수 있다. 추가 실시예들에서, 상기 테스팅 속도는 초당 약 120 기가 비트 (Gbits)들일 수 있다.

앞서 말한 것으로부터, 본 기술의 특정 실시예들은 예시를 위해 여기에 설명되었지만, 다양한 변경들이 본 기술의 범위로부터 벗어나지 않고 이루어질 수 있는 것이 이해될 것이다. 예를 들면, 상기 웨이퍼들 및 트랜스레이터들은 상기에서 명확히 도시되고 설명된 것들 이외의 다른 구성들로 배열된 컨택들을 가질 수 있다. 특정 실시예들의 문맥에서 설명된 본 개시의 특정 양상들은 다른 실시예들에서 조합되거나 또는 제거될 수 있다. 예를 들면, 몇몇 실시예들은 단지 웨이퍼 스택의 특정 요소들만을 포함한다. 따라서, 본 개시 및 연관된 기술은 여기에 명확하게 도시되거나 또는 설명되지 않은 다른 실시예들을 포함할 수 있다.

#### 도면

[0040]

[0041]

### 도면1

## 도면2

## 도면3a

# 도면3b

# 도면4a

# *도면4b*

## 도면5

## 도면6