(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4688822号 (P4688822)

(45) 発行日 平成23年5月25日(2011.5.25)

(24) 登録日 平成23年2月25日(2011.2.25)

(51) Int.Cl. F 1

GO 6 F 13/12 (2006.01) GO 6 F 13/12 3 1 O C GO 6 F 13/36 (2006.01) GO 6 F 13/36 3 1 O A GO 6 F 15/78 (2006.01) GO 6 F 15/78 5 1 O B

請求項の数 3 (全 27 頁)

(21) 出願番号 特願2006-547231 (P2006-547231)

(86) (22) 出願日 平成18年6月6日 (2006.6.6)

(86) 国際出願番号 PCT/JP2006/311337

(87) 国際公開番号 W02006/134804 (87) 国際公開日 平成18年12月21日 (2006.12.21)

審査請求日 平成18年11月24日 (2006.11.24) (31) 優先権主張番号 特願2005-175677 (P2005-175677)

(32) 優先日 平成17年6月15日 (2005. 6. 15) (33) 優先権主張国 日本国 (JP)

前置審査

||(73)特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

|(74)代理人 100109210

弁理士 新居 広守

|(72)発明者 川上 隆央

日本国大阪府門真市大字門真1006番地

松下電器産業株式会社内

|(72)発明者 中島 雅逸

日本国大阪府門真市大字門真1006番地

松下電器産業株式会社内

(72) 発明者 清原 督三

日本国大阪府門真市大字門真1006番地

松下電器産業株式会社内

最終頁に続く

(54) 【発明の名称】外部デバイスアクセス装置およびシステムLSI

## (57)【特許請求の範囲】

## 【請求項1】

マスタから外部デバイスへのアクセスを制御する外部デバイスアクセス装置であって、 前記マスタからの外部デバイスへの書き込み要求に応じて、書き込みアドレスを格納す るための書き込みアドレス格納手段と、

前記書き込み要求に応じて、書き込みデータを格納するための書き込みデータ格納手段と、

前記マスタからアクセス可能であり、読み出しアドレスを格納するための読み出しアドレス格納手段と、

前記マスタからアクセス可能であり、外部デバイスから読み出されたデータを格納する ための読み出しデータ格納手段と、

前記マスタからの書き込み要求または読み出し要求とアドレス指定に応じて、外部デバイスへのアクセスを制御する制御手段と、

前記外部デバイスから出力される状態信号を格納する状態信号格納手段と、

前記外部デバイスから出力される状態信号と、前記状態格納手段に格納された状態信号との一方を選択して前記マスタに出力する選択手段と、

を備え、

前記制御手段は、

前記マスタから外部デバイスへの書き込み要求に応じて、マスタからの書き込みアドレ スと書き込みデータとをそれぞれ書き込みアドレス格納手段と書き込みデータ格納手段と

20

に格納するとともに、マスタに受理信号を出力し、さらに、当該書き込みアドレスによって指定される外部デバイスに対して、当該書き込みデータを書き込み、

\_\_前記マスタから前記読み出しデータ格納手段への書き込み要求に応じて、前記読み出しアドレス格納手段に読み出しアドレスを格納<u>し、</u>さらに、当該読み出しアドレスによって指定される外部デバイスからデータを読み出して前記読み出しデータ格納手段に格納し、さらに、前記読み出しデータ格納手段に格納すると同時に、前記外部デバイスから出力される状態信号を前記状態信号格納手段に格納し、

前記マスタから前記読み出しデータ格納手段へのデータ読み出し要求に応じて、前記読み出しデータ格納手段から読み出しデータを出力し、さらに、前記状態信号格納手段から 状態信号を前記選択手段を介して出力する

ことを特徴とする外部デバイスアクセス装置。

## 【請求項2】

請求項1記載の外部デバイスアクセス装置であって、

前記制御手段は、

前記マスタから外部デバイスへの書き込み要求に応じて、マスタからの書き込みアドレスと書き込みデータとをそれぞれ書き込みアドレス格納手段と書き込みデータ格納手段とに格納するとともに、マスタに受理信号を出力するのと同時に、その時点の外部デバイスからの状態信号を前記選択手段を介して出力する制御と、

\_\_前記マスタから前記読み出しデータ格納手段への書き込み要求に応じて、前記読み出しアドレス格納手段に読み出しアドレス<u>を</u>格納するとともに<u>、そ</u>の時点の外部デバイスからの状態信号を前記選択手段を介して出力する制御と、

前記マスタから前記読み出しデータ格納手段へのデータ読み出し要求に応じて、前記読み出しデータ格納手段から読み出しデータを出力するのと同時に、前記状態信号格納手段から格納している状態信号を前記選択手段を介して前記マスタに出力する制御と

を行う

ことを特徴とする外部デバイスアクセス装置。

## 【請求項3】

マスタと、

請求項1または2に記載の外部デバイスアクセス装置と、

前記マスタから外部デバイスアクセス装置を介してアクセスされる外部デバイスと を備えるシステムLSI。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、システムLSIにおいて、マスタが外部デバイスへアクセスすることに関し、特に、マスタが外部デバイスを容易に拡張し、かつ拡張の際にマスタが外部デバイスの種類に依存しないための外部デバイスアクセス装置に関する。

### 【背景技術】

[00002]

メディア処理には外部デバイスでマスタをアシストすることが有効な場合があり、その ためのマスタには、外部デバイスを拡張するための拡張バスを持たせることがある。

[0003]

ここで、メディア処理とは、音声処理、画像処理などのデータ処理一般のこと、マスタとはCPUやマイコン等、主制御を担当する装置のこと、外部デバイスとはそのCPUやマイコン等をアシストする、コプロセッサやアクセラレータ、メモリ等の周辺装置のことである。

## [0004]

マスタは拡張バスを持ち、アクセス空間に外部デバイスの資源を割り当てることで、その外部デバイスの資源をマスタの拡張された資源として扱うことができるようになり、マスタと外部デバイスとの通信を高速に行うことが可能となる。このことにより、マスタの

10

20

30

40

10

20

30

40

50

処理性能を上げ、ソフト・ハードの両面の機能実現をさらに容易にすることができる。

#### [0005]

ここで、アクセス空間とはマスタがアクセスできる、プログラムアクセス、データアクセスや入出力アクセス等のためのアドレスの割り当てられた空間のことである。

## [0006]

このアクセスを実現する方法としては、従来、マスタが拡張バスのインターフェースを もち、そのインターフェースを介して、オンチップの外部デバイスにアクセスする方法や 、さらに、チップ外の外部デバイスに対しては、別のインターフェースを介して、拡張バ スのプロトコルに変換して、マスタの拡張バスのインターフェースを介してアクセスする などの方法が取られてきた。(例えば、特許文献 1 参照。)

【特許文献1】特開平7-6151号公報(第15頁、図5)

【発明の開示】

【発明が解決しようとする課題】

[0007]

従来の方法では、システムLSIのカスタマイズにおいて、例えばメディア処理の高度化に伴ってマスタを高速化する場合、個々に動作速度の異なる外部デバイスへのアクセスに対応するために、外部デバイス毎にマスタ自身を最適化することが必要であり、システムLSIのカスタマイズを複雑かつ煩雑にしているという問題がある。

[00008]

また、外部デバイス個別の最適化をマスタ自身において実施しない場合は、ボトルネックとなる外部デバイスへのアクセスレイテンシやスループットなどによるペナルティがマスタの性能に多大な影響を与えてしまうという課題がある。

[0009]

また、外部デバイス個別の最適化をマスタ自身において実施するためには、新たなメディア処理に対応した外部デバイスが新規に必要となる度に、また不具合等の理由で外部デバイスが改変される度に、マスタ自身の改変をする必要が発生し、開発資産の有効活用という点において、多大なロスを生み出すという課題がある。

[0010]

本発明は、マスタ自身の最適化をしなくてもマスタから外部デバイスへのアクセス性能を劣化させず、システムLSI開発資産を有効活用させる外部デバイスアクセス装置およびシステムLSIを提供することを目的とする。

【課題を解決するための手段】

[0011]

上記課題を解決するため本発明の外部デバイスアクセス装置は、マスタから外部デバイスアクセス装置であって、前記マスタからのからのアクセスを制御する外部デバイスアクセス装置であって、前記マスタからのアドレスを格納するための書き込みアドレスを格納するための書き込みアドレスを格納するための書き込みアドレスを格納するための書き込みアクセス可能であり、読み出しアドレス格納手段と、前記マスタからアクセス可能であり、外部デバイスのの意込の出しアドレス格納手段と、前記マスタからアクセス可能でありに、外部デバイスのの表もとの読み出しアドレス格納するための読み出しでであり、外部デバイスのの書き込みである制御手段とを備え、前記制御手段は、前記マスタからがボバイスへの書き込みアドレスと書き込みデータとをそれぞれ書き込みアドレスと書き込みデータとをそれぞれ書き込みアドレスと書き込みデータ格納手段とに格納するとともに、マスタによって指定される外部デバイスからデータを書き込み、マスタによって指定される外部デバイスからデータを書き込み、マスタによって指定される外部デバイスからデータを読み出し、前記読み出しデータ格納手段に格納する。

[0012]

この構成によれば、メディア処理の高度化に伴ってマスタが高速化する場合、個々に動

作速度の異なる外部デバイスへのアクセスにおいて、マスタの書き込み要求または読み出し要求時にマスタの状態に依存しないアクセスを実現し、外部デバイスへのアクセスペナルティを隠蔽してマスタの性能への影響を少なくできる効果がある。

#### [0013]

さらに外部デバイスに応じて、外部デバイスアクセス装置の資源を調整することにより 、外部デバイスへのアクセスの最適化が容易に実施できる効果がある。

### [0014]

またシステムLSIにおいては、マスタが外部デバイスへアクセスするために外部デバイスアクセス装置を備えることにより、システムLSIを開発する度にマスタの改変をする必要がなくなり外部デバイスアクセス装置の改変のみで済むため、システムLSIにおけるマスタの開発コストを大幅に低減する効果がある。

#### [0015]

ここで、前記外部デバイスアクセス装置は、さらに、前記外部デバイスから出力される 状態信号を格納する状態信号格納手段を備え、前記制御部は、さらに、前記書き込みデータ格納手段に格納されたデータを外部デバイスに書き込むと同時に、前記外部デバイスから出力される前記状態信号を前記状態信号格納手段に格納し、前記読み出しアドレス格納 手段に格納されたアドレスによって指定される外部デバイスからデータを読み出して前記 読み出しデータ格納手段に格納すると同時に、前記外部デバイスから出力される状態信号 を前記状態信号格納手段に格納し、前記状態信号格納手段は、格納している状態信号を前記スタに出力するようにしてもよい。

### [0016]

この構成によれば、さらに外部デバイスの状態をマスタへ伝達する機能を実現し、マスタの性能に寄与する効果がある。

#### [0017]

ここで、前記外部デバイスアクセス装置は、前記読み出しアドレス格納手段および前記 読み出しデータ格納手段の代わりに、それらを兼用するアドレス / データ格納手段を備え るようにしてもよい。

### [0018]

この構成によれば、さらに読み出しアドレス格納手段と前記読み出しデータ格納手段とを独立に備える必要がなくなるので、外部デバイスアクセス装置をより小さくし、コストを削減する効果がある。

## [0019]

ここで、前記外部デバイスアクセス装置は、さらに、前記書き込みアドレスまたは前記読み出しアドレスが、未実装の外部デバイスのアドレスであるか否かを示す未実装情報を格納するための未実装情報格納手段を備え、前記制御部は、さらに、前記書き込みアドレス格納手段または読み出しアドレス格納手段に格納された書き込みアドレスまたは読み出しアドレスによって指定される外部デバイスが未実装であるかどうかを判定し、未実装である場合には、前記未実装情報格納手段に未実装情報を格納し、当該未実装情報を前記マスタに通知するようにしてもよい。

### [0020]

この構成によれば、さらに読み出しアドレスまたは書き込みアドレスが、実装されていない外部デバイスを指すことを検出する機能を実現し、マスタの性能に寄与する効果がある。

## [0021]

ここで、前記外部デバイスアクセス装置は、さらに、未実装の外部デバイスのアドレスをエラーアドレスとして格納するためのエラーアドレス格納手段を備え、前記制御部は、さらに、前記書き込みアドレス格納手段または読み出しアドレス格納手段に格納された書き込みアドレスまたは読み出しアドレスによって指定される外部デバイスが未実装であるかどうかを判定し、未実装である場合には、当該アドレスをエラーアドレスとして前記エラーアドレス格納手段に格納し、当該エラーアドレスを前記マスタに通知するようにして

10

20

30

40

もよい。

## [0022]

この構成によれば、さらに指定されたアドレスが、任意の外部デバイスに対して実装されていないことを検出し、そのアドレスをマスタが認識できる機能を実現し、マスタの性能に寄与する効果がある。

### [0023]

ここで、前記制御部は、さらに、前記書き込みアドレス格納手段または読み出しアドレス格納手段に格納された書き込みアドレスまたは読み出しアドレスによって指定される外部デバイスが未実装であるかどうかを判定し、未実装である場合には、当該アドレスをエラーアドレスとして前記読み出しデータ格納手段に格納し、当該エラーアドレスを前記マスタに通知するようにしてもよい。

10

## [0024]

この構成によれば、エラーアドレス格納手段を独立に備える必要がなく、外部デバイス アクセス装置をより小さくし、コストを削減する効果がある。

### [0025]

ここで、前記外部デバイスアクセス装置は、さらに、前記マスタからの書き込み要求に応じて、外部デバイスから読み出しデータ格納手段への読み出しを完了したか否かを示す格納動作状態信号を格納する格納動作状態保持手段を備え、前記制御部は、さらに、格納動作状態信号に基づいて、前記マスタから読み出しアドレス格納手段への書き込みを規制するようにしてもよい。

20

## [0026]

この構成によれば、さらに、マスタが外部デバイスの格納動作状態を認識し、マスタの アクセス要求順序を保持することで、マスタの性能に寄与する効果がある。

#### [0027]

また、本発明のシステムLSIは、上記と同様の手段を備える。

## 【発明の効果】

### [0028]

本発明によれば、メディア処理の高度化に伴ってマスタが高速化する場合、個々に動作速度の異なる外部デバイスへのアクセスにおいて、マスタの書き込み要求または読み出し要求時にマスタの状態に依存しないアクセスを実現し、外部デバイスへのアクセスペナルティを隠蔽してマスタの性能への影響を少なくできる効果がある。

30

## [0029]

さらに外部デバイスに応じて、外部デバイスアクセス装置の資源を調整することにより 外部デバイスへのアクセスの最適化が容易に実施できる効果がある。

## [0030]

またシステムLSIにおいては、マスタが外部デバイスへアクセスするために外部デバイスアクセス装置を備えることにより、システムLSIを開発する度にマスタの改変をする必要がなくなり外部デバイスアクセス装置の改変のみで済むため、システムLSIにおけるマスタの開発コストを大幅に低減する効果がある。

40

### [0031]

さらに外部デバイスの状態をマスタへ伝達する機能を実現し、マスタの性能に寄与する効果がある。

## [0032]

また外部デバイスアクセス装置をより小さくしてコストを削減し、マスタの性能に寄与する効果がある。

【発明を実施するための最良の形態】

### [0033]

以下、マスタとはCPUやマイコン等、書き込みまたは読み出しの制御を担当する装置のことを指し、外部デバイスとはそのCPUやマイコン等をアシストする、コプロセッサやアクセラレータ等の装置を指し、かつその装置はマスタがアドレス指定によりアクセス

可能な資源を有しているとし、実施例を示していく。

## [0034]

<第1の実施形態>

本発明の第1の実施形態の外部デバイスアクセス装置について、図面を参照しながら説明する。

## [0035]

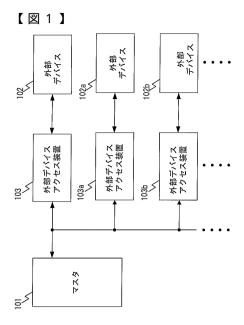

図1は、本発明の第1の実施形態におけるシステムLSIを示すブロック図である。このシステムLSIは、マスタ101と、外部デバイス102、102a、102b、・・・と、外部デバイスアクセス装置103、103a、103b、・・・を備える。この例では、外部デバイスアクセス装置は外部デバイスに対応して備えられる。外部デバイスアクセス装置103は、マスタ101の外部デバイス102への書き込み要求または読み出し要求を受けて、マスタ101の状態に依存しないアクセスを実現し、マスタ101に対して外部デバイスへのアクセスペナルティを隠蔽するように構成されている。外部デバイスアクセス装置103a、103b、・・・も同様である。

#### [0036]

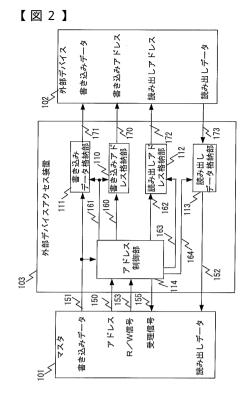

図 2 は本発明の第 1 の実施形態の外部デバイスアクセス装置 1 0 3 の構成を示すブロック図である。

### [0037]

はじめに外部デバイスアクセス装置103の構成について説明する。

## [0038]

外部デバイスアクセス装置103は、マスタ101との間でアドレスバス150、書き込みデータ入力バス151、読み出しデータ出力バス152、書き込み読み出し制御信号(以下、R/W信号と呼ぶ)バス153、受理信号155を介して接続され、また、外部デバイス102との間で、書き込みアドレス出力バス170、書き込みデータ出力バス171、読み出しアドレス出力バス172、読み出しデータ入力バス173を介して接続される。

### [0039]

また、外部デバイスアクセス装置103は、書き込みアドレス格納部110、書き込みデータ格納部111、読み出しアドレス格納部112、読み出しデータ格納部113、アドレス制御部114から構成される。

### [0040]

書き込みアドレス格納部110は、アドレス制御部114から書き込みアドレス160と書き込み許可信号161を入力し、格納したアドレスを外部デバイス102へ出力する

## [0041]

書き込みデータ格納部111は、マスタから、書き込みデータ入力バス151を介した書き込みデータと、アドレス制御部114から書き込み許可信号161とを入力し、格納したデータを外部デバイス102へ出力する。

### [0042]

読み出しアドレス格納部112は、アドレス制御部114から読み出しアドレス162と読み出しアドレス許可信号163とを入力し、格納したアドレスを外部デバイス102へ出力する。

## [0043]

読み出しデータ格納部113は、外部デバイスから読み出しデータ入力バス173を介した読み出しデータと、アドレス制御部からの読み出しデータ許可信号164を入力し、 格納したデータをマスタ101へ出力する。

### [0044]

また、読み出しデータ格納部113は、マスタ101が持つアクセス空間に割り当てられたアドレスを持つ。

## [0045]

10

20

30

40

アドレス制御部114は、マスタから、アドレスバス150を介したアドレスと、R/W信号バス153を介したR/W信号と、書き込みデータ入力バス151を介した書き込みデータとを入力し、書き込みアドレス160と、書き込み許可信号161とを書き込みアドレス格納部110へ出力し、書き込み許可信号161を書き込みデータ格納部111へ出力し、読み出しアドレス162と読み出しアドレス許可信号163とを読み出しアドレス格納部112へ出力し、読み出しデータ許可信号164を読み出しデータ格納部113へ出力する。

## [0046]

次に外部デバイスアクセス装置103の動作について説明する。

### [0047]

外部デバイスアクセス装置103の動作は、通常の書き込み動作、あらかじめ外部デバイス102のデータを読み出しデータ格納部113へ読み出しておく動作、あらかじめ読み出しデータ格納部113へ読み出しておいたデータをマスタ101へ出力する動作であり、順に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み出し動作とする。

## [0048]

通常書き込み動作は、マスタ101からの書き込み要求に応じて、外部デバイスアクセス装置103にアドレスバス150からのアドレスと、R/W信号バス153からのR/W信号がアドレス制御部114に入力される。

## [0049]

アドレス制御部 1 1 4 では、R / W信号と、アドレスバス 1 5 0 からのアドレスが読み出しデータ格納部 1 1 3 に割り当てられたアドレスではないことをもとに、通常書き込み動作であることを認識し、書き込みアドレス 1 6 0 と書き込み許可信号 1 6 1 とを書き込みアドレス格納部 1 1 0 に出力してアドレスを格納させ、書き込み許可信号 1 6 1 を書き込みデータ格納部 1 1 1 に出力して書き込みデータバス 1 5 1 からのデータを格納させる

### [0050]

格納したアドレスとデータは、外部デバイスが受け付けるまで保持し、受付を完了後に 通常書き込み動作を完了する。

## [0051]

プリフェッチ動作は、マスタ101からの書き込み要求に応じて、外部デバイスアクセス装置103にアドレスバス150からのアドレスと、R/W信号バス153からのR/W信号と、書き込みデータバス151からのデータがアドレス制御部114に入力される

## [0052]

アドレス制御部114では、R/W信号と、アドレスバス150からのアドレスが読み出しデータ格納部113に割り当てられたアドレスであることをもとに、プリフェッチ動作であることを認識し、書き込みデータバス151からのデータを読み出しアドレスとして、読み出しアドレス162と読み出しアドレス許可信号163とを読み出しアドレス格納部112に出力してアドレスを格納させる。

## [0053]

格納したアドレスは、外部デバイス102が受け付けて、外部デバイス102からの読み出しデータを読み出しデータ格納部113に格納するまで保持し、格納を完了後にプリフェッチ動作を完了する。

### [0054]

プリフェッチデータ読み出し動作は、マスタ101からの読み出し要求に応じて、外部デバイスアクセス装置103にアドレスバス150からのアドレスと、R/W信号バス153からのR/W信号とがアドレス制御部114に入力される。

## [0055]

アドレス制御部114では、R/W信号と、アドレスバス150からのアドレスが読み

10

20

30

40

10

20

30

40

50

出しデータ格納部113に割り当てられたアドレスであることをもとに、プリフェッチデータ読み出し動作であることを認識し、読み出しデータ許可信号164を読み出しデータ格納部113に出力して、読み出しデータバス152を介してマスタ101に出力する。

#### [0056]

マスタ101が読み出しデータを受け付けるまで読み出しデータを保持し、受付を完了後にプリフェッチリード動作を完了する。

### [0057]

これら動作を持つことによる利点としては、通常書き込み動作では、マスタ101からの書き込み要求を外部デバイスアクセス装置103が保持するため、外部デバイスの受付を待つことなくマスタ101は書き込みを完了させて動作することが可能となり、マスタ101に依存することなく、外部デバイス102への書き込みを行うことが可能となる。

### [0058]

プリフェッチ動作では、マスタ101からの書き込み要求を使用して、あらかじめ外部デバイス102のデータを読み出しデータ格納部113へ読み出しておく動作を実現するとともに、通常書き込み動作と同様に、マスタ101からの書き込み要求を外部デバイスアクセス装置103が読み出し要求として保持するため、外部デバイスの受付を待つことなくマスタ101は書き込みを完了させて動作することが可能となり、マスタ101に依存することなく、外部デバイス102からの読み出しを行うことが可能となる。

## [0059]

プリフェッチデータ読み出し動作では、マスタ101からの読み出し要求により、あらかじめ読み出しデータ格納部113へ読み出しておいたデータをマスタ101へ出力するため、外部デバイス102に依存することなく、データの読み出しを行うことが可能となる。

#### [0060]

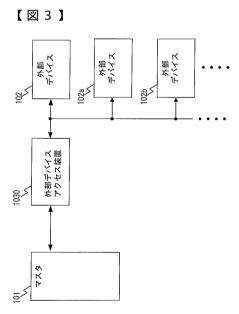

なお、図1のシステムLSIでは外部デバイスアクセス装置と外部デバイスとが1対1で対応しているが、1対多で対応するようにしてもよい。その場合のシステムLSIの構成例を図3に示す。図3の外部デバイスアクセス装置1030は、複数の外部デバイスのそれぞれのアクセスレイテンシに対応し、マスタ101に対して各外部デバイスへのアクセスペナルティを隠蔽するように構成されている。

## [0061]

<第2の実施形態>

本発明の第2の実施形態の外部デバイスアクセス装置について、図面を参照しながら説明する。

## [0062]

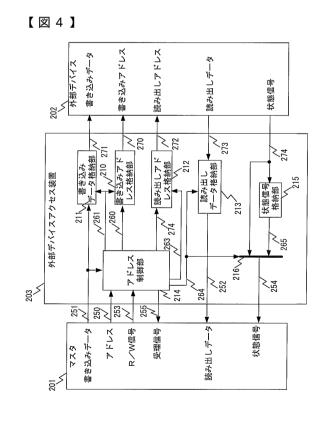

図4は本発明の第2の実施形態の外部デバイスアクセス装置構成図である。

### [0063]

はじめに外部デバイスアクセス装置203の構成について説明する。

## [0064]

外部デバイスアクセス装置 2 0 3 は、マスタ 2 0 1 との間でアドレスバス 2 5 0 、書き込みデータ入力バス 2 5 1、読み出しデータ出力バス 2 5 2、R / W信号入力バス 2 5 3、状態信号出力バス 2 5 4、受理信号 2 5 5 を介して接続され、また、外部デバイス 2 0 2 との間で書き込みアドレス出力バス 2 7 0、書き込みデータ出力バス 2 7 1、読み出しアドレス出力バス 2 7 2、読み出しデータ入力バス 2 7 3、状態信号入力バス 2 7 4を介して接続される。

### [0065]

また、外部デバイスアクセス装置 2 0 3 は、書き込みアドレス格納部 2 1 0 、書き込み データ格納部 2 1 1 、読み出しアドレス格納部 2 1 2 、読み出しデータ格納部 2 1 3 、ア ドレス制御部 2 1 4 、状態信号格納部 2 1 5 、セレクタ 2 1 6 から構成される。

### [0066]

書き込みアドレス格納部210は、アドレス制御部214から書き込みアドレス260

と書き込み許可信号261を入力し、格納したアドレスを外部デバイス202へ出力する

## [0067]

書き込みデータ格納部 2 1 1 は、マスタから、書き込みデータ入力バス 2 5 1 を介した書き込みデータと、アドレス制御部 2 1 4 から書き込み許可信号 2 6 1 とを入力し、格納したデータを外部デバイス 2 0 2 へ出力する。

### [0068]

読み出しアドレス格納部212は、アドレス制御部214から読み出しアドレス262と読み出しアドレス許可信号263とを入力し、格納したアドレスを外部デバイス202へ出力する。

## [0069]

読み出しデータ格納部213は、外部デバイスから読み出しデータ入力バス273を介した読み出しデータと、アドレス制御部214からの読み出しデータ許可信号264を入力し、格納したデータをマスタ201へ出力する。

### [0070]

また、読み出しデータ格納部 2 1 3 は、マスタ 2 0 1 が持つアクセス空間に割り当てられたアドレスを持つ。

### [0071]

アドレス制御部 2 1 4 は、マスタから、アドレスバス 2 5 0 を介したアドレスと、R / W信号バス 2 5 3 を介した R / W信号と、書き込みデータ入力バス 2 5 1 を介した書き込みデータとを入力し、書き込みアドレス 2 6 0 と、書き込み許可信号 2 6 1 とを書き込みアドレス格納部 2 1 0 へ出力し、書き込み許可信号 2 6 1 を書き込みデータ格納部 2 1 1 へ出力し、読み出しアドレス 2 6 2 と読み出しアドレス許可信号 2 6 3 とを読み出しアドレス格納部 2 1 2 へ出力し、読み出しデータ許可信号 2 6 4 を読み出しデータ格納部 2 1 3 へ出力する。

## [0072]

状態信号格納部 2 1 5 は、外部デバイスから状態信号入力バス 2 7 4 を介した状態信号を入力し、格納した信号をセレクタ 2 1 6 へ出力する。

## [0073]

セレクタ216は、状態信号入力バス274を介して入力される状態信号と、状態信号格納部215に格納されている状態信号を、読み出しデータ許可信号264で選択して、状態信号出力バス254を介してマスタ201へ出力する。

### [0074]

次に外部デバイスアクセス装置 2 0 3 の動作について説明する。第 1 の発明を実施する 形態での説明と同様に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み 出し動作である。

## [0075]

通常書き込み動作は、マスタ201からの書き込み要求に応じて、外部デバイスアクセス装置203にアドレスバス250からのアドレスと、R/W信号バス253からのR/W信号がアドレス制御部214に入力される。

## [0076]

アドレス制御部 2 1 4 では、R / W信号と、アドレスバス 2 5 0 からのアドレスが読み出しデータ格納部 2 1 3 に割り当てられたアドレスではないことをもとに、通常書き込み動作であることを認識し、書き込みアドレス 2 6 0 と書き込み許可信号 2 6 1 とを書き込みアドレス格納部 2 1 0 に出力してアドレスを格納させ、書き込み許可信号 2 6 1 を書き込みデータ格納部 2 1 1 に出力して書き込みデータバス 2 5 1 からのデータを格納させる

### [0077]

格納したアドレスとデータは、外部デバイス202が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。

10

20

30

40

### [0078]

また本動作時は、外部デバイス202の状態を状態信号として、セレクタ216で選択し、直接マスタ201へ出力する。

### [0079]

プリフェッチ動作は、マスタ201からの書き込み要求に応じて、外部デバイスアクセス装置203にアドレスバス250からのアドレスと、R / W信号バス253からのR / W信号と、書き込みデータバス251からのデータがアドレス制御部214に入力される

### [0800]

アドレス制御部 2 1 4 では、R / W信号と、アドレスバス 2 5 0 からのアドレスが読み出しデータ格納部 2 1 3 に割り当てられたアドレスであることをもとに、プリフェッチ動作であることを認識し、書き込みデータバス 2 5 1 からのデータを読み出しアドレスとして、読み出しアドレス 2 6 2 と読み出しアドレス許可信号 2 6 3 とを読み出しアドレス格納部 2 1 2 に出力してアドレスを格納させる。

### [0081]

格納したアドレスは、外部デバイスが受け付けて、外部デバイス202からの読み出しデータを読み出しデータ格納部213に格納するまで保持し、格納を完了後にプリフェッチ動作を完了する。

### [0082]

また本動作時は、外部デバイス202の状態を状態信号として、状態信号格納部215に格納する。

#### [0083]

プリフェッチデータ読み出し動作は、マスタ201からの読み出し要求に応じて、外部デバイスアクセス装置203にアドレスバス250からのアドレスと、R/W信号バス253からのR/W信号とがアドレス制御部214に入力される。

## [0084]

アドレス制御部 2 1 4 では、 R / W信号と、アドレスバス 2 5 0 からのアドレスが読み出しデータ格納部 2 1 3 に割り当てられたアドレスであることをもとに、プリフェッチデータ読み出し動作であることを認識し、読み出しデータ許可信号 2 6 4 を読み出しデータ格納部 2 1 3 に出力して、読み出しデータバス 2 5 2 を介してマスタ 2 0 1 に出力する。

### [0085]

また本動作時は、状態信号格納部 2 1 5 に格納された状態信号をセレクタ 2 1 6 で選択し、マスタ 2 0 1 に出力する。

### [0086]

これら動作を持つことによる利点としては、通常書き込み動作では、第1の発明を実施するための形態に記載の利点に加えて、外部デバイス202の状態をマスタ201に送ることが可能となる。

## [0087]

プリフェッチ動作では、第1の発明を実施するための形態に記載の利点に加えて、プリフェッチした時点の外部デバイス202の状態を、状態信号格納部215に格納し保持しておくことが可能となる。

### [0088]

プリフェッチデータ読み出し動作では、第1の発明を実施するための形態に記載の利点に加えて、状態信号格納部215に保持しているプリフェッチ動作を完了した時点の外部デバイス202の状態を、マスタ201に送ることが可能となる。

## [0089]

<第3の実施形態>

本発明の第3の実施形態の外部デバイスアクセス装置について、図面を参照しながら説明する。

## [0090]

10

20

30

40

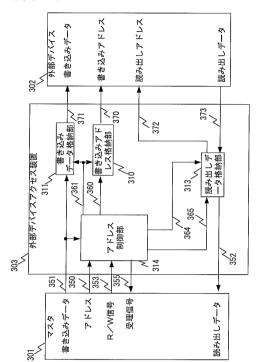

図5は本発明の第3の実施形態の外部デバイスアクセス装置構成図である。

## [0091]

はじめに外部デバイスアクセス装置303の構成について説明する。

## [0092]

外部デバイスアクセス装置303は、マスタ301との間でアドレスバス350、書き込みデータ入力バス351、読み出しデータ出力バス352、R/W信号入力バス353、受理信号355を介して接続され、また、外部デバイス302との間で書き込みアドレス出力バス370、書き込みデータ出力バス371、読み出しアドレス出力バス372、読み出しデータ入力バス373を介して接続される。

## [0093]

また、外部デバイスアクセス装置303は、書き込みアドレス格納部310、書き込み データ格納部311、読み出しデータ格納部313、アドレス制御部314から構成され る。

## [0094]

書き込みアドレス格納部310は、アドレス制御部314から書き込みアドレス360と書き込み許可信号361を入力し、格納したアドレスを外部デバイス302へ出力する

#### [0095]

書き込みデータ格納部311は、マスタから、書き込みデータ入力バス351を介した書き込みデータと、アドレス制御部314から書き込み許可信号361とを入力し、格納したデータを外部デバイス302へ出力する。

#### [0096]

読み出しデータ格納部313は、読み出しアドレス362と読み出しアドレス許可信号363とを入力し、格納したアドレスを外部デバイス302へ出力する。その読み出しアドレスより外部デバイスから読み出しデータ入力バス373を介した読み出しデータと、アドレス制御部からの読み出しデータ格納部制御364を入力し、格納したデータをマスタ301へ出力する。

## [0097]

また、読み出しデータ格納部 3 1 3 は、マスタ 3 0 1 が持つアクセス空間に割り当てられたアドレスを持つ。

## [0098]

アドレス制御部 3 1 4 は、マスタから、アドレスバス 3 5 0 を介したアドレスと、R / W信号バス 3 5 3 を介した R / W信号と、書き込みデータ入力バス 3 5 1 を介した書き込みデータとを入力し、書き込みアドレス 3 6 0 と、書き込み許可信号 3 6 1 とを書き込みアドレス格納部 3 1 0 へ出力し、書き込み許可信号 3 6 1 を書き込みデータ格納部 3 1 1 へ出力し、読み出しアドレス 3 6 5 と、読み出しデータ格納部制御 3 6 4 を読み出しデータ格納部 3 1 3 へ出力する。

## [0099]

次に外部デバイスアクセス装置303の動作について説明する。第1の発明を実施する 形態での説明と同様に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み 出し動作である。

### [0100]

通常書き込み動作は、マスタ301からの書き込み要求に応じて、外部デバイスアクセス装置303にアドレスバス350からのアドレスと、R/W信号バス353からのR/W信号がアドレス制御部314に入力される。

## [0101]

アドレス制御部 3 1 4 では、 R / W信号と、アドレスバス 3 5 0 からのアドレスが読み出しデータ格納部 3 1 3 に割り当てられたアドレスではないことをもとに、通常書き込み動作であることを認識し、書き込みアドレス 3 6 0 と書き込み許可信号 3 6 1 とを書き込みアドレス格納部 3 1 0 に出力してアドレスを格納させ、書き込み許可信号 3 6 1 を書き

10

20

30

40

込みデータ格納部311に出力して書き込みデータバス351からのデータを格納させる

## [0102]

格納したアドレスとデータは、外部デバイス302が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。

### [0103]

プリフェッチ動作は、マスタ301からの書き込み要求に応じて、外部デバイスアクセス装置303にアドレスバス350からのアドレスと、R / W信号バス353からのR / W信号と、書き込みデータバス351からのデータがアドレス制御部314に入力される

[0104]

アドレス制御部314では、R/W信号と、アドレスバス350からのアドレスが読み出しデータ格納部313に割り当てられたアドレスであることをもとに、プリフェッチ動作であることを認識し、書き込みデータバス351からのデータを読み出しアドレスとして、読み出しアドレス365と読み出しデータ格納部制御364とを読み出しデータ格納部313に出力してアドレスを格納させる。格納したアドレスは、外部デバイスが受け付けて、外部デバイス302からの読み出しデータを読み出しデータ格納部313に格納するまで保持し、格納を完了後にプリフェッチ動作を完了する。

[ 0 1 0 5 ]

プリフェッチデータ読み出し動作は、マスタ301からの読み出し要求に応じて、外部デバイスアクセス装置303にアドレスバス350からのアドレスと、R/W信号バス353からのR/W信号とがアドレス制御部314に入力される。

[0106]

アドレス制御部 3 1 4 では、 R / W信号と、アドレスバス 3 5 0 からのアドレスが読み出しデータ格納部 3 1 3 に割り当てられたアドレスであることをもとに、プリフェッチデータ読み出し動作であることを認識し、読み出しデータ格納部制御 3 6 4 を読み出しデータ格納部 3 1 3 に出力して、読み出しデータバス 3 5 2 を介してマスタ 3 0 1 に出力する

[0107]

マスタ301が読み出しデータを受け付けるまで読み出しデータを保持し、受付を完了 後にプリフェッチリード動作を完了する。

[0108]

これら動作を持つことによる利点としては、プリフェッチ動作では、第1の発明を実施するための形態及び第2の発明を実施するための形態に記載の利点に加えて、読み出しデータ格納部制御364を設けることにより、読み出しデータ格納部313のみでプリフェッチ動作を実現できるため、外部デバイスアクセス装置の面積増加を抑制することが可能となる。

[0109]

<第4の実施形態>

本発明の第4の実施形態の外部デバイスアクセス装置について、図面を参照しながら説 40 明する。

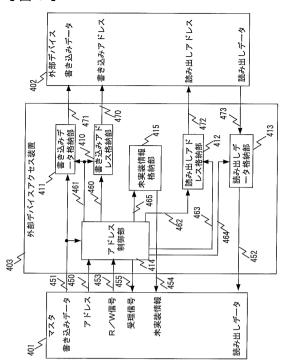

[0110]

図6は本発明の第4の実施形態の外部デバイスアクセス装置構成図である。

[0111]

はじめに外部デバイスアクセス装置403の構成について説明する。

[0112]

外部デバイスアクセス装置403は、マスタ401との間でアドレスバス450、書き込みデータ入力バス451、読み出しデータ出力バス452、R/W信号入力バス453、未実装情報バス454、受理信号455を介して接続され、また、外部デバイス402と、書き込みアドレス出力バス470、書き込みデータ出力バス471、読み出しアドレ

10

20

30

ス出力バス472、読み出しデータ入力バス473を介して接続される。

## [0113]

また、外部デバイスアクセス装置403は、書き込みアドレス格納部410、書き込み データ格納部411、読み出しアドレス格納部412、読み出しデータ格納部413、ア ドレス制御部414、未実装情報格納部415から構成される。

### [0114]

書き込みアドレス格納部410は、アドレス制御部414から書き込みアドレス460と書き込み許可信号461を入力し、格納したアドレスを外部デバイス402へ出力する

## [0115]

書き込みデータ格納部411は、マスタから、書き込みデータ入力バス451を介した書き込みデータと、アドレス制御部414から書き込み許可信号461とを入力し、格納したデータを外部デバイス402へ出力する。

## [0116]

読み出しアドレス格納部412は、アドレス制御部414から読み出しアドレス462と読み出しアドレス許可信号463とを入力し、格納したアドレスを外部デバイス402 へ出力する。

## [0117]

読み出しデータ格納部413は、外部デバイスから読み出しデータ入力バス473を介した読み出しデータと、アドレス制御部からの読み出しデータ許可信号464を入力し、 格納したデータをマスタ401へ出力する。

#### [0118]

また、読み出しデータ格納部413は、マスタ401が持つアクセス空間に割り当てられたアドレスを持つ。

### [0119]

アドレス制御部414は、マスタから、アドレスバス450を介したアドレスと、R/W信号バス453を介したR/W信号と、書き込みデータ入力バス451を介した書き込みデータとを入力し、書き込みアドレス460と、書き込み許可信号461とを書き込みアドレス格納部410へ出力し、書き込み許可信号461を書き込みデータ格納部411へ出力し、読み出しアドレス162と読み出しアドレス許可信号463とを読み出しアドレス格納部412へ出力し、読み出しデータ許可信号464を読み出しデータ格納部413へ出力し、未実装情報465を未実装情報格納部415へ出力する。

### [0120]

未実装情報格納部415は、アドレス制御部414から未実装情報465を入力し、マスタ401へ未実装情報バス454を介して、格納した未実装情報を出力する。

## [0121]

次に外部デバイスアクセス装置 4 0 3 の動作について説明する。第 1 の発明を実施する 形態での説明と同様に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み 出し動作である。

## [0122]

通常書き込み動作は、マスタ401からの書き込み要求に応じて、外部デバイスアクセス装置403にアドレスバス450からのアドレスと、R/W信号バス453からのR/W信号がアドレス制御部414に入力される。

## [0123]

アドレス制御部414では、R/W信号と、アドレスバス450からのアドレスが読み出しデータ格納部413に割り当てられたアドレスではない場合には、通常書き込み動作であることを認識し、書き込みアドレス460と書き込み許可信号461とを書き込みアドレス格納部410に出力してアドレスを格納させ、書き込み許可信号461を書き込みデータ格納部411に出力して書き込みデータバス451からのデータを格納させる。アドレスバス450からのアドレスが実装されていないアドレスの場合には、未実装である

10

20

30

40

ことを認識し、未実装情報465を未実装情報格納部415に格納する。

#### [0124]

アドレスとデータを格納した場合は、外部デバイス402が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。未実装情報を格納した場合は、マスタ401が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。

### [0125]

プリフェッチ動作は、マスタ401からの書き込み要求に応じて、外部デバイスアクセス装置403にアドレスバス450からのアドレスと、R / W信号バス453からのR / W信号と、書き込みデータバス451からのデータがアドレス制御部414に入力される

## [0126]

アドレス制御部414では、R/W信号と、アドレスバス450からのアドレスが読み出しデータ格納部413に割り当てられたアドレスである場合は、プリフェッチ動作であることを認識し、書き込みデータバス451からのデータを読み出しアドレスとして、読み出しアドレス462と読み出しアドレス許可信号463とを読み出しアドレス格納部412に出力してアドレスを格納させる。アドレスバス450からのアドレスが実装されていないアドレスの場合、または書き込みデータバス451からのデータをアドレスとしたときのアドレスが実装されていないアドレスの場合は、未実装であることを認識し、未実装情報465を未実装情報格納部415に格納する。

## [0127]

アドレスを格納した場合は、外部デバイスが受け付けて、外部デバイス402からの読み出しデータを読み出しデータ格納部413に格納するまで保持し、格納を完了後にプリフェッチ動作を完了する。未実装情報を格納した場合は、マスタ401が受け付けるまで保持し、受付を完了後にプリフェッチ動作を完了する。

### [0128]

プリフェッチデータ読み出し動作は、マスタ401からの読み出し要求に応じて、外部デバイスアクセス装置403にアドレスバス450からのアドレスと、R/W信号バス453からのR/W信号とがアドレス制御部414に入力される。

## [0129]

アドレス制御部414では、R/W信号と、アドレスバス450からのアドレスが読み出しデータ格納部413に割り当てられたアドレスである場合は、プリフェッチデータ読み出し動作であることを認識し、読み出しデータ許可信号464を読み出しデータ格納部413に出力して、読み出しデータバス452を介してマスタ401に出力する。アドレスバス450からのアドレスが実装されていないアドレスの場合は、未実装であることを認識し、未実装情報465を未実装情報格納部415に格納する。

### [0130]

アドレスを格納した場合は、マスタ401が読み出しデータを受け付けるまで読み出しデータを保持し、受付を完了後にプリフェッチリード動作を完了する。未実装情報を格納した場合は、マスタ401が受け付けるまで保持し、受付を完了後にプリフェッチ動作を完了する。

## [0131]

これら動作を持つことによる利点としては、通常書き込み動作では、第1の発明を実施するための形態に記載の利点に加えて、マスタ401からのアドレス指定に対して、実装されているかどうかを判定し未実装情報として送ることで、マスタ401に依存することなく、外部デバイス402に対する実装、未実装を容易に設定することが可能となる。

## [0132]

プリフェッチ動作では、第1の発明を実施するための形態に記載の利点に加えて、マスタ401からのアドレス指定、データに対して、実装されているかどうかを判定し未実装情報として送ることで、マスタ401に依存することなく、外部デバイス402、読み出しデータ格納部413に割り当てるアドレスに対する実装、未実装を容易に設定すること

10

20

30

40

が可能となる。

## [0133]

プリフェッチデータ読み出し動作では、第1の発明を実施するための形態に記載の利点に加えて、マスタ401からのアドレス指定に対して、実装されているかどうかを判定し未実装情報として送ることで、マスタ401に依存することなく、読み出しデータ格納部413に割り当てるアドレスに対する実装、未実装を容易に設定することが可能となる。

#### [ 0 1 3 4 ]

<第5の実施形態>

本発明の第5の実施形態の外部デバイスアクセス装置について、図面を参照しながら説明する。

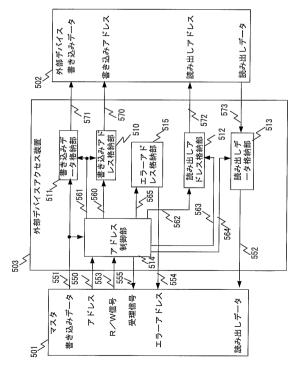

[0135]

図7は本発明の第5の実施形態の外部デバイスアクセス装置構成図である。

[0136]

はじめに外部デバイスアクセス装置503の構成について説明する。

[0137]

外部デバイスアクセス装置 5 0 3 は、マスタ 5 0 1 との間でアドレスバス 5 5 0 、書き込みデータ入力バス 5 5 1、読み出しデータ出力バス 5 5 2、 R / W信号入力バス 5 5 3 、エラーアドレスバス 5 5 4、受理信号 5 5 5 を介して接続され、また、外部デバイス 5 0 2 との間で、書き込みアドレス出力バス 5 7 0、書き込みデータ出力バス 5 7 1、読み出しアドレス出力バス 5 7 2、読み出しデータ入力バス 5 7 3 を介して接続される。

[0138]

また、外部デバイスアクセス装置 5 0 3 は、書き込みアドレス格納部 5 1 0 、書き込み データ格納部 5 1 1 、読み出しアドレス格納部 5 1 2 、読み出しデータ格納部 5 1 3 、ア ドレス制御部 5 1 4 、エラーアドレス格納部 5 1 5 から構成される。

[0139]

書き込みアドレス格納部510は、アドレス制御部514から書き込みアドレス560と書き込み許可信号561を入力し、格納したアドレスを外部デバイス502へ出力する

[0140]

書き込みデータ格納部 5 1 1 は、マスタから、書き込みデータ入力バス 5 5 1 を介した書き込みデータと、アドレス制御部 5 1 4 から書き込み許可信号 5 6 1 とを入力し、格納したデータを外部デバイス 5 0 2 へ出力する。

[0141]

読み出しアドレス格納部512は、アドレス制御部514から読み出しアドレス562と読み出しアドレス許可信号563とを入力し、格納したアドレスを外部デバイス502 へ出力する。

[0142]

読み出しデータ格納部513は、外部デバイスから読み出しデータ入力バス573を介した読み出しデータと、アドレス制御部からの読み出しデータ許可信号564を入力し、格納したデータをマスタ501へ出力する。

[0143]

また、読み出しデータ格納部 5 1 3 は、マスタ 5 0 1 が持つアクセス空間に割り当てられたアドレスを持つ。

[0144]

アドレス制御部 5 1 4 は、マスタから、アドレスバス 5 5 0 を介したアドレスと、R / W信号バス 5 5 3 を介した R / W信号と、書き込みデータ入力バス 5 5 1 を介した書き込みデータとを入力し、書き込みアドレス 5 6 0 と、書き込み許可信号 5 6 1 とを書き込みアドレス格納部 5 1 0 へ出力し、書き込み許可信号 5 6 1 を書き込みデータ格納部 5 1 1 へ出力し、読み出しアドレス 5 6 2 と読み出しアドレス許可信号 5 6 3 とを読み出しアドレス格納部 5 1 2 へ出力し、読み出しデータ許可信号 5 6 4 を読み出しデータ格納部 5 1

10

20

40

30

3 へ出力し、エラーアドレス 5 6 5 をエラーアドレス格納部 5 1 5 へ出力する。

## [0145]

エラーアドレス格納部 5 1 5 は、アドレス制御部 5 1 4 からエラーアドレス 5 6 5 を入力し、マスタ 5 0 1 ヘエラーアドレスバス 5 5 4 を介して、格納したエラーアドレスを出力する。

## [0146]

次に外部デバイスアクセス装置 5 0 3 の動作について説明する。第 1 の発明を実施する 形態での説明と同様に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み 出し動作である。

## [0147]

通常書き込み動作は、マスタ501からの書き込み要求に応じて、外部デバイスアクセス装置503にアドレスバス550からのアドレスと、R/W信号バス553からのR/W信号がアドレス制御部514に入力される。

### [0148]

アドレス制御部 5 1 4 では、R / W信号と、アドレスバス 5 5 0 からのアドレスが読み出しデータ格納部 5 1 3 に割り当てられたアドレスではない場合には、通常書き込み動作であることを認識し、書き込みアドレス 5 6 0 と書き込み許可信号 5 6 1 とを書き込みアドレス格納部 5 1 0 に出力してアドレスを格納させ、書き込み許可信号 5 6 1 を書き込みデータ格納部 5 1 1 に出力して書き込みデータバス 5 5 1 からのデータを格納させる。アドレスバス 5 5 0 からのアドレスが実装されていないアドレスの場合には、未実装であることを認識し、そのアドレスをエラーアドレス 5 6 5 としてエラーアドレス格納部 5 1 5 に格納する。

## [0149]

アドレスとデータを格納した場合は、外部デバイス 5 0 2 が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。エラーアドレスを格納した場合は、マスタ 5 0 1 が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。

### [0150]

プリフェッチ動作は、マスタ501からの書き込み要求に応じて、外部デバイスアクセス装置503にアドレスバス550からのアドレスと、R/W信号バス553からのR/W信号と、書き込みデータバス551からのデータがアドレス制御部514に入力される

## [0151]

アドレス制御部 5 1 4 では、R / W信号と、アドレスバス 5 5 0 からのアドレスが読み出しデータ格納部 5 1 3 に割り当てられたアドレスである場合は、プリフェッチ動作であることを認識し、書き込みデータバス 5 5 1 からのデータを読み出しアドレスとして、読み出しアドレス 5 6 2 と読み出しアドレス許可信号 5 6 3 とを読み出しアドレス格納部 5 1 2 に出力してアドレスを格納させる。アドレスバス 5 5 0 からのアドレスが実装されていないアドレスの場合、または書き込みデータバス 5 5 1 からのデータをアドレスとしたときのアドレスが実装されていないアドレスの場合は、未実装であることを認識し、そのアドレスをエラーアドレス 5 6 5 としてエラーアドレス格納部 5 1 5 に格納する。

## [0152]

アドレスを格納した場合は、外部デバイスが受け付けて、外部デバイス502からの読み出しデータを読み出しデータ格納部513に格納するまで保持し、格納を完了後にプリフェッチ動作を完了する。エラーアドレスを格納した場合は、マスタ501が受け付けるまで保持し、受付を完了後にプリフェッチ動作を完了する。

## [0153]

プリフェッチデータ読み出し動作は、マスタ 5 0 1 からの読み出し要求に応じて、外部デバイスアクセス装置 5 0 3 にアドレスバス 5 5 0 からのアドレスと、 R / W信号バス 5 5 3 からの R / W信号とがアドレス制御部 5 1 4 に入力される。

## [0154]

50

10

20

30

アドレス制御部 5 1 4 では、R / W信号と、アドレスバス 5 5 0 からのアドレスが読み出しデータ格納部 5 1 3 に割り当てられたアドレスである場合は、プリフェッチデータ読み出し動作であることを認識し、読み出しデータ許可信号 5 6 4 を読み出しデータ格納部 5 1 3 に出力して、読み出しデータバス 5 5 2 を介してマスタ 5 0 1 に出力する。アドレスバス 5 5 0 からのアドレスが実装されていないアドレスの場合は、未実装であることを認識し、そのアドレスをエラーアドレス 5 6 5 としてエラーアドレス格納部 5 1 5 に格納する。

## [0155]

アドレスを格納した場合は、マスタ 5 0 1 が読み出しデータを受け付けるまで読み出しデータを保持し、受付を完了後にプリフェッチリード動作を完了する。エラーアドレスを格納した場合は、マスタ 5 0 1 が受け付けるまで保持し、受付を完了後にプリフェッチ動作を完了する。

[0156]

これら動作を持つことによる利点としては、通常書き込み動作では、第1の発明を実施するための形態に記載の利点に加えて、マスタ501からのアドレス指定に対して、実装されているかどうかを判定しエラーアドレスとして送ることで、マスタ501は容易にエラーアドレスを知ることが可能となり、例えばデバッグ時などに有効となる。

[ 0 1 5 7 ]

プリフェッチ動作では、第1の発明を実施するための形態に記載の利点に加えて、マスタ501からのアドレス指定、データに対して、実装されているかどうかを判定しエラーアドレスとして送ることで、マスタ501は容易にエラーアドレスを知ることが可能となり、例えばデバッグ時などに有効となる。

[0158]

プリフェッチデータ読み出し動作では、第1の発明を実施するための形態に記載の利点に加えて、マスタ501からのアドレス指定に対して、実装されているかどうかを判定しエラーアドレスとして送ることで、マスタ501は容易にエラーアドレスを知ることが可能となり、例えばデバッグ時などに有効となる。

[0159]

<第6の実施形態>

本発明の第 6 の実施形態の外部デバイスアクセス装置について、図面を参照しながら説明する。

[0160]

図8は本発明の第6の実施形態の外部デバイスアクセス装置構成図である。

[0161]

はじめに外部デバイスアクセス装置603の構成について説明する。

[0162]

外部デバイスアクセス装置603は、マスタ601と、アドレスバス650、書き込みデータ入力バス651、読み出しデータ出力バス652、R/W信号入力バス653、エラーアドレスバス654を介して接続し、外部デバイス602と、書き込みアドレス出力バス670、書き込みデータ出力バス671、読み出しアドレス出力バス672、読み出しデータ入力バス673を介して接続される。

[0163]

また、外部デバイスアクセス装置603は、書き込みアドレス格納部610、書き込みデータ格納部611、読み出しアドレス格納部612、読み出しデータ格納部613、アドレス制御部614から構成される。

[0164]

書き込みアドレス格納部610は、アドレス制御部614から書き込みアドレス660と書き込み許可信号661を入力し、格納したアドレスを外部デバイス602へ出力する

50

10

20

30

40

[0165]

書き込みデータ格納部611は、マスタから、書き込みデータ入力バス651を介した書き込みデータと、アドレス制御部614から書き込み許可信号661とを入力し、格納したデータを外部デバイス602へ出力する。

### [0166]

読み出しアドレス格納部612は、アドレス制御部614から読み出しアドレス662と読み出しアドレス許可信号663とを入力し、格納したアドレスを外部デバイス602へ出力する。

## [0167]

読み出しデータ格納部613は、外部デバイスから読み出しデータ入力バス673を介した読み出しデータと、アドレス制御部からの読み出しデータ格納部制御664と、エラーアドレス665とを入力し、格納したデータまたはエラーアドレスをマスタ601へ出力する。

### [0168]

また、読み出しデータ格納部 6 1 3 は、マスタ 6 0 1 が持つアクセス空間に割り当てられたアドレスを持つ。

#### [0169]

アドレス制御部614は、マスタから、アドレスバス650を介したアドレスと、R/W信号バス653を介したR/W信号と、書き込みデータ入力バス651を介した書き込みデータとを入力し、書き込みアドレス660と、書き込み許可信号661とを書き込みアドレス格納部610へ出力し、書き込み許可信号661を書き込みデータ格納部611へ出力し、読み出しアドレス662と読み出しアドレス許可信号663とを読み出しアドレス格納部612へ出力し、読み出しデータ格納部制御664を読み出しデータ格納部613へ出力する。

#### [ 0 1 7 0 ]

次に外部デバイスアクセス装置 6 0 3 の動作について説明する。第 1 の発明を実施する 形態での説明と同様に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み 出し動作である。

## [0171]

通常書き込み動作は、マスタ601からの書き込み要求に応じて、外部デバイスアクセス装置603にアドレスバス650からのアドレスと、R/W信号バス653からのR/W信号がアドレス制御部614に入力される。

## [0172]

アドレス制御部614では、R/W信号と、アドレスバス650からのアドレスが読み出しデータ格納部613に割り当てられたアドレスではない場合には、通常書き込み動作であることを認識し、書き込みアドレス660と書き込み許可信号661とを書き込みアドレス格納部610に出力してアドレスを格納させ、書き込み許可信号661を書き込みデータ格納部611に出力して書き込みデータバス651からのデータを格納させる。アドレスバス650からのアドレスが実装されていないアドレスの場合には、未実装であることを認識し、そのアドレスを読み出しデータ格納部613に格納する。

## [0173]

アドレスとデータを格納した場合は、外部デバイス602が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。エラーアドレスを格納した場合は、マスタ601が受け付けるまで保持し、受付を完了後に通常書き込み動作を完了する。

## [0174]

プリフェッチ動作は、マスタ601からの書き込み要求に応じて、外部デバイスアクセス装置603にアドレスバス650からのアドレスと、R / W信号バス653からのR / W信号と、書き込みデータバス651からのデータがアドレス制御部614に入力される

## [0175]

アドレス制御部 6 1 4 では、 R / W信号と、アドレスバス 6 5 0 からのアドレスが読み

20

10

30

40

出しデータ格納部613に割り当てられたアドレスである場合は、プリフェッチ動作であることを認識し、書き込みデータバス651からのデータを読み出しアドレスとして、読み出しアドレス662と読み出しアドレス許可信号663とを読み出しアドレス格納部612に出力してアドレスを格納させる。アドレスバス650からのアドレスが実装されていないアドレスの場合、または書き込みデータバス651からのデータをアドレスとしたときのアドレスが実装されていないアドレスの場合は、未実装であることを認識し、そのアドレスをエラーアドレスとして読み出しデータ格納部613に格納する。

## [0176]

アドレスを格納した場合は、外部デバイスが受け付けて、外部デバイス602からの読み出しデータを読み出しデータ格納部613に格納するまで保持し、格納を完了後にプリフェッチ動作を完了する。エラーアドレスを格納した場合は、マスタ601が受け付けるまで保持し、受付を完了後にプリフェッチ動作を完了する。

[0177]

プリフェッチデータ読み出し動作は、マスタ601からの読み出し要求に応じて、外部デバイスアクセス装置603にアドレスバス650からのアドレスと、R/W信号バス653からのR/W信号とがアドレス制御部614に入力される。

[0178]

アドレス制御部 6 1 4 では、 R / W信号と、アドレスバス 6 5 0 からのアドレスが読み出しデータ格納部 6 1 3 に割り当てられたアドレスである場合は、プリフェッチデータ読み出し動作であることを認識し、読み出しデータ許可信号 6 6 4 を読み出しデータ格納部 6 1 3 に出力して、読み出しデータバス 6 5 2 を介してマスタ 6 0 1 に出力する。

[0179]

アドレスを格納した場合は、マスタ601が読み出しデータを受け付けるまで読み出しデータを保持し、受付を完了後にプリフェッチリード動作を完了する。エラーアドレスを格納した場合は、マスタ601が受け付けるまで保持し、受付を完了後にプリフェッチ動作を完了する。

[0180]

これら動作を持つことによる利点としては、通常書き込み動作では、第1の発明を実施するための形態及び第5の発明を実施するための形態に記載の利点に加えて、読み出しデータ格納部613のみでマスタ601にエラーアドレスを送ることを実現できるため、外部デバイスアクセス装置の面積増加を抑制することが可能となる。

[0181]

プリフェッチ動作では、第1の発明を実施するための形態及び第5の発明を実施するための形態に記載の利点に加えて、読み出しデータ格納部613のみでマスタ601にエラーアドレスを送ることを実現できるため、外部デバイスアクセス装置の面積増加を抑制することが可能となる。

[0182]

プリフェッチデータ読み出し動作では、第1の発明を実施するための形態及び第5の発明を実施するための形態に記載の利点に加えて、読み出しデータ格納部613のみでマスタ601にエラーアドレスを送ることを実現できるため、外部デバイスアクセス装置の面積増加を抑制することが可能となる。

[0183]

<第7の実施形態>

本発明の第7の実施形態の外部デバイスアクセス装置について、図面を参照しながら説明する。

[0184]

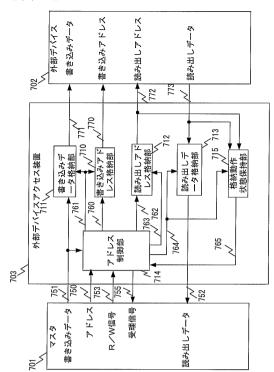

図9は本発明の第7の実施形態の外部デバイスアクセス装置構成図である。

【0185】

はじめに外部デバイスアクセス装置703の構成について説明する。

[0186]

20

10

30

40

外部デバイスアクセス装置703は、マスタ701と、アドレスバス750、書き込みデータ入力バス751、読み出しデータ出力バス752、R/W信号入力バス753を介して接続し、外部デバイス702と、書き込みアドレス出力バス770、書き込みデータ出力バス771、読み出しアドレス出力バス772、読み出しデータ入力バス773を介して接続される。

### [0187]

また、外部デバイスアクセス装置703は、書き込みアドレス格納部710、書き込みデータ格納部711、読み出しアドレス格納部712、読み出しデータ格納部713、アドレス制御部714、格納動作状態保持部715から構成される。

## [0188]

書き込みアドレス格納部710は、アドレス制御部714から書き込みアドレス760と書き込み許可信号761を入力し、格納したアドレスを外部デバイス702へ出力する

## [0189]

書き込みデータ格納部711は、マスタから、書き込みデータ入力バス751を介した書き込みデータと、アドレス制御部714から書き込み許可信号761とを入力し、格納したデータを外部デバイス702へ出力する。

## [0190]

読み出しアドレス格納部 7 1 2 は、アドレス制御部 7 1 4 から読み出しアドレス 7 6 2 と読み出しアドレス許可信号 7 6 3 とを入力し、格納したアドレスを外部デバイス 7 0 2 へ出力する。

### [0191]

読み出しデータ格納部713は、外部デバイスから読み出しデータ入力バス773を介した読み出しデータと、アドレス制御部からの読み出しデータ許可信号764を入力し、格納したデータをマスタ701へ出力する。

## [0192]

また、読み出しデータ格納部713は、マスタ701が持つアクセス空間に割り当てられたアドレスを持つ。

## [0193]

アドレス制御部714は、マスタから、アドレスバス750を介したアドレスと、R/W信号バス753を介したR/W信号と、書き込みデータ入力バス751を介した書き込みデータとを入力し、書き込みアドレス760と、書き込み許可信号761とを書き込みアドレス格納部710へ出力し、書き込み許可信号761を書き込みデータ格納部711へ出力し、読み出しアドレス762と読み出しアドレス許可信号763とを読み出しアドレス格納部712へ出力し、読み出しデータ許可信号764を読み出しデータ格納部713と格納動作状態保持部715へ出力する。

## [0194]

格納動作保持部保持部715は、外部デバイスから読み出しデータ入力バス773を介した読み出しデータと、読み出しアドレス格納部712からのアドレスと、アドレス制御部714から読み出しデータ許可信号764を入力し、アドレス制御部714へ格納動作状態765を出力する。

### [0195]

次に外部デバイスアクセス装置 7 0 3 の動作について説明する。第 1 の発明を実施する 形態での説明と同様に、通常書き込み動作、プリフェッチ動作、プリフェッチデータ読み 出し動作である。

## [0196]

通常書き込み動作は、マスタ701からの書き込み要求に応じて、外部デバイスアクセス装置703にアドレスバス750からのアドレスと、R/W信号バス753からのR/W信号がアドレス制御部714に入力される。

## [0197]

50

10

20

30

アドレス制御部 7 1 4 では、R / W信号と、アドレスバス 7 5 0 からのアドレスが読み出しデータ格納部 7 1 3 に割り当てられたアドレスではないことをもとに、通常書き込み動作であることを認識し、書き込みアドレス 7 6 0 と書き込み許可信号 7 6 1 とを書き込みアドレス格納部 7 1 0 に出力してアドレスを格納させ、書き込み許可信号 7 6 1 を書き込みデータ格納部 7 1 1 に出力して書き込みデータバス 7 5 1 からのデータを格納させる

[0198]

格納したアドレスとデータは、外部デバイスが受け付けるまで保持し、受付を完了後に 通常書き込み動作を完了する。

[0199]

プリフェッチ動作は、マスタ701からの書き込み要求に応じて、外部デバイスアクセス装置703にアドレスバス750からのアドレスと、R/W信号バス753からのR/W信号と、書き込みデータバス751からのデータがアドレス制御部714に入力される

[0200]

アドレス制御部714では、R/W信号と、アドレスバス750からのアドレスが読み出しデータ格納部713に割り当てられたアドレスであることをもとに、プリフェッチ動作であることを認識し、書き込みデータバス751からのデータを読み出しアドレスとして、読み出しアドレス762と読み出しアドレス許可信号763とを読み出しアドレス格納部712に出力してアドレスを格納させる。

[0201]

格納したアドレスは、外部デバイス702に出力するとともに、格納動作中であることを示すために格納動作状態保持部715へも出力し、格納動作中であることを保持させる。出力したアドレスは外部デバイス702が受け付けて、外部デバイス702からの読み出しデータを読み出しデータ格納部713に格納するまで保持し、格納を完了後に、格納動作状態保持部715保持させていた格納動作中であることを取り消し、プリフェッチ動作を完了する。

[0202]

プリフェッチデータ読み出し動作は、マスタ701からの読み出し要求に応じて、外部デバイスアクセス装置703にアドレスバス750からのアドレスと、R/W信号バス753からのR/W信号とがアドレス制御部714に入力される。

[0203]

アドレス制御部714では、R/W信号と、アドレスバス750からのアドレスが読み出しデータ格納部713に割り当てられたアドレスであることと、格納動作状態保持部715からの格納動作状態765をもとに、プリフェッチデータ読み出し動作であること、かつ以前にマスタ701が要求したプリフェッチ動作中でないことを認識した場合は、読み出しデータ許可信号764を読み出しデータ格納部713に出力して、読み出しデータバス752を介してマスタ701に出力する。

[0204]

マスタ 7 0 1 が読み出しデータを受け付けるまで読み出しデータを保持し、受付を完了 '後にプリフェッチリード動作を完了する。

[0205]

プリフェッチデータ読み出し動作であること、かつ以前にマスタ701が要求したプリフェッチ動作中である場合には、外部デバイスアクセス装置703はマスタ701からのプリフェッチデータ読み出し動作を受け付けず、マスタ701を待機させる。

[0206]

これら動作を持つことによる利点としては、プリフェッチデータ読み出し動作では、第1の発明を実施するための形態に記載の利点に加えて、以前にマスタ 7 0 1 が要求したプリフェッチ動作中である場合には、プリフェッチデータ読み出し動作を受け付けないため、あらかじめ外部デバイス 7 0 2 のデータを読み出しデータ格納部 7 1 3 へ読み出してお

10

20

30

40

く前のデータを読み出すことを防ぎ、マスタ701の要求する命令順序のとおりに動作することを保障することが可能となる。

## [0207]

なお、本発明の構成は上記に詳述された構成に限定されない。例えば、第2の実施形態から第7の実施形態において、図1のように1つのマスタに対し複数の外部デバイスアクセス装置と複数の外部デバイスとを備える構成であっても、図3のように1つのマスタに対し1つの外部デバイスアクセス装置と複数の外部デバイスとを備える構成であってもよい。また、外部デバイスアクセス装置は、書き込みアドレス格納部、書き込みデータ格納部、読み出しアドレス格納部、読み出しデータ格納部、アドレス制御部、状態信号格納部、未実装情報格納部、エラーアドレス格納部、格納動作状態保持部を複数備えていてもよい。

10

【産業上の利用可能性】

### [0208]

本発明にかかる外部デバイスアクセス装置は、マスタと外部デバイス間のアクセスに関して、マスタの状態に依存しないアクセスを実現して、アクセスペナルティを低減し、マスタの性能への影響を低減できる効果があり、マスタと外部デバイスを備えるシステムLSIに有用である。またマスタに対して、外部デバイスの構成に依存せず外部デバイスを容易に拡張できるため、システムLSIにおいてマスタを汎用的に用いる場合には、マスタを改変する必要が生じないため、開発コストを大幅に削減できることが有用である。

【図面の簡単な説明】

20

30

[0209]

- 【図1】図1は、第1の実施形態のシステムLSIの構成を示すブロック図である。

- 【図2】図2は、第1の実施形態の外部デバイスアクセス装置の構成を示すブロック図である。

- 【図3】図3は、第1の実施形態の他のシステムLSIの構成を示すブロック図である。

- 【図4】図4は、第2の実施形態の外部デバイスアクセス装置の構成を示すブロック図で ある。

- 【図5】図5は、第3の実施形態の外部デバイスアクセス装置の構成を示すブロック図で ある。

- 【図6】図6は、第4の実施形態の外部デバイスアクセス装置の構成を示すブロック図で ある。

- 【図7】図7は、第5の実施形態の外部デバイスアクセス装置の構成を示すブロック図で ある

- 【図8】図8は、第6の実施形態の外部デバイスアクセス装置の構成を示すブロック図で ある。

- 【図9】図9は、第7の実施形態の外部デバイスアクセス装置の構成を示すブロック図である。

【符号の説明】

[ 0 2 1 0 ]

- 101 マスタ

- 102 外部デバイス

- 103 外部デバイスアクセス装置

- 110 書き込みアドレス格納部

- 111 書き込みデータ格納部

- 1 1 2 読み出しアドレス格納部

- 113 読み出しデータ格納部

- 1 1 4 アドレス制御部

- 150 アドレスバス

- 151 書き込みデータ入力バス

- 152 読み出しデータ出力バス

50

- 153 R/W信号バス

- 160 書き込みアドレス

- 161 書き込み許可信号

- 162 読み出しアドレス

- 163 読み出しアドレス許可信号

- 164 読み出しデータ許可信号

- 170 書き込みアドレス出力バス

- 171 書き込みデータ入力出力バス

- 172 読み出しアドレス出力バス

- 173 読み出しデータ入力バス

- 2 1 5 状態信号格納部

- 254 状態信号出力バス

- 274 状態信号入力バス

- 364 読み出しデータ格納部制御

- 365 読み出しアドレス

- 372 読み出しアドレスバス

- 4 1 5 未実装情報格納部

- 454 未実装情報バス

- 465 未実装情報

- 5 1 5 エラーアドレス格納部

- 554 エラーアドレスバス

- 565 エラーアドレス

- 664 読み出しデータ格納部制御

- 665 エラーアドレス

- 7 1 5 格納動作状態保持部

- 765 格納動作状態

10

【図5】

【図6】

【図7】

【図8】

【図9】

## フロントページの続き

(72)発明者 森下 広之

日本国大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 檜垣 信生

日本国大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 工藤 洋介

日本国大阪府門真市大字門真1006番地 松下電器産業株式会社内

## 審査官 横山 佳弘

(56)参考文献 特開平05-012190(JP,A)

特開2003-006133(JP,A)

特開平06-110823(JP,A)

特開2004-252580(JP,A)

特開平02-019955(JP,A)

## (58)調査した分野(Int.CI., DB名)

G06F 13/12

G06F 13/36

G06F 15/78

G06F 13/14