## (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 116391262 A (43) 申请公布日 2023.07.04

(21)申请号 202180004082.5

(22)申请日 2021.10.31

(85) PCT国际申请进入国家阶段日 2021.12.22

(86) PCT国际申请的申请数据 PCT/CN2021/127794 2021.10.31

(87) PCT国际申请的公布数据 W02023/070638 EN 2023.05.04

(71) 申请人 长江存储科技有限责任公司 地址 430000 湖北省武汉市东湖新技术开 发区未来三路88号

(72) **发明人** 杨涛 赵冬雪 杨远程 夏志良 霍宗亮

(74) 专利代理机构 北京永新同创知识产权代理 有限公司 11376 专利代理师 林锦辉 刘景峰

(51) Int.CI.

H01L 29/786 (2006.01)

权利要求书4页 说明书50页 附图57页

#### (54) 发明名称

具有垂直晶体管的存储器器件及其形成方 法

#### (57) 摘要

在某些方面中,一种存储器器件包括垂直晶体管、存储单元、位线和主体线。垂直晶体管包括在第一方向上延伸的半导体主体。半导体主体包括掺杂的源极、掺杂的漏极和沟道部分。存储单元耦合到第一端子。第一端子是源极和漏极中的一者。位线在垂直于第一方向的第二方向上延伸并且耦合到第二端子。第二端子是源极和漏极中的另一者。主体线耦合到半导体主体的沟道部分。

1.一种存储器器件,包括:

垂直晶体管,所述垂直晶体管包括在第一方向上延伸的半导体主体,其中,所述半导体主体包括掺杂的源极、掺杂的漏极和沟道部分;

存储单元,所述存储单元耦合到第一端子,所述第一端子是所述源极和所述漏极中的一者;

位线,所述位线在垂直于所述第一方向的第二方向上延伸并且耦合到第二端子,所述 第二端子是所述源极和所述漏极中的另一者;以及

主体线,所述主体线耦合到所述半导体主体的所述沟道部分。

- 2.根据权利要求1所述的存储器器件,其中,所述主体线和所述存储单元耦合到所述垂直晶体管在所述第一方向上的相对端部。

- 3.根据权利要求1或2所述的存储器器件,其中,所述位线在所述第一方向上在所述存储单元与所述主体线之间。

- 4.根据权利要求1-3中的任何一项所述的存储器器件,其中,所述位线与所述第二端子接触,并且所述位线通过所述第二端子与所述半导体主体的所述沟道部分分离。

- 5.根据权利要求1-4中的任何一项所述的存储器器件,其中

所述第一端子形成在所述半导体主体的基部的一个端部上;

所述第二端子形成在所述半导体主体的突出部的一个或多个侧面上;并且

所述沟道部分形成在所述半导体主体的所述基部和所述突出部中。

- 6.根据权利要求1-5中的任何一项所述的存储器器件,其中,所述半导体主体包括单晶硅,并且所述沟道部分包括未掺杂的单晶硅或者具有与所述源极和所述漏极不同类型的掺杂剂的掺杂的单晶硅。

- 7.根据权利要求6所述的存储器器件,其中,所述主体线包括与所述半导体主体的所述 沟道部分接触的多晶硅层以及与所述多晶硅层接触的金属层。

- 8.根据权利要求1-7中的任何一项所述的存储器器件,还包括在垂直于所述第一方向和所述第二方向的第三方向上延伸的字线,

其中,所述垂直晶体管还包括在所述第三方向上与所述半导体主体的一个或多个侧面接触的栅极结构。

- 9.根据权利要求1-8中的任何一项所述的存储器器件,其中,所述垂直晶体管和所述存储单元形成动态随机存取存储器(DRAM)单元、相变存储器(PCM)单元或者铁电RAM(FRAM)单元。

- 10.一种三维(3D)存储器器件,包括:

- 第一半导体结构,所述第一半导体结构包括外围电路;

- 第二半导体结构,所述第二半导体结构包括:

垂直晶体管,所述垂直晶体管包括在第一方向上延伸的半导体主体,其中,所述半导体主体包括掺杂的源极、掺杂的漏极和沟道部分;

存储单元,所述存储单元耦合到第一端子,所述第一端子是所述源极和所述漏极中的一者:

位线,所述位线在垂直于所述第一方向的第二方向上延伸并且耦合到第二端子,所述 第二端子是所述源极和所述漏极中的另一者;以及 主体线,所述主体线耦合到所述半导体主体的所述沟道部分;以及

键合界面,所述键合界面在所述第一方向上在所述第一半导体结构与所述第二半导体结构之间。

- 11.根据权利要求10所述的3D存储器器件,其中,所述存储单元在所述第一方向上在所述键合界面与所述垂直晶体管之间。

- 12.根据权利要求10或11所述的3D存储器器件,还包括在垂直于所述第一方向和所述 第二方向的第三方向上延伸的字线,

其中,所述垂直晶体管还包括在所述第三方向上与所述半导体主体的一个或多个侧面接触的栅极结构。

- 13.根据权利要求12所述的3D存储器器件,其中,所述字线在所述第一方向上在所述键合界面与所述位线之间。

- 14.根据权利要求10-13中的任何一项所述的3D存储器器件,其中

所述第一半导体结构还包括第一键合层,其中,所述第一键合层包括第一键合触点,并 且所述第二半导体结构还包括第二键合层,其中,所述第二键合层包括第二键合触点;并且 所述第一键合触点与所述第二键合触点在所述第一键合界面处接触。

- 15.根据权利要求10-14中的任何一项所述的3D存储器器件,其中,所述主体线和所述存储单元耦合到所述垂直晶体管在所述第一方向上的相对端部。

- 16.根据权利要求10-15中的任何一项所述的3D存储器器件,其中,所述位线在所述第一方向上在所述存储单元与所述主体线之间。

- 17.根据权利要求10-16中的任何一项所述的3D存储器器件,其中,所述位线与所述第二端子接触,并且所述位线通过所述第二端子与所述半导体主体的所述沟道部分分离。

- 18.根据权利要求10-17中的任何一项所述的3D存储器器件,其中

所述第一端子形成在所述半导体主体的基部的一个端部上;

所述第二端子形成在所述半导体主体的突出部的一个或多个侧面上:并且

所述沟道部分形成在所述半导体主体的所述基部和所述突出部中。

- 19.根据权利要求10-18中的任何一项所述的3D存储器器件,其中,所述半导体主体包括单晶硅,并且所述沟道部分包括未掺杂的单晶硅或者具有与所述源极和所述漏极不同类型的掺杂剂的掺杂的单晶硅。

- 20.根据权利要求19所述的3D存储器器件,其中,所述主体线包括与所述半导体主体的 所述沟道部分接触的多晶硅层以及与所述多晶硅层接触的金属层。

- 21.一种存储器系统,包括:

存储器器件,所述存储器器件被配置为存储数据并且包括:

垂直晶体管,所述垂直晶体管包括在第一方向上延伸的半导体主体,其中,所述半导体主体包括掺杂的源极、掺杂的漏极和沟道部分:

存储单元,所述存储单元耦合到第一端子,所述第一端子是所述源极和所述漏极中的一者:

位线,所述位线在垂直于所述第一方向的第二方向上延伸并且耦合到第二端子,所述 第二端子是所述源极和所述漏极中的另一者;以及

主体线,所述主体线耦合到所述半导体主体的所述沟道部分;以及

存储器控制器,所述存储器控制器耦合到所述存储器器件并且被配置为通过所述位线和所述主体线控制所述垂直晶体管和所述存储单元。

22.一种用于形成存储器器件的方法,包括:

形成从衬底的第一侧垂直延伸的半导体主体;

从所述衬底的与所述第一侧相对的第二侧去除所述衬底,以暴露所述半导体主体的第一端部;

从所述半导体主体的所暴露的第一端部形成所述半导体主体的突出部;

对所述半导体主体的所述突出部的部分进行掺杂;

形成与所述半导体主体的所述突出部的所掺杂的部分接触的位线;以及

形成与所述半导体主体的所述突出部的另一部分接触的主体线。

- 23.根据权利要求22所述的方法,还包括在去除所述衬底之前,对所述半导体主体的与所述第一端部相对的第二端部进行掺杂。

- 24.根据权利要求23所述的方法,还包括在去除所述衬底之前,在所述半导体主体的所掺杂的第二端部上形成存储单元。

- 25.根据权利要求24所述的方法,其中,形成所述存储单元包括:

在所述半导体主体的所掺杂的第二端部上形成第一电极;

在所述第一电极上形成电容器电介质;以及

在所述电容器电介质上形成第二电极。

26.根据权利要求22-25中的任何一项所述的方法,其中,形成所述半导体主体包括:

在所述衬底上方形成夹在两个电介质层之间的字线:

形成延伸穿过所述字线和所述电介质层的开口,以暴露所述衬底的部分;以及

从所述开口中的所述衬底的所暴露的部分外延生长所述半导体主体。

27.根据权利要求26所述的方法,还包括在外延生长所述半导体主体之前,在所述开口的侧壁上形成栅极电介质。

28.根据权利要求22-27中的任何一项所述的方法,其中,形成所述主体线包括:

形成与所述半导体主体的所述突出部的所述另一部分接触的多晶硅层;以及形成与所述多晶硅层接触的金属层。

29.一种用于形成三维(3D)存储器器件的方法,包括:

在第一衬底上形成外围电路:

形成从第二衬底垂直延伸的半导体主体;

以面对面的方式键合所述第一衬底和所述第二衬底:

夫除所述第二衬底,以暴露所述半导体主体的第一端部:

从所述半导体主体的所暴露的第一端部对所述半导体主体的部分进行掺杂;以及形成与所述半导体主体的另一部分接触的主体线。

- 30.根据权利要求29所述的方法,还包括形成与所述半导体主体的所掺杂的部分接触的位线。

- 31.根据权利要求29或30所述的方法,还包括在对所述半导体主体的所述部分进行掺杂之前,从所述半导体主体的所暴露的第一端部形成所述半导体主体的突出部。

- 32.根据权利要求31所述的方法,其中,所述半导体主体的所掺杂的部分和所述另一部

分在所述半导体主体的所述突出部中。

33.根据权利要求29-32中的任何一项所述的方法,还包括:

在所述外围电路上方形成包括第一键合触点的第一键合层;以及

在所述半导体主体上方形成包括第二键合触点的第二键合层,

其中,在所述键合之后,所述第一键合触点与第二键合触点在键合界面处接触。

34.根据权利要求29-33中的任何一项所述的方法,其中,所述键合包括混合键合。

## 具有垂直晶体管的存储器器件及其形成方法

### 背景技术

[0001] 本公开涉及存储器器件及其制造方法。

[0002] 通过改进工艺技术、电路设计、编程算法和制造工艺,将平面存储器单元缩小到更小的尺寸。然而,随着存储器单元的特征尺寸接近下限,平面工艺和制造技术变得具有挑战性且成本高。结果,用于平面存储器单元的存储器密度接近上限。

[0003] 三维(3D)存储器架构可以解决平面存储器单元中的密度限制。3D存储器架构包括存储器阵列和用于促进存储器阵列的操作的外围电路。

### 发明内容

[0004] 在一个方面中,一种存储器器件包括垂直晶体管、存储单元、位线和主体线。垂直晶体管包括在第一方向上延伸的半导体主体。半导体主体包括掺杂的源极、掺杂的漏极和沟道部分。存储单元耦合到第一端子。第一端子是源极和漏极中的一者。位线在垂直于第一方向的第二方向上延伸并且耦合到第二端子。第二端子是源极和漏极中的另一者。主体线耦合到半导体主体的沟道部分。

[0005] 在另一方面中,一种3D存储器器件包括第一半导体结构、第二半导体结构以及在第一方向上在第一半导体结构与第二半导体结构之间的键合界面,第一半导体结构包括外围电路。第二半导体结构包括垂直晶体管、存储单元、位线和主体线。垂直晶体管包括在第一方向上延伸的半导体主体。半导体主体包括掺杂的源极、掺杂的漏极和沟道部分。存储单元耦合到第一端子。第一端子是源极和漏极中的一者。位线在垂直于第一方向的第二方向上延伸并且耦合到第二端子。第二端子是源极和漏极中的另一者。主体线耦合到半导体主体的沟道部分。

[0006] 在又一方面中,一种存储器系统包括被配置为存储数据的存储器器件以及耦合到存储器器件的存储器控制器。存储器器件包括垂直晶体管、存储单元、位线和主体线。垂直晶体管包括在第一方向上延伸的半导体主体。半导体主体包括掺杂的源极、掺杂的漏极和沟道部分。存储单元耦合到第一端子。第一端子是源极和漏极中的一者。位线在垂直于第一方向的第二方向上延伸并且耦合到第二端子。第二端子是源极和漏极中的另一者。主体线耦合到半导体主体的沟道部分。存储器控制器被配置为通过位线和主体线控制垂直晶体管和存储单元。

[0007] 在再一方面中,公开了一种用于形成存储器器件的方法。形成从衬底的第一侧垂直延伸的半导体主体。从衬底的与第一侧相对的第二侧去除衬底,以暴露半导体主体的第一端部。从半导体主体的暴露的第一端部形成半导体主体的突出部。对半导体主体的突出部的部分进行掺杂。形成与半导体主体的突出部的掺杂的部分接触的位线。形成与半导体主体的突出部的另一部分接触的主体线。

[0008] 在再一方面中,公开了一种用于形成3D存储器器件的方法。在第一衬底上形成外围电路。形成从第二衬底垂直延伸的半导体主体。以面对面的方式键合第一衬底和第二衬底。去除第二衬底,以暴露半导体主体的第一端部。从半导体主体的暴露的第一端部对半导

体主体的部分进行掺杂。形成与半导体主体的另一部分接触的主体线。

### 附图说明

[0009] 并入本文并且形成说明书的一部分的附图示出了本公开的方面,并且与说明书一起进一步用于解释本公开的原理并且使得相关领域技术人员能够制成和使用本公开。

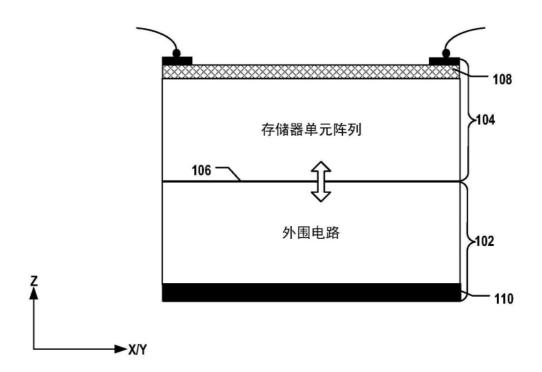

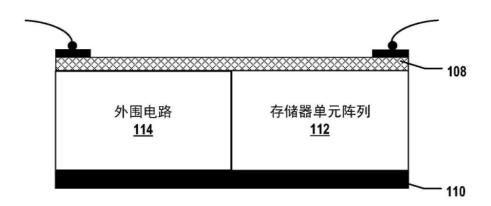

[0010] 图1A示出了根据本公开的一些方面的3D存储器器件的截面的示意图。

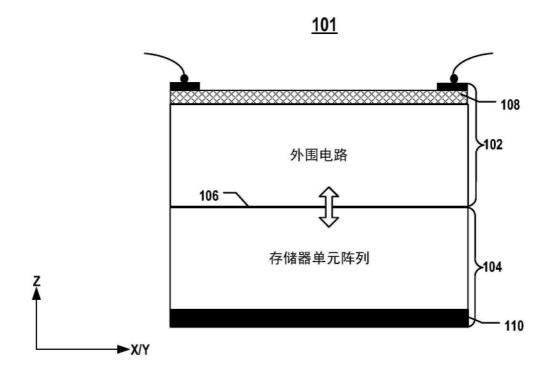

[0011] 图1B示出了根据本公开的一些方面的另一3D存储器器件的截面的示意图。

[0012] 图1C示出了根据本公开的一些方面的又一3D存储器器件的截面的示意图。

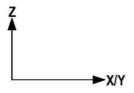

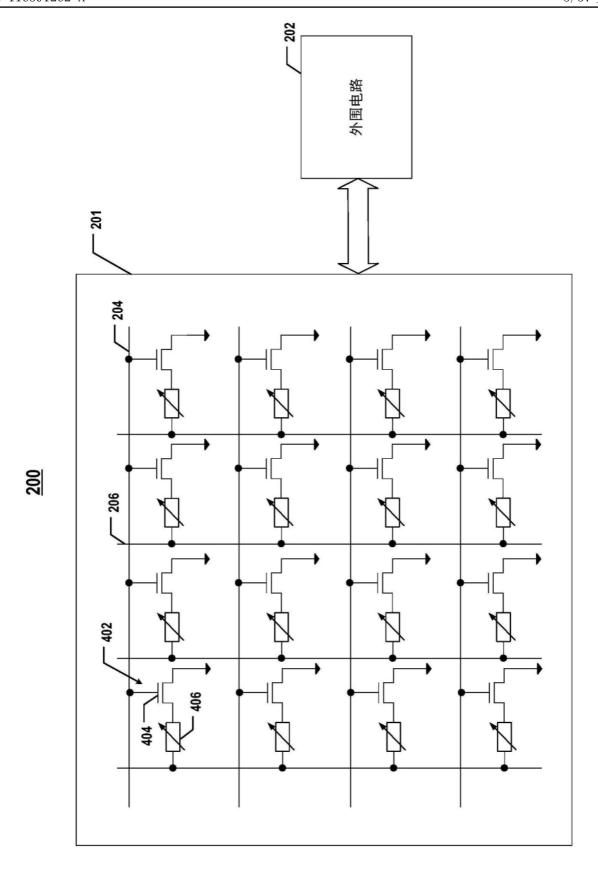

[0013] 图2示出了根据本公开的一些方面的包括外围电路和各自具有垂直晶体管的存储器单元阵列的存储器器件的示意图。

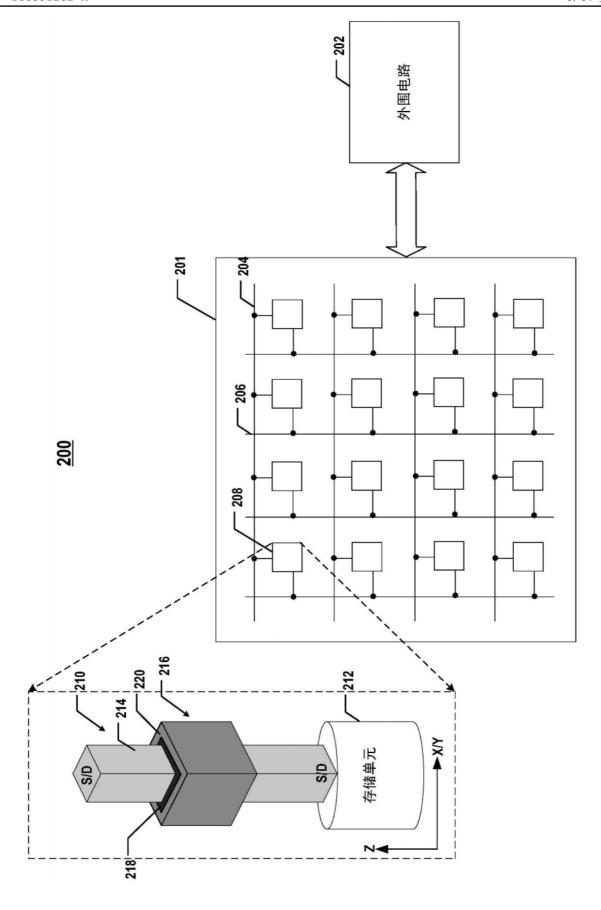

[0014] 图3示出了根据本公开的一些方面的包括外围电路和动态随机存取存储器 (dynamic random-access memory, DRAM) 单元阵列的存储器器件的示意性电路图。

[0015] 图4示出了根据本公开的一些方面的包括外围电路和相变存储器 (phase-change memory, PCM) 单元阵列的存储器器件的示意性电路图。

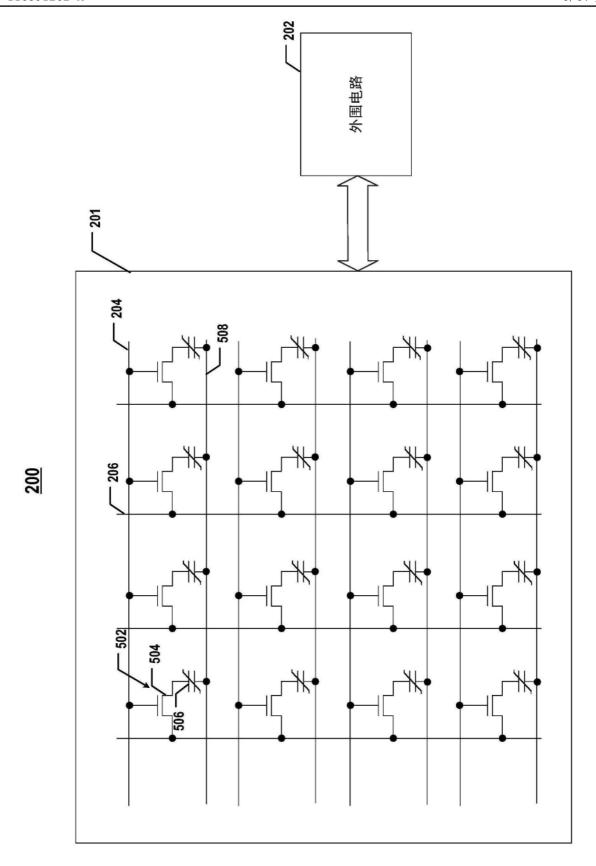

[0016] 图5A示出了根据本公开的一些方面的包括外围电路和铁电随机存取存储器 (ferroelectric random-access memory,FRAM)单元阵列的存储器器件的示意性电路图。

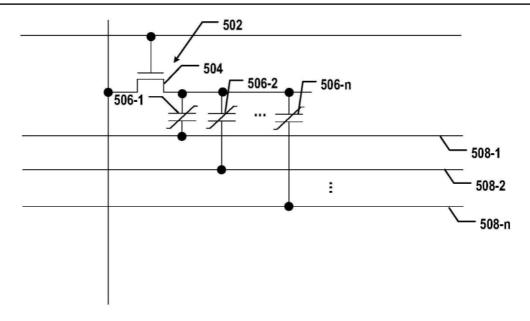

[0017] 图5B示出了根据本公开的一些方面的1TnC FRAM单元的示意性电路图。

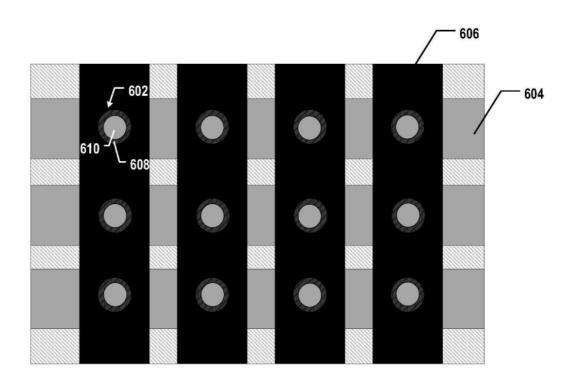

[0018] 图6示出了根据本公开的一些方面的存储器器件中的各自包括垂直晶体管的存储器单元的阵列的平面图。

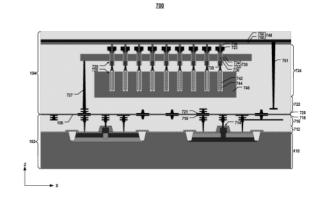

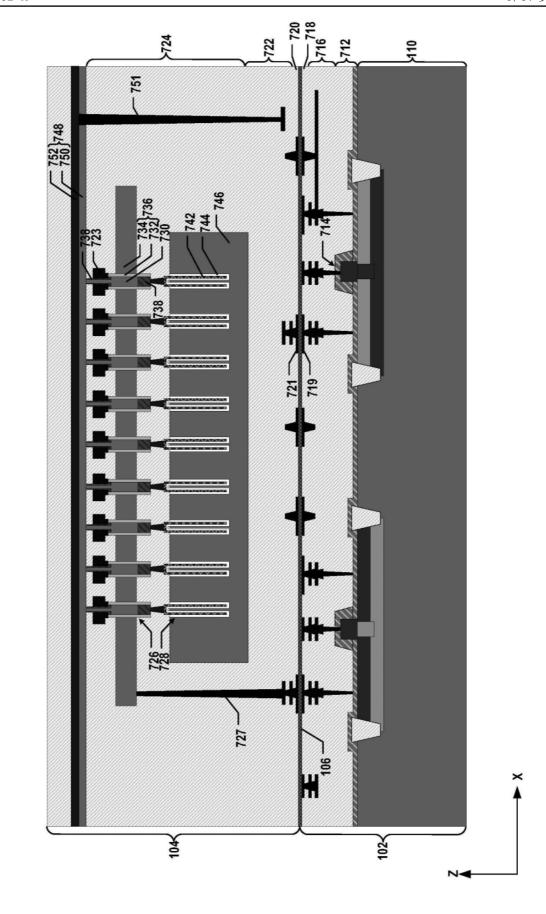

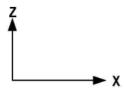

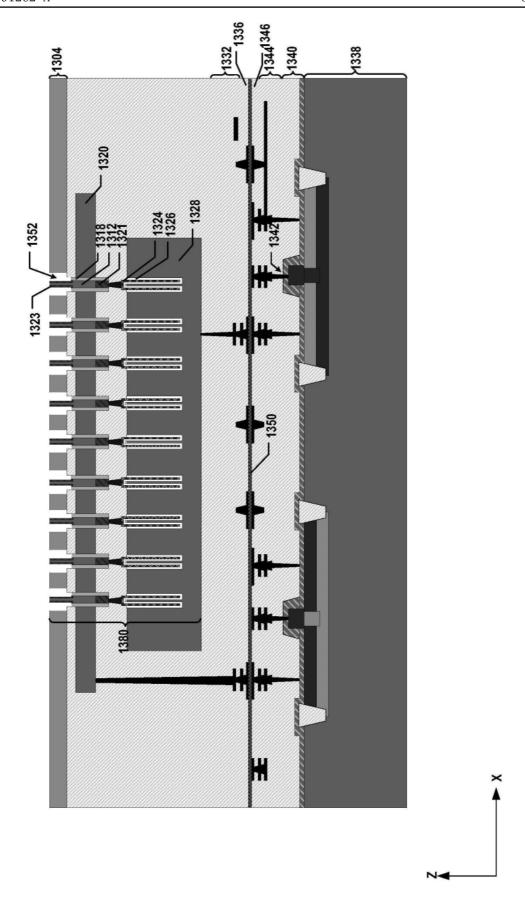

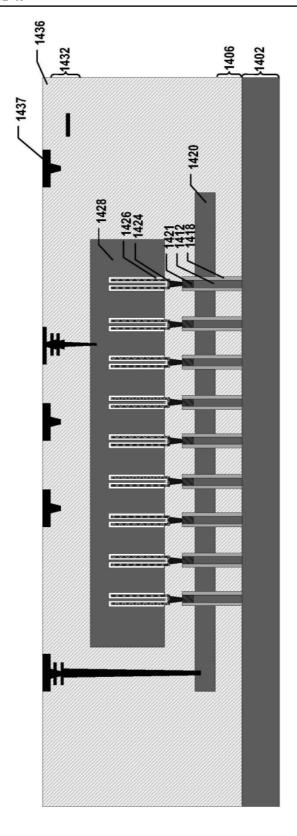

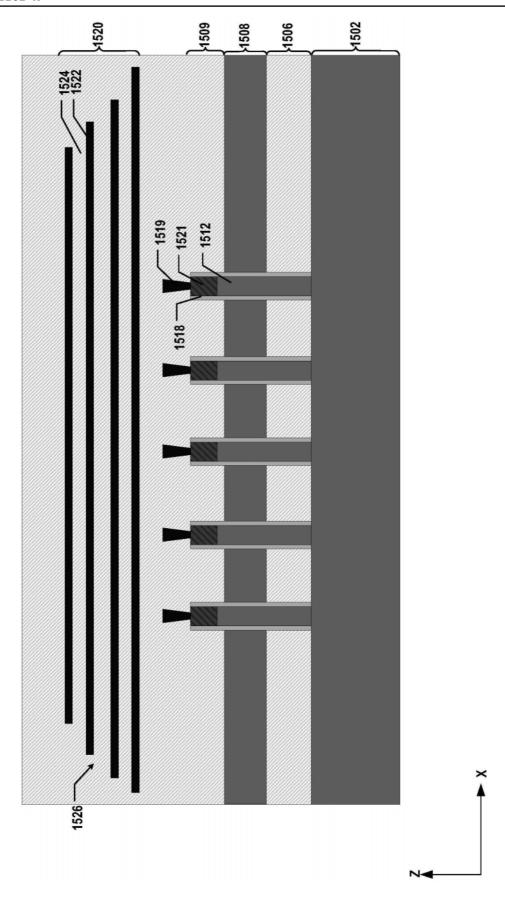

[0019] 图7A示出了根据本公开的一些方面的包括垂直晶体管的3D存储器器件的截面的侧视图。

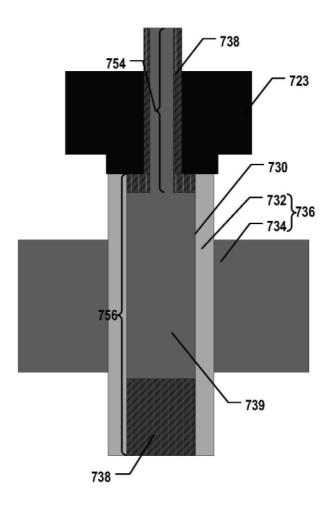

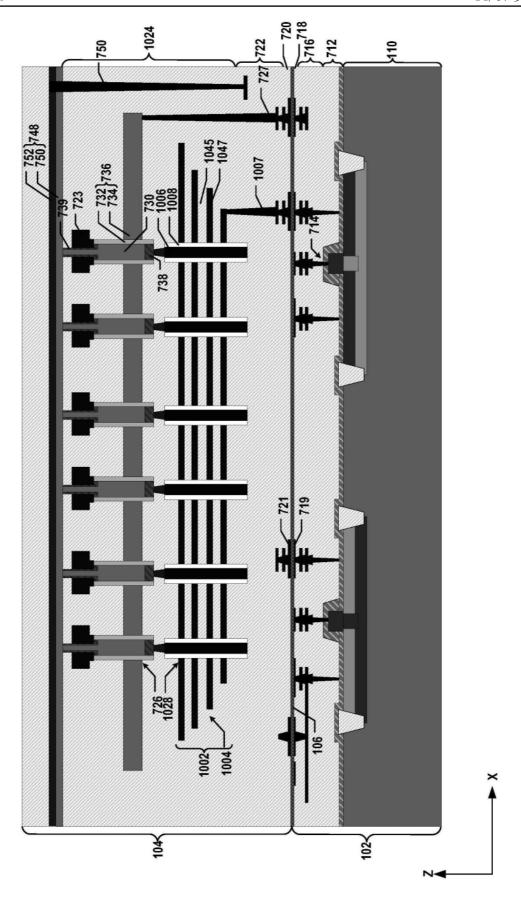

[0020] 图7B示出了根据本公开的一些方面的图7A中的垂直晶体管的截面的放大侧视图。

[0021] 图8示出了根据本公开的一些方面的存储器器件中的各自包括垂直晶体管的存储器单元的另一阵列的平面图。

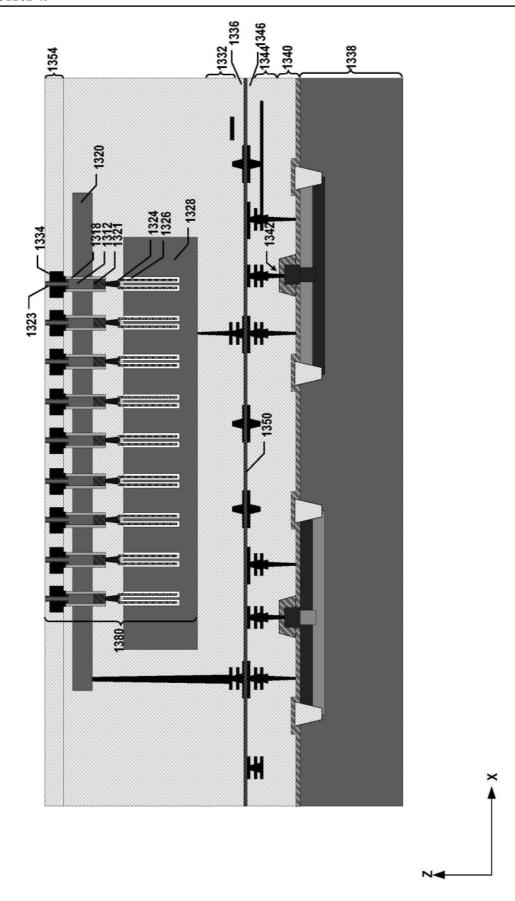

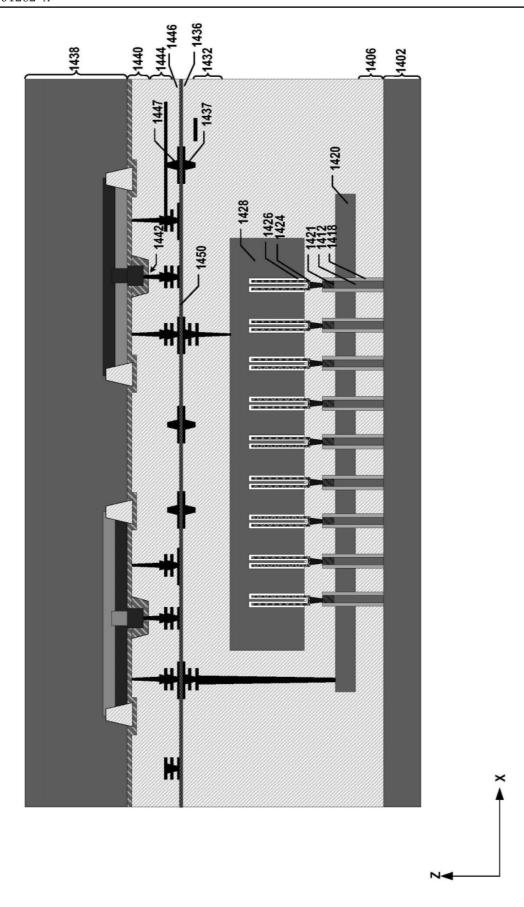

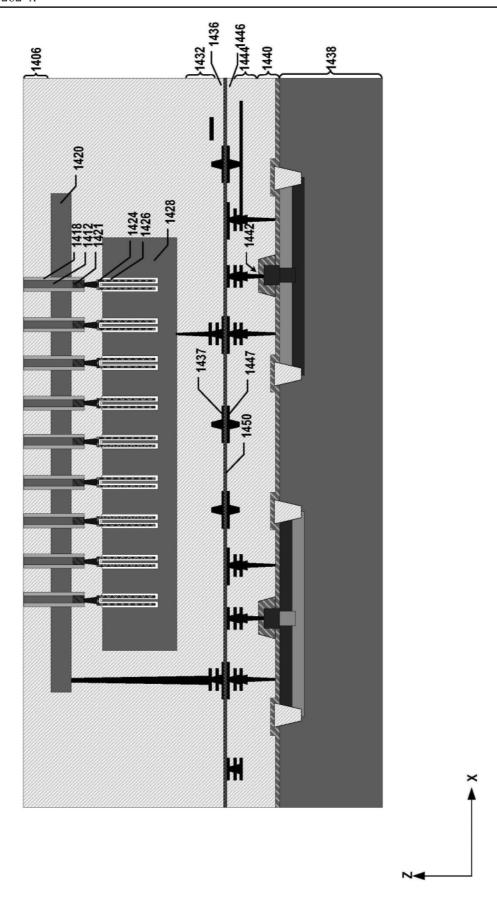

[0022] 图9A示出了根据本公开的一些方面的包括垂直晶体管的另一3D存储器器件的截面的侧视图。

[0023] 图9B示出了根据本公开的一些方面的图9A中的垂直晶体管的截面的放大侧视图。

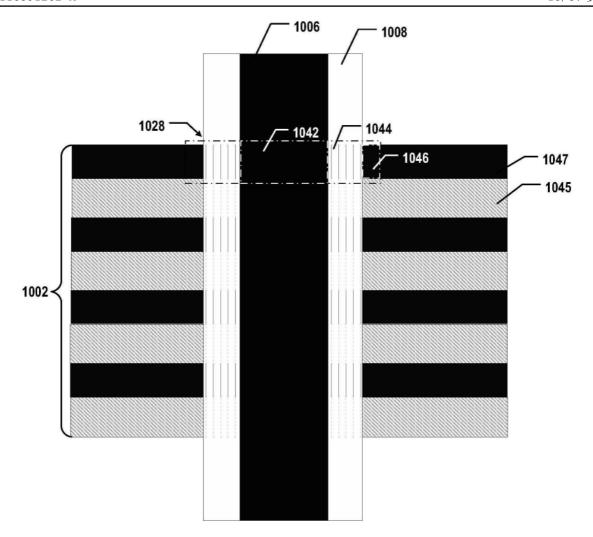

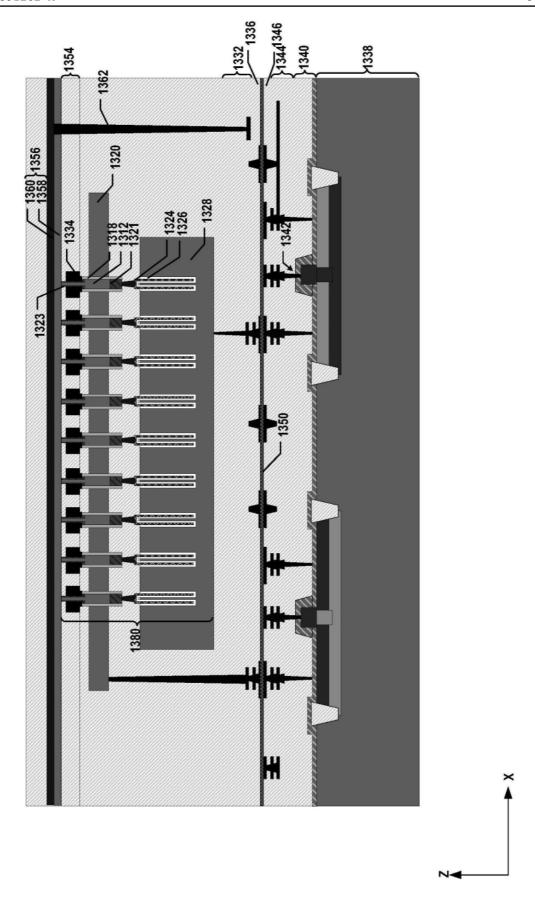

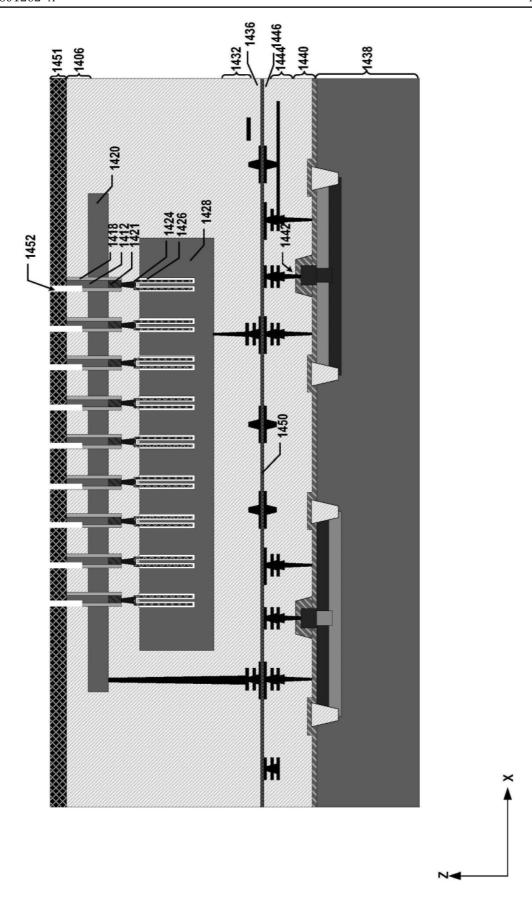

[0024] 图10A示出了根据本公开的一些方面的包括垂直晶体管和堆叠存储单元的又一3D存储器器件的截面的侧视图。

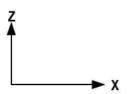

[0025] 图10B示出了根据本公开的一些方面的图10A中的堆叠存储单元的截面的放大侧视图。

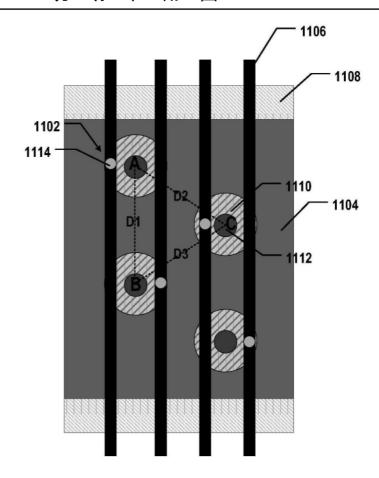

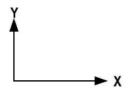

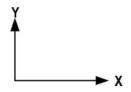

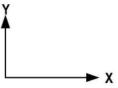

[0026] 图11示出了根据本公开的一些方面的各自包括垂直晶体管的存储器单元的阵列的布局图。

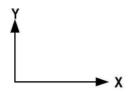

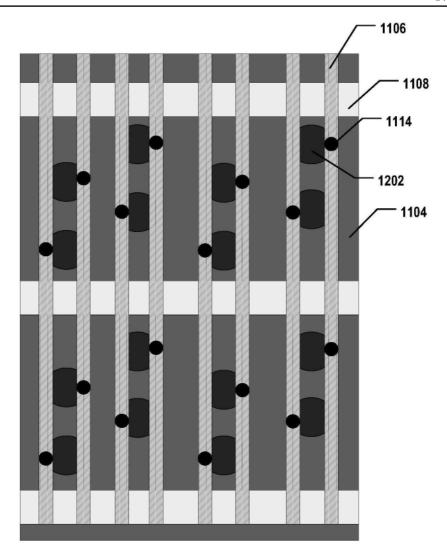

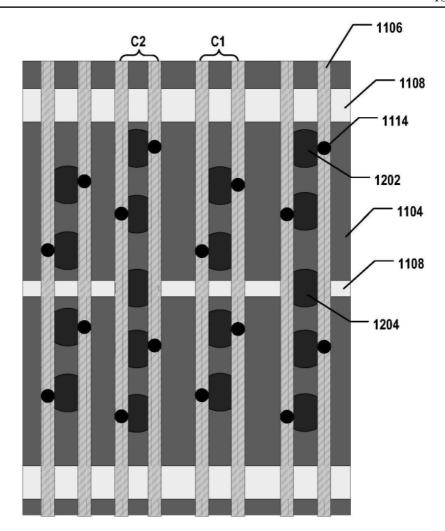

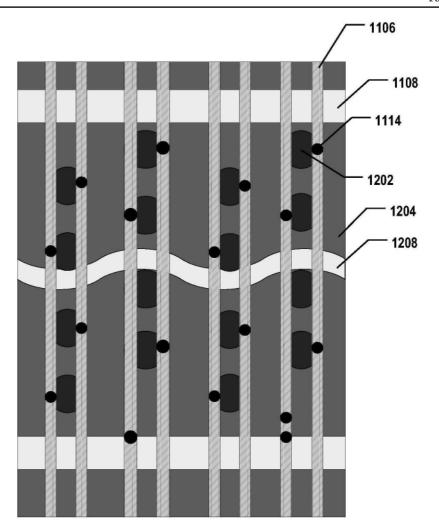

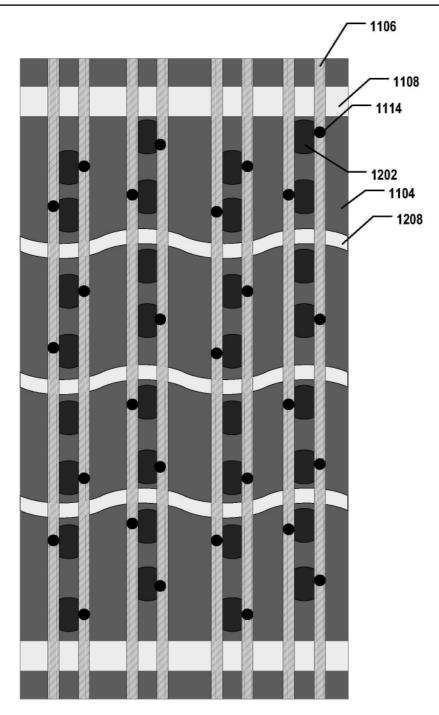

[0027] 图12A-图12E示出了根据本公开的各个方面的各自包括垂直晶体管的存储器单元的各种阵列的布局图。

[0028] 图13A-图13M示出了根据本公开的一些方面的用于形成包括垂直晶体管的3D存储器器件的制造工艺。

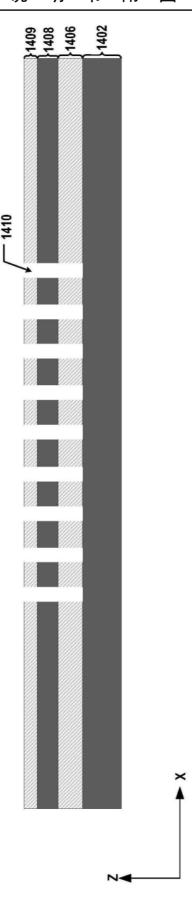

[0029] 图14A-图14M示出了根据本公开的一些方面的用于形成包括垂直晶体管的另一3D 存储器器件的制造工艺。

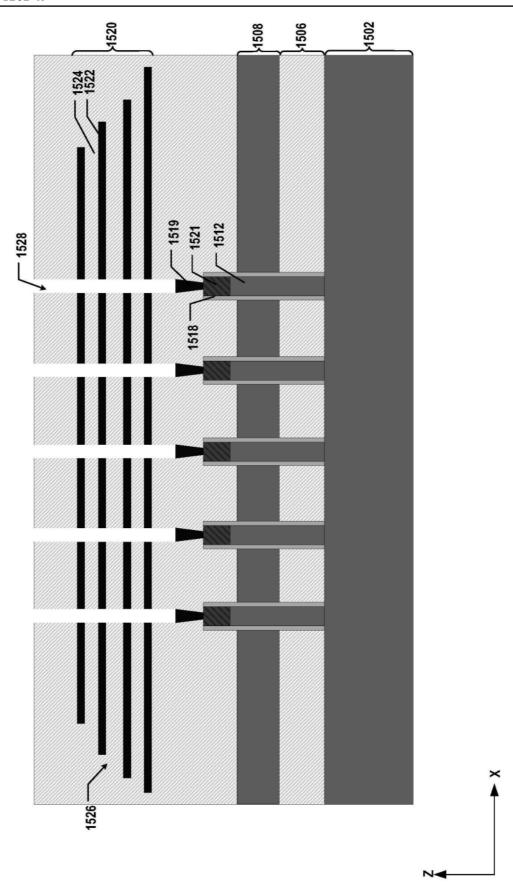

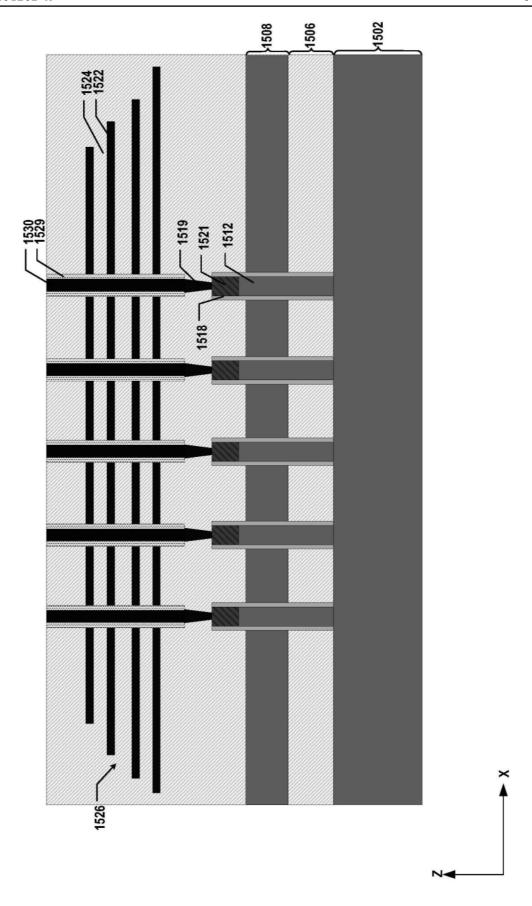

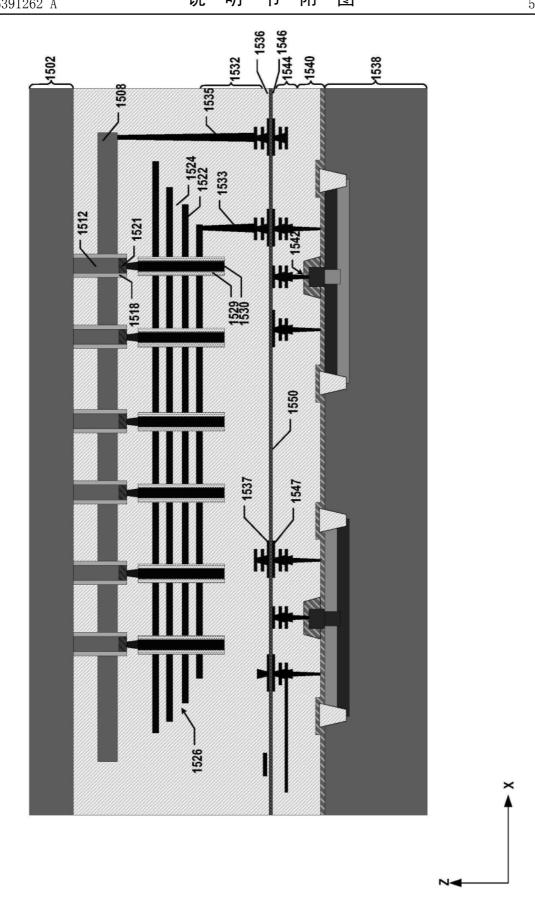

[0030] 图15A-图15E示出了根据本公开的一些方面的用于形成包括垂直晶体管和堆叠存储单元的3D存储器器件的制造工艺。

[0031] 图16示出了根据本公开的一些方面的用于形成包括垂直晶体管的3D存储器器件的方法的流程图。

[0032] 图17示出了根据本公开的一些方面的用于形成各自包括垂直晶体管的存储器单元的阵列的方法的流程图。

[0033] 图18示出了根据本公开的一些方面的用于形成各自包括垂直晶体管的存储器单元的另一阵列的方法的流程图。

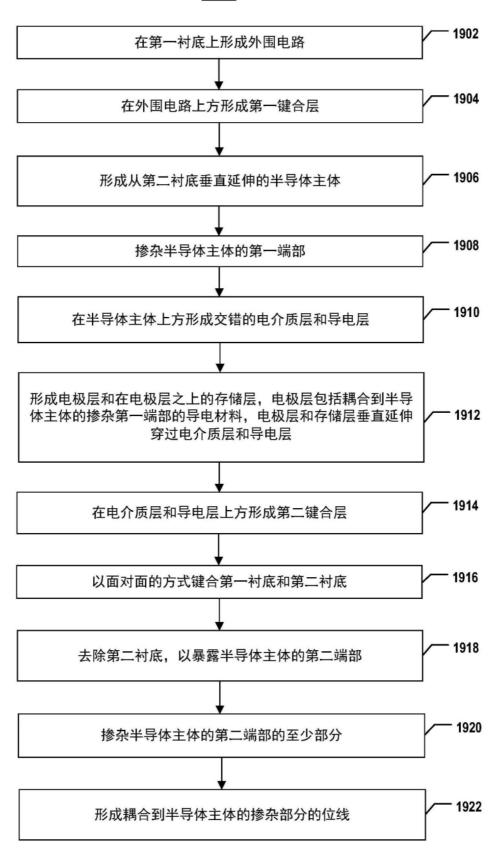

[0034] 图19示出了根据本公开的一些方面的用于形成包括垂直晶体管和堆叠存储单元的3D存储器器件的方法的流程图。

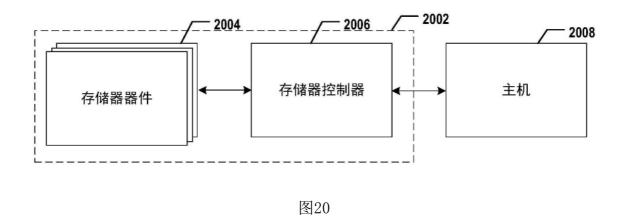

[0035] 图20示出了根据本公开的一些方面的具有存储器器件的示例性系统的框图。

[0036] 将参考附图描述本公开。

### 具体实施方式

[0037] 尽管讨论了具体的配置和布置,但是应当理解,这样做仅仅是出于说明的目的。这样,在不脱离本公开的范围的情况下,可以使用其他配置和布置。此外,本公开也可以用于各种其他应用。如本公开中描述的功能和结构特征可以彼此组合、调整和修改,并且以在附图中未具体描绘的方式,使得这些组合、调整和修改在本公开的范围内。

[0038] 一般地,术语可以至少部分地从上下文中的使用来理解。例如,至少部分地取决于上下文,如本文所用的术语"一个或多个"可以用于以单数意义描述任何特征、结构或特性,或者可以用于以复数意义描述特征、结构或特性的组合。类似地,诸如"一"或"所述"的术语同样可以被理解为传达单数用法或传达复数用法,这至少部分地取决于上下文。另外,术语"基于"可以被理解为不一定旨在传达排他的一组因素,并且可以替代地允许存在不一定明确描述的附加因素,这同样至少部分地取决于上下文。

[0039] 应当容易理解,在本公开中的"在…上"、"在…上方"和"在…之上"的含义应该以最广泛的方式来解释,使得"在…上"不仅意味着"直接在某物上",而且还包括"在某物上"并且其间具有中间特征或层的含义,并且"在…上方"或"在…之上"不仅意味着"在某物上方"或"在某物之上"的含义,而且还可以包括"在某物上方"或"在某物之上"并且其间不具中间特征或层(即,直接在某物上)的含义。

[0040] 此外,诸如"在…下面"、"在…下方"、"下部"、"在…上方"、"上部"等的空间相对术语在本文中为了便于描述可以用于描述一个元件或特征与(一个或多个)另一元件或特征的如图中所示的关系。空间相对术语旨在涵盖除了图中描绘的取向之外的在器件使用或操作中的不同取向。装置可以以其他方式定向(旋转90度或在其他取向下),并且本文所用的空间相对描述词也可以被相应地解释。

[0041] 如本文所用,术语"衬底"是指一种在其上添加后续材料层的材料。这种衬底本身可以被图案化。添加在衬底的顶部上的材料可以被图案化,或者可以保持不被图案化。此外,衬底可以包括多种半导体材料,例如硅、锗、砷化镓、磷化铟等。替代地,衬底可以由诸如玻璃、塑料、或蓝宝石晶圆的非导电材料制成。

[0042] 如本文所用,术语"层"是指包括具有厚度的区域的材料部分。层可以在整个下层

结构或上层结构之上延伸,或者可以具有小于下层结构或上层结构的范围的范围。此外,层可以是同质或非同质的连续结构的区域,其厚度小于连续结构的厚度。例如,层可以位于处于连续结构的顶表面与底表面之间的或处于连续结构的顶表面和底表面处的任何一对水平面之间。层可以水平地、垂直地和/或沿着锥形表面延伸。衬底可以是层,可以在其中包括一个或多个层,和/或可以在其上、其上方和/或其下方具有一个或多个层。层可以包括多个层。例如,互连层可以包括一个或多个导体和接触层(其中形成互连线和/或垂直互连通路(过孔)触点)以及一个或多个电介质层。

[0043] 晶体管被用作一些存储器器件(例如,DRAM、PCM和铁电DRAM(FRAM))的存储器单元中的开关或选择器件。然而,现有存储器单元中常用的平面晶体管通常具有水平结构,其中掩埋字线在衬底中,并且位线在衬底上方。因为平面晶体管的源极和漏极横向地设置在不同的位置处,这增加了晶体管占用的面积。平面晶体管的设计也使耦合到存储器单元的互连结构(例如,字线和位线)的布置复杂化,例如限制了字线和/或位线的间距,从而增加了制造复杂性并且降低了产品良率。此外,由于位线和存储单元(例如,电容或PCM元件)布置在平面晶体管的同一侧(位于晶体管与衬底上方),因此位线工艺裕度会受到存储单元的限制,并且位线与存储单元(例如,电容器)之间的耦合电容会增加。当饱和漏极电流不断增加时,平面晶体管也可能遭受高泄漏电流,这对于存储器器件的性能来说是不期望的。

[0044] 另一方面,随着存储器单元的数量不断增加,为了维持相同的芯片大小,存储器单元阵列中的部件(例如,晶体管、存储单元(例如,电容器)、字线和/或位线)的尺寸需要不断减小,以避免显著降低存储器单元阵列效率。然而,存储单元的器件尺寸的不断减小面临很大的挑战。例如,利用现有设计和仪器,蚀刻电容器孔的纵横比已经达到其极限,因此,可能无法通过使其不断增加来提高存储器单元密度。

[0045] 因此,一些存储器器件用垂直晶体管代替平面晶体管,以增加性能和/或存储器单元阵列效率。然而,与其中可以容易地用特定电势对衬底主体进行偏置以使电荷完全耗尽的平面晶体管不同,垂直晶体管中的半导体主体的上端部和下端部被充分掺杂,以在那些存储器器件中形成源极和漏极,这可能导致浮体效应(floating body effect)。例如,垂直晶体管的半导体主体可能由于形成在沟道与位线之间的二极管而变得浮置。结果,在半导体主体中累积的电荷可能导致负面影响,例如,结构中的寄生晶体管的开路和导致截止状态泄漏、导致更高的电流消耗以及在DRAM情况下导致来自存储器单元的信息的丢失。它还可能导致历史效应,即晶体管的阈值电压依赖于其先前状态。

[0046] 为了解决上述问题中的一个或多个问题,本公开介绍了一种解决方案,其中垂直晶体管代替常规平面晶体管作为存储器器件(例如,DRAM、PCM和FRAM)的存储器单元阵列中的开关和选择器件。与平面晶体管相比,垂直布置的晶体管(即,漏极与源极在平面图中重叠)可以减小晶体管的面积,并且简化互连结构的布局(例如,金属布线字线与位线),这可以降低制造复杂性并且提高良率。例如,为了易于制造,可以减小字线和/或位线的问距。晶体管的垂直结构还允许位线和存储单元(例如,电容器)在垂直方向上布置在晶体管的相对侧面上(例如,一个在晶体管上方,一个在晶体管下方),使得位线的工艺裕度可以增加,并且位线与存储单元之间的耦合电容可以减小。

[0047] 与本公开的范围一致,半导体主体的一个端部可以被部分掺杂,使得半导体主体的沟道部分可以耦合到主体线,以将半导体主体偏置在特定电势处,以抑制浮体效应。在一

些实施方式中,半导体主体的突出部的一个或多个侧面被掺杂,以形成与位线接触的源极/漏极,而突出部的剩余部分(例如,顶部)与主体线接触,以使得能够从沟道耗尽电荷。

[0048] 根据本公开的一些方面,具有垂直晶体管的存储器单元阵列和存储器单元阵列的外围电路可以形成在不同的晶圆上并且以面对面的方式键合在一起。因此,制造存储器单元阵列的热预算不会影响外围电路的制造。与并排布置相比,堆叠的存储器单元阵列和外围电路还可以减小芯片尺寸,从而提高阵列效率。面对面键合还可以允许对垂直晶体管进行背侧处理,以在键合之后从背侧形成半导体主体的部分掺杂的突出部以及位线和主体线。

[0049] 根据本公开的一些方面,在平面图中,存储器单元阵列可以以交错布局布置,而不是以交叉点正交布局(也称为直线或对准布局)布置,以进一步增加单元密度并且减小单位单元尺寸。在一些实施方式中,在交错布局中的任何相邻存储器单元之间保持最小单元距离相同,以最小化单位单元尺寸。为了在交错布局中保持相同的最小单元距离,在各种实施方式中,可以将耦合到分离相邻字线的缝隙结构或者蛇形形状缝隙结构的虚设存储器单元引入到存储器设计中。

[0050] 根据本公开的一些方面,与单个存储单元相反,每个垂直晶体管可以耦合到多个堆叠存储单元(例如,铁电电容器),以进一步增加存储器单元密度。也就是说,存储单元可以在3D中垂直按比例增加,以克服制造限制。在一些实施方式中,铁电存储器器件(例如,FRAM)的多条板线形成在堆叠体结构中,堆叠体结构具有在垂直晶体管上方的交错的导电层和电介质层,并且每条板线耦合到堆叠存储单元中的相应一个存储单元。

[0051] 图1A示出了根据本公开的一些方面的3D存储器器件100的截面的示意图。3D存储器器件100表示键合的芯片的示例。3D存储器器件100的部件(例如,存储器单元阵列和外围电路)可以单独形成在不同衬底上并且然后接合以形成键合的芯片。3D存储器器件100可以包括第一半导体结构102,第一半导体结构102包括存储器单元阵列的外围电路。3D存储器器件100还可以包括第二半导体结构104,第二半导体结构104包括存储器单元阵列。外围电路(又被称为控制和感测电路)可以包括用于促进存储器单元阵列的操作的任何合适的数字、模拟和/或混合信号电路。例如,外围电路可以包括页缓冲器、解码器(例如,行解码器和列解码器)、感测放大器、驱动器(例如,字线驱动器)、输入/输出(I/0)电路、电荷泵、电压源或发生器、电流或电压基准、上述功能电路的任何部分(例如,子电路)、或电路的任何有源或无源部件(例如,晶体管、二极管、电阻器或电容器)中的一个或多个。根据一些实施方式,第一半导体结构102中的外围电路使用互补金属氧化物半导体(complementary metaloxide-semiconductor,CMOS)技术,例如,其可以利用逻辑工艺(例如,90nm、65nm、60nm、45nm、32nm、28nm、22nm、20nm、16nm、14nm、10nm、7nm、5nm、3nm、2nm等的技术节点)来实施。

[0052] 如图1A中所示,3D存储器器件100还可以包括第二半导体结构104,第二半导体结构104包括可以使用晶体管作为开关和选择器件的存储器单元的阵列(存储器单元阵列)。在一些实施方式中,存储器单元阵列包括DRAM单元阵列或任何FRAM单元阵列。为了便于描述,DRAM单元阵列或FRAM单元阵列可以用作用于描述本公开中的存储器单元阵列的示例。但是应当理解,存储器单元阵列不限于DRAM单元阵列或FRAM单元阵列,并且可以包括可以使用晶体管作为开关和选择器件的任何其他合适类型的存储器单元阵列,例如PCM单元阵列、静态随机存取存储器(static random-access memory,SRAM)单元阵列、电阻存储器单

元阵列、磁存储器单元阵列、自旋转移力矩(spin transfer torque,STT)存储器单元阵列,仅举几个示例,或者其任何组合。

[0053] 第二半导体结构104可以是DRAM器件,其中以DRAM单元阵列的形式提供存储器单元。在一些实施例中,每个DRAM单元包括用于将数据位存储为正电荷或负电荷的电容器以及控制(例如,开关和选择)对该DRAM单元的访问的一个或多个晶体管(又被称传输晶体管)。在一些实施方式中,每个DRAM单元是一晶体管一电容器(one-transistor,one-capacitor,1T1C)单元。由于晶体管总是泄漏少量电荷,所以电容器将缓慢放电,从而导致存储在其中的信息耗尽。这样,根据一些实施方式,DRAM单元必须例如通过第一半导体结构102中的外围电路来刷新以保持数据。

[0054] 替代地,第二半导体结构104可以是FRAM器件,其中以FRAM单元阵列的形式提供存储器单元。在一些实施例中,每个FRAM单元包括铁电电容器,以用于基于铁电材料在外部电场下的两个极化状态之间的切换来存储相应FRAM单元的二进制信息。在一些实施方式中,每个FRAM单元是用于存储多位二进制信息的一晶体管一电容器(1T1C)单元。在一些实施方式中,每个FRAM单元是一晶体管多电容器(one-transistor,multi-capacitors,1TnC)单元,其中,n是大于1的正整数。与本公开的范围一致,每个1TnC FRAM单元可以包括垂直堆叠的多个铁电电容器,每个铁电电容器耦合到多条平行的横向延伸的板线中的一条板线。

[0055] 如图1A中所示,3D存储器器件100还包括垂直地在第一半导体结构102与第二半导体结构104之间(在垂直方向上,例如,图1A中的z方向)的键合界面106。如下面详细描述的,第一半导体结构102和第二半导体结构104可以单独制造(并且在一些实施方式中并行制造),使得制造第一半导体结构102和第二半导体结构104中的一个半导体结构的热预算不限制制造第一半导体结构102和第二半导体结构104中的另一半导体结构的工艺。此外,可以穿过键合界面106形成大量互连(例如,键合触点),以在第一半导体结构102与第二半导体结构104之间进行直接的短距离(例如,微米级)电连接,而不是在电路板(例如,印刷电路板(printed circuit board,PCB))上的长距离(例如,毫米或厘米级)芯片到芯片数据总线,由此消除芯片接口延迟并且以降低的功耗实现高速I/0吞吐量。第二半导体结构104中的存储器单元阵列与第一半导体结构102中的外围电路之间的数据传递可以通过跨越键合界面106的互连(例如,键合触点)来执行。通过垂直集成第一半导体结构102和第二半导体结构104,可以减小芯片尺寸,并且可以增加存储器单元密度。

[0056] 应当理解,堆叠的第一半导体结构102和第二半导体结构104的相对位置不受限制。例如,图18示出了根据一些实施方式的另一示例性3D存储器器件101的截面的示意图。与图1A中的3D存储器器件100不同,在3D存储器器件100中,包括存储器单元阵列的第二半导体结构104在包括外围电路的第一半导体结构102上方,在图1B中的3D存储器器件101中,包括外围电路的第一半导体结构102在包括存储器单元阵列的第二半导体结构104上方。然而,根据一些实施方式,键合界面106垂直地形成在3D存储器器件101中的第一半导体结构102与第二半导体结构104之间,并且第一半导体结构102和第二半导体结构104通过键合(例如,混合键合)垂直地接合。混合键合(也被称为"金属/电介质混合键合")是直接键合技术(例如,在不使用中间层(例如,焊料或粘合剂)的情况下在表面之间形成键合),并且可以同时获得金属-金属(例如,铜-铜)键合和电介质-电介质(例如,氧化硅-氧化硅)键合。第二半导体结构104中的存储器单元阵列与第一半导体结构102中的外围电路之间的数据传递

可以通过跨越键合界面106的互连(例如,键合触点)来执行。

[0057] 还应当理解,具有垂直晶体管的存储器单元阵列和存储器单元阵列的外围电路可以以并排方式(即彼此紧挨地)形成在同一晶圆上。与面对面键合方案相比,可以减小制造相同数量的存储器器件所需的晶圆的数量以及键合工艺涉及的复杂性。例如,图1C示出了根据本公开的一些方面的又一3D存储器器件103的截面的示意图。如图1C中所示,与在不同器件平面中彼此堆叠相反,存储器器件103可以包括在同一器件平面中并排布置的存储器单元阵列区112和外围电路区114。存储器单元阵列可以形成在存储器单元阵列区112中,并且存储器单元阵列的外围电路可以形成在设置在存储器单元阵列区112旁边的外围电路区114中。

[0058] 应当注意,图1A-图1C中包括x轴、y轴和z轴以进一步示出3D存储器器件100、101和103中的部件的空间关系。3D存储器器件100、101或103的衬底110包括在x-y平面中横向延伸的两个横向表面:在晶圆的正侧上的顶表面,在该顶表面上可以形成3D存储器器件100、101或103,以及在晶圆的与正侧相对的背侧上的底表面。z轴垂直于x轴和y轴两者。如本文所用,当衬底110在z方向(垂直于x-y平面的垂直方向,例如,衬底的厚度方向)上定位在3D存储器器件100、101或103的最低平面中时,在z方向上相对于存储器器件100、101或103的衬底110,来确定3D存储器器件100、101或103的一个部件(例如,层或器件)是在另一部件(例如,层或器件)"上"、"上方"还是"下方"。在本公开全文中应用了用于描述空间关系的相同概念。

[0059] 如图1A-图1C中所示,3D存储器器件100、101或103还可以包括焊盘引出互连层108,以用于焊盘引出目的,即,使用其上可以焊接键合线的接触焊盘与外部器件互连。焊盘引出互连层108和衬底110可以设置在z方向上的具有存储器单元阵列和外围电路的器件平面的相对侧面上。换句话说,根据一些实施方式,存储器单元阵列和外围电路垂直地设置在3D存储器器件100、101或103中的焊盘引出互连层108与衬底110之间。如图1A和图1B中所示,衬底110和焊盘引出互连层108的相对位置不限于第一半导体结构102和第二半导体结构104。在如图1A中所示的一个示例中,衬底110可以是具有外围电路的第一半导体结构102的部分,并且焊盘引出互连层108可以是具有存储器单元阵列的第二半导体结构104的部分,并且焊盘引出互连层108可以是具有存储器单元阵列的第二半导体结构104的部分,并且焊盘引出互连层108可以是具有外围电路的第一半导体结构102的部分。换句话说,在键合的3D存储器器件100或101中,在不同示例中,可以从存储器单元阵列侧或从外围电路侧实现焊盘引出。

[0060] 图2示出了根据本公开的一些方面的包括外围电路和各自具有垂直晶体管的存储器单元阵列的存储器器件200的示意图。存储器器件200可以包括存储器单元阵列201和耦合到存储器单元阵列201的外围电路202。3D存储器器件100和101可以是其中存储器单元阵列201和外围电路202可以分别包括在第二半导体结构104和第一半导体结构102中的存储器器件200的示例。3D存储器器件103可以是其中存储器单元阵列201和外围电路202可以分别包括在存储器单元阵列区112和外围电路区114中的存储器器件200的另一示例。存储器单元阵列201可以是任何合适的存储器单元阵列,其中每个存储器单元208包括垂直晶体管210和耦合到垂直晶体管210的一个或多个存储单元212。在一些实施方式中,存储器单元阵列201是DRAM单元阵列,并且存储单元212是用于将电荷存储为由相应DRAM单元存储的二进

制信息的电容器。在一些实施方式中,存储器单元阵列201是PCM单元阵列,并且存储单元212是用于基于PCM元件在非晶相和晶相中的不同电阻率来存储相应PCM单元的二进制信息的PCM元件(例如,包括硫属化物合金)。在一些实施方式中,存储器单元阵列201是FRAM单元阵列,并且存储单元212是用于基于铁电材料在外部电场下的两个极化状态之间的切换来存储相应FRAM单元的二进制信息的铁电电容器。

[0061] 如图2中所示,存储器单元208可以布置在具有行和列的二维(2D)阵列中。存储器器件200可以包括耦合外围电路202与存储器单元阵列201以用于控制位于行中的存储器单元208中的垂直晶体管210的开关的字线204,以及耦合外围电路202与存储器单元阵列201以用于将数据发送到位于列中的存储器单元208和/或从位于列中的存储器单元208接收数据的位线206。即,每条字线204耦合到相应行的存储器单元208,并且每条位线耦合到相应列的存储器单元208。

[0062] 与本公开的范围一致,诸如垂直金属氧化物半导体场效应晶体管 (metal-oxide-semiconductor field-effect transistor, MOSFET) 的垂直晶体管210可以代替常规的平面晶体管作为存储器单元208的传输晶体管,以减小由传输晶体管占用的面积、耦合电容以及互连布线复杂性,如下面详细描述的。如图2中所示,在一些实施方式中,与其中在衬底中形成有源区的平面晶体管不同,垂直晶体管210包括在衬底(未示出)上方垂直(在z方向上)延伸的半导体主体214。也就是说,半导体主体214可以在衬底的顶表面上方延伸,以不仅暴露半导体主体214的顶表面,还暴露半导体主体214的一个或多个侧表面。如图2中所示,例如,半导体主体214可以具有立方体形状以暴露其四个侧面。应当理解,半导体主体214可以具有任何合适的3D形状,例如多面体形状或圆柱体形状。也就是说,半导体主体214在平面图中(例如,在x-y平面中)的截面可以具有方形形状、矩形形状(或梯形形状)、圆形(或椭圆形形状)或任何其他合适的形状。应当理解,与本公开的范围一致,对于在平面图中具有圆形或椭圆形形状的截面的半导体主体,半导体主体仍然可以被认为具有多个侧面,使得栅极结构与半导体主体的多于一个的侧面接触。如下面关于制造工艺所述,半导体主体214可以由衬底形成(例如,通过蚀刻和/或外延),并且因此具有与衬底(例如,硅衬底)相同的半导体材料(例如,硅晶体硅)。

[0063] 如图2中所示,垂直晶体管210还可以包括与半导体主体214的一个或多个侧面接触的栅极结构216,即,栅极结构216在有源区的(一个或多个)侧表面的一个或多个平面中与半导体主体214接触。换句话说,垂直晶体管210的有源区(即,半导体主体214)可以至少部分地被栅极结构216围绕。栅极结构216可以包括在半导体主体214的一个或多个侧面之上的栅极电介质218,例如,如图中2所示与半导体主体214的四个侧表面接触。栅极结构216还可以包括在栅极电介质218之上并且与栅极电介质218接触的栅极电极220。栅极电介质218可以包括任何合适的电介质材料,例如,氧化硅、氮化硅、氮氧化硅或高介电常数(高k)电介质。例如,栅极电介质218可以包括氧化硅,即栅极氧化物。栅极电极220可以包括任何合适的导电材料,例如多晶硅、金属(例如,钨(W)、铜(Cu)、铝(A1)等)、金属化合物(例如,氮化钛(TiN)、氮化钽(TaN)等)或硅化物。例如,栅极电极220可以包括掺杂多晶硅,即,栅极多晶硅。在一些实施方式中,栅极电极220包括多个导电层,例如TiN层之上的W层。应当理解,在一些示例中,栅极电极220和字线204可以是连续导电层。换句话说,栅极电极220可以被视为形成栅极结构216的字线204的部分,或者字线204可以被视为栅极电极220的延伸以耦

合到外围电路202。

[0064] 如图2中所示,垂直晶体管210的半导体主体214可以包括分别在垂直方向(z方向)上形成在半导体主体214的两个端部处的一对源极和漏极(S/D,掺杂区,又被称源极电极和漏极电极)。源极和漏极可以掺杂有任何合适的P型掺杂剂(例如,硼(B)或镓(Ga))或者任何合适的N型掺杂剂(例如,磷(P)或砷(As))。垂直晶体管210的半导体主体214还可以包括沟道部分,即,除了源极和漏极之外的剩余部分,在晶体管操作期间(一个或多个)沟道形成在剩余部分中。在一些实施方式中,垂直晶体管210的半导体主体214包括单晶硅,并且沟道部分包括未掺杂的单晶硅或者具有与源极和漏极不同类型的掺杂剂的掺杂的单晶硅。源极和漏极可以在垂直方向(z方向)上被栅极结构216分离。换句话说,栅极结构216垂直地形成在源极与漏极之间。结果,当施加到栅极结构216的栅极电极220的栅极电压高于垂直晶体管210的阈值电压时,垂直晶体管210的一个或多个沟道(未示出)可以在源极与漏极之间垂直地形成在半导体主体214的沟道部分中。也就是说,根据一些实施方式,垂直晶体管210的每个沟道也在半导体主体214还伸所沿的垂直方向上形成。与本公开的范围一致,半导体主体214的沟道部分可以与主体线(图2中未示出)接触,以允许来自沟道的电荷通过主体线耗尽,以减少上文描述的浮体效应和所产生的问题。

[0065] 在一些实施方式中,如图2中所示,垂直晶体管210为多栅极晶体管。也就是说,栅极结构216可以与半导体主体214的多于一个的侧面(例如,图2中的四个侧面)接触以形成多于一个的栅极,使得在操作中可以在源极与漏极之间的半导体主体214中的沟道部分中形成多于一个的沟道。也就是说,与仅包括单个平面栅极(并且产生单个平面沟道)的平面晶体管不同,由于半导体主体214的3D结构和围绕半导体主体214的多个侧面的栅极结构216,图2中所示的垂直晶体管210可以包括在半导体主体214的多个侧面上的多个垂直栅极。结果,与平面晶体管相比,图2中所示的垂直晶体管210可以具有更大的栅极控制面积,以用更小的亚阈值摆幅实现更好的沟道控制。在截止状态期间,由于沟道完全耗尽,因此垂直晶体管210的泄漏电流( $I_{\rm off}$ )也可以显著减小。多栅极垂直晶体管可以包括例如双栅极垂直晶体管(例如,双侧栅极垂直晶体管)、三栅极垂直晶体管(例如,三侧栅极垂直晶体管)和全环栅(gate all around,GAA)垂直晶体管。

[0066] 应当理解,尽管垂直晶体管210在图2中被示为多栅极晶体管,但本文中所公开的垂直晶体管还可以包括单栅极晶体管。也就是说,例如,出于增加晶体管和存储器单元密度的目的,栅极结构216可以与半导体主体214的单个侧面接触。还应当理解,尽管栅极电介质218被示为与相邻垂直晶体管(未示出)的其他栅极电介质分离(即,分离结构),但是栅极电介质218可以是具有垂直晶体管的多个栅极电介质的连续电介质层的部分。

[0067] 在平面晶体管和一些横向多栅极晶体管 (例如,FinFET)中,有源区 (例如,半导体主体 (例如,鳍状物))横向延伸 (在x-y平面中),并且源极和漏极设置在相同横向平面 (x-y平面)中的不同位置处。相反,根据一些实施方式,在垂直晶体管210中,半导体主体214垂直 (在z方向上)延伸,并且源极和漏极设置在不同的横向平面中。在一些实施方式中,源极和漏极分别在垂直方向 (z方向)上形成在半导体主体214的两个端部处,从而在平面图中重叠。结果,与平面晶体管和横向多栅极晶体管相比,可以减小垂直晶体管210所占用的面积 (在x-y平面中)。此外,耦合到垂直晶体管210的金属布线也可以被简化,因为互连可以在不同平面中布线。例如,位线206和存储单元212可以形成在垂直晶体管210的相对侧面上。在

一个示例中,位线206可以耦合到半导体主体214的上端部处的源极或漏极,而存储单元212可以耦合到半导体主体214的下端部处的另一源极或漏极。

[0068] 如图2中所示,存储单元212可以耦合到垂直晶体管210的源极或漏极。存储单元212可以包括能够存储二进制数据(例如,0和1)的任何器件,包括但不限于用于DRAM单元的电容器、用于FRAM单元的铁电电容器以及用于PCM单元的PCM元件。在一些实施方式中,垂直晶体管210控制耦合到垂直晶体管210的相应存储单元212的选择和/或状态切换。尽管图2示出了单个存储单元212,但是应当理解,在一些示例中,多个存储单元212(例如,多个铁电电容器)可以在z方向上堆叠,并且耦合到垂直晶体管210,例如,在1TnC存储器单元中。

[0069] 在如图3中所示的一些实施方式中,每个存储器单元208是包括晶体管304(例如,使用图2中的垂直晶体管210实施)和电容器306(例如,图2中的存储单元212的示例)的DRAM单元302。晶体管304的栅极(例如,对应于栅极电极220)可以耦合到字线204,晶体管304的源极和漏极中的一者可以耦合到位线206,晶体管304的源极和漏极中的另一者可以耦合到电容器306的一个电极,并且电容器306的另一个电极可以耦合到地。

[0070] 在如图4中所示的一些实施方式中,每个存储器单元208是包括晶体管404(例如,使用图2中的垂直晶体管210实施)和PCM元件406(例如,图2中的存储单元212的示例)PCM单元402。晶体管404的栅极(例如,对应于栅极电极220)可以耦合到字线204,晶体管404的源极和漏极中的一者可以耦合到地,晶体管404的源极和漏极中的另一者可以耦合到PCM元件406的一个电极,并且PCM元件406的另一个电极可以耦合到位线206。

[0071] 在如图5A中所示的一些实施方式中,每个存储器单元208是包括晶体管504(例如,使用图2中的垂直晶体管210实施)和铁电电容器506(例如,图2中的存储单元212的示例)的FRAM单元502。晶体管504的栅极(例如,对应栅极电极220)可以耦合到字线204,晶体管504的源极和漏极中的一者可以耦合到位线206,晶体管504的源极和漏极中的另一者可以耦合到性线206,晶体管504的源极和漏极中的另一者可以耦合到铁电电容器506的另一个电极可以耦合到板线508。也就是说,与由两条线(字线204和位线206)控制的DRAM单元302和PCM单元402(又称为两端存储器单元)不同,FRAM单元502(又被称为三端存储器单元)可以由三条线(字线204、位线206和板线508)控制。尽管图5A示出了FRAM单元502的1T1C配置,但是应当理解,在其他示例中,FRAM单元502可以在1TnC配置中。例如,如图5B中所示,在1TnC配置中的FRAM单元502可以包括耦合到晶体管504的源极和漏极中的另一者的n个亚铁电电容器506-1、506-2、…、和506-n。也就是说,每个亚铁电电容器506-1、506-2、…、或506-n的一个电极可以耦合到晶体管504的同一源极/漏极,并且每个亚铁电电容器506-1、506-2、…、或506-n的另一个电极可以耦合到n条板线508-1、508-2、…、和508-n中的相应一条板线,使得每个亚铁电电容器506-1、506-2、…、或506-n可以由相应板线508-1、508-2、…、或508-n单独控制。

[0072] 外围电路202可以通过位线206、字线204和任何其他合适的金属布线耦合到存储器单元阵列201。如上所述,外围电路202可以包括任何合适的电路,以用于通过经由字线204和位线206向每个存储器单元208施加电压信号和/或电流信号并且从每个存储器单元208感测电压信号和/或电流信号来促进存储器单元阵列201的操作。外围电路202可以包括使用CMOS技术形成的各种类型的外围电路。

[0073] 根据本公开的一些方面,在垂直晶体管的半导体主体的远离存储单元的一个端部处,仅对半导体主体的部分进行掺杂,以形成与位线接触的源极和漏极中的一者(例如,

DRAM单元或者FRAM单元的漏极),同时,半导体主体的剩余部分(即,沟道部分)与主体线接触,以用于沟道电荷耗尽,由此减少垂直晶体管的浮体效应。例如,图6示出了根据本公开的一些方面的存储器器件600中的各自包括垂直晶体管的存储器单元602的阵列的平面图。如图6中所示,存储器器件600可以包括各自在第一横向方向(x方向,被称为字线方向)上延伸的多条字线604。存储器器件600还可以包括各自在垂直于第一横向方向的第二横向方向(y方向,被称为位线方向)上延伸的多条位线606。应当理解,图6未示出存储器器件600在相同横向平面中的截面,并且为了便于布线,字线604和位线606可以形成在不同横向平面中,如下文详细描述的。

[0074] 存储器单元602可以形成在字线604与位线606的相交处。在一些实施方式中,每个存储器单元602包括具有半导体主体(例如,图2中的半导体主体214)和栅极结构(例如,图2中的栅极结构216)的垂直晶体管(例如,图2中的垂直晶体管210)。半导体主体可以在垂直于第一横向方向和第二横向方向的垂直方向(z方向,未示出)上延伸。垂直晶体管可以是多栅极晶体管或单栅极晶体管。在一些实施方式中,存储器单元602的阵列在平面图中可以以行和列布置。存储器单元602的每一行可以在字线方向上延伸,并且存储器单元602的每一列可以在位线方向上延伸。存储器单元602的行可以在位线方向上被分离,并且存储器单元602的每一列可以在空线方向上被分离。如图6中所示,在一些实施方式中,存储器单元602的阵列以交叉点正交布局布置,在交叉点正交布局中,存储器单元602形成在字线604与位线606的每一交叉点(相交)中,存储器单元602的在位线方向上的两个相邻行彼此对准(不交错),并且存储器单元602的在字线方向上的两个相邻列也彼此对准(不交错)。图6中的交叉点正交布局的单位单元尺寸可以是例如4F²(又称为4F2单元尺寸)。

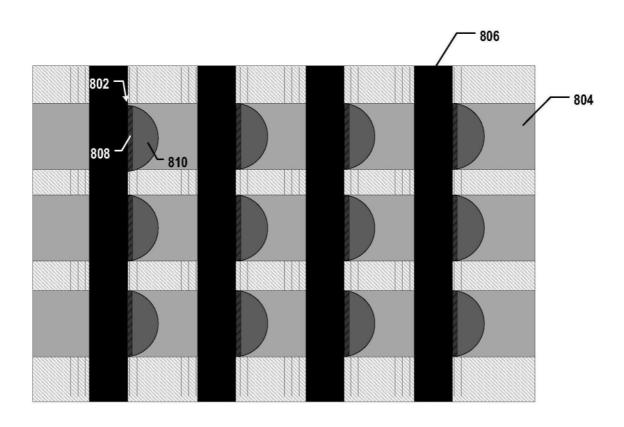

[0075] 半导体主体可以包括掺杂的源极608、掺杂的漏极608和沟道部分610。根据一些实施方式,在半导体主体的在垂直方向上的一个端部(远离存储单元的端部,例如,如图6的平面图中所示)处,半导体主体被部分掺杂,以形成掺杂的源极/漏极608以及被源极/漏极608围绕的沟道部分610。根据一些实施方式,对于存储器单元602的每一列,相应位线606耦合到半导体主体的源极/漏极608而非沟道部分610。也就是说,位线606可以与相应存储器单元602的半导体主体的源极/漏极608接触,但是通过源极/漏极608与沟道部分610分离。在一些存储器器件中的垂直晶体管中,半导体主体的远离存储单元的端部被完全掺杂并且因此完全被源极/漏极覆盖并且与位线接触,与这样的垂直晶体管不同,半导体主体的沟道部分610可以耦合到主体线(图6中未示出),以通过主体线从半导体主体释放沟道电荷。

[0076] 如图6中所示,在一些实施方式中,源极/漏极608形成在半导体主体的所有侧面上,并且位线606在平面图中完全包围(例如,围绕并且接触)半导体主体。在一些实施方式中,源极/漏极608在平面图中在x方向和y方向上横向地在位线606与沟道部分610之间。应当理解,尽管图6中所示的半导体主体在平面图中具有圆形形状的截面,但是源极/漏极608可以形成在如上文所述的具有任何合适形状的截面的半导体主体的所有侧面上,例如,形成在平面图中具有矩形形状或方形形状的截面的半导体主体的所有四个侧面上。

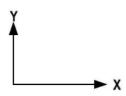

[0077] 图7A示出了根据本公开的一些方面的包括垂直晶体管的3D存储器器件700的截面的侧视图。3D存储器器件700可以是存储器器件600的一个示例。应当理解,图7A仅用于说明性目的,并且实际上可以不必反映实际器件结构(例如,互连)。作为上文关于图1A描述的3D存储器器件100的一个示例,3D存储器器件700是包括第一半导体结构102和堆叠在第一半

导体结构102之上的第二半导体结构104的键合芯片。根据一些实施方式,第一半导体结构102和第二半导体结构104在它们之间的键合界面106处接合。如图7A中所示,第一半导体结构102可以包括衬底110,衬底110可以包括硅(例如,单晶硅、c-Si)、硅锗(SiGe)、砷化镓(GaAs)、锗(Ge)、绝缘体上硅(silicon-on-insulator,SOI)或任何其他合适的材料。

[0078] 第一半导体结构102可以包括衬底110上的外围电路712。在一些实施方式中,外围电路712包括多个晶体管714(例如,平面晶体管和/或3D晶体管)。沟槽隔离(例如,浅沟槽隔离(shallow trench isolation,STI))和掺杂区(例如,晶体管714的阱、源极和漏极)也可以形成在衬底110上或衬底110中。

[0079] 在一些实施方式中,第一半导体结构102还包括在外围电路712上方的互连层716,以向和从外围电路712传递电信号。互连层716可以包括多个互连(本文也被称为"触点"),包括横向互连线和垂直互连通路(vertical interconnect access,VIA)触点。如本文所用,术语"互连"可以广泛地包括任何合适类型的互连,例如中段工艺(middle-end-of-line,MEOL)互连和后段工艺(back-end-of-line,BEOL)互连。互连层716还可以包括一个或多个层间电介质(interlayer dielectric,ILD)层(也被称为"金属间电介质(intermetal dielectric,IMD)层"),在ILD层中可以形成互连线和过孔触点。也就是说,互连层716可以包括多个ILD层中的互连线和过孔触点。在一些实施方式中,外围电路712通过互连层716中的互连彼此耦合。互连层716中的互连可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以由电介质材料形成,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。

[0080] 如图7A中所示,第一半导体结构102还可以包括在键合界面106处并且在互连层716和外围电路712上方的键合层718。键合层718可以包括多个键合触点719和对键合触点719进行电隔离的电介质。键合触点719可以包括导电材料,例如Cu。键合层718的剩余区域可以由电介质材料(例如,氧化硅)形成。键合层718中的键合触点719和周围电介质可以用于混合键合。类似地,如图7A中所示,第二半导体结构104也可以包括在键合界面106处并且在第一半导体结构102的键合层718上方的键合层720。键合层720可以包括多个键合触点721和对键合触点721进行电隔离的电介质。键合触点721可以包括导电材料,例如Cu。键合层720的剩余区域可以由电介质材料(例如,氧化硅)形成。键合层720中的键合触点721和周围电介质可以用于混合键合。根据一些实施方式,键合触点721在键合界面106处与键合触点719接触。

[0081] 第二半导体结构104可以在键合界面106处以面对面的方式键合在第一半导体结构102的顶部上。在一些实施方式中,作为混合键合(也被称为"金属/电介质混合键合")的结果,键合界面106设置在键合层720与718之间,混合键合是直接键合技术(例如,在不使用中间层(例如,焊料或粘合剂)的情况下在表面之间形成键合)并且可以同时获得金属-金属键合和电介质-电介质键合。在一些实施方式中,键合界面106是键合层720和718相遇并且键合的位置。实际上,键合界面106可以是具有一定厚度的层,其包括第一半导体结构102的键合层718的顶表面和第二半导体结构104的键合层720的底表面。

[0082] 在一些实施方式中,第二半导体结构104还包括在键合层720上方的互连层722,以传递电信号。互连层722可以包括多个互连,例如MEOL互连和BEOL互连。在一些实施方式中,互连层722中的互连还包括局部互连,例如位线触点(未示出)、字线触点727和主体线触点

751。互连层722还可以包括一个或多个ILD层,互连线和过孔触点可以形成在ILD层中。互连层722中的互连可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以用电介质材料形成,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低介电常数(低k)电介质或其任何组合。在一些实施方式中,外围电路712包括字线驱动器/行解码器,字线驱动器/行解码器通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的字线触点727。在一些实施方式中,外围电路712包括位线驱动器/列解码器,位线驱动器/列解码器通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的位线触点。在一些实施方式中,外围电路712包括电压源或地,电压源或地通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的主体线触点751。

[0083] 在一些实施方式中,第二半导体结构104包括DRAM器件,其中,存储器单元在互连层722和键合层720上方以DRAM单元724(例如,图6中的存储器单元602的示例)的阵列的形式提供。应当理解,图7A中的3D存储器器件700的截面可以是沿字线方向(x方向)截取的,并且在x方向上横向延伸的一条字线734可以耦合到一行DRAM单元724。每个DRAM单元724可以包括垂直晶体管726(例如,图2中的垂直晶体管210的示例)和耦合到垂直晶体管726的电容器728(例如,图2中的存储单元212的示例)。DRAM单元724可以在由一个晶体管和一个电容器组成的1T1C配置中(即,1T1C单元)中。应当理解,DRAM单元724可以是任何合适的配置,例如,nT1C、1TnC、nTnC等。

[0084] 垂直晶体管726可以是用于对相应DRAM单元724进行开关的MOSFET。在一些实施方式中,垂直晶体管726包括垂直(在z方向上)延伸的半导体主体730(即,其中可以形成多个沟道的有源区)以及与半导体主体730的一个或多个侧面接触的栅极结构736。在其中垂直晶体管726是GAA垂直晶体管的一些实施方式中,半导体主体730具有立方体形状或者圆柱体形状,并且栅极结构736与半导体主体730的所有侧面接触,即,在平面图中完全地包围半导体主体730。在其中垂直晶体管726是三栅极垂直晶体管、双栅极垂直晶体管或单栅极垂直晶体管的一些实施方式中,半导体主体730具有立方体形状或圆柱体形状,并且栅极结构736与半导体主体730的一个侧面或一些侧面(而非所有侧面)接触,即,在平面图中部分地包围半导体主体730。根据一些实施方式,栅极结构736包括栅极电极734以及至少在字线方向上横向地在栅极电极734与半导体主体730之间的栅极电介质732。例如,对于具有圆柱体形状的半导体主体730,半导体主体730、栅极电介质732和栅极电极734可以以此顺序从垂直晶体管726的中心径向设置。在一些实施方式中,栅极电介质732围绕并且接触半导体主体730,并且栅极电极734围绕并且接触栅极电介质732。

[0085] 在一些实施方式中,栅极电介质732包括电介质材料,例如氧化硅、氮化硅或高k电介质,高k电介质包括但不限于氧化铝  $(A1_20_3)$ 、氧化铪  $(Hf0_2)$ 、氧化钽  $(Ta_20_5)$ 、氧化锆  $(Zr0_2)$ 、氧化钛  $(Ti0_2)$  或其任何组合。在一些实施方式中,栅极电极734包括导电材料,导电材料包括但不限于W、Co、Cu、Al、TiN、TaN、多晶硅、硅化物或其任何组合。在一些实施方式中,栅极电极734包括多个导电层,例如,TiN层之上的W层。在一个示例中,栅极结构736可以是"栅极氧化物/栅极多晶硅"栅极,其中,栅极电介质732包括氧化硅,并且栅极电极734包括参杂多晶硅。在另一示例中,栅极结构736可以是高k金属栅极  $(high-k\ metal\ gate,HKMG)$ ,其中,栅极电介质732包括高k电介质,并且栅极电极734包括金属。

[0086] 如图7A中所示,在一些实施方式中,半导体主体730在垂直方向(z方向)上具有两个端部(上端部和下端部),并且两个端部在垂直方向(z方向)上分别延伸超出栅极电极/字线734进入到ILD层中。也就是说,半导体主体730可以具有比栅极电极/字线734的垂直尺寸(例如,在z方向上)大的垂直尺寸(例如,深度),并且半导体主体730的上端部和下端部都不与栅极电极/字线734的相应端部齐平。因此,可以避免位线723与字线/栅极电极734之间或者字线/栅极电极734与电容器728之间的短路。

如图7A以及图7B的放大图中所示,从掺杂角度,即从半导体主体730的特定部分是 否被掺杂或其掺杂剂类型的角度来看,垂直晶体管726的半导体主体730可以包括源极和漏 极(两者均称为738,因为它们的位置可以互换)以及沟道部分739。在一个示例中,半导体主 体730的耦合到电容器728的下端部可以被完全掺杂,以形成源极和漏极738中的一者(例 如,垂直晶体管726的源极),而半导体主体730的远离电容器728的上端部可以被部分掺杂, 以形成源极和漏极738中的另一者(例如,垂直晶体管726的漏极)。因此,半导体主体730的 剩余未掺杂/本征部分可以变为沟道部分739。在另一示例中,半导体主体730的耦合到电容 器728的下端部可以用(一种或多种)N型掺杂剂完全掺杂,以形成源极和漏极738中的一者 (例如,垂直晶体管726的源极),而半导体主体730的远离电容器728的上端部可以用(一种 或多种)N型掺杂剂部分掺杂,以形成源极和漏极738中的另一者(例如,垂直晶体管726的漏 极)。因此,半导体主体730的剩余部分可以变为沟道部分739,沟道部分739可以用(一种或 多种)P型掺杂剂掺杂。在又一示例中,半导体主体730的耦合到电容器728的下端部可以用 (一种或多种)P型掺杂剂完全掺杂,以形成源极和漏极738中的一者(例如,垂直晶体管726 的源极),而半导体主体730的远离电容器728的上端部可以用(一种或多种)P型掺杂剂部分 掺杂,以形成源极和漏极738中的另一者(例如,垂直晶体管726的漏极)。因此,半导体主体 730的剩余部分可以变为沟道部分739,沟道部分739可以用(一种或多种)N型掺杂剂掺杂。 在一些实施方式中,从形状角度,即从半导体主体730的不同部分之间的相对尺寸和几何关 系的角度来看,半导体主体730具有基部756和突出部754,如图7B中所示。例如,基部756可 以具有比突出部754大的横向尺寸。突出部754可以从基部756的内部完全突出,即,突出部 754的所有侧面在平面图中都在基部756的边界内。在一些实施方式中,基部756面向字线/ 栅极电极734,并且突出部754面向位线723。

[0088] 源极和漏极738中的一者(例如,在图7A中的下端部处)可以形成在基部756的一个端部(例如,图7A中的下端部)上。源极和漏极738中的另一者(例如,在图7A中的上端部处)可以形成在半导体主体730的突出部754的一个或多个侧面上。在一些实施方式中,如图7A和图7B中所示,源极和漏极738中的远离电容器728的一者(例如,垂直晶体管726的漏极)形成在突出部754的所有侧面上。沟道部分739可以形成在半导体主体730的基部756和突出部754中。也就是说,半导体主体730的基部756和突出部754两者都可以具有未掺杂的或者用与源极和漏极738不同类型的掺杂剂掺杂的部分,从而变为沟道部分739。如图7A和图7B中所示,根据一些实施方式,与基部756的被掺杂以变为源极/漏极738的部分的下端部(即底部)不同,突出部754的上端部(即顶部)未用与源极和漏极738相同类型的掺杂剂掺杂以变为源极/漏极738的部分,而是作为沟道部分739的部分。如图7B中所示,根据一些实施方式,栅极结构736的栅极电介质732与半导体主体730的基部756接触,但是未进一步延伸以与半导体主体730的突出部754接触。换句话说,栅极电介质732可以与半导体主体730的突出部

754分离。

[0089] 在一些实施方式中,半导体主体730包括半导体材料,例如,单晶硅、多晶硅、非晶硅、Ge、任何其他半导体材料或其任何组合。在一个示例中,半导体主体730可以包括单晶硅,并且半导体主体730的沟道部分739可以包括未掺杂的单晶硅或者具有与源极和漏极738不同类型的掺杂剂的掺杂的单晶硅。源极和漏极738可以掺杂有期望掺杂水平的N型掺杂剂(例如,P或As)或者P型掺杂剂(例如,B或Ga)。在一些实施方式中,源极和漏极738掺杂有N型掺杂剂(例如,P或As),并且沟道部分739是未掺杂/本征的,或者掺杂有P型掺杂剂(例如,B或Ga)。

[0090] 如上文所述,由于栅极电极734可以是字线的部分或者在字线方向(例如,图6中的 x方向)上延伸作为字线,因此尽管图7A中未直接示出,但是3D存储器器件700的第二半导体结构104还可以包括各自在字线方向(x方向)上延伸的多条字线(例如,图6中的字线604的示例,也被称为734)。每条字线734可以耦合到一行DRAM单元724。也就是说,位线723和字线734可以在两个垂直的横向方向上延伸,并且垂直晶体管726的半导体主体730可以在与位线723和字线734延伸的两个横向方向垂直的垂直方向上延伸。根据一些实施方式,字线734与字线触点727接触。在一些实施方式中,字线734包括导电材料,导电材料包括但不限于W、Co、Cu、A1、TiN、TaN、多晶硅、硅化物或其任何组合。在一些实施方式中,字线734包括多个导电层,例如,TiN层之上的W层。

[0091] 如图7A中所示,3D存储器器件700的第二半导体结构104还可以包括各自在位线方向(图6中的y方向)上延伸的多条位线723(例如,图6中的位线606的示例)。每条位线723可以耦合到一列DRAM单元724。在一些实施方式中,位线723耦合到源极和漏极738中的远离电容器728的一者(例如,垂直晶体管726的漏极)。例如,如图7B中所示,位线723可以与形成在半导体主体730的突出部754的所有侧面上的源极/漏极738接触,但是通过源极/漏极738与半导体主体730的沟道部分739分离。也就是说,根据一些实施方式,位线723不与半导体主体730的其中形成垂直晶体管726的沟道的沟道部分739接触,以抑制浮体效应。

[0092] 如图7A中所示,3D存储器器件700的第二半导体结构104还可以包括主体线748,主体线748横向延伸(在位线方向和/或字线方向上)并且耦合到半导体主体730的沟道部分739。主体线748还可以耦合到主体线触点751,主体线触点751进而可以通过互连层722和716以及键合层718和720耦合到第一半导体结构102中的外围电路712。结果,半导体主体730的沟道部分739可以例如经由主体线748、主体线触点751以及互连层722和716及键合层718和720中的任何其他合适的互连,通过外围电路712中的电压源或地而耦合到特定电势,使得半导体主体730的沟道部分739中的沟道电荷可以在3D存储器器件700的操作期间被释放,以减轻浮体效应和所产生的问题。应当理解,在一些示例中,主体线748可以耦合到不在外围电路712中的电压源或地,只要半导体主体730中的沟道的电荷可以被耗尽。

[0093] 如上文所述,半导体主体730的突出部754的上端部(顶部)未被源极/漏极738覆盖,使得主体线748可以与半导体主体730的沟道部分739接触。在一些实施方式中,突出部754的上端部延伸超出位线723,使得与突出部754的上端部接触的主体线748与位线723分离,以避免短路。在一些实施方式中,主体线748包括与半导体主体730的沟道部分739接触的多晶硅层750,以降低主体线748与半导体主体730之间的接触电阻。在一些实施方式中,主体线748还包括与多晶硅层750接触的金属层752(例如,W或Cu层),以降低主体线748的薄

层电阻。应当理解,在其他示例中,主体线748的结构和/或材料可以变化,只要主体线748可以以合理的接触电阻和薄层电阻将半导体主体730的沟道部分739耦合到特定电势。

[0094] 主体线748和电容器728可以耦合到垂直晶体管726的在z方向上的相对端部。例如,主体线748可以耦合到垂直晶体管726的上端部,而电容器728可以耦合到垂直晶体管726的下端部,如图7A中所示。在一些实施方式中,位线723在z方向上在电容器728与主体线748之间,因为位线723与半导体主体730的突出部754的侧面接触,而主体线748与突出部754的上端部接触。在一些实施方式中,电容器728在z方向上在键合界面106与垂直晶体管726之间,并且字线734在z方向上在键合界面106与位线723之间。上文描述的并且在图7A中描绘的3D存储器器件700的第二半导体结构104中的各种部件的相对空间关系可以通过如下工艺得到:如下文关于制造工艺详细描述的第一半导体结构102与第二半导体结构104之间的面对面键合工艺,以及用于形成突出部754、位线723和主体线748的背侧工艺,所述工艺使得能够设计具有减少的浮体效应的垂直晶体管726。

[0095] 如图7A中所示,在一些实施方式中,电容器728包括在垂直晶体管726的源极或漏极738下方并且耦合到(例如,在半导体主体730的基部756的下端部处)源极或漏极738的第一电极742。电容器728还可以包括与第一电极742接触的电容器电介质744以及与电容器电介质744接触的第二电极746。也就是说,电容器电介质744可以夹在电极742和746之间。在一些实施方式中,每个第一电极742耦合到同一DRAM单元724中的相应垂直晶体管726的源极或漏极738,而所有第二电极746是耦合到地(例如,公共地)的公共板的部分。尽管图7A中未示出,但是应当理解,第二半导体结构104还可以包括与第二电极746的公共板接触的电容器触点,以用于将电容器728的第二电极746耦合到外围电路712或直接耦合到地。

[0096] 应当理解,电容器728的结构和配置不限于图7A中叉指式电容器(又被称为指状电容器)示例,并且可以包括任何合适的结构和配置,例如平面电容器、堆叠电容器、多鳍电容器、圆柱电容器、沟槽电容器或衬底-平板电容器。在一些实施方式中,电容器电介质744包括电介质材料,例如,氧化硅、氮化硅或高k电介质,高k电介质包括但不限于 $A1_20_3$ 、 $Hf0_2$ 、 $Ta_20_5$ 、 $Zr0_2$ 、 $Ti0_2$ 、或其任何组合。应当理解,在一些示例中,电容器728可以是在FRAM单元中使用的铁电电容器,并且电容器电介质744可以由具有铁电材料(例如,锆钛酸铅 (PZT) 或钽酸锶铋 (SBT))的铁电层代替。在一些实施方式中,电极742和746包括导电材料,导电材料包括但不限于W、Co、Cu、Al、Tin、Tan、多晶硅、硅化物或其任何组合。

[0097] 尽管图7A中未示出,但是应当理解,在一些示例中,第二半导体结构104还可以包括在主体线748上方的焊盘引出互连层(例如,图1A中的焊盘引出互连层108)。焊盘引出互连层可以包括在一个或多个ILD层中的互连,例如,接触焊盘。焊盘引出互连层和互连层722可以形成在DRAM单元724的相对侧面上。根据一些实施方式,垂直晶体管726垂直地设置在电容器728与焊盘引出互连层之间。在一些实施方式中,焊盘引出互连层中的互连可以在3D存储器器件700与外部电路之间传递电信号,例如,以用于焊盘引出目的。还应当理解,3D存储器器件的焊盘引出不限于来自具有DRAM单元724的第二半导体结构104,并且可以来自具有外围电路712的第一半导体结构102。例如,如图1B中所示,3D存储器器件101可以包括在第一半导体结构102中的焊盘引出互连层。

[0098] 还应当理解,存储器单元阵列不限于图6、图7A和图7B中所示的示例,在所述示例中,位线在平面图中完全包围半导体主体的突出部,并且源极/漏极形成在半导体主体的突

出部的所有侧面上。例如,图8示出了根据本公开的一些方面的存储器器件800中的各自包括垂直晶体管的存储器单元802的另一阵列的平面图。如图8中所示,存储器器件800可以包括多条字线804,每条字线在第一横向方向(x方向,被称为字线方向)上延伸。存储器器件800还可以包括多条位线806,每条位线在垂直于第一横向方向的第二横向方向(y方向,被称为位线方向)上延伸。应当理解,图8未示出存储器器件800在相同横向平面中的截面,并且为了便于布线,字线804和位线806可以形成在不同横向平面中,如下文详细描述的。

[0099] 存储器单元802可以形成在字线804与位线806的相交处。在一些实施方式中,每个存储器单元802包括具有半导体主体(例如,图2中的半导体主体214)和栅极结构(例如,图2中的栅极结构216)的垂直晶体管(例如,图2中的垂直晶体管210)。半导体主体可以在垂直于第一横向方向和第二横向方向的垂直方向(z方向,未示出)上延伸。垂直晶体管可以是多栅极晶体管或单栅极晶体管。在一些实施方式中,存储器单元802的阵列在平面图中可以以行和列布置。存储器单元802的每一行可以在字线方向上延伸,并且存储器单元802的每一列可以在位线方向上延伸。存储器单元802的行可以在位线方向上被分离,并且存储器单元802的每一列可以在空线方向上被分离。如图8中所示,在一些实施方式中,存储器单元802的阵列以交叉点正交布局布置,在交叉点正交布局中,存储器单元802形成在字线804与位线806的每一交叉点(相交)中,存储器单元802的在位线方向上的两个相邻行彼此对准(不交错),并且存储器单元802的在字线方向上的两个相邻列也彼此对准(不交错)。图8中的交叉点正交布局的单位单元尺寸可以是例如4F²(又称为4F2单元尺寸)。

[0100] 半导体主体可以包括掺杂的源极808、掺杂的漏极808和沟道部分810。根据一些实施方式,在半导体主体的在垂直方向上的一个端部(远离存储单元的端部,例如,如图8的平面图中所示)处,半导体主体被部分掺杂,以形成掺杂的源极/漏极808以及沟道部分810。根据一些实施方式,与图6中的沟道部分610被源极/漏极608围绕的存储器单元602不同,在图8中,沟道部分810不被源极/漏极808围绕。相反,根据一些实施方式,源极/漏极808在平面图中仅邻接沟道部分810的一个侧面。根据一些实施方式,对于存储器单元802的每一列,相应位线806耦合到半导体主体的源极/漏极808而非沟道部分810。也就是说,位线806可以与相应存储器单元802的半导体主体的源极/漏极808接触,但是通过源极/漏极808与沟道部分810分离。在一些存储器器件中的垂直晶体管中,半导体主体的远离存储单元的端部被完全掺杂并且因此完全被源极/漏极覆盖并且与位线接触,与这样的垂直晶体管不同,半导体主体的沟道部分810可以耦合到主体线(图8中未示出),以通过主体线从半导体主体释放沟道电荷。

[0101] 与图6中的源极/漏极608形成在半导体主体的所有侧面上并且位线606在平面图中完全包围半导体主体的存储器单元602不同,如图8中所示,在一些实施方式中,源极/漏极808形成在半导体主体的一个侧面或一些侧面上而非所有侧面上,并且位线806在平面图中部分地包围(例如,围绕并且接触)半导体主体。在一些实施方式中,源极/漏极808在平面图中在x方向上但不在y方向上横向地在位线806与沟道部分810之间。应当理解,尽管图8中所示的半导体主体在平面图中具有半圆形形状的截面,但是源极/漏极808可以形成在如上文所述的具有任何合适形状的截面的半导体主体的一个或多个侧面上,例如,形成在平面图中具有矩形形状或方形形状的截面的半导体主体的四个侧面中的一个侧面上。

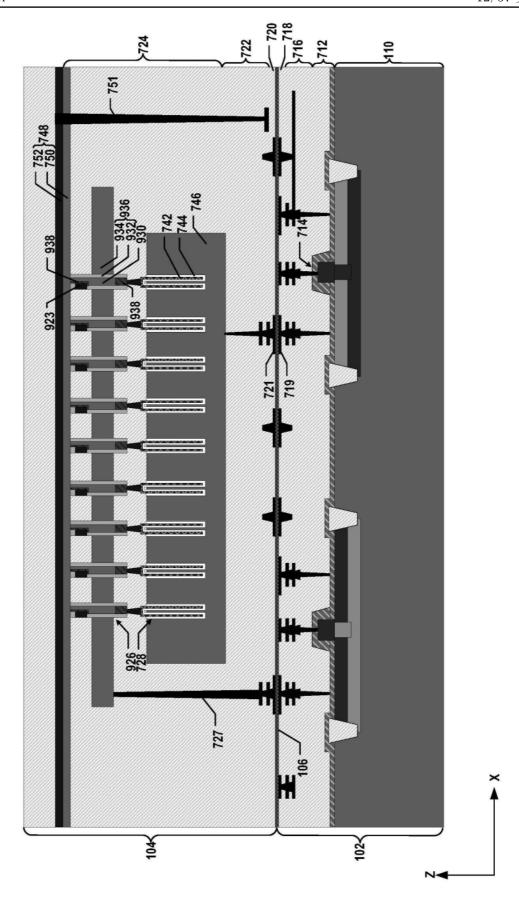

[0102] 图9A示出了根据本公开的一些方面的包括垂直晶体管的另一3D存储器器件900的

截面的侧视图。3D存储器器件900可以是存储器器件900的一个示例。应当理解,图9A仅用于说明性目的,并且实际上可以不必反映实际器件结构(例如,互连)。作为上文关于图1A描述的3D存储器器件100的一个示例,3D存储器器件900是包括第一半导体结构102和堆叠在第一半导体结构102之上的第二半导体结构104的键合芯片。根据一些实施方式,第一半导体结构102和第二半导体结构104在它们之间的键合界面106处接合。如图9A中所示,第一半导体结构102可以包括衬底110,衬底110可以包括硅(例如,单晶硅、c-Si)、SiGe、GaAs、Ge、SOI或任何其他合适的材料。

[0103] 第一半导体结构102可以包括衬底110上的外围电路712。在一些实施方式中,外围电路712包括多个晶体管714(例如,平面晶体管和/或3D晶体管)。沟槽隔离(例如,STI)和掺杂区(例如,晶体管714的阱、源极和漏极)也可以形成在衬底110上或衬底110中。

[0104] 在一些实施方式中,第一半导体结构102还包括在外围电路712上方的互连层716,以向和从外围电路712传递电信号。互连层716可以包括多个互连,包括横向互连线和VIA触点。互连层716还可以包括一个或多个ILD层,在ILD层中可以形成互连线和过孔触点。也就是说,互连层716可以包括多个ILD层中的互连线和过孔触点。在一些实施方式中,外围电路712通过互连层716中的互连彼此耦合。互连层716中的互连可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以由电介质材料形成,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。

[0105] 如图9A中所示,第一半导体结构102还可以包括在键合界面106处并且在互连层716和外围电路712上方的键合层718。键合层718可以包括多个键合触点719和对键合触点719进行电隔离的电介质。键合触点719可以包括导电材料,例如Cu。键合层718的剩余区域可以由电介质材料(例如,氧化硅)形成。键合层718中的键合触点719和周围电介质可以用于混合键合。类似地,如图9A中所示,第二半导体结构104也可以包括在键合界面106处并且在第一半导体结构102的键合层718上方的键合层720。键合层720可以包括多个键合触点721和对键合触点721进行电隔离的电介质。键合触点721可以包括导电材料,例如Cu。键合层720的剩余区域可以由电介质材料(例如,氧化硅)形成。键合层720中的键合触点721和周围电介质可以用于混合键合。根据一些实施方式,键合触点721在键合界面106处与键合触点719接触。

[0106] 第二半导体结构104可以在键合界面106处以面对面的方式键合在第一半导体结构102的顶部上。在一些实施方式中,作为混合键合的结果,键合界面106设置在键合层720与718之间,混合键合是直接键合技术(例如,在不使用中间层(例如,焊料或粘合剂)的情况下在表面之间形成键合)并且可以同时获得金属-金属键合和电介质-电介质键合。在一些实施方式中,键合界面106是键合层720和718相遇并且键合的位置。实际上,键合界面106可以是具有一定厚度的层,其包括第一半导体结构102的键合层718的顶表面和第二半导体结构104的键合层720的底表面。

[0107] 在一些实施方式中,第二半导体结构104还包括在键合层720上方的互连层722,以传递电信号。互连层722可以包括多个互连,例如MEOL互连和BEOL互连。在一些实施方式中,互连层722中的互连还包括局部互连,例如位线触点(未示出)、字线触点727和主体线触点751。互连层722还可以包括一个或多个ILD层,互连线和过孔触点可以形成在ILD层中。互连层722中的互连可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或

其任何组合。ILD层可以用电介质材料形成,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。在一些实施方式中,外围电路712包括字线驱动器/行解码器,字线驱动器/行解码器通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的字线触点727。在一些实施方式中,外围电路712包括位线驱动器/列解码器,位线驱动器/列解码器通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的位线触点。在一些实施方式中,外围电路712包括电压源或地,电压源或地通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的主体线触点751。

[0108] 在一些实施方式中,第二半导体结构104包括DRAM器件,其中,存储器单元在互连层722和键合层720上方以DRAM单元724(例如,图6中的存储器单元602的示例)的阵列的形式提供。应当理解,图9A中的3D存储器器件900的截面可以是沿字线方向(x方向)截取的,并且在x方向上横向延伸的一条字线934可以耦合到一行DRAM单元724。每个DRAM单元724可以包括垂直晶体管926(例如,图2中的垂直晶体管210的示例)和耦合到垂直晶体管926的电容器728(例如,图2中的存储单元212的示例)。DRAM单元724可以在由一个晶体管和一个电容器组成的1T1C配置中(即,1T1C单元)中。应当理解,DRAM单元724可以是任何合适的配置,例如,nT1C、1TnC、nTnC等。

[0109] 垂直晶体管926可以是用于对相应DRAM单元724进行开关的MOSFET。在一些实施方式中,垂直晶体管926包括垂直(在z方向上)延伸的半导体主体930(即,其中可以形成多个沟道的有源区)以及与半导体主体930的一个或多个侧面接触的栅极结构936。在其中垂直晶体管926是GAA垂直晶体管的一些实施方式中,半导体主体930具有立方体形状或者圆柱体形状,并且栅极结构936与半导体主体930的所有侧面接触,即,在平面图中完全地包围半导体主体930。在其中垂直晶体管926是三栅极垂直晶体管、双栅极垂直晶体管或单栅极垂直晶体管的一些实施方式中,半导体主体930具有立方体形状或圆柱体形状,并且栅极结构936与半导体主体930的一个侧面或一些侧面(而非所有侧面)接触,即,在平面图中部分地包围半导体主体930。根据一些实施方式,栅极结构936包括栅极电极934以及至少在字线方向上横向地在栅极电极934与半导体主体930之间的栅极电介质932。例如,对于具有圆柱体形状的半导体主体930,半导体主体930、栅极电介质932和栅极电极934可以以此顺序从垂直晶体管926的中心径向设置。在一些实施方式中,栅极电介质932围绕并且接触半导体主体930,并且栅极电极934围绕并且接触栅极电介质932。

[0110] 在一些实施方式中,栅极电介质932包括电介质材料,例如氧化硅、氮化硅或高k电介质,高k电介质包括但不限于 $A1_20_3$ 、 $Hf0_2$ 、 $Ta_20_5$ 、 $Zr0_2$ 、 $Ti0_2$ 或其任何组合。在一些实施方式中,栅极电极934包括导电材料,导电材料包括但不限于W、Co、Cu、A1、TiN、TaN、多晶硅、硅化物或其任何组合。在一些实施方式中,栅极电极934包括多个导电层,例如,TiN层之上的W层。在一个示例中,栅极结构936可以是"栅极氧化物/栅极多晶硅"栅极,其中,栅极电介质932包括氧化硅,并且栅极电极934包括掺杂多晶硅。在另一示例中,栅极结构936可以是HKMG,其中,栅极电介质932包括高k电介质,并且栅极电极934包括金属。

[0111] 如图9A中所示,在一些实施方式中,半导体主体930在垂直方向(z方向)上具有两个端部(上端部和下端部),并且两个端部在垂直方向(z方向)上分别延伸超出栅极电极/字线934进入到ILD层中。也就是说,半导体主体930可以具有比栅极电极/字线934的垂直尺寸

(例如,在z方向上)大的垂直尺寸(例如,深度),并且半导体主体930的上端部和下端部都不与栅极电极/字线934的相应端部齐平。因此,可以避免位线923与字线/栅极电极934之间或者字线/栅极电极934与电容器928之间的短路。

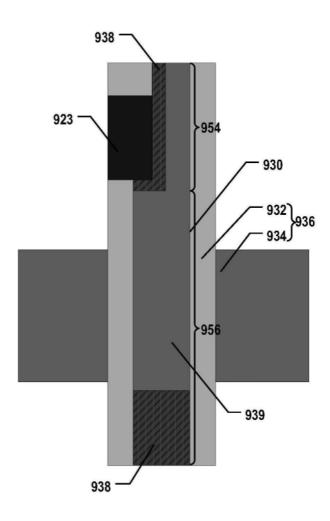

如图9A以及图9B的放大图中所示,从掺杂角度,即从半导体主体930的特定部分是 否被掺杂或其掺杂剂类型的角度来看,垂直晶体管926的半导体主体930可以包括源极和漏 极(两者均称为938,因为它们的位置可以互换)以及沟道部分939。在一个示例中,半导体主 体930的耦合到电容器728的下端部可以被完全掺杂,以形成源极和漏极938中的一者(例 如,垂直晶体管926的源极),而半导体主体930的远离电容器728的上端部可以被部分掺杂, 以形成源极和漏极938中的另一者(例如,垂直晶体管926的漏极)。因此,半导体主体930的 剩余未掺杂部分可以变为沟道部分939。在另一示例中,半导体主体930的耦合到电容器728 的下端部可以用(一种或多种)N型掺杂剂完全掺杂,以形成源极和漏极938中的一者(例如, 垂直晶体管926的源极),而半导体主体930的远离电容器728的上端部可以用(一种或多种) N型掺杂剂部分掺杂,以形成源极和漏极938中的另一者(例如,垂直晶体管926的漏极)。因 此,半导体主体930的剩余部分可以变为沟道部分939,沟道部分939可以用(一种或多种)P 型掺杂剂掺杂。在又一示例中,半导体主体930的耦合到电容器728的下端部可以用(一种或 多种)P型掺杂剂完全掺杂,以形成源极和漏极938中的一者(例如,垂直晶体管926的源极), 而半导体主体930的远离电容器728的上端部可以用(一种或多种)P型掺杂剂部分掺杂,以 形成源极和漏极938中的另一者(例如,垂直晶体管926的漏极)。因此,半导体主体930的剩 余部分可以变为沟道部分939,沟道部分939可以用(一种或多种)N型掺杂剂掺杂。在一些实 施方式中,从形状角度,即从半导体主体930的不同部分之间的相对尺寸和几何关系的角度 来看,半导体主体930具有基部956和突出部954,如图9B中所示。例如,基部956可以具有比 突出部954大的横向尺寸。与其中突出部754从基部756的内部完全地突出的3D存储器器件 700不同,突出部954从基部956的内部部分地突出并且从基部956的边界部分地突出,即,突 出部954的一个侧面或一些侧面在基部956的边界内,而突出部954的(一个或多个)剩余侧 面在平面图中与基部956的边界对准。在一些实施方式中,基部956面向字线/栅极电极934, 并且突出部954面向位线923。

[0113] 源极和漏极938中的一者(例如,在图9A中的下端部处)可以形成在基部956的一个端部(例如,图9A中的下端部)上。源极和漏极938中的另一者(例如,在图9A中的上端部处)可以形成在半导体主体930的突出部954的一个或多个侧面上。在一些实施方式中,如图9A和图9B中所示,源极和漏极938中的远离电容器728的一者(例如,垂直晶体管926的漏极)形成在突出部954的一个侧面或一些侧面上,而不是所有侧面上。沟道部分939可以形成在半导体主体930的基部956和突出部954中。也就是说,半导体主体930的基部956和突出部954两者都可以具有未掺杂的或者用与源极和漏极938不同类型的掺杂剂掺杂的部分,从而变为沟道部分939。如图9A和图9B中所示,根据一些实施方式,与基部956的被掺杂以变为源极/漏极938的部分的下端部(即底部)不同,突出部954的上端部(即顶部)未用与源极和漏极938相同类型的掺杂剂掺杂以变为源极/漏极938的部分,而是作为沟道部分939的部分。如图9B中所示,根据一些实施方式,栅极结构936的栅极电介质932不仅与半导体主体930的基部956接触,还延伸以与半导体主体930的交出部954接触。换句话说,与图7A中的与半导体主体730的突出部754分离的栅极电介质732不同,栅极电介质932可以与半导体主体930

的突出部954接触。

[0114] 在一些实施方式中,半导体主体930包括半导体材料,例如,单晶硅、多晶硅、非晶硅、Ge、任何其他半导体材料或其任何组合。在一个示例中,半导体主体930可以包括单晶硅,并且半导体主体930的沟道部分939可以包括未掺杂的单晶硅或者具有与源极和漏极938不同类型的掺杂剂的掺杂的单晶硅。源极和漏极938可以掺杂有期望掺杂水平的N型掺杂剂(例如,P或As)或者P型掺杂剂(例如,B或Ga)。在一些实施方式中,源极和漏极938掺杂有N型掺杂剂(例如,P或As),并且沟道部分939是未掺杂/本征的,或者掺杂有P型掺杂剂(例如,B或Ga)。

[0115] 如上文所述,由于栅极电极934可以是字线的部分或者在字线方向(例如,图8中的 x方向)上延伸作为字线,因此尽管图9A中未直接示出,但是3D存储器器件900的第二半导体结构104还可以包括各自在字线方向(x方向)上延伸的多条字线(例如,图8中的字线804的示例,也被称为934)。每条字线934可以耦合到一行DRAM单元724。也就是说,位线923和字线934可以在两个垂直的横向方向上延伸,并且垂直晶体管926的半导体主体930可以在与位线923和字线934延伸的两个横向方向垂直的垂直方向上延伸。根据一些实施方式,字线934与字线触点727接触。在一些实施方式中,字线934包括导电材料,导电材料包括但不限于W、Co、Cu、Al、TiN、TaN、多晶硅、硅化物或其任何组合。在一些实施方式中,字线934包括多个导电层,例如,TiN层之上的W层。

[0116] 如图9A中所示,3D存储器器件900的第二半导体结构104还可以包括各自在位线方向(图8中的y方向)上延伸的多条位线923(例如,图8中的位线806的示例)。每条位线923可以耦合到一列DRAM单元724。在一些实施方式中,位线923耦合到源极和漏极938中的远离电容器928的一者(例如,垂直晶体管926的漏极)。例如,如图9B中所示,位线923可以与形成在半导体主体930的突出部954的一个侧面或一些侧面上的源极/漏极938接触,但是通过源极/漏极938与半导体主体930的沟道部分939分离。突出部954的其余侧面可以与栅极电介质932接触。也就是说,根据一些实施方式,位线923不与半导体主体930的其中形成垂直晶体管926的沟道的沟道部分939接触,以抑制浮体效应。

[0117] 如图9A中所示,3D存储器器件900的第二半导体结构104还可以包括主体线748,主体线748横向延伸(在位线方向和/或字线方向上)并且耦合到半导体主体930的沟道部分939。主体线748还可以耦合到主体线触点751,主体线触点751进而可以通过互连层722和716以及键合层718和720耦合到第一半导体结构102中的外围电路712。结果,半导体主体930的沟道部分939可以例如经由主体线748、主体线触点751以及互连层722和716及键合层718和720中的任何其他合适的互连,通过外围电路712中的电压源或地而耦合到特定电势,使得半导体主体930的沟道部分939中的沟道电荷可以在3D存储器器件900的操作期间被释放,以减轻浮体效应和所产生的问题。应当理解,在一些示例中,主体线748可以耦合到不在外围电路712中的电压源或地,只要半导体主体930中的沟道的电荷可以被耗尽。

[0118] 如上文所述,半导体主体930的突出部954的上端部(顶部)未被源极/漏极938覆盖,使得主体线748可以与半导体主体930的沟道部分939接触。在一些实施方式中,突出部954的上端部延伸超出位线923,使得与突出部954的上端部接触的主体线748与位线923分离,以避免短路。在一些实施方式中,主体线748包括与半导体主体930的沟道部分939接触的多晶硅层750,以降低主体线748与半导体主体930之间的接触电阻。在一些实施方式中,

主体线748还包括与多晶硅层750接触的金属层752(例如,W或Cu层),以降低主体线748的薄层电阻。应当理解,在其他示例中,主体线748的结构和/或材料可以变化,只要主体线748可以以合理的接触电阻和薄层电阻将半导体主体930的沟道部分939耦合到特定电势。

[0119] 主体线748和电容器728可以耦合到垂直晶体管926的在z方向上的相对端部。例如,主体线748可以耦合到垂直晶体管926的上端部,而电容器728可以耦合到垂直晶体管926的下端部,如图9A中所示。在一些实施方式中,位线923在z方向上在电容器728与主体线748之间,因为位线923与半导体主体930的突出部954的侧面接触,而主体线748与突出部954的上端部接触。在一些实施方式中,电容器728在z方向上在键合界面106与垂直晶体管926之间,并且字线934在z方向上在键合界面106与位线923之间。上文描述的并且在图9A中描绘的3D存储器器件900的第二半导体结构104中的各种部件的相对空间关系可以通过如下工艺得到:如下文关于制造工艺详细描述的第一半导体结构102与第二半导体结构104之间的面对面键合工艺,以及用于形成突出部954、位线923和主体线748的背侧工艺,所述工艺使得能够设计具有减少的浮体效应的垂直晶体管926。

[0120] 如图9A中所示,在一些实施方式中,电容器728包括在垂直晶体管926的源极或漏极938下方并且耦合到(例如,在半导体主体930的基部956的下端部处)源极或漏极938的第一电极742。电容器728还可以包括与第一电极742接触的电容器电介质744以及与电容器电介质744接触的第二电极746。也就是说,电容器电介质744可以夹在电极742和746之间。在一些实施方式中,每个第一电极742耦合到同一DRAM单元724中的相应垂直晶体管926的源极或漏极938,而所有第二电极746是耦合到地(例如,公共地)的公共板的部分。尽管图9A中未示出,但是应当理解,第二半导体结构104还可以包括与第二电极746的公共板接触的电容器触点,以用于将电容器728的第二电极746耦合到外围电路712或直接耦合到地。

[0121] 应当理解,电容器728的结构和配置不限于图9A中叉指式电容器(又被称为指状电容器)示例,并且可以包括任何合适的结构和配置,例如平面电容器、堆叠电容器、多鳍电容器、圆柱电容器、沟槽电容器或衬底-平板电容器。在一些实施方式中,电容器电介质744包括电介质材料,例如,氧化硅、氮化硅或高k电介质,高k电介质包括但不限于 $A1_20_3$ 、 $Hf0_2$ 、 $Ta_20_5$ 、 $Zr0_2$ 、 $Ti0_2$ 、或其任何组合。应当理解,在一些示例中,电容器728可以是在FRAM单元中使用的铁电电容器,并且电容器电介质744可以由具有铁电材料(例如,PZT或SBT)的铁电层代替。在一些实施方式中,电极742和746包括导电材料,导电材料包括但不限于W、Co、Cu、A1、TiN、TaN、多晶硅、硅化物或其任何组合。

[0122] 尽管图9中未示出,但是应当理解,在一些示例中,第二半导体结构104还可以包括在主体线748上方的焊盘引出互连层(例如,图1A中的焊盘引出互连层108)。焊盘引出互连层可以包括在一个或多个ILD层中的互连,例如,接触焊盘。焊盘引出互连层和互连层722可以形成在DRAM单元724的相对侧面上。根据一些实施方式,垂直晶体管926垂直地设置在电容器728与焊盘引出互连层之间。在一些实施方式中,焊盘引出互连层中的互连可以在3D存储器器件900与外部电路之间传递电信号,例如,以用于焊盘引出目的。还应当理解,3D存储器器件的焊盘引出不限于来自具有DRAM单元724的第二半导体结构104,并且可以来自具有外围电路712的第一半导体结构102。例如,如图1B中所示,3D存储器器件101可以包括在第一半导体结构102中的焊盘引出互连层。

[0123] 如上文所述,根据本公开的一些方面,存储器单元可以包括多个存储单元(例如,

电容器、铁电电容器或PCM元件),例如,1TnC或nTnC DRAM单元或FRAM单元。多个电容器(包括铁电电容器)可以垂直堆叠,以在蚀刻高纵横比电容器孔的当前制造极限之下进一步增加电容密度、单元密度和/或在单个存储器单元中实现多位信息存储。例如,图10A示出了根据本公开的一些方面的包括垂直晶体管和堆叠存储单元的另一3D存储器器件1000的截面的侧视图。应当理解,图10A仅用于说明性目的,并且实际上可以不必反映实际器件结构(例如,互连)。作为上文关于图1A描述的3D存储器器件100的一个示例,3D存储器器件1000是包括第一半导体结构102和堆叠在第一半导体结构102之上的第二半导体结构104的键合芯片。根据一些实施方式,第一半导体结构102和第二半导体结构104在它们之间的键合界面106处接合。如图10A中所示,第一半导体结构102可以包括衬底110,衬底110可以包括硅(例如,单晶硅、c-Si)、SiGe、GaAs、Ge、SOI或任何其他合适的材料。

[0124] 第一半导体结构102可以包括衬底110上的外围电路712。在一些实施方式中,外围电路712包括多个晶体管714(例如,平面晶体管和/或3D晶体管)。沟槽隔离(例如,STI)和掺杂区(例如,晶体管714的阱、源极和漏极)也可以形成在衬底110上或衬底110中。

[0125] 在一些实施方式中,第一半导体结构102还包括在外围电路712上方的互连层716,以向和从外围电路712传递电信号。互连层716可以包括多个互连,包括横向互连线和VIA触点。互连层716还可以包括一个或多个ILD层,在ILD层中可以形成互连线和过孔触点。也就是说,互连层716可以包括多个ILD层中的互连线和过孔触点。在一些实施方式中,外围电路712通过互连层716中的互连彼此耦合。互连层716中的互连可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以由电介质材料形成,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。

[0126] 如图10A中所示,第一半导体结构102还可以包括在键合界面106处并且在互连层716和外围电路712上方的键合层718。键合层718可以包括键合触点719和对键合触点719进行电隔离的电介质。键合触点719可以包括导电材料,例如Cu。键合层718的剩余区域可以由电介质材料(例如,氧化硅)形成。键合层718中的键合触点719和周围电介质可以用于混合键合。类似地,如图10A中所示,第二半导体结构104也可以包括在键合界面106处并且在第一半导体结构102的键合层718上方的键合层720。键合层720可以包括键合触点721和对键合触点721进行电隔离的电介质。键合触点721可以包括导电材料,例如Cu。键合层720的剩余区域可以由电介质材料(例如,氧化硅)形成。键合层720中的键合触点721和周围电介质可以用于混合键合。根据一些实施方式,键合触点721在键合界面106处与键合触点719接触。

[0127] 第二半导体结构104可以在键合界面106处以面对面的方式键合在第一半导体结构102的顶部上。在一些实施方式中,作为混合键合的结果,键合界面106设置在键合层720与718之间,混合键合是直接键合技术(例如,在不使用中间层(例如,焊料或粘合剂)的情况下在表面之间形成键合)并且可以同时获得金属-金属键合和电介质-电介质键合。在一些实施方式中,键合界面106是键合层720和718相遇并且键合的位置。实际上,键合界面106可以是具有一定厚度的层,其包括第一半导体结构102的键合层718的顶表面和第二半导体结构104的键合层720的底表面。

[0128] 在一些实施方式中,第二半导体结构104还包括在键合层720上方的互连层722,以传递电信号。互连层722可以包括多个互连,例如MEOL互连和BEOL互连。在一些实施方式中,

互连层722中的互连还包括局部互连,例如位线触点(未示出)、板线触点1007、字线触点727和主体线触点751。互连层722还可以包括一个或多个ILD层,互连线和过孔触点可以形成在ILD层中。互连层722中的互连可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以用电介质材料形成,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。在一些实施方式中,外围电路712包括字线驱动器/行解码器,字线驱动器/行解码器通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的字线触点727。在一些实施方式中,外围电路712包括位线驱动器/列解码器,位线驱动器/列解码器通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的位线触点。在一些实施方式中,外围电路712包括电压源或地,电压源或地通过键合层720和718中的键合触点721和719以及互连层716耦合到互连层722中的主体线触点751。

[0129] 在一些实施方式中,第二半导体结构104包括FRAM器件,其中,存储器单元在互连层722和键合层720上方以FRAM单元1024(例如,图5B中的FRAM单元502的示例)的阵列的形式提供。应当理解,图10A中的3D存储器器件1000的截面可以是沿字线方向(x方向)截取的,并且在x方向上横向延伸的一条字线734可以耦合到一行FRAM单元1024。每个FRAM单元1024可以包括垂直晶体管726(例如,图2中的垂直晶体管210的示例)和耦合到垂直晶体管726的多个垂直堆叠的铁电电容器1028(例如,图2中的存储单元212的示例)。FRAM单元1024可以在由一个晶体管和多个铁电电容器组成的1TnC配置中(即,1TnC单元)。应当理解,FRAM单元1024可以是任何合适的配置,例如,nTnC等。

[0130] 垂直晶体管726可以是用于对相应FRAM单元1024进行开关的MOSFET。在一些实施方式中,垂直晶体管726包括垂直(在z方向上)延伸的半导体主体730(即,其中可以形成多个沟道的有源区)以及与半导体主体730的一个或多个侧面接触的栅极结构736。在其中垂直晶体管726是GAA垂直晶体管的一些实施方式中,半导体主体730具有立方体形状或者圆柱体形状,并且栅极结构736与半导体主体730的所有侧面接触,即,在平面图中完全地包围半导体主体730。在其中垂直晶体管726是三栅极垂直晶体管、双栅极垂直晶体管或单栅极垂直晶体管的一些实施方式中,半导体主体730具有立方体形状或圆柱体形状,并且栅极结构736与半导体主体730的一个侧面或一些侧面(而非所有侧面)接触,即,在平面图中部分地包围半导体主体730。根据一些实施方式,栅极结构736包括栅极电极734以及至少在字线方向上横向地在栅极电极734与半导体主体730之间的栅极电介质732。例如,对于具有圆柱体形状的半导体主体730,半导体主体730、栅极电介质732和栅极电极734可以以此顺序从垂直晶体管726的中心径向设置。在一些实施方式中,栅极电介质732围绕并且接触半导体主体730,并且栅极电极734围绕并且接触栅极电介质732。

[0131] 在一些实施方式中,栅极电介质732包括电介质材料,例如氧化硅、氮化硅或高k电介质,高k电介质包括但不限于 $A1_20_3$ 、 $Hf0_2$ 、 $Ta_20_5$ 、 $Zr0_2$ 、 $Ti0_2$ 或其任何组合。在一些实施方式中,栅极电极734包括导电材料,导电材料包括但不限于W、Co、Cu、A1、TiN、TaN、多晶硅、硅化物或其任何组合。在一些实施方式中,栅极电极734包括多个导电层,例如,TiN层之上的W层。在一个示例中,栅极结构736可以是"栅极氧化物/栅极多晶硅"栅极,其中,栅极电介质732包括氧化硅,并且栅极电极734包括掺杂多晶硅。在另一示例中,栅极结构736可以是HKMG,其中,栅极电介质732包括高k电介质,并且栅极电极734包括金属。

[0132] 如图10A中所示,在一些实施方式中,半导体主体730在垂直方向(z方向)上具有两个端部(上端部和下端部),并且两个端部在垂直方向(z方向)上分别延伸超出栅极电极/字线734进入到ILD层中。也就是说,半导体主体730可以具有比栅极电极/字线734的垂直尺寸(例如,在z方向上)大的垂直尺寸(例如,深度),并且半导体主体730的上端部和下端部都不与栅极电极/字线734的相应端部齐平。因此,可以避免位线723与字线/栅极电极734之间或者字线/栅极电极734与电容器728之间的短路。

如图10和图7B中所示,从掺杂角度,即从半导体主体730的特定部分是否被掺杂或 其掺杂剂类型的角度来看,垂直晶体管726的半导体主体730可以包括源极和漏极(两者均 称为738,因为它们的位置可以互换)以及沟道部分739。在一个示例中,半导体主体730的耦 合到电容器728的下端部可以被完全掺杂,以形成源极和漏极738中的一者(例如,垂直晶体 管726的源极),而半导体主体730的远离电容器728的上端部可以被部分掺杂,以形成源极 和漏极738中的另一者(例如,垂直晶体管726的漏极)。因此,半导体主体730的剩余未掺杂 部分可以变为沟道部分739。在另一示例中,半导体主体730的耦合到电容器728的下端部可 以用(一种或多种)N型掺杂剂完全掺杂,以形成源极和漏极738中的一者(例如,垂直晶体管 726的源极),而半导体主体730的远离电容器728的上端部可以用(一种或多种)N型掺杂剂 部分掺杂,以形成源极和漏极738中的另一者(例如,垂直晶体管726的漏极)。因此,半导体 主体730的剩余部分可以变为沟道部分739,沟道部分739可以用(一种或多种)P型掺杂剂掺 杂。在又一示例中,半导体主体730的耦合到电容器728的下端部可以用(一种或多种)P型掺 杂剂完全掺杂,以形成源极和漏极738中的一者(例如,垂直晶体管726的源极),而半导体主 体730的远离电容器728的上端部可以用(一种或多种)P型掺杂剂部分掺杂,以形成源极和 漏极738中的另一者(例如,垂直晶体管726的漏极)。因此,半导体主体730的剩余部分可以 变为沟道部分739,沟道部分739可以用(一种或多种)N型掺杂剂掺杂。在一些实施方式中, 从形状角度,即从半导体主体730的不同部分之间的相对尺寸和几何关系的角度来看,半导 体主体730具有基部756和突出部754,如图7B中所示。例如,基部756可以具有比突出部754 大的横向尺寸。突出部754可以从基部756的内部完全突出,即,突出部754的所有侧面在平 面图中都在基部756的边界内。在一些实施方式中,基部756面向字线/栅极电极734,并且突 出部754面向位线723。

[0134] 源极和漏极738中的一者(例如,在图10A中的下端部处)可以形成在基部756的一个端部(例如,图10A中的下端部)上。源极和漏极738中的另一者(例如,在图10A中的上端部处)可以形成在半导体主体730的突出部754的一个或多个侧面上。在一些实施方式中,如图10和图7B中所示,源极和漏极738中的远离铁电电容器1028的一者(例如,FRAM单元1024的漏极)形成在突出部754的所有侧面上。沟道部分739可以形成在半导体主体730的基部756和突出部754中。也就是说,半导体主体730的基部756和突出部754两者都可以具有未掺杂的或者用与源极和漏极738不同类型的掺杂剂掺杂的部分,从而变为沟道部分739。如图10和图7B中所示,根据一些实施方式,与基部756的被掺杂以变为源极/漏极738的部分的下端部(即底部)不同,突出部754的上端部(即顶部)未用与源极和漏极738相同类型的掺杂剂掺杂以变为源极/漏极738的部分,而是作为沟道部分739的部分。如图7B中所示,根据一些实施方式,栅极结构736的栅极电介质732与半导体主体730的基部756接触,但是未进一步延伸以与半导体主体730的突出部754接触。换句话说,栅极电介质732可以与半导体主体730

的突出部754分离。

[0135] 在一些实施方式中,半导体主体730包括半导体材料,例如,单晶硅、多晶硅、非晶硅、Ge、任何其他半导体材料或其任何组合。在一个示例中,半导体主体730可以包括单晶硅,并且半导体主体730的沟道部分739可以包括未掺杂的单晶硅或者具有与源极和漏极738不同类型的掺杂剂的掺杂的单晶硅。源极和漏极738可以掺杂有期望掺杂水平的N型掺杂剂(例如,P或As)或者P型掺杂剂(例如,B或Ga)。在一些实施方式中,源极和漏极738掺杂有N型掺杂剂(例如,P或As),并且沟道部分739是未掺杂/本征的,或者掺杂有P型掺杂剂(例如,B或Ga)。

[0136] 如上文所述,由于栅极电极734可以是字线的部分或者在字线方向上延伸作为字线,因此尽管图10A中未直接示出,但是3D存储器器件1000的第二半导体结构104还可以包括各自在字线方向(x方向)上延伸的多条字线。每条字线734可以耦合到一行FRAM单元1024。也就是说,位线723和字线734可以在两个垂直的横向方向上延伸,并且垂直晶体管726的半导体主体730可以在与位线723和字线734延伸的两个横向方向垂直的垂直方向上延伸。根据一些实施方式,字线734与字线触点727接触。在一些实施方式中,字线734包括导电材料,导电材料包括但不限于W、Co、Cu、Al、TiN、TaN、多晶硅、硅化物或其任何组合。在一些实施方式中,字线734包括多个导电层,例如,TiN层之上的W层。

[0137] 如图10A中所示,3D存储器器件1000的第二半导体结构104还可以包括各自在位线方向上延伸的多条位线723。每条位线723可以耦合到一列FRAM单元1024。在一些实施方式中,位线723耦合到源极和漏极738中的远离铁电电容器1028的一者(例如,垂直晶体管726的漏极)。例如,如图7B中所示,位线723可以与形成在半导体主体730的突出部754的所有侧面上的源极/漏极738接触,但是通过源极/漏极738与半导体主体730的沟道部分739分离。也就是说,根据一些实施方式,位线723不与半导体主体730的其中形成垂直晶体管726的沟道的沟道部分739接触,以抑制浮体效应。

[0138] 如图10A中所示,3D存储器器件1000的第二半导体结构104还可以包括主体线748,主体线748横向延伸(在位线方向和/或字线方向上)并且耦合到半导体主体730的沟道部分739。主体线748还可以耦合到主体线触点751,主体线触点751进而可以通过互连层722和716以及键合层718和720耦合到第一半导体结构102中的外围电路712。结果,半导体主体730的沟道部分739可以例如经由主体线748、主体线触点751以及互连层722和716及键合层718和720中的任何其他合适的互连,通过外围电路712中的电压源或地而耦合到特定电势,使得半导体主体730的沟道部分739中的沟道电荷可以在3D存储器器件1000的操作期间被释放,以减轻浮体效应和所产生的问题。应当理解,在一些示例中,主体线748可以耦合到不在外围电路712中的电压源或地,只要半导体主体730中的沟道的电荷可以被耗尽。

[0139] 如上文所述,半导体主体730的突出部754的上端部(顶部)未被源极/漏极738覆盖,使得主体线748可以与半导体主体730的沟道部分739接触。在一些实施方式中,突出部754的上端部延伸超出位线723,使得与突出部754的上端部接触的主体线748与位线723分离,以避免短路。在一些实施方式中,主体线748包括与半导体主体730的沟道部分739接触的多晶硅层750,以降低主体线748与半导体主体730之间的接触电阻。在一些实施方式中,主体线748还包括与多晶硅层750接触的金属层752(例如,W或Cu层),以降低主体线748的薄层电阻。应当理解,在其他示例中,主体线748的结构和/或材料可以变化,只要主体线748可

以以合理的接触电阻和薄层电阻将半导体主体730的沟道部分739耦合到特定电势。

[0140] 主体线748和铁电电容器1028可以耦合到垂直晶体管726的在z方向上的相对端部。例如,主体线748可以耦合到垂直晶体管726的上端部,而铁电电容器1028可以耦合到垂直晶体管726的下端部,如图10A中所示。在一些实施方式中,位线723在z方向上在铁电电容器1028与主体线748之间,因为位线723与半导体主体730的突出部754的侧面接触,而主体线748与突出部754的上端部接触。在一些实施方式中,铁电电容器1028在z方向上在键合界面106与垂直晶体管726之间,并且字线734在z方向上在键合界面106与位线723之间。上文描述的并且在图10A中描绘的3D存储器器件1000的第二半导体结构104中的各种部件的相对空间关系可以通过如下工艺得到:如下文关于制造工艺详细描述的第一半导体结构102与第二半导体结构104之间的面对面键合工艺,以及用于形成突出部754、位线723和主体线748的背侧工艺,所述工艺使得能够设计具有减少的浮体效应的垂直晶体管726。

[0141] 应当理解,图10A中的垂直晶体管726和位线723仅是出于说明性目的提供的,并且可以被本文公开的任何其他合适的对应物(例如,图9A中的垂直晶体管926和位线923)代替。还应当理解,3D存储器器件1000中的垂直晶体管可以是任何其他合适的垂直晶体管,只要垂直晶体管包括垂直延伸的半导体主体,并且半导体主体的一个端部可以耦合到多个垂直堆叠存储单元(例如,本文公开的铁电电容器1028)。

如图10A和图10B中所示,对于每个FRAM单元1024(图5B中的FRAM单元502的示例), 第二半导体结构104可以包括垂直(在z方向上)堆叠的并且耦合到相应垂直晶体管726(图 5B中的晶体管504的示例)的多个铁电电容器1028(例如,图5B中的铁电电容器506-1、506-2、…、506-n的示例)。第二半导体结构104还可以包括各自横向(即,垂直于垂直方向)延伸 并且耦合到铁电电容器1028中的相应一个铁电电容器的多条板线1047(图5B中的板线508-1、508-2、…、508-n的示例)。如图10B的放大图中所示,根据一些实施方式,每个铁电电容器 1028包括第一电极1046、第二电极1042以及在字线方向和/或位线方向上横向地夹在第一 电极1046与第二电极1042之间的铁电区段1044(存储单元的存储区段的示例)。在一些实施 方式中,同一FRAM单元1024的堆叠铁电电容器1028的第二电极1042是耦合到半导体主体 730的下端部(例如,源极/漏极738)的连续电极层1006的部分,并且同一FRAM单元1024的堆 **叠铁电电容器1028的铁电区段1044是在电极层1006之上的连续铁电层1008(存储单元的存** 储层的示例)的部分。电极层1006可以包括导电材料,例如,金属。在一些实施方式中,每个 第一电极1046和相应板线1047是相应连续导电层1047的部分。也就是说,与栅极电极/字线 734类似,第一电极1046可以被视为板线1047的部分,或者板线1047可以被视为第一电极 1046的延伸。另一方面,根据一些实施方式,同一FRAM单元1024的堆叠铁电电容器1028的第 一电极1046在垂直方向上彼此间隔开。两个相邻的第一电极1046(和导电层1047)可以通过 电介质层1045中的相应一个电介质层分离。对于具有圆柱形形状的电极层1006,电极层 1006、铁电层1008和导电层1047可以以此顺序从电极层1006的中心径向设置。在一些实施 方式中,铁电层1008围绕并且接触电极层1006,并且导电层1047围绕并且接触铁电层1008。 如图10A中所示,堆叠铁电电容器1028可以以电极层1006和铁电层1008的形式提 供,电极层1006和铁电层1008垂直(在z方向)延伸穿过包括交错的导电层1047和电介质层 1045的堆叠体结构1002。在一些实施方式中,3D存储器器件1000的第二半导体结构104还包 括具有多个对的堆叠体结构1002,每个对包括导电层1047和电介质层1045。每个导电层

1047和电介质层1045可以在字线方向和/或位线方向上横向延伸。堆叠体结构1002可以在z方向上设置在键合界面106与垂直晶体管726之间。字线734可以在z方向上垂直设置在堆叠体结构1002与位线723之间。根据一些实施方式,堆叠体结构1002中的堆叠并且交错的导电层1047和电介质层1045在垂直方向上交替。堆叠体结构1002中的导电层1047和电介质层1045对的数量可以确定每个FRAM单元1024中的堆叠铁电电容器1028的数量。因此,FRAM单元1024的电容可以垂直按比例增加,而不会增加平面面积和增加工艺复杂性(例如,蚀刻高纵横比电容器孔)。导电层1047可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、多晶硅、掺杂硅、硅化物或其任何组合。在一些实施方式中,每个导电层1047包括金属层,例如,W层。

[0144] 如上文所述,导电层1047可以包括板线1047和与铁电层1008接触的第一电极1046。在一些实施方式中,电介质层1045和导电层1047的边缘可以限定堆叠体结构1002的阶梯结构1004,阶梯结构1004包括用于板线互连(例如,着陆板线触点1007)的多个阶梯(级)。导电层/板线1047可以横向延伸,终止在阶梯结构1004的相应阶梯处。在一些实施方式中,阶梯结构1004的每两个相邻阶梯在横向方向(例如,图10A中的x方向)上偏移一定距离。因此,每个偏移可以形成用于在垂直方向上与板线触点1007互连的"着陆区域"。如图10A中所示,3D存储器器件1000的第二半导体结构104还可以包括在阶梯结构1004处分别与导电层1047接触的板线触点1007。因此,同一FRAM单元1024中的多个第一电极1046中的每个第一电极可以分别通过相应板线1047、相应板线触点1007、互连层722和716中的互连以及键合层720和718耦合到外围电路712。每个铁电电容器1028可以耦合到相应板线1047。

[0145] 如图10A中所示,3D存储器器件1000的第二半导体结构104还可以包括电极层1006和在电极层1006之上的铁电层1008。电极层1006和铁电层1008中的每者可以在z方向上延伸穿过堆叠体结构1002,以形成每个FRAM单元1024的垂直堆叠铁电电容器1028。在一些实施方式中,电极层1006是连续层并且包括多个第二电极1042,并且铁电层1008是连续层并且包括多个铁电区段1044。第一电极1046、第二电极1042和铁电区段1044可以形成用于每个FRAM单元1024的在垂直方向上堆叠的多个铁电电容器1028。电极层1006可以被同一FRAM单元1024的所有铁电电容器1028共享,并且用作用于将同一FRAM单元1024的每个铁电电容器1028耦合到相应垂直晶体管726的公共电极。电极层1006可以包括导电材料,导电材料包括但不限于W、Co、Cu、A1、多晶硅、掺杂硅、硅化物或其任何组合。在一些实施方式中,电极层1006包括金属层,例如,W层。

[0146] 应当理解,FRAM单元1024被示为具有多个垂直堆叠存储单元的存储器单元的示例,铁电电容器1028被示为垂直堆叠存储单元的示例。在一些示例中,存储器单元可以是DRAM单元,并且垂直堆叠存储单元可以是垂直堆叠电容器。还应当理解,铁电层1008被示为包括存储区段的存储层的示例,并且铁电区段1044被示为存储区段的示例。铁电层1008可以是包括铁电材料的存储层。在一些示例中,存储层可以包括电容器的电介质材料,例如,高k电介质。

[0147] 尽管图10A中未示出,但是应当理解,在一些示例中,第二半导体结构104还可以包括在主体线748上方的焊盘引出互连层(例如,图1A中的焊盘引出互连层108)。焊盘引出互连层可以包括在一个或多个ILD层中的互连,例如,接触焊盘。焊盘引出互连层和互连层722可以形成在FRAM单元1024的相对侧面上。根据一些实施方式,垂直晶体管726垂直地设置在

铁电电容器1028与焊盘引出互连层之间。在一些实施方式中,焊盘引出互连层中的互连可以在3D存储器器件1000与外部电路之间传递电信号,例如,以用于焊盘引出目的。还应当理解,3D存储器器件的焊盘引出不限于来自具有FRAM单元1024的第二半导体结构104,并且可以来自具有外围电路712的第一半导体结构102。例如,如图1B中所示,3D存储器器件101可以包括在第一半导体结构102中的焊盘引出互连层。

[0148] 如上文关于图6和图8所述,本文公开的存储器单元阵列可以以交叉点正交布局布置,交叉点正交布局具有4F2单元尺寸。根据本公开的一些方面,通过将布局从交叉点正交布局改为具有固定最小单元距离的交错布局,可以进一步减小存储器单元阵列的单位单元尺寸。例如,图11示出了根据本公开的一些方面的各自包括垂直晶体管的存储器单元1102的阵列的布局图。存储器单元1102可以包括包括垂直晶体管和耦合到垂直晶体管的一个或多个存储单元的任何合适的存储器单元,例如,本文公开的存储器单元。

[0149] 存储器单元1102的阵列可以以行和列布置。根据一些实施方式,存储器单元1102的每一行在字线方向(x方向)上延伸,并且存储器单元的每一列在位线方向(y方向)上延伸。也就是说,可以在位线方向上布置存储器单元1102的行,并且可以在字线方向上布置存储器单元1102的列。如图11所示,与交叉点正交布局相反,存储器单元1102的阵列可以以交错布局布置。例如,在平面图中,存储器单元1102的两个相邻行可以彼此交错的(不对准),并且存储器单元1102的两个相邻列也可以彼此交错(不对准)。

[0150] 如图11中所示,根据一些实施方式,一组四个存储器单元1102中的每一个存储器单元耦合到同一字线1104,该字线在位线方向(y方向)上形成在两个相邻缝隙结构1108之间。缝隙结构1108可以包括一种或多种电介质材料(例如,氧化硅或氮化硅),以在位线方向上分离相邻字线1104。在一些实施方式中,该组四个存储器单元1102中的每一个存储器单元耦合到四条位线1106中的相应一条位线。结果,尽管该组四个存储器单元共享同一字线1104,但是该组四个存储器单元1102中的每一个存储器单元可以由相应位线1106单独控制。换句话说,根据一些实施方式,特定字线1104和特定位线1106的组合对应于相应存储器单元1102。在一些实施方式中,耦合到同一字线1104的一组存储器单元1102可以包括在同一列中的n个存储器单元1102,其中,n是大于1的正整数,并且n个存储器单元1102可以分别耦合到n条位线1106,以实现对每个存储器单元1102的单独控制。换句话说,多条位线1106可以耦合到同一列中的存储器单元1102。结果,在同一列中存在耦合到同一字线1104的多个存储器单元的情况下,每条位线1106可以不完全地包围相应存储器单元1102的半导体主体(例如,具有图7A和图7B中所示的设计),而是可以部分地包围相应存储器单元1102的半导体主体(例如,具有图9A和图9B中所示的设计)。

[0151] 在图11的平面图中,每条位线1106可以通过相应位线触点1114耦合到相应存储器单元1102的源极/漏极1110,并且与相应存储器单元1102的半导体主体的沟道部分1112分离,沟道部分1112耦合到主体线(未示出)以减少浮体效应。应当理解,图11中所示的源极/漏极1110和沟道部分1112的设计仅用于说明性目的,并且在其他示例中可以变化,只要每个存储器单元1102的源极/漏极1110可以耦合到相应位线1106。如图11中所示,耦合到字线1104的一组四个存储器单元1102在本文中被称为"功能存储器单元",因为它们可以由字线1104和位线1106控制。相反,耦合到缝隙结构1108的存储器单元(图11中未示出)在本文中被称为"虚设存储器单元",因为其不能由字线1104控制。

[0152] 为了减小单位单元尺寸,存储器单元1102的交错布局被设计为使得任何存储器单元1102与其相邻存储器单元1102之间的最小单元距离保持相同。例如,如图11中所示,第一存储器单元A与在存储器单元A的同一列中的第二存储器单元B之间的最小距离D1可以与存储器单元A与相邻列中的第三存储器单元C之间的最小距离D2相同,即,D1=D2。两个存储器单元之间的距离是可以在平面图中的两个存储器单元的几何中心(例如,两个圆的圆心)之间测量的,如图11中所示。应当理解,对于特定存储器单元,在同一列或相邻列中可以存在多于一个的相邻存储器单元。因此,最小距离可以是存储器单元与同一列或相邻列中的最近存储器单元之间的距离,即,距不同相邻存储器单元的距离的最小值。

[0153] 如图11中所示,在一些示例中,最小距离D1/D2还可以与存储器单元B与存储器单元C之间的距离D3相同,即,D1=D2=D3。也就是说,根据一些实施方式,存储器单元A、B和C在平面图中分别设置在等边三角形( $\Delta$ )的顶点上。因此,图11中所示的存储器单元1102的交错布局还可以被称为"德尔塔"( $\Delta$ )布置。根据图11中所示的德尔塔布置,任何存储器单元1102与其相邻存储器单元1102之间的最小单元距离保持相同,使得能单位单元尺寸可以最小化。

[0154] 图12A-图12E示出了根据本公开的各个方面的各自包括垂直晶体管的存储器单元的各种阵列的布局图。图12A-图12E可以示出具有图11中公开的德尔塔布置的交错布局的各种示例。如图12A中所示,根据一些实施方式,每个缝隙结构1108具有在平面图中在字线方向(x方向)上延伸的直线形状,并且在位线方向(y方向)上分离两条相邻字线1104。因此,存储器单元可以包括多组功能存储器单元1202,并且每组功能存储器单元1202耦合到相应字线1104。在每组功能存储器单元1202内,功能存储器单元1202根据上文关于图11公开的德尔塔布置来布置,使得任何功能存储器单元1202与在同一组中(即,耦合到同一字线1104)的其相邻功能存储器单元1202之间的最小单元距离可以保持相同。图12A中公开的交错布局的单位单元尺寸可以减小到2.64F<sup>2</sup>(即,2.64F2单元尺寸)。

[0155] 然而,由于图12A中公开的交错布局不包括耦合到相邻组的功能存储器单元1202之间的缝隙结构1108的任何虚设存储器单元,因此德尔塔布置可能不适用于跨越相邻组的存储器单元。例如,在跨越缝隙结构1108的同一列中的分别在两个相邻组的功能存储器单元1202中的两个相邻功能存储器单元1202之间的距离可以不同于(例如,大于)每组功能存储器单元1202内的功能存储器单元1202的最小距离(例如,图11中的D1/D2/D3)。

[0156] 因此,为了进一步减小单位单元尺寸,如图12B中所示,可以引入一组或多组虚设存储器单元1204。在一些实施方式中,同一组的每个虚设存储器单元1204耦合到在平面图中具有直线形状的相应缝隙结构1108。在一些实施方式中,虚设存储器单元1204不耦合到任何字线1104或位线1106。结果,在图12B中所示的交错布局的一些列(例如,C1)中,在跨越其间的缝隙结构1108的同一列中的分别在两个相邻组的功能存储器单元1202中的两个相邻功能存储器单元1202之间的距离可以与每组功能存储器单元1202内的功能存储器单元1202的最小距离(例如,图11中的D1/D2/D3)相同;并且在一些列(例如,C2)中,虚设存储器单元1204与在同一列中的相邻组的功能存储器单元1202中的相邻功能存储器单元1202之间的距离也与该最小距离(例如,图11中的D1/D2/D3)相同。因此,通过将虚设存储器单元1204引入到图12B中的交错布局中,德尔塔布置可以适用于所有存储器单元1202和1204,甚至可以适用于跨越不同组的存储器单元1202和1204。图12B中公开的交错布局的单位单元

尺寸可以进一步减小到2.17F<sup>2</sup>(即,2.17F2单元尺寸)。

然而,与功能存储器单元1202不同,虚设存储器单元1204不能由字线1104和位线 1106控制以存储信息,并且因此,即使具有减小的单位单元尺寸,实际单元密度可能仍受虚 设存储器单元1204限制。因此,为了进一步增加实际单元密度,如图12C中所示,可以引入各 自具有蛇形形状的缝隙结构1208。在一些实施方式中,与具有直线形状的缝隙结构1108不 同,缝隙结构1208具有蛇形形状,以在遵循在相邻行之间的功能存储器单元1202的交错图 案。结果,即使没有引入虚设存储器单元1204,在图12C中所示的交错布局的每一列中,在跨 越其间的蛇形形状缝隙结构1208的同一列中的分别在两个相邻组的功能存储器单元1202 中的两个相邻功能存储器单元1202之间的距离可以与每组功能存储器单元1202内的功能 存储器单元1202的最小距离(例如,图11中的D1/D2/D3)相同。应当理解,图12C中所示的缝 隙结构1208的具体蛇形形状仅用于说明性目的,并且在其他示例中可以变化,只要该形状 遵循在相邻行之间功能存储器单元1202的交错图案,以允许在跨越缝隙结构1208的任何列 中的在两个相邻组中的两个相邻功能存储器单元1202之间的距离与最小距离相同。与图 12B中所示的交错布局类似,图12C中公开的交错布局的单位单元尺寸可以是2.17F<sup>2</sup>(即 2.17F2单元尺寸),因为德尔塔布置可以适用于所有功能存储器单元1202,甚至适用于跨越 不同组的功能存储器单元1202。与图12B中所示的交错布局相比,通过在图12C所示的交错 布局中消除虚设存储器单元1204,可以增加实际单元密度。

[0158] 如图12C中所示,蛇形形状缝隙结构1208和直线形状缝隙结构1108可以在交错布局中交替,即,在缝隙结构1108和1208中具有相同数量和比例(1/2)。然而,图12C中的交错布局的单位单元尺寸仍然受到直线形状缝隙结构1108的限制。因此,通过增加蛇形形状缝隙结构1208在所有缝隙结构1108和1208中的比例,即,通过减小直线形状缝隙结构1108的比例,可以进一步减小单位单元尺寸。例如,在图12D的交错布局中,三个蛇形形状缝隙结构1208可以布置在两个相邻直线形状缝隙结构1108之间,从而使蛇形形状缝隙结构1208在所有缝隙结构1108和1208中的比例增加到3/5。在图12E中所示的一般情况下,假设k个蛇形形状缝隙结构1208可以布置在两个相邻直线形状缝隙结构1108之间,则蛇形形状缝隙结构1208在所有缝隙结构1108和1208中的比例被设置为k/(k+2),其中,k是正整数。

[0159] 图20示出了根据本公开的一些方面的具有存储器器件的系统2000的框图。系统2000可以是移动电话、台式计算机、膝上型计算机、平板计算机、车辆计算机、游戏控制台、打印机、定位设备、可穿戴电子设备、智能传感器、虚拟现实(virtual reality,VR)设备、增强现实(argument reality,AR)设备或其中具有储存器的任何其他合适的电子设备。如图20中所示,系统2000可以包括主机2008和具有一个或多个存储器器件2004和存储器控制器2006的存储器系统2002。主机2008可以是电子设备的处理器,例如中央处理单元(central processing unit,CPU),或者片上系统(system-on-chip,SoC),例如应用处理器(application processor,AP)。主机2008可以被配置为向存储器器件2004发送数据或从存储器器件2004接收数据。

[0160] 存储器器件2004可以是本文所公开的任何存储器器件,例如3D存储器器件100、101和103,存储器器件200、600和800以及3D存储器器件700、900和1000。在一些实施方式中,存储器器件2004包括存储器单元阵列,每个存储器单元包括垂直晶体管,如上文详细描述。

[0161] 根据一些实施方式,存储器控制器2006耦合到存储器器件2004和主机2008,并且 被配置为控制存储器器件2004。存储器控制器2006可以管理存储在存储器器件2004中的数 据,并且与主机2008通信。存储器控制器2006可以被配置为控制存储器器件2004的操作,例 如读取、写入和刷新操作。存储器控制器2006还可以被配置为管理关于存储或要存储在存 储器器件2004中的数据的各种功能,包括但不限于刷新和定时控制、命令/请求转译、缓冲 和调度以及功率管理。在一些实施方式中,存储器控制器2006还被配置为确定计算机系统 可以使用的最大存储器容量、存储器库(memory bank)的数量、存储器类型和速度、存储器 颗粒数据深度和数据宽度、以及其他重要参数。也可以由存储器控制器2006执行任何其他 合适的功能。存储器控制器2006可以根据特定通信协议与外部设备(例如,主机2008)通信。 例如,存储器控制器2006可以通过各种接口协议中的至少一种接口协议与外部设备通信, 接口协议例如USB协议、MMC协议、外围部件互连(peripheral component interconnection, PCI) 协议、PCI高速 (PCI-E) 协议、高级技术附件 (advanced technology attachment, ATA)协议、串行ATA协议、并行ATA协议、小型计算机小型接口(small computer small interface, SCSI)协议、增强型小型磁盘接口(enhanced small disk interface, ESDI)协议、集成驱动电子(integrated drive electronics, IDE)协议、火线协议等。

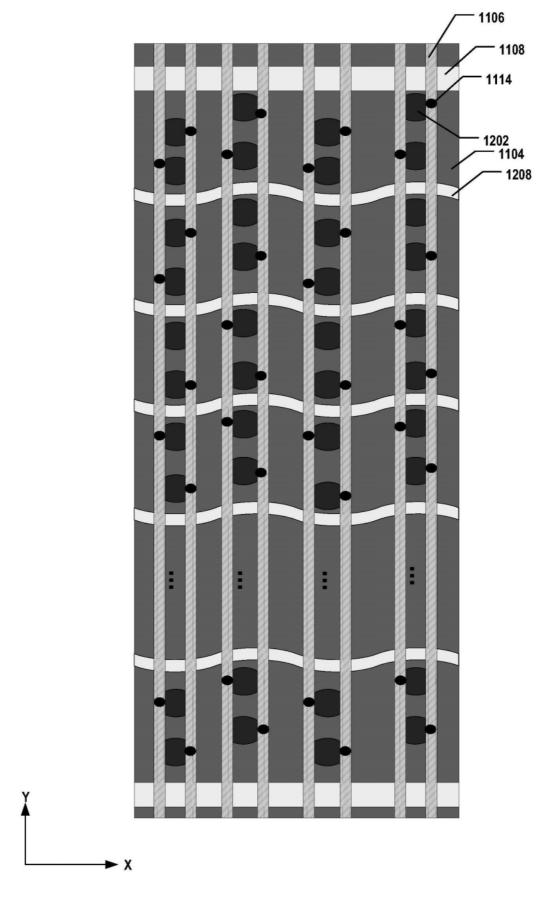

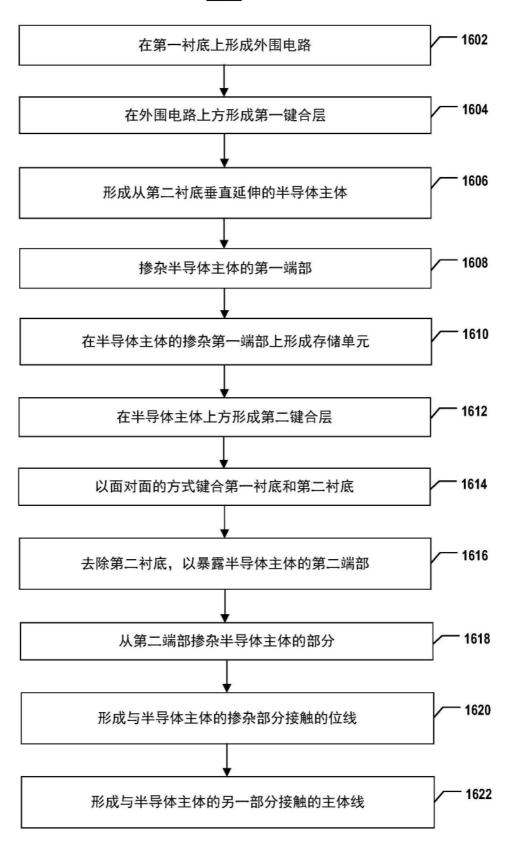

[0162] 图13A-图13M示出了根据本公开的一些方面的用于形成包括垂直晶体管的3D存储器器件的制造工艺。图14A-图14M示出了根据本公开的一些方面的用于形成包括垂直晶体管的另一3D存储器器件的制造工艺。图16示出了根据本公开的一些方面的用于形成包括垂直晶体管的3D存储器器件的方法1600的流程图。图13A-图13M中所示的3D存储器器件的示例包括图7A中所示的3D存储器器件700。图14A-图14M中所示的3D存储器器件的示例包括图9A中所示的3D存储器器件900。将一起描述图13A-图13M、图14A-图14M和图16。应当理解,方法1600中所示的操作不是详尽无遗的,并且也可以在所示操作中的任何操作之前、之后或之间执行其他操作。此外,一些操作可以同时执行,或者以与图16中所示的不同的顺序执行。

[0163] 参考图16,方法1600开始于操作1602,在操作1602中,在第一衬底上形成外围电路。第一衬底可以包括硅衬底。在一些实施方式中,在外围电路上方形成互连层。互连层可以包括在一个或多个ILD层中的多个互连。

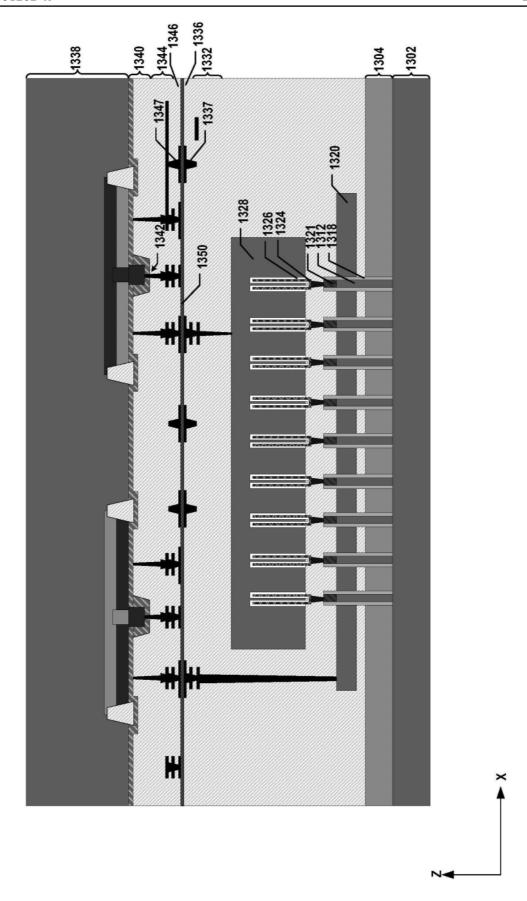

[0164] 如图13H中所示,在硅衬底1338上形成多个晶体管1342。晶体管1342可以通过多种工艺形成,所述工艺包括但不限于光刻、干法/湿法蚀刻、薄膜沉积、热生长、注入、化学机械抛光(chemical mechanical polishing,CMP)和任何其他合适的工艺。在一些实施方式中,通过离子注入和/或热扩散在硅衬底1338中形成掺杂区,掺杂区例如用作晶体管1342的源极和漏极。在一些实施方式中,也通过湿法/干法蚀刻和薄膜沉积在硅衬底1338中形成隔离区(例如,STI)。晶体管1342可以在硅衬底1338上形成外围电路1340。

[0165] 如图13H中所示,可以在具有晶体管1342的外围电路1340上方形成互连层1344。互连层1344可以包括在多个ILD层中的MEOL互连和/或BEOL互连以与外围电路1340进行电连接。在一些实施方式中,互连层1344包括多个ILD层和以多种工艺形成在ILD层中的互连。例如,互连层1344中的互连可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于化学气相沉积(chemical vapor deposition,CVD)、物理气相沉积(physical vapor deposition,PVD)、原子层沉积(atomic layer deposition,ALD)、电镀、

无电镀或其任何组合。形成互连的制造工艺还可以包括光刻、CMP、湿法/干法蚀刻或任何其他合适的工艺。ILD层可以包括通过一种或多种薄膜沉积工艺沉积的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。图13H中示出的ILD层和互连可以被统称为互连层1344。

[0166] 方法1600进行至操作1604,如图16中所示,在操作1604中,在外围电路(和互连层)上方形成第一键合层。第一键合层可以包括第一键合触点。如图13H中所示,在互连层1344和外围电路1340上方形成键合层1346。键合层1346可以包括被电介质围绕的多个键合触点1347。在一些实施方式中,通过一种或多种薄膜沉积工艺在互连层1344的顶表面上沉积电介质层(例如,ILD层),薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,电介质层中的电介质材料的光刻和干法/湿法蚀刻)首先图案化穿过电介质层的接触孔,可以形成穿过电介质层并且与互连层1344中的互连接触的键合触点1347。接触孔可以用导体(例如,Cu)填充。在一些实施方式中,填充接触孔包括在沉积导体之前沉积阻挡层、粘合层和/或晶种层。

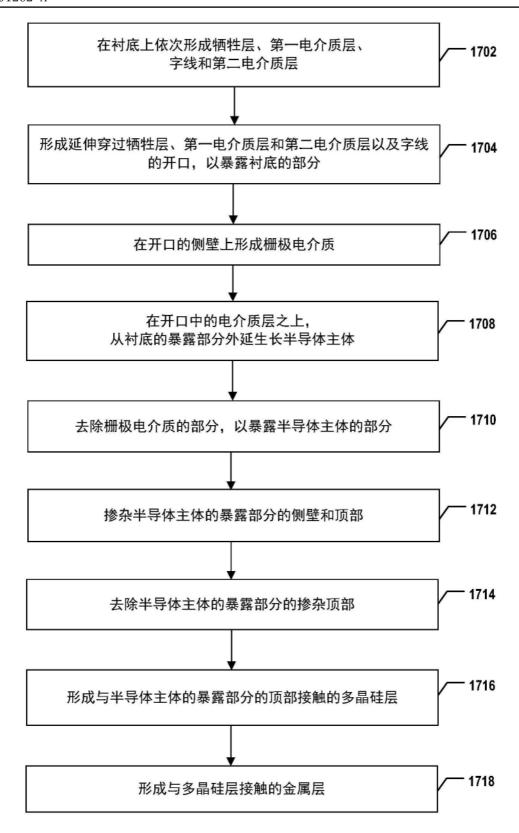

[0167] 方法1600进行至操作1606,如图16中所示,在操作1606中,形成从第二衬底垂直延伸的半导体主体。第二衬底可以包括硅衬底。为了形成半导体主体,在衬底上方形成夹在两个电介质层之间的字线,形成延伸穿过字线和电介质层的开口,以暴露衬底的部分,并且在开口中从衬底的暴露部分外延生长半导体主体。为了形成半导体主体,在外延生长半导体主体之前,在开口的侧壁上形成栅极电介质。

[0168] 在一些实施方式中,垂直延伸的半导体主体从第二衬底的第一侧(例如,正侧)形成,并且被栅极电介质围绕。为了形成半导体主体,在图17中的操作1702处,在衬底上依次形成牺牲层、第一电介质层、字线和第二电介质层。牺牲层可以包括氮化硅,第一电介质层和第二电介质层可以包括氧化硅,并且字线可以包括金属。

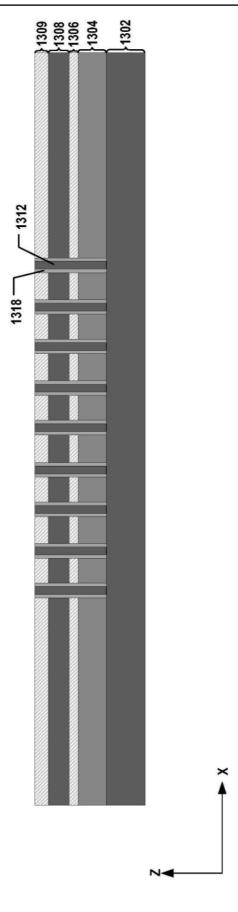

[0169] 如图13A中所示,牺牲层1304、第一电介质层1306、字线1308和第二电介质层1309依次形成在硅衬底1302上。在一些实施方式中,使用一种或多种薄膜沉积工艺将氮化硅、氧化硅、金属(例如,W)和氧化硅依次沉积到硅衬底1302上,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。应当理解,第一电介质层1306和第二电介质层1309的材料可以包括氧化硅以外的任何合适的电介质材料,并且字线1308的材料可以包括金属以外的任何合适的导电材料。还应当理解,牺牲层1304的牺牲材料不限于氮化硅,并且可以包括与第一电介质层1306和硅衬底1302的材料不同的任何合适的牺牲材料。硅衬底1302可以是本征的(即,未掺杂的)或者掺杂有第一类型的掺杂剂,例如,P型掺杂剂(例如,B或Ga)。

[0170] 在图17中的操作1704处,形成延伸穿过牺牲层、第一电介质层、字线和第二电介质层的开口,以暴露衬底的部分。如图13A中所示,形成开口1310的阵列,每个开口垂直(在z方向上)延伸穿过第二电介质层1309、字线1308、第一电介质层1306和牺牲层1304的堆叠体以达到硅衬底1302。结果,可以从开口1310暴露硅衬底1302的部分。在一些实施方式中,执行光刻工艺,以例如基于字线和位线的设计,使用蚀刻掩模(例如,光致抗蚀剂掩模)图案化开口1310的阵列,并且执行一种或多种干法蚀刻和/或湿法蚀刻工艺(例如,反应离子蚀刻(reactive ion etch,RIE)),以蚀刻穿过第二电介质层1309、字线1308、第一电介质层1306和牺牲层1304的开口1310,直到被硅衬底1302停止。

[0171] 在图17中的操作1706处,在开口的侧壁上形成栅极电介质。如图13B中所示,分别

在开口1310的侧壁上形成栅极电介质1318。为了形成栅极电介质1318,可以使用一种或多种薄膜沉积工艺将栅极电介质层(例如,氧化硅层或高k电介质层)沉积到开口1310中,以覆盖每个开口1310的侧壁和底部,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合的。然后,可以使用干法蚀刻和/或湿法蚀刻(例如,RIE)对栅极电介质层进行部分蚀刻,以去除栅极电介质层在开口1310的底部上的部分,以仍然从开口1310暴露硅衬底1302的部分。因此,栅极电介质层的在开口1310的侧壁上的剩余部分可以变为栅极电介质1318。因此,栅极电介质1318以及字线1308的与栅极电介质1318接触的部分可以变为要形成的垂直晶体管的栅极结构。

在图17中的操作1708处,在开口中的栅极电介质之上,从衬底的暴露部分外延生 [0172] 长半导体主体。如图13C中所示,分别在开口1310中的栅极电介质1318(图13B中所示)之上 形成半导体主体1312的阵列。半导体主体1312可以从相应开口1310中的硅衬底1302的相应 暴露部分,外延生长在相应栅极电介质1318之上。用于外延生长半导体主体1312的制造工 艺可以包括但不限于气相外延(vapor-phase epitaxy, VPE)、液相外延(liquid-phase epitaxy,LPE)、分子束外延(molecular-beam epitaxy,MPE)或者其任何组合。外延可以从 开口1310中的硅衬底1302的暴露部分向上发生(朝向正z方向)。因此,半导体主体1312可以 具有与硅衬底1302相同的材料,即,单晶硅。与硅衬底1302一样,半导体主体1312可以是本 征的(即,未掺杂的)或者掺杂有第一类型的掺杂剂,例如,P型掺杂剂(例如,B或Ga)。根据开 口1310的形状,半导体主体1312可以具有与开口1310相同的形状,例如立方体形状或圆柱 体形状。在一些实施方式中,执行平面化工艺(例如,CMP),以去除半导体主体1312的超出第 二电介质层1309的顶表面的多余部分。结果,根据一些实施方式,由此形成半导体主体1312 (例如,单晶硅主体)的阵列,每个半导体主体1312被相应栅极电介质1318围绕并且从硅衬 底1302垂直(在z方向上)延伸穿过第二电介质层1309、字线1308、第一电介质层1306和牺牲 层1304的堆叠体。

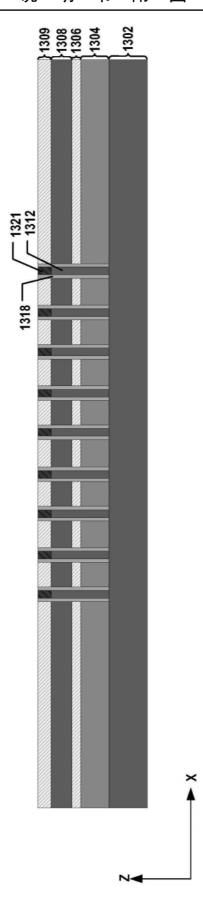

[0173] 重新参考图16,方法1600进行至操作1608,在操作1608中,对半导体主体的第一端部进行掺杂。如图13D中所示,对每个半导体主体1312的暴露上端部(即,半导体主体1312在垂直方向(z方向)上的两个端部中的远离硅衬底1302的一个端部)进行掺杂,以形成源极/漏极1321。在一些实施方式中,执行注入工艺和/或热扩散工艺,以向半导体主体1312的暴露上端部掺杂P型掺杂剂或N型掺杂剂,以形成源极/漏极1321。在一些实施方式中,通过在半导体主体1312的暴露上端部处执行硅化工艺,在源极/漏极1321上形成硅化物层。

[0174] 方法1600进行至操作1610,如图16中所示,在操作1610中,在半导体主体的掺杂第一端部上形成存储单元。存储单元可以包括电容器、铁电电容器或PCM元件。在一些实施方式中,为了形成是电容器的存储单元,在半导体主体的掺杂第一端部上形成第一电极,在第一电极上形成电容器电介质,并且在电容器电介质上形成第二电极。在一些实施方式中,在字线上方形成互连层。互连层可以包括在一个或多个ILD层中的多个互连。

[0175] 如图13E中所示,例如通过使用一种或多种薄膜沉积工艺沉积电介质,在第二电介质层1309的顶表面之上形成一个或多个ILD层,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。应当理解,在其中ILD层包括氧化硅(与第二电介质层1309相同的材料)的一些示例中,ILD层与第二电介质层1309之间的边界和界面可能在沉积之后变得不可区分。如图13E中所示,在ILD层中依次形成第一电极1324、电容器电介质1326和第二电极1328,以形成

与半导体主体1312接触的电容器。在一些实施方式中,通过使用光刻和蚀刻工艺图案化并且蚀刻与相应源极/漏极1321对准的电极开口,并且使用薄膜沉积工艺沉积填充电极开口的导电材料,来在相应源极/漏极1321(即,相应半导体主体1312的掺杂上端部)上形成每个第一电极1324。类似地,在一些实施方式中,通过使用光刻和蚀刻工艺图案化并且蚀刻电极开口,并且使用薄膜沉积工艺沉积填充电极开口的导电材料,来在电容器电介质1326上形成第二电极1328。

[0176] 如图13F中所示,可以在字线1320上方形成互连层1332。互连层1332可以包括在多个ILD层中的MEOL互连和/或BEOL互连,以与字线1320和第二电极1328进行电连接。在一些实施方式中,互连层1332包括多个ILD层和以多种工艺形成在ILD层中的互连。例如,互连层1332中的互连可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD、电镀、无电镀或其任何组合。形成互连的制造工艺还可以包括光刻、CMP、湿法/干法蚀刻或者任何其他合适的工艺。ILD层可以包括通过一种或多种薄膜沉积工艺沉积在第二电极1328上的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。图13F中所示的ILD层和互连可以被统称为互连层1332。

[0177] 方法1600进行至操作1612,如图16中所示,在操作1612中,在半导体主体(和互连层)上方形成第二键合层。第二键合层可以包括第二键合触点。如图13F中所示,在互连层1332和半导体主体1312上方形成键合层1336。键合层1336可以包括被电介质围绕的多个键合触点1337。在一些实施方式中,通过一种或多种薄膜沉积工艺在互连层1332的顶表面上沉积电介质层(例如,ILD层),薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,电介质层中的电介质材料的光刻和干法/湿法蚀刻)首先图案化穿过电介质层的接触孔,可以形成穿过电介质层并且与互连层1332中的互连接触的键合触点1337。接触孔可以用导体(例如,Cu)填充。在一些实施方式中,填充接触孔包括在沉积导体之前沉积阻挡层、粘合层和/或晶种层。

[0178] 方法1600进行至操作1614,如图16所示,在操作1614中,以面对面的方式键合第一村底和第二村底。键合可以包括混合键合。在一些实施方式中,在键合之后,第一键合触点与第二键合触点在键合界面处接触。在一些实施方式中,在键合之后,第二村底在第一村底上方。在一些实施方式中,在键合之后,第一村底在第二村底上方。

[0179] 如图13G中所示,将硅衬底1338和形成在硅衬底1338上的部件(例如,外围电路1340中的晶体管1342)上下翻转,并且使面向下的键合层1346与面向上的键合层1336键合(即,以面对面的方式),由此形成键合界面1350。在一些实施方式中,在键合之前,对键合表面应用处理工艺,例如,等离子体处理、湿法处理和/或热处理。尽管图13G中未示出,但是可以将硅衬底1302和形成在硅衬底1302上的部件(例如,半导体主体1312)上下翻转,并且可以使面向下的键合层1336与面向上的键合层1346键合(即,以面对面的方式),由此形成键合界面1350。在键合之后,键合层1336中的键合触点1337与键合层1346中的键合触点1347彼此对准并且接触,使得半导体主体1312可以跨越键合界面1350电连接到外围电路1340。应当理解,在键合芯片中,半导体主体1312可以在外围电路1340上方或下方。然而,在键合之后,键合界面1350可以垂直形成在外围电路1340与半导体主体1312之间。

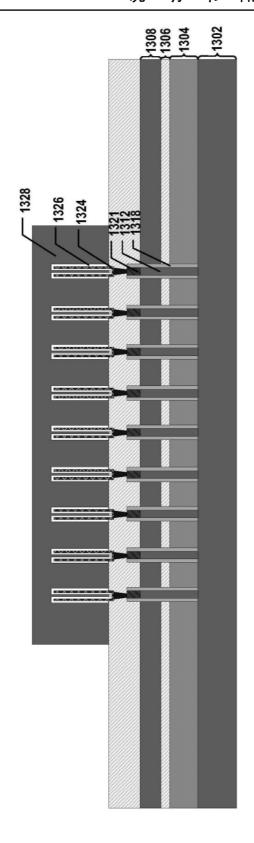

[0180] 方法1600进行至操作1616,如图16中所示,在操作1616中,去除第二衬底,以暴露半导体主体的与第一端部相对的第二端部。在一些实施方式中,为了去除第二衬底,从衬底

的第二侧对衬底进行抛光,直至被牺牲层停止。如图13H中所示,从背侧去除硅衬底1302(图 13G中所示),以暴露半导体主体1312的上端部(在翻转之前用作下端部)。在一些实施方式中,例如,使用CMP工艺从背侧对硅衬底1302进行抛光,直至被牺牲层1304和半导体主体1312的上端部停止。

[0181] 方法1600进行至操作1618,如图16中所示,在操作1618中,从半导体主体的暴露第二端部对半导体主体的部分进行掺杂。在一些实施方式中,在对半导体主体的部分进行掺杂之前,从半导体主体的暴露第二端部形成半导体主体的突出部。半导体主体的掺杂部分和另一部分可以在半导体主体的突出部中。在一些实施方式中,对半导体主体的突出部的部分进行掺杂。

[0182] 为了形成半导体主体的突出部并且对突出部的部分进行掺杂,在图17的操作1710处,例如,通过干法蚀刻和/或湿法蚀刻去除栅极电介质的部分,以暴露半导体主体的部分。如图13I中所示,从半导体主体1312的上端部去除栅极电介质1318的部分,以暴露半导体主体1312的部分。半导体主体1312的未被栅极电介质1318围绕的暴露部分可以被视为半导体主体1312的突出部,并且半导体主体1312的仍被栅极电介质1318围绕的其余部分可以被视为半导体主体1312的基部。在一些实施方式中,相对于牺牲层1304(例如,包括氮化硅)和半导体主体1312(例如,硅),采用湿法蚀刻剂(例如,氢氟酸(hydrofluoric acid,HF))选择性地蚀刻栅极电介质1318(例如,包括氧化硅)。可以控制蚀刻速率和/或持续时间,以确保仅去除掉栅极电介质1318的部分。在一些实施方式中,栅极电介质1318的剩余部分的上端部不在牺牲层1304的底表面上方。

[0183] 如图13I中所示,在去除栅极电介质1318的部分之后,形成围绕半导体主体1312的 突出部的凹陷1352。在一些实施方式中,例如,通过干法蚀刻和/或湿法蚀刻进一步去除半导体主体1312的突出部的部分,以扩大凹陷1352,即牺牲层1304中的开口。

[0184] 在图17中的操作1712处,对半导体主体的暴露部分的侧壁和顶部进行掺杂。如图 13J中所示,对半导体主体1312的暴露部分(即突出部)的侧壁和顶部进行掺杂以形成掺杂区1325。在一些实施方式中,执行注入工艺和/或热扩散工艺,以通过凹陷1352向半导体主体1312的暴露上端部掺杂P型掺杂剂或N型掺杂剂,以形成掺杂区1325。在其中用第一类型的掺杂剂(例如,P型掺杂剂)掺杂硅衬底1302和半导体主体1312的一些实施方式中,用不同于硅衬底1302和半导体主体1312的第二类型的掺杂剂(N型掺杂剂)掺杂掺杂区1325。可以控制注入工艺和/或热扩散工艺,使得掺杂剂局限于半导体主体1312的突出部的暴露表面(例如,侧壁和顶部),而不扩散至整个突出部。换句话说,在掺杂之后,半导体主体1312的突出部可以包括掺杂区1325和剩余部分(未掺杂的或者掺杂有不同类型的掺杂剂)。

[0185] 在图17中的操作1714处,去除半导体主体的暴露部分的掺杂顶部。在一些实施方式中,为了去除半导体主体的暴露部分的掺杂顶部,对牺牲层进行减薄,并且对半导体主体的暴露部分进行抛光,直到被减薄的牺牲层停止。

[0186] 如图13J中所示,例如,使用湿法蚀刻和/或干法蚀刻对牺牲层1304进行减薄,使得减薄的牺牲层1304的顶表面变得低于半导体主体1312的暴露部分(即突出部)的掺杂顶部。如图13K中所示,去除半导体主体1312的突出部的掺杂顶部,从而留下掺杂区1325的在突出部的侧壁上的剩余部分,以变为另一个源极/漏极1323。因此,可以从上端部暴露半导体主体1312的突出部的不被掺杂或者掺杂有不同类型的掺杂剂的部分。在一些实施方式中,例

如,使用CMP工艺对半导体主体1312的突出部进行抛光,以去除掺杂区1325的部分(即突出部的掺杂顶部),直到被减薄的牺牲层1304的顶表面停止。结果,半导体主体1312的突出部的上端部可以变得与减薄的牺牲层1304的顶表面齐平。可以在半导体主体1312的突出部的侧壁上(而非顶部上)形成源极/漏极1323。

[0187] 因此,根据一些实施方式,由此形成各自具有半导体主体1312、源极/漏极1321和1323、栅极电介质1318以及栅极电极(字线1320的与栅极电介质1318接触的部分)的垂直晶体管,如图13K中所示。如上文所述,根据一些实施方式,还由此形成各自具有第一电极1324和第二电极1328以及电容器电介质1326的电容器,并且由此形成各自具有垂直晶体管和耦合到垂直晶体管的电容器的DRAM单元1380,如图13K中所示。

[0188] 重新参考图16,方法1600进行至操作1620,在操作1620中,形成与半导体主体的掺杂部分接触的位线。在一些实施方式中,位线与半导体主体的突出部的掺杂部分接触。如图13L中所示,在凹陷1352中形成位线1334以与源极/漏极1323(图13K中所示)接触。位线1334的上端部可以低于半导体主体1312的突出部的上端部,使得位线1334不覆盖突出部的不被掺杂或者掺杂有不同类型的掺杂剂的部分的暴露上端部。为了形成位线1334,在一些实施方式中,例如使用湿法蚀刻和/或干法蚀刻首先去除牺牲层1304(图13K中所示),并且使用一种或多种薄膜沉积工艺沉积导电层,例如,金属(例如,W)层,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合的。可以通过控制沉积速率和/或持续时间,或者通过在沉积之后对导电层进行回蚀刻,而将导电层的厚度控制为小于半导体主体1312的突出部的高度。然后,可以使用光刻以及干法蚀刻和/或湿法蚀刻工艺对导电层进行图案化,以形成各自围绕并且接触相应源极/漏极1323的多条位线1334。

[0189] 如图13L中所示,在位线1334之间以及位线1334上方形成电介质层1354,以使位线1334电绝缘。可以通过使用一种或多种薄膜沉积工艺沉积电介质材料(例如,氧化硅)层来形成电介质层1354,以覆盖位线1334,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。在一些实施方式中,执行平面化工艺(例如,CMP),以去除覆盖半导体主体1312的突出部的上端部的多余电介质材料,使得突出部的上端部与电介质层1354的顶表面齐平,并且因此仍然保持暴露。

[0190] 方法1600进行至操作1622,如图16所示,在操作1622中,形成与半导体主体的另一部分接触的主体线。在一些实施方式中,主体线与半导体主体的突出部的未掺杂的或者掺杂有与掺杂部分不同类型的掺杂剂的另一部分接触。

[0191] 为了形成主体线,在图17中的操作1716处,形成与半导体主体的暴露部分(突出部)的顶部接触的多晶硅层。如图13M中所示,形成与半导体主体1312的突出部的顶部接触的多晶硅层1358。也就是说,突出部的不被掺杂或掺杂有不同类型的掺杂剂的部分的暴露上端部可以与多晶硅层1358接触。可以通过使用一种或多种薄膜沉积工艺在电介质层1354以及半导体主体1312的部分的暴露上端部上沉积多晶硅层来形成多晶硅层1358,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。如图13M中所示,由于位线1334的上端部低于半导体主体1312的突出部的上端部并且被电介质层1354覆盖,因此位线1334通过电介质层1354与多晶硅层1358电绝缘。由于多晶硅层1358和半导体主体1312可以具有相同的半导体材料(例如,硅),因此可以降低多晶硅层1358与半导体主体1312之间的接触电阻。

[0192] 在操作1718处,形成与多晶硅层接触的金属层。如图13M中所示,形成与多晶硅层

1358接触的金属层1360,以降低薄层电阻。例如,可以通过使用一种或多种薄膜沉积工艺在多晶硅层1358上沉积金属(例如,W)层来形成金属层1360,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。根据一些实施方式,由此形成包括多晶硅层1358和金属层1360的主体线1356,以与半导体主体1312的不被掺杂或者掺杂有不同类型的掺杂剂的部分接触。在一些实施方式中,例如,通过湿法/干法蚀刻工艺以及随后的导电材料沉积形成延伸穿过电介质层1354和其他ILD层的主体线触点1362。主体线触点1362可以与主体线1356以及互连层1332中的互连接触。

[0193] 尽管未示出,但是应当理解,可以在主体线1356上方形成焊盘引出互连层。焊盘引出互连层可以包括形成在一个或多个ILD层中的互连,例如,焊盘触点。焊盘触点可以包括导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以包括电介质材料,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。还应当理解,在一些示例中,可以在硅衬底1338的背侧上形成焊盘引出互连层,并且可以形成垂直延伸穿过硅衬底1338的穿衬底触点(through substrate contacts,TSC)。可以在形成焊盘引出互连层和TSC之前,例如,使用平面化工艺和/或蚀刻工艺,对硅衬底1338进行减薄。

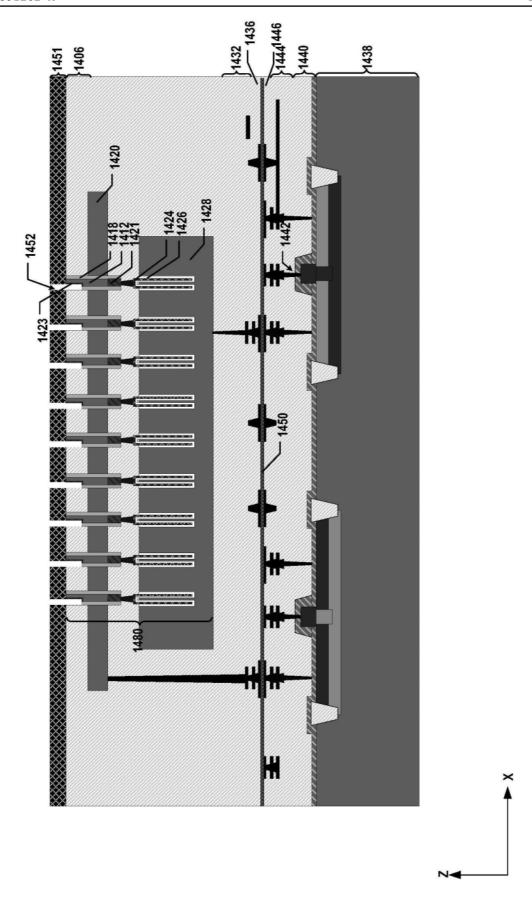

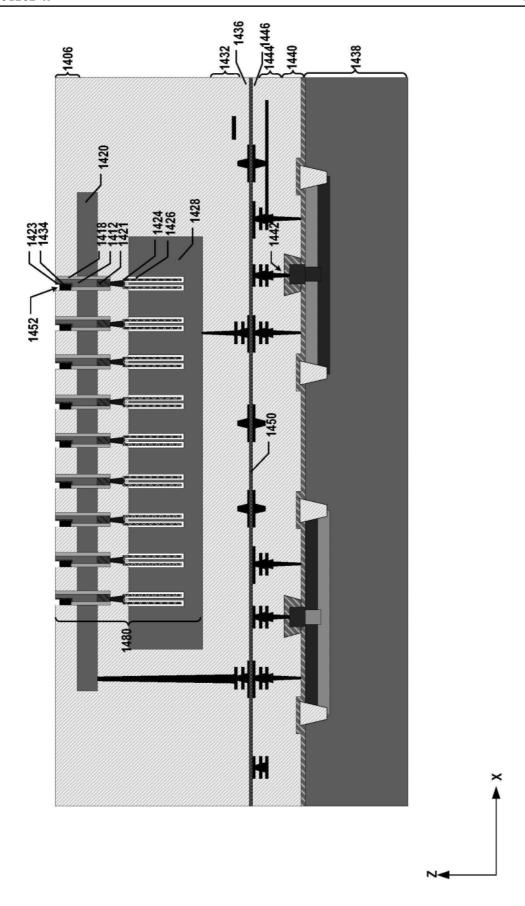

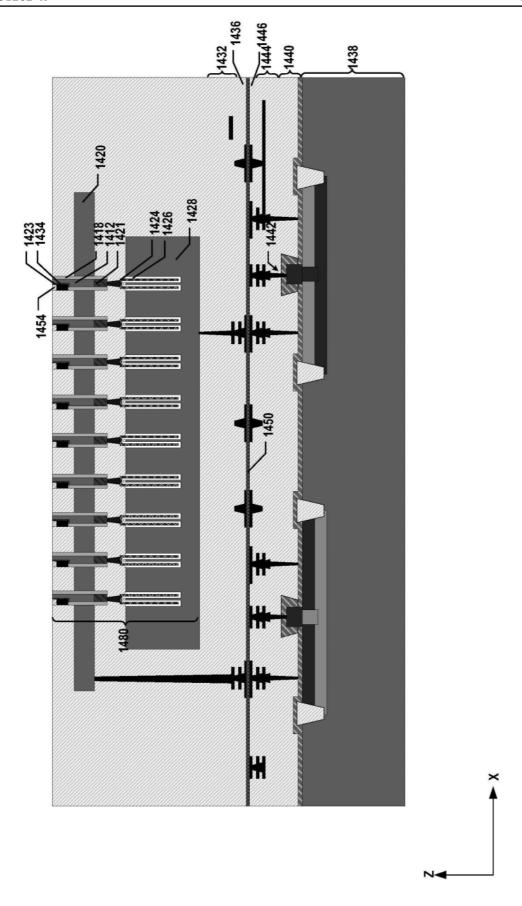

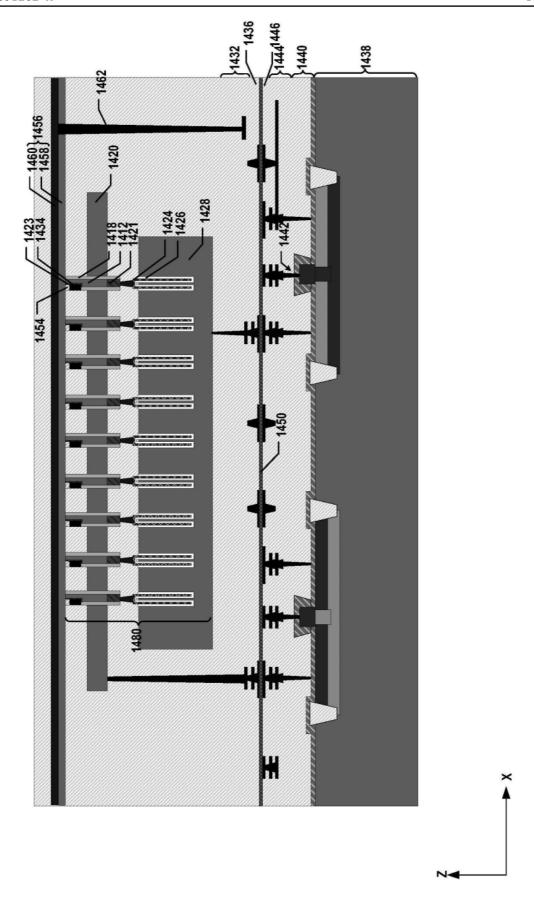

[0194] 如上文所述,图13A-图13M以及图17示出了形成具有与图7A中的垂直晶体管726对应的垂直晶体管的DRAM单元1380的制造工艺和方法。在如图14A-图14M以及图18中所示的一些实施方式中,示出了形成具有与图9A中的垂直晶体管926对应的垂直晶体管的DRAM单元1480的制造工艺和方法。

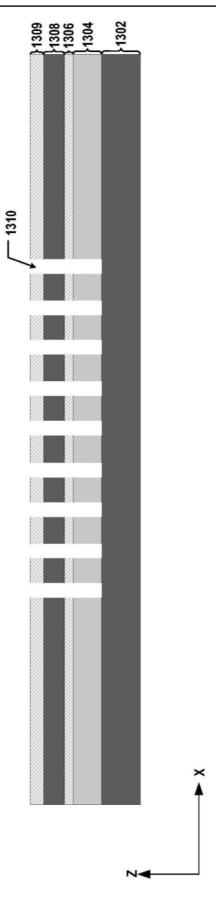

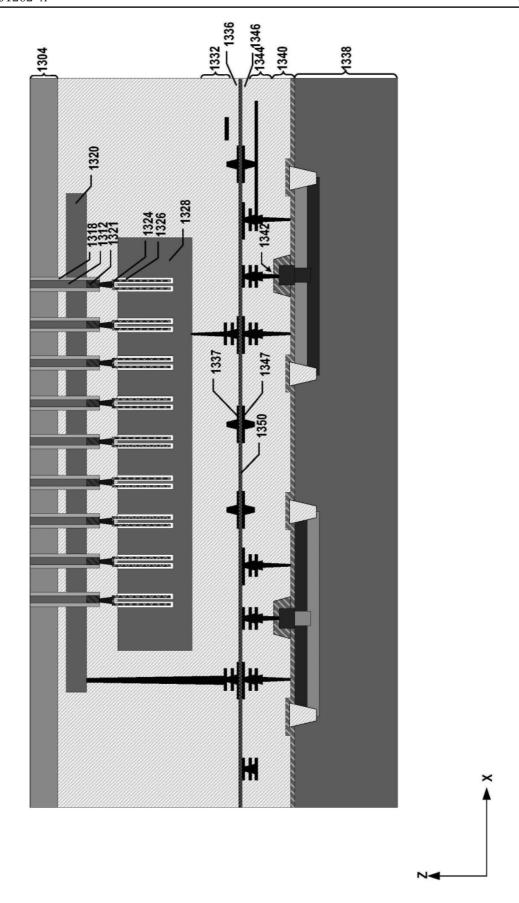

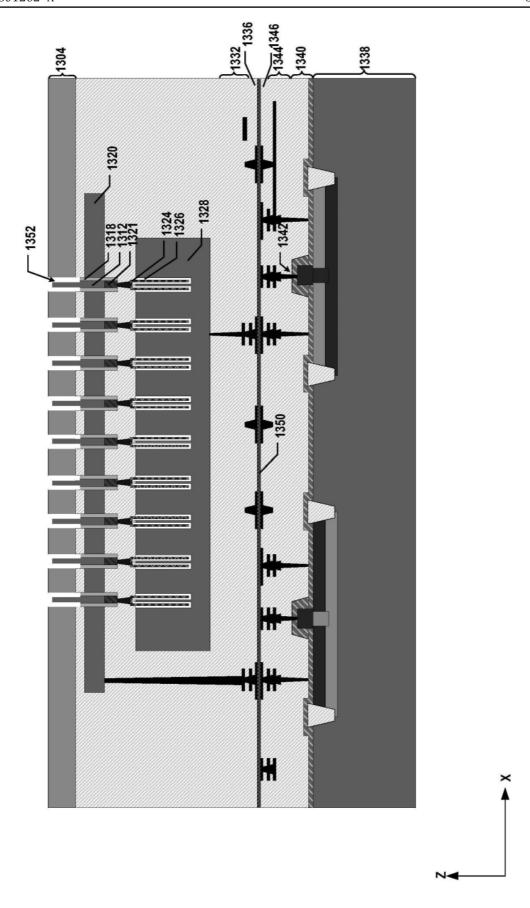

[0195] 参考图16,方法1600开始于操作1602,在操作1602中,在第一衬底上形成外围电路。第一衬底可以包括硅衬底。在一些实施方式中,在外围电路上方形成互连层。互连层可以包括在一个或多个ILD层中的多个互连。

[0196] 如图14H中所示,在硅衬底1438上形成多个晶体管1442。晶体管1442可以通过多种工艺形成,所述工艺包括但不限于光刻、干法/湿法蚀刻、薄膜沉积、热生长、注入、CMP和任何其他合适的工艺。在一些实施方式中,通过离子注入和/或热扩散在硅衬底1438中形成掺杂区,掺杂区例如用作晶体管1442的源极和漏极。在一些实施方式中,也通过湿法/干法蚀刻和薄膜沉积在硅衬底1438中形成隔离区(例如,STI)。晶体管1442可以在硅衬底1438上形成外围电路1440。

[0197] 如图14H中所示,可以在具有晶体管1442的外围电路1440上方形成互连层1444。互连层1444可以包括在多个ILD层中的MEOL互连和/或BEOL互连以与外围电路1440进行电连接。在一些实施方式中,互连层1444包括多个ILD层和以多种工艺形成在ILD层中的互连。例如,互连层1444中的互连可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD、电镀、无电镀或其任何组合。形成互连的制造工艺还可以包括光刻、CMP、湿法/干法蚀刻或任何其他合适的工艺。ILD层可以包括通过一种或多种薄膜沉积工艺沉积的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。图14H中示出的ILD层和互连可以被统称为互连层1444。

[0198] 方法1600进行至操作1604,如图16中所示,在操作1604中,在外围电路(和互连层)上方形成第一键合层。第一键合层可以包括第一键合触点。如图14H中所示,在互连层1444和外围电路1440上方形成键合层1446。键合层1446可以包括被电介质围绕的多个键合触点

1447。在一些实施方式中,通过一种或多种薄膜沉积工艺在互连层1444的顶表面上沉积电介质层(例如,ILD层),薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,电介质层中的电介质材料的光刻和干法/湿法蚀刻)首先图案化穿过电介质层的接触孔,可以形成穿过电介质层并且与互连层1444中的互连接触的键合触点1447。接触孔可以用导体(例如,Cu)填充。在一些实施方式中,填充接触孔包括在沉积导体之前沉积阻挡层、粘合层和/或晶种层。

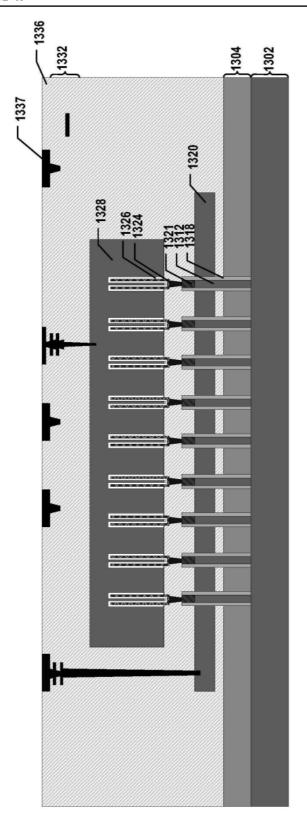

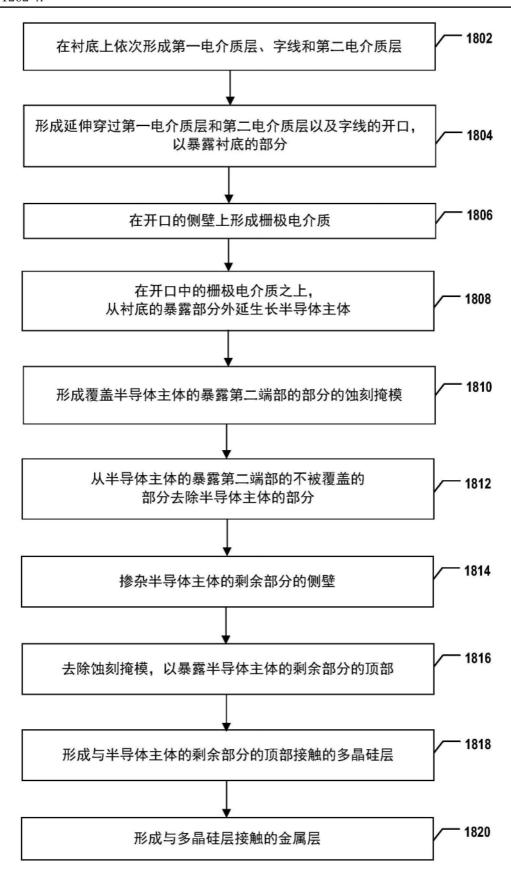

[0199] 方法1600进行至操作1606,如图16中所示,在操作1606中,形成从第二衬底垂直延伸的半导体主体。第二衬底可以包括硅衬底。为了形成半导体主体,在衬底上方形成夹在两个电介质层之间的字线,形成延伸穿过字线和电介质层的开口,以暴露衬底的部分,并且在开口中从衬底的暴露部分外延生长半导体主体。为了形成半导体主体,在外延生长半导体主体之前,在开口的侧壁上形成栅极电介质。

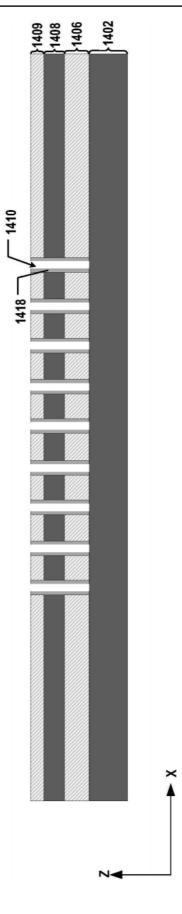

[0200] 在一些实施方式中,垂直延伸的半导体主体从第二衬底的第一侧(例如,正侧)形成。为了形成半导体主体,在图18中的操作1802处,在衬底上依次形成第一电介质层、字线和第二电介质层,第一电介质层和第二电介质层可以包括氧化硅,并且字线可以包括金属。[0201] 如图14A中所示,第一电介质层1406、字线1408和第二电介质层1409依次形成在硅衬底1402上。在一些实施方式中,使用一种或多种薄膜沉积工艺将氧化硅、金属(例如,W)和氧化硅依次沉积到硅衬底1402上,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。应当理解,第一电介质层1406和第二电介质层1409的材料可以包括氧化硅以外的任何合适的电介质材料,并且字线1408的材料可以包括金属以外的任何合适的导电材料。硅衬底1402可以是本征的(即,未掺杂的)或者掺杂有第一类型的掺杂剂,例如,P型掺杂剂(例如,B或Ga)。

[0202] 在图18中的操作1804处,形成延伸穿过第一电介质层、字线和第二电介质层的开口,以暴露衬底的部分。如图14A中所示,形成开口1410的阵列,每个开口垂直(在z方向上)延伸穿过第二电介质层1409、字线1408、和第一电介质层1406的堆叠体以达到硅衬底1402。结果,可以从开口1410暴露硅衬底1402的部分。在一些实施方式中,执行光刻工艺,以例如基于字线和位线的设计,使用蚀刻掩模(例如,光致抗蚀剂掩模)图案化开口1410的阵列,并且执行一种或多种干法蚀刻和/或湿法蚀刻工艺(例如,RIE),以蚀刻穿过第二电介质层1409、字线1408和第一电介质层1406的开口1410,直到被硅衬底1402停止。

[0203] 在图18中的操作1806处,在开口的侧壁上形成栅极电介质。如图14B中所示,分别在开口1410的侧壁上形成栅极电介质1418。为了形成栅极电介质1418,可以使用一种或多种薄膜沉积工艺将栅极电介质层(例如,氧化硅层或高k电介质层)沉积到开口1410中,以覆盖每个开口1410的侧壁和底部,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合的。然后,可以使用干法蚀刻和/或湿法蚀刻(例如,RIE)对栅极电介质层进行部分蚀刻,以去除栅极电介质层在开口1410的底部上的部分,以仍然从开口1410暴露硅衬底1402的部分。因此,栅极电介质层的在开口1410的侧壁上的剩余部分可以变为栅极电介质1418。因此,栅极电介质1418以及字线1408的与栅极电介质1418接触的部分可以变为要形成的垂直晶体管的栅极结构。

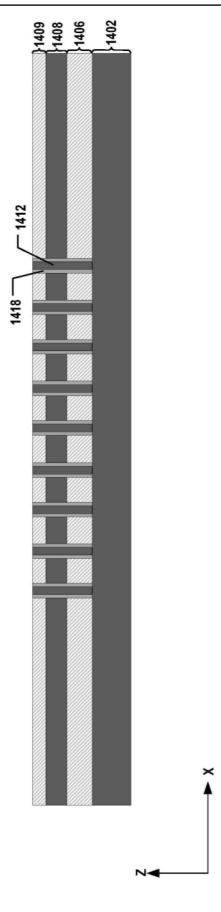

[0204] 在图18中的操作1808处,在开口中的栅极电介质之上,从衬底的暴露部分外延生长半导体主体。如图14C中所示,分别在开口1410中的栅极电介质1418(图14B中所示)之上

形成半导体主体1412的阵列。半导体主体1412可以从相应开口1410中的硅衬底1402的相应暴露部分,外延生长在相应栅极电介质1418之上。用于外延生长半导体主体1412的制造工艺可以包括但不限于VPE、LPE、MPE或者其任何组合。外延可以从开口1410中的硅衬底1402的暴露部分向上发生(朝向正z方向)。因此,半导体主体1412可以具有与硅衬底1402相同的材料,即,单晶硅。与硅衬底1402一样,半导体主体1412可以是本征的(即,未掺杂的)或者掺杂有第一类型的掺杂剂,例如,P型掺杂剂(例如,B或Ga)。根据开口1410的形状,半导体主体1412可以具有与开口1410相同的形状,例如立方体形状或圆柱体形状。在一些实施方式中,执行平面化工艺(例如,CMP),以去除半导体主体1412的超出第二电介质层1409的顶表面的多余部分。结果,根据一些实施方式,由此形成半导体主体1412(例如,单晶硅主体)的阵列,每个半导体主体1412被相应栅极电介质1418围绕并且从硅衬底1402垂直(在z方向上)延伸穿过第二电介质层1409、字线1408和第一电介质层1406的堆叠体。

[0205] 重新参考图16,方法1600进行至操作1608,在操作1608中,对半导体主体的第一端部进行掺杂。如图14D中所示,对每个半导体主体1412的暴露上端部(即,半导体主体1412在垂直方向(z方向)上的两个端部中的远离硅衬底1402的一个端部)进行掺杂,以形成源极/漏极1421。在一些实施方式中,执行注入工艺和/或热扩散工艺,以向半导体主体1412的暴露上端部掺杂P型掺杂剂或N型掺杂剂,以形成源极/漏极1421。在一些实施方式中,通过在半导体主体1412的暴露上端部处执行硅化工艺,在源极/漏极1421上形成硅化物层。

[0206] 方法1600进行至操作1610,如图16中所示,在操作1610中,在半导体主体的掺杂第一端部上形成存储单元。存储单元可以包括电容器、铁电电容器或PCM元件。在一些实施方式中,为了形成是电容器的存储单元,在半导体主体的掺杂第一端部上形成第一电极,在第一电极上形成电容器电介质,并且在电容器电介质上形成第二电极。在一些实施方式中,在字线上方形成互连层。互连层可以包括在一个或多个ILD层中的多个互连。

[0207] 如图14E中所示,例如通过使用一种或多种薄膜沉积工艺沉积电介质,在第二电介质层1409的顶表面之上形成一个或多个ILD层,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。应当理解,在其中ILD层包括氧化硅(与第二电介质层1409相同的材料)的一些示例中,ILD层与第二电介质层1409之间的边界和界面可能在沉积之后变得不可区分。如图14E中所示,在ILD层中依次形成第一电极1424、电容器电介质1426和第二电极1428,以形成与半导体主体1412接触的电容器。在一些实施方式中,通过使用光刻和蚀刻工艺图案化并且蚀刻与相应源极/漏极1421对准的电极开口,并且使用薄膜沉积工艺沉积填充电极开口的导电材料,来在相应源极/漏极1421(即,相应半导体主体1412的掺杂上端部)上形成每个第一电极1424。类似地,在一些实施方式中,通过使用光刻和蚀刻工艺图案化并且蚀刻电极开口,并且使用薄膜沉积工艺沉积填充电极开口的导电材料,来在电容器电介质1426上形成第二电极1428。

[0208] 如图14F中所示,可以在字线1420上方形成互连层1432。互连层1432可以包括在多个ILD层中的ME0L互连和/或BE0L互连,以与字线1420和第二电极1428进行电连接。在一些实施方式中,互连层1432包括多个ILD层和以多种工艺形成在ILD层中的互连。例如,互连层1432中的互连可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD、电镀、无电镀或其任何组合。形成互连的制造工艺还可以包括光刻、CMP、湿法/干法蚀刻或者任何其他合适的工艺。ILD层可以包括通过一种或多种薄膜沉积工

艺沉积在第二电极1428上的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。图14F中所示的ILD层和互连可以被统称为互连层1432。

[0209] 方法1600进行至操作1612,如图16中所示,在操作1612中,在半导体主体(和互连层)上方形成第二键合层。第二键合层可以包括第二键合触点。如图14F中所示,在互连层1432和半导体主体1412上方形成键合层1436。键合层1436可以包括被电介质围绕的多个键合触点1437。在一些实施方式中,通过一种或多种薄膜沉积工艺在互连层1432的顶表面上沉积电介质层(例如,ILD层),薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,电介质层中的电介质材料的光刻和干法/湿法蚀刻)首先图案化穿过电介质层的接触孔,可以形成穿过电介质层并且与互连层1432中的互连接触的键合触点1437。接触孔可以用导体(例如,Cu)填充。在一些实施方式中,填充接触孔包括在沉积导体之前沉积阻挡层、粘合层和/或晶种层。

[0210] 方法1600进行至操作1614,如图16所示,在操作1614中,以面对面的方式键合第一村底和第二村底。键合可以包括混合键合。在一些实施方式中,在键合之后,第一键合触点与第二键合触点在键合界面处接触。在一些实施方式中,在键合之后,第二衬底在第一衬底上方。在一些实施方式中,在键合之后,第一衬底在第二衬底上方。

[0211] 如图14G中所示,将硅衬底1438和形成在硅衬底1438上的部件(例如,外围电路1440中的晶体管1442)上下翻转,并且使面向下的键合层1446与面向上的键合层1436键合(即,以面对面的方式),由此形成键合界面1450。在一些实施方式中,在键合之前,对键合表面应用处理工艺,例如,等离子体处理、湿法处理和/或热处理。尽管图14G中未示出,但是可以将硅衬底1402和形成在硅衬底1402上的部件(例如,半导体主体1412)上下翻转,并且可以使面向下的键合层1436与面向上的键合层1446键合(即,以面对面的方式),由此形成键合界面1450。在键合之后,键合层1436中的键合触点1437与键合层1446中的键合触点1447彼此对准并且接触,使得半导体主体1412可以跨越键合界面1450电连接到外围电路1440。应当理解,在键合芯片中,半导体主体1412可以在外围电路1440上方或下方。然而,在键合之后,键合界面1450可以垂直形成在外围电路1440与半导体主体1412之间。

[0212] 方法1600进行至操作1616,如图16中所示,在操作1616中,去除第二衬底,以暴露半导体主体的与第一端部相对的第二端部。在一些实施方式中,为了去除第二衬底,从衬底的第二侧对衬底进行抛光,直至被第一电介质层停止。如图14H中所示,从背侧去除硅衬底1402(图14G中所示),以暴露半导体主体1412的上端部(在翻转之前用作下端部)。在一些实施方式中,例如,使用CMP工艺从背侧对硅衬底1402进行抛光,直至被第一电介质层1406和半导体主体1412的上端部停止。

[0213] 方法1600进行至操作1618,如图16中所示,在操作1618中,从半导体主体的暴露第二端部对半导体主体的部分进行掺杂。在一些实施方式中,在对半导体主体的部分进行掺杂之前,从半导体主体的暴露第二端部形成半导体主体的突出部。半导体主体的掺杂部分和另一部分可以在半导体主体的突出部中。在一些实施方式中,对半导体主体的突出部的部分进行掺杂。

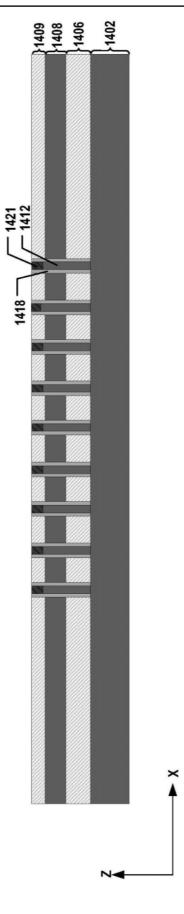

[0214] 为了形成半导体主体的突出部并且对突出部的部分进行掺杂,在图18中的操作 1810处,形成覆盖半导体主体的暴露第一端部的部分的蚀刻掩模。如图14I中所示,在第一 电介质层1406上形成蚀刻掩模1451。蚀刻掩模1451可以被图案化为覆盖半导体主体1412的

暴露上端部的部分,从而使半导体主体1412的暴露上端部的剩余部分不被覆盖。在一些实施方式中,使用一种或多种薄膜沉积工艺在第一电介质层1406和半导体主体1412的暴露上端部上沉积蚀刻掩模材料(例如,碳、光致抗蚀剂等)层,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,可以使用光刻和干法蚀刻和/或湿法蚀刻对蚀刻掩模材料层进行图案化,以形成穿过蚀刻掩模材料层的开口,每个开口与相应半导体主体1412的上端部的部分对准,如图14I中所示。穿过蚀刻掩模1451的每个开口被图案化为暴露相应半导体主体1412的上端部的部分,从而留下半导体主体1412的上端部的剩余部分仍未被蚀刻掩模1451覆盖。

[0215] 在图18中的操作1812处,从半导体主体的暴露第一端部的未被覆盖的部分去除半导体主体的部分,以暴露半导体主体的剩余部分的侧壁。如图14I中所示,例如,使用干法蚀刻和/或湿法蚀刻去除未被蚀刻掩模1451覆盖的半导体主体1412的部分和栅极电介质1418的部分(从它们的上端部),以形成凹陷1452。凹陷1452可以暴露半导体主体1412的部分,该部分具有不与栅极电介质1418接触的侧壁,如图14I中所示。半导体主体1412的未被栅极电介质1418完全围绕的暴露部分可以被视为半导体主体1412的突出部,并且半导体主体1412的仍被栅极电介质1418完全围绕的其余部分可以被视为半导体主体1412的基部。在一些实施方式中,通过蚀刻掩模1451的开口执行RIE工艺,以蚀刻半导体主体1412和栅极电介质1418的未被覆盖的部分。可以控制蚀刻速率和/或持续时间,以确保仅去除掉栅极电介质1418和半导体主体1412的部分。根据一些实施方式,半导体主体1412的剩余突出部的一个侧面或一些侧面(而非所有侧面)仍然与栅极电介质1418接触,而突出部的(一个或多个)其余侧面从凹陷1452暴露并且不与栅极电介质1418接触。

[0216] 在图18中的操作1814处,对半导体主体的剩余部分的侧壁进行掺杂。如图14J中所示,对半导体主体1412的剩余部分(例如,突出部)的侧壁进行掺杂,以形成另一源极/漏极1423。在一些实施方式中,执行注入工艺和/或热扩散工艺,以通过凹陷1452向半导体主体1412的暴露上端部掺杂P型掺杂剂或N型掺杂剂,以形成掺杂区,即源极/漏极1423。在其中用第一类型的掺杂剂(例如,P型掺杂剂)对硅衬底1402和半导体主体1412进行掺杂的一些实施方式中,用与硅衬底1402和半导体主体1412不同的第二类型的掺杂剂(N型掺杂剂)对源极/漏极1423进行掺杂。可以控制注入工艺和/或热扩散工艺,使得掺杂剂局限于半导体主体1412的突出部的暴露表面(例如,侧壁),而不扩散至整个突出部。换句话说,在掺杂之后,半导体主体1412的突出部可以包括源极/漏极1423和剩余部分(未掺杂的或者掺杂有不同类型的掺杂剂)。如图14I中所示,由于半导体主体1412的突出部的顶部在掺杂期间保持被蚀刻掩模1451覆盖,因此突出部的顶部保持不被掺杂或者掺杂有不同类型的掺杂剂。也就是说,可以在半导体主体1412的突出部的一个侧壁或一些侧壁(而非顶部)上形成源极/漏极1423。

[0217] 因此,根据一些实施方式,由此形成各自具有半导体主体1412、源极/漏极1421和1423、栅极电介质1418以及栅极电极(字线1420的与栅极电介质1418接触的部分)的垂直晶体管,如图14J中所示。如上文所述,根据一些实施方式,还由此形成各自具有第一电极1424和第二电极1428以及电容器电介质1426的电容器,并且由此形成各自具有垂直晶体管和耦合到垂直晶体管的电容器的DRAM单元1480,如图14J中所示。

[0218] 在图18中的操作1816处,去除蚀刻掩模,以暴露半导体主体的剩余部分的顶部。如

图14K中所示,例如,使用湿法蚀刻和/或干法蚀刻去除蚀刻掩模1451(图14J中所示),以暴露半导体主体1412的突出部的顶部以及第一电介质层1406。

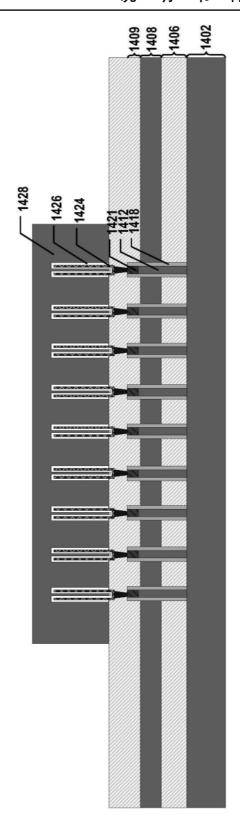

[0219] 重新参考图16,方法1600进行至操作1620,在操作1620中,形成与半导体主体的掺 杂部分接触的位线。在一些实施方式中,位线与半导体主体的剩余部分的掺杂侧壁接触。如 图14K中所示,在凹陷1452中形成位线1434以与源极/漏极1423接触。位线1434的上端部可 以低于半导体主体1412的突出部的上端部,使得位线1434不覆盖突出部的不被掺杂或者掺 杂有不同类型的掺杂剂的部分的暴露上端部。为了形成位线1434,在一些实施方式中,使用 一种或多种薄膜沉积工艺沉积导电层(例如,金属(例如,W)层),以部分地填充凹陷1452,薄 膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。可以通过控制沉积速率和/或持续时 间,来将位线1434的厚度控制为小于半导体主体1412的突出部的高度。在一些实施方式中, 导电层完全填充凹陷1452,并且使用CMP和随后的凹陷1452中的导电层的回蚀刻而去除多 余导电材料,以将所得到的位线1434的厚度控制为小于半导体主体1412的突出部的高度。 如图14L中所示,在凹陷1452中的位线1434之上(图14K中所示)形成电介质层 1454,以使位线1434电绝缘。可以通过使用一种或多种薄膜沉积工艺沉积电介质材料(例 如,氧化硅)层来填充凹陷1452,而形成电介质层1454,薄膜沉积工艺包括但不限于CVD、 PVD、ALD或其任何组合。在一些实施方式中,执行平面化工艺(例如,CMP),以去除覆盖半导 体主体1412的突出部的上端部的多余电介质材料,使得突出部的上端部与电介质层1454的 顶表面齐平,并且因此仍然保持暴露。

[0221] 方法1600进行至操作1622,如图16所示,在操作1622中,形成与半导体主体的另一部分接触的主体线。在一些实施方式中,主体线与半导体主体的剩余部分的另一部分接触。 [0222] 为了形成主体线,在图18中的操作1818处,形成与半导体主体的剩余部分(突出部)的顶部接触的多晶硅层。如图14M中所示,形成与半导体主体1412的突出部的顶部接触的多晶硅层1458。也就是说,突出部的暴露上端部可以与多晶硅层1458接触。可以通过使用一种或多种薄膜沉积工艺在电介质层1454以及半导体主体1412的部分的暴露上端部上沉积多晶硅层来形成多晶硅层1458,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。如图14M中所示,由于位线1434的上端部低于半导体主体1412的突出部的上端部并且被电介质层1454覆盖,因此位线1434通过电介质层1454与多晶硅层1458电绝缘。由于多晶硅层1458和半导体主体1412可以具有相同的半导体材料(例如,硅),因此可以降低多晶硅层1458与半导体主体1412之间的接触电阻。

[0223] 在操作1820处,形成与多晶硅层接触的金属层。如图14M中所示,形成与多晶硅层1458接触的金属层1460,以降低薄层电阻。例如,可以通过使用一种或多种薄膜沉积工艺在多晶硅层1458上沉积金属(例如,W)层来形成金属层1460,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。根据一些实施方式,由此形成包括多晶硅层1458和金属层1460的主体线1456,以与半导体主体1412的不被掺杂或者掺杂有不同类型的掺杂剂的部分接触。在一些实施方式中,例如,通过湿法/干法蚀刻工艺以及随后的导电材料沉积形成延伸穿过ILD层的主体线触点1462。主体线触点1462可以与主体线1456以及互连层1432中的互连接触。

[0224] 尽管未示出,但是应当理解,可以在主体线1456上方形成焊盘引出互连层。焊盘引出互连层可以包括形成在一个或多个ILD层中的互连,例如,焊盘触点。焊盘触点可以包括

导电材料,导电材料包括但不限于W、Co、Cu、Al、掺杂硅、硅化物或其任何组合。ILD层可以包括电介质材料,电介质材料包括但不限于氧化硅、氮化硅、氮氧化硅、低k电介质或其任何组合。还应当理解,在一些示例中,可以在硅衬底1438的背侧上形成焊盘引出互连层,并且可以形成垂直延伸穿过硅衬底1438的TSC。可以在形成焊盘引出互连层和TSC之前,例如,使用平面化工艺和/或蚀刻工艺,对硅衬底1438进行减薄。

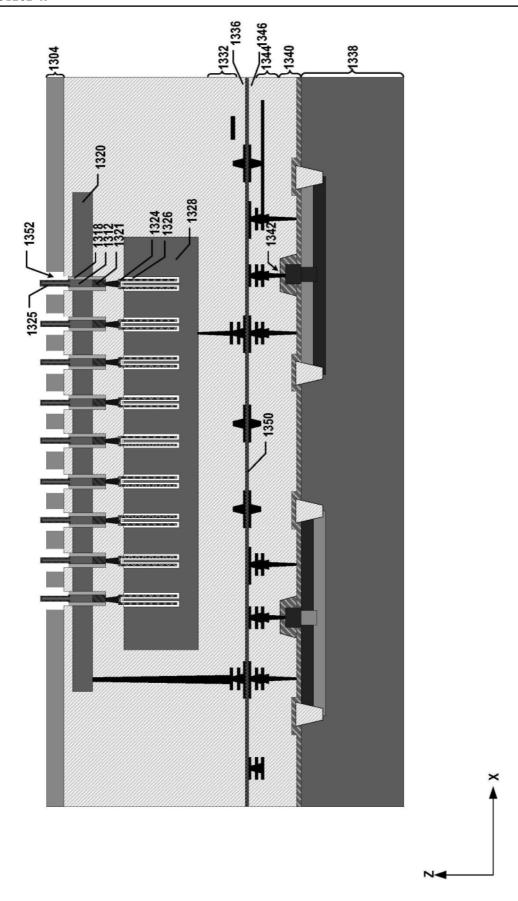

[0225] 图15A-图15E示出了根据本公开的一些方面的用于形成包括垂直晶体管和堆叠存储单元的3D存储器器件的制造工艺。图19示出了根据本公开的一些方面的用于形成包括垂直晶体管和堆叠存储单元的3D存储器器件的方法1900的流程图。图15A-图15E以及图19中所示的3D存储器器件的示例包括图10A中所示的3D存储器器件1000。将一起描述图15A-图15E以及图19。应当理解,方法1900中所示的操作不是详尽无遗的,并且也可以在所示操作中的任何操作之前、之后或之间执行其他操作。此外,一些操作可以同时执行,或者以与图19中所示的不同的顺序执行。

[0226] 参考图19,方法1900开始于操作1902,在操作1902中,在第一衬底上形成外围电路。第一衬底可以包括硅衬底。在一些实施方式中,在外围电路上方形成互连层。互连层可以包括在一个或多个ILD层中的多个互连。

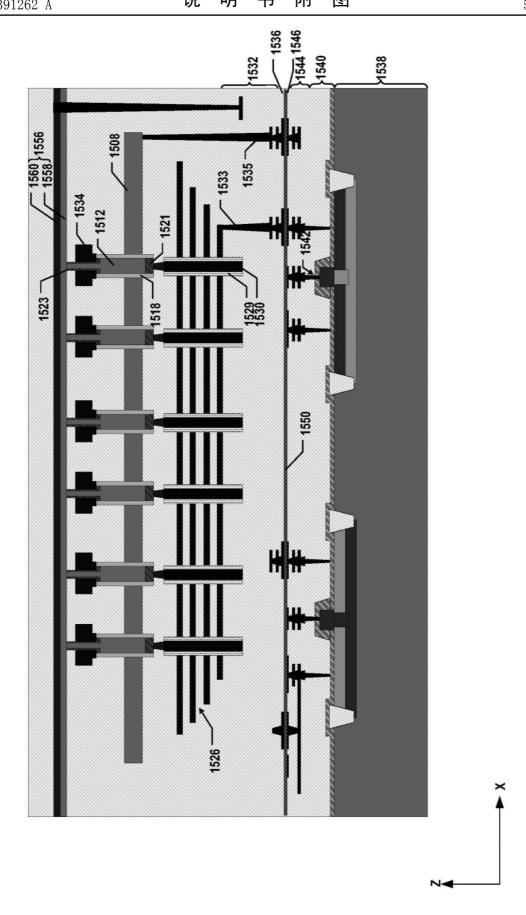

[0227] 如图15D中所示,在硅衬底1538上形成多个晶体管1542。晶体管1542可以通过多种工艺形成,所述工艺包括但不限于光刻、干法/湿法蚀刻、薄膜沉积、热生长、注入、CMP和任何其他合适的工艺。在一些实施方式中,通过离子注入和/或热扩散在硅衬底1538中形成掺杂区,掺杂区例如用作晶体管1542的源极和漏极。在一些实施方式中,也通过湿法/干法蚀刻和薄膜沉积在硅衬底1538中形成隔离区(例如,STI)。晶体管1542可以在硅衬底1538上形成外围电路1540。

[0228] 如图15D中所示,可以在具有晶体管1542的外围电路1540上方形成互连层1544。互连层1544可以包括在多个ILD层中的MEOL互连和/或BEOL互连以与外围电路1540进行电连接。在一些实施方式中,互连层1544包括多个ILD层和以多种工艺形成在ILD层中的互连。例如,互连层1544中的互连可以包括通过一种或多种薄膜沉积工艺沉积的导电材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD、电镀、无电镀或其任何组合。形成互连的制造工艺还可以包括光刻、CMP、湿法/干法蚀刻或任何其他合适的工艺。ILD层可以包括通过一种或多种薄膜沉积工艺沉积的电介质材料,薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。图15D中示出的ILD层和互连可以被统称为互连层1544。

[0229] 方法1900进行至操作1904,如图19中所示,在操作1904中,在外围电路(和互连层)上方形成第一键合层。第一键合层可以包括第一键合触点。如图15D中所示,在互连层1544和外围电路1540上方形成键合层1546。键合层1546可以包括被电介质围绕的多个键合触点1547。在一些实施方式中,通过一种或多种薄膜沉积工艺在互连层1544的顶表面上沉积电介质层(例如,ILD层),薄膜沉积工艺包括但不限于CVD、PVD、ALD或其任何组合。然后,通过使用图案化工艺(例如,电介质层中的电介质材料的光刻和干法/湿法蚀刻)首先图案化穿过电介质层的接触孔,可以形成穿过电介质层并且与互连层1544中的互连接触的键合触点1547。接触孔可以用导体(例如,Cu)填充。在一些实施方式中,填充接触孔包括在沉积导体之前沉积阻挡层、粘合层和/或晶种层。

[0230] 方法1900进行至操作1906,如图19中所示,在操作1906中,形成从第二衬底的第一

侧(例如,正侧)垂直延伸的半导体主体。第二衬底可以包括硅衬底。为了形成半导体主体,在衬底上方形成夹在两个电介质层之间的字线,形成延伸穿过字线和电介质层的开口,以暴露衬底的部分,并且在开口中从衬底的暴露部分外延生长半导体主体。为了形成半导体主体,在外延生长半导体主体之前,在开口的侧壁上形成栅极电介质。

[0231] 如图15A中所示,形成各自从硅衬底1502垂直延伸的半导体主体1512的阵列。半导体主体1512可以被栅极电介质1518围绕并且垂直延伸穿过夹在电介质层1506和1509之间的字线1508。用于形成半导体主体1512和栅极电介质1518的制造工艺可以与上文关于半导体主体1312或1412以及栅极电介质1318或1418描述的制造工艺相同,并且因此不再重复。

[0232] 方法1900进行至操作1908,如图19中所示,在操作1908中,对半导体主体的第一端部进行掺杂。如图15A中所示,对每个半导体主体1512的上端部(即,半导体主体1512在垂直方向(z方向)上的两个端部中的远离硅衬底1502的一个端部)进行掺杂,以形成源极/漏极1521。在一些实施方式中,执行注入工艺和/或热扩散工艺,以向半导体主体1512的上端部掺杂P型掺杂剂或N型掺杂剂,以形成源极/漏极1521。在一些实施方式中,通过在半导体主体1512的上端部处执行硅化工艺而在源极/漏极1521上形成硅化物层。

[0233] 方法1900进行至操作1910,如图19中所示,在操作1910中,在半导体主体上方形成交错的电介质层和导电层。在一些实施方式中,为了形成电介质层和导电层,交替沉积电介质层和导电层。在一些实施方式中,在电介质层和导电层的边缘处形成阶梯结构。

[0234] 如图15A中所示,在半导体主体1512上方形成多个交错的电介质层1524和导电层1522。在一些实施方式中,使用一种或多种薄膜沉积工艺交替沉积电介质层1524和导电层1522,薄膜沉积工艺包括但不限于PVD、CVD、ALD或其任何组合的。在一些实施方式中,电介质层1524包括氧化硅,并且导电层1522包括金属,例如,W。在一些实施方式中,在形成电介质层1524和导电层1522之前,形成电极触点1519。每个电极触点1519可以与相应半导体主体1512的源极/漏极1521接触。为了形成电极触点1519,接触孔可以与对应半导体主体1512对准,并且被蚀刻穿过ILD层,以暴露源极/漏极1521,并且可以使用一种或多种薄膜沉积工艺沉积填充接触孔的导电材料,薄膜沉积工艺包括但不限于PVD、CVD、ALD或其任何组合。

[0235] 如图15A中所示,在交错的电介质层1524和导电层1522的边缘处形成阶梯结构1526。阶梯结构1526可以通过所谓的"修整-蚀刻"工艺形成,"修整-蚀刻"工艺在每一循环中修整(例如,通常从所有方向逐渐向内蚀刻)图案化的光致抗蚀剂层,随后使用修整的光致抗蚀剂层作为蚀刻掩模来蚀刻交错的电介质层1524和导电层1522的暴露部分,以形成阶梯结构1526的一个台阶/级。可以重复该工艺,直到形成阶梯结构1526的所有台阶/级。

[0236] 方法1900进行至操作1912,如图19中所示,在操作1912中,形成包括导电材料并且 耦合到半导体主体的第一端部的电极层以及在电极层之上的存储层。电极层和存储层可以 垂直延伸穿过电介质层和导电层。在一些实施方式中,为了形成电极层和存储层,形成延伸 穿过电介质层和导电层的开口,在开口的侧壁上沉积存储层,并且在开口中的存储层之上 形成电极层。存储层可以包括铁电材料,并且电极层可以包括金属。

[0237] 如图15B中所示,形成各自垂直延伸穿过交错的电介质层1524和导电层1522的开口1528的阵列。每个开口1528可以暴露相应半导体主体1512的相应电极触点1519或者源极/漏极1521(如果没有形成电极触点1519的话)。可以通过首先使用光刻图案化具有与电极触点1519或源极/漏极1521对准的开口的蚀刻掩模(未示出),随后穿过交错的电介质层

1524和导电层1522进行可以被电极触点1519或源极/漏极1521停止的干法蚀刻和/或湿法蚀刻(例如,深反应离子蚀刻(DRIE))来形成开口1528。