(19)**日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)公開番号 **特開2023-44509**

(P2023-44509A) (43)公開日 **令和5年3月30日(2023.3.30)**

(51)国際特許分類

FΙ

テーマコード(参考)

G 0 6 F 12/00 (2006.01)

G 0 6 F 12/00

5 B 1 6 0

G 0 6 F 12/00 5 9 7 U

審査請求 未請求 請求項の数 6 OL (全22頁)

(21)出願番号 (22)出願日 特願2021-152564(P2021-152564) 令和3年9月17日(2021.9.17) (71)出願人 318010018

5 5 0 Z

キオクシア株式会社

東京都港区芝浦三丁目1番21号

(74)代理人 110002147

弁理士法人酒井国際特許事務所

(72)発明者 安田 哲也

東京都港区芝浦三丁目1番21号 キオ

クシア株式会社内

Fターム(参考) 5B160 NA03

(54) 【発明の名称】 メモリシステムおよびメモリシステムの制御方法

## (57)【要約】

【課題】ウェアレベリングを好適に制御する。

【解決手段】メモリシステムのコントローラは、複数の ブロック毎に、データが記憶されている状態を示す使用 中であるか否かを示す第1情報、消去した回数を示す第 2情報、及び次の消去までの待時間を示す第3情報を管 理し、ホストから受信した第1のシーケンシャルライト を実行し、ホストから受信した第2のシーケンシャルラ イトを実行するに際し、第1の差分と第2の差分と第3 の差分とに基づき、複数のブロック毎の消去回数を平準 化する処理の実行要否を決定する。第1の差分は、デー タのライト前後における第1ブロックの待時間の差であ る。第2の差分は、第1のシーケンシャルライトにおけ る消去順序の第1の最大値と第2のシーケンシャルライ トにおける消去順序の第2最大値との差分に対応する。 第3の差分は、第1ブロックの消去回数と第1情報が使 用中を示していない第2ブロックの消去回数との差であ る。

【選択図】図9

## 【特許請求の範囲】

#### 【請求項1】

消去単位であるブロックを複数含む不揮発性メモリと、

前記不揮発性メモリに接続されるとともにホストに接続可能であるコントローラと、 を備え、

前記コントローラは、

前記複数のブロック毎に、データが記憶されている状態を示す使用中であるか否かを示す第 1 情報、消去した回数を示す第 2 情報、及び次の消去までの待時間を示す第 3 情報を管理し、

前記ホストから第1のシーケンシャルライトの要求を受信し、

受信した前記第1のシーケンシャルライトを実行し、

前記第1のシーケンシャルライトの後に前記ホストから第2のシーケンシャルライトの要求を受信し、

受信した前記第2のシーケンシャルライトを実行するに際し、第1の差分と、第2の差分と、第3の差分と、に基づき、前記第1情報が前記使用中を示している第1ブロックに対する前記複数のブロック毎の消去回数を平準化する処理の実行要否を決定し、

前記第1の差分は、前記第1ブロックに対して次に実行されるデータのライト前後における前記第1ブロックの待時間の差であり、

前記第2の差分は、前記第2のシーケンシャルライトの書き込み対象となった複数のブロックについて、前記第1のシーケンシャルライトにおける消去順序の第1の最大値と前記第2のシーケンシャルライトにおける消去順序の第2最大値との差分に対応し、

前記第3の差分は、前記第1ブロックの消去回数と第1情報が前記使用中を示していない第2プロックの消去回数との差である、

メモリシステム。

#### 【請求項2】

前記コントローラは、今回のシーケンシャルライトのアクセスパタンが、前記複数のブロックに対する、前記不揮発性メモリ内の静的データ量の比率である静的データ比率の低いアクセスパタンである場合、前記平準化する処理を実行せず、前記今回のシーケンシャルライトのアクセスパタンが、前記複数のブロックに対する前記静的データ比率の高いアクセスパタンである場合、前記平準化する処理として、書き換え元ブロックに記憶されているデータを書き換え先ブロックへ書き換える処理を実行する、

## 【請求項3】

前記コントローラは、前記第1の差分と、前記第2の差分の履歴に基づく閾値と、の比較に応じて、前記不揮発性メモリ内の静的データ量の比率である静的データ比率を推測する。

請求項1に記載のメモリシステム。

請求項1に記載のメモリシステム。

# 【請求項4】

前記第2の差分の履歴は、リングバッファに保存される、

請求項1に記載のメモリシステム。

#### 【請求項5】

前記ブロック毎の待時間は、前記不揮発性メモリ内のブロックのデータを消去した順序である消去順序、前記不揮発性メモリ内のブロックのデータを消去した時刻である消去時刻、又は前記不揮発性メモリ内のブロックからデータを消去した後の経過時間である、請求項1に記載のメモリシステム。

## 【請求項6】

消去単位であるブロックを複数含む不揮発性メモリを備えるメモリシステムの制御方法であって、

前記複数のブロック毎に、データが記憶されている状態を示す使用中であるか否かを示す第1情報、消去した回数を示す第2情報、及び次の消去までの待時間を示す第3情報を

10

20

30

40

管理することと、

ホストから第1のシーケンシャルライトの要求を受信することと、

受信した前記第1のシーケンシャルライトを実行することと、

前記第1のシーケンシャルライトの後に前記ホストから第2のシーケンシャルライトの要求を受信することと、

受信した前記第2のシーケンシャルライトを実行するに際し、第1の差分と、第2の差分と、第3の差分と、に基づき、前記第1情報が前記使用中を示している第1ブロックに対する前記複数のブロック毎の消去回数を平準化する処理の実行要否を決定することと、を含み、

前記第1の差分は、前記第1ブロックに対して次に実行されるデータのライト前後における前記第1ブロックの待時間の差であり、

前記第2の差分は、前記第2のシーケンシャルライトの書き込み対象となった複数のブロックについて、前記第1のシーケンシャルライトにおける消去順序の第1の最大値と前記第2のシーケンシャルライトにおける消去順序の第2最大値との差分に対応し、

前記第3の差分は、前記第1ブロックの消去回数と第1情報が前記使用中を示していない第2ブロックの消去回数との差である、

メモリシステムの制御方法。

【発明の詳細な説明】

【技術分野】

[0001]

本実施形態は、メモリシステムおよびメモリシステムの制御方法に関する。

【背景技術】

[0002]

従来、不揮発性メモリを有するSSD(Solid State Drive)などのメモリシステムが知られている。SSDに搭載される不揮発性メモリの一例としては、NAND型のフラッシュメモリ(以下、NANDメモリという)が知られている。NANDメモリは、NAND回路を格子状に並べたメモリセルアレイを備える。メモリセルアレイは、データの消去単位である複数のブロックに分割される。SSDは、NANDメモリの所望のブロックにデータを書き込むにあたって、対象のブロックに対する消去を実行する。その後、SSDは、消去されたブロックに対してデータを書き込む。また、NANDメモリは、特性の劣化を避けるために、ブロックの消去可能な回数について制限を設けている。

[0003]

ところで、このようなメモリシステムにおいては、NANDメモリの各ブロックの寿命のばらつきを防ぐために、ブロック毎の消去回数(または書き込み回数)の平準化を図る処理が実行される。この処理は、ウェアレベリングとも称される。ウェアレベリングの手法として、書き換え頻度が低いスタティック(静的)データが書き込まれているブロックと、書き換え頻度が高いダイナミック(動的)データが書き込まれているブロックとの両者を対象とするSWL(Static Wear Leveling)が知られている。

【先行技術文献】

【特許文献】

[0004]

【特許文献1】米国特許第10417123号明細書

【特許文献2】米国特許出願公開第2019/0205245号明細書

【 特 許 文 献 3 】 米 国 特 許 出 願 公 開 第 2 0 1 4 / 0 8 0 1 4 3 4 号 明 細 書

【発明の概要】

【発明が解決しようとする課題】

[0005]

一つの実施形態は、ウェアレベリングを好適に制御することを可能とするメモリシステムおよびメモリシステムの制御方法を提供する。

【課題を解決するための手段】

30

10

20

## [0006]

一つの実施形態のメモリシステムは、消去単位であるブロックを複数含む不揮発性メモ リと、前記不揮発性メモリに接続されるとともにホストに接続可能であるコントローラと 、を備える。コントローラは、前記複数のブロック毎に、データが記憶されている状態を 示す使用中であるか否かを示す第1情報、消去した回数を示す第2情報、及び次の消去ま での待時間を示す第3情報を管理し、前記ホストから第1のシーケンシャルライトの要求 を受信し、受信した前記第1のシーケンシャルライトを実行し、前記第1のシーケンシャ ルライトの後に前記ホストから第2のシーケンシャルライトの要求を受信する。コントロ ーラは、受信した前記第2のシーケンシャルライトを実行するに際し、第1の差分と、第 2 の差分と、第 3 の差分と、に基づき、前記第 1 情報が前記使用中を示している第 1 ブロ ックに対する前記複数のブロック毎の消去回数を平準化する処理の実行要否を決定する。 前記第1の差分は、前記第1ブロックに対して次に実行されるデータのライト前後におけ る前記第1ブロックの待時間の差である。前記第2の差分は、前記第2のシーケンシャル ライトの書き込み対象となった複数のブロックについて、前記第1のシーケンシャルライ トにおける消去順序の第1の最大値と前記第2のシーケンシャルライトにおける消去順序 の第2最大値との差分に対応する。前記第3の差分は、前記第1ブロックの消去回数と第 1 情報が前記使用中を示していない第2ブロックの消去回数との差である。

【図面の簡単な説明】

#### [0007]

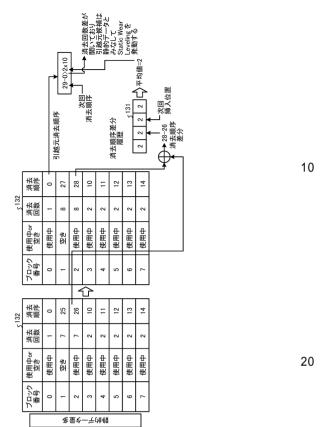

- 【図1】実施形態にかかるメモリシステムの構成を示す図。

- 【図2】実施形態の管理テーブルのデータ構成の一例を示す図。

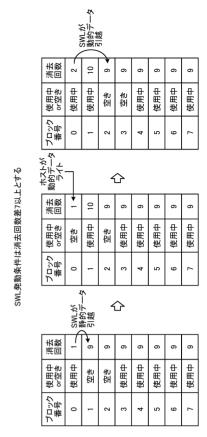

- 【 図 3 】 実 施 形 態 の 静 的 デ ー タ 量 が 少 な い ア ク セ ス パ タ ン の 例 を 示 す 図 。

- 【 図 4 】 実 施 形 態 の 静 的 デ ー タ 量 が 多 い ア ク セ ス パ タ ン の 例 を 示 す 図 。

- 【図5】比較例1にかかる従来のSWLの実行例を示す図。

- 【 図 6 1 】比較 例 1 にかかる従来の S W L の別の実行例を示す図。

- 【 図 6 2 】比 較 例 1 に か か る 従 来 の S W L の 別 の 実 行 例 を 示 す 図 。

- 【 図 6 3 】比較例 1 にかかる従来の S W L の別の実行例を示す図。

- 【 図 6 4 】比較例 1 にかかる従来の S W L の別の実行例を示す図。

- 【 図 6 5 】比 較 例 1 に か か る 従 来 の S W L の 別 の 実 行 例 を 示 す 図 。

- 【図6-6】比較例1にかかる従来のSWLの別の実行例を示す図。

- 【 図 6 7 】比較例 1 にかかる従来のSWLの別の実行例を示す図。

- 【 図 6 8 】比較 例 1 に か か る 従 来 の S W L の 別 の 実 行 例 を 示 す 図 。

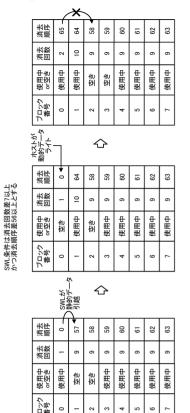

- 【 図 7 1 】 比 較 例 2 に か か る 従 来 の S W L の 実 行 例 を 示 す 図 。

- 【 図 7 2 】 比 較 例 2 に か か る 従 来 の S W L の 実 行 例 を 示 す 図 。

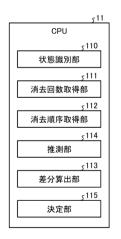

- 【 図 8 】 実 施 形 態 の S W L 処 理 に か か る 機 能 を 示 す 機 能 ブ ロ ッ ク 図 。

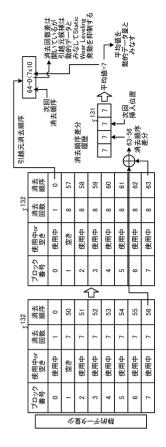

- 【 図 9 】 実 施 形 態 に か か る 静 的 デ ー タ 比 率 の 低 い ア ク セ ス パ タン に つ い て の S W L の 発 動 要否の判断例を示す図。

- 【 図 1 0 】 実 施 形 態 に か か る 静 的 デ ー タ 比 率 の 高 い ア ク セ ス パ タ ン に つ い て の S W L の 発 動要否の判断例を示す図。

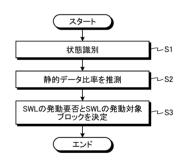

- 【図11】実施形態にかかるSWLの処理の流れを示すフローチャート。

- 【発明を実施するための形態】

## [00008]

以下に添付図面を参照して、実施形態にかかるメモリシステムおよびメモリシステムの 制御方法を詳細に説明する。なお、この実施形態により本発明が限定されるものではない

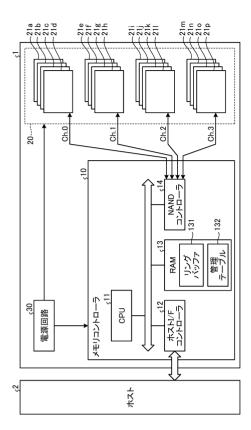

#### [0009]

図1は、実施形態にかかるメモリシステム1の構成を示す図である。メモリシステム1 は、例えばSSD(Solid State Drive)であり、ホスト2と接続可能である。メモ リシステム1とホスト2との間の通信路の規格は、特定の規格に限定されない。一例では 、 P C I e (Peripheral Component Interconnect Express)又はSAS(Se

10

20

30

40

rial Attached SCSI)が採用され得る。

[0010]

ホスト 2 は、例えばパーソナルコンピュータ、携帯情報端末、サーバなどである。メモリシステム 1 は、ホスト 2 からアクセスコマンド(一例では、リードコマンドおよびライトコマンド)を受け付けることができる。

(5)

[0011]

メモリシステム 1 は、メモリコントローラ 1 0 と、不揮発性メモリである N A N D 型のフラッシュメモリ(以下、N A N D メモリという) 2 0 と、電源回路 3 0 と、を備えている。

[0012]

N A N D メモリ 2 0 は、 1 以上のメモリチップ 2 1 によって構成される。ここでは、 N A N D メモリ 2 0 は、 1 6 個のメモリチップ 2 1 a ~ 2 1 p を備える。

[0013]

NANDメモリ20を構成する16個のメモリチップ21(21a~21p)は、それぞれ、4つのチャネル(ch.0~ch.3)の何れかを介してメモリコントローラ10に接続されている。図1の例に従えば、メモリチップ21a~21dは、チャネル0(ch.0)に接続されている。メモリチップ21e~21hは、チャネル1(ch.1)に接続されている。メモリチップ21i~21lは、チャネル2(ch.2)に接続されている。メモリチップ21m~21pは、チャネル3(ch.3)に接続されている。

[0014]

各チャネルは、I/O信号線および制御信号線を含む、配線群によって構成される。I /O信号線は、例えば、データ、アドレス、およびコマンドを送受信するための信号線で ある。制御信号線は、例えば、WE(ライトイネーブル)信号、RE(リードイネーブル )信号、CLE(コマンドラッチイネーブル)信号、ALE(アドレスラッチイネーブル )信号、WP(ライトプロテクト)信号等を送受信するための信号線である。

[0015]

メモリコントローラ 1 0 は、各チャネルを個別に制御することができる。メモリコントローラ 1 0 は、4 つのチャネルを同時に制御することによって、それぞれに接続されたチャネルが異なる合計 4 つのメモリチップ 2 1 を並列に動作させることができる。

[0016]

なお、メモリシステム 1 に具備されるチャネルの数は、 4 つに限定されない。また、各 チャネルに接続されているメモリチップ 2 1 の数は、 4 つに限定されない。

[0017]

各メモリチップ21は、NANDメモリ20の記憶領域を構成するものであって、NAND回路を格子状に並べたメモリセルアレイを備えている。メモリセルアレイには、ホスト2から受信したデータおよびメモリシステム1の動作に必要となるデータ(ファームウェアプログラムおよび管理情報など)などが格納される。

[0018]

メモリセルアレイは、複数のブロックに分割される。ブロックは、消去の単位である。 メモリコントローラ 1 0 は、NANDメモリ 2 0 の所望のブロックにデータを書き込むに あたって、このブロック全体を消去した後、消去されたブロックに対してデータを書き込 む。NANDメモリ 2 0 は、ブロックごとに、消去可能な回数に制限を設けている。

[0019]

電源回路 3 0 は、メモリコントローラ 1 0 および N A N D メモリ 2 0 を駆動するための内部電源を生成する。電源回路 3 0 は、生成した内部電源をメモリコントローラ 1 0 および N A N D メモリ 2 0 のそれぞれに供給する。

[0020]

メモリコントローラ10は、メモリシステム1の制御を実行する回路である。例えば、メモリコントローラ10は、後述のRAM(Random Access Memory)13を利用して、ホスト2とNANDメモリ20との間のデータ転送を実行する。

10

20

30

20

30

40

## [0021]

## [0022]

N A N D コントローラ 1 4 は、N A N D メモリ 2 0 に対するアクセスを実行する回路である。

## [0023]

RAM13は、キャッシュ、バッファ、およびワーキングエリアとして機能するメモリである。例えば、RAM13は、DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、またはこれらの組み合わせによって構成される。なお、RAM13は、メモリコントローラ10の外部に配置されてもよい。

#### [0024]

R A M 1 3 には、リングバッファ 1 3 1 が設けられている。また、R A M 1 3 には、管理テーブル 1 3 2 が設けられている。リングバッファ 1 3 1 および管理テーブル 1 3 2 は、C P U 1 1 によって操作される。

#### [0025]

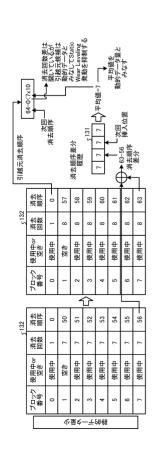

ここで、図2は管理テーブル132のデータ構成の一例を示す図である。図2に示すように、管理テーブル132は、NANDメモリ20のメモリチップ21のブロックを示すブロック番号毎に、空き、消去回数、及び消去順序を記憶する。空きは、ブロックを使用中なのか空き(すなわち未使用)なのかを示すデータである。消去回数は、ブロックのデータを消去した回数を示すデータである。データを消去した後、ブロックにデータが書き込まれるため、消去回数は、書き込み回数に対応する。消去順序は、次の消去までの待時間を表すものであってブロックのデータを消去した順序を特定することができるデータである。

# [0026]

なお、本実施形態においては、管理テーブル 1 3 2 は、消去順序をブロック毎の待時間として記憶するようにしたが、これに限るものではない。例えば、消去順序に代えて、ブロックのデータを消去した時刻である消去時刻、ブロックからデータを消去した後の経過時間などをブロック毎の待時間として記憶するようにしてもよい。

# [ 0 0 2 7 ]

なお、RAM13に記憶されたデータは、内部電源が断たれる前にNANDメモリ20に、管理情報として書き込まれる。NANDメモリ20に書き込まれた管理情報は、不揮発に記憶される。そして、NANDメモリ20に記憶された管理情報は、次の内部電源が供給された後に、RAM13に展開される。

## [0028]

ホストインタフェースコントローラ 1 2 は、ホスト 2 とメモリコントローラ 1 0 との間の情報(コマンド、データ)の送受信を制御する。

## [0029]

CPU11は、メモリシステム1に予め記憶されるプログラム(ファームウェアプログラムは、例えばNADAモリ20に記憶されている。CPU11は、メモリシステム1の起動時に、NANDメモリ20からRAM13にファームウェアプログラムをロードする。そして、CPU11は、RAM13にロードされたファームウェアプログラムを実行する。CPU11は、ファームウェアプログラムに従って、メモリコントローラ10の種々の機能を実現する

#### [0030]

20

30

40

50

例えば、CPU111は、SWL(Static Wear Leveling)を実行する。SWLは、NANDメモリ20の各ブロックの寿命が不均一に短くなるのを防ぐための処理である。CPU11は、SWLにおいて、書き換え頻度が低いスタティックデータ(静的データ)が書き込まれているブロックも対象にして、ブロック毎の消去回数(書き込み回数)の平準化を図る処理を実行する。より詳細には、SWLは、静的データが書き込まれているブロックと、書き換え頻度が高いダイナミックデータ(動的データ)が書き込まれているブロックとの両者を対象とし、ブロック毎の消去回数を平準化する。具体的には、CPU11は、SWLにおいて、静的データが書き込まれているブロックの消去回数が少なければ、空きの状態のブロックのうち消去回数が多いブロックへ静的データを書き換える。このようなSWLにより、消去回数の少ないブロックが空きの状態となり、そのブロックを動的データの書込みに利用させることで、ブロック毎の消去回数の平準化を図ることができる。

[0031]

ところで、上述のようなSWLの実行に際しては、NANDメモリ20のブロックに対するアクセスパタンを考慮する必要がある。ここで、NANDメモリ20のブロックに対するアクセスパタンについて説明する。アクセスパタンは、静的データ量と動的データ量との比率に対応する。

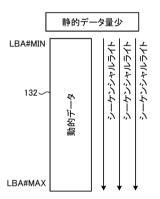

[0032]

図3は、静的データ量が少ない(すなわち、ほとんどない)アクセスパタンの例を示す 図である。図3に示す例は、静的データ量が少ないアクセスパタンとして、NANDメモリ20のあるLBA(Logical Block Address)範囲に対するデータのシーケンシャルライトの繰り返しを想定したものである。あるLBA範囲にシーケンシャルライトが繰り返されることで、このLAB範囲のデータは、動的データとして扱われる。

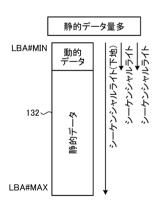

[ 0 0 3 3 ]

図4は、静的データ量が多いアクセスパタンの例を示す図である。図4に示す例は、静的データ量が多いアクセスパタンとして、まず、プリコンディショニング(pre-conditioning:下地)としてNANDメモリ20の全LBA範囲に対するデータのシーケンシャルライトを少なくとも1回実施し、その後、NANDメモリ20の狭域のあるLBA範囲に対するデータのシーケンシャルライトの繰り返しを想定したものである。シーケンシャルライトが繰り返されることで、狭域のあるLBA範囲のデータは、動的データとして扱われる。シーケンシャルライトを少なくとも1回実施された後、データが書き込まれないLBA範囲のデータは、静的データとして扱われる。

[0034]

ここで、本実施形態に対する比較例のSWLの課題について説明する。

[0035]

ここで、図5は比較例1にかかるSWLの実行例を示す図である。図5に示す比較例1は、NANDメモリ内のブロック毎の消去回数のみに基づいてSWLの発動要否の判断を行う例を示すものである。例えばホストからの動的データのライトによる消去回数の増加速度に対してSWLによる静的データの書き換え速度が遅い場合、書き換え元候補ブロックと書き換え先候補ブロックの消去回数差が一定の条件より大きくなることがある。この状態で、比較例1にかかるSWLが実行される場合を説明する。ここで、消去回数の増加速度は、ある時間における消去回数の増加数を示し、SWLによる書き換え速度は、同じある時間におけるSWLによる書き換えの数を示す。図5に示した例では、一定の条件は、消去回数差が7である。

[0036]

静的データが書き込まれている使用中ブロック(ブロック番号 0)とある空きブロック (ブロック番号 1)との消去回数差(9-1=8)は一定の条件(7)より大きい。この ため書き換え元ブロック(ブロック番号 0)から書き換え先ブロック(ブロック番号 1) への、SWLによるデータの書き換えが実行される。このSWLは、静的データを書き換 えているため適切な処理である。この書き換えの完了後、書き換え元ブロック(ブロック 番号 0)は空きブロックとなる。ここで空きブロックのうち書き換え回数が少ないブロックをする。ここで空きブロックのうち書き換え回数がからの動的データがライトされたとする。書き込み対象ブロック(ブロック番号 0)の利用時、消しなの動的データがライトされたとする。書き換え対象ブロック(ブロック番号 2)の消去回数が + 1(1 + 1 = 2)される。書き換え対象ブロック(ブロック番号 2)の消去回数が、第年である。である。である。である。である。である。である。であった場合、空きブロック(ブロック番号 2)と書き換え対象ブロックが(ク番号 0)との消去回数差(9・2=7)は一定の条件(7)と同じである。このため、音換え対象ブロックであるにも関わらず、SWLによって、書き換え元ブロック番号 0)に書き換えたブロック番号 0)に書き換え元ブロック番号 0)に書き換え元ブロック番号 0)に書き換えたデータは動的データであるため、この書き換えとなる。

[0037]

また、図6-1~図6-8は比較例1にかかるSWLの別の実行例を示す図である。図6-1~図6-8に示す比較例1は、NANDメモリ内のブロック毎の消去回数に基づいてSWLの発動要否の判断を行っていた例を示すものである。図6-1~図6-8では、ブロックが空きの状態は空きが×で示され、ブロックが空きでない状態は空きが「で示される。図6-1に示すように、ブロック番号0に静的データが格納されており、ブロック番号2~7に動的データが格納されているものとする。また、何らかの要因によりブロック番号1が空きであるものとする。なお、図6-1~図6-8において動的データに付された数字は、各図において格納された順番を示すものである。

[0038]

このような状態で、図6・1に示すように、静的データが格納されているブロック(ブロック番号0)以外のブロックに対する動的データのシーケンシャルライトの繰り返しがあったとする。ここで、ブロック番号0が一定の条件(例えば、空きブロック(ブロック番号1)があり、その空きブロックとの消去回数差が7)に到達した場合、ブロック番号0の静的データが空きブロック(ブロック番号1)に書き換えられる。その後、図6・2に示すように、書き換え元のブロック番号0は、空きブロックとなる。また、ブロック番号1は、静的データが書き込まれ、空きの状態ではなくなり、及び消去回数が+1されて9となる。

[0039]

その後、図6・3に示すように、静的データが格納されているブロック(ブロック番号1)以外のブロックに対する動的データのシーケンシャルライトの繰り返し(例えば、8回の繰り返し)があったとする。ここで、ブロック番号1が一定の条件(例えば、空きブロック(ブロック番号2)があり、その空きブロックとの消去回数差が7)に到達した場合、ブロック番号1の静的データが空きブロック(ブロック番号2)に書き換えられる。その後、図6・4に示すように、書き換え元のブロック番号1は、空きブロックとなる。また、ブロック番号2は、静的データが書き込まれ、空きの状態ではなくなり、及び消去回数が+1されて17となる。

[0040]

さらに、図6-5に示すように、空きブロックとなったブロック番号1に動的データが書き込まれた場合において、動的データが格納されているブロック番号0と動的データが格納されているブロック番号3との消去回数差が一定の条件(ここでは、消去回数差が7)に到達している場合には、動的データを引越元候補とする。そして、図6-5に示すように、ブロック番号3を空きブロックとした後、ブロック番号0の動的データが、空きブロック(ブロック番号3)に書き換えられる。そして、図6-6に示すように、書き換え元のブロック番号0は、空きブロックとなる。また、ブロック番号3は、動的データが書き込まれ、空きの状態ではなくなり、及び消去回数が+1されて17となる。

[0041]

30

20

10

20

30

40

その後、図6・7に示すように、静的データが格納されているブロック(ブロック番号2)以外のブロックに対する動的データのシーケンシャルライトの繰り返し(例えば、7又は8回の繰り返し)があったとする。ここで、ブロック番号2の静的データが一定の条件(例えば、空きブロック(ブロック番号3)があり、その空きブロックとの消去回数差が7)に到達した場合、ブロック番号2の静的データが空きブロック(ブロック番号3)に書き換えられる。図6・8に示すように、書き換え元のブロック番号2は、空きブロックとなる。また、ブロック番号3は、静的データが書き込まれ、空きの状態ではなくなり、及び消去回数が+1されて25となる。

#### [0042]

すなわち、比較例 1 に示すように、NANDメモリ内のブロック毎の消去回数のみによるSWLの発動要否の判断では、全面シーケンシャルライトの繰り返しのような静的データ比率(NANDメモリ内の静的データ量の比率)の低いアクセスパタンにおいて動的データを書き換えてしまうという課題がある。このように近い将来において上書きが発生することが予想される動的データに対して静的データと同様にSWLによってデータを書き換えることが多発すると、信頼性向上に寄与しない書き込みまたは消去の回数(Write/Erase Cycles)が消費されて不要にSSDの寿命を短くすることになる。

#### [0043]

ここで、図7‐1および図7‐2は比較例2にかかるSWLの実行例を示す図である。図7‐1および図7‐2に示す比較例2は、NANDメモリ内のブロック毎の消去回数および消去順序によってSWLの発動要否の判断を行う例を示すものである。比較例1においてアクセスパタンがNANDメモリの全LBA範囲に対する動的データのシーケンシャルライトの繰り返しであった場合、書き換え対象ブロック(例えば、ブロック番号0)に書き込まれるのは動的データであるため、2回目のSWLによる書き換えは無駄である。これに対して、図7‐1に示すように、比較例2は、ブロックのデータを消去した順序である消去順序をブロック毎に記憶しておき、消去回数が多い場合であっても、消去順序の差分が一定量(図7‐1では、例えば消去順序差が56以上)を満たさない場合、SWLの発動を抑制するようにしている。

#### [0044]

しかしながら、比較例 2 は、将来において N A N D メモリの全 L B A 範囲に対してシーケンシャルライトを繰り返すことを想定している。このため、図 7 - 2 に示すように、比較例 2 は、N A N D メモリの狭域の L B A 範囲に対するシーケンシャルライトの繰り返しのような静的データ比率の高いアクセスパタンにおいては、消去順序の差分が一定量(図 7 - 2 では、例えば消去順序差が 5 6 以上)に到達するまで一部の局所的なブロックだけの消去回数を増加させることになる。このため、比較例 2 においては、図 7 - 2 に示すように、静的データを格納するブロック(例えば、ブロック番号 0 , 4 ~ 7 )と動的データを格納するブロック(例えば、ブロック番号 0 , 4 ~ 7 )と動的データを格納するブロック(例えば、ブロック番号 1 ~ 3 )との間の消去回数差の広がりを加速させてしまい、ブロック間の消去回数の平準化を阻害してしまうという課題がある。

# [0045]

そこで、本実施形態のメモリシステム1においては、静的データ比率(NANDメモリ内の静的データ量の比率)の低いアクセスパタンにおいてはSWL発動を抑制し、静的データ比率の高いアクセスパタンにおいてはSWLを発動させて積極的なデータの書き換えを実行することにより、ブロック間の消去回数の平準化を実現する。概略的には、メモリシステム1は、NANDメモリ20のメモリチップ21内のブロックの消去順序の差分履歴を導入することで静的データ比率を推測する。これにより、本実施形態のメモリシステム1は、静的データ比率の低いアクセスパタンであればSWL発動を抑制しつつ、静的データ比率の高いアクセスパタンであればSWLを発動させて消去回数差の平準化を加速させるようにしたものである。

# [0046]

本実施形態のメモリシステム1が実行するSWL処理について詳述する。

# [0047]

20

30

40

50

ここで、図8は、本実施形態のメモリシステム1が実行するSWL処理にかかる機能を示す機能ブロック図である。図8に示すように、CPU11は、プログラムに従うことにより、状態識別部110と、消去回数取得部111と、待時間取得部である消去順序取得部111と、差分算出部113と、推測部114と、決定部115として機能する。

[0048]

状態識別部110は、NANDメモリ20のメモリチップ21内のブロック毎に、ブロックが使用中の状態か空きの状態かの識別を行う。そして、状態識別部110は、ブロックについて識別した状態の情報を、RAM13の管理テーブル132に記憶する。

[0049]

消去回数取得部111は、NANDメモリ20のメモリチップ21内のブロック毎に、ブロックのデータを消去した回数である消去回数をカウントする。そして、消去回数取得部111は、カウントしたブロック毎の消去回数を、RAM13の管理テーブル132に記憶する。より詳細には、消去回数取得部111は、NANDメモリ20の所望のブロックにデータを書き込むにあたって、当該ブロックを消去したことに応じて、消去回数をインクリメントする。

[0050]

消去順序取得部112は、NANDメモリ20のメモリチップ21内のブロック毎に、ブロックのデータを消去した順序である消去順序をカウントする。そして、消去順序取得部112は、カウントしたブロック毎の消去順序を、RAM13の管理テーブル132に記憶する。より詳細には、消去順序取得部112は、NANDメモリ20の所望のブロックにデータを書き込むにあたって、当該ブロックを消去したことに応じて、当該ブロックの次回の消去順序を算出する。

[0051]

差分算出部113は、今回のシーケンシャルライトの周回で書き込み対象となった複数のブロックについて、前回のシーケンシャルライトにおける前回の消去順序の最大値と今回のシーケンシャルライトにおける今回の消去順序の最大値との差分(第2の待時間の差分)を算出する。そして、差分算出部113は、算出した差分を、差分履歴として、リングバッファ131に記憶する。なお、差分算出部113は、新しい差分履歴を、リングバッファ131の最古の差分履歴が書き込まれた位置に上書して記憶する。

[ 0 0 5 2 ]

なお、本実施形態においては、差分算出部113は、差分履歴をリングバッファ131 に記憶するようにしたが、これに限るものではない。例えば、差分算出部113は、差分 履歴を一般的なバッファに記憶するようにしてもよい。

[0053]

推測部 1 1 4 は、書き換え元ブロックに対する、次に実行される書き換えの前後における消去順序の差分(第 1 の待時間の差分)と、リングバッファ 1 3 1 に記憶された差分(第 2 の待時間の差分)とに基づいて、NANDメモリ 2 0 のメモリチップ 2 1 内の静的データ量の比率(静的データ比率)を推測する。推測部 1 1 4 は、リングバッファ 1 3 1 に記憶された消去順序差分(第 2 の待時間の差分)履歴の平均値を係数として、後述する S W L 閾値を変化させる。

[ 0 0 5 4 ]

決定部 1 1 5 は、管理テーブル 1 3 2 に記憶されている書き換え元ブロックの消去回数と書き換え先ブロックの消去回数との差、および推測部 1 1 4 で推測した静的データ比率に基づき、SWLの発動要否を決定する。また、決定部 1 1 5 は、SWLを発動する場合、SWLの発動対象となるブロックを決定する。

[0055]

次に、本実施形態のメモリシステム 1 における S W L の発動要否の判断処理について詳述する。

[0056]

まず、静的データ比率の低いアクセスパタンについてのSWLの発動要否の判断例につ

20

30

40

50

いて説明する。

#### [0057]

図9は、静的データ比率の低いアクセスパタンについてのSWLの発動要否の判断例を示す図である。図9に示す例は、静的データ比率の低いアクセスパタンとして、NANDメモリ20の全LBA範囲に対する動的データのシーケンシャルライトの繰り返しを想定したものである。なお、データの書き換え元のブロックを、使用中のブロック群内において消去回数が最小のブロック(ブロック番号0)とする。また、データの書き換え先のブロックをブロック群内の1つの空きブロック(ブロック番号1)とする。

#### [0058]

まず、決定部115は、書き換え先のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号0)の消去回数との差が、一定の条件(例えば、消去回数差が7)以上であるかを判定する。図9に示す例では、書き換え先のブロック(ブロック番号1)の消去回数は1である。したがって、書き換え先のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号0)の消去回数との差は6であるので、決定部115は、SWLの発動を抑制する。

## [0059]

図9に示す例は、シーケンシャルライトを1周実行する前後の状態を示すものである。なお、図9において、左側に示す管理テーブル132が、シーケンシャルライトを1周実行した後の状態を示し、右側に示す管理テーブル132が、シーケンシャルライトを1周実行した後の状態を示す。図9に示す例では、シーケンシャルライトを1周実行した後、書き換え先のブロック(プロック番号1)の消去回数は1である。したがって、書き換え先のブロック(ブロック番号0)の消去回数との差は7である。決定部115は、書き換え先のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号1)の消去回数とが7)以上であると判定する。決定部115は、判定の結果、書き換え元のブロック(ブロック番号0)から書き換え先のブロック(ブロック番号1)へのSWLを発動することを決定する。

## [0060]

次に、推測部114は、書き換え元のブロック(ブロック番号0)の次回の消去順序と現在の消去順序との差分(第1の待時間の差分)がSWL閾値以上であるかを判定する。ここで、SWL閾値は、消去順序差分履歴の平均値を10倍した値である。

# [0061]

まず、差分算出部113は、書き換え先ブロックの書き換え前後におけるアクセス範囲を示す第2の待時間の差分、すなわち前回のシーケンシャルライトのアクセス範囲における前回の消去順序の最大値と、今回のシーケンシャルライトのアクセス範囲における今回の消去順序の最大値と、の差分を算出する。図9に示す例では、今回のシーケンシャルライトの周回で書き込み対象となった複数のブロックのうち、例えば消去順序が最大であるブロック番号7に着目する。ブロック番号7は、管理テーブル132で管理されているう回のシーケンシャルライトの周回における前回の消去順序の最大値は56であり、管理テーブル132で管理されている今回のシーケンシャルライトの周回を実行後の今回の消去順序の最大値は63である。差分算出部113は、63-56=7を差分履歴として、リングバッファ131に記憶する。図9に示す例では、今回のシーケンシャルライトの周回で書き込み対象となった複数のブロックについて、リングバッファ131に記憶された差分履歴の平均値は7である。

#### [0062]

ここで、差分履歴の平均値は、NANDメモリ20に対するデータのアクセス範囲(レンジ)に関する指標である。すなわち、差分履歴の平均値が大きい(NANDメモリ20のメモリチップ21内のブロック数に近い)ことは、アクセス範囲が、NANDメモリ2

0の広域のLBA範囲に対するアクセスパタンであることを示す。差分履歴の平均値が小さい(NANDメモリ20のメモリチップ21内のブロック数から遠い)ことは、アクセス範囲が、NANDメモリ20の狭域のLBA範囲に対するアクセスパタンであることを示す。

#### [0063]

また、差分履歴の平均値のX倍は、NANDメモリ20のアクセス範囲(レンジ)に対するシーケンシャルライトの周回数Xを示すものである。本実施形態においては、NANDメモリ20の寿命と信頼性とを担保すべく、周回数X=10(周)とした例を示している。

#### [0064]

推測部114は、状態識別部110で使用中であると識別された書き換え元ブロックの、次に実行される書き換えの前後における消去順序の差分(第1の待時間の差分)と、リングバッファ131に記憶された消去順序差分(第2の待時間の差分)履歴の平均値・7、に基づき、メモリシステム1内の静的データ量の比率(静的データ比率)を推測する。図9に示す例では、書き換え元のブロック(ブロック番号0)の次回の消去順序は64であり、書き換え元のブロック(ブロック番号0)の現在の消去順序は0である。したがって、推測部114は、64-0<7×10となることから、書き換え元のブロック(ブロックの第去順序と書き換え元のブロック(ブロック番号0)の現在の消去順序との差が、差分履歴の平均値の10倍(SWL閾値)以上でないと判定する。この場合、推測部114は、静的データ量が少なく、動的データ量が多いとみなし、静的データ比率が低いと推測する。

# [0065]

そして、決定部115は、管理テーブル132に記憶されている書き換え元ブロックの消去回数と書き換え先ブロックの消去回数との差、および推測部114で推測された静的データ比率に基づき、SWLの発動要否の判断を行う。図9に示す例では、決定部115は、書き換え元ブロックの消去回数と書き換え先ブロックの消去回数との差は開いているが、書き換え元候補は動的データであるとみなして、SWLの発動を抑制する。

#### [0066]

次に、静的データ比率の高いアクセスパタンについてのSWLの発動要否の判断例について説明する。

# [0067]

図10は、静的データ比率の高いアクセスパタンについてのSWLの発動要否の判断例を示す図である。図10に示す例は、静的データ比率の高いアクセスパタンとして、NANDメモリ20の全LBA範囲に対する静的データのシーケンシャルライトを1周実施した後、全LBA範囲のうち狭域のLBA範囲に対する動的データのシーケンシャルライトの繰り返しを想定したものである。なお、データの書き換え元のブロックを、使用中のブロック群内において消去回数が最小のブロック(ブロック番号0)とする。また、データの書き換え先のブロックをブロック群内の1つの空きブロック(ブロック番号1)とする

## [0068]

まず、決定部115は、書き換え先のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号0)の消去回数との差が、一定の条件(例えば、消去回数差が7)以上であるかを判定する。図10に示す例では、書き換え先のブロック(ブロック番号1)の消去回数は1である。したがって、書き換え先のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号1)の消去回数と書き換え元のブロック(ブロック番号0)の消去回数との差は6であるので、決定部115は、SWLの発動を抑制する。

# [0069]

図 1 0 に示す例は、シーケンシャルライトを 1 周実行する前後の状態を示すものである。なお、図 1 0 において、左側に示す管理テーブル 1 3 2 が、シーケンシャルライトを 1

10

20

30

20

30

40

50

周実行する前の状態を示し、図10の右側に示す管理テーブル132が、シーケンシャルライトを1周実行した後の状態を示す。図10に示す例では、シーケンシャルライトを1周実行した後、書き換え先のブロック(ブロック番号1)の消去回数は8、書き換え元のブロック(ブロック番号1)の消去回数と1である。したがって、書き換え先のブロック(ブロック番号1)の消去回数との差は7である。決定部115は、書き換え先のブロック(ブロック番号1)の消去回数とと書き換え元のブロック(ブロック番号1)の消去回数とき換え元のブロック(ブロック番号1)の消去回数との差が7とする)以上であると判定する。決定部115は、判定の結果、書き換え元のブロック(ブロック番号0)から書き換え先のブロック(ブロック番号1)へのSWLを発動することを決定する。

[0070]

次に、推測部114は、書き換え元のブロック(ブロック番号0)の次回の消去順序と現在の消去順序との差分が、SWL閾値以上であるかを判定する。ここでも、SWL閾値は、消去順序差分履歴の平均値を10倍した値である。

[0071]

まず、差分算出部113は、前回のシーケンシャルライトのアクセス範囲における前回の消去順序の最大値と、今回のシーケンシャルライトのアクセス範囲における今回の消去順序の最大値と、の差分を算出する。図10に示す例では、今回のシーケンシャルライトの周回で書き込み対象となった複数のブロックのうち、例えば消去順序が最大であるブロック番号2に着目する。ブロック番号2は、管理テーブル132で管理されている前回のジーケンシャルライトの周回における前回の消去順序の最大値は26であり、管理テーブル132で管理されている今回のシーケンシャルライトの周回を実行後の今回の消去順序の最大値は28である。差分算出部113は、28・26=2を差分履歴として、リングバッファ131に記憶する。図10に示す例では、今回のシーケンシャルライトの周回で書き込み対象となった複数のブロックについて、リングバッファ131に記憶された差分履歴の平均値は2である。

[0072]

なお、本実施形態においては、図9および図10に示すように、リングバッファ131は、4つのバッファエントリに差分履歴を順に記憶するようにしているが、これに限るものではなく、5以上のバッファエントリに差分履歴を順に記憶するようにしてもよい。具体的には、リングバッファ131は、NANDメモリ20のプロック数に応じた数分のバッファエントリに差分履歴を順に記憶するようにしてもよい。なお、バッファエントリの数は可変であってもよい。

[0073]

推測部114は、状態識別部110で使用中であると識別された書き換え元ブロックの、次に実行される書き換えの前後における消去順序の差分(第1の待時間の差分)と、リングバッファ131に記憶された消去順序差分(第2の待時間の差分)履歴の平均値・2に基づき、メモリシステム1内の静的データ量の比率(静的データ比率)を推測する。図10に示す例では、書き換え元のブロック(ブロック番号0)の次回の消去順序は29であり、書き換え元のブロック(ブロック番号0)の現在の消去順序は0である。したがって、推測部114は、29・0>2×10となることから、書き換え元のブロック(ブロック番号0)の現在の消去順序との差が、差分履歴の平均値の10倍(SWL閾値)以上であると判定する。この場合、推測部114は、静的データ量が多く、動的データ量が少ないとみなし、静的データ比率が高いと推測する。

[0074]

そして、決定部115は、管理テーブル132に記憶されている書き換え元ブロックの消去回数と書き換え先ブロックの消去回数との差、および推測部114で推測された静的データ比率に基づき、SWLの発動要否の判断を行う。図10に示す例では、決定部115は、消去回数差が開いており、書き換え元候補は静的データであるとみなして、SWL

を発動する。

#### [0075]

図11は、SWLの処理の流れを示すフローチャートである。

#### [0076]

図11に示すように、まず、状態識別部110は、NANDメモリ20のメモリチップ 21内のブロック毎に、使用中の状態か空きの状態かの識別を行う。そして、状態識別部 110は、識別した状態の情報を、RAM13の管理テーブル132に記憶する(S1)

#### [0077]

次に、推測部114は、状態識別部110で使用中であると識別された所定の書き換え元ブロックの書き換えの前後における第1の待時間の差分と、状態識別部110で使用中でないと識別された所定の書き換え先ブロックの書き換えの前後におけるアクセス範囲に対応する第2の待時間の差分とに基づいて、NANDメモリ20のメモリチップ21内の静的データ量の比率である静的データ比率を推測する(S2)。

#### [0078]

次に、決定部 1 1 5 は、書き換え元ブロックの消去回数と書き換え先ブロックの消去回数との差、および静的データ比率に基づき、ブロック毎の消去回数を平準化する SWL(Static Wear Leveling)の発動要否と SWLの発動対象プロックとを決定する(S3)。

# [0079]

このように、本実施形態のメモリシステム1によれば、ブロック毎の消去回数およびブロック毎の待時間だけでなく、静的データ比率も含めて、SWL発動の判断と発動対象ブロックとを決定することで、アクセスパタン毎の判断を適正化することができる。

## [0800]

本実施形態のメモリシステム1によれば、書き換え先ブロックの書き換え前後における待時間(例えば、消去順序)の差分値の履歴を記憶し、この履歴からNANDメモリ20内の静的データ量の比率である静的データ比率を推測する。そして、メモリシステム1は、推測した静的データ比率からSWLの発動と対象ブロックを決定する。

# [0081]

これにより、NANDメモリ20の全LBA範囲に対する動的データのシーケンシャルライトの繰り返しなどの動的データ比率が高いアクセスパタンにおいては、動的データの書き換えを抑制することができる。また、NANDメモリ20の全LBA範囲のうち狭域のLBA範囲に対する動的データのシーケンシャルライトの繰り返しのような動的データ比率が低いアクセスパタンにおいては、積極的な書き換えによりブロック毎の消去回数の平準化を実現することができる。

# [0082]

すなわち、本実施形態のメモリシステム 1 によれば、静的データ比率の低いアクセスパタンにおいて動的データを書き換えてしまうという課題、静的データ比率の高いアクセスパタンにおいてブロック毎の消去回数差の平準化を阻害してしまうという課題、を回避することができる。

# [0083]

本実施形態のメモリシステム 1 のメモリコントローラ 1 0 で実行されるプログラムは、N A N D メモリ 2 0 等に予め組み込まれて提供される。

#### [0084]

本実施形態のメモリシステム 1 のメモリコントローラ 1 0 で実行されるプログラムは、インストール可能な形式または実行可能な形式のファイルで C D - R O M、フレキシブルディスク (FD)、CD-R、DVD (Digital Versatile Disc)等のコンピュータで読み取り可能な記録媒体に記録して提供するように構成してもよい。

# [0085]

さらに、本実施形態のメモリシステム1のメモリコントローラ10で実行されるプログ

10

20

30

40

ラムを、インターネット等のネットワークに接続されたコンピュータ上に格納し、ネットワーク経由でダウンロードさせることにより提供するように構成しても良い。また、本実施形態のメモリシステム 1 のメモリコントローラ 1 0 で実行されるプログラムをインターネット等のネットワーク経由で提供または配布するように構成しても良い。

[0086]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる

10

[0087]

なお、本技術は以下のような構成も採ることができる。

( 1 )消 去 単 位 で あ る ブ ロ ッ ク を 複 数 含 む 不 揮 発 性 メ モ リ と 、

前記不揮発性メモリに接続されるとともにホストに接続可能であるコントローラと、 を備え、

前記コントローラは、

前記複数のブロック毎に、データが記憶されている状態を示す使用中であるか否かを示す第 1 情報、消去した回数を示す第 2 情報、及び次の消去までの待時間を示す第 3 情報を管理し、

20

30

前記ホストから第1のシーケンシャルライトの要求を受信し、

受信した前記第1のシーケンシャルライトを実行し、

前記第 1 のシーケンシャルライトの後に前記ホストから第 2 のシーケンシャルライトの要求を受信し、

受信した前記第2のシーケンシャルライトを実行するに際し、第1の差分と、第2の差分と、第3の差分と、に基づき、前記第1情報が前記使用中を示している第1ブロックに対する前記複数のブロック毎の消去回数を平準化する処理の実行要否を決定し、

前記第1の差分は、前記第1ブロックに対して次に実行されるデータのライト前後における前記第1ブロックの待時間の差であり、

前記第2の差分は、前記第2のシーケンシャルライトの書き込み対象となった複数のブロックについて、前記第1のシーケンシャルライトにおける消去順序の第1の最大値と前記第2のシーケンシャルライトにおける消去順序の第2最大値との差分に対応し、

前記第3の差分は、前記第1ブロックの消去回数と第1情報が前記使用中を示していない第2ブロックの消去回数との差である、

メモリシステム。

[ 0 0 8 8 ]

(2)前記コントローラは、今回のシーケンシャルライトのアクセスパタンが、前記複数のブロックに対する、前記不揮発性メモリ内の静的データ量の比率である静的データ比率の低いアクセスパタンである場合、前記平準化する処理を実行せず、前記今回のシーケンシャルライトのアクセスパタンが、前記複数のブロックに対する前記静的データ比率の高いアクセスパタンである場合、前記平準化する処理として、書き換え元ブロックに記憶されているデータを書き換え先ブロックへ書き換える処理を実行する、

40

(1)に記載のメモリシステム。

[0089]

(3)前記コントローラは、前記第1の差分と、前記第2の差分の履歴に基づく閾値と、の比較に応じて、前記不揮発性メモリ内の静的データ量の比率である静的データ比率を推測する、

(1)に記載のメモリシステム。

[0090]

(4)前記第2の差分の履歴は、リングバッファに保存される、

(1)に記載のメモリシステム。

#### [0091]

(5)前記ブロック毎の待時間は、前記不揮発性メモリ内のブロックのデータを消去した順序である消去順序、前記不揮発性メモリ内のブロックのデータを消去した時刻である消去時刻、又は前記不揮発性メモリ内のブロックからデータを消去した後の経過時間である

(1)に記載のメモリシステム。

#### [0092]

(6)消去単位であるブロックを複数含む不揮発性メモリを備えるメモリシステムの制御 方法であって、

10

前記複数のブロック毎に、データが記憶されている状態を示す使用中であるか否かを示す第 1 情報、消去した回数を示す第 2 情報、及び次の消去までの待時間を示す第 3 情報を管理することと、

ホストから第1のシーケンシャルライトの要求を受信することと、

受信した前記第1のシーケンシャルライトを実行することと、

前記第1のシーケンシャルライトの後に前記ホストから第2のシーケンシャルライトの要求を受信することと、

受信した前記第2のシーケンシャルライトを実行するに際し、第1の差分と、第2の差分と、第3の差分と、に基づき、前記第1情報が前記使用中を示している第1ブロックに対する前記複数のブロック毎の消去回数を平準化する処理の実行要否を決定することと、を含み、

20

前記第1の差分は、前記第1ブロックに対して次に実行されるデータのライト前後における前記第1ブロックの待時間の差であり、

前記第2の差分は、前記第2のシーケンシャルライトの書き込み対象となった複数のブロックについて、前記第1のシーケンシャルライトにおける消去順序の第1の最大値と前記第2のシーケンシャルライトにおける消去順序の第2最大値との差分に対応し、

前記第3の差分は、前記第1ブロックの消去回数と第1情報が前記使用中を示していない第2ブロックの消去回数との差である、

メモリシステムの制御方法。

## 【符号の説明】

[0093]

30

- 1 メモリシステム

- 2 0 不揮発性メモリ

- 1 1 0 状態識別部

- 1 1 1 消去回数取得部

- 1 1 2 待時間取得部

- 1 1 4 推測部

- 1 1 5 決定部

- 131 リングバッファ

【図面】

【図1】

【図2】

| ブロック番号 | 空き  | 消去回数 | 消去順序 |

|--------|-----|------|------|

| 0      | 使用中 | 1    | 0    |

| 1      | 空き  | 17   | 54   |

| 2      | 空き  | 17   | 55   |

| 3      | 使用中 | 17   | 56   |

| 4      | 使用中 | 1    | 5    |

| 5      | 使用中 | 1    | 6    |

| 6      | 使用中 | 1    | 7    |

| 7      | 使用中 | 1    | 8    |

20

30

【図3】

【図4】

【図5】

【図6-1】

| ブロック番号 | 空き | 消去回数 |   | ■ 静的データ        |

|--------|----|------|---|----------------|

| 0      | ×  | 1    |   | ■動的データ<br>書込み順 |

| 1      | 0  | 8    | ✓ |                |

| 2 1    | ×  | 8    |   |                |

| 3 2    | ×  | 8    |   |                |

| 4 3    | ×  | 8    |   |                |

| 5 4    | ×  | 8    |   |                |

| 6 5    | ×  | 8    |   |                |

| 7 6    | ×  | 8    |   |                |

10

【図6-2】

| ブロック番号 | 空き | 消去回数 |

|--------|----|------|

| 0      | 0  | 1    |

| 1      | ×  | 9    |

| 2 1    | ×  | 8    |

| 3 2    | ×  | 8    |

| 4 3    | ×  | 8    |

| 5 4    | ×  | 8    |

| 6 5    | ×  | 8    |

| 7 6    | ×  | 8    |

【図6-3】

| ブロック番号 | 空き | 消去回数 |   |

|--------|----|------|---|

| 0 6    | ×  | 9    |   |

| 1      | ×  | 9    |   |

| 2      | 0  | 16   | ✓ |

| 3 1    | ×  | 16   |   |

| 4 2    | ×  | 16   |   |

| 5 3    | ×  | 16   |   |

| 6 4    | ×  | 16   |   |

| 7 5    | ×  | 16   |   |

40

# 【図6-4】

| ブロック番号 | 空き | 消去回数 |

|--------|----|------|

| 0 6    | ×  | 9    |

| 1      | 0  | 9    |

| 2      | ×  | 17   |

| 3 1    | ×  | 16   |

| 4 2    | ×  | 16   |

| 5 3    | ×  | 16   |

| 6 4    | ×  | 16   |

| 7 5    | ×  | 16   |

# 【図6-5】

| 動的データが<br>引越元候補になる |      |    |    |      |         |

|--------------------|------|----|----|------|---------|

|                    |      |    |    |      |         |

|                    | ブロック | 番号 | 空き | 消去回数 |         |

|                    | 0    | 5  | ×  | 9    |         |

|                    | 1    | 6  | ×  | 10   | $  \  $ |

|                    | 2    |    | ×  | 17   |         |

|                    | 3    |    | 0  | 16   | ✓       |

|                    | 4    | _  | ×  | 16   |         |

|                    | 5    | 2  | ×  | 16   |         |

|                    | 6    | 3  | ×  | 16   |         |

|                    | 7    | 4  | ×  | 16   |         |

10

# 【図6-6】

| ブロック番号 | 空き | 消去回数 |

|--------|----|------|

| 0      | 0  | 9    |

| 1 6    | ×  | 10   |

| 2      | ×  | 17   |

| 3 5    | ×  | 17   |

| 4 1    | ×  | 16   |

| 5 2    | ×  | 16   |

| 6 3    | ×  | 16   |

| 7 4    | ×  | 16   |

# 【図6-7】

| ブロック番号 | 空き | 消去回数 |   |

|--------|----|------|---|

| 0 2    | ×  | 17   |   |

| 1 1    | ×  | 17   |   |

| 2      | ×  | 17   |   |

| 3      | 0  | 24   | ~ |

| 4 3    | ×  | 24   |   |

| 5 4    | ×  | 24   |   |

| 6 5    | ×  | 24   |   |

| 7 6    | ×  | 24   |   |

20

30

# 【図6-8】

|        |    | W - L W |

|--------|----|---------|

| ブロック番号 | 空き | 消去回数    |

| 0 2    | ×  | 17      |

| 1      | ×  | 17      |

| 2      | 0  | 17      |

| 3      | ×  | 25      |

| 4 3    | ×  | 24      |

| 5 4    | ×  | 24      |

| 6 5    | ×  | 24      |

| 7 6    | ×  | 24      |

# 【図7-1】

【図7-2】

SWL条件は消去回数差7以上 かつ消去順序差56以上とする

| ブロック<br>番号 | 使用中<br>or空き | 消去<br>回数 | 消去<br>順序 |                 |

|------------|-------------|----------|----------|-----------------|

| 0          | 使用中         | 1        | 0 -      | 消去回数差が<br>開きすぎる |

| 1          | 空き          | 17       | 54 ◀     | ▶ 開きすぎる         |

| 2          | 空き          | 17       | 55       |                 |

| 3          | 使用中         | 17       | 56       |                 |

| 4          | 使用中         | 1        | 5        |                 |

| 5          | 使用中         | 1        | 6        |                 |

| 6          | 使用中         | 1        | 7        |                 |

| 7          | 使用中         | 1        | 8        |                 |

【図8】

40

10

20

# 【図9】

【図10】

# 【図11】

30

- 【手続補正書】

- 【提出日】令和3年12月23日(2021.12.23)

- 【手続補正1】

- 【補正対象書類名】明細書

- 【補正対象項目名】0004

- 【補正方法】変更

- 【補正の内容】

- [ 0 0 0 4 ]

- 【特許文献1】米国特許第10417123号明細書

- 【特許文献2】米国特許出願公開第2019/0205245号明細書

- 【 特 許 文 献 3 】 米 国 特 許 出 願 公 開 第 2 0 1 4 / 0 1 8 1 4 3 4 号 明 細 書

10

30