### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2020-109605 (P2020-109605A)

(43) 公開日 令和2年7月16日(2020.7.16)

(51) Int. Cl. F. I

テーマコード (参考)

GO6F 9/46 (2006.01)

GO6F 9/46 410

審査請求 有 請求項の数 17 OL 外国語出願 (全 37 頁)

(21) 出願番号 特願2019-113329 (P2019-113329)

(31) 優先権主張番号 1821301.7

(32) 優先日 平成30年12月31日 (2018.12.31)

(33) 優先権主張国・地域又は機関

英国 (GB)

(71) 出願人 518371892

グラフコアー リミテッド

Graphcore Limited イギリス国, ビーエス1 2ピーエイチ, ブリストル, ワイン ストリート 11-

19

11-19 Wine Street, B ristol, BS1 2PH, Unit

ed Kingdom

(74)代理人 100169904

弁理士 村井 康司

(74)代理人 100121120

弁理士 渡辺 尚

最終頁に続く

(54) 【発明の名称】 マルチスレッドプロセッサのレジスタファイル

### (57)【要約】

【課題】マルチスレッドプロセッサのレジスタファイル を提供する。

【解決手段】並列スレッドを実行するためのバレルスレッド実行ユニットと、各並列スレッドに対するコンテキストレジスタのそれぞれのセットを含む1つまたは複数のレジスタファイルとを含むプロセッサ。レジスタファイルのうちの1つは、並列スレッドのいくつかまたは含む、プロセッサの命令セットにおいて定義される命令のタイプは、オペランドを有する算術命令を含み、オペランドを有する算術命令を含み、オペランドは、算術命令が実行されるスレッドの算術レジスタのそれぞれのセットの中から送信元および送信先を指定する。実行ユニットは、算術命令のオペコードに応答して、送信元からの入力に共有重みレジスタのうちの少なくとも1つからの重みのうちの少なくとも1つを乗じることを含む演算を実行し、結果を送信先に入れるように構成される。

【選択図】図4

### 【特許請求の範囲】

### 【請求項1】

1 つまたは複数のレジスタファイルと、

命令セットにおいて定義される命令タイプのインスタンスを実行するように構成された 実行ユニットであって、前記命令セットの各命令が、オペコードおよび 0 またはそれ以上 のオペランドからなる、実行ユニットと

を含むプロセッサであって、

前記実行ユニットは、多数の並列スレッドを実行するように構成されたバレルスレッド 実行ユニットであり、前記並列スレッドの各々は、インターリーブされた時間スロットの 繰り返しシーケンスに対応し、前記1つまたは複数のレジスタファイルは、前記並列スレ ッドの各々に対し、前記対応するスレッドのプログラム状態を保持するように構成された コンテキストレジスタのそれぞれのセットを含み、コンテキストレジスタの各セットは、 前記対応するスレッドによる使用のための算術オペランドレジスタの対応するセットを含 み、

前記1つまたは複数のレジスタファイルのうちの1つは、前記並列スレッドのいくつかまたはすべてに共通の共有の重みレジスタのセットをさらに含み、

前記命令セットにおいて定義される前記命令のタイプは、オペランドを有する算術命令を含み、前記オペランドは、前記算術命令が実行される前記スレッドの算術レジスタの前記対応するセットの中から送信元および送信先を指定し、

前記実行ユニットは、前記算術命令の前記オペコードに応答して、前記送信元からの入力に前記共有の重みレジスタのうちの少なくとも1つを乗じることを含む演算を実行し、結果を前記送信先に入れるように構成される、プロセッサ。

#### 【請求項2】

前記共有の重みレジスタのうちの前記少なくとも1つは、前記算術命令の前記オペコードから暗黙的であり、前記算術命令のいかなるオペランドによって指定されない、請求項1に記載のプロセッサ。

### 【請求項3】

前記算術命令は、前記共有の重みレジスタのセットの中から前記共有の重みレジスタの うち少なくとも1つを指定するさらなるオペランドを取る、請求項1に記載のプロセッサ

#### 【請求項4】

前記入力は、ベクトルを含み、前記乗算は、前記入力と前記共有の重みレジスタからの 重みのベクトルとのドット積を含む、請求項1~3のいずれか一項に記載のプロセッサ。

### 【請求項5】

前記共有の重みレジスタのうちの前記少なくとも1つは、複数のサブセットのうち前記 共有の重みレジスタのサブセットを含み、各サブセットは、それぞれの重みベクトルを保 持し、前記さらなるオペランドは、前記乗算において使用するためにどのサブセットから 前記重みベクトルを取り入れるかを選択する、請求項3または4に記載のプロセッサ。

#### 【請求頃6】

前記算術命令は、ベクトルドット積命令、累積ベクトルドット積命令、行列積命令、累積行列積命令または畳み込み命令のうちの1つを含む、請求項1~5のいずれか一項に記載のプロセッサ。

### 【請求項7】

前記並列スレッドは、複数のワーカースレッドを含み、前記実行ユニットは、少なくともいくつかの時間に、前記ワーカースレッドを管理するように構成された少なくとも1つのスーパーバイザスレッドを含むスーパーバイザサププログラムを実行するようにさらに構成される、請求項1~6のいずれか一項に記載のプロセッサ。

### 【請求項8】

前記スーパーバイザサブプログラムは、前記共有の重みレジスタファイルに前記重みを書き込むように構成される、請求項7に記載のプロセッサ。

10

20

30

40

#### 【請求項9】

前記共有の重みレジスタの前記重みは、前記スーパーバイザサブプログラムのみが書き 込むことができ、前記ワーカースレッドは、前記共有の重みレジスタを読み取ることしか できないように構成される、請求項8に記載のプロセッサ。

### 【請求項10】

前記コンテキストレジスタは、並列に実行することができる前記ワーカースレッドの各 々に対する前記コンテキストレジスタのセットのうち対応する1つを含み、コンテキスト レジスタの追加のセットは、前記スーパーバイザサブプログラムのプログラム状態を保持 するように構成される、請求項7~9のいずれか一項に記載のプロセッサ。

### 【請求項11】

前記スーパーバイザサブプログラムは、最初に前記スロットのすべてにおいて動作する ことによって開始し、前記ワーカースレッドを起動する前に前記重みを書き込むように構 成され、

前記スーパーバイザサブプログラムは、前記スーパーバイザサブプログラムが動作して いた前記スロットの各々を対応する前記ワーカースレッドに委ねることによって、前記ワ カースレッドを起動する、請求項10に記載のプロセッサ。

### 【請求項12】

前記命令セットは、実行命令を含み、前記実行命令は、前記スーパーバイザサブプログ ラムの一部として実行されると、前記実行命令が実行された前記スロットを前記ワーカー スレッドのうちの1つに委ね、前記スーパーバイザサブプログラムの代わりに前記ワーカ - スレッドがそのスロットにおいて起動される、請求項11に記載のプロセッサ。

前記命令セットは、終了命令を含み、前記終了命令は、前記ワーカースレッドのうちの 1つの一部として実行されると、前記終了命令が実行された前記スロットを前記スーパー バ イ ザ サ ブ プ ロ グ ラ ム に 返 し 、 前 記 ワ ー カ ー ス レ ッ ド の 代 わ り に 前 記 ス ー パ ー バ イ ザ サ ブ プログラムがそのスロットにおいて再び実行を続ける、請求項12に記載のプロセッサ。

### 【請求項14】

前 記 レ ジ ス タ フ ァ イ ル は 、 各 並 列 ワ ー カ ー ス レ ッ ド に 対 す る 別 個 の 算 術 レ ジ ス タ フ ァ イ ルを含み、前記それぞれの算術レジスタファイルは、前記それぞれの算術オペランドレジ スタを含む、請求項7~13のいずれか一項に記載のプロセッサ。

#### 【請求項15】

前 記 レ ジ ス タ フ ァ イ ル は 、 前 記 重 み レ ジ ス タ を 含 む 別 個 の 重 み レ ジ ス タ フ ァ イ ル を 含 む 、請求項14に記載のプロセッサ。

### 【請求項16】

前記重みレジスタファイルは、前記スーパーバイザサブプログラムのみが書き込むこと ができ、前記ワーカースレッドは前記重みレジスタファイルを読み取ることしかできない ように構成される、請求項15に記載のプロセッサ。

### 【請求項17】

請求項1~16のいずれか一項に従って構成されたプロセッサを操作する方法であって 、 前 記 実 行 ユ ニ ッ ト を 通 じ て 前 記 プ ロ セ ッ サ 上 で 前 記 算 術 命 令 の 1 つ ま た は 複 数 の イ ン ス タンスを含むプログラムを実行するステップを含む、方法。

【発明の詳細な説明】

### 【技術分野】

#### [00001]

本開示は、マルチスレッドプロセッサにおいて実行される機械語命令による使用のため のレジスタファイルの構成に関する。

### 【背景技術】

### [0002]

グラフィックス処理装置(GPU)およびデジタル信号プロセッサ(DSP)などの特 定のアプリケーション用に設計されたプロセッサの開発への関心が高まってきている。最 10

20

30

40

近関心を集めた別のタイプのアプリケーション特有のプロセッサは、出願人によって「IPU(intelligence processing unit)」(知能処理装置)と呼ばれる機械知能アプリケーション専用のものである。これらは、例えば、ニューラルネットワークなどの知識モデルを訓練するかまたは知識モデルの訓練を補助するため、あるいは、そのようなモデルに基づいて予測もしくは推論を実行するかまたは予測もしくは推論の実行を補助するために、ホストによって割り当てられた仕事を実行するように構成されたアクセラレータプロセッサとして採用することができる。

### [0003]

機械知能アルゴリズムは、複数の相互接続ノードのグラフによって表すことができる「 知識モデル」に反復更新を実行することに基づく。各ノードは、その入力の関数を表す。 ノードは、グラフへの入力を受信するものもあれば、1つまたは複数の他のノードからの 入力を受信するものもある一方で、ノードの出力は、他のノードの入力を形成するものも あれば、グラフの出力を提供するものもある(いくつかの事例では、所定のノードは、こ れらのグラフへの入力、グラフからの出力および他のノードとの接続のすべてを有するも のさえもあり得る)。さらに、各ノードにおける関数は、1つまたは複数のそれぞれのパ ラメータ(例えば、重み)によってパラメータ化される。学習段階では、経験に基づく入 カデータセットに基づいて、グラフが全体として、可能な入力の範囲に対して所望の出力 を生成するように、様々なパラメータに対する値を見出すことを目的とする。この学習を 行うための様々なアルゴリズムは、確率的勾配降下法に基づく誤差逆伝播アルゴリズムな ど、当技術分野において知られている。入力データに基づく複数の反復にわたり、パラメ ータは、それらの誤差を減少するように徐々に調節され、グラフは、解に向けて収束する 。次いで、後続の段階では、学習済みのモデルを使用して、指定された入力セットに与え られる出力の予測を行うこと、または、指定された出力セットに与えられる入力(原因) に関する推論を行うことができる。

#### [0004]

機械知能アプリケーション用に設計されたプロセッサは、機械知能アプリケーションにおいて一般的に採用されている算術演算を実行するための専用命令をプロセッサの命令セットに含み得る(命令セットは、機械語命令タイプの基本セットであり、プロセッサの実行ユニットは、それぞれのオペコードおよび0またはそれ以上のオペランドによって定義されるタイプの各々を認識するように構成される)。例えば、ニューラルネットワークを支がの機械知能アプリケーションにおいて必要な共通の演算は、入力データセットにわたるカーネルの畳み込みであり、カーネルは、ニューラルネットワークのノードの重みを表す。データにわたって大きなサイズのカーネルの畳み込みを実行するため、畳み込みは、着数のベクトルまたは行列積に分解することができ、その各々は、後続の積の出力と累まする部分和を出力する。畳み込みの実行において使用するためのベクトルおよび行列乗算タイプの演算を実行するための専用の算術命令をプロセッサの命令セットに含むプロセッサは、既に存在している。

### 【発明の概要】

【課題を解決するための手段】

#### [0005]

プロセッサは、複数のプログラムスレッドの並列実行に対するサポートを提供することもできる。このサポートは、典型的には、各スレッドに対するコンテキストレジスタのそれぞれのセットを含み、各セットは、並列に実行される多数のスレッドのうちのそれぞれのスレッドのプログラム状態(「コンテキスト」)を保持するために使用される。所定のスレッドのコンテキストレジスタに保持されるプログラム状態は、典型的には、そのスレッドに対するプログラムカウンタと、スレッドの状態(例えば、一時停止している、実行されているなど)を記録する1つまたは複数の制御状態レジスタと、それぞれのスレッドの算術命令に基づいて操作される値およびそれぞれのスレッドの算術命令によって出力される値を一時的に保持するための算術オペランドレジスタを含む多数のオペランドレジスタを含む。異なる並列スレッドは、異なるそれぞれの実行時間スロットにおいて共通の

10

20

30

40

実行パイプラインを通じて時間的にインターリーブ(interleave)され、各スロットは、 コンテキストレジスタのセットのうちの異なるそれぞれのコンテキストレジスタのレジス タのみを利用する。

#### [0006]

従来の方式では、各スレッドは、各スレッドに対する別個の算術レジスタファイルの算術オペランドレジスタのそれ自体の対応するセットを含む。所定のスレッドの一部として命令が実行される際、その命令は、暗黙的に、その特定のスレッドの算術レジスタファイルの算術オペランドレジスタを常に使用する。

### [0007]

スレッドが、実際に、同じオペランド値のいくつかに基づいて動作することがある一方で、各スレッドに対して特定の値を有する他のいくつかのオペランドに基づいて、各スレッドに対して特定の値をしたが知られている。その例として、各でともあるアプリケーションが発生しうで、カの世の大力では、大きでは行列を乗りがある。一つでは、カークに共通の重みのカーネットワーク発生し、多くのノードは、実際に、の主が、異なる接続を有する。例えば、ある特徴を検出するためにそれぞれのように共通の重みのカーネルを畳み込むが、カークに共通の重みのカーネルを畳み込むがでは、ここの共行では、が構成されるシナリオを考えるの共ののメードの処理を実行するようにないがでは、が構成されるシナリオでは、所定の算術命令が、スレッド間でよる1つまたは複数のオペランドと、個々の対応するスレッドに特有の1つまたは複数のオペランドと、個々の対応するスレッドに特有の1つまたは複数のオペランドと、は基づいて動作可能となるメカニズムを提供することになるいかなるアプリケーションにおいても生じ得る。

#### [00008]

本明細書で開示される一態様によれば、1つまたは複数のレジスタファイルと、命令セ ットにおいて定義される命令タイプのインスタンスを実行するように構成された実行ユニ ットとを含むプロセッサが提供され、命令セットの各命令は、オペコードおよび0または それ以上のオペランドからなる。実行ユニットは、多数の並列スレッドを実行するように 構成されたバレルスレッド実行ユニットであり、並列スレッドの各々は、インターリーブ された時間スロットの繰り返しシーケンスのうちの異なるそれぞれのものであり、並列ス レッドの各々に対し、 1 つまたは複数のレジスタファイルは、それぞれのスレッドのプロ グラム状態を保持するように構成されたコンテキストレジスタのそれぞれのセットを含み コンテキストレジスタの各セットは、それぞれのスレッドによる使用のための算術オペ ランドレジスタのそれぞれのセットを含む。 1 つまたは複数のレジスタファイルのうちの 1 つは、並列スレッドのいくつかまたはすべてに共通の共有重みレジスタのセットをさら に含む。 命令セットにおいて定義される命令のタイプは、オペランドを有する算術命令を 含み、オペランドは、算術命令が実行されるスレッドの算術レジスタのそれぞれのセット の中から送信元および送信先を指定する。実行ユニットは、算術命令のオペコードに応答 して、上記送信元からの入力に共有重みレジスタのうちの少なくとも1つからの重みのう ちの少なくとも1つを乗じることを含む演算を実行し、結果を上記送信先に入れるように 構成される。

### [0009]

実施形態では、共有重みレジスタのうちの上記少なくとも 1 つは、算術命令のオペコードから暗黙的であってもよく、算術命令のいかなるオペランドによっても指定されなくて もよい。

#### [0010]

実施形態では、算術命令は、共有重みレジスタのセットの中から共有重みレジスタのうちの上記少なくとも 1 つを指定するさらなるオペランドを取ってもよい。

### [0011]

10

20

30

実施形態では、入力は、ベクトルを含んでもよく、乗算は、入力と共有重みレジスタからの重みのベクトルとのドット積を含んでもよい。

### [0012]

実施形態では、共有重みレジスタのうちの上記少なくとも1つは、多数のサブセットの中から共有重みレジスタのサブセットを含んでもよく、各サブセットは、それぞれの重みベクトルを保持し、上記さらなるオペランドは、上記乗算において使用するためにどのサブセットから重みベクトルを取り入れるかを選択可能であってもよい。

### [0013]

実施形態では、上記算術命令は、ベクトルドット積命令、累積ベクトルドット積命令、 行列積命令、累積行列積命令または畳み込み命令のうちの1つを含んでもよい。

[0014]

実施形態では、並列スレッドは、多数のワーカースレッドを含んでもよく、実行ユニットは、少なくともいくつかの時間に、ワーカースレッドを管理するように構成された少なくとも1つのスーパーバイザスレッドを含むスーパーバイザサブプログラムを実行するようにさらに構成されてもよい。

[0015]

実施形態では、スーパーバイザサブプログラムは、共有重みレジスタファイルに重みを 書き込むように構成されてもよい。

[0016]

実施形態では、共有重みレジスタの重みは、スーパーバイザサブプログラムのみが書き 込むことができ、ワーカースレッドは、共有重みレジスタを読み取りのみ可能であっても よい。

[0017]

実施形態では、コンテキストレジスタは、並列に実行することができるワーカースレッドの各々に対するコンテキストレジスタのセットのそれぞれを含んでもよく、コンテキストレジスタの追加のセットは、スーパーバイザサブプログラムのプログラム状態を保持するように構成されてもよい。

[0018]

実施形態では、スーパーバイザサブプログラムは、最初にスロットのすべてにおいて動作することによって開始し、ワーカースレッドを起動する前に重みを書き込むように構成されてもよい。すなわち、スーパーバイザサブプログラムは、スーパーバイザサブプログラムが最初に動作していたいくつかまたはすべてのスロットの各々を対応するワーカースレッドに委ねることによって各ワーカースレッドを起動してもよい。

[0019]

実施形態では、命令セットは、実行(run)命令を含んでもよい。実行命令は、スーパーバイザサブプログラムの一部として実行されると、実行命令が実行されたスロットをワーカースレッドのうちの1つに委ね、スーパーバイザサブプログラムの代わりにワーカースレッドをそのスロットにおいて起動させる。

[0020]

実施形態では、命令セットは、終了(exit)命令を含んでもよい。終了命令は、ワーカースレッドのうちの1つの一部として実行されると、終了命令が実行されたスロットをスーパーバイザサブプログラムに返し、ワーカースレッドの代わりに、スーパーバイザサブプログラムがそのスロットにおいて再び実行を続ける。

[ 0 0 2 1 ]

実施形態では、レジスタファイルは、各並列ワーカースレッドに対する別個の算術レジスタファイルを含み、それぞれの算術レジスタファイルは、それぞれの算術オペランドレジスタを含む。

[0022]

実施形態では、レジスタファイルは、重みレジスタを含む別個の重みレジスタファイル を含んでもよい。 10

20

30

40

#### [ 0 0 2 3 ]

実施形態では、重みレジスタファイルは、スーパーバイザサブプログラムのみが書き込むことができ、ワーカースレッドは重みレジスタファイルを読み取ることしかできないように構成されてもよい。

### [0024]

本発明の別の態様によれば、上記または本明細書の他の場所の任意の実施形態に従って構成されたプロセッサを操作する方法であって、実行ユニットを通じてプロセッサ上で算術命令の1つまたは複数のインスタンスを含むプログラムを実行するステップを含む、方法が提供される。

### [0025]

本開示の実施形態を理解することを支援するため、および、そのような実施形態をどのように実施するかを示すため、単なる例示として、添付の図面を参照する。

【図面の簡単な説明】

[0026]

- 【図1】例示的なマルチスレッドプロセッサの概略ブロック図である。

- 【図2】インターリーブされた時間スロットのスキームを概略的に示す。

- 【 図 3 】 多 数 の イ ン タ ー リ ー ブ さ れ た 時 間 ス ロ ッ ト に お い て 実 行 す る ス ー パ ー バ イ ザ ス レ ッ ド お よ び 多 数 の ワ ー カ ー ス レ ッ ド を 概 略 的 に 示 す 。

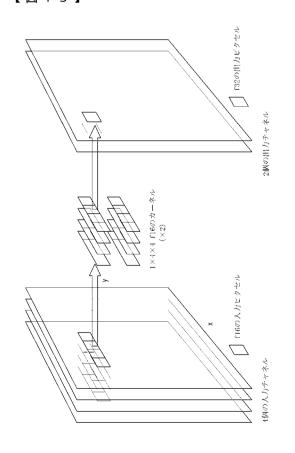

- 【 図 4 】 例 示 的 な プ ロ セ ッ サ の 論 理 ブ ロ ッ ク 構 造 を 概 略 的 に 示 す 。

- 【図5】構成プロセッサのアレイを含むプロセッサの概略ブロック図である。

- 【図6】機械知能アルゴリズムにおいて使用されるグラフの概略図である。

- 【図7】あるタイプのロード/ストア命令を実装する際に使用するためのアドレスパッキングスキームを概略的に示す。

- 【図8】ストライドレジスタセットにおける既定のストライド値の構成を概略的に示す。

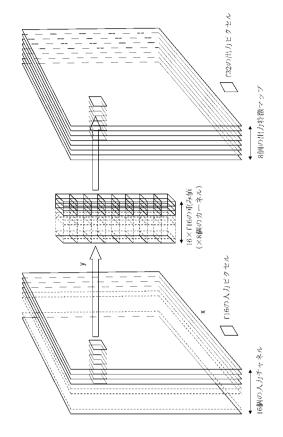

- 【 図 9 】 あるボリュームの入力データと 3 Dカーネル K との畳み込みを概略的に示す。

- 【図 1 0 】累積行列積命令の位相のシーケンスによって実行された行列乗算を概略的に示す。

- 【図11】累積行列積命令の動作をさらに示す。

- 【図12】畳み込みを実行するように構成された累積行列積命令のシーケンスの一連のループの例を与える。

- 【図13】畳み込み命令の動作を概略的に示す。

- 【図14】一連の畳み込み命令の例を与える。

- 【発明を実施するための形態】

- [ 0 0 2 7 ]

実施形態の詳細な説明

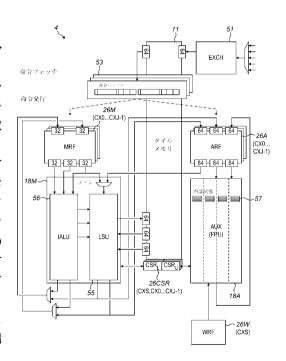

図1は、本開示の実施形態によるプロセッサ4の例を示す。プロセッサ4は、バレルスレッド処理装置の形態のマルチスレッド処理装置10と、ローカルメモリ11(すなわち、マルチタイルアレイの場合は同じタイル上、または、単一プロセッサチップの場合は同じチャップ上)とを含む。バレルスレッド処理装置は、パイプラインの実行時間が、インターリーブされた時間スロットの繰り返しシーケンス(その各々は、所定のスレッドによって占有される)に分割されるタイプのマルチスレッド処理装置である。また、これは、でよるらに詳細に論じられるように、並列実行と呼ぶこともできる。メモリ11は、命令メモリ12およびデータメモリ22(異なるアドレス可能メモリユニットの異なる領域において実装することができる)を含む。命やメモリ12は、処理装置10によって実行される機械語を格納し、データメモリ22は、実行コードによって処理されるデータと、実行コードによって出力されたデータ(例えば、そのような処理の結果として)の両方を格納する。

[0028]

メモリ 1 2 は、プログラムの複数の異なるスレッドを格納し、各スレッドは、所定の 1 つまたは複数のタスクを実行するための命令の対応するシーケンスを含む。本明細書で言 10

20

30

40

20

30

40

50

及される命令は、単一のオペコードおよび 0 またはそれ以上のオペランドからなる機械語命令(すなわち、プロセッサの命令セットの基本命令のうちの 1 つのインスタンス)を意味することに留意されたい。実施形態では、プログラムは、多数のワーカースレッドと、1 つまたは複数のスーパーバイザスレッドとして構造化することができるスーパーバイザサブプログラムとを含む。これらについては、間もなくさらに詳細に論じる。

#### [0029]

マルチスレッドプロセッサは、典型的には並列的に、互いに並んで配置された複数のプログラムスレッドの実行が可能なプロセッサである。並列実行は、スレッドが、共通の実行パイプライン(またはパイプラインの少なくとも共通部分)を共有し、異なるスレッドが、繰り返しサイクルの異なるインターリーブされた時間スロットにおいて、この同じ共有された実行パイプラインを通じてインターリーブされることを意味する。これにより、パイプライン遅延を隠蔽する機会が増大するので、性能が向上する。プロセッサは、複数の異なるスレッドに共通の何らかのハードウェア(例えば、共通の命令メモリ、データメモリおよび / または実行ユニット)を含むが、マルチスレッドをサポートするため、プロセッサは、各スレッドに特有の何らかの専用ハードウェアも含む。

#### [0030]

専用ハードウェアは、並列に実行することができるスレッドの少なくとも各々に対するコンテキストレジスタ26の個別のセット(すなわち、サイクルの1スロット当たり1セット)を含む。マルチスレッドプロセッサについて述べる際、「コンテキスト」は、互いに並んで実行されている複数のスレッドのそれぞれのスレッドのプログラム状態(例えば、プログラムカウンタ値、ステータスおよび現在のオペランド値)を指す。コンテキストレジスタは、それぞれのスレッドのこのプログラム状態を表すためのそれぞれのレジスタを指す。レジスタファイルのレジスタは、レジスタアドレスが命令語においてビットとして固定されるという点で、一般的なメモリとは別個のものであり、メモリアドレスは、命令を実行することによって演算することができる。

### [0031]

処理装置10内では、命令メモリ12からのスレッドの複数の異なるスレッドを、単一の実行パイプライン13を通じてインターリーブできる(ただし、典型的には、命令メモリに格納された全スレッドのサブセットのみが全プログラムの任意の所定のポイントにおいてインターリーブされうる)。マルチスレッド処理装置10は、コンテキストレジスタ26の多数のセットを含み、各セット26は、並列に実行することができる複数のスレッドのうちの異なるそれぞれのスレッドの状態(コンテキスト)を表すように構成される。また、マルチスレッド処理装置10は、並列に実行されるスレッドに共通の共有された実行パイプライン13や、インターリーブ方法で(例えば、ラウンドロビン方法で)共有されたパイプラインを通じて実行するための並列スレッドをスケジュールするためのスケジューラ24も含む。処理装置10は、多数のスレッドに共通の共有された命令メモリ12と、これもまた多数のスレッドに共通の共有されたデータメモリ22とに接続される。

### [0032]

実行パイプライン 1 3 は、フェッチステージ 1 4 と、復号ステージ 1 6 と、命令セットアーキテクチャによって定義されるような、算術および論理演算、アドレス計算、ロードおよびストア操作ならびに他の動作を実行することができる実行ユニットを含む実行ステージ 1 8 とを含む。

### [0033]

コンテキストレジスタ26の各セットは、対応する1つまたは複数の制御レジスタを含み、制御レジスタは、それぞれのスレッドに対する少なくともプログラムカウンタ(PC)を含み(スレッドが現在実行し命令アドレスを追跡するため)、また、実施形態では、対応するスレッドの現在の状態(スレッドが現在実行されているかまたは一時停止しているかなど)を記録する1つまたは複数の制御状態レジスタ(CSR)のセットも含む。また、コンテキストレジスタファイル26の各セットは、それぞれのスレッドによって実行される命令のオペランド(すなわち、実行される際にそれぞれのスレッドの命令のオペコ

ードによって定義された動作に基づいて操作される値または定義された動作から生じる値)を一時的に保持するためのオペランドレジスタのそれぞれのセットも含む。レジスタ 26の各セットは、1つまたは複数のレジスタファイルにおいて実装することができる。

#### [0034]

フェッチステージ 1 4 は、 複数のコンテキストの各々のコンテキストのプログラムカウ ンタ(PC)ヘアクセスできる。対応するスレッドのそれぞれに対し、フェッチステージ 14は、プログラムカウンタによって示されたプログラムメモリ12の次のアドレスから そのスレッドの次の命令をフェッチする。プログラムカウンタは、分岐命令によって分岐 されない限り、各実行サイクルを自動的にインクリメントする。次いで、フェッチステー ジ14は、フェッチした命令を復号のために復号ステージ16に渡し、次いで、復号ステ ージ16は、命令を実行するために、命令において指定されたいかなるオペランドレジス 夕の復号化されたアドレスと共に、復号化された命令を実行ユニット18に渡す。実行ユ ニット18は、オペランドレジスタおよび制御状態レジスタヘアクセスできる。実行ユニ ットは、算術命令の場合のように、復号化されたレジスタアドレスに基づいて命令を実行 するときに、そのオペランドレジスタおよび制御状態レジスタを用いてもよい(例えば、 2 つのオペランドレジスタの値の加算、乗算、減算または除算を行い、対応するスレッド の別のオペランドレジスタに結果を出力する)。あるいは、命令がメモリアクセス(ロー ドまたはストア)を定義する場合は、実行ユニット18のロード/ストアロジックは、命 令に従って、データメモリからそれぞれのスレッドのオペランドレジスタに値をロードす るか、または、それぞれのスレッドのオペランドレジスタからデータメモリ22に値を格 納する。

#### [0035]

フェッチステージ14は、スケジューラ24の制御の下で、実行される命令を命令メモリ12からフェッチ可能に接続される。スケジューラ24は、時間スロットの繰り返しシーケンスにおいて次々と並列に実行しているスレッドのセットの各々から命令をフェッチするようにフェッチステージ14を制御するように構成され、従って、間もなくさらに詳細に論じられるように、パイプライン13のリソースを多数の時間的にインターリーブされた時間スロットに分割する。例えば、スケジューリングスキームは、ラウンドロビンまたは重み付けラウンドロビンであり得る。そのような方法で動作するプロセッサに対する別の用語は、バレルスレッドプロセッサである。

### [0036]

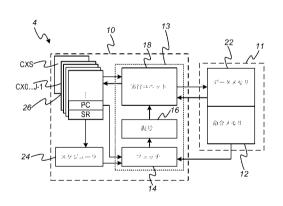

スケジューラ24によって実装されるインタリーブスキームの例は、図2に示されている。ここでは、並列スレッドは、ラウンドロビンスキームに従ってインターリーブされ、それにより、スキームの各ラウンド内では、ラウンドは、時間スロットのシーケンスS0、S1、S2…SJ-1(例えば、J=4またはJ=6)に分割され、各スロットは、それぞれのスレッドを実行するためのものである。典型的には、各スロットは、1つの実行サイクルの長さであり、異なるスロットが均等にサイズ指定されるが、すべての可能な実施形態において必ずしもそうであるとは限らず、例えば、1回の実行ラウンド当たりいるを形態において必ずしもそうであるとは限らず、例えば、1回の実行ラウンド当たりにンスキームも可能である。一般に、バレルスレッドは、均一なラウンドロビンまたは重み付けラウンドロビンスケジュールを採用することができ、後者の場合、重み付けは、固定することも、適応化させることもできる。

### [0037]

1回の実行ラウンド当たりのシーケンスが何であれ、このパターンは繰り返され、各ラウンドは、複数の時間スロットの各々の対応するインスタンスを含む。従って、本明細書で言及される場合は、時間スロットは、シーケンスにおける繰り返し割り当てられる場所を意味し、シーケンスの特定の繰り返しにおける時間スロットの特定のインスタンスを意味しないことに留意されたい。別の言い方をすれば、スケジューラ24は、パイプライン13の実行サイクルを多数の時間的にインターリープされた(時分割多重化)実行チャネルに分配し、各実行チャネルは、時間スロットの繰り返しシーケンスにおけるそれぞれの

10

20

30

40

20

30

40

50

時間スロットの再現を含む。示される実施形態では、 4 つの時間スロットが存在しているが、これは単なる例示を目的としており、他の数も可能である。例えば、好ましい一実施 形態では、実際に、 6 つの時間スロットが存在する。

### [0038]

実施形態では、コンテキストレジスタ26は、並列に実行することができる」個の数のスレッド(示される例では、J=3であるが、これに限定されない)の各々に対するワーカーコンテキストレジスタCX0…CX(J-1)のそれぞれのセットと、1つの追加のスーパーバイザコンテキストレジスタファイルCXSとを含む。ワーカーコンテキストレジスタファイルは、ワーカースレッドのコンテキストを保持し、スーパーバイザコンテキストレジスタファイルは、スーパーバイザスレッドのコンテキストを保持する。実施形態では、スーパーバイザコンテキストは、ワーカーの各々とは異なる数のレジスタを有することに留意されたい。従って、処理装置10は、時間スロットよりも1つ多いコンテキストレジスタファイル26を含む(すなわち、処理装置10は、バレルスレッドが可能なインターリーブされた時間スロットの数よりも1つ多いコンテキストをサポートする)。

### [0039]

ワーカーコンテキストCX0…CXJの各々は、プログラマが望むアプリケーション特有の演算タスクは何でも実行するために、4つの実行時間スロットS0…SJののりったのに現在割り当てられている多数のワーカースレッドのそれぞれのワーカースレッドので表すために使用される(この場合もやはり、このワーカーコンテキストは、なりに留意されたい)。追加のコンテキストCXSは、「スーパーバイザスとのリーカースレッドの総数の単なるサブイザスとのリーカーストの状態を表すために使用され、その役割は、少なくとも実行のためにS11の人のより当てるかという意味で、ワーカースレッドの実行を調整することである。オーバーバイザスレッドは、外部の交換またはバリア同期の実行などの他の「オードーシーア」または調整責任を有し得る。当然ながら、J=4の示される事例は、例では、フーア」または調整責任を有し得る。当然ながら、J=4の示される事例は、例では、フーア」または調整責任を有し得る。当然ながら、J=4の示される事例は、例では、フーア」または調整責任を有し得る。当然ながら、J=4の示される事例は、例のとする実装形態の単なる一例であることに留意されたい。例えば、別の実装形態では、フーア・ファーカーコンテキスト)である。

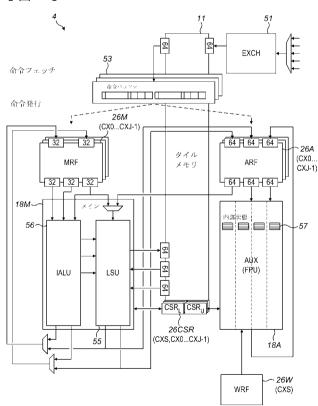

### [0040]

図3を参照すると、実施形態では、スーパーバイザスレッドSVは、インターリーブされた実行時間スロットのスキームにそれ自体の時間スロットを有さない。また、ワーカースレッドへのスロットの割り当ては柔軟に定義されるため、ワーカーも同様である。むしろ、各時間スロットは、ワーカーコンテキストを格納するためのコンテキストレジスタのそれ自体のセットを有し、そのセットは、ワーカーによって、スロットがワーカーに割り当てられる際に使用されるが、スロットがスーパーバイザに割り当てられる際には使用されない。所定のスロットがスーパーバイザに割り当てられる際は、そのスロットは代わりに、スーパーバイザのコンテキストレジスタファイルCXSを使用する。スーパーバイザは、常に、それ自体のコンテキストへのアクセスを有し、ワーカーは、スーパーバイザコンテキストレジスタファイルCXSを占有することはできない。

### [0041]

スーパーバイザスレッドSVは、ありとあらゆる時間スロットS0…S3(またはより一般的にはS0…SJ-1)において動作する能力を有する。スケジューラ24は、プログラムが全体として開始されると、スーパーバイザスレッドを時間スロットのすべてに割り当てることで開始するように構成される。しかし、スーパーバイザスレッドには、後続のある時点で(すぐにまたは1つもしくは複数のスーパーバイザタスクを実行した後に)、実行しているスロットの各々をワーカースレッドのそれぞれに(例えば、図3に示される例では、最初にワーカーW0…W3(またはより一般的にはW0…WJ-1)に)一時的に委ねるためのメカニズムが提供される。これは、命令メモリ12のワーカースレッド

のアドレスをオペランドとして少なくとも取る実行(run)命令を実行するスーパーバイザスレッドによって達成される。ワーカースレッドは、互いに並列に実行することができるコードの部分であり、その各々は、実行される1つまたは複数のそれぞれの演算タスクを表す。

### [0042]

実行命令は、この命令自体が実行されている現在の時間スロットを、オペランドによって指定されたワーカースレッドに委ねるように、スケジューラ 2 4 に作用する。実行命令では、委ねられるものが、この命令が実行される時間スロットであることは暗黙的であることに留意されたい(機械語命令の文脈では、暗黙的であるということは、オペランドがこれを指定する必要がないということ、すなわち、オペコード自体から暗黙のうちに理解されていることを意味する)。従って、渡される時間スロットは、スーパーバイザが実行命令を実行する時間スロットである。

#### [0043]

スーパーバイザスレッドSVは、ワーカースレッドW0…WJ-1の異なるそれぞれのワーカースレッド(命令メモリ12の可能なワーカースレッドのより大きなセットから選択される)にその時間スロットのいくつかまたはすべてを渡すために、複数の時間スロットのうちの1つまたは複数の他の時間スロットの各々において同様の動作を実行する。最後のスロットに対してそのように行われた時点で、スーパーバイザは、中断される(次にで、スロットのうちの1つがワーカーWから返された際に、中断したところからを開される)。従って、スーパーバイザスレッドSVは、各々が1つまたは複数のタスクを実行する異なるワーカースレッドを、インターリーブされた実行時間スロットに割り当てることができる。ワーカースレッドを実行命令を使用してスーパーバイザスレッドが決定すると、スーパーバイザスレッドは、実行命令が実行された時間スロットにこのワーカーを割り当てる。

#### [0044]

いくつかの実施形態では、命令セットは、「すべてを実行する(run-all)」という実行命令の変形形態も含み得る。この命令は、複数のワーカーのセットを共に起動するために使用され、すべてが同じコードを実行する。実施形態では、この命令は、処理装置のスロットS0…S3(またはより一般的にはS0…S(J-1))内のワーカーを1つ残らず起動する。

### [0045]

いったん起動されると、現在割り当てられているワーカースレッドW0…WJ-1の各々は、それぞれの実行命令によって指定されたコードにおいて定義された1つまたは複数の演算タスクの実行に進む。次いで、この実行の終了時には、それぞれのワーカースレッドは、実行している時間スロットをスーパーバイザスレッドに返す。これは、それぞれのワーカースレッドにおいて終了(exit)命令を実行することによって達成される。終了命令は、この命令自体が実行されている現在の時間スロットをスーパーバイザスレッドに戻すように、スケジューラ24は、そのスロットにおいてスーパーバイザの実行を続ける。

### [0046]

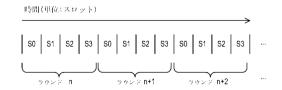

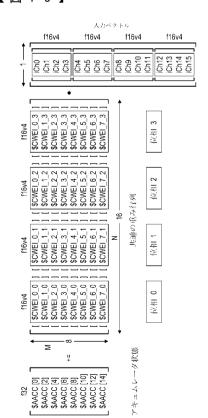

図4は、実行ユニット18およびコンテキストレジスタ26の詳細を含むプロセッサ4のさらなる例示的な詳細を示す。プロセッサは、並列実行が可能なM個のスレッドの各々に対するそれぞれの命令バッファ53を含む。コンテキストレジスタ26は、ワーカーMコンテキストおよびスーパーバイザコンテキストの各々に対する対応するメインレジスタファイル(MRF)26Mを含む。コンテキストレジスタは、ワーカーコンテキストの少なくとも各々に対するそれぞれの補助レジスタファイル(ARF)26Aをさらに含む。コンテキストレジスタ26は、共通の重みレジスタファイル(WRF)26Wをさらに含む。現在実行しているワーカースレッドのすべてが、重みレジスタファイル(WRF)から読み出しアクセス可能である。スーパーバイザスレッドをWRFに書き込むことができ

10

20

30

40

20

30

40

50

る唯一のスレッドとするよう、WRFはスーパーバイザコンテキストと関連付けられてもよい。また、コンテキストレジスタ26は、スーパーバイザおよびワーカーコンテキストの各々に対する制御状態レジスタ26CSRの対応するグループも含んでもよい。実行ユニット18は、メイン実行ユニット18Mおよび補助実行ユニット18Aを含む。メイン実行ユニット18Mは、ロード/ストアユニット(LSU)55および整数演算論理ユニット(IALU)56を含む。補助実行ユニット18Aは、少なくとも浮動小数点演算ユニット(FPU)を含む。

### [ 0 0 4 7 ]

J 個のインターリーブされた時間スロットS0...SJ-1の各々では、スケジューラ 2 4 は、命令メモリ 1 2 から、現在の時間スロットに対応するJ個の命令バッファ 5 3 のそ れぞれに、対応するスレッドの少なくとも1つの命令をフェッチするようにフェッチステ ージ14を制御する。実施形態では、各時間スロットは、プロセッサの1つの実行サイク ルであるが、他のスキーム(例えば、重み付けラウンドロビン)も除外されない。 プロセ ッサ4の各実行サイクル(すなわち、プログラムカウンタ時間を記録するプロセッサクロ ックの各サイクル)では、フェッチステージ14は、実装形態に応じて、単一の命令また は小さな「命令バンドル」(例えば、2命令バンドルまたは4命令バンドル)をフェッチ する。次いで、各命令は、復号ステージ16を介して、命令がメモリアクセス命令である か 、 整 数 演 算 命 令 で あ る か 、 浮 動 小 数 点 演 算 命 令 で あ る か に 応 じ て そ れ ぞ れ ( そ の オ ペ コ ードに従って)、メイン実行ユニット18MのLSU 55もしくはIALU は補助実行ユニット18AのFPUのうちの1つに発行(issue)される。メイン実行ユ ニット18MのLSU 55およびIALU 56は、MRF 26Mからのレジスタを 使用してそれらの命令を実行し、MRF 26M内の特定のレジスタは、命令のオペラン ドによって指定される。補助実行ユニット18AのFPUは、ARF 26AおよびWR 2 6 Wのレジスタを使用して演算を実行し、ARF内の特定のレジスタは、命令のオ ペランドによって指定される。実施形態では、WRFのレジスタは、命令タイプにおいて 暗黙的であり得る(すなわち、その命令タイプに対して事前に決定される)。また、補助 実 行 ユ ニ ッ ト 1 8 A は 、 浮 動 小 数 点 演 算 命 令 の タ イ プ の う ち の 1 つ ま た は 複 数 の 演 算 を 実 行 す る 際 に 使 用 す る た め の い く つ か の 内 部 状 態 5 7 を 保 持 す る た め の 補 助 実 行 ユ ニ ッ ト 1 8 A の内部にある論理ラッチの形態の回路も含んでもよい。

### [ 0 0 4 8 ]

バンドルの命令をフェッチして実行する実施形態では、所定の命令バンドルの個々の命令は、下流の独立したパイプライン18M、18A(図4に示される)において並列して、同時に実行される。2つの命令のバンドルを実行する実施形態では、2つの命令は、下流のそれぞれの補助およびメインパイプラインにおいて同時に実行することができる。この場合、メインパイプラインは、MRFを使用するタイプの命令を実行するように構成され、補助パイプラインは、ARFを使用するタイプの命令を実行するために使用される。命令の適切な相補バンドルへのペアリング(pairing)は、コンパイラによって実現(handled)してもよい。

### [0049]

[0050]

各ワーカースレッドコンテキストは、メインレジスタファイル(MRF)26Mおよび補助レジスタファイル(ARF)26Aのそれ自体のインスタンス(すなわち、バレルスレッドスロットの各々に対して1つのMRFおよび1つのARF)を有する。MRFまたはARFに関連して本明細書で説明される機能は、コンテキスト別に動作するものと理解されたい。しかし、スレッド間で共有される単一の共有された重みレジスタファイル(WRF)が存在する。各スレッドは、それ自体のコンテキスト26のMRFおよびARFのみにアクセスすることができる。しかし、現在実行しているワーカースレッドはすべて、共通のWRFにアクセスすることができる。従って、WRFは、すべてのワーカースレッドによる使用のための重みの共通のセットを提供する。実施形態では、スーパーバイザのみがWRFに書き込むことができ、ワーカーは、WRFから読み取ることしかできない。

20

30

40

50

プロセッサ 4 の命令セットは、少なくとも 1 つのタイプのロード (load)命令を含み、 そのロード命令は、実行されると、そのオペコードが、データメモリ22からロード命令 が実行されたスレッドのそれぞれのARF 26AへのデータのロードをLSU 行わせる。ARF内の送信先の場所は、ロード命令のオペランドによって指定される。ロ ード命令の別のオペランドは、それぞれのMRF 26Mのアドレスレジスタを指定し、 それぞれのMRF 26Mのアドレスレジスタは、データをロードするためのデータメモ リ22のアドレスへのポインタを保持する。また、プロセッサ4の命令セットは、少なく とも 1 つのタイプのストア (store) 命令も含み、そのストア命令は、実行されると、そ のオペコードが、ストア命令が実行されたスレッドのそれぞれのARFからデータメモリ 2 2 へのデータの格納を L S U 5 5 に行わせる。 A R F 内のストアの送信元の場所は、 ストア命令のオペランドによって指定される。ストア命令の別のオペランドは、MRFの アドレスレジスタを指定し、MRFのアドレスレジスタは、データを格納するためのデー タメモリ22のアドレスへのポインタを保持する。一般に、命令セットは、別個のロード およびストア命令タイプ、ならびに/あるいは、ロードおよびストア操作を組み合わせて 単一の命令にした少なくとも1つのロード/ストア命令タイプを含んでもよい。間もなく さらに詳細に論じられるように、命令セットは、2つのロード操作および1つのストア操 作をすべて単一の命令で実行する特定のタイプのロード/ストア命令を含んでもよい。所 定のプロセッサ4の命令セットは、複数の異なる種類のロード、ストアおよび/またはロ ード/ストア命令タイプを含み得ることに留意されたい。

[0051]

また、プロセッサの命令セットは、算術演算を実行するための1つまたは複数のタイプの算術命令も含む。本明細書で開示される実施形態によれば、これらの命令イプの原令は、第の重みレジスタファイルWRF 26Wを利用する少なくとも1つのタイプの命令は、算術命令が実行されたスレッドのそれぞれのARF 26Aの対応する算術演算の少なくとも1つの送信元を指定する少なくとも1つの送信元を指定する少なくとも1つの送信元を指定する少なくとも1つのが表情では、共通のWRFの少なくとも1つののが表情では、共通のWRFののである。実施形態では、この送信元は、問題あるのでは、すべてのワーカースレッドに共通である。実施形態では、この送信元は、問題あるのは、おいいであるである。すなわち、このタイプことは元の場所は、オペランドを指定する必要有が、ないなの意味において、暗黙的であるという事前に決定される)。あるいは、他のットに対して事前に決定される)のものであるでは、WRFの少数の異なるセットのであるいは、他のットに対して事がに対して事ができる。しかし、重みの送信元の場所には、第術命令は、WRFの少数の異なるセットのできる。しかし、重みの形態では、第術命令は、WRFの少数の異なるセットのできる。しかし、重みの送信では、第術命令は、WRFの少数の異なるセットのどの重みレジスタのもという事実は(例えば、汎用MRFまたはARFとは対照的に)、依然といるでは、1つまに対している。

[0052]

算術命令の関連タイプのオペコードに応答して、補助実行ユニット18Aの演算ユニット(例えば、FPU)は、オペコードによって指定されるように算術演算を実行し、算術演算は、スレッドのそれぞれのARFの指定された送信元レジスタおよびWRFの送信元レジスタの値に基づいて演算するステップを含む。また、演算ユニットは、算術命令の送信先オペランドによって明示的に指定されるように、スレッドのそれぞれのARFの送信先レジスタへの算術演算の結果の出力も行う。

[0053]

共通のWRF 26Wの送信元を採用することができる算術命令の例示的なタイプは、1つもしくは複数のベクトル乗算命令タイプ、1つもしくは複数の行列乗算命令タイプ、1つもしくは複数の累積ベクトル乗算命令タイプおよび/または累積行列乗算命令タイプ(命令のあるインスタンスから次のインスタンスまで乗算の結果を累計する)ならびに/あるいは1つもしくは複数の畳み込み命令タイプを含んでもよい。例えば、ベクトル乗算命令タイプは、ARFからの既定の重みベクトルを乗じることができる。あるいは、行列乗算命令タイプは、ARFからの明示的な

20

30

40

50

入力ベクトルにWRFからの既定の重み行列を乗じることができる。別の例として、畳み込み命令タイプは、ARFからの入力行列にWRFからの既定の行列を畳み込むことができる。多数のスレッドに共通の共有重みレジスタファイルWRFを有することにより、各スレッドは、それ自体のそれぞれのデータに共通のカーネルを乗じるまたは畳み込むことができる。これは機械学習アプリケーションにおいて、例えば、各スレッドがニューラルネットワークの異なるノードを表し、共通のカーネルが検索または訓練されている特徴(例えば、グラフィカルデータのエリアまたはボリュームのエッジまたは特定の形状)を表す場合に、多く現れるシナリオであるため、これは有益である。

### [0054]

実施形態では、WRF 26Wの値は、スーパーバイザスレッドによって書き込むことができる。スーパーバイザ(実施形態では、すべてのスロットS0・・・SMにおいて定行することによって開始される)は、最初に、いくつかの共通の重み値をWRFの既定の場所に書き込むために、一連のプット(put)命令を実行する。次いで、スーパーバイザは、スロットS0…SJ-1のうちのいくつかまたはすべてのそれぞれのワーカーを起動するための命令を実行する(またはすべての命令を実行する)。次いで、各ワーカーは起い上記で論じられるタイプの1つまたは複数の算術命令の1つまたは複数のインスタールの方を改らして対応する解析であると、それらの対応するARF 26Aにロードされると、それら明本ではある人力データに対して対応する算術演算を実行する(ただし、スーパーバイザにあずる人力データに対して対応する算術演算を実行する。ただし、スーパーバイザにあずれてWRF 26Wに書き込まれた共通重みを使用して)。各スレッドがそのそれぞれのタスクを終了すると、各ワーカーは、そのスロットをスーパーバイザに返すために、終了すると、行っバイザは、新しい値をWRFに書き込み、新しいスレッドセットを起動することができる(または、新しいセットを起動して、WRFの既存の値の使用を続けることができる)。

### [0055]

「メイン」、「補助」および「重み」というラベルは必ずしも制限されないことが理解 されよう。実施形態では、それらのラベルは、第1のレジスタファイル(1つのワーカー コンテキスト当たり)、第2のレジスタファイル(1つのワーカーコンテキスト当たり) および共有された第3のレジスタファイル(例えば、スーパーバイザコンテキストの一部 であるが、すべてのワーカーがアクセス可能である)のいずれかであってもよい。ARF 2 6 A および補助実行ユニット 1 8 A は、算術命令(または少なくとも浮動小数点演算 )のために使用されるため、算術レジスタファイルおよび算術実行ユニットと呼ぶことも できる。MRF 2.6Mおよびメイン実行ユニット18Mは、それらの使用のうちの1つ がメモリにアクセスするためのものであるため、メモリアドレスレジスタファイルおよび ロード / ストアユニットと呼ぶこともできる。重みレジスタファイル(WRF)26Wは 、間もなくさらに詳細に論じられるように、一定の1つまたは複数のタイプの算術命令で 使用される乗法重みを保持するために使用されるため、そのように呼ばれる。例えば、こ れらの重みレジスタファイル(WRF)26Wは、ニューラルネットワークのノードの重 みを表すために使用することができる。別の方法で見ると、MRFは、整数オペランドを 保持するために使用されるため、整数レジスタファイルと呼ぶことができ、ARFは、浮 動小数点オペランドを保持するために使用されるため、浮動小数点レジスタファイルと呼 ぶことができる。2つのバンドルの命令を実行する実施形態では、MRFは、メインパイ プラインによって使用されるレジスタファイルであり、ARFは、補助パイプラインによ って使用されるレジスタである。

### [0056]

しかし、代替の実施形態では、レジスタ空間 2 6 は、必ずしもこれらの異なる目的のためにこれらの別個のレジスタファイルに分割されるとは限らないことに留意されたい。代わりに、メインおよび補助実行ユニットを通じて実行される命令は、同じ共有されたレジスタファイルの中から、レジスタを指定することができる場合がある(マルチスレッドプロセッサの場合、1 つのコンテキスト当たり1 つのレジスタファイル)。また、パイプラ

20

30

40

50

イン 1 3 は、命令のバンドルを同時に実行するために、必ずしも並列構成パイプライン (例えば、補助およびメインパイプライン)を含まなければならないわけではない。

### [0057]

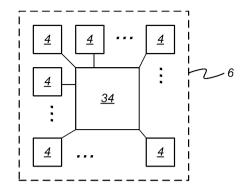

また、プロセッサ4は、メモリ11と1つまたは複数の他のリソース(例えば、プロセッサの他の例および/またはネットワークインタフェースもしくはネットワーク接続記憶でNAS)デバイスなどの外部のデバイス)との間でデータを交換するための交換フェース51も含んでもよい。図5に示されるように、実施形態では、プロセッサ4は、相互接続プロセッサタイルのアレイ6のうちの1つを形成することができ、Aルのではより広の一部を実行する。従って、個々のプロセッサ4(タイルのよいより広がつロセッサまたは処理システム6の一部を形成する。タイル4は、それらのして接続することができる。タイル4は、同じチップ(すなわち、ダイ)上、異なるでは、アレイは、各々が複数のタイル4を含む複数テムプよがら形成することができる)で実装することができる。従って、相互接続システィカよび交換インタフェース51は、内部(オンチップ)相互接続メカニズムおよび、または外部(インターチップ)交換メカニズムを相応に含み得る。

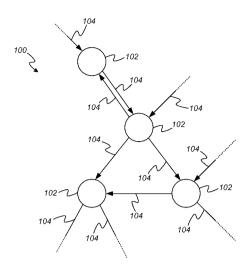

### [0058]

マルチスレッドおよび / またはマルチタイルプロセッサまたはシステムの例示的なアプリケーションの 1 つでは、複数のスレッドおよび / またはタイル 4 にわたって実行されるプログラムは、ニューラルネットワークの訓練および / またはニューラルネットワークに基づく推論の実行を行うように構成されたアルゴリズムなどの機械知能アルゴリズムを含む。そのような実施形態では、各ワーカースレッド、各タイル上で実行されるプログラムの一部または各タイル上の各ワーカースレッドは、ニューラルネットワーク(グラフのタイプ)の異なるノード 1 0 2 を表すために使用され、それに従って、スレッド間および / またはタイル間の通信は、グラフのノード 1 0 2 間のエッジ 1 0 4 を表す。これは、図 6 に示されている。

### [0059]

機械知能は、機械知能アルゴリズムが知識モデルを学習する学習段階から始まる。モデルは、相互接続ノード(すなわち、頂点)102およびエッジ(すなわち、リンク)104のグラフを含む。グラフの各ノード102は、1つまたは複数の入力エッジと、1つまたは複数の出力エッジとを有する。ノード102のいくつかの入力エッジのうちのいは、ノード102の他のいくつかの出力エッジであり、それにより、ノードが互いに接続され、グラフが形成される。さらに、ノード102の1つまたは複数の入力エッジのうちの1つまたは複数は、全体としてのグラフへの入力を形成し、ノード102の1つまたは複数の出力エッジのうちの1つまたは複数は、全体としてのグラフの出力を形成する。さらに、所定のノードは、グラフへの入力、グラフからの出力および他のノードとの接続のすべてを有するものであってもよい。各エッジ104は、値又はテンソル(n次元行列)を伝達し、これらは、ノード102の入力エッジに提供される入力を形成する。、出力エッジから提供される出力を形成する。

### [0060]

各ノード102は、その1つまたは複数の入力エッジにおいて受信される1つまたは複数の入力についての関数を表し、この関数の結果は、1つまたは複数の出力エッジにおいて提供される出力である。各関数は、1つまたは複数の対応するパラメータ(重みと呼ばれる場合もあるが、必ずしも乗法重みである必要はない)によってパラメータ化される。一般に、異なるノード102によって表される関数は、関数の異なる形態であることおよび/または異なるパラメータによってパラメータ化することが可能である。

### [0061]

さらに、各ノードの関数の1つまたは複数のパラメータの各々は、対応する誤差値によって特徴付けられる。さらに、対応する条件は、各ノード102のパラメータの誤差と関連付けることができる。単一のパラメータによってパラメータ化された関数を表すノード

102の場合、条件は、簡単な閾値であってもよく、すなわち、条件は、誤差が指定閾値内にある場合に満たされるが、誤差が閾値を超える場合には満たされない。複数の対応するパラメータによってパラメータ化されたノード102の場合、誤差の許容レベルに達たそのノード102に対する条件は、より複雑なものであってもよい。例えば、条件はは、そのノード102のパラメータの各々がそれぞれの閾値内に収まる場合にのみ満たされる。別の例として、同じノード102に対する異なるパラメータの誤差を組み合わせた組合せ計量を定義することができ、条件は、組合せ計量の値が指定閾値内に収まるといる場合は満たされていまいが、そうでなければ、条件は、組合せ計量の値が閾値を超える場合は満たされない(あるいは、計量の定義に応じて、その逆も同様である)。条件によって満たされない(あるいは、計量の定義に応じて、その逆も同様である)。条件を場合は満たされない。

### [0062]

学習段階では、アルゴリズムは、経験データ(すなわち、グラフへの入力の異なる可能な組合せを表す複数のデータポイント)を受信する。多くの経験データが受信されるにつれて、アルゴリズムは、パラメータの誤差をできうる限り最小化するよう、経験データに基づいて、グラフの様々なノード102のパラメータを段階的に調節する。目標は、所定の入力に対してグラフの出力が所望の出力にできる限り近くなるようなパラメータの値を見出すことである。グラフが全体としてそのような状態に向かう傾向となったときに、グラフは収束したと言える。適切な収束度が得られた後、グラフは、予測または推論を実行するため(すなわち、何らかの所定の入力に対する結果を予測するかまたは何らかの所定の出力に対する原因を推論するため)に使用することができる。

#### [0063]

学習段階は、多くの異なる可能な形態を取ることができる。例えば、教師ありアプローチ(supervised approach)では、入力経験データは、訓練データ(すなわち、既知の出力に対応する入力)の形態を取る。各データポイントを用いて、アルゴリズムは、出出が所定の入力に対して既知の出力により近くなるように、パラメータを調節することができる。後続の予測段階では、グラフは、入力クエリを近似予測出力にマッピングするために使用することができる(または、推論する場合は、その逆も同様である)。また、他のの法も可能である。例えば、教師なしアプローチ(unsupervised approach)では、1つの入力データ当たり1つの参照結果という概念は存在せず、代わりに、機械知アルゴリプローチ(reinforcement approach)では、アルゴリズムは、入力経験データの各データポイントに対して少なくとも1つの可能な出力を試し、この出力が、正か否か(およに対して少なくとも1つの可能な出力を試し、この出力が、正か否か(およたは合い)が知らされる。多くの試行にわたり、アルゴリズムは、正の結果をもたらす入力を対力を対力を言るように、グラフのパラメータを徐々に調節することができる。グラフを学習するための様々な手法およびアルゴリズムは、機械学習の当業者に知られている。

### [0064]

本明細書で開示される技法の例示的なアプリケーションによれば、各ワーカースレッドは、ニューラルネットワークなどの機械知能グラフのノード102のそれぞれの個々のノードと関連付けられた演算を実行するようにプログラムされる。この場合、ノード102間のエッジ104の少なくともいくつかは、スレッド間のデータの交換に相当するものであってもよいし、タイル間の交換に関与するものであってもよい。1つのタイル4当たり複数のスレッドを有するマルチタイル構成6の場合、各タイル4は、グラフのサブグラフを実行する。各サブグラフは、1つまたは複数のスーパーバイザスレッドを含むスーパーバイザサブプログラムと、それぞれのサブグラフのノード102を表すワーカースレッドのセットとを含む。

### [0065]

10

20

30

20

30

40

50

機械知能などのアプリケーションでは、プロセッサ4(例えば、タイル)のデータメモリ22におよびデータメモリ22からデータを効率的に流すことができることが望ましい。例えば、このことは、ベクトルドット積命令、行列積、累積ベクトルドット積、累積行列積または専用畳み込み命令(高度の算術複雑性を単一の算術命令に詰め込んだもの)などの複雑な算術命令のシーケンスを伴わせる上で特に(ただし、排他的にではない)有益であるう。

#### [0066]

そのような問題に対処するため、実施形態は、プロセッサ4の命令セットにおいて、2つのロード操作および1つのストア操作を実行し、次いで、独立ストライドをロードおよびストアアドレスの各々に自動的に適用するタイプのロード/ストア命令を提供し、それらの動作はすべて、命令のオペコードの単一のインスタンスに応答して行われる。その上、命令は、適切なレジスタファイル(例えば、MRF 26M)における効率的なアドレスパッキングを使用し、それにより、3つのアドレス(2つのロードアドレスおよび1つのストアアドレス)が2つのレジスタの空間にパッキングされる。これにより、単一の命令において、MRF 26MからLSUへの単に3つのポートのみを用いて、3つのメモリアドレスおよびストライドレジスタへのアクセス(3つのレジスタの各々へのアクセスに対してそれぞれのポート1つずつ)が可能になる。

### [0067]

命令は、本明細書では、「1d2xst64pace」と呼ぶことができ、これは、2つの64ビット値をロードし、1つの64ビット値を格納するという事実を指し、「pace」は、ストライドと同義語である。しかし、このラベルまたは特定のビット幅は、必ずしも限定的なものと受け止められない。命令は、より一般的には、単にロード/ストア命令(ただし、これは、必ずプロセッサの命令セットのロード/ストア命令の唯一の種類であるということを示唆するものでない)または「1dx2st」(ロード×2およびストア)と呼ぶことができる。その構文は以下の通りである。

ld2xst \$aDst,\$aSrc,\$mAddr,\$mStride,Strim

### [0068]

\$ a D s t は、補助(または算術)レジスタファイル(ARF)26Aの送信先を識別する1つまたは複数のオペランドを指し、送信先は、ARFのレジスタのうちの1つまたは複数を含む。実施形態では、ARFのレジスタの各々は、32ビット幅であり、送信先\$ a D s t は、4つのそのような32ビットレジスタ(\$ a D s t 0 : D s t 0 + 3)からなり得る。1d2xst64paceの送信先オペランドは、ARFのこれらの送信先レジスタのうちの単に1つの送信先レジスタの場所(例えば、最も低い\$ a D s t 0)を指定できるのみであり、他の送信先レジスタの場所は、これに関して暗黙的であってもよい(例えば、ARFの次の3つの隣接するレジスタ)。あるいは、他の実装形態では、複数の送信先オペランドの各々が、別個のオペランドによって明示的に独立して識別できることは除外されない(ただし、これには、命令幅の増加が必要になる)。

### [0069]

\$ a S r c は、A R F 2 6 A の送信元を識別する1つまたは複数のオペランドを指し、送信元は、A R F のレジスタのうちの1つまたは複数を含む。実施形態では、A R F のレジスタの各々は、3 2 ビット幅であり、送信元\$ a S r c は、2 つのそのような3 2 ビットレジスタ(\$ a S r c 0 : S r c + 1 ) からなり得る。1 d 2 x s t 6 4 p a c e の送信元オペランドは、A R F のこれらの送信元レジスタのうちの単に1つの送信元レジスタの場所(例えば、最も低い\$ a S r c 0 ) を指定できるのみであり、他の送信元レジスタの場所は、これに関して暗黙的であり得る(例えば、A R F の次の隣接するレジスタ)。あるいは、他の実装形態では、複数の送信元オペランドの各々が、別個のオペランドによって明示的に独立して識別できることは除外されない(ただし、これには、命令幅の増加が必要になる)。

### [0070]

20

30

40

50

\$ m A d d r は、メインレジスタファイル(M R F ) 2 6 M の 2 つのレジスタ(\$ m A d d r 0 : A d d r 0 + 1 )の場所を指定する 1 つまたは複数のオペランドを指し、 2 つのレジスタ間では、 3 つのアドレス( 2 つのロードアドレスおよび 1 つのストアアドレス)が保持される。実施形態では、 M R F のレジスタの各々は、 3 2 ビット幅である。メモリアドレスオペランドは、 M R F のこれらのレジスタのうちの単に 1 つのレジスタの場所(例えば、最も低い \$ m A d d r 0 )を指定できるのみであり、他のレジスタの場所は、これに関して暗黙的であってもよい(例えば、 M R F の次の隣接するレジスタ)。 あるいは、他の実装形態では、メモリアドレスレジスタの各々が、 別個のオペランドによって明示的に独立して識別できることは除外されない(ただし、これには、命令幅の増加が必要になる)。

[0071]

Strimmは、即値オペランドのセットであり、それぞれの即値オペランドは、2つのロードアドレスおよび1つのストアアドレスの各々に対するものである。MRF 26Mでは、多数のフィールドを含むストライドレジスタが提供される。各フィールドは、異なる可能なストライド値の既定のセットの異なる対応するストライド値を保持する。ストライド値は、メモリアドレスをどの程度インクリメントするかを示す値(すなわち、メモリアドレスステップ)であり、典型的には、一連のステップにおいて使用するためのものである。2つのロードおよび1つのストアの各々に対し、対応する即値ストライドオペランドは、命令の現在のインスタンスの対応するロードまたはストア操作を実行した後に、対応するロードまたはストアアドレスに適用するためにストライドレジスタのどのフィールドからストライド値を取り入れるかを指定する。この動作は、ロード/ストア命令の後続のインスタンスの利益のために、MRF 26Mのアドレスに沿って移動する。

[0072]

実施形態では、ロード / ストアユニット 5 5 は、ある特徴をサポートし、その特徴により、即値ストライドオペランドの 1 つの特別な値は、レジスタフィールドを指し示すというよりむしろ、 1 のストライド値(すなわち、使用されるアドレス空間における 1 アドレス単位の増加)を直接指定することができる。すなわち、即値ストライドオペランドが取りうる値のうち、 1 つは、 1 のストライドを指定し、他の値のいくつかまたはすべては、プログラム可能なストライド値を保持しているストライドレジスタの異なる可能なフィールドを指定する。ここでの 1 単位は、データアクセスのアトミックサイズを意味する。例えば、オペランドが 1 6 ビット浮動小数点値の 4 要素ベクトルである場合は、インクリメントは、 1 単位当たり 1 アトムであり、それは、 8 バイト( 6 4 ビット)に等しい。

[0073]

ストライドレジスタは、MRF 26Mのレジスタである。実施形態では、ワーカー自体は、それ自体のストライドレジスタ(それ自体のMRF)のフィールドのストライド値を書き込むことに対する責任を有する。あるいは、他の実装形態では、ストライドレジスタのフィールドのストライド値がスーパーバイザスレッドSVによって書き込めること、または、手法の組合せを使用できることは除外されない。

[0074]

オペランドによる\$mStrideの指定に対する要件は、実装形態に応じたプロセッサ4の任意の特徴である。実施形態では、ロード / ストア命令は、MRF 26Mのストライドレジスタ\$mStrideの場所を指定するオペランドを取る。従って、プログラムは、多数の可能なストライドレジスタの中からストライドレジスタを選択し、ストライドの選択におけるさらなる一層の柔軟性を提供することができる。しかし、代替の実装形態では、\$mStrideの場所を固定するかまたは暗黙的にし、ロード / ストア命令のオペランドを必要としないようにすることができることは除外されない。

[0075]

図 7 は、 3 つのアドレスを M R F 2 6 M の 2 つの 3 2 ビットレジスタにパッキングする例を示し、各アドレスは、 2 1 ビットである。また、図 7 は、 3 つのストライド値を M R F の 1 つの 3 2 ビットレジスタにパッキングする例も示し、各ストライド値は、 1 0 ビ

20

30

40

50

ットである(この事例では、レジスタの2ビットは未使用である)。従って、ロード/ストア命令は、単一の命令において、MRFの単に2つの32ビット幅ポートを介して、3つのメモリアドレスにアクセスすることができる。第3の32ビット幅ポートは、同じ命令によって、ストライドレジスタにアクセスするために使用することができ、ストライドレジスタは、例えば、MRFの32ビット幅ストライドレジスタにパッキングされた3つの10ビット幅フィールドの3つの10ビットストライド値(アドレスデルタ)を含む(そのレジスタの2ビットは未使用のままである)。図7に示される特定のパッキングは単なる例であることに留意されたい。例えば、別の実装形態では、addr1というよりむしろ、addr2が2つのレジスタをまたぐことができる。

[0076]

図 8 は、MRF 2 6 Mにおける複数のストライドレジスタ \$ mStrideA、 \$ m StrideB、\$mStrideC...の構成を示す。これらはいずれも、ロード/スト ア命令の対応するオペランドによって、ストライドレジスタ\$mStrideとして指定 することができる。可能なストライドレジスタの各々は、多数のフィールドを含み、例え ば、実施形態では、3つのフィールドを含む(ただし、実装形態に応じて、必ずしもロー ドおよびストアアドレスのものと同じ数とは限らないフィールドやストライドレジスタが 存在する)。2つのロードアドレスおよび1つのストアアドレスの各々に対し、即値St rimmのセットのそれぞれの即値オペランドは、それぞれのストライド値(それぞれの ロードまたはストアに続いて適用されるアドレスデルタ)を取り入れるためのストライド レジスタ \$ m S t r i d e の可能なフィールドのうちの 1 つを指定することができる。例 えば、実施形態では、ストライドオペランドが2つのロードおよび1つのストアの各々に 対して2ビットである場合は、可能な値のうちの3つは、3つのストライドフィールドの うちの異なるストライドフィールドを指定し、他の可能な値は、レジスタに保持されてい る値を参照することなく、単に、1のストライドを指定するのみである。例えば、00は . 1(アトム)のストライドを指定し、01は、ストライドレジスタの第1のフィールド を指定し、10は、ストライドレジスタの第2のフィールドを指定し、11は、ストライ ドレジスタの第3のフィールドを指定することになる。

[0077]

実施形態では、即値ストライドの可能な値のうちの1つは、ストライドレジスタ\$mStrideのフィールドというよりむしろ、1のデフォルトインクリメントを指定することに留意されたい。

[0078]

動作の際、実行ユニット18によって実行されると、ロード/ストア命令のオペコード(復号ステージ16によって復号された後)は、以下の動作を実行するようにLSU 55をトリガする。LSU 55は、MRF 26Mの\$mAddrに保持されるアドレスによって指定されるメモリ22の2つのロードアドレスから、\$aDscによって指定されるARF 26Aの送信先に、値をロードする。さらに、LSU 55は、ARFの\$aSrcから、MRFの\$mAddrに保持されたアドレスによって指定されるメモリ22のストアアドレスに、値をロードする。次いで、LSU 55は、3つの即値オペランドStrimmのそれぞれの即値オペランドによって指定されるようなMRFのストライドレジスタ\$mStrideのそれぞれのフィールドからのそれぞれのストライド値の分だけ、2つのロードアドレスおよび1つのストアアドレスの各々を独立してポストインクリメントする。

[0079]

注:ロード / ストア命令の現在のインスタンスの2つのロードアドレスおよび1つのストアアドレスの各々に対し、現在の命令のストライド操作は、現在のロード / ストア操作のロードおよびストア操作の各々に続いてそれぞれ、それぞれのストライドの分だけそれぞれのアドレスをインクリメントする。実装形態に応じて、このことは、すべてのインクリメントがロードとストアの両方の後に共に適用されること(例えば、ロード、ロード、ストア、インクリメント、インクリメント、を意味し得る。あるいは、

ストライド操作は、各ロードおよびストアの直後に、それぞれのアドレスをインクリメントすることができる(例えば、ロード、インクリメント、ロード、インクリメント、ストア、インクリメント)。実際に、ストアは、ロードのうちの一方または両方の前に来ることもできる。重要なことは、単に、各ロードアドレスのインクリメントがそのそれぞれのロードの後に行われること、そして、ストアアドレスのインクリメントがストアの後に行われることである。肝心なことは、ロード/ストア命令の後続のインスタンスに備えて、MRFのロードおよびストアアドレスに沿って移動することである。

### [0800]

実施形態では、メモリ11(または少なくともデータメモリ22)は、メモリからデータをロードするための単に2つの64ビットポートと、メモリにデータを格納するための単に1つの64ビット幅ポートとを有するのみである。実施形態では、MRF 26M(所定のコンテキストの)は、ロード/ストアユニット55への単に3つの32ビットにポートを有するのみであり、ARF 26A(所定のコンテキストの)は、ロード/ストアユニット55への単に1つの64ビット幅ポートを有するのみである(注:示される例では、IALU 56は、MRF 26Mからポインタを回収し、LSU 55に渡すために使用され、従って、事実上、IALU 56は、LSU 55の一部として動作する。従って、この例では、MRF 26MからLSU 55への3つのポートは、MRF 26MからIALU 56への3つのポートを含む。また、他の実装形態では、LSU 55は、MRF 26Mから直接、ポインタを回収し、そのポインタに基づいてそれ自体のアドレスを演算できることも除外されない)。

#### [0081]

実施形態では、ARFの4つの32ビット送信先レジスタ\$ a D s t 0: D s t 0 + 3 (合計で128ビット)は、メモリ22から、例えば、16ビット浮動小数点(f 16)値の4要素ベクトルおよび32ビット浮動小数点(f 32)値の2要素ベクトルをロードするために使用することができる。ARFの2つの32ビット送信元レジスタ\$ a S r c 0: S r c + 1 (合計で64ビット)は、メモリ22に、例えば、f 32値の32ビットの2要素ベクトルを格納するために使用することができる。

### [0082]

プログラムにおいて使用するため、ロード/ストア命令は、算術命令などの他のタイプの命令の中に散在し、算術命令は、ロード命令の送信先から入力を取り入れ、その入力に基づいて演算を実行し、ロード/ストア命令の送信元に結果を出力する。すなわち、プログラムは、ロード/ストア命令のインスタンスと、少なくとも1つの算術命令(以前に命及されたベクトルドット積命令、行列積命令、累積ベクトルドット積命令、累積行列積命令、累積がからないのロード/ストア命令の送信先は、算術命令のうちの少なくともいくつかの算術命令の送信元であり、算術命令のうちの少なくともいくつかの算術命令の送信元であり、口ード/ストア命令の高い意味的密度に起因して、その2つのロードおよびストライド機能により、プログラムは、ロードおよびストア操作に費やされるコードオーバーヘッドが小さな状態で、効率的にデータを処理することができる。

### [0083]

例えば、プログラムは、一連の複数対の命令を含んでもよく、命令の各対は、ロード/ストア命令のインスタンスと、それに続く算術命令の対応するインスタンスとからなる。命令の各対では、ロード/ストア命令の送信元は、先行する対からの算術命令の送信先として設定され、ロード/ストア命令の送信先は、現在の対または後続の対の対応する算術命令の送信元として設定される。例えば、以下の構文を有する「arith」という算術命令を考える。

arith \$aDst,\$aSrcA,\$aSrcB

### [ 0 0 8 4 ]

50

10

20

30

20

30

40

50

構文中、\$aDstは、ARF 26Aの送信先を指定するオペランドを指し、\$aSrcA、\$aSrcBは、ARFの2つの送信元を指定するオペランドを指す(「arith」は、少なくともこの構文を有する算術命令のためにここで使用される一般名であることが理解されよう)。次いで、プログラムは、例えば、以下のような一連の複数対の命令によってプログラムすることができる。

. . .

ldx2st Xin-Pin, Pout, Tripacked, Strides; ar ith Pout, Xin, Pin;

ldx2st Xin-Pin, Pout, Tripacked, Strides; ar

ith Pout, Xin, Pin;

ldx2st Xin-Pin, Pout, Tripacked, Strides; ar

ith Pout, Xin, Pin;

ldx2st Xin-Pin,Pout,Tripacked,Strides;ar

ith Pout, Xin, Pin;

• • •

### または

. . .

ldx2st Xin-Pin, Pout\_A, Tripacked, Strides; arith Pout\_A, Xin, Pin;

ldx2st Xin-Pin,Pout\_B,Tripacked,Strides;

arith Pout\_B, Xin, Pin;

ldx2st Xin-Pin,Pout\_A,Tripacked,Strides;

arith Pout\_A, Xin, Pin;

ldx2st Xin-Pin, Pout\_B, Tripacked, Strides; arith Pout\_B, Xin, Pin;

. . .

### など。

### [0085]

実施形態では、各対は、命令バンドルであり、すなわち、下流のそれぞれのパイプラインにおいて同時に実行される。例えば、実施形態では、ロード / ストア命令は、MRF26 Mを使用してメインパイプラインによって実行され、算術命令は、ARF26 Aを使用して補助パイプラインによって並列して実行される。しかし、代替の実現形態では、単一のパイプライン処理装置を通じてロード / ストアおよび算術命令を次々と実行できることは除外されない。

### [0086]

20

30

40

50

先は、後続の命令対のロード/ストア命令のストア操作の送信元と同じになるように設定される。2つの同時命令のバンドルとして各対を実行する実施形態では、Xin、Pinは、以前のバンドルのロード/ストア命令によって実行されたロードの送信先と同じになるように設定され、Poutは、次のバンドルの1dx2stのストア操作の送信元と同じになるように設定される。この実施形態は、同じレジスタを再利用するが、2つの命令が並列して実行されるため、現在の算術命令に対する入力データは、以前のロード命令によって読み取られたものである。次いで、現在の1dx2stは、次の算術命令に対する入力データを準備するために、それらの同じレジスタを再利用する。

### [0087]

従って、各対では、ロード/ストア(1dx2st)は、以前の命令の以前の対(例えば、バンドル)の以前の算術命令から現在見出されている出力をレジスタPoutに格納し、また、メモリからレジスタXinおよびPinに値をロードする。同じ対(例えば、バンドル)の次の算術命令は、以前にロードされた値に基づいて算術演算を実行し、後続の対の後続のロード/ストア命令のストア操作によって格納するためにレジスタPoutに出力する。

#### [0088]

実施形態では、算術命令は、共有されたWRF 26Wの少なくとも第3の暗黙的な送信元を有することに留意されたい。これらの送信元は、WRFに書き込むスーパーバイザスレッドによって設定することができる。従って、スーパーバイザは、すべての実行ワーカースレッドの算術演算によって暗黙的に使用される共通の重みを設定する。

#### [0089]

また、MRF 26Mの\$mAddr0:Addr0+1を指定するメモリアドレス「 Tripacked」の値は、それぞれのワーカーによっていくつかの初期値に設定され る。また、MRFの可能なストライドレジスタ \$ mStrideの各々のフィールドのス トライド値は、それぞれのワーカーによって設定される。ロード/ストア命令が実行され る度、メモリアドレスレジスタ \$ m A d d r 0 : A d d r 0 + 1 内の 3 つのアドレス ( 2 つのロードアドレスおよび1つのストアアドレス)の各々は、それぞれのストライド値の 分だけポストインクリメントされる。再び図7および8を参照すること。例えば、仮に、 ロード/ストア命令が \$ m S t r i d e = \$ m S t r i d e A および S t r i m m = 0 1 1 0 0 0 ( 第 1 の即値ストライドオペランド = 0 1 、第 2 の即値ストライドオペランド = 1 0 および第 3 の即値ストライドオペランド = 0 0 )と指定するとする。これは、第 1 の ロードを実行した後、\$mStrideAのフィールド0のストライド値の分だけ第1の ロードアドレスがインクリメントされ、第 2 のロードを実行した後、 \$ m S t r i d e A のフィールド1のストライド値の分だけ第2のロードアドレスがインクリメントされ、格 納後、アトミックインクリメントの分だけストアアドレスがインクリメントされる(使用 されているアドレス空間の 1 メモリアドレスステップずつインクリメントされる)ことを 意味する。ロード/ストア命令の後続のインスタンスは、\$mStrideの同じまたは 異なる値および3つの即値オペランドの各々の同じまたは異なる値を指定するように設定 することができる。従って、一連の命令の各ロード/ストア命令では、ロードおよびスト アの場所は制御可能な方法で移動することができる。従って、コードは、新しいアドレス を演算するための追加の整数演算命令を必要とすることなく、入力データ空間を通じて柔 軟な方法で効率的に走査することができる。

### [0090]

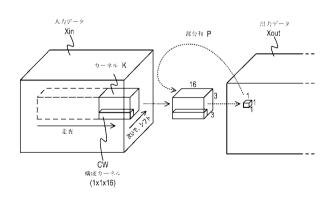

図9は、上記の実施形態が有益であり得る例示的なアプリケーション、すなわち、入力データXinの多次元部分とカーネルKとの畳み込みの実行を示す。例えば、入力データは、3Dボリュームの入力データであってもよく、カーネルKは、3Dカーネルであってもよい。また、入力データは、入力チャネルと呼ぶこともでき、出力データは、出力特徴チャネルと呼ぶことができる。データが多次元であると言われる場合は、これは、データが二次元以上の座標系の座標の多数の組合せの各々における値を取ることを意味し、各次元(すなわち、各軸)は、異なる独立変数を表す(そして、座標の所定の組合せにおける

データの値は、従属変数である)。

### [0091]

これの例は、各データ値がピクセルを表す画像処理におけるものである。例えば、典型的には、赤、緑およみ演算の前に「「16値に変換される。それ、別個のののである。例えば、世別で、それらののである。例えば、世別で、おりののでは、別個の方が使用され、次、B値は、別個の方がでは、とを有している。従ってののである。のでは、別個の方がでもよく、ボリュームのでは、対し、エリカを表す。別ののでは、ボリュームのようでは、対し、エリカを表す。別ののは、ボリュームの3つの次元は、対し、では、が、フレームの3ののでは、データはは、が、である。別ののでは、ボリュームの3つの次元は、データは、ボリュームの3つの次元は、データは、ボリュームの3つの表では、データは、ボリュームの3つの表には、データは、ボリュームの3つの表では、データは、ボリューを表のの方には、データは、ボリューを表のの方には、アータは、アータも除外されない。画像またはグラフス処理に限に、三次元またはそれらの次元は、ユーザ挙動などを引きるアプリケーションにおいてユーザまたはそれの次元は、ユーザ挙動などを表してもよい。

### [0092]

カーネルKは、既定の重みの行列である。カーネルKは、ニューラルネットワークが認のために訓練されているかまたは後続の推論において検索されているある特徴をの種語において検索をしているある特徴をの事業をは他の何らかの特定の種子の形状を表してもよい。機械学習アプリケーションでは、ニューラルネットワークである。カーネルはでしては、これでもいるを表してもよいに相当してもよい(ただし、後に異なる接続10~~では、同じカーネル値を使用するが、単に22は、それのワーカースレッドによなでする。カースレッドは、それぞれのカーカースレッドによるでは、後のアーカースレッドによるである。ワーカースレッドのようできるが、インシャーをはは、共有の重みレジスタファイル(WRF)26Wにその作れなている同じカーネルにまたは算術)レジスタファイル(ARF)26Aを介してメモリ28のそれぞれの補助(または算術)レッド自体のそれぞれの入力データにそのカーネルを置からおよびメモリ22に流れるスレッド自体のそれぞれの入力データにそのカーネルを引み込む。

### [0093]

三次元の離散畳み込み(\*)は、以下のように表すことができる。

Xin \* K [ x , y , z ] = \_x ' , y ' , z ' ( K [ x ' , y ' , z ' ] Xin [ x - x ' , y - y ' , z - z ' ] )

従って、畳み込みは、入力データにカーネルを重ね合わせることができる可能な位置のいくのかまたはすべてにわたってカーネル K をシステマチックに走査することを含むされてにわたってカーネル K をシスカカの音とでしたができることをのような位置の各々では、カーネルと重なり合うの部分の各ピクセルの値とが乗算の名々の結果は加算され、その特定のオーバーレイ位置におれて、これらの個々の乗算の各々の結果はカカラはの対応するがいで、この動作はおり、カデータ(1つのカーネル位置当たり1つのスカラ値)の対応するがリュームのを得ば、カーネルに対するカースカラ値の置で繰り返される。例えばて開いて、カーネルができ、カーネルがで、カーネルは、ボリュームの長さば、開重なり合うデータポイントとが乗じられる。次いで、カーネルは、ボリュームの長さにがある。から合うデータポイントとが乗じられる。がに、ボイント乗算およるでが、カーネルは新しいを標位置におけるカーネルを目に沿ってがある。から、カーネルは新しい座標位置にシフトされ、全ボリュームが走査されるまで、カーネルは新しい座標位置にシフトされ、全ボリュームが走査される方が再び実行されるなど、以下同様である。所定の各位置におけるカーネルは、出力であるときである。所定の各位置におけるカーネルは、出力であるときである。所定の各位置におけるカーネルは、

10

20

30

50

40

ータの1つのピクセル(1つのスカラ値)を生成する。従って、出力データXoutは、 畳み込み走査のステップサイズに応じて、入力データと同じまたは同様のサイズを有する ことになる。

### [0094]

実際には、この動作は、より小さな動作に分割する必要がある。このことは、所定の位 置 に お け る デ ー タ と カ ー ネ ル と の 畳 み 込 み を 多 く の 個 々 の べ ク ト ル ド ッ ト 積 お よ び 部 分 和 に分けることによって行うことができる。このことは、図9の中央および右側に示されて いる。仮に、例えば、カーネルのサイズが3×3×16ピクセルであるとする(「ピクセ ル」は、本論考のために、必ずしも画像を指すとは限らない)。すなわち、カーネルは、 3 × 3 × 1 6 の既定の重み値からなる。このカーネルは、 9 つの 1 6 要素ベクトル C W ( 本明細書では、カーネルKの構成カーネルとも呼ばれる)に分割することができる。最初 に、これらの9つのベクトルのうちの1つと対応する位置における入力データとの間でド ット積(すなわち、スカラ積)が取られ、部分和P(スカラ)が得られる。次いで、9つ のベクトルのうちの別のものとの間でドット積が取られ、第1の部分和と累計して、第2 の部分和(この場合も、スカラ)が得られる。次いで、9つのベクトルのうちの別のもの との間でドット積が取られ、この結果を第2の部分和と累計して、第3の部分和が得られ るなど、以下同様である。この動作が終了し、9つのベクトルのすべてを累計した時点で 、総累計結果は、出力データXoutにおける単一のポイントまたはピクセルの値を与え る。次いで、この動作は、入力データXinのボリュームに対する異なる位置にわたって カーネルKが走査されるにつれて、各カーネル位置で繰り返され、従って、出力データX out(1つのカーネル位置当たり1つの出力データポイント)の対応するボリュームが 得られる。

### [0095]

実施形態では、畳み込みなどの演算を効率的な方法で実行することを支援するため、プロセッサ4の命令セットは、累積積(「amp」)命令の形態の算術命令を含む。その命令は、以下の構文を有する。

amp \$aDst,\$aSrcA,\$aSrcB,Phase 構文中、\$aDstは、この場合もやはり、ARF 26Aの送信先を指定するオペランドを指し、\$aSrcA、\$aSrcBは、ARFの2つの送信元を指定するオペランドを指す。「Phase」は、累積の位相を指定する即値オペランドである。例えば、実施形態では、位相オペランドは、4つの可能な位相0・・・3のうちの1つを指定することができ、これは、第1の入力として4つの半精度(16ビット)浮動小数点値の1つのイクトルを取り入れ、第2の入力として1つの単精度(32ビット)浮動小数点値を取り入れ、1つの単精度(32ビット)浮動小数点値を取り入れ、1つの単精度(32ビット)浮動小数点値を取り入れ、1つの単精度(32ビット)の対であり、実施形態では、第2の入力は、2つの単精度浮動小数点値(2×32ビット)の対であり、出力も同様である。しかし、これらの特定の精度の値および要素の数は、すべての可能な実施形態に制限されないことが理解されよう。

### [0096]

ampなどの1つまたは複数のタイプの命令に対し、実施形態では、WRFの重みの場所は、完全に暗黙的である。その代替としてまたはそれに加えて、1つまたは複数の他のタイプの命令は、WRFの少数の異なるセットの中からどの重みのセットを使用するかを指定する追加のオペランド(図示せず)を取ることができる。例えば、その例は、後に言及されるスリムな畳み込み(slim convolution)(「slic」)命令であり得る。

#### [0097]

以前に説明されたロード/ストア命令(1d2xst)と組み合わせると、amp命令などの命令は、メモリからデータを効率的に流し、ドット積および部分和を実行し、部分和をメモリに戻すために使用することができる。例えば、以下のような4つの命令対のル

10

20

30

40

20

30

40

50

ープを経るシーケンスを含むプログラムを考慮する。

Loop {

ldx2st Xin-Pin,Pout,Tripacked,Strides;am

p Pout,Xin,Pin,Phase=0;

ldx2st Xin-Pin,Pout,Tripacked,Strides;am

p Pout,Xin,Pin,Phase=1;

ldx2st Xin-Pin,Pout,Tripacked,Strides;am

p Pout,Xin,Pin,Phase=2;

ldx2st Xin-Pin,Pout,Tripacked,Strides;am

p Pout,Xin,Pin,Phase=3;

[0098]

}

別の例示的なバージョンは、以下の通りである。

Loop {

ldx2st Xin-Pin, Pout\_A, Tripacked, Strides; amp Pout\_A, Xin, Pin, Phase = 0; ldx2st Xin-Pin, Pout\_B, Tripacked, Strides;

amp Pout\_B, Xin, Pin, Phase = 1;

ldx2st Xin-Pin,Pout\_A,Tripacked,Strides; amp Pout\_A,Xin,Pin,Phase=2;

ldx2st Xin-Pin,Pout\_B,Tripacked,Strides; amp Pout\_B,Xin,Pin,Phase=3; }

など。

### [0099]

この場合もやはり、実施形態では、各対は、命令バンドルであり、すなわち、下流のそれぞれのパイプライン(例えば、メインおよび補助パイプライン)において同時に実行される。

### [0100]

命令の各対は、ロード/ストア命令のインスタンスおよびそれに続く累積積(amp) 命令のインスタンスを含む。 a m p 命令の送信元は、同じまたは先行する命令対のロード / ストア命令によって実行された 2 つのロードの送信先である。 2 つの同時命令のバンド ルとして各対を実行する実施形態では、ampの送信元(Xin、Pin)は、以前のバ ンドルにおいて実行されたロードの送信先と同じになるように設定される。amp命令の 送信先は、後続の命令対(例えば、次のバンドル)においてロード/ストア命令によって 実行される1つのストアの送信元である。amp命令の送信元\$aSrcA、\$aSrc Bのうちの一方は、入力データXinから入力ベクトルxを取り入れるために使用される 。他方は、部分和を取り入れるために使用される。amp命令は、実行されると、その入 力 ベ ク ト ル × と 重 み レ ジ ス タ フ ァ イ ル W R F 2 6 W か ら の 重 み C W の 対 応 す る ベ ク ト ル ( このベクトルCWは、全体または 3 DカーネルKの構成カーネルである ) とのドット積 を実行する。位相オペランドは、ドット積の結果を累計するための位相を指定する。ルー プの所定のインスタンスにおけるシーケンスの命令の各対では、位相オペランドは、シー ケン ス の 異 な る 連 続 位 相 を 指 定 す る 異 な る そ れ ぞ れ の 値 に 設 定 さ れ る 。 位 相 オ ペ ラ ン ド に よって指定されるようなシーケンスのこれらの連続位相にわたり、amp命令の効果は、 連続ドット積の各々の結果を累計することである。入力部分和との累計は、シーケンスの 第1の位相において始まる。

### [0101]

ロード / ストア命令のストライド機能により、プログラムは、MRF 26Mに含めるための新しいメモリアドレスを演算するための別個の整数演算命令を必要とすることなく、メモリアドレスに沿って、命令の各対を有する次のデータ片に自動的にシフトすること

20

30

40

50

ができる。ストライドレジスタ\$mStrideから多くの事前にプログラムされたスト ライドのうちのいずれかを選択できるとの上記ロード/ストア命令の能力は、図9におい て例示として示されるものなどの多次元データを取り扱う上で特に有益である。メモリ空 間は、一次元であるが、データは、二次元、三次元またはそれ以上の次元を有し得る。多 次元データ空間への1Dメモリ空間のマッピングに応じて、カーネルKが入力データXi nを通じて走査されるにつれて、メモリ空間の対応するメモリアドレスを通じて異なるサ イズのステップを取る必要がある場合がある。例えば、カーネルKが入力データXinの 一次元に沿って長さ方向に走査されるにつれて、各走査位置におけるデータのメモリアド レスは、アトミックステップでインクリメントするが、垂直平面において走査をシフトす る必要がある際は、入力データXinの次のデータ片またはサブセットに到達するために 、メモリアドレスの異なるサイズのステップが必要とされる(そして、独立して、第2の 入力および出力アドレスに対して同じプロセスが行われる)場合がある。1つのストライ ドレジスタ\$mStrideまたは複数のストライドレジスタ(例えば、\$mStrid e A、 \$ m S t r i d e B、・・・)の異なるフィールドは、有利には、メモリ空間の異 なるサイズのジャンプで事前にプログラムすることができる。次いで、プログラマまたは コンパイラは、ロード/ストア命令別にどのジャンプサイズを使用するかを選択するため に、即値オペランドStrimmを設定することができる(次のアドレスまたは次のステ ップサイズを再計算するための別個の整数演算命令を必要とすることなく)。

[0102]

実施形態では、amp命令は、累積行列積命令である。この命令の動作については、図10~12を参照して説明する。図10に示されるように、amp命令は、FPUによって実行されると、入力データ×inからのN要素入力ベクトルと重みのM×N行列(WRF 26Wから)との乗算を実行する。実施形態では、M=8およびN=16である。行列のM個の行の各々は、異なる対応するカーネルK0、K1…KM・1からの構成べつといい。従って、amp命令は、入力データとM個の異なるカーネルKとの並列畳み込みのコンポーネントを実行するために使用される。例えば、スカーネルKとの並列畳み込みのコンポーネントを実行するために使用される。例えば、これらのカーネルの各々は、入力データと異なるそれぞれの特徴(例えば、異なるエッジまたは形状)との畳み込みに相当してもよい。畳み込みニューラルネットワークの場合におけるのカーネルは、特徴フィルタであり、M個のカーネルの各々は、入力層における異なる特徴の存在の検出を試みる。所定のカーネルKに対し、amp命令は、1つのドット積および累積のみを実行する。しかし、行列は、データと複数のカーネルとの効率的な並列畳み込みを行えるようにする。

[0103]

N要素入力ベクトルは、N1個のセグメントに分けられ、その各々は、N2個の要素の サブベクトルを含む(従って、N = N 1 × N 2 )。実施形態では、N 1 = 4 およびN 2 = 4 である。 a m p 命令の位相オペランドは、N 1 個の異なるセグメントに対応するN 1 個 の異なる可能な値 0 ... N 1 - 1 のうちの 1 つを取り入れる。ループを経るシーケンスの各 インスタンスでは、各連続対の a m p 命令は、位相 0 ... N 1 - 1 のうちの異なる連続位相 を指定する位相オペランドの異なる値を取る。各位相は、N要素入力ベクトルのN1個の サブベクトルのうちの対応するものと行列のM個の行の各々とのドット積(従って、M個 の異なるカーネルKの各々に対する演算の一部)を実行する。実行ユニット18(実施形 態では、補助または算術実行ユニット18A)のFPUは、M個のアキュムレータ状態\$ AACC(1スレッド当たり)を有する。実施形態では、これらのアキュムレータ状態\$ AACCは、FPUの内部状態57として実装される。しかし、代替の実装形態では、こ れらのアキュムレータ状態\$AACCを複数のレジスタファイル26(例えば、それぞれ のスレッドのARF 26A)のうちの1つのレジスタファイル26のレジスタとして実 装できることは除外されない。示される例では、これらのアキュムレータ状態\$AACC は、偶数番号が付けられた状態 \$ AACC [ 0 ] 、 \$ AACC [ 2 ] ... \$ AACC [ 1 4 ] であり、奇数番号が付けられた状態 \$ AACC [ 1 ] 、 \$ AACC [ 3 ] ... \$ AACC [ 1 5 ] は、シーケンスの異なるループ間で値を伝播するために使用することができるが

20

30

40

50

、これは、実装形態の詳細であり、これに限定されない。

### [0104]

図11は、amp命令の動作を図に示す。図12は、一連のamp命令の例を与える。各々は、上記で示されるように、命令対の対応するロード/ストア命令が先行すると理解されている。図12では、Pnは、単精度入力部分和nであり、xnは、f16v4入力ベクトルであり、CWm,nは、共通の重み状態\$CWEI\_m\_nであり、Rnは、Pnで始まる連続ドット積累積の最終的な単精度結果である。

### [0105]

動作の際、amp命令のオペコード(復号済みの)に応答して、実行ユニット18(実施形態では、補助実行ユニット18A)のFPUは、以下の動作を実行する。

・ amp命令の送信元オペランドのうちの1つによって指定されたARF 26Aのレジスタから、M/N1個の数の部分和を取り入れ、これらの部分和を次のループに対するプロパゲータ状態に一時的に置く。このプロパゲータ状態は、FPUの内部状態57で実装することができるか、または、代替の実装形態では、レジスタファイル26(例えば、ARF)のうちの1つのレジスタファイル26の別のレジスタであり得る。各位相は、M/N1個の部分和の異なるサブセットを取り入れる。N1個の位相にわたり、M個のそのような部分和は、プロパゲータ状態にされる。従って、M=8およびN1=4の場合は、各amp命令は、入力として2つの部分和(例えば、2つのf32値)を取り入れ、これらをプロパゲータ状態に保持し、すべての4つの位相にわたり、8つの部分和が受信される。

### [0106]

・ amp命令の送信元オペランドのうちの1つによって指定されたARF 26Aのレジスタから、入力ベクトルXinのN2要素セグメント(サブベクトル)を取り入れる。行列のM個の行の各々(従って、M個のカーネルK0…KM・1の各々)に対し、この入力ベクトルXinのN2要素セグメントとWRFからの重みCWの対応するサブベクトルとのドット積を実行する。どの列から重みのサブベクトルが取り入れられるかは、位相オペランドの値に依存する。さらに、位相がシーケンスの第1の(すなわち、初期の)位相である場合は、部分和のうちの対応するものがM個のドット積の各々に加えられる。以前のループの各amp命令はそれぞれのM/N1個(N1は、位相の数)の部分和を取り入れたため、以前のループは、現在のループに備えてすべてのM個の部分和をプロパゲータ状態に置いたことになることに留意されたい。

### [0107]

・ M個の行の各々に対し、上記の計算の結果は、M個のアキュムレータ状態 \$ A A C C のうちの対応する状態に既にある任意の値と累計され(総和が求められ)、それによって、M個の結果 R O・・・R M - 1 のうちの対応するものを生成する。従って、N 1 個の位相にわたり、 a m p 命令は、完全なN 要素入力ベクトルとW R F からの重みの対応するN 要素ベクトルとのドット積を実行する。

### [0108]

・ 現在のループでは、以前のループからのM/N1個の数の結果Rは、amp命令の送信先オペランドによって指定されたARFの送信先レジスタに出力される。各位相は、M/N1個の部分和の異なるサブセットを出力し、N1個の位相にわたり、M個のそのような部分和がプロパゲータ状態にされる。従って、M=8およびN1=4の実施形態では、1つのamp命令当たり2つの結果(例えば、2つのf32)が出力され、すべての4つの位相にわたってすべての8つの結果R0・・・R7が出力される。

#### [0109]

・ 現在のループの最後の位相の後(または結果が上書きされる前の次のループの第 1 の位相の開始時)、現在のループの結果 R は、次のループの出力に備えて、プロパゲータ状態に一時的に置かれる。このプロパゲータ状態は、 F P U の内部状態 5 7 で実装することができるか、または、代替の実装形態では、レジスタファイル 2 6 (例えば、 A R F)のうちの 1 つのレジスタファイル 2 6 の別のレジスタであってもよい。

20

30

40

50

### [0110]

要約すると、単一の部分和は、(1)第1のドット積結果に加えられ、アキュムレータ 状態(以前に保持された値を上書きする)で格納され、(2)さらなる3つのドット積結 果と累計され、(3)一時的なプロパゲータ状態にコピーされる(その場合、その値は、 今後のamp命令の送信先オペランドに書き込まれる)。ステップ(3)の代替手段は、 アキュムレータからそのまま得られた結果として生じた部分和をamp命令の送信先オペ ランドに書き込むことである。いずれの方法にせよ、ステップ(1)および(3)は、ハ ードウェアにおいて重複してもよく、4サイクルループを提供する。

### [0111]

実施形態では、アキュムレータ状態は、明示的にリセットする必要はない。各行列ベクトル乗算の出発点はメモリから読み取られた入力部分和であるため、出力ボリュームは、畳み込みの開始時に、アキュムレータ状態をリセットするというよりむしろ、すべての要素がゼロに設定される。そうは言っても、実施形態では、タイル4は、実際に、1から0にアキュムレータ状態のすべてを初期化することができる。

### [0112]

現在のamp命令の入力プロパゲータ状態は、次のループでの使用のために保持されることに留意されたい。また、amp命令によってARFの送信先レジスタに出力される結果は、現在のampの累積演算が適用される前の既存のアキュムレータ状態である(すなわち、累積の以前の短いシーケンスの結果であり、現在の入力を含まない)。

### [0113]

プログラムは、結果 R が後続のループに対する部分和入力 P になるように構成される( プログラマまたはコンパイラによって)。その正確な関係は、プログラマまたはコンパイ ラにかかっており、データおよびカーネルの構造に依存する。典型的には、部分和は、 0 の初期値(メモリ内の)を有する。

### [ 0 1 1 4 ]

ループ間の時間差により、シーケンスは、ウォームアップ期間を必要とすることに留意されたい。提示されている特定の入力ベクトルとamp命令によって返されている4位相計算の結果との間には待ち時間がある。その待ち時間は固定されており、これは、最初のM個の結果が無効であるか、関心のないものであるかまたは意味のないものであり、ウォームアップコードにおいて処理されることを意味する。有益な結果が生み出されないこのウォームアップ期間の後、コードは繰り返しループに入り、それにより、先に進み、有益な結果が必要なメモリ場所に書き込まれる(示される例では、一度に64ビット)。また、内側のループの後にはクールダウン期間もあり、クールダウン期間では、新しい入力は提供されないが、最終的な出力値が格納される。図12は、f16v4sisoampに対するウォームアップ期間および「結果待ち時間」を示す。

### [0115]

実施形態では、カーネルの数はM=8であり、入力ベクトルの要素の数はN=16であり、 位相の数はN1=4である。実施形態では、入力べクトルの各要素は、f16値である。と位れたのよび各結果は、f32値である。そのようなクトルの4つのf16位ののまたりとで、データを対当たり2つのf32値である。それは、1つの命令対当たり2つのf32値のレートで、データを出することがでできる。それは、U555に相当するでがでで、するとは、からしなができる。とがプラインののからは、ができるのとでがである。といれのカートでは、MRF26Mからしていてきる。2つの64ビット幅ポートは、MRF26Mからしていてきる。2つの64ビット幅ポートは、ARF26Mから補助実行ユニット18AのFPUへのカーネル当たり1つの出力値である。この特定のシナリオでは、それらの出力値は、各々が32ビットであることを示す。この特定のシナリオでは、それらの出力値は、各々が32ビットである。この特定のシナリオでは、それらの出力値は、各を表し、この特定のシナリオでは、それらの出力値は、各を表は、ADを表は、ADを表は、ADを表が32ビットである。この特定のシナリオでは、それらの出力値は、ADを表は、ADを表は、ADを表は、ADを表が32ビットである。

20

30

40

50

上記のループは、4 ティック(tick)ごとに16個の入力値(命令ごとに4 x f 16の入力値)を処理する。従って、その入力レートを維持するため、プロセッサ4は、4 ティックループごとに8 x 3 2 ビット値を生成しなければならず、それは、1つのループ当たり4 x 6 4 ビットストアまたは1 ティック当たり1 x 6 4 ビットストアを意味する。

重みCWは、共有されたWRF 26Wから取り入れられ、各スレッドに対して同じで ある。ニューラルネットワークなどのアプリケーションでは、異なるデータと重みの同じ セットとを乗じる(畳み込みの一部など)必要がある多くのシナリオがあるということが 分かる。例えば、ニューラルネットワークのいくつかのノードは、全く同じ重みを含むが 、異なる接続を含む場合がある。例えば、各カーネルK(m=0・・・M)は、入力デー タ(例えば、グラフィック画素のエリアまたはボリューム)と特徴(例えば、エッジまた は形状)との畳み込みを表すことができる。従って、これらのカーネルに対応するワーカ ースレッドには、別個の重みは不要である。代わりに、スーパーバイザが所有する重み状 態の単に1つのコピーが提供されるのみである。従って、共有の重みレジスタファイルか らの共有されたスレッドオペランドの使用により、有利には、重みに対するレジスタ空間 が少なくて済む。 図 1 2 は、各 1 6 要素入力ベクトルに対しループが 8 個の出力値( 1 つ のカーネル当たり1つの出力値)を生成することを示す。この特定のシナリオでは、それ らの出力値は、各々が32ビットである。上記のループは、4つのサイクルごとに16個 の入力値(命令ごとに 4 × f 1 6 の入力値)を処理する。従って、その入力レートを維持 するため、プロセッサ4は、4サイクルループごとに8×32ビット値を生成し、それは 、 1 つのループ当たり 4 × 6 4 ビットストアまたは 1 つのサイクル当たり 1 × 6 4 ビット ストアを意味する。

[0117]

[0116]

実施形態では、奇数アキュムレータ\$AACC[1]、\$AACCC[3]・・・\$AACC[15]は、結果(Rx)をずらすために使用され、部分和入力(Px)にも同じことをするために使用される。部分入力は、一度に2つずつ後方のエンジン、すなわち、アキュムレータレジスタ\$AACC[13]および\$AACC[15]に供給される。各サイクルでは、それらの値は、前方に移動し、この場合には、\$AACC[11]および\$AACC[9]へと移動する。それらの値が送信先AMPユニットに到達すると、それらの値は、累積に備えて、奇数番号が付けられたアキュムレータというよりむしろ、偶数番号が付けられたアキュムレータに移動する。従って、{\$AACC[15],\$AACC[13],\$AACC[2],\$AACC[2],\$AACC[0]}となる。

[ 0 1 1 8 ]

図13および14は、本明細書で説明されるタイプのロード/ストア命令(すなわち、それぞれのスレッドのARF 26Aを介して流された入力データに共通の重みレジスタファイル(WRF)26Wからの重みの2Dセットを畳み込む畳み込み命令)から恩恵を得ることができる別のタイプの算術命令を示す。実施形態では、この命令は、半精度浮動小数点ベクトルのスリムな畳み込み(s1ic命令)の形態を取ることができ、例えば、「f16v4s1ic」は、f16値の4要素サブベクトルに基づいて演算するという事実を指す。この命令は、1つの半精度および1つの単精度入力を有し、単精度出力を有る。s1icはampと同様であり、ampと同じハードウェアを使用する。しかし、この命令は、8つのカーネルの各々に対する1×1×16累積ドット積というよりむしろ、2つのカーネルの各々に対する1×4×4畳み込み(真の畳み込みである)を実行する。実際に、実施形態では、この命令は、1×N×4畳み込み(Nは、2、3または4である)を実行するように構成することができる。

[0119]

累積行列積(「amp」)およびスリムな畳み込み(「slic」)命令は、ワーカーコンテキストにわたる重み共有が適切なシナリオに対して、高性能の乗累算シーケンスを容易にする。実施形態では、ampおよびslic命令は、単精度数フォーマットと半

精度数フォーマットの両方をサポートし、同じ基本的な方法で動作することができる。共通の演算構成状態(WRF 26Wの共有の重みを含む)は、最初に、スーパーバイザコンテキストによって初期化される。次いで、入力データの2つのストリーム、すなわち、入力起動(ピクセル)データおよび後続の乗累算シーケンスに対する初期値を指定する部分和値(畳み込みの場合、これらは、部分的に演算された出力ピクセル / 起動である)が処理される。出力データ(結果として生じた累計済み部分和値)の単一のストリームが生成される。各部分和入力値は、最終的な部分和結果が出力として示される前に、固定長シーケンスの乗累算の対象となる。多くのドット積および累算は、演算エンジンによって上でされ、並列して発生する。第1の被乗数は、入力データストリームによって提供され、第2の被乗数は、共通の演算構成状態によって提供される。

[0120]

以下の表は、いくつかの例示的なampおよびslic命令の変形形態をリストし、実施形態では、それらのいずれかまたはすべては、プロセッサの命令セットに含めることができる。

### [0121]

### 【表1】

| 命令            | 入力データフォーマット | 入力部分和    | 出力部分和    |

|---------------|-------------|----------|----------|

|               |             | フォーマット   | フォーマット   |

| f16v4sisoamp  | 半精度 (v4)    | 単精度 (v2) | 単精度 (v2) |

| f16v4hihoamp  | 半精度 (v4)    | 半精度 (v2) | 半精度 (v2) |

| f16v4sihoamp  | 半精度 (v4)    | 単精度 (v2) | 半精度 (v2) |

| f32sisoamp    | 単精度 (スカラ)   | 単精度 (v2) | 単精度 (v2) |

| f16v4sisoslic | 半精度 (v4)    | 単精度 (v2) | 単精度 (v2) |

| f16v4hihoslic | 半精度 (v4)    | 半精度 (v2) | 半精度 (v2) |

| f16v4sihoslic | 半精度 (v4)    | 単精度 (v2) | 半精度 (v2) |

| f32sisoslic   | 単精度 (スカラ)   | 単精度 (v2) | 単精度 (v2) |

注:いくつかのタイプの命令では、重みの場所は完全に暗黙的であるが、他のタイプでは、多くの異なるセットのうちのどれをWRFにおいて使用するかを選択するオペランドを取る。f16v4sisoslic命令は、例えば、f16v4sisoampの重み状態の4分の1のみを必要とする。その結果、ソフトウェアは、最大で4セットの重みをプリロードすることができる。重みセット選択は、即値オペランドの2ビットによって指定される。他方では、f16v4sisoampの場合は、完全な重み状態を取り入れ、従って、その中での選択はない。

#### [ 0 1 2 2 ]

上記の実施形態は単なる例示として説明されていることが理解されよう。

### [ 0 1 2 3 ]

例えば、本開示の範囲は、上記で説明されるアーキテクチャであり、そのアーキテクチャでは、スーパーバイザスレッドに対して別個のコンテキストが提供されるか、または、スーパーバイザスレッドは、スロットで実行し、次いで、そのスロットをワーカーに委ねる。スーパーバイザは、代わりに、汎用コンテキストを使用することができる。あるいは、別の構成では、例えば、スーパーバイザは、それ自体の専用スロットで動作できる。さらに、実装形態は、スーパーバイザの役割さえも有するスレッドのうちの特定のものに限定されない。さらに、本開示の範囲は、タイルのアレイにおけるタイルであるプロセッサ

10

20

30

40

4 に限定されない。代替の実施形態では、プロセッサ 4 は、例えば、スタンドアロンプロセッサでも、単一チッププロセッサでもあってもよい。

### [0124]

実行ユニット18の実装形態は、別個のメイン実行ユニット18Mおよび補助実行ユニット18Aにも、別個のMRFおよびARFにも限定されない。一般に、レジスタは、1つまたは複数のレジスタファイルのいずれからのものでもあってもよく、異なるメモリアクセスと算術演算との間で共有することも、分離することもできる。

### [ 0 1 2 5 ]

共有の重みレジスタファイルを使用する算術命令は、行列積または畳み込み命令に限定されない。より一般的には、共有の重みレジスタファイルは、いかなるタイプの算術命令または命令の組合せに対しても使用することができ、例えば、別個の命令もしくは汎用コードにおいて累積が行われる非累積行列積命令、または、以前の積の結果が必ずしも後続の積の入力であるとは限らない行列乗算(畳み込み以外)の他のシーケンスに対して使用することができる。他の例は、ベクトルドット積または累積ベクトルドット積命令(すなわち、M個の異なるカーネルを並列して適用する必要がない算術命令)を含んでもよい。

#### [0126]

さらに、本開示の範囲は、例示として上記で開示される、特定のレジスタサイズ、ポートビット幅、ポートの数、値精度、ベクトルサイズまたは行列サイズに限定されない。他のレジスタおよびポートビット幅が可能であり、他の値の精度および他のベクトルまたは行列サイズ(例えば、要素の数の観点から)も同様に可能である。

#### [0127]

さらに、他の実装形態では、2つのレジスタへの2つのロードアドレスおよび1つのストアアドレスの他のパッキング(例えば、2つの16ビットレジスタへの3つの10ビットアドレス、または、2つの64ビットレジスタへの3つの42ビットアドレス)が可能である。また、ロードおよびストアアドレスは、必ずしも同じ長さである必要はない。さらに、代替の実装形態では、ストライドレジスタへのストライド値の他のパッキング(例えば、32ビットレジスタへの4つの8ビットストライドフィールドなど)も可能である

### [0128]

さらに、さらなる変形形態では、本開示の適用性は、画像処理に限定されない。「カーネル」という用語は、本明細書で使用される場合は、ベクトル乗算、行列乗算、畳み込みまたは他のもの(例えば、相関)などの演算を含む任意のプロセスの一部として適用されるいかなる重みの行列も意味してもよい。また、アプリケーション能力は、3 D ボリュームのデータに限定されない。入力データ(およびカーネル)は、線形でも、2 D でも、より高い多次元性(3 より大きい独立変数または自由度)を有するものでもあってもよい。さらに、本開示の範囲は、機械学習アプリケーションに限定されない。並列スレッド間で共通の1 つまたは複数のオペランドと各スレッドに特有の1 つまたは複数のオペランドとの組合せに基づいて動作を実行することが望ましい場合がある他の多くのアプリケーションが存在する。

### [0129]

開示される技法の他の変形形態または使用事例は、本明細書の本開示が与えられた時点で当業者に明らかになるであろう。本開示の範囲は、説明される実施形態による制限は受けず、添付の請求項による制限のみを受ける。

### 【符号の説明】

### [0130]

- 4 プロセッサ

- 6 タイルのアレイ

- 10 マルチスレッド処理装置

- 11 ローカルメモリ

- 12 命令メモリ

10

20

30

- 13 実行パイプライン

- 14 フェッチステージ

- 16 復号ステージ

- 18 実行ユニット

- 18A 補助実行ユニット

- 18 M メイン実行ユニット

- 22 データメモリ

- 24 スケジューラ

- 26 コンテキストレジスタファイル

- 2 6 A 補助レジスタファイル

- 26 С S R 制御状態レジスタ

- 26M メインレジスタタファイル

- 26W 共通の重みレジスタファイル

- 3 4 相互接続システム

- 5 1 交換インタフェース

- 53 命令バッファ

- 55 ロード/ストアユニット

- 5 6 整数演算論理ユニット

- 5 7 内部状態

- 102 ノード

- 104 エッジ

### 【図1】

### 【図2】

### 【図3】

### 【図4】

10

### 【図5】

### 【図6】

### 【図7】

### 【図8】

| \$mStrideA | strideA2 | strideA1 | strideA0 |

|------------|----------|----------|----------|

| \$mStrideB | strideB2 | strideB1 | strideB0 |

| \$mStrideC | strideC2 | strideC1 | strideC0 |

| ŧ          |          | :        |          |

### 【図9】

### 【図10】

# 【図11】

## 【図12-1】

| \$aSrc0 1                                          | \$AACC[14]                                                                                         | \$AACC[12]                                                                                               | \$AACC[10]                                                           | \$AACC[8]                                                            |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| 0 <sup>3</sup> lP <sub>0</sub> ,P <sub>1</sub>     |                                                                                                    |                                                                                                          |                                                                      |                                                                      |

| 0 P2,P3                                            |                                                                                                    | ,                                                                                                        |                                                                      | [WARM UP                                                             |

| 0 P4,P5                                            |                                                                                                    | •                                                                                                        |                                                                      |                                                                      |

| 0 P <sub>6</sub> ,P <sub>7</sub>                   |                                                                                                    |                                                                                                          |                                                                      |                                                                      |

| x <sub>0</sub> IP <sub>8</sub> .P <sub>9</sub>     | R <sub>7</sub> =x <sub>0</sub> .CW <sub>7,0</sub> +P <sub>7</sub>                                  | R <sub>6</sub> =x <sub>0</sub> .CW <sub>6,0</sub> +P <sub>6</sub>                                        | R <sub>5</sub> =x <sub>0</sub> .CW <sub>5,0</sub> +P <sub>5</sub>    | R <sub>4</sub> =x <sub>0</sub> .CW <sub>4,0</sub> +P <sub>4</sub>    |

| x <sub>1</sub>  P <sub>10</sub> ,P <sub>11</sub>   | R <sub>7</sub> =x <sub>1</sub> .CW <sub>7,1</sub>                                                  | R <sub>6</sub> =x <sub>1</sub> .CW <sub>6,1</sub>                                                        | R <sub>5</sub> =x <sub>1</sub> .CW <sub>5,1</sub>                    | R <sub>4</sub> =x <sub>1</sub> .CW <sub>4,1</sub>                    |

| x <sub>2</sub>  P <sub>12</sub> ,P <sub>13</sub>   | R <sub>7</sub> =x <sub>2</sub> .CW <sub>7,2</sub>                                                  | $R_6 = x_2 \cdot CW_{6,2}$                                                                               | R <sub>5</sub> =x <sub>2</sub> .CW <sub>5,2</sub>                    | R <sub>4</sub> =x <sub>2</sub> .CW <sub>4,2</sub>                    |

| x <sub>3</sub>  P <sub>14</sub> ,P <sub>15</sub>   | $R_7 = x_3 \cdot CW_{7,3}$                                                                         | R <sub>6</sub> =x <sub>3</sub> .CW <sub>6,3</sub>                                                        | R <sub>5</sub> =x <sub>3</sub> .CW <sub>5,3</sub>                    | R <sub>4</sub> =x <sub>3</sub> .CW <sub>4,3</sub>                    |

| x <sub>4</sub>  P <sub>16</sub> ,P <sub>17</sub>   | R <sub>15</sub> =x <sub>4</sub> .CW <sub>7,0</sub> +P <sub>15</sub>                                | R <sub>14</sub> =x <sub>4</sub> .CW <sub>6,0</sub> +P <sub>14</sub>                                      | R <sub>13</sub> =x <sub>4</sub> .CW <sub>5,0</sub> +P <sub>13</sub>  | R <sub>12</sub> =x <sub>4</sub> .CW <sub>4,0</sub> +P <sub>12</sub>  |

| x <sub>5</sub>  P <sub>18</sub> ,P <sub>19</sub>   | R <sub>15</sub> =x <sub>5</sub> .CW <sub>7,1</sub>                                                 | R <sub>14</sub> =x <sub>5</sub> .CW <sub>6,1</sub>                                                       | R <sub>13</sub> =x <sub>5</sub> .CW <sub>5,1</sub>                   | R <sub>12</sub> =x <sub>5</sub> .CW <sub>4,1</sub>                   |

| x <sub>6</sub>  P <sub>20</sub> ,P <sub>21</sub>   | R <sub>15</sub> =x <sub>6</sub> .CW <sub>7,2</sub>                                                 | R <sub>14</sub> =x <sub>6</sub> .CW <sub>6,2</sub>                                                       | R <sub>13</sub> =x <sub>6</sub> .CW <sub>5,2</sub>                   | R <sub>12</sub> =x <sub>6</sub> .CW <sub>4,2</sub>                   |

| x <sub>7</sub> IP <sub>22</sub> ,P <sub>23</sub>   | R <sub>15</sub> =x <sub>7</sub> .CW <sub>7,3</sub>                                                 | R <sub>14</sub> =x <sub>7</sub> .CW <sub>6,3</sub>                                                       | R <sub>13</sub> =x <sub>7</sub> .CW <sub>5,3</sub>                   | R <sub>12</sub> =x <sub>7</sub> .CW <sub>4,3</sub>                   |

| x <sub>8</sub> lP <sub>24</sub> ,P <sub>25</sub>   | R <sub>31</sub> =x <sub>8</sub> -CW <sub>7.0</sub> +P <sub>23</sub>                                | R <sub>22</sub> =x <sub>8</sub> .CW <sub>6,0</sub> +P <sub>22</sub>                                      | R <sub>21</sub> =x <sub>8</sub> .CW <sub>5,0</sub> +P <sub>21</sub>  | R <sub>20</sub> =x <sub>8</sub> .CW <sub>4,0</sub> +P <sub>20</sub>  |

| x <sub>9</sub>  P <sub>26</sub> ,P <sub>27</sub>   | R <sub>23</sub> =x <sub>9</sub> .CW <sub>7,1</sub>                                                 | $R_{22}=x_9.CW_{6,1}$                                                                                    | R <sub>21</sub> =x <sub>9</sub> .CW <sub>5,1</sub>                   | R <sub>20</sub> =x <sub>9</sub> .CW <sub>4,1</sub>                   |

| x <sub>10</sub> IP <sub>28</sub> ,P <sub>29</sub>  | R <sub>23</sub> =x <sub>10</sub> .CW <sub>7,2</sub>                                                | $R_{22} = x_{10} \cdot CW_{6,2}$                                                                         | $R_{21}=x_{10}$ :CW <sub>5,2</sub>                                   | R <sub>20</sub> =x <sub>10</sub> .CW <sub>4,2</sub>                  |

| X <sub>11</sub> IP <sub>30</sub> ,P <sub>31</sub>  | R <sub>23</sub> =x <sub>11</sub> .CW <sub>7,3</sub>                                                | $R_{22}=x_{11}.CW_{6,3}$                                                                                 | R <sub>21</sub> =x <sub>11</sub> .CW <sub>5.3</sub>                  | R <sub>20</sub> =x <sub>11</sub> .CW <sub>4,3</sub>                  |

| x <sub>12</sub> IP <sub>32</sub> ,P <sub>33</sub>  | R <sub>31</sub> =x <sub>12</sub> .CW <sub>7,0</sub> +P <sub>31</sub>                               | R <sub>30</sub> =x <sub>12</sub> .CW <sub>6,0</sub> +P <sub>30</sub>                                     | R <sub>29</sub> =x <sub>12</sub> .CW <sub>5,0</sub> +P <sub>29</sub> | R <sub>28</sub> =x <sub>12</sub> .CW <sub>4,0</sub> +P <sub>28</sub> |

| P.は、再构度人)<br>xaは、F16v4人力<br>CWは、共通のi<br>Riは、P.で始まる | "Att、HW/位人力部分和1である。<br>"sdt、F1694人リペクトルである。<br>78は、F3道の毛み状態50812 m.nである。<br>8.は、P.で始まる道絵ドット程界積の複終1 | "はた、単格度人力部分和である。<br>sdt、F16v1人力ペクトルである。<br>"%は、Us値の再み状態80M11.m.nである。<br>8.は、P.で始まる連絡ドット程界積の最終的な単構度結果である。 |                                                                      |                                                                      |

# 【図12-2】

| PERIOD]                                                              |                                                                      |                                                                      |                                                                      |                                  |

|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------|

|                                                                      |                                                                      |                                                                      | •                                                                    | ,                                |

|                                                                      |                                                                      |                                                                      | ,                                                                    |                                  |

| R <sub>3</sub> =x <sub>0</sub> .CW <sub>3,0</sub> +P <sub>3</sub>    | R <sub>2</sub> =x <sub>0</sub> .CW <sub>2,0</sub> +P <sub>2</sub>    | R <sub>1</sub> =x <sub>0</sub> .CW <sub>1,0</sub> +P <sub>1</sub>    | R <sub>0</sub> =x <sub>0</sub> .CW <sub>0,0</sub> +P <sub>0</sub>    | ı                                |

| R <sub>3</sub> =x <sub>1</sub> .CW <sub>3,1</sub>                    | R <sub>2</sub> =x <sub>1</sub> .CW <sub>2,1</sub>                    | R <sub>1</sub> =x <sub>1</sub> .CW <sub>1,1</sub>                    | R <sub>0</sub> =x <sub>1</sub> .CW <sub>0,1</sub>                    |                                  |

| R <sub>3</sub> =x <sub>2</sub> .CW <sub>3,2</sub>                    | R <sub>2</sub> =x <sub>2</sub> .CW <sub>2,2</sub>                    | R <sub>1</sub> =x <sub>2</sub> .CW <sub>1,2</sub>                    | R <sub>0</sub> =x <sub>2</sub> .CW <sub>0,2</sub>                    | ,                                |

| R <sub>3</sub> =x <sub>3</sub> .CW <sub>3,3</sub>                    | R <sub>2</sub> =x <sub>3</sub> .CW <sub>2,3</sub>                    | R <sub>1</sub> =x <sub>3</sub> .CW <sub>1,3</sub>                    | R <sub>0</sub> =x <sub>3</sub> .CW <sub>0,3</sub>                    | ,                                |

| R <sub>11</sub> =x <sub>4</sub> .CW <sub>3,0</sub> +P <sub>11</sub>  | R <sub>10</sub> =x <sub>4</sub> .CW <sub>2,0</sub> +P <sub>10</sub>  | R <sub>9</sub> =x <sub>4</sub> .CW <sub>1,0</sub> +P <sub>9</sub>    | R <sub>8</sub> =x <sub>4</sub> .CW <sub>0,0</sub> +P <sub>8</sub>    | R <sub>0</sub> ·R <sub>1</sub>   |

| R <sub>11</sub> =x <sub>5</sub> .CW <sub>3,1</sub>                   | R <sub>10</sub> =x <sub>5</sub> .CW <sub>2.1</sub>                   | R <sub>9</sub> =x <sub>5</sub> .CW <sub>1,1</sub>                    | R <sub>8</sub> =x <sub>5</sub> .CW <sub>0,1</sub>                    | R <sub>2</sub> ,R <sub>3</sub>   |

| R <sub>11</sub> =x <sub>6</sub> .CW <sub>3,2</sub>                   | R <sub>10</sub> =x <sub>6</sub> .CW <sub>2,2</sub>                   | R <sub>9</sub> =x <sub>6</sub> .CW <sub>1,2</sub>                    | R <sub>8</sub> =x <sub>6</sub> .CW <sub>0,2</sub>                    | R <sub>4</sub> ,R <sub>5</sub>   |

| R <sub>11</sub> =x <sub>7</sub> .CW <sub>3,3</sub>                   | R <sub>10</sub> =x <sub>7</sub> .CW <sub>2.3</sub>                   | R <sub>9</sub> =x <sub>7</sub> .CW <sub>1,3</sub>                    | R <sub>8</sub> =x <sub>7</sub> .CW <sub>0.3</sub>                    | R <sub>6</sub> ,R <sub>7</sub>   |

| R <sub>19</sub> =x <sub>8</sub> .CW <sub>3,0</sub> +P <sub>19</sub>  | R <sub>18</sub> =x <sub>8</sub> .CW <sub>2,0</sub> +P <sub>18</sub>  | R <sub>17</sub> =x <sub>8</sub> .CW <sub>1,0</sub> +P <sub>17</sub>  | R <sub>16</sub> =x <sub>8</sub> .CW <sub>0,0</sub> +P <sub>16</sub>  | R <sub>8</sub> ,R <sub>9</sub>   |

| R <sub>19</sub> =x <sub>9</sub> .CW <sub>3,1</sub>                   | R <sub>18</sub> =x <sub>9</sub> .CW <sub>2,1</sub>                   | R <sub>17</sub> =x <sub>9</sub> .CW <sub>1,1</sub>                   | R <sub>16</sub> =x <sub>9</sub> .CW <sub>0,1</sub>                   | R <sub>10</sub> 'R <sub>11</sub> |

| R <sub>19</sub> =x <sub>10</sub> .CW <sub>3,2</sub>                  | R <sub>18</sub> =x <sub>10</sub> .CW <sub>2,2</sub>                  | R <sub>17</sub> =x <sub>10</sub> .CW <sub>1,2</sub>                  | R <sub>16</sub> =x <sub>10</sub> .CW <sub>0,2</sub>                  | R <sub>12</sub> ,R <sub>13</sub> |

| R <sub>19</sub> =x <sub>11</sub> .CW <sub>3,3</sub>                  | R <sub>18</sub> =x <sub>11</sub> .CW <sub>2.3</sub>                  | R <sub>17</sub> =x <sub>11</sub> .CW <sub>1,3</sub>                  | R <sub>16</sub> =x <sub>11</sub> .CW <sub>0,3</sub>                  | R <sub>14</sub> ,R <sub>15</sub> |

| R <sub>27</sub> =x <sub>12</sub> .CW <sub>3,0</sub> +P <sub>27</sub> | R <sub>26</sub> =x <sub>12</sub> .CW <sub>2,0</sub> +P <sub>26</sub> | R <sub>25</sub> =x <sub>12</sub> .CW <sub>1,0</sub> +P <sub>25</sub> | R <sub>24</sub> =x <sub>12</sub> .CW <sub>0,0</sub> +P <sub>24</sub> | R <sub>16</sub> ,R <sub>17</sub> |

【図13】

# 【図14-1】

# 【図14-2】

|                                                  | \$AACC[14]                                                                                                  | \$AACC[10]                                                                                           | \$AACC[6]                                          | \$AACC[2]                                         |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------|

|                                                  |                                                                                                             | R₁=x <sub>0</sub> .CW <sub>5,0</sub> +P₁                                                             |                                                    |                                                   |

|                                                  | •                                                                                                           | $R_3 = x_1 \cdot CW_{5,0} + P_3$                                                                     | R <sub>1</sub> =x <sub>1</sub> .CW <sub>3,0</sub>  |                                                   |

|                                                  | ·                                                                                                           | R <sub>5</sub> =x <sub>2</sub> .CW <sub>5,0</sub> +P <sub>5</sub>                                    | R <sub>3</sub> =x <sub>2</sub> .CW <sub>3,0</sub>  | R <sub>1</sub> =x <sub>2</sub> .CW <sub>1,0</sub> |

|                                                  | ,                                                                                                           | R <sub>7</sub> =x <sub>3</sub> .CW <sub>5.0</sub> +P <sub>7</sub>                                    | R <sub>5</sub> =x <sub>3</sub> .CW <sub>3.0</sub>  | R <sub>3</sub> =x <sub>3</sub> .CW <sub>1,0</sub> |

|                                                  | ,                                                                                                           | R <sub>9</sub> =x <sub>4</sub> .CW <sub>5,0</sub> +P <sub>9</sub>                                    | R <sub>7</sub> =x <sub>4</sub> .CW <sub>3,0</sub>  | R <sub>5</sub> =x <sub>4</sub> .CW <sub>1,0</sub> |

| x <sub>5</sub>  P <sub>10</sub> ,P <sub>11</sub> |                                                                                                             | R <sub>11</sub> =x <sub>5</sub> .CW <sub>5,0</sub> +P <sub>11</sub>                                  | R <sub>9</sub> =x <sub>5</sub> .CW <sub>3,0</sub>  | R <sub>7</sub> =x <sub>5</sub> .CW <sub>1,0</sub> |

|                                                  |                                                                                                             | R <sub>13</sub> =x <sub>6</sub> .CW <sub>5,0</sub> +P <sub>13</sub>                                  | R <sub>11</sub> =x <sub>6</sub> .CW <sub>3,0</sub> | R <sub>9</sub> =x <sub>6</sub> .CW <sub>1,0</sub> |

| l6v4si.                                          | 表3.156:f16v4sisosTic、1x4のシーケンス例。                                                                            | ス(例)。                                                                                                |                                                    |                                                   |

|                                                  | \$AACC[14]                                                                                                  | \$AACC[10]                                                                                           | \$AACC[6]                                          | \$AACC[2]                                         |

|                                                  | R <sub>1</sub> =x <sub>0</sub> .CW <sub>7.0</sub> +P <sub>1</sub>                                           |                                                                                                      |                                                    |                                                   |

|                                                  | R <sub>3</sub> =x <sub>1</sub> .CW <sub>7,0</sub> +P <sub>3</sub>                                           | R <sub>1</sub> =x <sub>4</sub> .CW <sub>5,0</sub>                                                    |                                                    |                                                   |

|                                                  | R <sub>5</sub> =x <sub>2</sub> .CW <sub>7,0</sub> +P <sub>5</sub>                                           | R <sub>3</sub> =x <sub>2</sub> .CW <sub>5,0</sub>                                                    | R <sub>1</sub> =x <sub>2</sub> .CW <sub>3,0</sub>  |                                                   |

|                                                  | R <sub>7</sub> =x <sub>3</sub> .CW <sub>7.0</sub> +P <sub>7</sub>                                           | R <sub>5</sub> =x <sub>3</sub> .CW <sub>5.0</sub>                                                    | R <sub>3</sub> =x <sub>3</sub> .CW <sub>3,0</sub>  | R <sub>1</sub> =x <sub>3</sub> .CW <sub>1,0</sub> |

|                                                  | R <sub>9</sub> =x <sub>4</sub> .CW <sub>7,0</sub> +P <sub>9</sub>                                           | $R_7 = x_4 \cdot CW_{5,0}$                                                                           | R <sub>5</sub> =x <sub>4</sub> .CW <sub>3,0</sub>  | R <sub>3</sub> =x <sub>4</sub> .CW <sub>1,0</sub> |

|                                                  | R <sub>11</sub> =x <sub>5</sub> .CW <sub>7,0</sub> +P <sub>11</sub>                                         | R <sub>9</sub> =x <sub>5</sub> .CW <sub>5.0</sub>                                                    | R <sub>7</sub> =x <sub>5</sub> .CW <sub>3,0</sub>  | R <sub>5</sub> =x <sub>5</sub> .CW <sub>1,0</sub> |

|                                                  | R <sub>13</sub> =x <sub>6</sub> .CW <sub>7,0</sub> +P <sub>13</sub>                                         | R <sub>11</sub> =x <sub>6</sub> .CW <sub>5,0</sub>                                                   | R <sub>9</sub> =x <sub>6</sub> .CW <sub>3.0</sub>  | R <sub>7</sub> =x <sub>6</sub> .CW <sub>1,9</sub> |

| 特度人。<br>6v4人人<br>共通の<br>で始まる                     | P.は、単物度人力部分和である。<br>%は、Ff6v1人力ペラトルである。<br>CM <sub>m.i</sub> は、共通の重み状態SCWE1_m.nである。<br>R.は、P.で始まる連続ドット程昇程の接約 | 5点に、再格度人力部分和である。<br>2dは、Ffeが人力ペクトルである。<br>CMは、共通の代み状態8CMEL.mである。<br>Ruは、R.で始まる連続ドット程異程の最終的な単精度結果である。 | 2                                                  |                                                   |

|                                                  |                                                                                                             |                                                                                                      |                                                    |                                                   |

| \$AACC[12]                                       | \$AACC[8]                                                                                                   | \$AACC[4]                                                                                            | \$AACC[0]                                          | \$aDst0                                           |

|                                                  | R <sub>0</sub> =x <sub>0</sub> .CW <sub>4.0</sub> +P <sub>0</sub>                                           |                                                                                                      |                                                    |                                                   |

|                                                  | R <sub>2</sub> =x <sub>1</sub> .CW <sub>4,0</sub> +P <sub>2</sub>                                           | R <sub>0</sub> =x <sub>1</sub> .CW <sub>2,0</sub>                                                    |                                                    | •                                                 |