# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110456889 B (45) 授权公告日 2024. 08. 13

(21)申请号 201910894251.1

(22)申请日 2019.09.20

(65) 同一申请的已公布的文献号 申请公布号 CN 110456889 A

(43)申请公布日 2019.11.15

(73) 专利权人 广州市智谱科技有限公司 地址 510700 广东省广州市黄埔区伴河路 118号601房

专利权人 湖南慧谱科技有限公司

(72)发明人 何巨彬 詹植广 林镜棠 周俊宇

(74) 专利代理机构 深圳市舜立知识产权代理事务所(普通合伙) 44335

专利代理师 侯艺

(51) Int.CI.

GO6F 1/18 (2006.01)

(56)对比文件

CN 210199661 U,2020.03.27

审查员 俞姝颖

权利要求书2页 说明书6页 附图3页

## (54) 发明名称

基于ARM架构的边缘计算阵列服务器

#### (57) 摘要

1.一种基于ARM架构的边缘计算阵列服务器,包括背板和可拆卸电性连接于背板的多个底板,其特征在于,

所述背板包括第一电路板,所述第一电路板上设有第一电源芯片、主芯片、第一PHY芯片、至少一个万兆网接口、多个第一千兆网接口及多个第二千兆网接口,所述第一电源芯片电性连接主芯片、第一PHY芯片及万兆网接口,所述第一PHY芯片电性连接主芯片和第一千兆网接口的输出端,所述万兆网接口的输出端和第二千兆网接口的输出端电性连接主芯片,所述万兆网接口的输入端用于与外部的互联网通讯连接;

所述底板包括第二电路板,所述第二电路板上设有第二电源芯片、核心板及第二PHY芯片,所述第二PHY芯片电性连接第二电源芯片和核心板,第二PHY芯片可拆卸电性连接所述背板的第二千兆网接口或第一千兆网接口的输入端;

所述核心板包括ARM处理器、DDR存储器及FLASH芯片,所述DDR存储器和FLASH芯片电性连接ARM处理器,所述第二电源芯片和第二PHY芯片电性连接ARM处理器;

该第一千兆网接口为序列16至24网口;该第二千兆网接口为序列1至15网口。

- 2.如权利要求1所述的基于ARM架构的边缘计算阵列服务器,其特征在于,所述第一电源芯片包括第一背板电源芯片、第二背板电源芯片、第三背板电源芯片,所述第一背板电源芯片、第三背板电源芯片、第三背板电源芯片均电性连接外部的接入电源,所述第一背板电源芯片电性连接第一PHY芯片和主芯片,所述第二背板电源芯片电性连接第一PHY芯片、主芯片及万兆网接口,所述第三背板电源芯片电性连接主芯片。

- 3.如权利要求2所述的基于ARM架构的边缘计算阵列服务器,其特征在于,第二电源芯片包括第一底板电源芯片、第二底板电源芯片及第三底板电源芯片,所述第一底板电源芯片、第二底板电源芯片及第三底板电源芯片均电性连接外部的接入电源,所述第一底板电源芯片电性连接第二PHY芯片和ARM处理器,所述第二底板电源芯片电性连接ARM处理器,所述第三底板电源芯片电性连接ARM处理器。

- 4.如权利要求3所述的基于ARM架构的边缘计算阵列服务器,其特征在于,所述第二电路板上设有USB连接器,USB连接器电性连接ARM处理器,所述第三底板电源芯片电性连接USB连接器。

- 5.如权利要求1所述的基于ARM架构的边缘计算阵列服务器,其特征在于,该基于ARM架构的边缘计算阵列服务器还包括串行接口,所述串行接口与主芯片电性连接。

- 6.如权利要求3所述的基于ARM架构的边缘计算阵列服务器,其特征在于,所述主芯片的型号为BCM56150、第一PHY芯片的型号为B50282、第一背板电源芯片的型号为RT8120、第二背板电源芯片的型号为RT8293A、第三背板电源芯片的型号为RT8120;

第一底板电源芯片的型号为RT8272GS、第二底板电源芯片的型号为ZTP7106T、第三底板电源芯片的型号为RT8272GS、第二PHY芯片的型号为RTL8211。

7.如权利要求1-6任一项所述的基于ARM架构的边缘计算阵列服务器,其特征在于,该基于ARM架构的边缘计算阵列服务器还包括壳体,所述壳体的一端设有开口,所述背板设于所述壳体内壁,所述背板位于所述壳体远离开口的一端,所述第一千兆网接口和第二千兆网接口呈矩形阵列分布于第一电路板上,所述背板的第一千兆网接口和第二千兆网接口面向所述开口的一端,所述第二电路板为矩形结构,所述第二电路板的第一个边沿、第二个边沿,第三个边沿均设有护板,所述第二电路板的第一个边沿的护板与所述第二电路板的第

- 三个边沿的护板相对设置,三个护板与第二电路板围成一个容置区域,第二电源芯片、ARM 处理器及第二PHY芯片均位于所述容置区域内,与所述第二PHY芯片连接的接口位于所述第二电路板的第四个边沿,所述底板连接于背板时,所述底板设有第二PHY芯片的接口的一端穿过开口置于容置区域内,并与一个第一千兆网接口或一个第二千兆网接口连接,所述第二电路板的第二边沿的护板部分盖合于开口。

- 8. 如权利要求7所述的基于ARM架构的边缘计算阵列服务器,其特征在于,所述开口为矩形结构,所述第二电路板的第二边沿的护板为矩形结构,所述第二电路板的第二边沿的护板的面积与开口的面积大小比值为1:24。

# 基于ARM架构的边缘计算阵列服务器

#### 技术领域

[0001] 本发明涉及服务器技术领域,特别涉及一种基于ARM架构的边缘计算阵列服务器。

### 背景技术

[0002] 目前市场上刀片服务器是指在标准高度的机架式机箱内可插装多个卡式的服务器单元。专门为特殊应用行业和高密度计算机环境设计的,其主要结构为一大型主体机箱,内部可插上许多"刀片",其中每一块"刀片"实际上就是一块系统主板。它们可以通过"板载"硬盘启动自己的操作系统,类似于一个个独立的服务器,在这种模式下,每一块母板运行自己的系统,服务于指定的不同用户群,相互之间没有关联。不过,管理员可以将这些母板集合成一个服务器集群。在集群模式下,所有的母板可以连接起来提供高速的网络环境,并同时共享资源,为相同的用户群服务。由于每块"刀片"都是热插拔的,所以,系统可以地进行替换。但是现有的刀片服务器缺陷是功耗大,其机柜与刀片价格都比较昂贵,对于拥有一个或两个刀片中心的企业用户来说,成本太高。

## 发明内容

[0003] 本发明的主要目的是提供一种基于ARM架构的边缘计算阵列服务器,旨在将底板集成到连接有互联网的背板上,可提供高速的网络环境并共享资源,结构简单,功耗低,成本低。

[0004] 为实现上述目的,本发明提出一种基于ARM架构的边缘计算阵列服务器,该基于ARM架构的边缘计算阵列服务器包括背板和可拆卸电性连接于背板的多个底板,

[0005] 所述背板包括第一电路板,所述第一电路板上设有第一电源芯片、主芯片、第一PHY芯片、至少一个万兆网接口、多个第一千兆网接口及多个第二千兆网接口,所述第一电源芯片电性连接主芯片、第一PHY芯片及万兆网接口,所述第一PHY芯片电性连接主芯片和第一千兆网接口的输出端,所述万兆网接口的输出端和第二千兆网接口的输出端电性连接主芯片,所述万兆网接口的输入端用于与外部的互联网通讯连接;

[0006] 所述底板包括第二电路板,所述第二电路板上设有第二电源芯片、核心板及第二 PHY芯片,所述第二PHY芯片电性连接第二电源芯片和核心板,第二PHY芯片可拆卸电性连接 所述背板的第二千兆网接口或第一千兆网接口的输入端。

[0007] 优选地,所述核心板包括ARM处理器、DDR存储器及FLASH芯片,所述DDR存储器和FLASH芯片电性连接ARM处理器,所述第二电源芯片和第二PHY芯片电性连接ARM处理器。

[0008] 优选地,所述第一电源芯片包括第一背板电源芯片、第二背板电源芯片、第三背板电源芯片,所述第一背板电源芯片、第二背板电源芯片、第三背板电源芯片均电性连接外部的接入电源,所述第一背板电源芯片电性连接第一PHY芯片和主芯片,所述第二背板电源芯片电性连接第一PHY芯片、主芯片及万兆网接口,所述第三背板电源芯片电性连接主芯片。

[0009] 优选地,第二电源芯片包括第一底板电源芯片、第二底板电源芯片及第三底板电源芯片,所述第一底板电源板芯片、第二底板电源芯片及第三底板电源芯片均电性连接外

部的接入电源,所述第一底板电源芯片电性连接第二PHY芯片和ARM处理器,所述第二底板电源芯片电性连接ARM处理器,所述第三底板电源芯片电性连接ARM处理器。

[0010] 优选地,所述第二电路板上设有USB连接器,USB连接器电性连接ARM处理器,所述第三底板电源芯片电性连接USB连接器。

[0011] 优选地,第一千兆网接口为序列16至24网口;第二千兆网接口为序列1至15网口。

[0012] 优选地,该基于ARM架构的边缘计算阵列服务器还包括串行接口,所述串行接口与 主芯片电性连接。

[0013] 优选地,所述主芯片的型号为BCM56150、第一PHY芯片的型号为B50282、第一背板电源芯片的型号为RT8120、第二背板电源芯片的型号为RT8293A、第三背板电源芯片的型号为RT8120;

[0014] 第一底板电源芯片的型号为RT8272GS、第二底板电源芯片的型号为ZTP7106T、第三底板电源芯片的型号为RT8272GS、第二PHY芯片的型号为RTL8211。

[0015] 优选地,该基于ARM架构的边缘计算阵列服务器还包括壳体,所述壳体的一端设有开口,所述背板设于所述壳体内壁,所述背板位于所述壳体远离开口的一端,所述第一千兆网接口和第二千兆网接口呈矩形阵列分布于第一电路板上,所述背板的第一千兆网接口和第二千兆网接口面向所述开口的一端,所述第二电路板为矩形结构,所述第二电路板的第一个边沿、第三个边沿均设有护板,所述第二电路板的第一个边沿的护板与所述第二电路板的第三个边沿的护板相对设置,三个护板与第二电路板围成一个容置区域,第二电源芯片、ARM处理器及第二PHY芯片均位于所述容置区域内,所述第二PHY芯片的接口位于所述第二电路板的第四个边沿,所述底板连接于背板时,所述底板设有第二PHY芯片的接口的一端穿过开口置于容置区域内,并与一个第一千兆网接口或一个第二千兆网接口连接,所述第二电路板的第二边沿的护板部分盖合于开口。

[0016] 优选地,所述开口为矩形结构,所述第二电路板的第二边沿的护板为矩形结构,所述第二电路板的第二边沿的护板的面积与开口的面积大小比值为1:24。

[0017] 本发明技术方案通过背板和可拆卸电性连接于背板的多个底板,所述背板包括第一电路板,所述第一电路板上设有第一电源芯片、主芯片、第一PHY芯片、至少一个万兆网接口、多个第一千兆网接口及多个第二千兆网接口,所述第一电源芯片电性连接主芯片、第一PHY芯片及万兆网接口,所述第一PHY芯片电性连接主芯片和第一千兆网接口的输出端,所述万兆网接口的输出端和第二千兆网接口的输出端电性连接主芯片,所述万兆网接口的输入端用于与外部的互联网通讯连接;所述底板包括第二电路板,所述第二电路板上设有第二电源芯片、核心板及第二PHY芯片,所述第二PHY芯片电性连接第二电源芯片和核心板,第二PHY芯片可拆卸电性连接所述背板的第二千兆网接口或第一千兆网接口的输入端,以此将多个底板集成到连接有互联网的背板上,底板之间的信息交换及与外部的信息交换均通过互联网传输即可实现,可提供高速的网络环境并共享资源,适合在网络边缘环境部署,能更好的支持以ARM架构的多种智能终端的计算任务,并且相对于现有的刀片服务器结构更简单,功耗低,成本也更低。

#### 附图说明

[0018] 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现

有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

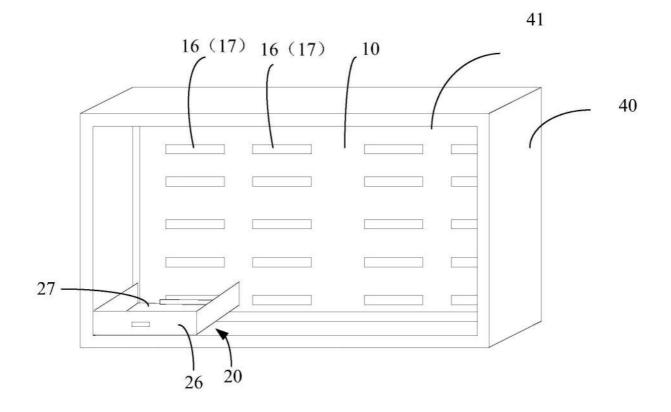

[0019] 图1为本发明基于ARM架构的边缘计算阵列服务器一实施例的结构示意图;

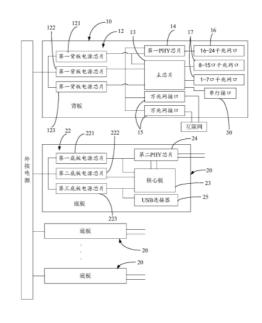

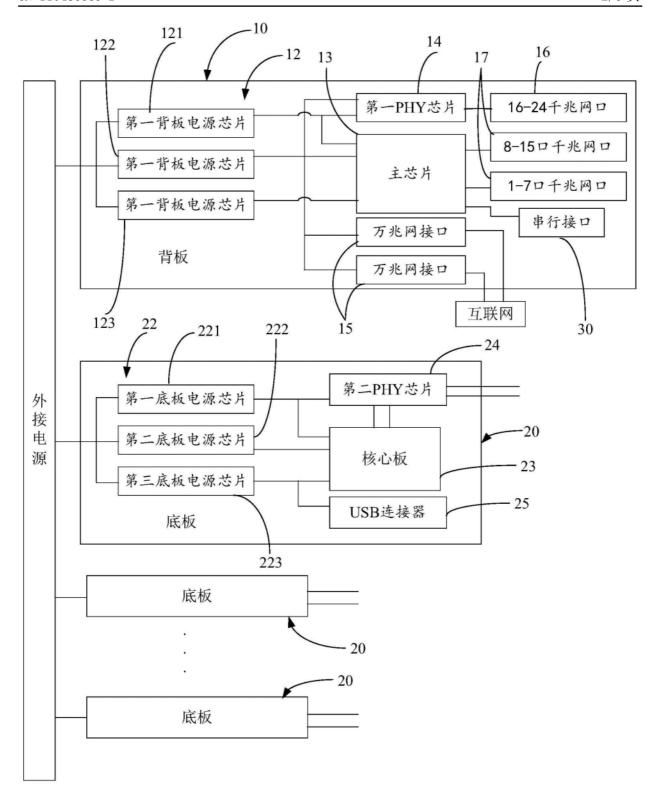

[0020] 图2为本发明基于ARM架构的边缘计算阵列服务器一实施例的内部电路结构示意图;

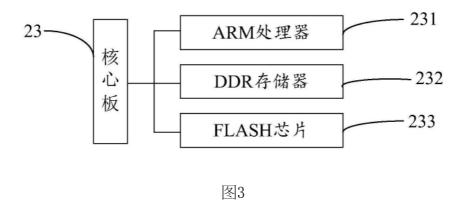

[0021] 图3为图2基于ARM架构的边缘计算阵列服务器的核心板的电路组成结构示意图。

[0022] 附图标号说明:

[0023]

| 标号  | 名称       | 标号  | 名称        |

|-----|----------|-----|-----------|

| 10  | 背板       | 222 | 第二底板电源芯片  |

| 12  | 第一电源芯片   | 223 | 第三底板电源芯片  |

| 121 | 第一背板电源芯片 | 23  | 核心板       |

| 122 | 第二背板电源芯片 | 231 | ARM处理器    |

| 123 | 第三背板电源芯片 | 232 | DDR存储器    |

| 13  | 主芯片      | 233 | FLASH芯片   |

| 14  | 第一PHY芯片  | 24  | 第二PHY芯片   |

| 15  | 万兆网接口    | 25  | USB连接器    |

| 16  | 第一千兆网接口  | 26  | 护板        |

| 17  | 第二千兆网接口  | 27  | 容置区域      |

| 20  | 底板       | 30  | 串行接口      |

| 22  | 第二电源芯片   | 40  | <b>売体</b> |

| 221 | 第一底板电源芯片 | 41  | 开口        |

[0024] 本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

#### 具体实施方式

[0025] 下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0026] 需要说明,本发明实施例中所有方向性指示(诸如上、下、左、右、前、后……)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

[0027] 在本发明中,除非另有明确的规定和限定,术语"连接"、"固定"等应做广义理解,例如,"固定"可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系,除非另有明确的限定。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

[0028] 另外,在本发明中如涉及"第一"、"第二"等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有"第一"、

"第二"的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

[0029] 本发明提出一种基于ARM架构的边缘计算阵列服务器。

[0030] 参照图1至图3,在本发明一实施例中,该基于ARM架构的边缘计算阵列服务器包括背板10和可拆卸电性连接于背板10的多个底板20,

[0031] 所述背板10包括第一电路板,所述第一电路板上设有第一电源芯片12、主芯片13、第一PHY芯片14、至少一个万兆网接口15、多个第一千兆网接口16及多个第二千兆网接口17,所述第一电源芯片12电性连接主芯片13、第一PHY芯片14及万兆网接口15,所述第一PHY芯片14电性连接主芯片13和第一千兆网接口16的输出端,所述万兆网接口15的输出端和第二千兆网接口17的输出端电性连接主芯片13,所述万兆网接口15的输入端用于与外部的互联网通讯连接;

[0032] 所述底板20包括第二电路板,所述第二电路板上设有第二电源芯片22、核心板23及第二PHY芯片24,所述第二PHY芯片24电性连接第二电源芯片22和核心板23,第二PHY芯片24可拆卸电性连接所述背板10的第二千兆网接口17或第一千兆网接口16的输入端。

[0033] 其中的万兆网接口15的输入端用于与外部的互联网通讯连接,具体可为万兆网接口15的输入端与一电脑主板连接,通过电脑接入互联网进行通讯。其中的所述主芯片13的型号为BCM56150、第一PHY芯片14的型号为B50282、第二PHY芯片24的型号为RTL8211。其中的核心板23是将MINIPC的核心功能打包封装的一块电子主板,参照图3,所述核心板23包括ARM处理器231、DDR存储器232及FLASH芯片233,所述DDR存储器232和FLASH芯片233电性连接ARM处理器231,所述第二电源芯片22和第二PHY芯片24电性连接ARM处理器231。其中的ARM处理器231、DDR存储器232及FLASH芯片233均可采用惯常设计即可,当底板20掉电后,存储的数据不会丢失,作用主要是存储软件资料。DDR存储器232为随机存储器,当背板10关机后,背板10和底板20都断电,里面寄存的程序会消失,它的作用是负责从ARM处理器231和FLASH芯片233之间传送数据起中转、缓冲作用。通过核心板23可使该基于ARM架构的边缘计算阵列服务器的结构更简单,相对成本更低。第一千兆网接口16为序列16至24网口;第二千兆网接口17为序列1至15网口,以便于满足不同使用需求,并且由于第二千兆网接口17不需要连接第一PHY芯片14,可节省元件,使其结构更简单,有利于降低成本。

[0034] 以此将多个底板20集成到连接有互联网的背板10上,底板20之间的信息交换及与外部的信息交换均通过互联网传输即可实现,可提供高速的网络环境并共享资源,并且相对于现有的刀片服务器结构更简单,功耗低,成本更低。

[0035] 参照图2,优选地,所述第一电源芯片12包括第一背板电源芯片121、第二背板电源芯片122、第三背板电源芯片123,所述第一背板电源芯片121、第二背板电源芯片122、第三背板电源芯片123均电性连接外部的接入电源,所述第一背板电源芯片121电性连接第一PHY芯片14和主芯片13,所述第二背板电源芯片122电性连接第一PHY芯片14、主芯片13及万兆网接口15,所述第三背板电源芯片123电性连接主芯片13。

[0036] 具体的,其中第一背板电源芯片121的型号可为RT8120、第二背板电源芯片122的型号可为RT8293A、第三背板电源芯片123的型号可为RT8120,所述第一背板电源芯片121、

第二背板电源芯片122、第三背板电源芯片123均电性连接外部的接入电源12V电压,第一背板电源芯片121输出1V电压分别给第一PHY芯片14和主芯片13,第二背板电源芯片122输出3.3V电压分别给第一PHY芯片14、主芯片13及万兆网接口15,第三背板电源芯片123输出1.5V电压给主芯片13,以此使背板10上的主芯片13、第一PHY芯片14及万兆网接口15进行工作时更稳定。

[0037] 优选地,第二电源芯片22包括第一底板电源芯片221、第二底板电源芯片222及第三底板电源芯片223,所述第一底板电源板芯片221、第二底板电源芯片222及第三底板电源芯片223均电性连接外部的接入电源,所述第一底板电源芯片221电性连接第二PHY芯片24和ARM处理器231,所述第二底板电源芯片222电性连接ARM处理器231,所述第三底板电源芯片223电性连接ARM处理器231。

[0038] 具体地,其中第一底板电源芯片221的型号可为RT8272GS、第二底板电源芯片222的型号可为ZTP7106T、第三底板电源芯片223的型号可为RT8272GS,所述第一底板电源芯片221、第二底板电源芯片222、第三底板电源芯片223均电性连接外部的接入电源12V电压,所述第一底板电源芯片221输出3.3V给第二PHY芯片24和ARM处理器231,第二底板电源芯片222输出1.8V给ARM处理器231,第三底板电源芯片223输出5V给ARM处理器231,ARM处理器231计算集群,能更好支持来自以ARM处理器231为中央处理器的各类型智能终端的计算任务,以此使底板20上的第二PHY芯片24和ARM处理器231进行工作时更稳定。

[0039] 优选地,所述第二电路板上设有USB连接器25,USB连接器25电性连接ARM处理器231,所述第三底板电源芯片223电性连接USB连接器25。通过USB连接器25可便于连接外部的存储设备,如U盘或具有存储功能的电子设备,以便于外部设备与该基于ARM架构的边缘计算阵列服务器进行数据交换。

[0040] 优选地,该基于ARM架构的边缘计算阵列服务器还包括串行接口30,所述串行接口30与主芯片13电性连接。其中的串行接口30是采用串行通信方式的扩展接口,如串行接口30可为RS-232-C、RS-422或RS485,以满足用户更多的使用需求。

[0041] 参照图3,优选地,该基于ARM架构的边缘计算阵列服务器还包括壳体40,所述壳体40的一端设有开口41,所述背板10设于所述壳体40内壁,所述背板10位于所述壳体40远离开口的一端,所述第一千兆网接口16和第二千兆网接口17呈矩形阵列分布于第一电路板上,所述背板10的第一千兆网接口16和第二千兆网接口17面向所述开口41的一端,所述第二电路板为矩形结构,所述第二电路板的第一个边沿、第二个边沿、第三个边沿均设有护板26,所述第二电路板的第一个边沿的护板26与所述第二电路板的第三个边沿的护板26相对设置,三个护板26与第二电路板围成一个容置区域27,第二电源芯片22、ARM处理器231及第二PHY芯片24均位于所述容置区域27内,与所述第二PHY芯片24连接的接口位于所述第二电路板的第四个边沿,所述底板20连接于背板10时,所述底板20设有第二PHY芯片24的接口的一端穿过开口41置于容置区域27内,并与一个第一千兆网接口16或一个第二千兆网接口17连接,所述第二电路板的第二边沿的护板26部分盖合于开口41。

[0042] 其中的壳体40可为金属材质,与所述第二PHY芯片24连接的接口与干兆网接口16或第二干兆网接口17的输入端相适配,所述第二电路板的第二个边沿的护板26的两端与对应的第一个边沿护板和第三个边沿护板连接,通过三个护板26可防止连接在背板10上的相邻的两个底板20上的电子元件形成干扰,使其结构更合理,还便于对第二电路板上的电子

元器件之间导线的收纳整理,使其使用更方便。优选地,所述开口41为矩形结构,所述第二电路板的第二边沿的护板26为矩形结构,所述第二电路板的第二边沿的护板26的面积与开口41的面积大小比值为1:24。以此当24个底板20与对应的第一千兆网接口16或一个第二千兆网接口17连接后,第二电路板的第二边沿的护板26可刚好完全盖合于开口41,使其结构更简单,并可防止灰尘,使其通讯更稳定。更进一步地,第二电路板的第二边沿的护板26可设有拉手(未标示),可更方便其使用。

[0043] 以上所述仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是在本发明的发明构思下,利用本发明说明书及附图内容所作的等效结构变换,或直接/间接运用在其他相关的技术领域均包括在本发明的专利保护范围内。

图1

图2