# (10) **DE 10 2012 206 531 B4** 2015.09.10

(12)

## **Patentschrift**

(21) Aktenzeichen: 10 2012 206 531.8

(22) Anmeldetag: 20.04.2012(43) Offenlegungstag: 17.10.2013(45) Veröffentlichungstag

der Patenterteilung: 10.09.2015

(51) Int Cl.: **B81C 1/00** (2006.01)

**B81B 7/02** (2006.01) **H01L 21/265** (2006.01)

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(66) Innere Priorität:

10 2012 206 328.5 17.04.2012

(73) Patentinhaber:

Infineon Technologies AG, 85579 Neubiberg, DE

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler, Zinkler, Schenk & Partner mbB Patentanwälte, 81373 München, DE (72) Erfinder:

Schreiber, Kai-Alexander, Villach, AT; Behrendt, Andreas, Villach, AT; Sgouridis, Sokratis, Annenheim, AT; Winkler, Bernhard, 93049 Regensburg, DE; Zgaga, Martin, Rosegg, AT

(56) Ermittelter Stand der Technik:

DE 40 00 496 A1 US 2008 / 0 061 029 A1 US 2009 / 0 007 681 A1 US 5 719 073 A US 5 445 718 A

### (54) Bezeichnung: Verfahren zur Erzeugung einer Kavität innerhalb eines Halbleitersubstrats

(57) Hauptanspruch: Verfahren zum Herstellen eines mikroelektromechanischen Systems mit folgenden Merkmalen:

Bereitstellen eines dotierten Halbleitersubstrats mit einer ersten Oberfläche und einer der ersten Oberfläche gegenüber liegenden zweiten Oberfläche;

Durchführen eines Lithographieprozesses und einer anschließenden Implantation zur Herstellung eines umdotierten Bereichs innerhalb des dotierten Halbleitersubstrats, wobei ein pn-Übergang bei einer Tiefe innerhalb des Halbleitersubstrats gebildet wird, wobei die Tiefe des pn-Übergangs eine gewünschte Tiefe eines Bodens zumindest einer zu bildenden Kavität bestimmt;

Durchführen eines Strukturierungsprozesses zur Herstellung von mikroelektromechanischen Strukturen in dem Halbleitersubstrat und an der zweiten Oberfläche, wobei zumindest ein Teil der vorgesehenen mikroelektromechanischen Strukturen sich in den umdotierten Bereich erstreckt; Trockenätzen des Halbleitersubstrats von der ersten Oberfläche des Halbleitersubstrats aus an zumindest einem beabsichtigten Kavitätsort, um zumindest eine vorläufige Kavität zu erhalten, wobei das Trockenätzen gestoppt wird, bevor die gewünschte Tiefe der Kavität erreicht wird;

Abscheiden eines Schutzmaterials hinsichtlich eines nachfolgenden elektrochemischen Ätzprozesses an der ersten Oberfläche des Halbleitersubstrats und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität;

Entfernen des Schutzmaterials zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität um das Halbleitersubstrat freizulegen; und

elektrochemisches Ätzen des Halbleitersubstrats an dem freigelegten Abschnitt des Bodens der zumindest einen vorläufigen Kavität bis zu dem pn-Übergang, so dass dieser als elektrochemischer Ätzstopp den Boden der zumindest einen Kavität bildet, so dass die zumindest eine Kavität an den Teil der mikroelektromechanischen Strukturen angrenzt, der sich in den umdotierten Bereich erstreckt.

#### **Beschreibung**

**[0001]** Ausführungsbeispiele der vorliegenden Erfindung schaffen Verfahren zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrat. Weitere Ausführungsbeispiele der vorliegenden Erfindung schaffen ein mikroelektromechanisches System

[0002] Manche mikroelektromechanische Systeme (engl. "microelectromechanical systems", MEMS), wie auch manche hoch integrierte Komponenten der Mikroelektronik benötigen relativ tiefe Kavitäten, Löcher bzw. Aussparungen. Zum Beispiel werden in der MEMS-Technologie die eigentlichen MEMS-Strukturen häufig an einer ersten Oberfläche eines Halbleitersubstrats (zum Beispiel der oberen Oberfläche bzw. einer Vorderseite) strukturiert. Je nach Typ der MEMS-Komponente kann es erforderlich sein, diese an der ersten Oberfläche bzw. an der Vorderseite vorhandenen Strukturen auch von einer zweiten Oberfläche bzw. Rückseite des Halbleitersubstrats zugänglich zu machen, wobei die zweite Oberfläche bezüglich des Halbleitersubstrats entgegengesetzt zu der ersten Oberfläche angeordnet ist. Ein Beispiel ist ein Drucksensor, dessen Membranen mittels ME-MS-Technologie an der ersten Oberfläche bzw. Vorderseite des Halbleitersubstrats bereitgestellt wird, aber zusätzlich auch einen Zugang von der zweiten Oberfläche bzw. Rückseite erfordert, über welchen die Membran mit dem zu messende Druck beaufschlagt werden kann. Weitere Beispiele sind akustische Wandler (Lautsprecher oder Mikrofon) und Beschleunigungssensoren. Die Herstellung von Kavitäten auf Silizium-Wafern (allgemein: Wafern aus Halbleitermaterial), welche für die Erzeugung von MEMS (mikroelektromechanische Systeme) Bauteilen (zum Beispiel Druck- und Beschleunigungssensoren) jeglicher Art (Sensoren und Aktuatoren) Anwendung finden, stellt eine häufig auftretende Aufgabe in der ME-MS-Technologie dar.

[0003] Derzeit werden diese Kavitäten typischerweise in Reinstsilizium mittels anisotroper, elektrochemischer Ätzung in TMAH (Tetramethylammoniumhydroxid) durchgeführt. Das Ätzen mit TMAH ist ein nasschemisches Ätzverfahren. Rein nass chemische geätzte Kavitäten weisen typischerweise flächenmäßig eine relativ große Ausdehnung auf, da selektiv mit natürlich vorgegebenem Flankenwinkel von 54, 7° (ätzselektiv vorgegebener Kristallwinkel zwischen den Si <100> und Si <111> Ebenen) geätzt wird. Anders ausgedrückt kann mit einem nasschemischen Ätzverfahren typischerweise nur ein relativ geringes Aspektverhältnis erzielt werden. Als Aspektverhältnis wird typischerweise das Verhältnis aus der Tiefe einer Struktur zu ihrer (kleinsten) lateralen Ausdehnung bezeichnet.

[0004] Ein bekanntes Verfahren zur Erzeugung von Kavitäten ist in DE 40 00 496 A1 gezeigt, wobei mit Hilfe einer Fotomaskierungstechnik zuerst mindestens eine Ausnehmung mit im Wesentlichen senkrecht zu den beiden Hauptoberflächen des Halbleiterkörpers verlaufenden seitlichen Begrenzungsflächen und einer im Wesentlichen parallel zu den beiden Hauptoberflächen verlaufenden Bodenfläche von einer der beiden Hauptoberflächen aus durch anisotropes reaktives Ionenätzen in den Halbleiterkörper eingeätzt wird und anschließend die Ausnehmung in der Nähe ihrer Bodenfläche durch isotropes Ätzen mit einer lateralen Erweiterung versehen wird. Darüber hinaus beschreibt US 5719073 A einen beispielhaften reaktiven Ionenätzprozess, sowie US 2008/0061029 A1 einen weiteren Ätzprozess. Ferner zeigen US 5445718 A sowie US 2009/0007681 A1 einen pn-Übergang, der als Ätzstopp wirkt.

[0005] Zu den nasschemischen Ätzverfahren wird auch das so genannte elektrochemische Ätzen gezählt. Das elektrochemische Ätzen (engl.: "Electrochemical Etching" (ECE)) für Dotierstoffselektives Entfernen von Silizium ist ein Verfahren, um den Ätzvorgang zu automatisieren und selektiv zu steuern. In der Regel wird ein aktiver pn-Übergang benötigt und beide Arten von Dotierstoffen können als ätz-resistentes Material ("Ätz-Stop") dienen. In Kombination mit einem anisotropen Ätzverfahren kann das elektrochemische Ätzen dazu verwendet werden, um zum Beispiel die Dicke von MEMS-Strukturen (z. B. Membrandicke bei piezo-resistiven Drucksensoren) mit hoher Genauigkeit kontrollieren zu können. Die dazu benötigten selektiv-dotierten Regionen können zum Beispiel durch Implantation, Diffusion oder epitaxiale Abscheidung von Silizium oder einem anderen Halbleitermaterial geschaffen werden. Die Ätztiefe (und damit gegebenenfalls auch die Dicke von entsprechenden MEMS-Strukturen) kann bei einem elektrochemischen Ätzverfahren mit einer Genauigkeit von ca. 0,05 µm, unter Umständen sogar mit einer Genauigkeit von ca. 0,03 µm kontrolliert werden.

[0006] Es wäre wünschenswert, ein Verfahren zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats zur Verfügung stellen zu können, das die Möglichkeit eines mit relativ hoher Genauigkeit kontrollierbaren Ätzstopps mit einem möglichst großen erzielbaren Aspektverhältnis der erzeugten Kavität kombiniert. Alternativ oder zusätzlich wäre es wünschenswert, eine oder mehrere Kavitäten in einem Halbleitersubstrat erzeugen zu können, die einen möglichst geringen Flächenbedarf an der Oberfläche haben, von der Kavität(en) ausgehen. Weiterhin wäre es alternativ oder zusätzlich wünschenswert, eine oder mehrere relativ tiefe Kavitäten in einem Halbleitersubstrat auf möglichst kostengünstige und/oder schnelle Weise erzeugen zu können.

[0007] Diese Aufgabe(n) wird/werden gelöst durch ein Verfahren zum Herstellen eines mikroelektromechanischen Systems gemäß Anspruch 1 oder Anspruch 12.

[0008] Ausführungsbeispiele der vorliegenden Erfindung schaffen ein Verfahren zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrat. Das Verfahren umfasst: Trockenätzen des Halbleitersubstrat, Abscheiden eines Schutzmaterials, Entfernen des Schutzmaterials und elektrochemisches Ätzen des Halbleitersubstrat. Das Trockenätzen des Halbleiter Substrat erfolgt von einer Oberfläche des Halbleiter Substrats aus an zumindest einem beabsichtigten Kavitätsort, um zumindest eine vorläufige Kavität zu erhalten. Das Schutzmaterial wird hinsichtlich eines nachfolgenden Nassätzprozesses an der Oberfläche des Halbleitersubstrat und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität abgeschieden. Beim Entfernen des Schutzmaterials wird dieses zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität entfernt, um das Halbleitersubstrat freizulegen. Das elektrochemische Ätzen des Halbleitersubstrats erfolgt dann an dem freigelegten Abschnitt des Bodens der zumindest einen vorläufigen Kavität.

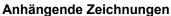

[0009] Weitere Ausführungsbeispiele der vorliegenden Erfindung schaffen ein Verfahren zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats. Das Verfahren umfasst das Durchführen eines Boschprozesses an einer Substratsoberfläche des Halbleitersubstrats, um zumindest eine vorläufige Kavität zu bilden. Das Verfahren umfasst weiterhin das Durchführen einer Plasma-chemischen Gasphasenabscheidung eines Siliziumoxids an der Substratoberfläche und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität. Ferner umfasst das Verfahren ein anisotropes Ätzen des Siliziumoxids zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität. Das Verfahren umfasst auch ein elektrochemisches, anisotrope Ätzen des Halbleitersubstrats unter Verwendung eines elektrochemisch-gesteuerten pn-Ätzstopps, wobei das elektrochemische, anisotrope Ätzen zumindest an dem Abschnitt des Bodens der zumindest einen vorläufigen Kavität erfolgt und die zumindest eine vorläufige Kavität auf diese Weise erweitert.

[0010] Weitere Ausführungsbeispiele der vorliegende Erfindung schaffen ein Verfahren zum Herstellen eines mikromechanischen Sensorsystems. Das Verfahren umfasst das Bereitstellen eines dotierten Halbleitersubstrats. Es folgt ein Umdotieren zumindest eines umdotierten Bereichs innerhalb des dotierten Halbleitersubstrats, wobei sich der zumindest eine umdotierte Bereich in einer bestimmten Tiefe von einer Substratoberfläche des Halbleitersubstrats befindet. Das Verfahren umfasst auch ein Durchführen eines Strukturierungsprozesses zur Herstellung von

mikroelektromechanischen Strukturen in dem Halbleitersubstrat und an der Substratoberfläche. Zumindest ein Teil der vorgesehenen mikroelektromechanischen Strukturen erstreckt sich in den umdotierten Bereich. Dann wird das Verfahrens zum Erzeugen zumindest einer Kavität innerhalb des Halbleitersubstrats durchgeführt, welches bereits oben erwähnt wurde. Die erzeugte Kavität grenzt nach Fertigstellung an den umdotierten Bereich und an den Teil der mikroelektromechanischen Strukturen an, der sich in den umdotierten Bereich erstreckt.

[0011] Gemäß weiteren Ausführungsbeispielen der vorliegenden Erfindung umfasst ein mikroelektromechanisches System ein Halbleitersubstrat mit einer Oberfläche und eine in dem Halbleitersubstrat gebildete Kavität. Eine Seitenwand der Kavität umfasst einen ersten Abschnitt und einen weiter von der Oberfläche des Substrats entfernten zweiten Abschnitt. Der erste Abschnitt erstreckt sich unter einem ersten Winkel zu der Oberfläche, der zwischen 70° und 110° beträgt. Der zweite Abschnitt erstreckt sich unter einem zweiten Winkel zu der Oberfläche, der zwischen 40° und 65° beträgt.

**[0012]** Ausführungsbeispiele basieren darauf, dass ein zunächst ausgeführter, anisotroper Ätzprozess dazu beiträgt, ein möglichst hohes Aspektverhältnis bzw. einen möglichst geringen Flächenbedarf der zu erzeugenden Kavität(en) zu erzielen. Dieser anisotrope Ätzprozess wird dann von einem elektrochemischen Ätzverfahren abgelöst, so dass eine relativ exakte Steuerung der Tiefe der zu erzeugenden Kavität (en) gegeben ist.

[0013] Durch die zuerst angewendete Trockenätzung erhält man bis zu einer gewissen Ätztiefe im Wesentlichen senkrechte Ätzflanken bzw. Seitenwände, die in Kombination mit dem nachfolgenden Prozessschritten eine Verringerung der für die Sensoren benötigten Chipfläche ermöglichen. Somit wird ein Herstellungsprozess der Halbleiterbauteile (z. B. Siliziumbauteile) mit geringerer Gesamtfläche ermöglicht.

[0014] Das Verfahren zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats kann weiterhin das Abscheiden einer Oxidmaske für das Trockenätzen des Halbleitersubstrats umfassen. Die Oxidmaske wird typischerweise vor dem Trockenätzen abgeschieden und strukturiert. Die Oxidmaske wird an dem zumindest einen beabsichtigten Kavitätsort lokal entfernt, z. B. durch einen Lithographieprozess.

[0015] Das Trockenätzen des Halbleitersubstrats kann zumindest einen der folgenden Prozesse umfassen: reaktives Ionenätzen (RIE), tiefes reaktives Ionenätzen (DRIE) und einen Boschprozess. Diese Ätzverfahren sind in der Regel hochgradig an-

isotrop, so dass die durch diese Prozesse erzeugte(n), vorläufige(n) Kavität(en) steile Seitenwände bzw. -Flanken erhält. Andere anisotrope Ätzverfahren oder allgemein Strukturierungsverfahren sind ebenfalls denkbar.

[0016] Das Schutzmaterial kann ein Oxid sein, insbesondere ein Siliziumoxid und/oder ein Spacer-Oxid. In der Regel wird sich die Wahl des Schutzmaterials danach richten, wie sich das Schutzmaterial während des nachfolgenden elektrochemischen Ätzvorgangs verhält, insbesondere ob es von dem elektrochemischen Ätzvorgang relativ wenig angegriffen wird, wohingegen das Substratmaterial relativ schnell geätzt wird. Anders ausgedrückt kann das Schutzmaterial so gewählt werden, dass eine möglichst hohe Selektivität des elektrochemischen Ätzens zwischen dem Halbleitersubstratmaterial und dem Schutzmaterial ausgenutzt bzw. erzielt wird.

**[0017]** Das Abscheiden des Schutzmaterials kann eine Plasma-Abscheidung, eine thermische Oxid-Abscheidung oder eine Kombination dieser umfassen.

[0018] Das Entfernen des Schutzmaterials kann ein Plasma-Ätzen umfassen. Das Plasma-Ätzen des Schutzmaterials sollte typischerweise anisotrop sein.

[0019] Das Verfahren zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats kann vor dem Entfernen des Schutzmaterials weiterhin ein Abscheiden einer Maske und ein Strukturieren der abgeschiedenen Maske umfassen. Auf diese Weise kann erreicht werden, dass das Schutzmaterial nur an bestimmten Stellen entfernt wird, wie an dem bereits erwähnten, zumindest einem Abschnitt des Bodens der zumindest einen vorläufigen Kavität. Es kann in Ausführungsbeispielen auch vorgesehen sein, dass das Schutzmaterial im Wesentlichen am gesamten Boden der Kavität entfernt wird. Da typischerweise die Tiefe der vorläufigen Kavität vergrößert werden soll, wird durch das Entfernen der Schutzschicht am Boden der vorläufigen Kavität (bzw. an zumindest einem Abschnitt davon) erreicht, dass der auf diese Weise freigelegte Boden (abschnitt) als Angriffsfläche für den nachfolgenden elektrochemischen Ätzvorgang zur Verfügung steht. Andere, nicht freigelegte Oberflächen des Halbleitersubstrats werden dagegen durch das Schutzmaterial geschützt und dementsprechend nicht von dem elektrochemischen Ätzvorgang betroffen sein.

[0020] Für das elektrochemische Ätzen kann ein basisches Ätzmedium verwendet werden.

**[0021]** Das elektrochemische Ätzen kann eine Ätzstopptechnik bereitstellen, z. B. durch Anlegen einer elektrischen Spannung zwischen dem Halbleitersubstrat und einer im Ätzmedium vorliegenden Elektrode.

[0022] Das Verfahren zum Erzeugen zumindest einer Kavität kann weiterhin die Durchführung eines Lithographieprozesses und einer anschließenden Implantation umfassen, um einen pn-Übergang bei einer Tiefe innerhalb des Halbleitersubstrats zu bilden, wobei die Tiefe des pn-Übergangs eine Funktion einer gewünschten Tiefe des Bodens der zumindest einen Kavität ist.

[0023] Das elektrochemische Ätzen kann einen ersten zeitlichen Abschnitt und einen zweiten zeitlichen Abschnitt umfassen. Während des ersten zeitlichen Abschnitts kann eine an das Halbleitersubstrat angelegte elektrische Spannung gesteigert werden. Während des zweiten zeitlichen Abschnitts kann die erreichte Spannung beispielsweise konstant gehalten oder wieder gesenkt werden. Das Bezugspotenzial der an das Halbleitersubstrat angelegten elektrischen Spannung wird in der Regel auf eine Elektrode bezogen sein, die sich im Ätzmedium befindet oder in Kontakt mit dem Ätzmedium. Die Spannungssteigerung kann sich auf einen Betrag der elektrischen Spannung beziehen. Typischerweise wird die elektrische Spannung an der Seite des pn-Übergangs an das Substrat angelegt, die entgegengesetzt zu der Oberfläche ist, von der aus die Kavitäten erzeugt werden. Auf diese Weise fällt zumindest ein Teil der angelegten elektrischen Spannung über dem pn-Übergang

**[0024]** Das Ätzmedium, das für elektrochemische Ätzen verwendet wird, kann z. B. Tetramethylammoniumhydroxid (TMAH), eine wässrige Lösung von Ethylendiamin und Brenzcatechin (EDP), Hydrazin, Kaliumhydroxid (KOH) oder eine Kombination dieser umfassen.

[0025] Gemäß Ausführungsbeispielen für das mikroelektromechanische System kann dieses weiterhin einen pn-Übergang innerhalb des Halbleitersubstrats umfassen. Dabei kann der pn-Übergang auf einer der Kavität entgegengesetzten Seite eines Bodens der Kavität angeordnet bzw. befindlich sein. Es ist jedoch auch möglich, dass der pn-Übergang im Wesentlichen auf einer Höhe mit dem Boden der Kavität ist, d. h. pn-Übergang und Boden der Kavität befinden sich im Wesentlichen in derselben Tiefe bzw. im selben Tiefenbereich, gemessen von einer der Substratoberflächen.

[0026] Der erste Abschnitt der Seitenwand der Kavität ist relativ oberflächennah bezüglich der Oberfläche des Halbleitersubstrats, von der die Kavität ausgeht und/oder in das Halbleitersubstrat hineinreicht. Der zweite Abschnitt kann dagegen tiefer innerhalb des Halbleitersubstrats sein.

[0027] In dem ersten Abschnitt kann die Seitenwand der Kavität eine Struktur mit mehreren übereinanderliegenden Hohlkehlen bzw. Einbuchtungen aufwei-

### DE 10 2012 206 531 B4 2015.09.10

sen. Eine derartige Struktur deutet typischerweise darauf hin, dass die Kavität bzw. ein erster Abschnitt der Kavität mittels eines Boschprozesses erzeugt wurde. Im Vergleich zu einem Querschnitt des ersten Kavitätsabschnitts kann ein zweiter Kavitätsabschnitt, der im Wesentlichen dem zweiten Abschnitt der Seitenwand zugeordnet ist, einen größeren Querschnitt aufweisen.

**[0028]** In Ausführungsbeispielen kann das mikroelektromechanische System einen Sensor, einen Aktor, einen Drucksensor, einen Beschleunigungssensor oder einen elektromechanischen Wandler umfassen.

[0029] Ein Substratabschnitt zwischen einem Boden der Kavität und der Oberfläche oder einer anderen Oberflächen des Halbleitersubstrats kann eine Membran, einen Balken, einen Kragarm oder ein mechanisches Masseelement des mikroelektromechanischen Systems bilden. Andere Strukturen, die innerhalb von mikroelektromechanischen Systemen zum Erzielen einer bestimmten Funktion eingesetzt werden, sind ebenfalls denkbar.

**[0030]** In Ausführungsbeispielen des mikroelektromechanischen Systems kann das Substrat hauptsächlich aus Silizium bestehen, abgesehen von gewollten und/oder ungewollten Verunreinigungen (Dotierungen) sowie ggf. Materialumwandlungen (z. B. lokal begrenzte Oxidierung oder Oxidschichtbildung).

**[0031]** In Ausführungsbeispielen kann die Seitenwand zumindest eine Stufe oder Kante aufweisen, die z. B. einen Übergang zwischen dem ersten Seitenwandabschnitt und dem zweiten Seitenwandabschnitt bildet. Auch innerhalb des zweiten Seitenwandabschnitts selbst kann die Seitenwand eine Stufe bzw. Kante aufweisen.

**[0032]** Das Aspektverhältnis der Kavität kann in Ausführungsbeispielen 1,5 oder mehr betragen.

**[0033]** Ausführungsbeispiele der vorliegenden Erfindung werden im Folgenden anhand der beiliegenden Figuren näher beschrieben. Es zeigen:

**[0034] Fig.** 1 zeigt ein schematisches Flussdiagramm eines Verfahrens zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats gemäß Ausführungsbeispielen.

**[0035] Fig.** 2 zeigt ein schematisches Flussdiagramm eines Verfahrens zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats gemäß weiteren Ausführungsbeispielen.

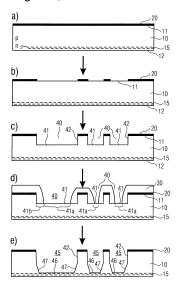

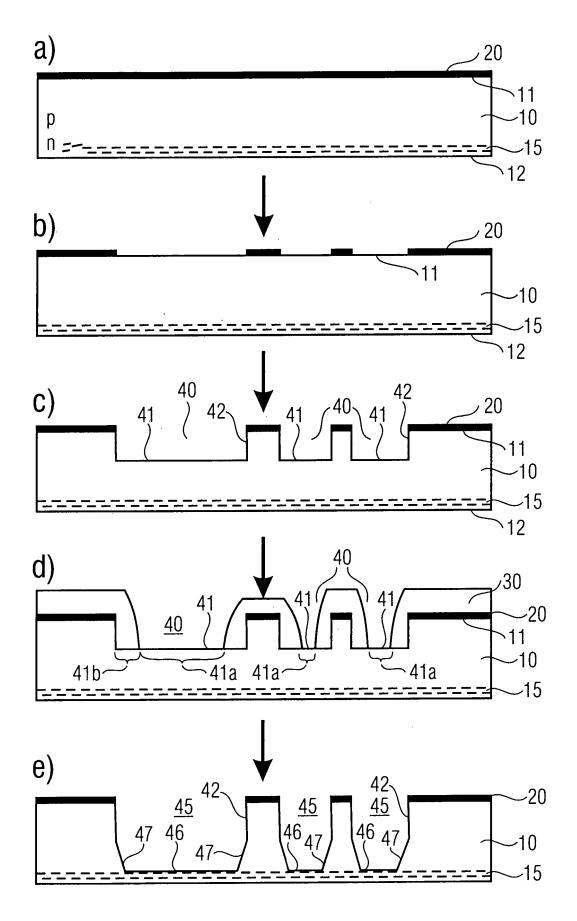

[0036] Fig. 3 veranschaulicht in schematischen Querschnittsansichten durch ein Halbleitersubstrat

das Verfahren zum Erzeugen zumindest einer Kavität gemäß Ausführungsbeispielen.

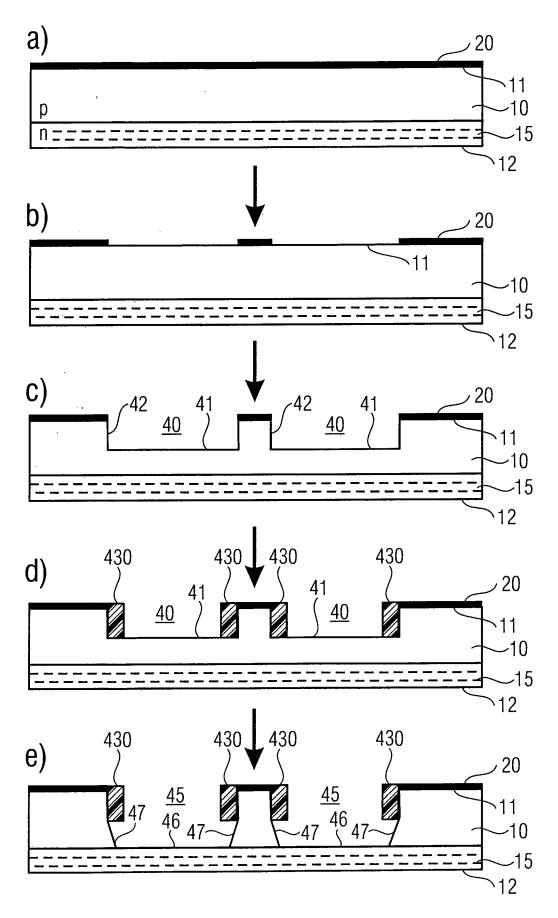

**[0037] Fig.** 4 veranschaulicht in schematischen Substratquerschnitten das Verfahren zum Erzeugen zumindest einer Kavität gemäß weiteren Ausführungsbeispielen.

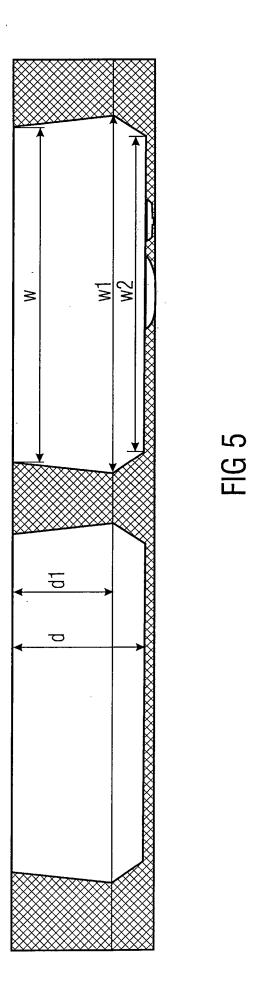

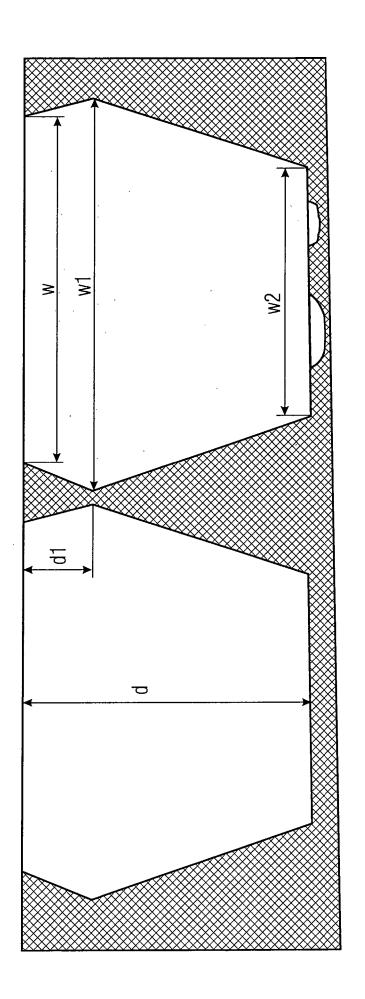

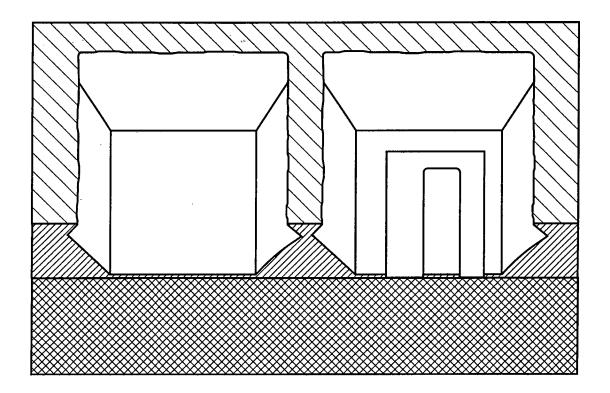

**[0038] Fig.** 5 zeigt eine schematische Querschnittsansicht von zwei Kavitäten, die mit einem Verfahren gemäß Ausführungsbeispielen erzeugt wurden.

[0039] Fig. 6 zeigt eine schematische Querschnittsansicht von zwei Kavitäten, die mit dem Verfahren gemäß weiteren Ausführungsbeispielen erzeugt wurden

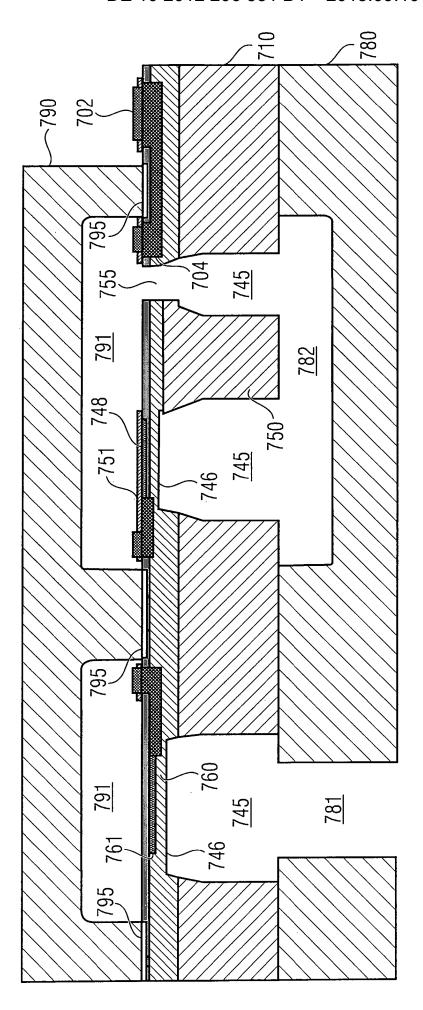

**[0040] Fig.** 7 zeigt eine schematische Querschnittsansicht eines mikroelektromechanischen Systems, einem Abdeck-Wafer und einen Zugangs-Wafer.

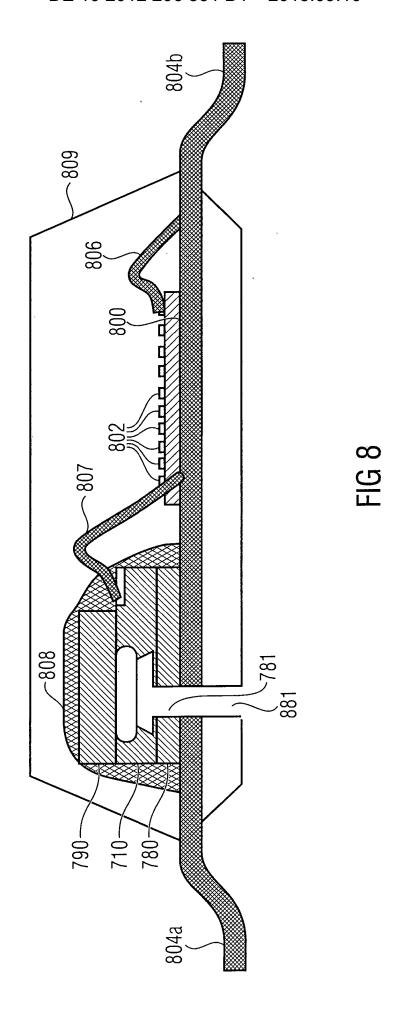

[0041] Fig. 8 zeigt eine schematische Querschnittsansicht einer Sensorvorrichtungsgeometrie.

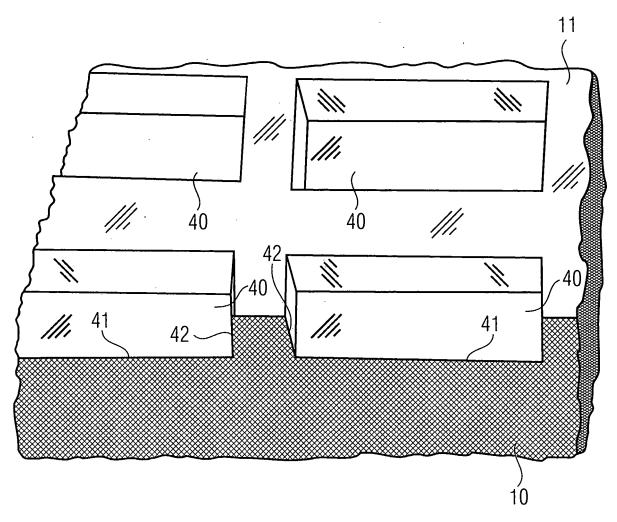

**[0042] Fig.** 9 zeigt eine schematische, perspektivische Querschnittsansicht von vier vorläufigen Kavitäten, die im Rahmen des Verfahrens zum Erzeugen zumindest einer Kavität gemäß Ausführungsbeispielen gebildet werden.

**[0043] Fig.** 10 zeigt eine schematische, perspektivische Querschnittsansicht von zwei Kavitäten, die mit dem Verfahren zum Erzeugen zumindest einer Kavität gemäß Ausführungsbeispielen erzeugt wurden.

**[0044] Fig.** 11 zeigt eine schematische Darstellung verschiedener Ätzmuster, die mit verschiedenen Ätzverfahren bzw. Kombinationen von Ätzverfahren erzielt werden können.

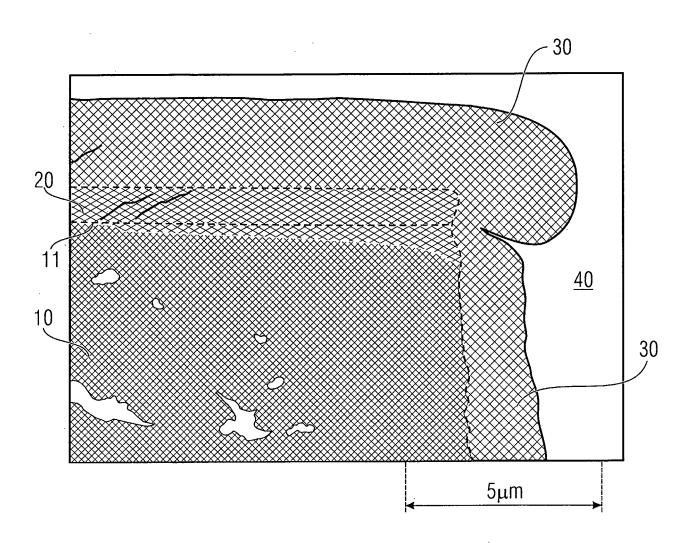

**[0045] Fig.** 12 zeigt als Elektronenmikroskopaufnahme eine Detailschnittansicht einer oberen Kante einer Kavitätsseitenwand.

[0046] Bevor im Folgenden Ausführungsbeispiele anhand der beiliegenden Figuren erläutert werden, wird darauf hingewiesen, dass gleiche Elemente oder Elemente gleicher Funktion mit denselben oder ähnlichen Bezugszeichen versehen sind und dass auf eine wiederholte Beschreibung dieser Elemente verzichtet wird. Die Beschreibung von Elementen mit gleichen oder ähnlichen Bezugszeichen sind daher untereinander austauschbar. Ein Merkmal oder mehrere Merkmale eines Ausführungsbeispiels können mit einem Merkmal oder mehreren Merkmalen eines anderen Ausführungsbeispiels kombiniert werden oder durch diese ersetzt werden.

[0047] In der MEMS-Technologie werden die meisten der mikroelektromechanischen Strukturen meist

an der Substratoberfläch gebildet. Insbesondere kann dabei das Substratmaterial selber strukturiert werden, sowie auch weitere Materialien an der Substratoberfläche abgeschieden und strukturiert werden, so dass die endgültige mikroelektromechanische Struktur typischerweise einen Schichtaufbau aufweist. Bei manchen mikroelektromechanischen Systemen kann es jedoch darüber hinaus erforderlich oder zweckmäßig sein, auch von der entgegengesetzten Substratoberfläche einen Zugang zu den mikroelektromechanischen Strukturen zu schaffen. Z. B. kann ein Drucksensor einen Zuführungskanal benötigen, über den der zu messende Druck der als mikroelektromechanisches Bauteil strukturierten Membran zugeführt wird. Bei einem Beschleunigungssensor kann es erforderlich oder zweckmäßig sein, dass das mechanische Masseelement, welches zur Erfassung der Beschleunigung dient, genügend weit ausgelenkt werden kann, wofür ein genügend großer Freiraum um das Masseelement vorgesehen sein muss, um diese Auslenkung nicht zu behindern. Bei diesen und weiteren Beispielen können Kavitäten in dem Halbleitersubstrat vorgesehen werden, die von einer Rückseite des Substrats (d. h. entgegengesetzt zu der Oberfläche, an der die mikroelektromechanischen Strukturen ausgebildet sind) ausgeformt werden.

[0048] Ausführungsbeispiele dienen zur Herstellung von Kavitäten auf Siliziumwafern (oder allgemeiner: Wafern aus Halbleitermaterial), welche für die Erzeugung von MEMS-Bauteilen (z. B. Druck- und Beschleunigungssensoren) jeglicher Art (Sensoren und Aktuatoren) Anwendung finden. Zur Erzeugung dieser Kavitäten im Bulk-Material von Reinstsilizium von MEMS-Bauteilen wird hier ein sogenannter "Kombinationsprozess" angewendet, welcher in der Sequenz folgende Prozessschritte typischerweise auf unterschiedlichen Prozessanlagen umfasst:

- 1. Trockenätzen (DRIE-"Deep reactive ion etching"/Boschprozess) unter Anwendung einer Oxid-Hartmaske

- 2. Abscheiden eines Spaceroxids und Ätzen einer Oxid-Spacer-Struktur als Seitenwandschutz für die nachfolgende nasschemische Ätzung

- 3. elektrochemische anisotrope Ätzung in TMAH Durch die zuerst (bei Schritt 1) angewendete Bosch-Ätzung erhält man bis zu einer gewissen Ätztiefe senkrechte Ätzflanken, die in Kombination mit den zwei nachfolgenden Prozessschritten (2. und 3.) eine Verringerung der für die Sensoren benötigen Chipfläche ermöglicht. Somit wird ein Herstellungsprozess der Silizium-Bauteile (allgemein Halbleiter-Bauteile) mit geringerer Gesamtfläche ermöglicht.

**[0049]** Der Kombinationsprozess gemäß Ausführungsbeispielen ermöglicht in diesem hier exemplarisch beschriebenen Beispiel eine Chipgröße von 4, 08 mm²; derzeit beträgt die MEMS-Siliziumsensorflä-

che 6,49 mm² für eine vergleichbare Struktur (37% Flächeneinsparung). Die verringerte Sensorbauteilfläche wird durch Verwendung des Bosch-Ätzprozesses ermöglicht, der senkrecht verlaufende Ätzflanken liefert. Je nach Tiefe (Ätzprozessdauer) der Bosch-Ätzung, kann die Fläche der Kavitäten und somit die der Silizium-MEMS-Sensorbauteile weiter reduziert werden. Eingeschränkt in der Ätztiefe beim Bosch-Ätzprozess ist man dadurch, dass ab einer bestimmten Ätztiefe keine pn-Ätzung nachgeschaltet erfolgen kann, da die Raumladungszone (abgekürzt RLZ) des pn-Übergangs in der Tiefe des Substrats bereits erreicht wird und kein selbstjustierter Ätzstopp erzielt wird.

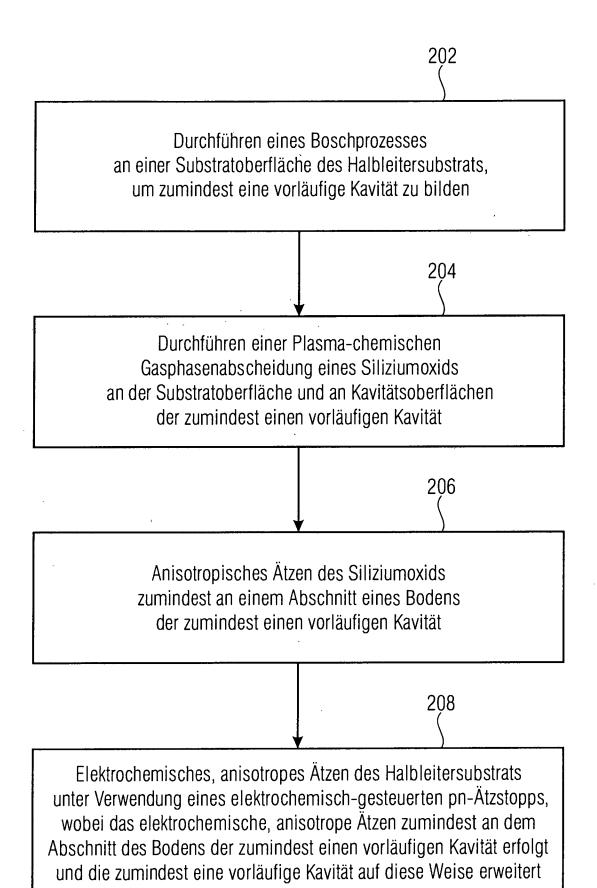

[0050] Fig. 1 zeigt ein schematisches Flussdiagramm eines Verfahrens zum Erzeugen zumindest einer Kavität innerhalb eines Halbleitersubstrats gemäß Ausführungsbeispielen. Bei einem Schritt 102 wird das Halbleitersubstrat zunächst von einer Oberfläche des Halbleitersubstrats aus an zumindest einem beabsichtigten Kavitätsort trockengeätzt, um zumindest eine vorläufige Kavität zu erhalten. Das Trockenätzen kann ein reaktives Ionenätzen (englisch: "Reactive ion etching" RIE) oder ein tiefes reaktives Ionenätzen (englisch: "Deep reactive ion etching", DRIE) umfassen.

[0051] Wie in dem Flussdiagramm von Fig. 1 bei Schritt 104 ersichtlich, wird dann ein Schutzmaterial abgeschieden. Das Schutzmaterial wird hinsichtlich eines nachfolgenden Nassätzprozesses (bei Schritt 108, siehe unten) an der Oberfläche des Halbleitersubstrats und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität abgeschieden. Das Abscheiden des Schutzmaterials kann im Wesentlichen ganzflächig und isotrop erfolgen, so dass Oberflächen des Substrats oder der zumindest einen Kavität im Wesentlichen unabhängig von ihrer Ausrichtung mit dem Schutzmaterial bedeckt werden. Als Schutzmaterial eignet sich in vielen Fällen ein Oxid des Substratmaterials. Das Schutzmaterial kann z. B. ein Spacer-Oxid sein. In diesem Fall kann der Schritt 104 auch als Spacer-Abscheidung bezeichnet werden. Konkret kann als Schutzmaterial Silan verwendet werden, wobei jedoch auch andere Schutzmaterialien möglich und keineswegs ausgeschlossen sind.

[0052] Anschließend wird das Schutzmaterial zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität entfernt, um das Halbleitersubstrat dort freizulegen, wie bei einem Schritt 106 des schematischen Flussdiagramms von Fig. 1 angedeutet. Durch das Zusammenwirken der Schritte 104 (Abscheiden des Schutzmaterials) und 106 (selektives lokales Entfernen des Schutzmaterials) ist das Halbleitersubstrat fast überall gegenüber dem nachfolgenden nasschemischen Ätzprozess bzw. dem elektrochemischen Ätzen geschützt,

bis auf an dem/den freigelegten Abschnitt(en). Dieser freigelegte Abschnitt bzw. die freigelegten Abschnitte können sich am Boden der zumindest einen vorläufigen Kavität befinden, so dass der nachfolgende nasschemische bzw. elektrochemische Ätzvorgang das Substrat an dieser/diesen Stelle(n) entfernt bzw. angreift und somit die Kavität tiefer macht, ohne die Öffnung der Kavität an der Oberfläche aufzuweiten. Dies ist bei einem Schritt 108 des schematischen Flussdiagramms von Fig. 1 dargestellt, wonach ein elektrochemisches Ätzen des Halbleitersubstrats an dem freigelegten Abschnitt des Bodens der zumindest einen vorläufigen Kavität durchgeführt wird. Je nach Wahl des elektrochemischen Ätzprozesses bzw. des nasschemischen Ätzprozesses kann es zu einer mehr oder weniger ausgeprägten Verbreiterung der Kavität innerhalb des Abschnitts kommen, der von dem elektrochemischen bzw. nasschemischen Ätzen erzeugt wird. Diese Verbreiterung der Kavität skaliert mit der zusätzlichen Tiefe, die im Rahmen des Schritts 108 durch das elektrochemische Ätzen für die Kavität erzielt wird. Im Vergleich zu einer Erzeugung der Kavität, die nur auf einem elektrochemischen Ätzen beruht, lassen sich mit dem Verfahren zum Erzeugen zumindest einer Kavität gemäß Ausführungsbeispielen Kavitäten erzeugen, die bei vergleichbarer Tiefe eine geringere laterale Ausdehnung aufweisen als andere Verfahren.

[0053] Die Wahl, bis zu welcher Tiefe der Schritt 102 des Trockenätzens durchgeführt wird und die weitere Formung der Kavität anschließend durch das elektrochemische Ätzen gemäß Schritt 108 fortgesetzt wird, kann an die Gegebenheiten und Erfordernisse des jeweiligen Prozesses bzw. der herzustellenden mikroelektromechanischen Systeme angepasst werden. Diese Wahl der Anteile des Trockenätzens und des elektrochemischen Ätzens kann z. B. Rücksicht nehmen auf die unterschiedlichen Ätzgeschwindigkeiten und daraus resultierenden Prozessdauern der zwei Ätzprozesse, deren Kosten (sowohl hinsichtlich der benötigten Anlagen wie auch der Betriebskosten) sowie eine höhere Ausbeute bzw. Anzahl der Chips je Wafer, die aufgrund einer mit dem vorgeschlagenen Kombinationsverfahren erreicht werden kann. Wenn der Vorteil der höheren Ausbeute pro Wafer die eventuell höheren Kosten zur Verarbeitung eines Wafers überwiegen, kann insbesondere angedacht werden, das Trockenätzen (Schritt 102) so lange wie möglich durchzuführen. Dies hängt insbesondere davon ab, wie genau die Ätztiefe während des Trockenätzens gesteuert und kontrolliert werden kann. Das Trockenätzen sollte in der Regel stoppen, bevor die gewünschte endgültige Tiefe der Kavität erreicht wird. da ansonsten das Risiko besteht, mikroelektromechanische Strukturen anzugreifen oder sogar zu zerstören, die in einer Verlängerung der endgültigen Kavität bzw. am Boden der Kavität liegen. Z. B. kann der Anteil des Trockenätzens zwei Drittel betragen,

bezogen auf die endgültige Tiefe der Kavität. Alternativ kann der Anteil des Trockenätzens zwischen 30% und 90% liegen und insbesondere folgende Werte haben: 30%, 50%, 75%, 80% oder 90%, jeweils bezogen auf eine endgültige Tiefe der zu erzeugenden Kavität.

[0054] Der Schritt des elektrochemischen Ätzens 108 stoppt in der Regel automatisch bei einer vorgegebenen Tiefe, was durch die Bereitstellung eines entsprechenden Ätzstopps (z. B. in Form eines pn-Übergangs mit daran angelegter elektrischer Spannung) erreicht wird.

[0055] Als mögliche Anwendung bieten Ausführungsbeispiele die Möglichkeit, die Bauteilfläche eines MEMS-Sensors (z. B. eines kombinierten Druckund Beschleunigungssensors) wesentlich zu verringern, um somit auf einem Wafer einer bestimmten Größe (z. B. auf einem 6-Zoll-Wafer oder einem 8-Zoll-Wafer) möglichst viele Sensor-Bauteile mit jeweils möglichst minimaler Fläche unterzubringen.

[0056] Bei dem hier als Beispiel genannten, kombinierten Druck- und Beschleunigungssensor kann man z. B. den Fokus auf eine Verringerung der Sensorfläche beim Beschleunigungssensor richten, der schlussendlich mit gleicher Empfindlichkeit wie dessen flächenmäßig größeres Pendant betrieben werden soll. Hierzu wird man in der Regel anstreben, dass die Inertialmasse des Sensors möglichst gleich bleibt, da nur dann eine weitgehend identische Resonanzfrequenz, mit der der Sensor betrieben wird, erzielt wird.

[0057] Man erreicht dies, indem die lithographisch strukturierte Waferrückseite (Wafermaterial beispielsweise Silizium) zunächst mittels einer Bosch-Ätzung (unter Verwendung einer Oxid-Hartmaske oder einem Ätzmedium-resistenten Negativ-Lack) abgetragen wird. Auf diese Weise erhält man im Bulk-Silizium im Wesentlichen senkrechte Ätzflanken. Unter Zuhilfenahme der SPACER-Technik (Plasma oder thermische Oxid-Abscheidung mit anschließender anisotroper Plasma-Ätzung) werden die senkrechten Seitenwände der Bosch-geätzten Kavitäten mittels einer Oxidschicht geschützt und eine darauffolgende elektrochemische, anisotrope Ätzung (in TMAH, EDP, Hydrazin, KOH oder weiterer gängiger basischer Ätzmedien) führt die Ätzfront bis zur Tiefe einer vorliegenden Raumladungszone im p-Substrat (elektrochemischer Ätzstopp vor dem in Sperrrichtung gepolten pn-Übergang-Ätzmedium vom p-Gebiet kommend, in Richtung des n-Gebiets stoppend), die die Membrandicke (Drucksensor) bzw. Cantileverdicke (Beschleunigungssensor) letztendlich bestimmt.

[0058] Ein Merkmal des Verfahrens gemäß Ausführungsformen ist der im Vergleich zu SOI ("Si-

licon-on-Insulator") Grundmaterial niedrige Silizium-Grundmaterialpreis. Eine weitere Möglichkeit, kleine Strukturgrößen bei MEMS-Sensorbauelementen mittels Silizium-Bulk-Ätzverfahren zu erzielen, ist die Verwendung von SOI-Grundmaterial. Hierbei wird jedoch kein pn-Ätzstoppverfahren und somit kein Kombinationsprozess angewendet. Meist beruht dieses Prinzip ausschließlich auf der Verwendung des Bosch-Ätzprozesses. Ein Ätzstopp erfolgt hierbei auf der Oxidschicht des SOI-Materials. MEMS-Produkte aus SOI-Grundmaterial und eine Verwendung von Bosch-Ätzverfahren weisen daher überwiegend senkrechte Ätzflanken auf.

[0059] Ausführungsbeispiele basieren somit auf dem hierin beschriebenen "Kombinationsprozess" (eine Variation des "Silizium-Micro Machining") zur Herstellung von MEMS-Siliziumsensorbauteilen sowie auch anderer MEMS-Komponenten oder elektronischer Komponenten auf Siliziumwaferbasis. Alternativ sind auch andere Halbleitermaterialien denkbar. Diese Technik ermöglicht eine Verringerung der erforderlichen Waferfläche (insbesondere Siliziumwaferfläche) und entsprechend die der Fläche von Bauteilen, insbesondere Siliziumsensorbauteilen (engl.: "shrink").

**[0060]** Ausführungsbeispiele umfassen die beschriebene Prozesssequenz zur Erzeugung von Kavitätsstrukturen z. B. im Bulk-Reinstsilizium <100>:

- a) Bosch-Ätzprozess (DRIE) unter Verwendung einer Positiv- oder Negativ-Lackmaske

- b) Plasma CVD-Abscheidung und anisotrope Ätzung eines undotierten Siliziumglases (SPACER-Technologie) zum Schutz der senkrechten Siliziumseitenwände der Bosch-geätzten Kavitäten

- c) elektrochemische, anisotrope Ätzung in einem basischen Medium mit Ätzstopptechnik (der Ätzstopp erfolgt im Tiefenprofil vor der Raumladungszone eines in Sperrrichtung gepolten pn-Übergangs, der beispielsweise mittels Lithographie und Implantationstechnik hergestellt wird)

[0061] Fig. 2 zeigt ein schematisches Flussdiagramm eines Verfahrens zum Erzeugen zumindest einer Kavität gemäß weiteren möglichen Ausführungsbeispielen. Das Verfahren beginnt, bei einem Schritt 202, mit der Durchführung eines Boschprozesses an einer Substratoberfläche des Halbleitersubstrats, um zumindest eine vorläufige Kavität zu bilden.

**[0062]** Es folgt die Durchführung einer Plasma-chemischen Gasphasenabscheidung (englisch: "Plasma chemical vapor deposition (CVD)") eines Siliziumoxids (oder auch eines anderen Oxids) an der Substratoberfläche und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität. Das Siliziumoxid wird in der Regel auch an Flächen abgeschieden, die nicht parallel zu der Substratoberfläche verlaufen,

wie es z. B. für die Seitenwände der vorläufigen Kavität der Fall ist. Das Siliziumoxid dient insbesondere als Schutzmaterial für einen nachfolgenden Ätzschritt (siehe Schritt **208** und die nachfolgende dazugehörige Beschreibung).

[0063] Wie bei einem Schritt 206 des schematischen Flussdiagramms von Fig. 2 angedeutet, wird das Siliziumoxid anschließend anisotropisch geätzt, und zwar zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität. Auf diese Weise wird das Siliziumoxid in diesem Bereich entfernt und der entsprechende Abschnitt des Bodens wird freigelegt, d. h. das Substratmaterial ist an dieser Stelle nicht mehr von Siliziumoxid bedeckt. Um ein örtlich selektives Ätzen des Siliziumoxids an den gewünschten Orten, d. h. an dem zumindest einen Abschnitt des Bodens der vorläufigen Kavität(en), zu ermöglichen, kann dem Schritt 206 ein Photolithographieschritt oder ein anderer geeigneter Prozess zur Maskierung/Demaskierung von Oberflächenbereichen vorangeschaltet sein.

[0064] Das Verfahren zum Erzeugen zumindest einer Kavität innerhalb des Halbleitersubstrats wird nach dem anisotropischen Ätzen des Siliziumoxids mit einem elektrochemischen, anisotropen Ätzen des Halbleitersubstrats fortgesetzt, wie in Schritt 208 zu sehen. Das elektrochemische, anisotrope Ätzen erfolgt unter Verwendung eines elektrochemisch-gesteuerten pn-Ätzstopps, wobei das elektrochemische-anisotrope Ätzen zumindest an dem Abschnitt des Bodens der zumindest einen vorläufigen Kavität erfolgt, welcher zuvor (Schritt 206) freigelegt worden war. Auf diese Weise wird die vorläufige Kavität erweitert, und zwar ausgehend von dem Boden der vorläufigen Kavität mit dem Ätzprofil, das für das verwendete elektrochemische, anisotrope Ätzverfahren charakteristisch ist. Beispielsweise können die Seitenwände der Kavität in dem Abschnitt, der von dem elektrochemischen, anisotropen Ätzen erzeugt wird, einen bestimmten Winkel mit der Substratoberfläche bilden, z. B. den Kristallwinkel zwischen den Si <100> und Si <111> Ebenen von 54,7°.

**[0065] Fig.** 3 zeigt eine schematische Darstellung des vorgeschlagenen Kombinationsprozesses in fünf schematischen Querschnittsansichten, die jeweils einen Zwischenschritt des Kombinationsprozesses darstellen.

[0066] Im Teilbild a) von Fig. 3 ist ein Substrat 10 im Querschnitt dargestellt. Das Substrat ist p-dotiert, was beispielsweise durch die Implantation von Bor-Atomen in das Kristallgitter, hier Silizium, erreicht werden kann. Das Substrat wird in dem hier dargestellten Beispiel als ein Siliziumkristall angenommen, dessen <100>-Ebene die Hauptflächen des Substrats 10 bilden, nämlich eine erste Oberfläche 11 und eine zweite Oberfläche 12. Man beachte, dass

in der MEMS-Technologie die mikroelektromechanischen Strukturen häufig an der hier als zweiten Oberfläche 12 bezeichneten Oberfläche des Substrats 10 vorab geschaffen und angeordnet sind. An der zweiten Oberfläche 12 oder in der Nähe dazu ist innerhalb des Substrats 10 ein umdotierter Bereich 15 vorgesehen. In dem hier dargestellten Beispiel eines p-dotierten Substrats 10 ist der umdotierte Bereich 15 somit n-dotiert. Die Umdotierung kann dadurch erzielt werden, dass in dem umdotierten Bereich 15 die Konzentration eines zweiten Dotierstoffs höher ist als die Konzentration des ersten Dotierstoffs (hier z. B. Bor), welche im gesamten Substrat 10 im Wesentlichen homogen ist. Auf diese Weise wird zwischen dem umdotierten Bereich 15 und dem Rest des Substrats 10 ein pn-Übergang gebildet. Der umdotierte Bereich 15 stellt in dem Beispiel von Fig. 3 dabei den n-Bereich dar und der Rest des Substrats 10 stellt den p-Bereich dar.

[0067] Im Teilbild a) von Fig. 3 ist auch eine Oxidschicht 20 dargestellt, die an der ersten Oberfläche 11 des Substrats 10 angeordnet ist. Die Oxidschicht 20 dient, wie nachfolgend dargestellt, als Hartmaske für den später durchzuführenden Trockenätzprozess bzw. Boschprozess.

[0068] Im Teilbild b) von Fig. 3 wurde die Oxidschicht 20 mittlerweile strukturiert mittels eines Lithographieverfahrens. Auf diese Weise ist die erste Oberfläche 11 des Substrats 10 an den beabsichtigten Kavitätsorten exponiert und außerhalb der beabsichtigten Kavitätsorte noch von der Oxidhartmaske 20 bedeckt.

[0069] Im Bild c) des Prozessablaufs von Fig. 3 ist das Substrat 10 im Querschnitt zu sehen, nachdem ein Boschprozess mit positivem Lack oder negativem Lack durchgeführt wurde. Der Boschprozess erzeugt vorläufige Kavitäten 40, die beispielsweise 300 µm tief sein können, gemessen von der ersten Oberfläche 11 des Substrats 10. Der Boschprozess oder ein anderer geeigneter Trockenätzprozess stellt einen ersten Teilprozess des Verfahrens zum Erzeugen zumindest einer Kavität gemäß Ausführungsbeispielen dar. Die vorläufigen Kavitäten 40 weisen jeweils einen Boden 41 auf. Die Kavitäten 40 weisen ferner Seitenwände 42 auf, die hier im Wesentlichen senkrecht zu der ersten Oberfläche 11 des Substrats 10 sind.

[0070] Im Teilbild d) von Fig. 3 ist der Zustand zu sehen, nachdem eine Oxid SPACER-Abscheidung/anisotrope Ätzung durchgeführt wurde. Zunächst wurde ein Schutzmaterial 30 (hier: Oxid SPACER-Material) an der ersten Oberfläche 11 des Substrats 10 und an den Oberflächen der vorläufigen Kavitäten 40 abgeschieden. Mittels einer lokalen anisotropen Ätzung des Schutzmaterials 30 werden insbesondere Abschnitte 41a der Böden 41 der vorläufigen Kavitä-

ten **40** wieder freigelegt. Ferner weisen in dem hier dargestellten Beispiel die Böden **41** auch nicht freigelegte Abschnitte **41b** auf. Die Dicke des abgeschiedenen Schutzmaterials kann zwischen 0,5 µm und 10 µm betragen, beispielsweise 2,5 µm. Die anisotrope Ätzung entfernt das Schutzmaterial **30** in den freizulegenden Abschnitten **41a** im Wesentlichen vollständig, so dass der Boden **41** der vorläufigen Kavitäten **40** (und somit das Substratmaterial) freigelegt wird (zumindest abschnittsweise). Die Schutzmaterialabscheidung und dessen (anisotrope) Ätzung stellt einen weiteren Schritt bzw. Prozessabschnitt des Verfahrens zum Erzeugen einer Kavität innerhalb des Halbleitersubstrats **10** dar.

[0071] Im Teilbild e) von Fig. 3 ist der Zustand als Querschnittsansicht dargestellt, nachdem eine pn-Atzung (anisotrop und elektrochemisch) durchgeführt wurde, welche einen weiteren Schritt des vorgeschlagenen Verfahrens zum Erzeugen einer Kavität darstellt. Eine anschließende Entfernung der Oxidschichten wurde zwischen den Zuständen der Teilbilder d) und e) ebenfalls durchgeführt. Die Seitenwände der nun geformten Kavitäten 45 weisen einen ersten Abschnitt 42 auf, der bereits im Rahmen des Trockenätzprozesses zwischen den Teilbildern b) und c) erzeugt wurde. Diese Abschnitte 42 werden fortgesetzt durch zweite Abschnitte 47, die auf die pn-Ätzung zurückgehen. Dementsprechend verlaufen die zweiten Abschnitte 47 der Seitenwände der Kavitäten 45 nicht notwendigerweise im Wesentlichen senkrecht zu der Substratoberfläche 11, sondern in einem Winkel dazu, beispielsweise in einem Winkel der zwischen 40° und 65° liegt, z. B. insbesondere 54,7°. Der Winkel der ersten Abschnitte 42 der Seitenwände der Kavitäten 45 bildet typischerweise einen Winkel mit der ersten Oberfläche 11, der zwischen 70° und 110° liegt, insbesondere zwischen 85° und 95°.

**[0072]** Die Kavitäten **45** weisen einen Boden **46** auf, der an den umdotierten Bereichen **15** angrenzt. Dies kommt daher, dass der umdotierte Bereich **15** für die pn-Ätzung einen Ätzstopp darstellt.

[0073] Eine mögliche und hier als Beispiel gewählte Ausführung der Erfindung erfolgt an einem Druckund einem Beschleunigungssensor auf gemeinsamer Sensorbauteilfläche. Hier werden die Wafer-rückseitigen Kavitäten in das <100>-Siliziumgrundmaterial mittels des beschriebenen Kombinationsprozesses hineingeätzt. Die Gesamttiefe kann hierbei variieren, übliche Ätztiefen richten sich nach erforderlicher Membrandicke bzw. des Cantilevers des Beschleunigungssensors und liegen hier bei ca. 375 µm bzw. 400 µm. Die Ätztiefe ist auch abhängig von der ursprünglichen Waferdicke.

[0074] Darüber hinaus ist angedacht, zwei antiparallel zueinander stehende Feder-Massesysteme in einer Kavität einzufügen, um ein sogenanntes Zweiachsen-Beschleunigungsmesssystem bereitzustellen. Aufgrund der Anwendung des Kombinationsprozesses gemäß Ausführungsbeispielen lassen sich diese beiden Strukturelemente platzsparend in einer Kavität integrieren und mit diesem Prozess auch strukturieren.

**[0075]** Die Massen der Beschleunigungssensoren sind flächenmäßig klein, da der Kombinationsprozess eine Massendicke ermöglicht, die der des Siliziumwafers entspricht.

[0076] Durch Variieren einer Implantationstiefe des zweiten Dotierstoffs, mit dem der umdotierte Bereich 15 in dem Substrat 10 geformt wird, können unterschiedliche Ätzstopptiefen für die pn-Ätzung bereitgestellt werden. Auf diese Weise können z. B. mehrere Kavitäten unterschiedlicher Tiefe während derselben pn-Ätzung hergestellt werden. Weiterhin ist es möglich, die Böden 46 der erzeugten Kavitäten 45 (Fig. 3e) auf diese Weise zu strukturieren, indem z. B. erhabene Strukturen, Vertiefungen oder Aussparungen vorgesehen werden.

[0077] Fig. 4 zeigt in schematischen Querschnittsansichten einen Prozessablauf gemäß Ausführungsbeispielen. Wie in Fig. 3 wird wieder von einem Substrat 10 ausgegangen, das eine p-Dotierung mittels Implantation von Bor-Atomen aufweist. Z. B. kann dadurch ein spezifischer Widerstand von ungefähr 3  $\Omega$ cm erreicht werden. Die Schicht 20 stellt eine Oxidhartmaske dar. Das Substrat weist in der Nähe bzw. direkt an der zweiten Substratoberfläche 12 einen umdotierten Bereich 15 auf, der somit n-dotiert ist.

[0078] Im Teilbild b) von Fig. 4 wurde eine Lithographie der Oxidhartmaske 20 durchgeführt, so dass die Oxidhartmaske 20 an zwei beabsichtigten Kavitätsorten entfernt wurde.

[0079] Zwischen den in den Teilbildern b) und c) von Fig. 4 dargestellten Zuständen wurde ein Boschprozess durchgeführt, der zur Ausbildung von vorläufigen Kavitäten 40 mit im Wesentlichen senkrechten Seitenwänden 42 und jeweils einem Boden 41 führt. Der Boschprozess kann beispielsweise über 200 µm Ätztiefe im sogenannten AVIZA-Verfahren ausgeführt werden.

[0080] Teilbild d) von Fig. 4 zeigt das Substrat 10 und die zwischenzeitlich geschaffenen Strukturen im Querschnitt, wonach ein Schutzmaterial 430 an den Seitenwänden der vorläufigen Kavitäten 40 angeordnet wurde. Dies kann beispielsweise durch eine Polymer-Abscheidung erfolgen. Die Dicke des abgeschiedenen Polymers bzw. Schutzmaterials 430 kann zwischen 150 nm und 500 nm betragen und ebenfalls im AVIZA-Reaktor ablaufen. Man beachte, dass der zuvor durchgeführte Boschprozess typischerweise oh-

nehin eine Polymer-Abscheidung an den Seitenwänden der nach und nach entstehenden vorläufigen Kavität **40** vorsieht.

[0081] Das Verfahren wird dann mit einer pn-Ätzung (elektrochemischer Ätzung) fortgesetzt, wodurch die vorläufige Kavität 40 zu einer finalen Kavität 45 insbesondere in die Tiefe erweitert wird. Dabei setzen sich die Seitenwände 42 der vorläufigen Kavität 40 mittels schräg verlaufender Seitenwandabschnitte 47 bis zum umdotierten Bereich 15 fort. Bei Erreichen des umdotierten Bereichs 15 stoppt die pn-Ätzung und die finale Kavität 45 weist einen Kavitätsboden 46 an dieser Stelle auf.

[0082] Fig. 5 zeigt eine schematische Querschnittsansicht von zwei Kavitäten, die mittels eines Verfahrens gemäß Ausführungsbeispielen erzeugt wurden. Die Kavitäten weisen eine Gesamttiefe d von einer Substratoberfläche auf, von der aus sich die zwei Kavitäten in das Substrat hinein erstrecken. An der Substratoberfläche haben die Kavitäten eine laterale Ausdehnung w. Bis zu einer Tiefe d1 verlaufen die Seitenwände der Kavitäten unter einem Winkel zur Substratoberfläche, der ungefähr 95° beträgt. Somit weiten sich die Kavitäten mit zunehmender Tiefe zunächst geringfügig auf. Zu einer derartigen Aufweitung kommt es, wenn der Boschprozess nicht optimal eingestellt ist. Polymerabscheide- und Siliziumätzraten müssen exakt aufeinander eingestellt sein, um senkrechte Flanken zu erhalten. Es sei allerdings angemerkt, dass nur wenige Anwendungen (nahezu) exakt senkrechte Flanken erfordern. Für viele andere Anwendungen ist es ausreichend, wenn annähernd senkrechte Flanken (z. B. mit einem Winkel zwischen 80° und 100°) erzeugt werden können. Bei der Tiefe d1 erreicht die laterale Ausdehnung ein Maximum w1. Der Abschnitt, welcher der Tiefe d1 entspricht, geht typischerweise auf die Durchführung eines Trockenätzverfahrens bzw. eines Bosch-Ätzprozesses zurück. Von der Tiefe d1 an nimmt die laterale Ausdehnung der Kavitäten mit zunehmender Tiefe ab und erreicht schließlich am Boden der Kavitäten einen Wert w2. Im Tiefenbereich d1 bis d bilden die Seitenwände der Kavitäten einen Winkel mit der Substratoberfläche, der zwischen 40° und 65° beträgt.

[0083] Man beachte, dass der Boden der rechten Kavität eine Struktur aufweist, die für eine mikroelektromechanische Struktur verwendet werden kann.

[0084] Fig. 6 zeigt im Vergleich zu Fig. 5 einen schematischen Querschnitt durch zwei Kavitäten, die mittels eines Kombinationsprozesses jedoch ohne Abscheiden eines Schutzmaterials zwischen der Trockenätzung und der elektrochemischen Ätzung erzeugt wurden. Weiterhin ist das Verhältnis der Tiefen, die mit dem Trockenätzprozess und dem elektrochemischen Ätzprozess erzeugt wurden, anders als bei dem in Fig. 5 dargestellten Beispiel. Insbeson-

dere überwiegt bei dem in Fig. 6 dargestellten Beispiel die elektrochemische Ätzung, in Fig. 5 dagegen die Trockenätzung. Da die Seitenwände der vorläufigen Kavität während der elektrochemischen Ätzung nicht durch ein Schutzmaterial geschützt waren, werden auch diese von der elektrochemischen Ätzung angegriffen. Bei der Tiefe d1 haben die Kavitäten ihre maximale laterale Ausdehnung w1. An dieser Stelle ist eine verbleibende Wandstärke zwischen den zwei Kavitäten bereits relativ gering. Daher kann bei Verwendung des Prozesses, der zur Erzeugung der in Fig. 6 dargestellten Kavitäten geführt hat, der laterale Abstand zwischen den zwei Kavitäten nicht weiter verringert werden, obwohl die im Bereich der jeweiligen Kavitätsböden angeordneten mikroelektromechanischen Strukturen eine derartige Verringerung des lateralen Abstands durchaus zulassen würden. Man beachte, dass der Boschätzprozess ungefähr bis zu einer Tiefe von 2 × d1 durchgeführt wurde. Im Vergleich zu der Konfiguration in Fig. 5 ist bei der Konfiguration gemäß Fig. 6 das Verhältnis w1/w2 größer, was dazu führt, dass eine laterale Flächenausnutzung bei der Konfiguration gemäß Fig. 6 ungünstiger als in Fig. 5 ist. Falls auf die anfängliche Trockenätzung bzw. den anfänglichen Boschprozess komplett verzichtet wird und die Kavität ausschließlich mittels der pn-Ätzung erzeugt wird, wäre die erzielbare Flächenausnutzung sogar noch ungünstiger.

[0085] Fig. 7 zeigt eine schematische Querschnittsansicht durch ein mikroelektromechanisches System, das einen geschichteten Aufbau aus drei Wafern aufweist. Ein Haupt-Wafer 710 ist Sandwich-artig zwischen einem Zugangs-Wafer 780 und einem Abdeck-Wafer 790 angeordnet. Die in Fig. 7 dargestellte Struktur bildet einen kombinierten Druck- und Beschleunigungssensor. Zu diesem Zweck weist der Haupt-Wafer 710 eine druckempfindliche Membran 760 auf, die an den Boden 746 der Kavität 745 angrenzt. Die Kavität 745 wurde mittels eines Verfahrens zum Erzeugen einer Kavität gemäß zumindest einigen Ausführungsbeispielen erzeugt. Auf einer Seite der druckempfindlichen Membran 760, die der Kavität 745 gegenüberliegt, weist der Abdeck-Wafer 790 eine Kavität 791 auf, die als Druckkammer bzw. Referenzdruckkammer für die Druckmessung dient. Zu diesem Zweck sind der Haupt-Wafer 710 und der Abdeck-Wafer 790 zumindest im Bereich der Kavität 791 im Wesentlichen gasdicht miteinander verbunden. Im Zugangs-Wafer 780 ist ein Kanal 781 ausgeführt, der zu der Kavität 745 führt und diese mit der Umgebung des Drucksensors verbindet, so dass der in der Umgebung vorherrschende Druck auf die Membran 760 wirken und diese ggf. deformieren kann. In der Membran 760 können vergrabene Widerstände 761 enthalten sein, die konfiguriert sind, die druckbedingte Deformation der Membran in eine Widerstandsänderung umzusetzen, welche elektrisch ausgewertet werden kann. Die Membran 760 kann eine Dicke von z. B. 5 μm bis 20 μm, insbesondere 10 µm aufweisen, wobei diese Werte lediglich beispielhaft und keinesfalls einschränkend anzusehen sind.

[0086] Rechts von dem Drucksensor ist der Beschleunigungssensorteil des mikroelektromechanischen Sensorsystems ausgebildet.

[0087] Der Abdeck-Wafer 790 ist mit dem Haupt-Wafer 710 mittels anodischem (Wafer-)Bonden 795 verbunden.

[0088] Der Beschleunigungssensor weist eine Masse 750 auf, die über einen Kragarm 751 mit dem Substrat des Haupt-Wafers 710 verbunden ist. Der Kragarm **751** wird auf seiner der Kavität **745** zugewandten Seite von dem Kavitätsboden 746 begrenzt. Aufgrund der Kragarmaufhängung kann die Masse 750 schwingen und somit auf eine Beschleunigung reagieren. Eine Verformung des Kragarms 751 kann mit Hilfe von Oberflächenwiderständen 748 gemessen werden. Eine weitere Kavität 745 ist rechts von der Masse 750 vorgesehen. Diese weitere Kavität 745 setzt sich durch den Haupt-Wafer 710 durch, bis sie eine der Kavitäten 791 erreicht, die in dem Abdeck-Wafer 790 ausgebildet ist. Die links und rechts von der Masse 750 befindlichen Kavitäten 745 sind auch mit einer in dem Zugangs-Wafer 780 ausgeführten Kavität 782 verbunden.

[0089] Ein elektrischer Anschluss des kombinierten Druck- und Beschleunigungssensors erfolgt über Hauptkontakte 702 und vergrabene, horizontale Durchführungen 704. Beispielhaft kann die Dicke des Haupt-Wafers 710 ca. 400  $\mu$ m betragen, die Dicke der Abdeck- und Zugangs-Wafer 790, 780 ca. 350  $\mu$ m.

[0090] In Fig. 7 ist auch erkennbar, dass die Kavitäten 745 in dem Haupt-Wafer 710 Seitenwände haben, die einen ersten Abschnitt und einen zweiten Abschnitt aufweisen. Der erste Abschnitt erstreckt sich im Wesentlichen senkrecht zu einer Oberfläche des Haupt-Wafers 710. Der zweite Abschnitt der Seitenwände verläuft dagegen in einem nicht senkrechten Winkel zur Oberfläche des Haupt-Wafers 710. Insbesondere für die Masse 750 des Beschleunigungssensor ist dies vorteilhaft, da die Masse im Vergleich zu früheren Verfahren vergleichbare laterale Abmessungen beibehalten kann, gleichzeitig jedoch die komplette Waferdicke ausnutzen kann. Dadurch erhöht sich die Masse des Elements 750, oder bei im Wesentlichen gleichbleibender Masse können geringere laterale Abmessungen gewählt werden.

[0091] Fig. 8 zeigt beispielhaft eine Sensorvorrichtungsgeometrie, in die die Anordnung von Fig. 7 integriert ist. Die Sensorvorrichtung weist ein Gehäuse 809 und Anschlüsse 804a, 804b auf. Innerhalb des Gehäuses ist der in Fig. 7 dargestellte Aufbau und

ein Ansteuer- und/oder Auswertechip 800 angeordnet. Der Chip 800 ist mittels elektrischer Verbindungen 806, 807 mit einem der Kontakte 804b und mit den Hauptkontakten 702 (Fig. 7) des Haupt-Wafers 710 verbunden. Die in Fig. 7 gezeigte Anordnung ist innerhalb des Gehäuses 809 gekapselt, wie durch die Kapselung 808 angedeutet. Der Zugangskanal 781 des Zugangs-Wafers 780 kommuniziert mit einem Loch 881, das in dem Gehäuse 809 ausgeführt ist. Der Kontakt 804a ist elektrisch isoliert von dem Kontakt 804b und stellt beispielsweise einen Massenanschluss dar. Man beachte, dass neben den hier dargestellten zwei Kontakten 804a, 804b weitere Kontakte vorgesehen sein können, um die Sensorvorrichtung mit elektrischer Energie zu versorgen und gemessene Signale herausführen zu können.

**[0092] Fig.** 9 zeigt eine schematische, perspektivische Querschnittsansicht von vier vorläufigen Kavitäten. Die vier vorläufigen Kavitäten haben hier rechteckige Grundrisse, wobei jedoch auch andere Formen denkbar sind. Die Seitenwände der vorläufigen Kavitäten weisen einen Winkel zur Substratoberfläche auf, der etwas größer als 90° ist.

[0093] Fig. 10 zeigt eine schematische, perspektivische Querschnittsansicht von zwei finalen Kavitäten, die mittels Bosch-Ätzung nach Oxid-Hartmasken-Strukturierung ohne Polymer-Abscheidung, sowie mittels pn-Ätzung (nach Lackentfernung) erzeugt wurden. Wie bereits im Zusammenhang mit Fig. 6 erwähnt, führt die fehlende Polymer-Abscheidung dazu, dass die während der Bosch-Ätzung erzeugten Seitenwände der vorläufigen Kavität nicht während der nachfolgenden pn-Ätzung geschützt sind. Daher werden die ursprünglich fast senkrechten Oberflächenseitenwandabschnitte zum Teil weggeätzt, bis eine effektiv als Ätzstopp wirkende <111>-Kristallebene erreicht wird.

**[0094]** Im Boden der rechten Kavität ist eine Struktur zu erkennen, die das Masseelement **750** (siehe **Fig.** 7) des Beschleunigungssensors andeutet.

[0095] Fig. 11 zeigt eine schematische Darstellung von Ätzmustern, die mittels verschiedener Ätzverfahren bzw. Kombinationen verschiedener Ätzverfahren erreicht werden können. Es wird angenommen, dass eine Kavität mit einer Tiefe d erzeugt werden soll und dass sämtlichen Ätzverfahren bzw. Kombinationen von Ätzverfahren an der Substratoberfläche dieselbe Angriffsfläche zur Verfügung steht.

[0096] Man betrachtet zunächst das mittels einer pn-Ätzung erzielbare Ätzmuster. Aufgrund der relativ flach verlaufenden Seitenwände verringert sich der Querschnitt der erzeugten Kavität mit zunehmender Tiefe. In dem in Fig. 11 dargestellten Beispiel hat die mit der pn-Ätzung hergestellte Kavität bei der Tiefe d nur noch eine sehr geringe laterale Ausdehnung.

**[0097]** Weiterhin sind in **Fig.** 11 auch die Ätzmuster von zwei unterschiedlichen Kombinationsprozessen aus Bosch-Ätzung und pn-Ätzung dargestellt. Die zwei Kombinationsprozesse unterscheiden sich hinsichtlich ihres Bosch-Ätzungs-Anteils.

**[0098]** Bei dem ersten Kombinationsprozess wird zunächst eine vorläufige Kavität mittels des Boschprozesses mit einer Tiefe  $d_{Bosch1}$  geätzt. Der BoschÄtz-Anteil ist somit  $d_{Bosch1}/d$ . Bei der zweiten Variante ist der Bosch-Ätz-Anteil höher, so dass die auf diese Weise erzeugte vorläufige Kavität eine Tiefe  $d_{Bosch2} > d_{Bosch1}$  hat (Bosch-Ätz-Anteil =  $d_{Bosch2}/d$  in diesem Fall).

[0099] In beiden Fällen schließt sich eine pn-Ätzung an. Hierbei können zwei Fälle unterschieden werden: im ersten Fall sind die Seitenwände der vorläufigen Kavität durch ein entsprechendes Schutzmaterial während der pn-Ätzung geschützt und werden somit im Wesentlichen nicht angegriffen. Im zweiten Fall sind die Seitenwände während der pn-Ätzung ungeschützt und werden daher ebenfalls verändert, was zu einer Verbreiterung der Kavität in diesem Bereich führt.

**[0100]** Als Beispiele seien noch folgende Werte angegeben: d = 400  $\mu$ m, d<sub>Bosch1</sub> = 200  $\mu$ m und d<sub>Bosch2</sub> = 300  $\mu$ m. Auch die nachfolgend angegebenen Zahlenwerte sind ausdrücklich als Beispiel anzusehen.

**[0101] Fig.** 11 veranschaulicht, dass mittels des ersten Kombinationsprozesses die laterale Ausdehnung der Kavität an deren Boden um den Wert 2  $w_A$  gegenüber der ausschließlich pn-geätzten Kavität vergrößert werden kann. Bezug nehmend auf die oben angegebenen Zahlenbeispiele würde  $w_A$  = 140  $\mu$ m betragen. Im Falle des zweiten Kombinationsprozesses (Bosch-Ätzung bis auf eine Tiefe  $d_{Bosch2}$ ) weist der Boden der finalen Kavität sogar eine Vergrößerung von  $2(w_A + w_B)$  gegenüber der ausschließlich pn-geätzten Kavität auf.

**[0102]** Bezug nehmend auf die oben angegebenen Zahlenwerte würde  $w_B$  in diesem Fall z. B. 72  $\mu$ m betragen.

[0103] Gerade in der MEMS-Technologie bestimmt die erforderliche laterale Erstreckung des Bodens der Kavität die Größe der Kavität, insbesondere deren maximale laterale Ausdehnung. Fig. 11 veranschaulicht, dass ein möglichst hoher Bosch-Ätz-Anteil in dieser Hinsicht Vorteile bringt. In der Praxis wird man häufig einen Kompromiss anstreben, der die unterschiedlichen Anlagen- und Prozesskosten für Bosch-Ätzung und pn-Ätzung, sowie die erzielbare bessere Flächenausnutzung in Betracht zieht. Zu beachten ist ferner, dass die pn-Ätzung gegenüber der Bosch-Ätzung typischerweise einen besser kontrollierbaren

Ätzstopp bereitstellt und somit eine genauere Fertigung von MEMS-Strukturen erlaubt.

**[0104]** Beim ersten Kombinationsprozess ist die laterale Ersteckung des Kavitätsbodens um den Betrag 2 ( $w_B + w_C$ ) kleiner als die laterale Erstreckung der mit der Bosch-Ätzung erzeugten vorläufigen Kavität. Wiederum in Bezug auf die oben angegebenen Zahlenwerte würde  $w_C$  hier 68 µm betragen.

[0105] Fig. 11 veranschaulicht auch eine Veränderung der Seitenwand der vorläufigen Kavität während der pn-Ätzung, falls die Seitenwand während der pn-Ätzung nicht durch ein geeignetes Schutzmaterial geschützt ist. Beim ersten Kombinationsprozess (Bosch-Ätzung bis  $d_{Bosch1}$ ) wird die Kavität in lateraler Richtung um den Wert 2  $w_D$  vergrößert, wobei  $w_D$  mit den oben angegebenen Zahlenwerten 72  $\mu$ m beträgt. Beim zweiten Kombinationsprozess (Bosch-Ätzung bis  $d_{Bosch2}$ ) beträgt die Vergrößerung der maximalen lateralen Ausdehnung 2 ( $w_D$  +  $w_E$ ) gegenüber der lateralen Ausdehnung der vorläufigen Kavität, wobei  $w_E$  bei Annahme der oben angegebenen Zahlenwerte 32  $\mu$ m beträgt.

**[0106]** Die folgende Tabelle fasst die beispielhaften Zahlenwerte für die in **Fig.** 11 gezeigten Dimensionen zusammen.

| 400 µm |

|--------|

| 200 µm |

| 300 µm |

| 140 µm |

| 72 µm  |

| 68 µm  |

| 72 µm  |

| 32 µm  |

|        |

[0107] Fig. 12 zeigt eine Elektronenmikroskopaufnahme einer Detailaschnittansicht (oder, im Falle einer entsprechenden Änderung, einer schematischen Detailschnittansicht als Strichzeichnung) einer oberen Kante einer Kavitätsseitenwand, in der das Schutzmaterial 30 an der Oberfläche des Substrats 10 und an der Seitenwand zu sehen ist. Es wurde, wie in Fig. 12 ersichtlich, eine Schutzoxiddicke des Schutzmaterials 30 von ungefähr 2500 nm gewählt. Die Dicke muss typischerweise so gewählt sein, dass am Boden und an den unteren Ecken der vorläufigen Kavität 40 eine ausreichende Schutzoxiddicke vorliegt, um beim nachfolgenden Plasma-Ätzen ein Anätzen der unteren Ecken bzw. der Seitenwände zu vermeiden. Die Schutzoxiddicke der Schicht 30 ist nicht konform: Sie ist an der Seitenwand dünner als auf der Substratoberseite. Auf der Substratoberseite 11 befindet sich zwischen Schutzoxidschicht 30 und Siliziumsubstrat 10 eine Oxidschicht 20 (vgl. auch

[0108] Fig. 3). Zur besseren Verdeutlichung sind in Fig. 12 die Grenzen zwischen dem Substrat 10, der Oxidschicht 20 und der Schutzoxidschicht 30 mit gestrichelten Linien angedeutet.

[0109] Obwohl manche Aspekte im Zusammenhang mit einer Vorrichtung beschrieben wurden, versteht es sich, dass diese Aspekte auch eine Beschreibung des entsprechenden Verfahrens darstellen, sodass ein Block oder ein Bauelement einer Vorrichtung auch als ein entsprechender Verfahrensschritt oder als ein Merkmal eines Verfahrensschrittes zu verstehen ist. Analog dazu stellen Aspekte, die im Zusammenhang mit einem oder als ein Verfahrensschritt beschrieben wurden, auch eine Beschreibung eines entsprechenden Blocks oder Details oder Merkmals einer entsprechenden Vorrichtung dar. Einige oder alle der Verfahrensschritte können durch einen Hardware-Apparat (oder unter Verwendung eines Hardware-Apparats), wie zum Beispiel einen Mikroprozessor, einen programmierbaren Computer oder eine elektronische Schaltung ausgeführt werden. Bei einigen Ausführungsbeispielen können einige oder mehrere der wichtigsten Verfahrensschritte durch einen solchen Apparat ausgeführt werden.

[0110] Die oben beschriebenen Ausführungsbeispiele stellen lediglich eine Veranschaulichung der Prinzipien der vorliegenden Erfindung dar. Es versteht sich, dass Modifikationen und Variationen der hierin beschriebenen Anordnungen und Einzelheiten anderen Fachleuten einleuchten werden. Deshalb ist beabsichtigt, dass die Erfindung lediglich durch den Schutzumfang der nachstehenden Patentansprüche und nicht durch die spezifischen Einzelheiten, die anhand der Beschreibung und der Erläuterung der Ausführungsbeispiele hierin präsentiert wurden, beschränkt sei.

[0111] In der vorausgehenden detaillierten Beschreibung kann gesehen werden, dass verschiedene Merkmale in Ausführungsbeispielen zusammengruppiert sind. Diese Weise der Offenbarung soll nicht als Absicht verstanden werden, dass die beanspruchten Ausführungsbeispiele mehr Merkmale benötigen, als explizit in dem jeweiligen Anspruch erwähnt sind. Vielmehr ist es so, dass erfinderischer Inhalt in weniger als allen Merkmalen eines einzelnen offenbarten Ausführungsbeispiels liegen kann. Daher sollen die folgenden Ansprüche hiermit als in die Beschreibung aufgenommen gelten, wobei jeder Anspruch für sich als ein separates Ausführungsbeispiel stehen kann. Obwohl jeder Anspruch für sich als separates Ausführungsbeispiel stehen kann, ist anzumerken, dass - obwohl ein abhängiger Anspruch sich in den Ansprüchen auf eine spezifische Kombination mit einem oder mehreren Ansprüchen beziehen kann andere Ausführungsbeispiele auch eine Kombination dieses abhängigen Anspruchs mit dem Gegenstand von jedem anderen abhängigen Anspruch oder

eine Kombination von jedem Merkmal mit anderen abhängigen und unabhängigen Ansprüchen umfassen oder einschließen können. Solche Kombinationen sind hierein vorgeschlagen, sofern nicht explizit ausgedrückt ist, dass eine spezifische Kombination nicht beabsichtigt ist. Weiterhin ist auch beabsichtigt, dass Merkmale eines Anspruches in irgendeinen anderen unabhängigen Anspruch aufgenommen werden können, selbst wenn dieser Anspruch nicht direkt abhängig ist von dem unabhängigen Anspruch.

**[0112]** Es ist weiterhin anzumerken, dass in der Beschreibung oder in den Ansprüchen offenbarte Verfahren durch eine Vorrichtung implementiert sein können, die Mittel zum Ausführen der jeweiligen Schritte oder Aktionen dieses Verfahrens aufweist.

**[0113]** Weiterhin kann in manchen Ausführungsbeispielen ein einzelner Schritt/Aktion in mehrere Unterschritte unterteilt werden oder mehrere Unterschritte enthalten. Derartige Unterschritte können in der Offenbarung des einzelnen Schritts enthalten und Teil der Offenbarung des einzelnen Schritts sein.

#### Patentansprüche

1. Verfahren zum Herstellen eines mikroelektromechanischen Systems mit folgenden Merkmalen: Bereitstellen eines dotierten Halbleitersubstrats mit einer ersten Oberfläche und einer der ersten Oberfläche gegenüber liegenden zweiten Oberfläche;

Durchführen eines Lithographieprozesses und einer anschließenden Implantation zur Herstellung eines umdotierten Bereichs innerhalb des dotierten Halbleitersubstrats, wobei ein pn-Übergang bei einer Tiefe innerhalb des Halbleitersubstrats gebildet wird, wobei die Tiefe des pn-Übergangs eine gewünschte Tiefe eines Bodens zumindest einer zu bildenden Kavität bestimmt;

Durchführen eines Strukturierungsprozesses zur Herstellung von mikroelektromechanischen Strukturen in dem Halbleitersubstrat und an der zweiten Oberfläche, wobei zumindest ein Teil der vorgesehenen mikroelektromechanischen Strukturen sich in den umdotierten Bereich erstreckt;

Trockenätzen des Halbleitersubstrats von der ersten Oberfläche des Halbleitersubstrats aus an zumindest einem beabsichtigten Kavitätsort, um zumindest eine vorläufige Kavität zu erhalten, wobei das Trockenätzen gestoppt wird, bevor die gewünschte Tiefe der Kavität erreicht wird;

Abscheiden eines Schutzmaterials hinsichtlich eines nachfolgenden elektrochemischen Ätzprozesses an der ersten Oberfläche des Halbleitersubstrats und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität:

Entfernen des Schutzmaterials zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität um das Halbleitersubstrat freizulegen; und

elektrochemisches Ätzen des Halbleitersubstrats an dem freigelegten Abschnitt des Bodens der zumindest einen vorläufigen Kavität bis zu dem pn-Übergang, so dass dieser als elektrochemischer Ätzstopp den Boden der zumindest einen Kavität bildet, so dass die zumindest eine Kavität an den Teil der mikroelektromechanischen Strukturen angrenzt, der sich in den umdotierten Bereich erstreckt.

2. Verfahren gemäß Anspruch 1, weiter umfassend:

Abscheiden einer Oxidmaske für das Trockenätzen des Halbleitersubstrats vor dem Trockenätzen.

- 3. Verfahren gemäß Anspruch 1 oder 2, wobei das Trockenätzen zumindest einen der folgenden Prozesse umfasst:

- reaktives Ionenätzen (RIE), tiefes reaktives Ionenätzen (DRIE) und einen Boschprozess.

- 4. Verfahren gemäß einem der Ansprüche 1 bis 3, wobei das Schutzmaterial ein Oxid, ein Siliziumoxid oder ein Spacer-Oxid ist.

- 5. Verfahren gemäß einem der Ansprüche 1 bis 4, wobei das Abscheiden des Schutzmaterials eine Plasma-Abscheidung, eine thermische Oxid-Abscheidung oder eine Kombination dieser umfasst.

- Verfahren gemäß einem der Ansprüche 1 bis 5, wobei das Entfernen des Schutzmaterials ein Plasma-Ätzen umfasst.

- 7. Verfahren gemäß einem der Ansprüche 1 bis 6, welches vor dem Entfernen des Schutzmaterials weiterhin ein Abscheiden einer Maske und ein Strukturieren der abgeschiedenen Maske umfasst.

- 8. Verfahren gemäß einem der Ansprüche 1 bis 7, wobei für das elektrochemische Ätzen ein basisches Ätzmedium verwendet wird.

- 9. Verfahren gemäß einem der Ansprüche 1 bis 8, wobei das elektrochemische Ätzen eine Ätzstopptechnik bereitstellt.

- 10. Verfahren gemäß einem der Ansprüche 1 bis 9, wobei das elektrochemische Ätzen einen ersten zeitlichen Abschnitt umfasst, währenddessen eine an das Halbleitersubstrat angelegte elektrische Spannung gesteigert wird, und einen zweiten zeitlichen Abschnitt umfasst.

- 11. Verfahren gemäß einem der Ansprüche 1 bis 10, wobei ein für das elektrochemische Ätzen verwendetes Ätzmedium Tetramethylammoniumhydroxid (TMAH), eine wässrige Lösung von Ethylendiamin und Brenzcatechin (EDP), Hydrazin, Kaliumhydroxid (KOH) oder eine Kombination dieser umfasst.

12. Verfahren zum Herstellen eines mikroelektromechanischen Systems mit folgenden Merkmalen: Bereitstellen eines dotierten Halbleitersubstrats mit einer ersten Substratoberfläche und einer der ersten Substratoberfläche gegenüber liegenden zweiten Substratoberfläche;

Durchführen eines Lithographieprozesses und einer anschließenden Implantation zur Herstellung eines umdotierten Bereichs innerhalb des dotierten Halbleitersubstrats, wobei ein pn-Übergang bei einer Tiefe innerhalb des Halbleitersubstrats gebildet wird, wobei die Tiefe des pn-Übergangs in Abhängigkeit einer gewünschten Tiefe eines Bodens zumindest einer zu bildenden Kavität gewählt ist;

Durchführen eines Strukturierungsprozesses zur Herstellung von mikroelektromechanischen Strukturen in dem Halbleitersubstrat und an der zweiten Oberfläche, wobei zumindest ein Teil der vorgesehenen mikroelektromechanischen Strukturen sich in den umdotierten Bereich erstreckt;

Durchführen eines Boschprozesses an der erste Substratoberfläche des Halbleitersubstrats, um zumindest eine vorläufige Kavität zu bilden, wobei der Boschprozess gestoppt wird, bevor die gewünschte Tiefe der Kavität erreicht wird;

Durchführen einer Plasma-chemischen Gasphasenabscheidung eines Siliziumoxids an der ersten Substratoberfläche und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität;

anisotropes Ätzen des Siliziumoxids zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität um das Halbleitersubstrat freizulegen; und

elektrochemisches, anisotropes Ätzen des Halbleitersubstrats unter Verwendung des pn-Übergangs als elektrochemisch-gesteuerten pn-Ätztopp, wobei das elektrochemische, anisotrope Ätzen zumindest an dem Abschnitt des Bodens der zumindest einen vorläufigen Kavität erfolgt und die zumindest eine vorläufige Kavität auf diese Weise erweitert, so dass die Kavität an dem pn-Übergang den Kavitätsboden aufweist und an den Teil der mikroelektromechanischen Strukturen angrenzt, der sich in den umdotierten Bereich erstreckt.

13. Verfahren gemäß Anspruch 12, weiter umfassend:

Abscheiden einer Oxidmaske für den Boschprozess vor dem Boschprozess.

- 14. Verfahren gemäß Anspruch 12 oder 13, wobei das anisotrope Ätzen des Siliziumoxids ein Plasma-Ätzen umfasst.

- 15. Verfahren gemäß einem der Ansprüche 12 bis 14. weiter umfassend:

Abscheidung einer Maske und Strukturierung der abgeschiedenen Maske vor dem anisotropen Ätzen des Siliziumoxids.

- 16. Verfahren gemäß einem der Ansprüche 12 bis 15, wobei für das elektrochemische, anisotrope Ätzen ein basisches Ätzmedium verwendet wird.

- 17. Verfahren gemäß einem der Ansprüche 12 bis 16, wobei das elektrochemische, anisotrope Ätzen einen ersten zeitlichen Abschnitt umfasst, währenddessen eine an das Halbleitersubstrat angelegte elektrische Spannung gesteigert wird, und einen zweiten zeitlichen Abschnitt umfasst.

- 18. Verfahren gemäß einem der Ansprüche 12 bis 17, wobei ein für das elektrochemische, anisotrope Ätzen verwendetes Ätzmedium Tetramethylammoniumhydroxid (TMAH), eine wässrige Lösung von Ethylendiamin und Brenzcatechin (EDP), Hydrazin, Kaliumhydroxid (KOH) oder eine Kombination dieser umfasst.

Es folgen 12 Seiten Zeichnungen

102 Trockenätzen des Halbleitersubstrats von einer Oberfläche des Halbleitersubstrats aus an zumindest einem beabsichtigten Kavitätsort um zumindest eine vorläufige Kavität zu erhalten 104 Abscheiden eines Schutzmaterials hinsichtlich eines nachfolgenden Nassätzprozesses an der Oberfläche des Halbleitersubstrats und an Kavitätsoberflächen der zumindest einen vorläufigen Kavität 106 Entfernen des Schutzmaterials zumindest an einem Abschnitt eines Bodens der zumindest einen vorläufigen Kavität um das Halbleitersubstrat freizulegen 108 Elektrochemisches Ätzen des Halbleitersubstrats an dem freigelegten Abschnitt des Bodens der zumindest einen vorläufigen Kavität

FIG 1

FIG 2

FIG 3

FIG 4

FIG 6

FIG 7

FIG 9

FIG 10

FIG 11

26/27

FIG 12