# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G11C 7/22** (2015.01) **G11C 8/00** (2006.01)

(21) 출원번호

10-2009-0076368

(22) 출원일자

2009년08월18일

심사청구일자 (65) 공개번호 2014년07월24일 10-2011-0018750

(43) 공개일자

2011년02월24일

(56) 선행기술조사문헌

US20090161453 A1

(45) 공고일자 2016년01월13일

(11) 등록번호 10-1585213

(24) 등록일자 2016년01월07일

(73) 특허권자

#### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

#### 전영진

경기도 화성시 삼성전자로 1, 삼성반도체 화성사 업장 지적재산팀 (반월동)

#### 김양기

경기도 화성시 삼성전자로 1, 삼성반도체 화성사 업장 지적재산팀 (반월동)

(74) 대리인

박상수

전체 청구항 수 : 총 10 항

심사관 : 손윤식

(54) 발명의 명칭 라이트 레벨링 동작을 수행하기 위한 메모리 장치의 제어 방법, 메모리 장치의 라이트 레벨링 방법, 및 라이트 레벨링 동작을 수행하는 메모리 컨트롤러, 메모리 장치, 및 메모리 시스템

#### (57) 요 약

본 발명은 라이트 레벨링 동작을 수행하기 위한 메모리 장치의 제어 방법, 메모리 장치의 라이트 레벨링 방법, 및 라이트 레벨링 동작을 수행하는 메모리 컨트롤러, 메모리 장치, 및 메모리 시스템을 공개한다. 이 방법은 메모리 장치로 전송할 클럭 신호를 생성하는 단계, 상기 메모리 장치로 전송할 데이터 스트로브 신호를 생성하는 단계, 라이트 레벨링 동작 시, 상기 메모리 장치로 전송되는 커맨드 신호 및 라이트 레벨링 제어 신호를 생성하는 단계, 상기 라이트 레벨링 동작 시, 상기 라이트 레벨링 제어 신호에 응답하여 상기 메모리 장치에서 수신한 상기 커맨드 신호와 상기 데이터 스트로브 신호의 위상차를 감지하는 단계, 및 상기 감지된 위상차에 따라 상기 메모리 장치의 노멀 모드에서 라이트 동작시, 상기 클럭 신호에 대한 상기 데이터 스트로브 신호의 발생 타이밍을 조절하는 단계를 포함하는 것을 특징으로 한다.

## 대 표 도 - 도15

### 명세서

### 청구범위

#### 청구항 1

메모리 장치로 전송할 클럭 신호를 생성하는 단계;

상기 메모리 장치로 전송할 데이터 스트로브 신호를 생성하는 단계;

라이트 레벨링 동작 시, 상기 메모리 장치로 전송할 커맨드 신호 및 라이트 레벨링 제어 신호를 생성하는 단계;

상기 라이트 레벨링 동작 시, 상기 라이트 레벨링 제어 신호에 응답하여 상기 메모리 장치에서 수신한 상기 커맨드 신호와 상기 데이터 스트로브 신호의 위상차를 감지하는 단계; 및

상기 감지된 위상차에 따라 상기 메모리 장치의 노멀 모드에서 라이트 동작시, 상기 클럭 신호에 대한 상기 데이터 스트로브 신호의 생성 타이밍을 조절하는 단계를 포함하는 메모리 장치의 제어 방법.

#### 청구항 2

제1항에 있어서, 상기 커맨드 신호는

라이트 커맨드 신호를 포함하는 메모리 장치의 제어 방법.

### 청구항 3

제1항에 있어서, 상기 커맨드 신호는

펄스 신호인 메모리 장치의 제어 방법.

#### 청구항 4

메모리 컨트롤러로부터 외부 클럭 신호를 수신하고, 상기 외부 클럭 신호에 응답하여 내부 클럭 신호를 생성하는 단계;

상기 메모리 컨트롤러로부터 외부 커맨드 신호를 수신하고, 상기 외부 커맨드 신호에 응답하여 상기 내부 클릭 신호에 동기시켜 내부 커맨드 신호를 생성하는 단계;

상기 메모리 컨트롤러로부터 외부 데이터 스트로브 신호를 수신하고, 상기 외부 데이터 스트로브 신호에 응답하여 내부 데이터 스트로브 신호를 생성하는 단계;

상기 내부 커맨드 신호와 상기 내부 데이터 스트로브 신호의 위상차를 검출하는 단계; 및

라이트 레벨링 동작시, 상기 위상차를 표시하는 감지 정보를 발생하는 단계를 포함하는 메모리 장치의 라이트 레벨링 방법.

### 청구항 5

제4항에 있어서, 상기 외부 커맨드 신호는

라이트 커맨드 신호를 포함하는 메모리 장치의 라이트 레벨링 방법.

### 청구항 6

제4항에 있어서, 상기 외부 커맨드 신호는

펄스 신호인 메모리 장치의 라이트 레벨링 방법.

## 청구항 7

제4항에 있어서, 상기 메모리 장치의 라이트 레벨링 방법은

상기 감지 정보를 상기 메모리 컨트롤러로 전송하는 단계를 더 포함하는 메모리 장치의 라이트 레벨링 방법.

#### 청구항 8

메모리 장치로 전송할 주기적 클럭 신호를 발생하는 클럭 발생부;

상기 메모리 장치로 전송할 데이터 스트로브 신호를 발생하는 데이터 스트로브 발생부; 및

상기 메모리 장치로 전송할 커맨드들을 발생하고, 라이트 레벨링 동작시 상기 메모리 장치로 전송할 커맨드 신 호 및 라이트 레벨링 제어 신호를 발생하는 제어부를 포함하는 메모리 컨트롤러.

### 청구항 9

메모리 컨트롤러로부터 외부 클럭 신호를 수신하여 내부 클럭 신호를 발생하는 클럭 버퍼;

상기 메모리 컨트롤러로부터 외부 커맨드 신호를 수신하고, 상기 외부 커맨드 신호에 응답하여 상기 내부 클럭 신호에 동기되는 내부 커맨드 신호를 발생하는 커맨드 디코더;

상기 메모리 컨트롤러로부터 외부 데이터 스트로브 신호를 수신하여 내부 데이터 스트로브 신호를 발생하는 데 이터 스트로브 버퍼; 및

라이트 레벨링 동작시, 상기 내부 커맨드 신호와 상기 내부 데이터 스트로브 신호의 위상차를 검출하여 상기 위 상차를 나타내는 감지 정보를 발생하는 위상 검출부를 포함하는 메모리 장치.

### 청구항 10

클럭 신호, 커맨드 및 어드레스 신호들을 발생하는 메모리 컨트롤러; 및

복수개의 메모리 장치들을 구비하고, 상기 클럭 신호, 상기 커맨드 및 어드레스 신호들을 수신하고, 상기 커맨 드 및 어드레스 신호에 응답하여 상기 복수개의 메모리 장치들 중 적어도 하나로/로부터 데이터를 저장하고 검 색하는 메모리 모듈을 구비하고,

라이트 레벨링 동작시, 상기 메모리 컨트롤러는 라이트 레벨링 동작을 수행하기 위한 커맨드 신호, 라이트 레벨 링 제어 신호, 및 데이터 스트로브 신호를 상기 복수개의 메모리 장치들 중 적어도 하나로 출력하고, 상기 적어 도 하나의 메모리 장치는 상기 커맨드 신호 및 상기 클럭 신호에 응답하여 노멀 모드에서의 동작시와 동일한 경 로를 통하여 내부 커맨드 신호를 발생하고, 상기 데이터 스트로브 신호에 응답하여 상기 노멀 모드에서의 동작 시와 동일한 경로를 통하여 내부 데이터 스트로브 신호를 발생하고, 상기 내부 커맨드 신호 및 상기 내부 데이 터 스트로브 신호의 위상차를 나타내는 감지 정보를 상기 메모리 컨트롤러로 출력하는 메모리 시스템.

### 발명의 설명

### 발명의 상세한 설명

### 기술분야

본 발명은 메모리 장치에 관한 것으로, 특히 라이트 레벨링 동작을 수행하는 메모리 컨트롤러, 메모리 장치 및 메모리 시스템과, 상기 라이트 레벨링 동작을 수행하기 위한 메모리 장치의 제어 방법 및 상기 메모리 장치의 라이트 레벨링 수행 방법에 관한 것이다.

#### 배경기술

고집적 전자 장치에 대한 지속적인 중요성에 따라, 고속 및 저전력으로 동작하고, 높은 집적도를 가지는 반도체 메모리 장치에 대한 요구가 지속되고 있다. 이를 달성하기 위해, 크기를 감소시키고, 수직/수평으로 배열된 트 랜지스터 셀들을 가지는 다층 장치(multiple-layered device)가 개발되고 있다.

반도체 장치들이 보다 소형화됨에 따라, 신호들을 교환하는 타이밍이 보다 중요하게 되었다. 특히, 메모리 시스 템에 있어서, 커맨드/어드레스 신호, 클럭 신호, 및 데이터 스트로브 신호의 타이밍의 정렬은 클럭 신호의 주파 수가 증가함에 따라 반드시 처리되어야 한다. 예를 들면, 메모리 컨트롤러와 메모리 장치를 구비하는 메모리 모 듈을 구비하는 메모리 시스템에서, 메모리 모듈의 메모리 장치 각각에 대한 신호 라인의 길이가 서로 다르기 때 문에, 메모리 모듈의 다른 메모리 장치들로 전송되는 신호의 타이밍은 달라질 수 있다.

특히, 최근의 메모리 시스템에서는, 메모리 장치에 데이터를 라이트하는 라이트 동작을 수행하는 동안, 클럭 신

[0004]

[0001]

[0002]

[0003]

- 3 -

호와 데이터 스트로브 신호가 적절한 타이밍 윈도우 내에 메모리 모듈의 각 메모리 장치에 도달하는 것을 보장하기 위해 라이트 레벨링 동작을 수행한다. 라이트 레벨링 동작을 수행하기 위해, 각 메모리 장치는 클럭 신호와 데이터 스트로브 신호가 전달되는 경로를 복제한 복제 경로(replica path) 회로를 구비한다. 그리고, 수신된 클럭 신호와 수신된 데이터 스트로브 신호 사이의 위상차를 감지하고, 이를 메모리 컨트롤러에 전송한다. 메모리 모듈의 메모리 장치 중 하나에 대한 라이트 동작시, 메모리 컨트롤러는 데이터 스트로브 신호를 지연시켜 데이터 스트로브 신호와 클럭 신호가 메모리 장치에 동시에 도달하도록 한다.

[0005]

동작 주파수가 증가함에 따라, 복제 경로를 이용하여 수행되는 라이트 레벨링 동작은 엄격한 타이밍 제한 내에 신호 타이밍을 조절하기에 불충분하다. 또한, 복제 경로는 고집적 장치인 메모리 장치의 회로 영역을 차지한다. 또한, 복제 경로는 시스템 전원을 소모할 수도 있다.

[0006]

나아가, 최근의 시스템에서는, 라이트 레벨링에 이용되는 위상 비교는 메모리 컨트롤러로부터 제공되어 각각 버피링된 버퍼드(buffered) 클럭 신호와 메모리 컨트롤러로부터 수신된 데이터 스트로브 신호를 버퍼링한 버퍼드데이터 스트로브 신호 사이에 이루어진다. 또한, 클럭 신호는 소정의 듀티 사이클을 가지고 주기적이고 지속적으로 토글링된다. 따라서, 교정 마진이 라이징 에지 또는 폴링 에지에서 클럭 신호와 데이터 스트로브 신호를 정렬하기 위해 주어지는 각 방향에 대하여 반주기(만일, 클럭 신호의 듀티비가 50%라면, 0.5 tCK)밖에 되지 않기 때문에 데이터 스트로브 신호를 토글링하는 클럭 신호에 정렬하는 것은 어렵다.

[0007]

또한, 인터페이스 및 복제 경로 회로 등의 내부 회로에 의해 유발된 스큐(skew)의 크기는 고정된 값을 가진다. 동시에, 동작 주파수가 증가함에 따라 클럭 사이클은 보다 감소한다. 이는 종래의 라이트 레벨링 동작을 수행하는 경우에 제한을 추가적으로 유발한다.

## 발명의 내용

## 해결 하고자하는 과제

[0008]

본 발명의 목적은 라이트 레벨링 동작시 교정 마진을 증가시키고, 메모리 장치의 레이아웃 면적을 감소시킬 수 있는 라이트 레벨링 동작을 위한 메모리 장치의 제어 방법을 제공하는데 있다.

[0009]

본 발명의 다른 목적은 상기 목적을 달성하기 위한 메모리 장치의 라이트 레벨링 방법을 제공하는데 있다.

[0010]

본 발명의 또 다른 목적은 상기 목적을 달성하기 위한 라이트 레벨링 동작을 수행하는 메모리 컨트롤러를 제공 하는데 있다.

[0011]

본 발명의 또 다른 목적은 상기 목적을 달성하기 위한 라이트 레벨링 동작을 수행하는 메모리 장치를 제공하는 데 있다.

[0012]

본 발명의 또 다른 목적은 상기 목적을 달성하기 위한 라이트 레벨링 동작을 수행하는 메모리 시스템을 제공하는데 있다.

### 과제 해결수단

[0013]

상기 목적을 달성하기 위한 본 발명의 메모리 장치의 제어 방법은 메모리 장치로 전송할 클럭 신호를 생성하는 단계, 상기 메모리 장치로 전송할 테이터 스트로브 신호를 생성하는 단계, 라이트 레벨링 동작 시, 상기 메모리 장치로 전송할 커맨드 신호 및 라이트 레벨링 제어 신호를 생성하는 단계, 상기 라이트 레벨링 동작 시, 상기라이트 레벨링 제어 신호에 응답하여 상기 메모리 장치에서 수신한 상기 커맨드 신호와 상기 데이터 스트로브 신호의 위상차를 나타내는 감지하는 단계, 및 상기 감지된 위상차에 따라 상기 메모리 장치의 노멀 모드에서 라이트 동작시 상기 클럭 신호에 대한 상기 테이터 스트로브 신호의 발생 타이밍을 조절하는 단계를 포함하는 것을 특징으로 한다.

[0014]

상기 목적을 달성하기 위한 본 발명의 메모리 장치의 제어 방법의 상기 커맨드 신호는 라이트 커맨드 신호를 포함하거나, 펄스 신호인 것을 특징으로 한다.

[0015]

상기 목적을 달성하기 위한 본 발명의 메모리 장치의 제어 방법의 상기 라이트 레벨링 동작은 파워업 동작시 또는 딥 파워 다운 모드 동작을 종료할 때 시작되거나, 주기적으로 시작되거나, 동작 온도의 변화, 상기 위상차의 변화 또는 메모리 장치의 데이터 핀의 임퍼던스의 변화 중 적어도 하나를 감지하면 시작되는 것을 특징으로 한다.

- [0016] 상기 목적을 달성하기 위한 본 발명의 메모리 장치의 제어 방법은 상기 라이트 레벨링 동작 시, 상기 감지된 위상차에 응답하여 발생된 타이밍 정보를 저장하는 단계를 더 포함하고, 상기 노멀 모드에서 라이트 동작 시 상기 클릭 신호에 대한 상기 데이터 스트로브 신호의 발생 타이밍을 상기 타이밍 정보를 이용하여 조절하는 것을 특징으로 한다.

- [0017] 상기 다른 목적을 달성하기 위한 본 발명의 메모리 장치의 라이트 레벨링 방법은 메모리 컨트롤러로부터 외부 클릭 신호를 수신하고, 상기 외부 클릭 신호에 응답하여 내부 클릭 신호를 생성하는 단계, 상기 메모리 컨트롤러로부터 외부 커맨드 신호를 수신하고, 상기 외부 커맨드 신호에 응답하여 상기 내부 클릭 신호에 동기시켜 내부 커맨드 신호를 생성하는 단계, 상기 메모리 컨트롤러로부터 외부 데이터 스트로브 신호를 수신하고, 상기 외부 데이터 스트로브 신호를 수신하고, 상기 외부 데이터 스트로브 신호에 응답하여 내부 데이터 스트로브 신호를 생성하는 단계, 상기 내부 커맨드 신호와 상기 내부 데이터 스트로브 신호의 위상차를 검출하는 단계, 및 라이트 레벨링 동작시 상기 위상차를 표시하는 감지 정보를 발생하는 단계를 포함하는 것을 특징으로 한다.

- [0018] 상기 다른 목적을 달성하기 위한 본 발명의 메모리 장치의 라이트 레벨링 방법의 상기 외부 커맨드 신호는 라이트 커맨드 신호를 포함하거나, 펄스 신호인 것을 특징으로 한다.

- [0019] 상기 다른 목적을 달성하기 위한 본 발명의 메모리 장치의 라이트 레벨링 방법은 상기 감지 정보를 상기 메모리 컨트롤러로 전송하는 단계를 더 포함하는 것을 특징으로 한다.

- [0020] 상기 다른 목적을 달성하기 위한 본 발명의 메모리 장치의 라이트 레벨링 방법은 노멀 모드 동작시 내부 라이트 커맨드 신호 및 데이터 버스를 통하여 상기 메모리 장치로 입력되는 외부 데이터 신호를 입력하기 위해 사용되는 상기 내부 데이터 스트로브 신호를 발생하되, 상기 노멀 모드 동작시 발생되는 상기 내부 라이트 커맨드 신호 및 상기 내부 데이터 스트로브 신호는 상기 라이트 레벨링 동작시 상기 내부 커맨드 신호 및 상기 내부 데이터 스트로브 신호는 상기 라이트 레벨링 동작시 상기 내부 커맨드 신호 및 상기 내부 데이터 스트로브 신호가 발생되는 경로와 동일한 경로를 통하여 발생되는 단계를 더 포함하는 것을 특징으로 한다.

- [0021] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 컨트롤러는 메모리 장치로 전송할 주기적 클릭 신호를 발생하는 클릭 발생부, 상기 메모리 장치로 전송할 데이터 스트로브 신호를 발생하는 데이터 스트로브 발생부, 및 상기 메모리 장치로 전송되는 커맨드들을 발생하고, 라이트 레벨링 동작시 상기 메모리 장치로 전송되는 커맨드신호 및 라이트 레벨링 제어 신호를 발생하는 제어부를 구비하는 것을 특징으로 한다.

- [0022] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 컨트롤러의 상기 커맨드 신호는 라이트 커맨드 신호를 포함하거나, 펄스 신호인 것을 특징으로 한다.

- [0023] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 컨트롤러는 상기 라이트 레벨링 동작 시, 상기 감지 정보에 응답하여 발생된 타이밍 정보를 저장하고, 노멀 모드에서 라이트 동작 시 상기 클럭 신호에 대한 상기 데이터 스트로브 신호의 발생 타이밍을 상기 타이밍 정보를 이용하여 조절하는 것을 특징으로 한다.

- [0024] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 장치는 메모리 컨트롤러로부터 외부 클럭 신호를 수신하여 내부 클럭 신호를 발생하는 클럭 버퍼, 상기 메모리 컨트롤러로부터 외부 커맨드 신호를 수신하고, 상기 외부 커맨드 신호에 응답하여 상기 내부 클럭 신호에 동기되는 내부 커맨드 신호를 발생하는 커맨드 디코더, 상기메모리 컨트롤러로부터 외부 데이터 스트로브 신호를 수신하여 내부 데이터 스트로브 신호를 발생하는 데이터스트로브 버퍼, 및 라이트 레벨링 동작시 상기 내부 커맨드 신호와 상기 내부 데이터 스트로브 신호의 위상차를 검출하여 상기 위상차를 나타내는 감지 정보를 발생하는 위상 검출부를 구비하는 것을 특징으로 한다.

- [0025] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 장치의 상기 외부 커맨드 신호는 라이트 커맨드 신호를 포함하거나, 펄스 신호인 것을 특징으로 한다.

- [0026] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 장치는 노멀 모드 동작시 상기 내부 커맨드 신호 및 데이터 버스를 통하여 상기 메모리 장치로 입력되는 외부 데이터 신호를 입력하기 위해 사용되는 상기 내부 데이터 스트로브 신호를 발생하되, 상기 노멀 모드 동작시 발생되는 상기 내부 커맨드 신호 및 상기 내부 데이터 스트로브 신호가 발생되는 경로와 동일한 경로를 통하여 발생되는 것을 특징으로 한다.

- [0027] 상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 시스템은 클릭 신호, 커맨드 및 어드레스 신호들을 발생하는 메모리 컨트롤러, 및 복수개의 메모리 장치들을 구비하고, 상기 클릭 신호, 상기 커맨드 및 어드레스 신호들을 수신하고, 상기 커맨드 및 어드레스 신호에 응답하여 상기 복수개의 메모리 장치들 중 적어도 하나로/로부터 데이터를 저장하고 검색하는 메모리 모듈을 구비하고, 라이트 레벨링 동작시 상기 메모리 컨트롤러는 라이트

레벨링 동작을 수행하기 위한 커맨드 신호, 라이트 레벨링 제어 신호, 및 데이터 스트로브 신호를 상기 복수개 의 메모리 장치들 중 적어도 하나로 출력하고, 상기 적어도 하나의 메모리 장치는 상기 커맨드 신호 및 상기 클 럭 신호에 응답하여 노멀 모드에서의 동작시와 동일한 경로를 통하여 내부 커맨드 신호를 발생하고, 상기 데이 터 스트로브 신호에 응답하여 상기 노멀 모드에서의 동작시와 동일한 경로를 통하여 내부 데이터 스트로브 신호 를 발생하고, 상기 내부 커맨드 신호 및 상기 내부 데이터 스트로브 신호의 위상차를 나타내는 감지 정보를 상 기 메모리 컨트롤러로 출력하는 것을 특징으로 한다.

상기 또 다른 목적을 달성하기 위한 본 발명의 메모리 시스템의 상기 커맨드 신호는 라이트 커맨드 신호를 포함 하는 것을 특징으로 한다.

### 直 과

따라서, 본 발명의 라이트 레벨링 동작을 수행하는 메모리 장치 및 메모리 시스템, 및 라이트 레벨링 동작 수행 방법은 메모리 장치의 면적을 감소시킬 수 있으며, 보다 정확하게 라이트 레벨링 동작을 수행할 수 있고, 또한 라이트 레벨링 동작시의 마진도 증가시킬 수 있다. 또한, 불필요한 전력 소비도 방지할 수 있다.

#### 발명의 실시를 위한 구체적인 내용

- 이하, 첨부된 도면을 참조하여 본 발명의 메모리 장치의 제어 방법, 메모리 장치의 라이트 레벨링 방법, 및 라 이트 레벨링 동작을 수행하는 메모리 컨트롤러, 메모리 장치, 및 메모리 시스템을 설명하면 다음과 같다.

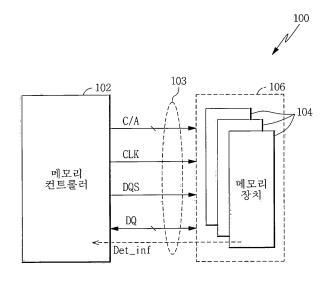

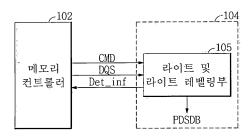

- 도 1은 본 발명의 메모리 시스템의 일실시예의 구성을 나타내는 것으로, 메모리 시스템(100)은 메모리 컨트롤러 (102) 및 메모리 모듈(106)을 구비하여 구성될 수 있으며, 메모리 모듈(106)은 복수개의 메모리 장치들(104)을 구비하여 구성될 수 있다. 또한, 메모리 컨트롤러(102)와 메모리 모듈(106) 사이의 입출력 인터페이스(103)를 구성하는 신호들은 커맨드/어드레스 신호(C/A), 클럭 신호(CLK), 데이터 버스 신호(DQ), 및 데이터 스트로브 신 호(DQS)등을 구비하여 구성될 수 있다. 커맨드/어드레스 신호(C/A)는 라이트/리드 동작시 메모리 컨트롤러(10 2)에서 발생되어 메모리 모듈(106)의 각 메모리 장치(104)로 출력되고, 메모리 장치(104)가 메모리의 특정 위치 또는 특정 어드레스로/로부터 데이터를 라이트/리드 하도록 지시한다. 메모리 컨트롤러(102)로부터 출력되는 신 호들은 클럭 신호(CLK)에 의해 동기된다. 메모리 장치(104)로/로부터 라이트/리드되는 데이터는 데이터 버스 (DQ)를 통해 전송되고, 데이터 스트로브 신호(DQS)에 따라 타이밍이 조절된다.

- 메모리 컨트롤러(102)에 의해 메모리 장치(104)가 라이트 레벨링 동작을 수행하는 동안, 각 메모리 장치(104)에 대한 데이터 스트로브 신호(DQS)의 타이밍이 결정된다. 이 때, 데이터 스트로브 신호(DQS)의 타이밍과 관련된 정보를 메모리 컨틀로러(102)로 제공하기 위해 감지 정보(Det\_inf)가 메모리 장치(104)에서 발생된다. 상기 감 지 정보(Det\_inf)는 데이터 라인(DQ)을 통하여 전송될 수 있다. 메모리 컨트롤러(102)는 상기 감지 정보 (Det\_inf)를 입력하고, 감지 정보(Det\_inf)에 따라 데이터 스트로브 신호(DQS)의 타이밍을 조절한다.

- 실시예에 따라, 감지 정보(Det\_inf)는 메모리 모듈(106)의 메모리 장치(104)와 메모리 컨트롤러(102) 사이의 전 용 라인으로 전송되는 1비트의 신호일 수도 있으며, 메모리 장치(104)와 메모리 컨트롤러(102) 사이의 데이터 라인(DQ)을 통하여 전송되는 1비트 또는 복수개의 비트의 신호일 수도 있다.

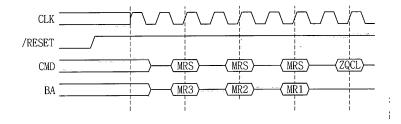

- 도 2는 도 1에 나타낸 본 발명의 메모리 시스템의 파워-업 동작의 실시예를 설명하기 위한 동작 타이밍도를 나 타낸 것으로서, 도 2에서 CLK는 클럭 신호를, /RESET은 파워 업 리셋 신호를, CMD는 커맨드/어드레스 신호(C/A) 중 커맨드 신호를, BA는 커맨드/어드레스 신호(C/A) 중 뱅크 어드레스 신호를 각각 나타낸다.

- 파워-업 동작시, 파워 업 리셋 신호(/RESET)는 소정 시간동안 로우 레벨을 유지하여 메모리 장치(104)를 리셋시 키고, 상기 소정 시간이 경과하면 하이 레벨로 비활성화된다. 파워 업 리셋 신호(/RESET)가 하이 레벨로 비활성 화되고 소정의 시간이 경과하면 클럭 신호(CLK)가 출력된다. 도시하지는 않았지만, 메모리 컨트롤러(102)는 파 워 업 리셋 신호(/RESET)가 하이 레벨로 비활성화되고 소정 시간 경과 후 클럭 인에이블 신호(미도시)를 하이 레벨로 활성화시키며, 클럭 신호(CLK)를 상기 클럭 인에이블 신호가 하이 레벨로 활성화되기 소정 시간 전부터 토글링시키도록 구성될 수 있다.

- [0036] 또한, 파워-업 동작시, 메모리 컨트롤러(102)는 메모리 장치(104)의 모드 설정 레지스터를 설정한다. 예를 들면, 메모리 컨트롤러(102)는 커맨드/어드레스 신호(C/A) 버스를 통해 모드 레지스터 설정(MRS)을 메모리 장치 로 전송하고, 어드레스 신호 라인을 통해 소정의 신호를 인가하여 메모리 장치(104)의 모드 설정 레지스터를 설 정할 수 있다. 이 때, 어드레스 신호 중 뱅크 어드레스 신호를 통해 설정할 모드 설정 레지스터를 선택하고, 어

[0029]

[0028]

[0031]

[0030]

[0032]

[0033]

[0035]

[0034]

드레스 신호 라인을 통해 소정의 신호를 인가하여 모드 설정 레지스터를 설정하도록 구성될 수 있다. 또한, 모드 설정 레지스터의 특정 비트를 설정함으로써 라이트 레벨링 동작을 수행하도록 구성될 수 있다.

- [0037]

- 일반적인 메모리 시스템에 있어서, 메모리 컨트롤러(102)는 다양한 형태의 또는 다양한 개수의 메모리 장치들 (104)과 호환성을 가진다. 따라서, 파워 업 동작시, 메모리 컨트롤러(102)는 커맨드/어드레스 버스(C/A)를 통해모드 레지스터 설정(MRS)을 전송함으로써 메모리 장치(104)와 통신한다. 이때, 메모리 장치(104)는 메모리 장치의 형태, 크기, 및 속도 등과 관련된 정보를 메모리 컨트롤러(102)로 전송한다. 또한, 메모리 컨트롤러(102)는 메모리 장치(104)를 식별하고, 메모리 장치(104)로 전송되는 신호의 타이밍을 조절하기 위한 라이트 레벨링 동작을 시작할 수 있다. 라이트 레벨링 동작에 대하여는 후술한다.

- [0038]

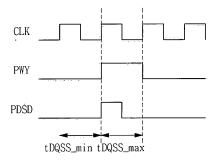

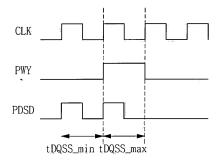

- 도 3a 및 도 3b는 본 발명의 메모리 장치 및 메모리 시스템의 라이트 레벨링 동작의 개념을 설명하기 위한 도면이다. 도 3a 및 도 3b에서 CLK는 클럭 신호를, PWY는 내부 라이트 커맨드 신호를, PDSD는 버퍼드(Buffered) 데이터 스트로브 신호를 각각 나타내며, tDQSS\_min은 클럭 신호의 위상보다 데이터 스트로브 신호의 위상이 얼마나 빠르더라도 라이트 레벨링 동작을 수행하여 타이밍을 조절할 수 있는지를 나타내는 제1 마진을, tDQSS\_max는 클럭 신호의 위상보다 데이터 스트로브 신호의 위상이 얼마나 느리더라도 라이트 레벨링 동작을 수행하여 타이밍을 조절할 수 있는지를 나타내는 제2 마진을 각각 나타낸다.

- [0039]

- 본 발명에 따른 메모리 장치 및 메모리 시스템에서는 클럭 신호(CLK)가 아니라 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))를 이용하여 라이트 레벨링 동작을 수행한다. 즉, 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY)) 및 버퍼드 데이터 스트로브 신호(PDSD)(또는 내부 데이터 스트로브 신호(PDSD\_p))의 위상을 비교함으로써 라이트 레벨링 동작을 수행한다. 따라서, 제1 마진(tDQSS\_min)은 제한없이 증가될수 있으며, 제2 마진(tDQSS\_max)은 클럭 신호의 주기만큼 보장된다.

- [0040]

- 도 3a 및 도 3b에서는 내부 커맨드 신호로서 내부 라이트 커맨드 신호(PWY)를 예시하였으나, 다른 내부 커맨드 신호를 이용하여 라이트 레벨링 동작을 수행할 수도 있다. 또한, 도 3a 및 도 3b에서는 내부 라이트 커맨드 신호(PWY)가 클럭 신호(CLK)의 한 주기에 해당하는 펄스폭을 가지는 것으로 도시하였으나, 라이트 레벨링 동작을 수행하기 위한 내부 커맨드 신호는 클럭 신호(CLK)의 주기의 n배(n은 1이상의 정수)에 해당하는 펄스폭을 가질수 있다.

- [0041]

- 또한, 도 3b에 나타낸 바와 같이, 라이트 레벨링 동작시 발생되는 버퍼드 데이터 스트로브 신호(PDSD)(또는 내부 데이터 스트로브 신호(PDSD\_p))는 심벌간 간섭 (ISI: inter symbol interference)에 의한 왜곡을 방지하기 위해 더미(dummy) 펄스(또는 프리앰블(preamble) 펄스)가 추가될 수도 있다. 도 3b에서는 하나의 더미 펄스(또는 프리앰블 펄스)가 추가된 경우를 예시하였으나, 경우에 따라 두 개 이상의 더미 펄스(또는 프리앰블 펄스)가 추가되도록 구성될 수도 있다.

- [0042]

- 도 4는 본 발명의 메모리 장치 및 메모리 시스템의 개념을 설명하기 위한 도면이다.

- [0043]

- 본 발명의 메모리 시스템에 따르면, 메모리 장치(104)는 라이트 레벨링을 위한 별도의 복제 경로를 구비하지 않는다. 대신, 노멀 동작시 이용되는 경로를 이용하여 라이트 레벨링 동작을 수행한다. 즉, 본 발명의 메모리 장치(104)의 라이트 및 라이트 레벨링부(105)는 라이트 레벨링 동작시 커맨드 신호(CMD)에 응답하여 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY)) 및 버퍼드 데이터 스트로브 신호(PDSD)의 위상차를 검출하여 감지 정보(Det\_inf)를 메모리 컨트롤러(102)로 출력하고, 노멀 모드에서의 동작시 메모리 컨트롤러(102)로부터 입력되는 데이터 스트로브 신호(DQS)를 수신하여 클럭 데이터 스트로브 신호(PDSDB)를 출력한다. 따라서, 레이아웃 면적을 감소시킬 수 있으며, 또한 복제 경로와 실제 동작시 이용되는 회로의 차이로 인해 라이트 레벨링마진이 감소하는 것도 방지할 수 있다. 또한, 보다 정확하게 라이트 레벨링 동작을 수행할 수 있다.

- [0044]

- 즉, 본 발명에 따른 라이트 레벨링 동작은 메모리 컨트롤러(102)로부터 입력되는 커맨드 신호(예를 들면, 라이트 커맨드 신호)에 응답하여 발생된 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호)와 노멀 동작시 메모리 컨트롤러(102)로부터 입력되는 데이터 스트로브 신호(DQS)에 응답하여 클럭 데이터 스트로브 신호(PDSDB)를 출력하는 회로에서 출력되는 신호(예를 들면, 버퍼드 데이터 스트로브 신호(PDSD) 또는 내부 데이터 스트로브 신호(PDSD)의 위상차를 검출하여 데이터 스트로브 신호(DQS)의 타이밍을 조절하는 방식으로 수행된다.

- [0045]

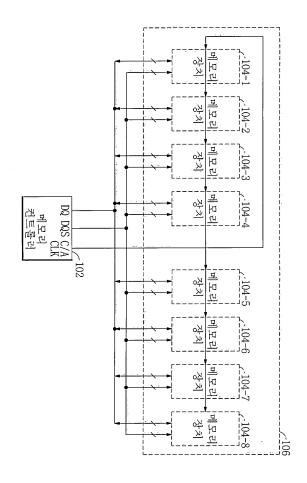

- 도 5는 본 발명의 메모리 시스템(100)의 실시예의 구성을 나타내는 것으로서, 언버퍼드(unbuffered) 메모리 모듈(106)(예를 들면, 언버퍼드 듀얼 인라인 메모리 모듈(UDIMM:Un-buffered Dual In-Line Memory Module))을 구비하는 경우를 나타낸 것이다.

- [0046]

- 도 5에 나타낸 바와 같이, 데이터 신호들(DQ) 및 데이터 스트로브 신호들(DQS)은 메모리 모듈(106)의 메모리 장

치들(104-1~104-8) 각각으로 개별적으로 인가된다. 반면, 커맨드/어드레스 신호(C/A) 및 클럭 신호(CLK)는 먼저 메모리 모듈(106)의 최좌측 메모리 장치(104-1)로 인가되고, 이후 순차적으로 최우측 메모리 장치(104-8)까지 인가된다. 이는 "fly-by" 방식으로 언급된다.

- [0047]

- 즉, 언버퍼드 메모리 모듈(106)의 경우, 커맨드/어드레스 신호(C/A) 및 클럭 신호(CLK)가 메모리 모듈(106)의 최좌측 메모리 장치(104-1)로부터 최우측 메모리 장치(104-8)로 순차적으로 인가되기 때문에, 각 메모리 장치에서 수신되는 클럭 신호(CLK)와 데이터 스트로브 신호(DQS)의 위상차가 서로 다르게 된다. 따라서, 이를 조정하기 위한 라이트 레벨링 동작이 필요하다.

- [0048]

- 라이트 레벨링 동작은 메모리 컨트롤러(102)에 의해 수행되며, 라이트 레벨링 동작에 의해 메모리 모듈(106)의 각 메모리 장치(104-1~104-8)에 대하여 클릭 신호(CLK)에 대한 데이터 스트로브 신호(DQS)의 타이밍이 조절된다. 이후에 메모리 장치의 노멀 모드에서의 동작시, 메모리 컨트롤러(102)로부터 라이트 커맨드가 인가되면, 메모리 장치에 따라 데이터 스트로브 신호(DQS)의 타이밍이 지연되거나 앞당겨지는 방식으로 적절하게 조절된다. 이와 같은 방식으로, fly-by 방식의 메모리 모듈을 포함하는 다양한 형태의 메모리 모듈에 대하여, 동작타이밍 조건을 보증하게 된다.

- [0049]

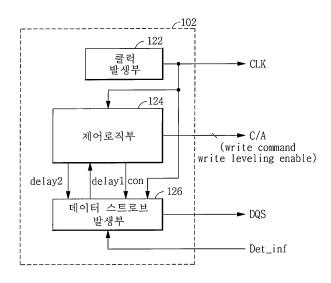

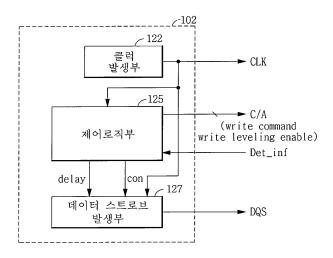

- 도 6은 본 발명의 메모리 시스템(100)의 메모리 컨트롤러(102)의 실시예의 구성을 나타내는 것으로서, 메모리 컨트롤러(102)는 클럭 발생부(122), 제어 로직부(124), 및 데이터 스트로브 발생부(126)를 구비하여 구성될 수 있다.

- [0050]

- 클럭 발생부(122)는 라이트 레벨링 동작 및 노멀 모드에서의 동작시 클럭 신호(CLK)를 발생하여 적어도 하나의 메모리 장치(104)로 전송한다. 클럭 신호(CLK)는 커맨드/어드레스 신호 버스를 통하여 메모리 장치(104)로 전송될 수 있다. 또한, 상기 클럭 신호(CLK)는 메모리 컨트롤러(102)의 제어 로직부(124) 및 데이터 스트로브 발생부(126)로도 인가된다.

- [0051]

- 제어 로직부(124)는 클럭 신호 발생부(122)로부터 출력된 클럭 신호(CLK)를 입력한다. 라이트 레벨링 동작시, 제어 로직부(124)는 클럭 신호(CLK)에 동기시킨 라이트 레벨링 인에이블 신호(write leveling enable) 등을 포함하는 라이트 레벨링 제어 신호를 커맨드/어드레스 신호 라인(C/A)을 통해 출력한다. 또한, 라이트 레벨링 동작시, 제어 로직부(124)는 클럭 신호(CLK)에 동기시킨 커맨드 신호(예를 들면, 라이트 커맨드(write command))를 발생시켜 커맨드/어드레스 신호 라인(C/A)을 통해 출력한다. 예를 들면, 제어 로직부(124)는 라이트 레벨링 동작시 메모리 장치(104)의 모드 설정 레지스터를 설정하기 위한 모드 레지스터 설정(MRS)과 함께 모드 설정 레지스터의 특정 비트의 값을 소정의 값으로 설정하기 위해 어드레스 신호 라인을 통하여 소정의 신호를 출력하도록 구성될 수 있다.

- [0052]

- 제어 로직부(124)는 파워 업 동작시, 또는 딥 파워 다운(deep power down) 모드 동작을 종료할 때 라이트 레벨링 당작을 수행하기 위해 상기 라이트 레벨링 인에이블 신호(write leveling enable)를 포함하는 라이트 레벨링 제어 신호를 출력하도록 구성될 수 있다. 추가적으로, 제어 로직부(124)는 주기적으로 라이트 레벨링 인에이블 신호(write leveling enable)를 포함하는 라이트 레벨링 제어 신호를 출력하도록 구성될 수도 있고, 메모리 장치(104)의 온도가 소정의 온도 이상이 되거나 데이터 핀들의 임피던스 정보(ZQ)가 변하면 라이트 레벨링 인에이블 신호(write leveling enable)를 포함하는 라이트 레벨링 제어 신호를 출력하도록 구성될 수도 있으며, 메모리 장치(104)로부터 라이트 레벨링 요구 신호가 입력되면 라이트 레벨링 인에이블 신호(write leveling enable)를 포함하는 라이트 레벨링 제어 신호를 출력하도록 구성될 수도 있다. 또한, 제어 로직부(124)는 라이트 레벨링 인에이블 신호(write leveling enable)를 출력하고, 어드레스 신호 라인을 통하여 소정의 신호를 출력하여 메모리 장치(104)의 모드 설정 레지스터를 설정하도록 구성될 수도 있다. 즉, 제어 로직부(124)로부터 출력되는 라이트 레벨링 인에이블 신호(write leveling enable)는 파워 업 동작시 출력되는 모드 레지스터 설정(MRS)과 동일한 커맨드 신호일 수 있으며, 제어 로직부(124)는 주기적으로, 또는 메모리 장치(104)가 소정의 온도 이상일 때, 또는 메모리 장치(104)로부터 라이트 레벨링 요구 신호가 입력되었을 때 모드 레지스터 설정(MRS) 및 특정한 어드레스 신호 라인으로 소정의 신호를 출력하여 메모리 장치(104)의 모드 설정 레지스터를 설정함으로써라이트 레벨링 동작을 수행하도록 구성될 수 있다.

- [0053]

- 또한, 제어 로직부(124)는 라이트 레벨링 동작시 라이트 레벨링 동작을 위한 제어 신호(con)를 데이터 스트로브 발생부(126)로 출력하고, 데이터 스트로브 발생부(126)로부터 출력되는 제1 지연 신호(delay1)를 입력하여 각메모리 장치(104)에 대한 데이터 스트로브 신호(DQS)의 지연값으로 저장한다. 제어 로직부(124)는 노멀 모드에서의 동작시 소정의 동작(예를 들면, 라이트 동작)을 수행하기 위한 제어 신호(con)를 출력하고 저장되어 있는 각메모리 장치(104)에 대한 데이터 스트로브 신호 지연값을 제2 지연 신호(delay2)로 출력한다.

[0054]

데이터 스트로브 발생부(126)는 제어 로직부(124)로부터 출력되는 제어 신호(con)에 응답하여 데이터 스트로브 신호(DQS)를 출력한다. 즉, 데이터 스트로브 발생부(126)는 라이트 레벨링 동작시, 제어 로직부(124)로부터 출력되는 라이트 레벨링 동작을 제어 신호(con)에 응답하여 데이터 스트로브 신호(DQS)를 출력하고, 감지 정보(Det\_inf)에 따라 데이터 스트로브 신호(DQS)의 타이밍을 조절하며, 조절된 데이터 스트로브 신호(DQS)의 타이밍에 따라 제1 지연 신호(delay1)를 출력할 수 있다. 예를 들면, 감지 정보(Det\_inf)는 메모리 장치(104)에서 수신한 데이터 스트로브 신호(DQS)의 위상이 내부 커맨드 신호의 위상(즉, 메모리 장치에서 수신한 클럭 신호의위상)보다 빠른지 느린지를 나타내는 신호일 수 있으며, 데이터 스트로브 신호(DQS)의 위상이 빠르다면 데이터 스트로브 신호(DQS)의 출력 타이밍을 늦추고, 데이터 스트로브 신호의 위상이 느리다면 데이터 스트로브 신호(DQS)의 출력 타이밍을 앞당겨 출력할 수 있으며, 소정의 시간 경과 후, 또는 감지 정보(Det\_inf)를 이용하여 메모리 장치(104)에서 수신한 데이터 스트로브 신호(DQS)의 위상과 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))의 위상이 동일해졌을 때의 데이터 스트로브 신호(DQS)의 지연 시간을 제1 지연 신호(delay 1)로 출력하도록 구성될 수 있다.

[0055]

또한, 데이터 스트로브 발생부(126)는 노멀 동작시, 제어 로직부(124)로부터 출력되는 노멀 동작을 위한 제어 신호(con)에 응답하여 제어 로직부(124)로부터 출력되는 제2 지연 신호(delay2)에 따라 데이터 스트로브 신호 (DQS)의 타이밍을 조절하여 출력할 수 있다.

[0056]

실시예에 따르면, 감지 정보(Det\_inf)는 라이트 레벨링 인에이블 신호에 응답하여 적어도 하나 이상의 데이터 버스 라인(DQ)을 통해 메모리 장치(104)로부터 메모리 컨트롤러(102)로 전송되는 업/다운 신호로 구성될 수 있다. 업/다운 신호는 데이터 스트로브 발생부(126)로 입력되고, 제1 지연 신호(delay1)가 데이터 스트로브 발생부(126)에 의해 생성된다. 제1 지연 신호(delay1)는 제어 로직부(124)에 저장되고, 이후에 메모리 시스템의 노 멀 동작시의 라이트 동작 시 이용될 수 있다. 메모리 장치로부터 수신된 감지 정보(Det\_inf)의 처리를 위한 다른 구성도 가능하며, 이에 관하여 동일하게 적용될 수 있다.

[0057]

노멀 모드에서의 동작 동안, 제어 로직부(124)는 클럭 신호(CLK)에 동기시킨 커맨드를 커맨드/어드레스 신호 버스를 통해 출력한다. 출력된 커맨드가 데이터 버스(DQ)를 통한 메모리 컨트롤러로부터의 신호 전송을 포함하는 경우에, 제어 로직부(124)는 신호가 전송될 메모리 장치(104)에 따른 데이터 스트로브 신호(DQS)에 대한 적절한 지연 정도를 결정하고, 데이터 스트로브 발생부(126)로 제2 지연 신호(delay2)를 제공한다. 이와 같은 방법으로 메모리 모듈(106)의 메모리 장치(104)에 라이트할 때마다 적절한 동작을 위해 데이터 스트로브 신호(DQS)의 적절한 지연 정도를 결정한다.

[0058]

데이터 스트로브 발생부(126)는 클럭 발생부(122)로부터 클럭 신호(CLK) 또한 인가받는다. 라이트 레벨링 동작시, 데이터 스트로브 발생부(126)는 데이터 스트로브 신호(예를 들면, 위상 비교를 위해 하나의 펄스를 가지는데이터 스트로브 신호(DQS) 또는 ISI에 의한 신호 왜곡을 방지하기 위한 프리앰블 펄스를 포함하는 두 개 이상의 펄스를 가지는데이터 스트로브 신호(DQS)를 출력한다.데이터 스트로브 발생부(126)는 감지 정보(Det\_inf)도입력한다.이 경우, 감지 정보(Det\_inf)는 상술한 바와 같이업다운 신호일수 있다. 노멀 동작시,데이터스트로브 발생부(126)는 서로 다른 스큐(skew)를 가지는메모리 장치에따라클럭 신호(CLK)에 대한 서로 다른지연시간을 가지는데이터 스트로브 신호(DQS)를 출력한다.데이터 스트로브 신호(DQS)의 지연 정도는라이트 델메모리 장치(104)에따른 제2 지연신호(delay2)에의해 결정된다.

[0059]

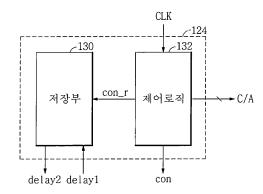

도 7은 도 6에 나타낸 본 발명의 메모리 컨트롤러(102)의 실시예의 제어 로직부(104)의 실시예의 구성을 나타낸 것으로서, 제어 로직부(124)는 저장부(130) 및 제어 로직(132)을 구비하여 구성될 수 있다.

[0060]

라이트 레벨링 동작시, 제어 로직(132)은 클럭 신호(CLK)에 동기시킨 라이트 레벨링 인예이블 신호 및 커맨드 신호(예를 들면, 라이트 커맨드 신호)를 커맨드/어드레스 버스(C/A)를 통해 출력한다. 제어 로직(132)은 데이터 스트로브 발생부(126)를 제어하기 위한 제어 신호(con) 및 저장부(130)를 제어하기 위한 저장부 제어 신호(con\_r)도 출력한다. 라이트 레벨링 동작시, 저장부(130)는 저장부 제어 신호(con\_r)에 응답하여 메모리 장치(104)에 대한 데이터 스트로브 신호(DQS)의 지연 정도를 저장한다. 상기 지연 정도는 제1 지연신호(delay1)에 의해 지시될 수 있다.

[0061]

즉, 라이트 레벨링 동작시, 데이터 스트로브 발생부(126)는 메모리 장치(104)로부터 출력되는 감지 정보(Det\_inf)에 따라 지연 시간을 가변시킨 데이터 스트로브 신호(DQS)를 출력한다. 또한, 데이터 스트로브 발생부(126)는 소정의 시간이 경과한 후, 또는 상기 감지 정보(Det\_inf)에 따라 데이터 스트로브 신호(DQS)와 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))의 위상차가 없거나, 소정의 범위 이내가 되는 상기 데이터 스트로브 신호(DQS)의 지연 시간을 제1 지연 신호(delay1)로 출력하고, 제어 로직부(124)의 저장부(130)는

각 메모리 장치(104)에 대한 상기 제1 지연 신호(delay1)를 저장한다.

노멀 동작시, 제어 로직부(124)의 제어 로직(132)은 클릭 신호(CLK)에 동기시킨 커맨드 신호를 커맨드/어드레스 [0062] 버스(C/A)를 통해 출력한다. 메모리 시스템의 메모리 장치에 라이트 동작을 수행하는 경우에, 제어 로직(132)은 저장부(130)에 저장된 정보를 이용하여 각 메모리 장치(104)에 대한 데이터 스트로브 신호(DQS)의 지연 정도를 나타내는 제2 지연 신호(delay2)를 데이터 스트로브 발생부(126)로 출력한다. 데이터 스트로브 발생부(126)는 상기 제2 지연 신호(delay2)에 응답하여 데이터 스트로브 신호(DQS)의 지연 시간을 결정하여 출력한다. 즉, 라 이트 동작을 수행하는 경우에, 제어 로직(132)은 라이트 동작을 수행하기 위한 제어 신호(con) 및 저장부 제어 신호(con\_r)를 출력하고, 저장부(130)는 상기 라이트 동작을 수행하기 위한 저장부 제어 신호(con\_r)에 응답하 여 라이트할 메모리 장치(104)에 대한 데이터 스트로브 신호(DQS)의 지연 정도를 나타내는 제2 지연 신호 (delay2)를 출력하도록 구성될 수 있으며, 데이터 스트로브 발생부(126)는 상기 라이트 동작을 수행하기 위한 제어 신호(con)에 응답하여 상기 제2 지연 신호(delav2)에 따라 데이터 스트로브 신호(DQS)의 지연 시간을 결정 하여 출력하도록 구성될 수 있다.

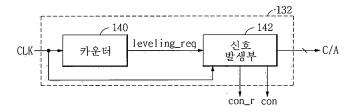

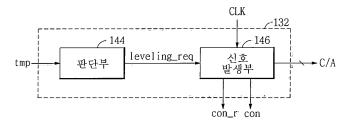

> 도 8a 및 도 8b는 제어 로직부(124)의 제어 로직(132)의 실시예의 구성을 나타내는 것이다. 이 실시예들은 소정 의 시젂(예를 들면, 파워-업 동작시, 또는 딥 파워 다우(deep power down) 모드 동작을 종료할 때)을 제외한 다 른 시점에서 라이트 레벨링 동작을 수행하는 경우의 구성을 나타낸 것이다.

> 도 8a에 나타낸 제어 로직(132)의 제1 실시예는 카운터(140) 및 신호 발생부(142)를 구비하여 구성될 수 있다. 카운터(140)는 클릭 신호(CLK)를 입력하여 주기적으로 활성화되는 레벨링 요구 신호(leveling\_req)를 출력한다. 신호 발생부(142)는 레벨링 요구 신호(leveling\_req)에 응답하여 라이트 레벨링 인에이블 신호(write leveling enable)(즉, 메모리 시스템의 메모리 장치가 라이트 레벨링 동작을 시작하도록 하는 신호)를 출력한다. 또한, 신호 발생부(142)는 클릭 신호에 동기시켜 라이트 커맨드(write command)를 출력하여 라이트 레벨링 동작을 수 행한다.

> 도 8b에 나타낸 제어 로직(132)의 제2 실시예는 판단부(144) 및 신호 발생부(146)를 구비하여 구성될 수 있다. 판단부(144)는 메모리 시스템의 메모리 장치(104) 또는 기타 관련된 다른 장치의 동작 온도를 나타내는 온도 신 호(tmp)를 입력하고, 온도 신호(tmp)에 응답하여 레벨링 요구 신호(leveling\_req)를 출력한다. 온도 신호(tmp) 는 동작 온도가 소정 온도에 도달하면 활성화되는 신호일 수도 있으며, 온도 센서 등에 의해 공급되고 온도에 따라 가변되는 신호일 수도 있다.

신호 발생부(146)는 도 8a에서 설명한 것과 동일하게 동작할 수 있다.

판단부(144)로 입력되는 신호는 온도 신호가 아닌 라이트 레벨링 동작이 필요한지 여부를 판단할 수 있는 다른 신호일 수도 있다. 예를 들면, 판단부(144)는 각 데이터 핀들의 임피던스(ZQ) 정보를 통해 레벨링 요구 신호 (leveling\_req)의 활성화 여부를 판단할 수 있다. 즉, 판단부(144)는 데이터 스트로브 신호들 간의 스큐(skew) 에 영향을 줄 수 있는 인자(factor) 중 하나인 임피던스를 감지하고, 이를 통해 라이트 레벨링을 수행하도록 구 성될 수도 있다. 따라서, 온도와 임피던스 이외의 상술한 스큐에 영향을 줄 수 있는 모든 인자를 감지하고 이를 통해 판단부(144)에서 라이트 레벨링을 요구할 수 있다.

도 8a 및 도 8b에서는 신호 발생부(142, 146)가 메모리 컨트롤러(102)에 배치된 카운터(140) 또는 판단부(144) 로부터 출력되는 레벨링 요구 신호(leveling\_req)에 응답하여 동작하는 경우를 예시하였지만, 신호 발생부(142, 146)는 메모리 장치(104)로부터 출력되는 레벨링 요구 신호에 응답하여 동작할 수도 있다. 즉, 카운터(140) 및/ 또는 판단부(144)는 메모리 컨트롤러(102)에 배치될 수도 있고, 메모리 장치(104)에 배치될 수도 있다. 또한, 신호 발생부(142, 146)는 상술한 바와 같이 파워업 동작시 또는 딥 파워 다운(deep power down) 모드를 종료할 때 메모리 장치(104) 및 메모리 컨트롤러(102)가 라이트 레벨링 동작을 수행하도록 동작할 수도 있다.

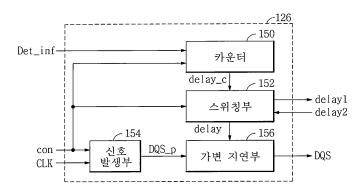

도 9는 도 6에 나타낸 본 발명의 메모리 시스템의 메모리 컨트롤러(102)의 데이터 스트로브 발생부(126)의 실시 예의 구성을 나타내는 것으로서, 데이터 스트로브 발생부(126)는 카운터(150), 스위칭부(152), 신호 발생부 (154), 및 가변 지연부(156)를 구비하여 구성될 수 있다.

신호 발생부(154)는 제어 로직부(124)로부터 출력된 제어 신호(con) 및 클럭 발생부(122)로부터 출력된 클럭 신 호(CLK)를 입력하고, 라이트 레벨링 동작시 또는 노멀 동작 중 라이트 동작시와 같이 제어 신호(con)가 데이터 스트로브 신호의 발생을 요청할 때 제1 데이터 스트로브 신호(DQS\_p)를 발생한다.

라이트 레벨링 동작시, 카운터(150)는 제어 신호(con) 및 감지 정보(Det\_inf)에 응답하여 지연 카운팅 신호 (delav\_c)를 출력한다. 즉, 카운터(150)로부터 출력되는 지연 카운팅 신호(delav\_c)는 메모리 장치(104)로부터

[0071]

[0070]

[0063]

[0064]

[0065]

[0066]

[0067]

[0068]

[0069]

-10 -

출력되는 감지 정보(Det\_inf)에 응답하여 증감할 수 있다. 예를 들면, 감지 정보(Det\_inf)가 메모리 장치(104)에서 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))의 위상이 버퍼드 데이터 스트로브 신호 (PDSD)보다 빠름을 나타내는 동안에는 상기 지연 카운팅 신호(delay\_c)가 증가하도록 구성될 수 있다.

- [0072] 스위칭부(152)는 제어 신호(con)에 응답하여 스위칭 동작을 수행한다. 예를 들면, 스위칭부(152)는 라이트 레벨 링 동작시 제어 신호(con)에 응답하여 상기 지연 카운팅 신호(delay\_c)를 지연 신호(delay) 및 제1 지연 신호 (delay1)로 출력하고, 노멀 모드에서의 동작시 제어 신호(con)에 응답하여 제어 로직부(124)로부터 출력되는 제2 지연 신호(delay2)를 지연 신호(delay)로 출력하도록 구성될 수 있다. 또한, 스위칭부(152)는 제어 신호(con)에 응답하여 라이트 레벨링 동작이 시작되고 소정 시간이 경과한 후, 지연 카운팅 신호(delay\_c)를 제1 지연 신호(delay1)로 출력하도록 구성될 수도 있다.

- [0073] 가변 지연부(156)는 상기 지연 신호(delay)에 응답하여 상기 제1 데이터 스트로브 신호(DQS\_p)를 소정 시간 지연시켜 데이터 스트로브 신호(DQS)로 출력한다.

- [0074] 도 10은 본 발명의 메모리 시스템(100)의 메모리 컨트롤러(102)의 다른 실시예의 구성을 나타낸 것으로서, 메모리 컨트롤러(102)는 클럭 발생부(122), 제어 로직부(125), 및 데이터 스트로브 발생부(127)를 구비하여 구성될 수 있다.

- [0075] 클럭 발생부(122)는 라이트 레벨링 동작 또는 노멀 동작 시 커맨드/어드레스 신호 버스(C/A)를 따라 하나 또는 그 이상의 메모리 장치(104)로 전송되는 클럭 신호(CLK)를 발생한다.

- [0076] 제어 로직부(125)는 클럭 발생부(122)로부터 클럭 신호(CLK)를 수신한다. 라이트 레벨링 동작시, 제어 로직부 (124)는 커맨드/어드레스 신호 버스(C/A)를 통하여 클럭 신호(CLK)에 동기시킨 커맨드 신호(예를 들면, 라이트 커맨드 신호) 및 라이트 레벨링 제어 신호(예를 들면, 라이트 레벨링 인에이블 신호)를 출력한다. 또한, 라이트 레벨링 동작의 시작에 응답하여, 제어 로직부(125)는 메모리 장치(104)에서 수신한 상기 커맨드 신호(예를 들면, 라이트 커맨드 신호) 및 데이터 스트로브 신호의 위상차를 나타내는 감지 정보(Det\_inf)를 수신한다. 감지 정보(Det\_inf)는 이후의 사용을 위해 제어 로직부(125)에 저장된다. 또한, 제어 로직부(125)는 데이터 스트로브 발생부(127)를 제어하기 위한 제어 신호(con) 및 데이터 스트로브 신호(DQS)의 타이밍을 조절하기 위한 지연 신호(delay)를 출력한다.

[0077]

[0078]

[0079]

- 데이터 스트로브 발생부(127)는 제어 로직부(124)로부터 출력되는 제어 신호(con) 및 클럭 발생부(122)로부터 출력되는 클럭 신호(CLK)에 응답하여 데이터 스트로브 신호(DQS)를 출력한다. 또한, 데이터 스트로브 발생부(127)는 노멀 모드에서 라이트 동작시 제어 로직부(124)로부터 출력되는 지연 신호(delay)에 따라 상기 클럭 신호(CLK)에 대한 데이터 스트로브 신호(DQS)의 지연 시간을 조절하여 출력한다.

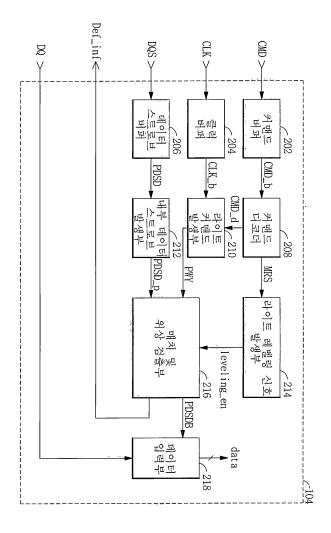

- 도 11은 본 발명의 메모리 장치(104)의 실시예의 구성을 나타내는 것으로서, 메모리 장치(104)는 커맨드 버퍼(202), 클럭 버퍼(204), 데이터 스트로브 버퍼(206), 커맨드 디코더(208), 라이트 커맨드 발생부(210), 내부 데이터 스트로브 발생부(212), 라이트 레벨링 신호 발생부(214), 매치 및 위상 검출부(216), 및 데이터 입력부(218)를 구비하여 구성될 수 있다. 커맨드 신호(CMD), 클럭 신호(CLK) 및 데이터 스트로브 신호(DQS)는 도 1 내지 도 10에 나타낸 메모리 컨트롤러(102)로부터 발생될 수 있다.

- 커맨드 버퍼(202)는 메모리 컨트롤러(102)로부터 출력되는 커맨드/어드레스 신호(C/A) 중 커맨드(CMD)를 수신한다. 커맨드 버퍼(202)는 예를 들면, 버퍼 및 래치 등을 구비하여 구성될 수 있다. 커맨드 버퍼(202)로부터 출력되는 버퍼드(buffered) 커맨드 신호(CMD\_b)는 커맨드 디코더(208) 등에 의해 처리되어 디코디드(decoded) 커맨드 신호(CMD\_d) 및/또는 모드 레지스터 설정(MRS)을 생성한다. 모드 레지스터 설정(MRS)은 라이트 레벨링 동작이 수행될 때 레벨링 인에이블 신호(leveling\_en)를 활성화시키는 라이트 레벨링 신호 발생부(214)로 제공된다.

- [0080] 클럭 버퍼(204)는 메모리 컨트롤러(102)로부터 출력되는 클럭 신호(CLK)를 수신한다. 클럭 버퍼(204)는 커맨드 버퍼(202)의 래치에 의해 발생되는 지연 정도를 클럭 버퍼(204)를 통해 전송되는 클럭 신호(CLK)에 적용하는 클럭 리피터를 구비하여 구성될 수 있다. 클럭 버퍼(204)로부터 출력되는 버퍼드 클럭 신호(CLK\_b)는 라이트 커맨드 발생부(210)로 인가된다.

- [0081] 라이트 커맨드 발생부(210)는 디코디드 커맨드 신호(CMD\_d)에 의한 버퍼드 클릭 신호(CLK\_b)의 샘플링에 응답하여 내부 라이트 커맨드 신호(PWY)를 출력한다.

- [0082] 내부 라이트 커맨드 신호(PWY)는 라이트 레이턴시(write latency)에 따라 소정의 클럭 수만큼 지연된 신호이다. 따라서, 내부 라이트 커맨드 신호(PWY)의 지연 특성은 라이트 레이턴시에 따라 프로그램된다. 라이트 커맨드 신

호가 인가되면, 라이트 커맨드 발생부(210)는 디코디드 커맨드 신호(CMD\_d)에 따라 버퍼드 클럭 신호(CLK\_b)를 샘플링한다. 상기 동작의 샘플링 결과가 내부 라이트 커맨드 신호(PWY) 발생 과정이다.

- [0083] 또한, 내부 라이트 커맨드 신호(PWY)의 펄스폭은 라이트 커맨드 발생부(210)에 의해 클럭 신호(CLK)의 주기의 n 배(n은 1이상의 정수)에 대응하는 펄스폭까지 늘어난다.

- [0084] 라이트 레벨링 동작시, 메모리 장치(104)마다 하나의 펄스를 가지는 내부 라이트 커맨드 신호(PWY)가 인가되면 충분하지만, 심벌간 간섭 (ISI: inter symbol interference)에 의한 왜곡을 방지하기 위해 적어도 하나의 더미 (dummy) 펄스(또는 프리앰블(preamble) 펄스)를 추가할 수도 있다.

- [0085] 데이터 스트로브 버퍼(206)는 데이터 스트로브 신호(DQS)를 버퍼하고 지연하여 버퍼드 데이터 스트로브 신호 (PDSD)를 발생시킨다. 내부 데이터 스트로브 발생부(212)는 버퍼드 데이터 스트로브 신호(PDSD)에 응답하여 내부 데이터 스트로브 신호(PDSD\_p)를 발생시킨다.

- [0086] 매치 및 위상 검출부(216)는 레벨링 인에이블 신호(leveling\_en), 내부 라이트 커맨드 신호(PWY), 및 내부 데이터 스트로브 신호(PDSD\_p)를 입력한다. 매치 및 위상 검출부(216)는 레벨링 인에이블 신호(leveling\_en)의 상태에 따라 라이트 레벨링 동작 여부를 판단하고, 라이트 레벨링 동작시, 내부 라이트 커맨드 신호(PWY)와 내부 데이터 스트로브 신호(PDSD\_p)의 위상차를 검출하여 상기 위상차를 나타내는 감지 정보(Det\_inf)를 발생한다. 상술한 바와 같이, 감지 정보(Det\_inf)는 데이터 버스(DQ) 또는 추가적으로 분리된 전용의 신호 라인을 통하여 메모리 컨트롤러(102)에 제공될 수 있다. 상술한 바와 같이, 감지 정보(Det\_inf)는 내부 라이트 커맨드 신호(PWY)와 내부 데이터 스트로브 신호(PDSD\_p)의 위상차를 나타내는 신호이며, 내부 라이트 커맨드 신호(PWY)는 메모리 장치(104)에 수신된 클럭 신호(CLK)에 동기된 라이트 커맨드 신호를 기초로 발생되며, 내부 데이터 스트로브 신호(PDSD\_p)는 메모리 장치(104)에 수신된 데이터 스트로브 신호(DQS)를 기초로 발생된다. 따라서, 감지 정보 (Det\_inf)는 메모리 장치(104)가 수신한 클럭 신호(CLK)와 메모리 장치(104)가 수신한 데이터 스트로브 신호(DQS)의 위상차에 대한 정보를 표시한다.

- [0087] 상기에서는 매치 및 위상 검출부(216)가 내부 라이트 커맨드 신호(PWY)와 내부 데이터 스트로브 신호(PDSD\_p)의 위상차를 비교하는 것을 예를 들어 설명하였으나, 내부 라이트 커맨드 신호(PWY) 내신 리드(Read), 프리차지 (Precharge), 리프레쉬(Refresh) 등 다른 내부 커맨드 신호를 이용할 수도 있다. 또한, 매치 및 위상 검출부 (216)는 내부 데이터 스트로브 신호(PDSD\_p) 대신 버퍼드 데이터 스트로브 신호(PDSD)를 이용할 수도 있다.

- [0088] 노멀 모드에서의 동작시(예를 들면, 노멀 모드에서 라이트 동작시), 매치 및 위상 검출부(216)는 데이터 스트로 브 신호(DQS) 도메인(domain)을 클럭 신호 도메인에 매치시키고, 클럭 데이터 스트로브 신호(PDSDB)를 발생시킨다. 데이터 입력부(216)는 클럭 데이터 스트로브 신호(PDSDB)에 응답하여 데이터 버스(DQ)를 통해 수신되는 메모리 셀에 라이트하기 위한 데이터를 입력하여 출력한다.

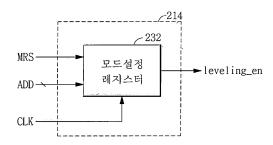

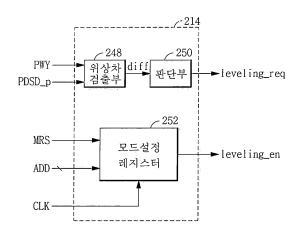

- [0089] 도 12a, 도 12b, 도 12c, 및 도 12d 각각은 도 11에 나타낸 본 발명의 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 실시예들의 구성을 나타내는 것으로서, 도 12a는 메모리 컨트롤러(102)에서 라이트 레벨링 동작의 시작 시점을 결정하는 경우의 라이트 레벨링 신호 발생부(214)의 실시예의 구성을, 도 12b 내지 도 12d는 메모리 장치(104)에서 라이트 레벨링 동작의 시작 시점을 결정하는 경우의 라이트 레벨링 신호 발생부(214)의 실시예의 구성을 각각 나타내는 것이다.

- [0090] 도 12a에 나타낸 본 발명의 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 제1 실시예는 모드 설정 레지스터(232)를 구비하여 구성될 수 있다.

- [0091] 모드 설정 레지스터(232)는 모드 레지스터 설정(MRS)에 응답하여 어드레스 신호(ADD)를 입력하여 설정되고, 설정된 값에 따라 레벨링 인에이블 신호(leveling\_en)를 출력한다. 즉, 메모리 컨트롤러(102)는 라이트 레벨링 동작시 모드 설정 레지스터(232)를 설정하기 위한 커맨드 및 어드레스 신호 라인을 통해 소정의 신호를 출력하도록 구성될 수 있으며, 메모리 장치(104)의 커맨드 디코더(208)는 상기 커맨드를 디코딩하여 모드 레지스터 설정(MRS)을 출력하고, 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 모드 설정 레지스터(232)는 상기 모드 레지스터 설정(MRS)에 응답하여 어드레스 신호 라인을 통해 입력되는 신호를 입력하여 저장된 값이설정되며, 설정된 값에 따라 라이트 레벨링 동작을 수행하기 위해 레벨링 인에이블 신호(leveling\_en)를 출력하도록 구성될 수 있다.

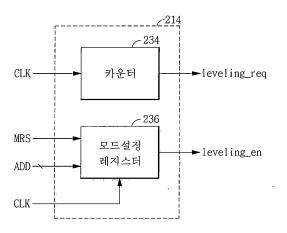

- [0092] 도 12b에 나타낸 본 발명의 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 제2 실시예는 카운터(234) 및 모드 설정 레지스터(236)를 구비하여 구성될 수 있다.

- [0093]

- 카운터(234)는 클럭 신호(CLK)(또는 버퍼드 클럭 신호(CLK\_b))를 카운팅하여 주기적으로 활성화되는 레벨링 요구 신호(leveling\_req)를 발생시킨다. 모드 설정 레지스터(236)의 기능은 도 12a에서 설명한 모드 설정 레지스터(232)의 기능과 동일하다. 즉, 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 카운터(234)에서 주기적으로 레벨링 요구 신호(leveling\_req)를 출력할 수 있으며, 메모리 컨트롤러(104)의 제어 로직부(124 또는 125)는 상기 레벨링 요구 신호(leveling\_req)에 응답하여 라이트 레벨링 동작을 수행하기 위해 모드 설정 레지스터(236)를 설정하기 위한 커맨드, 및 어드레스 신호 라인을 통해 소정의 신호를 출력하도록 구성될 수 있다.

- [0094]

- 도 12c에 나타낸 본 발명의 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 제3 실시예는 온도 감지부 (240), 판단부(242) 및 모드 설정 레지스터(246)를 구비하여 구성될 수 있다.

- [0095]

- 온도 감지부(240)는 메모리 장치(104)의 동작 온도를 나타내는 온도 신호(tmp)를 출력한다. 판단부(242)는 상기 온도 신호(tmp)에 응답하여 레벨링 요구 신호(leveling\_req)를 출력한다. 모드 설정 레지스터(246)의 기능은 도 12a에서 설명한 모드 설정 레지스터(232)의 기능과 동일하다. 예를 들면, 판단부(242)는 상기 온도 신호(tmp)를 입력하여 메모리 장치(104)의 동작 온도가 소정 온도에 도달하게 되면 레벨링 요구 신호(leveling\_req)를 출력하도록 구성될 수 있다. 이 경우에, 상술한 바와 같이, 메모리 컨트롤러(104)는 상기 레벨링 요구 신호(leveling\_req)에 응답하여 모드 설정 레지스터(246)를 설정하기 위한 커맨드 및 어드레스 신호를 출력하고, 모드 설정 레지스터(246)는 상기 커맨드 및 어드레스 신호에 응답하여 레벨링 인에이블 신호(leveling\_en)를 출력하도록 구성될 수 있다.

- [0096]

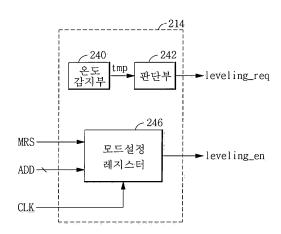

- 도 12d에 나타낸 본 발명의 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 제4 실시예는 위상차 검출부 (248), 판단부(250), 및 모드 설정 레지스터(252)를 구비하여 구성될 수 있다.

- [0097]

- 위상차 검출부(248)는 내부 라이트 커맨드 신호(PWY)와 내부 데이터 스트로브 신호(PDSD\_p)의 위상차를 검출하여 검출된 위상차(diff)를 출력한다. 판단부(250)는 상기 위상차(diff)에 응답하여 레벨링 요구 신호(leveling\_req)를 출력한다. 모드 설정 레지스터(252)의 기능은 도 12a에서 설명한 모드 설정 레지스터(232)의 기능과 동일하다. 예를 들면, 판단부(250)는 위상차 검출부(248)에서 검출하여 출력되는 내부 라이트 커맨드 신호(PWY)와 내부 데이터 스트로브 신호(PDSD\_p)의 위상차(diff)가 소정의 문턱값 이상이 되면 레벨링 요구 신호(leveling\_req)를 활성화시켜 출력하도록 구성될 수 있다. 이 경우에, 상술한 바와 같이, 메모리 컨트롤러(104)는 상기 레벨링 요구 신호(leveling\_req)에 응답하여 모드 설정 레지스터(252)를 설정하기 위한 커맨드 및 어드레스 신호를 출력하고, 모드 설정 레지스터(252)는 상기 커맨드 및 어드레스 신호에 응답하여 레벨링 인에이 블 신호(leveling\_en)를 출력하도록 구성될 수 있다.

- [0098]

- 또한, 상술한 바와 같이, 라이트 레벨링 동작은 파워업 동작시 또는 딥 파워 다운(deep power down) 모드를 종료할 때 수행될 수 있다. 따라서, 라이트 레벨링 신호 발생부(214)는 파워업 동작시 및/또는 딥 파워 다운(deep power down) 모드를 종료할 때 상기 레벨링 요구 신호(leveling\_req)를 출력하도록 구성될 수도 있다.

- [0099]

- 또한, 라이트 레벨링 신호 발생부(214)는 메모리 장치의 데이터 핀의 임피던스 정보(ZQ)의 변화를 감지하여 상기 레벨링 요구 신호(leveling\_req)를 출력하도록 구성될 수도 있다.

- [0100]

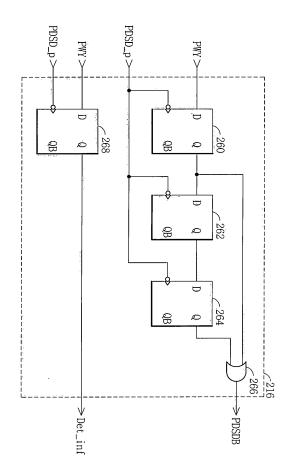

- 도 13은 도 11에 나타낸 본 발명의 메모리 장치(104)의 매치 및 위상 검출부(216)의 실시예의 구성을 나타낸 것으로서, 매치 및 위상 검출부(216)는 래치(D 플립플롭)들(260, 262, 264), OR 게이트(266), 및 위상 검출기(268)를 구비하여 구성될 수 있으며, 위상 검출기(268)는 래치(D 플립플롭)를 구비하여 구성될 수 있다.

- [0101]

- 래치들(260, 262, 264) 및 OR 게이트(266)는 내부 라이트 커맨드 신호(PWY) 및 내부 데이터 스트로브 신호 (PDSD\_p)에 응답하여 클럭 데이터 스트로브 신호(PDSDB)를 출력한다. 래치(260)는 내부 데이터 스트로브 신호 (PDSD\_p)에 응답하여 내부 라이트 커맨드 신호(PWY)를 래치하여 출력한다. 래치들(262, 264)은 래치(260)와 직렬로 연결되고, 각각 내부 데이터 스트로브 신호(PDSD\_p)에 응답하여 입력되는 전단의 래치의 출력 신호를 래치하여 출력한다. OR 게이트(266)는 래치(260) 및 래치들(262, 264)의 출력 신호(즉, 래치(264)의 출력 신호)를 논리합 연산하여 클럭 데이터 스트로브 신호(PDSDB)를 출력한다.

- [0102]

- 위상 검출기(268)는 내부 데이터 스트로브 신호(PDSD\_p)에 응답하여 내부 라이트 커맨드 신호(PWY)를 래치하여 감지 정보(Det\_inf)를 출력한다. 이때, 감지 정보(Det\_inf)는 내부 데이터 스트로브 신호(PDSD\_p)의 위상이 내부 라이트 커맨드 신호(PWY)의 위상보다 빠른지 느린지 여부를 표시한다.

- [0103]

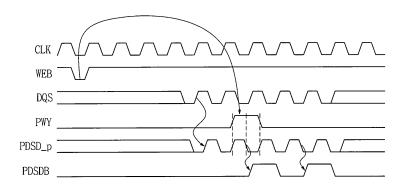

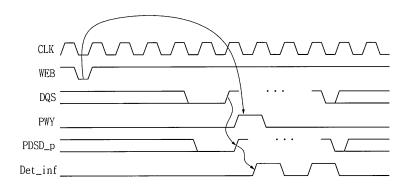

- 도 14a 및 도 14b는 도 11에 나타낸 본 발명의 메모리 장치(104)의 동작을 설명하기 위한 동작 타이밍도를 나타낸 것으로서, 노멀 모드에서의 라이트 동작시 및 라이트 레벨링 동작시의 동작을 각각 설명하기 위한 동작 타이

밍도이다. 도 14a 및 도 14b에서, CLK는 메모리 컨트롤러(102)로부터 메모리 장치(104)로 출력되는 클럭 신호를, WEB는 메모리 컨트롤러(102)로부터 메모리 장치(104)로 출력되는 라이트 인에이블 신호를, DQS는 메모리 컨트롤러(102)로부터 메모리 장치(104)로 출력되는 데이터 스트로브 신호를, PWY는 메모리 장치(104) 내부에서 발생되는 내부 라이트 커맨드 신호를, PDSD\_p는 메모리 장치(104) 내부에서 발생되는 내부 데이터 스트로브 신호를, PDSDB는 메모리 장치(104) 내부에서 발생되는 클럭 데이터 스트로브 신호를, Det\_inf는 메모리 장치(104)로부터 메모리 컨트롤러(102)로 출력되는 감지 정보를 각각 나타낸다.

- [0104]

- 도 13 및 도 14a를 참조하면, 노멀 모드에서의 동작시(예를 들면, 메모리 컨트롤러(102)로부터 라이트 인에이블 신호(WEB) 등의 라이트 커맨드가 출력되어 라이트 동작이 수행될 때), 메모리 장치(104)는 라이트 인에이블 신호(WEB), 클럭 신호(CLK) 및 데이터 스트로브 신호(DOS)를 수신한다.

- [0105]

- 커맨드 디코더(208)는 라이트 인에이블 신호(WEB)를 포함하는 커맨드 신호(CMD)를 디코딩하여 디코디드 커맨드 신호(CMD)를 출력하고, 라이트 커맨드 발생부(210)는 상기 디코디드 커맨드 신호(CMD)에 응답하여 버퍼드 클럭 신호(CLK\_b)를 샘플링하여 내부 라이트 커맨드 신호(PWY)를 발생한다. 즉, 라이트 인에이블 신호(WEB)에 응답하여 내부 라이트 커맨드 신호(PWY)가 발생된다. 동시에, 데이터 스트로브 신호(DQS)에 응답하여 내부 데이터 스트로브 신호(PDSD\_p)가 발생된다.

- [0106]

- 도 13을 참조하면, 내부 라이트 커맨드 신호(PWY)는 내부 데이터 스트로브 신호(PDSD\_p)의 폴링 에지(falling edge)에 응답하여 래치된다. 따라서, 클럭 데이터 스트로브 신호(PDSDB)는 내부 라이트 커맨드 신호(PWY)의 중 앙에 정렬된다.

- [0107]

- 상술한 바와 같이, 클럭 데이터 스트로브 신호(PDSDB)는 데이터 입력부(218)가 데이터 신호를 입력하는데 이용된다. 도면에서는, 라이트 레이턴시가 5인 경우를 예시하였으며, 따라서, 라이트 인에이블 신호(WEB)와 활성화시점과 내부 라이트 커맨드 신호(PWY)의 활성화시점 사이의 지연 시간차가 5개의 클럭 주기에 대응한다.

- [0108]

- 도 13 및 도 14b를 참조하면, 라이트 레벨링 동작시, 메모리 장치(104)는 노멀 모드에서의 동작시와 동일하게라이트 인에이블 신호(WEB), 클럭 신호(CLK) 및 데이터 스트로브 신호(DQS)를 수신하여 내부 라이트 커맨드 신호(PWY) 및 내부 데이터 스트로브 신호(PDSD\_p)를 발생한다. 즉, 라이트 레벨링 동작시, 메모리 장치(104)에서 수신된 클럭 신호(CLK)와 데이터 스트로브 신호(DQS)의 위상차를 감지하이 위한 내부 라이트 커맨드 신호(PWY) 및 내부 데이터 스트로브 신호(PDSD\_p)는 노멀 모드에서의 동작시와 동일한 경로를 통하여 발생된다.

- [0109]

- 도 13을 참조하면, 내부 라이트 커맨드 신호(PWY) 및 내부 데이터 스트로브 신호(PDSD\_p)는 위상 검출기(268) (예를 들면, 래치)로 인가되고, 위상 검출기(268)의 출력 신호는 내부 라이트 커맨드 신호(PWY)와 내부 데이터 스트로브 신호(PDSD\_p)의 위상차를 나타내는 감지 정보(Det\_inf)가 된다. 즉, 감지 정보(Det\_inf)가 로우 레벨이면 내부 데이터 스트로브 신호(PDSD\_p)의 위상이 내부 라이트 커맨드 신호(PWY)의 위상보다 빠르다는 것을 나타낸다.

- [0110]

- 상술한 바와 같이, 감지 정보(Det\_inf)는 메모리 컨트롤러(102)로 제공되어 각 메모리 장치(104)에서 수신된 클릭 신호(CLK)와 데이터 스트로브 신호(DQS)의 위상차를 알려준다. 따라서, 메모리 컨트롤러(104)는 각 메모리 장치(104)에 대하여 데이터 스트로브 신호(DQS)의 타이밍을 적절하게 조절할 수 있다.

- [0111]

- 본 발명에 따르면, 라이트 레벨링 동작시 출력되는 감지 정보(Det\_inf)는 라이트 동작과 같은 노멀 모드에서의 동작 시와 동일한 신호 경로를 통하여 발생된 신호를 이용하여 발생된다. 따라서, 감지 정보(Det\_inf)를 발생하기 위한 별도의 복제 경로(replica path)가 필요없으며, 복제 경로(replica path)와 실제 노멀 모드에서의 동작시의 경로 사이의 불일치로 인한 오차를 제거할 수 있어 보다 정확한 결과를 얻을 수 있다.

- [0112]

- 또한, 본 발명에 따르면, 라이트 레벨랑을 위한 위상 비교는 메모리 컨트롤러(102)로부터 수신한 라이트 인에이 블 신호(WEB)를 포함하는 라이트 커맨드 신호로부터 생성되는 내부 라이트 커맨드 신호(PWY)와 메모리 컨트롤러(102)로부터 수신한 데이터 스트로브 신호(DQS)로부터 생성되는 내부 데이터 스트로브 신호(PDSD\_p) 사이에서 이루어진다. 라이트 인에이블 신호(WEB)는 클럭 신호(CLK)에 동기되어 출력되고, 내부 라이트 커맨드 신호(PWY)는 수신된 클럭 신호(CLK)에 동기되어 발생된다. 따라서, 내부 라이트 커맨드 신호(PWY)는 수신된 클럭 신호(CLK)와 동일한 타이밍 특성을 가진다. 그런데, 내부 라이트 커맨드 신호(PWY)는 클럭 신호(CLK)와 같이 지속적으로 토글링될 필요가 없다. 따라서, 내부 라이트 커맨드 신호(PWY)의 필스폭은 클럭 신호의 주기의 n(n은 1이상의 정수)배 만큼 증가될 수 있다. 따라서, 클럭 신호(CLK)에 대한 데이터 스트로브 신호(DQS)의 타이밍을 적절하게 조절할 수 있는 마진을 증가시킬 수 있다.

- [0113]

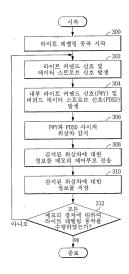

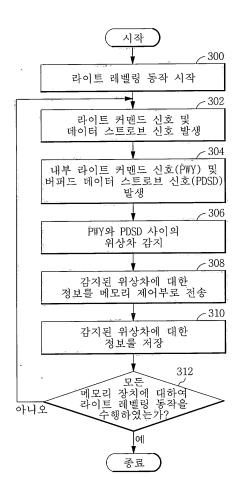

- 도 15는 본 발명의 라이트 레벨링 수행 방법의 실시예를 설명하기 위한 동작 흐름도를 나타낸 것이다. 300단계

에서, 모드 레지스터 설정 동작이 시작되어 메모리 컨트롤러(102)는 메모리 컨트롤러(102)와 연결된 메모리 장치(104)의 형태를 판단할 수 있으며, 라이트 레벨링 동작이 시작될 수 있다. 상술한 바와 같이, 라이트 레벨링 동작은 파워 업 동작시, 메모리 시스템(100)이 딥 파워 다운(deep power down) 모드를 종료할 때, 주기적으로, 또는 온도나 위상차, 또는 임피던스의 변화가 감지되었을 때 시작될 수 있으며, 메모리 컨트롤러(102)에 의해 시작될 수도 있고, 메모리 장치(104)에 의해 시작될 수도 있다.

- [0114] 302단계에서, 메모리 컨트롤러(102)는 라이트 레벨링 동작을 수행하기 위한 커맨드 신호(예를 들면, 라이트 커맨드 신호) 및 데이터 스트로브 신호(DQS)를 출력한다.

- [0115] 304단계에서, 메모리 장치(104)는 상기 커맨드 신호(예를 들면, 라이트 커맨드 신호) 및 데이터 스트로브 신호 (DQS)를 수신하여 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY)) 및 내부 데이터 스트로브 신호 (PDSD\_p)를 발생시킨다. 이때, 내부 커맨드 신호 및 내부 데이터 스트로브 신호는 노멀 모드에서의 동작 시와 동일한 경로를 통하여 발생된다. 또한, 내부 커맨드 신호의 펄스폭은 클릭 신호(CLK)의 주기의 n배(n은 1이상의 정수)에 대응하는 펄스폭을 가질 수 있다.

- [0116] 306단계에서, 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))와 내부 데이터 스트로브 신호 (PDSD\_p)의 위상차가 메모리 장치에서 감지된다.

- [0117] 308단계에서, 감지된 위상차를 나타내는 감지 정보(Det\_inf)가 메모리 장치(104)로부터 메모리 컨트롤러(102)로 전송된다. 이때, 감지 정보(Det\_inf)는 내부 데이터 스트로브 신호(PDSD\_p)의 위상이 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))의 위상보다 빠른지 느린지를 나타내는 신호일 수 있다.

- [0118] 310단계에서, 감지 정보(Det\_inf)에 기초하여, 각 메모리 장치(104)에 대한 위상차에 대한 정보가 메모리 컨트롤러(102)에 저장된다. 상기 저장된 정보는 클럭 신호 및/또는 커맨드 신호(예를 들면, 라이트 커맨드)에 대한데이터 스트로브 신호(DQS)의 타이밍을 조절하는데 이용된다. 즉, 감지 정보(Det\_inf)는 내부 데이터 스트로브 신호(PDSD\_p)의 위상이 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호(PWY))의 위상보다 빠른지 느린지를 나타내는 신호일 수 있다. 또한, 메모리 컨트롤러(102)는 라이트 레벨링 동작시 상기 감지 정보(Det\_inf)에 응답하여 출력되는 데이터 스트로브 신호(DQS)의 지연 시간을 조절하고, 소정 시간 경과후, 또는 감지 정보(Det\_inf)의 상태가 바뀌었을 때의 상기 데이터 스트로브 신호(DQS)의 지연 시간을 해당하는 메모리 장치(104)에 대한 데이터 스트로브 신호(DQS) 발생 타이밍 정보로서 저장하도록 구성될 수 있다.

[0119]

- 312단계에서, 메모리 컨트롤러(102)와 연결된 모든 메모리 장치들(104)에 대하여 라이트 레벨링 동작을 수행하였는지를 판단하여 모든 메모리 장치들(104) 각각에 대하여 상기 과정을 반복한다. 메모리 컨트롤러(102)는 각메모리 장치(104)에 대하여 소정 시간동안 상기 과정을 수행할 수도 있으며, 감지 정보(Det\_inf)를 이용하여 위상차가 소정의 범위 이내가 될 때까지 또는 감지 정보(Det\_inf)가 표시하는 위상차에 대한 정보가 변경될 때까지 상기 과정을 수행하도록 구성될 수도 있다. 312단계에서 판단한 결과, 모든 메모리 장치들(104)에 대하여 라이트 레벨링 동작을 완료하였으면 라이트 레벨링 동작을 종료하고 노멀 모드로 전환될 수 있다.

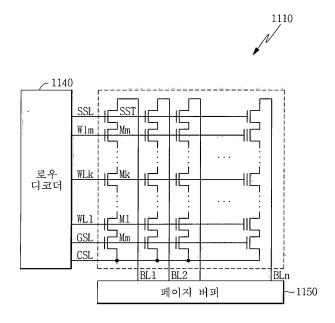

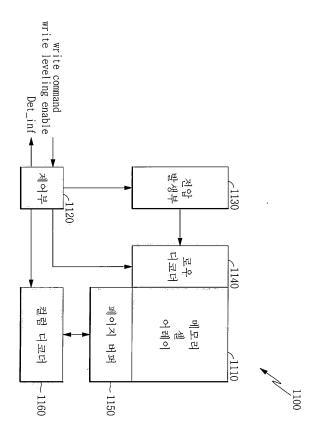

- [0120] 도 16a는 본 발명의 메모리 장치의 실시예의 구성을 나타내는 것으로서, 메모리 장치(1100)는 메모리 셀 어레이 (1110), 제어부(1120), 전압 발생부(1130), 로우 디코더(1140), 페이지 버퍼(1150), 및 컬럼 디코더(1160)를 구비하여 구성될 수 있다.

- [0121] 메모리 셀 어레이(1110)는 선택적으로 메모리 블록에 배치된 복수개의 메모리 셀 스트링들을 구비하여 구성될 수 있다. 제어부(1120)는 수행될 동작(예를 들면, 소거, 프로그램, 및 리드 동작)에 따라 제어 신호들을 전압 발생부(1130), 로우 디코더(1140), 및 컬럼 디코더(1160)로 출력한다. 전압 발생부(1130)는 패스 전압(Vpass), 리드 전압(Vread), 소거 전압(Verase), 스텝 전압(Vstep) 등과 같은 메모리 장치의 동작을 수행하는데 필요한 전압들을 발생시킨다. 로우 디코더(1140)는 메모리 셀 어레이(1110)의 스트링 선택 라인(SSL), 워드 라인(WLk), 접지 선택 라인(GSL), 및 공통 소스 라인(SSL) 등과 같은 라인들에 전압 발생부(1130)에서 발생된 전압들을 어떻게 인가할 것인지를 결정한다. 컬럼 디코더(1160)는 메모리 셀 어레이(1110)의 어떤 비트 라인들(BLn)의 신호들이 페이지 버퍼(1150)에 의해 리드되는지를 판단하거나, 프로그래밍 또는 소거 동작시 비트 라인들(BLn)로 인가되는 전압을 결정한다.

- [0122] 또한, 제어부(1120)는 라이트 레벨링 동작시 메모리 컨트롤러로부터 커맨드 신호(예를 들면, 라이트 커맨드 신호), 라이트 레벨링 인에이블 신호, 및 데이터 스트로브 신호 등을 수신하여 상기 커맨드 신호 및 클럭 신호에 응답하여 내부적으로 발생된 내부 커맨드 신호(예를 들면, 내부 라이트 커맨드 신호)와 상기 데이터 스트로브 신호에 응답하여 내부적으로 발생된 내부 데이터 스트로브 신호의 위상차를 검출하여 검출된 위상차에 대한 정

보를 나타내는 감지 정보(Det\_inf)를 메모리 컨트롤러로 출력한다. 라이트 레벨링 동작시 발생되는 내부 커맨드 신호 및 내부 데이터 스트로브 신호는 노멀 모드에서의 동작시와 동일한 경로를 통하여 발생되며, 상기 내부 커 맨드 신호는 클럭 신호의 주기의 n(n은 1이상의 정수)배에 대응하는 펄스폭을 가지는 펄스 신호일 수 있다.

- [0123] 도 16b는 도 16a에 나타낸 본 발명의 메모리 장치의 실시예의 메모리 셀 어레이(1110)의 실시예의 구성을 나타내는 것이다. 로우 디코더(1140)는 적어도 하나 이상의 스트링 선택 라인(SSL), 워드 라인(WLk), 접지 선택 라인(GSL), 및 공통 소스 라인(CSL)으로 다양한 전압을 인가한다. 페이지 버퍼(1150)는 메모리 셀 스트링의 비트라인(BLn)과 연결된다.

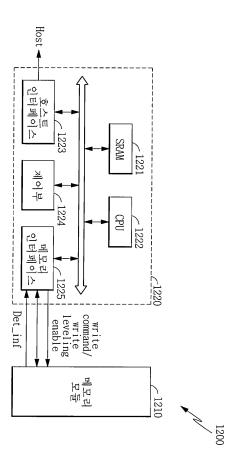

- [0124] 도 17은 본 발명의 실시예에 따른 메모리 장치를 구비하는 메모리 카드의 실시예의 구성을 나타내는 것이다. 메모리 카드(1200)는 커맨드 및 어드레스 신호(C/A)를 발생하는 메모리 컨트롤러(1220) 및 메모리 모듈(1210)을 구비하여 구성될 수 있다. 메모리 모듈(1210)은 복수개의 플래시 메모리 장치를 구비하는 플래시 메모리로 구성될 수 있다. 메모리 컨트롤러(1220)는 호스트로/로부터 커맨드 및 어드레스 신호를 송신/수신하는 호스트 인터페이스(1223), 및 메모리 모듈(1210)로/로부터 커맨드 및 어드레스 신호를 송신/수신하는 메모리 인터페이스(1225)를 구비하여 구성될 수 있다. 호스트 인터페이스(1223), 제어부(1224), 및 메모리 인터페이스(1225)는 컨트롤러 메모리(SRAM)(1221) 및 프로세서(CPU)(1222)와 공통 버스를 통하여 통신하다.

- [0125] 또한, 메모리 컨트롤러(1220)의 제어부(1224)는 라이트 레벨링 동작시, 메모리 인터페이스(1225)를 통하여 메모리 모듈(1210)의 복수개의 플래시 메모리 장치 중 적어도 하나의 플래시 메모리 장치로 라이트 레벨링 동작을 위한 커맨드 신호, 라이트 레벨링 제어 신호, 및 데이터 스트로브 신호를 출력하고, 상기 적어도 하나의 플래시 메모리 장치는 상기 커맨드 신호 및 클럭 신호에 응답하여 노멀 모드에서의 동작시와 동일한 경로를 통하여 내부 커맨드 신호를 발생하고, 상기 데이터 스트로브 신호에 응답하여 노멀 모드에서의 동작시와 동일한 경로를 통하여 내부 데이터 스트로브 신호를 발생하고, 상기 내부 커맨드 신호 및 내부 데이터 스트로브 신호의 위상차를 감지하여 감지된 위상차를 나타내는 감지 정보를 메모리 인터페이스(1225)를 통하여 메모리 컨트롤러(1220)의 제어부(1224)로 출력하고, 메모리 컨트롤러(1220)의 제어부(1224)는 상기 감지 정보를 저장하여 이후에 데이터 스트로브 신호의 출력 타이밍을 조절하는데 이용한다.

- [0126] 메모리 모듈(1210)은 메모리 컨트롤러(1220)로부터 커맨드 및 어드레스 신호(C/A)를 수신하고, 커맨드 및 어드레스 신호(C/A)에 응답하여 데이터를 메모리 모듈(1210)의 적어도 하나의 메모리 장치에/로부터 저장하거나 리드한다. 각 메모리 장치는 복수개의 메모리 셀들 및 상기 커맨드 및 어드레스 신호를 수신하고, 프로그래밍 및리드 동작시 적어도 하나의 메모리 셀을 억세스하기 위해 로우 신호 및 컬럼 신호를 발생하는 디코더를 구비한다.

- [0127] 메모리 컨트롤러(1220) 및 회로들(1221, 1222, 1223, 1224, 및 1225)을 포함하는 메모리 카드(1200)의 구성요 소들은 메모리 컨트롤러(1220)에 포함될 수 있으며, 메모리 모듈(1210)은 상술한 개념에 따라 프로그래밍되는 메모리 장치를 구비할 수 있다.

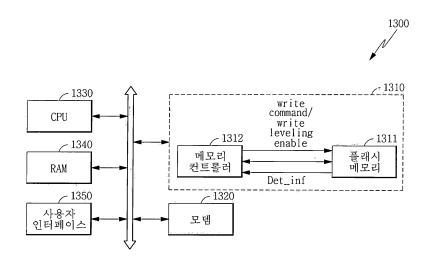

- [0128] 도 18은 본 발명의 메모리 카드(1310)를 구비하는 메모리 시스템의 실시예의 구성을 나타내는 것이다. 메모리 시스템(1300)은 공통 버스(1360)를 통하여 통신하는 프로세서(CPU)(1330), 랜덤 억세스 메모리(RAM)(1340), 사용자 인터페이스(1350), 및 모뎀(1320)을 구비하여 구성될 수 있다. 공통 버스(1360)와 연결된 장치들은 공통 버스(1360)를 통하여 메모리 카드(1310)로/로부터 신호를 송신/수신한다. 메모리 카드(1310)와 함께, 프로세서 (CPU)(1330), 랜덤 억세스 메모리(RAM)(1340), 사용자 인터페이스(1350), 및 모뎀(1320)을 포함하는 메모리 시스템(1300)의 각 구성 요소들은 본 발명에서 공개된 메모리 장치를 채용할 수 있다.

- [0129] 또한, 메모리 카드(1310)의 메모리 컨트롤러(1312)는 라이트 레벨링 동작시, 메모리 카드(1310)의 플래시 메모리(1311)로 라이트 레벨링 동작을 위한 커맨드 신호, 라이트 레벨링 제어 신호, 및 데이터 스트로브 신호를 출력하고, 플래시 메모리(1311)는 상기 커맨드 신호 및 클럭 신호에 응답하여 노멀 모드에서의 동작시와 동일한 경로를 통하여 내부 커맨드 신호를 발생하고, 상기 데이터 스트로브 신호에 응답하여 노멀 모드에서의 동작시와 동일한 경로를 통하여 내부 데이터 스트로브 신호를 발생하고, 상기 내부 커맨드 신호 및 내부 데이터 스트로브 신호의 위상차를 감지하여 감지된 위상차를 나타내는 감지 정보를 메모리 컨트롤러(1312)로 출력하고, 메모리 컨트롤러(1312)는 상기 감지 정보를 저장하여 이후에 데이터 스트로브 신호의 출력 타이밍을 조절하는데 이용한다.

- [0130] 메모리 시스템(1300)은 다양한 응용(예를 들면, 솔리드 스테이트 디스크(SSD), 카메라 이미지 센서(CIS) 및 컴퓨터 응용 칩셋 등과 같은 전자 장치)에 적용될 수 있다.

- [0131] 메모리 시스템 및 장치는 다양한 형태의 패키지(예를 들면, 볼 그리드 어레이(BGA), 칩 스케일 패키지(CSP), PLCC(plastic leaded chip carrier), PDIP(plastic dual in-line package), 멀티칩 패키지(MCP), WFP(wafer-level fabricated package), 및 WSP(wafer-level processed stock package) 등)로 패키징될 수 있다.

- [0132] 상기에서는 본 발명의 실시예를 참조하여 설명하였지만, 해당 기술분야의 숙련된 당업자는 하기의 특허 청구 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬수 있음을 이해할 수 있을 것이다.

### 도면의 간단한 설명

- [0133] 도 1은 본 발명의 메모리 시스템의 일실시예의 구성을 나타내는 것이다.

- [0134] 도 2는 도 1에 나타낸 본 발명의 메모리 시스템의 파워-업 동작의 실시예를 설명하기 위한 동작 타이밍도를 나타낸 것이다.

- [0135] 도 3a 및 도 3b는 본 발명의 메모리 장치 및 메모리 시스템의 라이트 레벨링 동작의 개념을 설명하기 위한 도면이다.

- [0136] 도 4는 본 발명의 메모리 장치 및 메모리 시스템의 개념을 설명하기 위한 도면이다.

- [0137] 도 5는 본 발명의 메모리 시스템(100)의 실시예의 구성을 나타내는 것으로서, 언버퍼드(unbuffered) 메모리 모듈(106)을 구비하는 경우를 나타낸 것이다.

- [0138] 도 6은 본 발명의 메모리 시스템(100)의 메모리 컨트롤러(102)의 실시예의 구성을 나타내는 것이다.

- [0139] 도 7은 도 6에 나타낸 본 발명의 메모리 컨트롤러(102)의 실시예의 제어 로직부(104)의 실시예의 구성을 나타낸 것이다.

- [0140] 도 8a 및 도 8b는 제어 로직부(124)의 제어 로직(132)의 실시예의 구성을 나타내는 것이다.

- [0141] 도 9는 도 6에 나타낸 본 발명의 메모리 시스템의 메모리 컨트롤러(102)의 데이터 스트로브 발생부(126)의 실시예의 구성을 나타내는 것이다.

- [0142] 도 10은 본 발명의 메모리 시스템(100)의 메모리 컨트롤러(102)의 다른 실시예의 구성을 나타낸 것이다.

- [0143] 도 11은 본 발명의 메모리 장치(104)의 실시예의 구성을 나타내는 것이다.

- [0144] 도 12a, 도 12b, 도 12c, 및 도 12d 각각은 도 11에 나타낸 본 발명의 메모리 장치(104)의 라이트 레벨링 신호 발생부(214)의 실시예들의 구성을 나타내는 것이다.

- [0145] 도 13은 도 11에 나타낸 본 발명의 메모리 장치(104)의 매치 및 위상 검출부(216)의 실시예의 구성을 나타낸 것 이다

- [0146] 도 14a 및 도 14b는 도 11에 나타낸 본 발명의 메모리 장치(104)의 동작을 설명하기 위한 동작 타이밍도를 나타 낸 것이다.

- [0147] 도 15는 본 발명의 라이트 레벨링 수행 방법의 실시예를 설명하기 위한 동작 흐름도를 나타낸 것이다.

- [0148] 도 16a는 본 발명의 메모리 장치의 실시예의 구성을 나타내는 것이다.

- [0149] 도 16b는 도 16a에 나타낸 본 발명의 메모리 장치의 실시예의 메모리 셀 어레이(1110)의 실시예의 구성을 나타내는 것이다.

- [0150] 도 17은 본 발명의 실시예에 따른 메모리 장치를 구비하는 메모리 카드의 실시예의 구성을 나타내는 것이다.

- [0151] 도 18은 메모리 카드(1310)를 구비하는 메모리 시스템의 실시예의 구성을 나타내는 것이다.

# 도면1

# 도면2

# 도면3a

# 도면3b

# 도면8a

# *도면8b*

# 도면12a

## 도면12b

## 도면12c

# 도면12d

# 도면14a

# 도면14b

# 도면16a

# 도면16b