#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

1/1368

(11)特許番号

特許第4187027号 (P4187027)

(45) 発行日 平成20年11月26日(2008.11.26)

(24) 登録日 平成20年9月19日(2008.9.19)

| (51) Int.Cl. |        |           | FΙ   |

|--------------|--------|-----------|------|

| G02F         | 1/1368 | (2006.01) | GO2F |

GO9F 9/30 (2006, 01) GO9F 9/30 338 HO1L 21/336 (2006.01) HO1L 29/78 612D HO1L 29/786 (2006, 01) HO1L 29/78 616T

> 請求項の数 1 (全 31 頁)

特願2006-247862 (P2006-247862) (21) 出願番号 (22) 出願日 平成18年9月13日 (2006.9.13) (65) 公開番号 特開2008-70521 (P2008-70521A) 平成20年3月27日(2008.3.27) (43) 公開日 審查請求日

平成19年3月6日(2007.3.6)

早期審査対象出願

前置審査

||(73)特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74)代理人 100094053

弁理士 佐藤 隆久

(72)発明者 入江 由季子

東京都品川区北品川6丁目7番35号 ソ

二一株式会社内

審査官 山口 裕之

最終頁に続く

## (54) 【発明の名称】表示装置

## (57)【特許請求の範囲】

## 【請求項1】

第1のソース・ドレイン領域および第2のソース・ドレイン領域がチャネル形成領域を 挟んで形成されており、ゲート絶縁膜を介してゲート電極が前記チャネル形成領域の上方 に設けられている画素スイッチング素子と、

上部電極および下部電極が誘電体膜を挟んで形成されており、前記第1のソース・ドレ イン領域と前記第2のソース・ドレイン領域と前記ゲート電極との上方において延在して 設けられており、前記下部電極が前記第2のソース・ドレイン領域および画素電極に接続 している保持容量素子と、

前記第1のソース・ドレイン領域および前記ゲート電極の上方であって前記保持容量素 子の下方において導電材料によって延在して形成されており、前記第2のソース・ドレイ ン領域の上方に形成されておらず、前記第1のソース・ドレイン領域に接続されている信 号配線中継部と、

前記画素スイッチング素子と前記信号配線中継部と前記保持容量素子との上方において 延在して設けられており、前記信号配線中継部に接続されており、前記画素スイッチング 素子にデータ信号を供給する信号配線と

を有し、

反転駆動により画素電極の電位が保持された際には、前記信号配線と前記第2のソース ・ドレイン領域とが、異なる極性の電位になり、前記下部電極と前記第1のソース・ドレ イン領域とが、異なる極性の電位になると共に、前記信号配線中継部と前記第1のソース

・ドレイン領域とが、同じ極性の電位になる 表示装置。

【発明の詳細な説明】

#### 【技術分野】

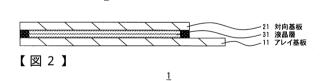

## [0001]

本発明は、表示装置およびその製造方法に関し、特に、基板において複数の画素が形成された画素領域にて、その複数の画素を反転駆動することによって画像を表示する表示装置およびその製造方法に関するものである。

## 【背景技術】

#### [00002]

液晶表示装置,有機 E L 表示装置などの表示装置は、CRT (Cathode Ray Tube)よりも、薄型、軽量、低消費電力といった利点を有し、パーソナルコンピューター、携帯電話、デジタルカメラなどの電子機器の表示装置として使用されている。

#### [0003]

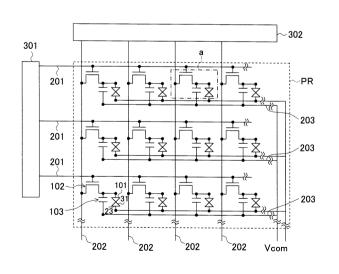

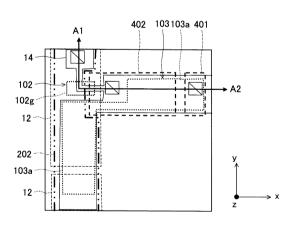

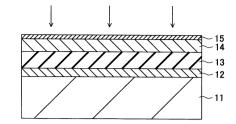

液晶表示装置は、一対の基板の間に液晶層が封入された液晶パネルを有しており、その液晶パネルの背面に設けられたバックライトなどの平面光源から照射された光を、その液晶パネルが透過して変調する。そして、その変調した光によって画像の表示が液晶パネルの正面にて実施される。このような液晶パネルとしては、たとえば、アクティブマトリクス方式が知られている。

#### [0004]

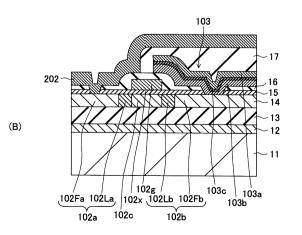

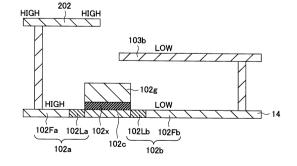

図21は、液晶表示装置において、アクティブマトリクス方式の液晶パネル100の回路構成を示す回路図である。図22は、液晶表示装置において、アクティブマトリクス方式の液晶パネル100の一部を示す平面図である。図23は、アクティブマトリクス方式の液晶パネル100の一部を示す断面図である。図22と図23とは、図21において一点鎖線で囲った部分aを示しており、図23においてアレイ基板11から層間絶縁膜17までの部分は、図22におけるA1-A2部分について示している。

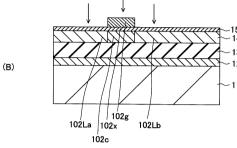

#### [0005]

液晶パネル 1 0 0 は、図 2 3 に示すように、アレイ基板 1 1 と、対向基板 2 1 と、液晶層 3 1 とを有する。

## [0006]

アレイ基板11は、図23に示すように、基板であり、たとえば、ガラスなどのように、光を透過する絶縁体により形成されている。そして、アレイ基板11においては、図21に示した部材において、画素電極101と画素スイッチング素子102と保持容量素子103と走査配線201と信号配線202と保持容量配線203とゲートドライバ301とソースドライバ302とが形成されている。ここでは、図21に示すように、画素電極101と画素スイッチング素子102と保持容量素子103と走査配線201と信号配線202と保持容量配線203とが、液晶パネル100の画素領域PRに形成されている。そして、ゲートドライバ301とソースドライバ302とが、その画素領域PRの周辺領域に形成されている。

## [0007]

対向基板 2 1 は、図 2 3 に示すように、基板であり、アレイ基板 1 1 と同様に、たとえば、ガラスなどのように、光を透過する絶縁体により形成されている。そして、対向基板 2 1 は、一方の面がアレイ基板 1 1 に対面しており、そのアレイ基板 1 1 に対面する面に、対向電極 2 3 が I T O などの透明電極として画素電極 1 0 1 に対応するように形成されている。

## [0008]

液晶層31は、図23に示すように、アレイ基板11と対向基板21との間に注入されており、配向処理されている。そして、液晶層31は、図21に示すように、画素電極101と対向電極23とに接続されており、その画素電極101と対向電極23とによって印加される電圧に基づいて配向状態が変化し、画面の表示が行われる。

10

20

30

40

### [0009]

このようなアクティブマトリクス方式の液晶パネル100を駆動する場合においては、ゲートドライバ301が y 方向に並ぶ走査配線201に走査信号を時間分割して順次走査して供給し、画素スイッチング素子102をオン状態にする。そして、この走査信号の供給のタイミングに合わせて、ソースドライバ302がデータ信号を信号配線202に供給し、オン状態の画素スイッチング素子102を介して画素電極101にデータ信号が印加される。これにより、液晶層31に電圧が印加され、液晶層31の光学特性が変化して、画像の表示が実施される(たとえば、特許文献1,特許文献2,特許文献3,特許文献4参照)。

## [0010]

上記の液晶パネル100においては、図22と図23とに示すように、画素スイッチング素子102と保持容量素子103とが、アレイ基板11の面において信号配線202などの導電層が形成される領域に対応するように形成されている。つまり、アレイ基板11の面の垂直方向zにおいて、画素スイッチング素子102と保持容量素子103とのそれぞれが、信号配線202、保持容量素子中継部401、画素電極中継部402などの導電層に対して、層間絶縁膜16を介してオーバーラップするように形成されている。これにより、画素領域PRの開口率が向上し、光透過率が向上するため、画像品質を向上させている。

## [0011]

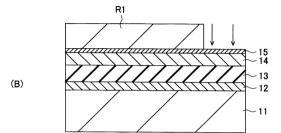

【特許文献1】特開2005-223027号公報

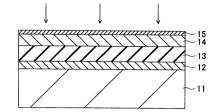

【特許文献2】特開2004-245872号公報

【特許文献3】特開2001-144298号公報

【特許文献 4 】特開 2 0 0 3 - 1 3 1 5 8 9 号公報

【発明の開示】

【発明が解決しようとする課題】

## [0012]

液晶パネル100を駆動させる際には、直流電圧によって液晶層31が劣化することを防止するために、反転駆動方式で駆動が行われている。反転駆動方式は、液晶層31に加わる電界の方向を交互に反転させる駆動方式であり、たとえば、交流のデータ信号を印加して、画素電極101に与える電位の正負を対向電極23の電位に対して交互に反転させることをいう。つまり、高電位と低電位とを交互に書き込むことをいう。

## [0013]

図24は、液晶パネル100を反転駆動させた際の波形図である。図24においては、 ラインL1は画素電極101の電位を示し、ラインL2は信号配線202から画素スイッ チング素子に印加されるデータ信号の波形を示し、ラインL3は基準電位を示している。

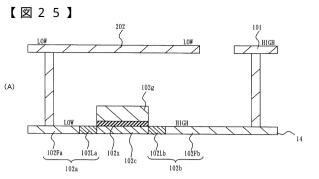

## [0014]

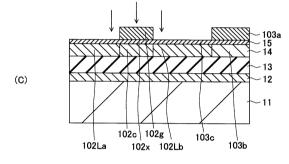

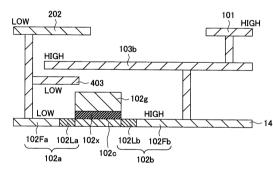

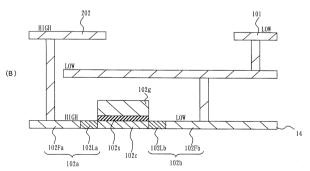

また、図25は、液晶パネル100を反転駆動させた際にゲートをオフした後に、液晶パネル100の各部において保持される電位を示す図である。図25において、図25(A)は、画素電極101に高電位HIGHが書き込まれた場合を示し、図25(B)は、画素電極101に低電位LOWが書き込まれた場合を示している。

## [0015]

液晶パネル100を反転駆動させる際には、走査配線201から画素スイッチング素子102のゲート電極102gに、走査信号としてゲートオン電圧を印加して、オン状態にする。そして、図24においてラインL2に示すように、基準電位L3に対して正となる高電位HIGHのデータ信号を、信号配線202から印加する。この高電位HIGHのデータ信号は、画素スイッチング素子102を介して、画素電極101に印加される。そして、所定期間のオン状態の後、走査配線201からゲート電極102gにゲートオフ電圧が印加されて、画素スイッチング素子102はオフ状態となり、信号配線202からの高電位HIGHのデータ信号の供給が終了される。

## [0016]

10

20

30

この時、画素電極101は、図24においてラインL1に示すように、高電位HIGHが書き込まれた状態となる。そして、図25(A)に示すように、信号配線202は、低電位LOWであり、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて信号配線202に接続されている側のソース・ドレイン領域102aは、信号配線202と同様に、低電位LOWとなる。一方で、画素電極101に接続されている側のソース・ドレイン領域102bは、画素電極101と同様に、高電位HIGHとなる。そして、図24に示すように、画素電極101は、オフ状態以後においても、液晶層31と保持容量素子103との電位保持特性により表示電圧を保持するが、リークしてオフ電流が発生することによって電位が変化する。

## [0017]

その後、再びゲートオン電圧が画素スイッチング素子102のゲート電極に印加され、画素スイッチング素子102がオン状態となる。そして、図24においてラインL2に示すように、上述した高電位HIGHの印加に続いて、基準電位L3に対して負となる低電位LOWのデータ信号が印加される。

#### [0018]

この時、画素電極101は、図24においてラインL1に示すように、低電位LOWが書き込まれた状態となる。そして、図25(B)に示すように、信号配線202は、高電位HIGHであり、画素スイッチング素子102の一対のソース・ドレイン領域102a ,102 bにおいて信号配線202に接続されている側のソース・ドレイン領域102a は、信号配線202と同様に、高電位HIGHとなる。一方で、画素電極101に接続されている側のソース・ドレイン領域102 b は、画素電極101と同様に、低電位LOWとなる。そして、上記と同様に、図24に示すように、画素電極101は、オフ状態以後においても、液晶層31と保持容量素子103との電位保持特性により表示電圧を保持するが、オフ電流の発生によって電位が変化する。

#### [0019]

このように高電位 H I G H と低電位 L O W とによって反転駆動を実施する際には、オフ電流によって画素電極 1 0 1 の保持している電位差が変化する。このため、画像情報が十分に保持されなくなり、画像品質が低下する場合がある。

## [0020]

また、ここでは、図24に示すように、高電位HIGHでの駆動後と低電位LOWでの駆動後との間では、オフ時のリーク電流の大きさが異なっており、高電位HIGHの場合でのオフ電流の方が大きくなる場合がある。このため、所定時間後の画素電極101においては、高電位HIGHの印加時の保持電位VHと低電位LOWの印加時での保持電位VLとが異なる。したがって、反転駆動させた場合には、高電位HIGHの場合と低電位LOWの場合との間での表示が異なることになり、フリッカや残像が発生し、画像品質が低下する場合がある。

## [0021]

このような不具合を抑制するために、画素スイッチング素子102においては、LDD(Lightly Doped Drain)構造が採用されている。このLDD構造のTFTにおいては、電気抵抗値が高い低濃度不純物拡散領域によってドレイン端での電界集中を緩和させて、オフ電流を低減させることにより、画像品質を向上させている。

#### [0022]

しかしながら、画素領域の開口率を向上させるために、図22と図23とに示すように、アレイ基板11の面において、画素スイッチング素子102と保持容量素子103とを、信号配線202などの導電層が形成される領域に対応するように形成する場合においては、上記のように高電位HIGHでの駆動と低電位LOWでの駆動との間においてオフ電流の大きさが、顕著に異なる場合がある。

## [0023]

具体的には、図25(A)に示すように、画素電極101が高電位HIGHを保持している場合には、画素スイッチング素子102の一対のソース・ドレイン領域102a,1

10

20

30

40

10

20

30

40

50

02 b において画素電極 101 に接続されている側のソース・ドレイン領域 102 b の電位が高電位 H I G H であるのに対し、そのソース・ドレイン領域 102 b に層間絶縁膜 16を介して対面する信号配線 202 が低電位 L O W であるために、その間において電位差が生じ、オフ時のリーク電流の発生が多くなる。

## [0024]

一方、図25(B)に示すように、画素電極101が低電位LOWを保持している場合には、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて信号配線202に接続されている側のソース・ドレイン領域102aの電位がHIGHであるのに対し、そのソース・ドレイン領域102aに層間絶縁膜16を介して対面する信号配線202も高電位HIGHであるために、その間において電位差が生じず、オフ時のリーク電流の発生が少なくなる。

[0025]

このため、アレイ基板11の面において、画素スイッチング素子102と保持容量素子103とを、信号配線202が形成される領域に対応するように形成する場合においては、フリッカや残像が発生し画像品質が低下する不具合が顕在化する場合がある。

[0026]

この現象は、上記のように画素スイッチング素子102を信号配線202などの導電層に対面させた場合だけでなく、画素スイッチング素子102を保持容量素子103に対面するように形成する場合においても同様である。

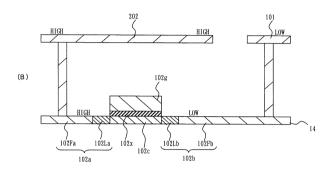

[0027]

図26は、画素スイッチング素子102を保持容量素子103に対面するように形成する場合において、液晶パネル100を反転駆動させた際にゲートをオフした後に、液晶パネル100の各部において保持される電位を模式的に示す図である。図26において、図26(A)は、画素電極に高電位が書き込まれた場合を示し、図26(B)は、画素電極に低電位が書き込まれた場合を示している。

[0028]

図26(A)に示すように、画素電極101が高電位HIGHを保持している場合には、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて画素電極101側に接続されている側のソース・ドレイン領域102bの電位が高電位HIGHであるのに対し、そのソース・ドレイン領域102bに層間絶縁膜16を介して対面する保持容量素子103の下部電極103bが高電位HIGHである。このため、そのソース・ドレイン領域102bと、保持容量素子103の下部電極103bとの間において層間絶縁膜16を介して対面する部分においては、電位差が生じないため、オフ時のリーク電流の発生が少なくなる。

[0029]

一方、図26(B)に示すように、画素電極101が低電位LOWを保持している場合には、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて信号配線202側に接続されている側のソース・ドレイン領域102aの電位が高電位HIGHであるのに対し、そのソース・ドレイン領域102aに層間絶縁膜16を介して対面する保持容量素子103の下部電極103bは、低電位LOWである。このため、その間において電位差が生じ、オフ時のリーク電流の発生が多くなる。

[0030]

このように、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて駆動時にドレイン側となる電位と、信号配線202または下部電極103bのように、そのドレイン側に対して層間絶縁膜16を介して対面している導電層の電位とが、互いに異なる場合には、上記のような不具合が生ずる場合がある。

[0031]

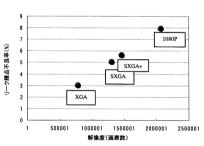

図27は、液晶パネルの解像度と、リーク輝点不良率との関係を示す図である。

[0032]

図27に示すように、液晶パネルの解像度が高くなるに伴って、リーク輝点不良率(%

)が高くなってきているため、この要因によって、画像品質の低下が発生する場合がある

#### [0033]

以上のように、画素領域の開口率を向上させるために、アレイ基板11の面において、画素スイッチング素子102を、信号配線202や保持容量素子103の下部電極103 bなどの導電層に対面するように形成する場合や、解像度を向上させる場合においては、オフ時のリーク電流が大きくなって画像の保持特性の低下が顕著になると共に、反転駆動時においてフリッカや残像が発生しやすくなるため、画像品質が低下する不具合が顕在化する場合がある。

#### [0034]

したがって、本発明は、画像品質を向上可能な表示装置およびその製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

## [0035]

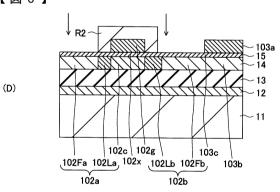

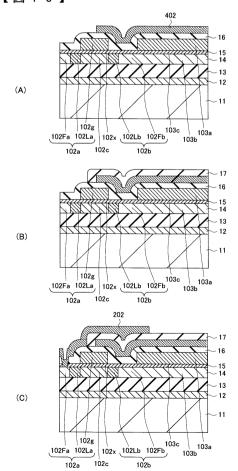

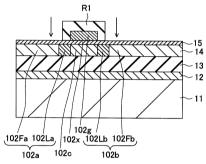

本発明の表示装置は、第1のソース・ドレイン領域および第2のソース・ドレイン領域 がチャネル形成領域を挟んで形成されており、ゲート絶縁膜を介してゲート電極が前記チ ャネル形成領域の上方に設けられている画素スイッチング素子と、上部電極および下部電 極が誘電体膜を挟んで形成されており、前記第1のソース・ドレイン領域と前記第2のソ ース・ドレイン領域と前記ゲート電極との上方において延在して設けられており、前記下 部電極が前記第2のソース・ドレイン領域および画素電極に接続している保持容量素子と 前記第1のソース・ドレイン領域および前記ゲート電極の上方であって前記保持容量素 子の下方において導電材料によって延在して形成されており、前記第2のソース・ドレイ ン領域の上方に形成されておらず、前記第1のソース・ドレイン領域に接続されている信 号配線中継部と、前記画素スイッチング素子と前記信号配線中継部と前記保持容量素子と の上方において延在して設けられており、前記信号配線中継部に接続されており、前記画 素スイッチング素子にデータ信号を供給する信号配線とを有し、反転駆動により画素電極 の電位が保持された際には、前記信号配線と前記第2のソース・ドレイン領域とが、異な る極性の電位になり、前記下部電極と前記第1のソース・ドレイン領域とが、異なる極性 の電位になると共に、前記信号配線中継部と前記第1のソース・ドレイン領域とが、同じ 極性の電位になる。

### 【発明の効果】

## [0036]

本発明によれば、画像品質を向上可能な表示装置およびその製造方法を提供することができる。

【発明を実施するための最良の形態】

#### [0037]

以下、本発明の実施形態の一例について、図面を参照して説明する。

## [0038]

## <参考実施形態1>

## (構成)

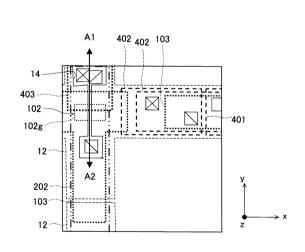

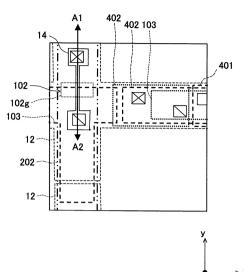

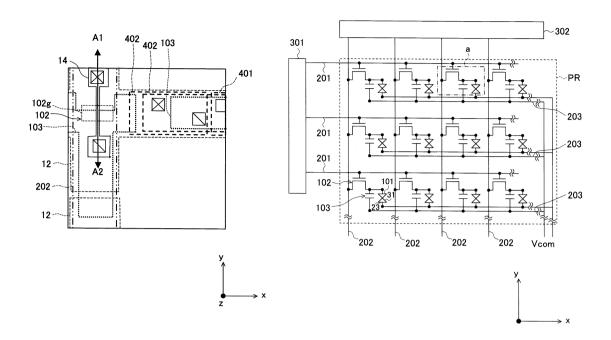

図1,図2,図3,図4は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1を示す図である。

## [0039]

ここで、図1は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の構成を示す断面図である。また、図2は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の回路構成を示す回路図である。また、図3は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の一部を示す平面図である。図3は、図2において一点鎖線で囲った部分aを示している。また、図4は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の一部を示す断面図である。図4のアレイ基板11から層間絶縁膜17までの部分は、図3におけるA1-A2部分に

10

20

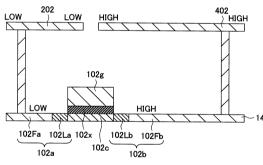

30

40

ついて示している。

## [0040]

液晶パネル1は、図1に示すように、アレイ基板11と、対向基板21と、液晶層31とを有する。また、この他に、図2に示すように、液晶パネル1は、対向電極23と、画素電極101と、画素スイッチング素子102と、保持容量素子103と、走査配線201と、信号配線202と、保持容量配線203と、ゲートドライバ301と、ソースドライバ302とを有する。つまり、本実施形態の液晶パネル1は、アクティブマトリクス方式である。各部について順次説明する。

## [0041]

アレイ基板11は、図1に示すように、基板であり、たとえば、ガラスなどのように、光を透過する絶縁体により形成されている。アレイ基板11においては、図2に示した部材において、画素電極101と画素スイッチング素子102と保持容量素子103と走査配線201と信号配線202と保持容量配線203とゲートドライバ301とソースドライバ302とが形成されている。ここでは、図2に示すように、画素電極101と画素スイッチング素子102と保持容量素子103と走査配線201と信号配線202と保持容量配線203とが、液晶パネル1の画素領域PRに形成されている。そして、ゲートドライバ301とソースドライバ302とが、その画素領域PRの周辺領域に形成されている

## [0042]

対向基板 2 1 は、図 1 に示すように、基板であり、アレイ基板 1 1 と同様に、たとえば、ガラスなどのように、光を透過する絶縁体により形成されている。対向基板 2 1 は、図 1 に示すように、一方の面がアレイ基板 1 1 に間隔を隔てて対面している。そして、対向基板 2 1 は、画素領域 P R の周囲においてシール材によってアレイ基板 1 1 に貼り付けられている。そして、図 4 に示すように、そのアレイ基板 1 1 に対面する面に、対向電極 2 3 が I T O などの透明電極として形成されている。ここでは、複数の画素電極 1 0 1 に対応する共通電極として、画素領域 P R の全面を覆うようにベタ状に形成されている。

#### [0043]

液晶層 3 1 は、図 1 に示すように、アレイ基板 1 1 と対向基板 2 1 との間に、たとえば、ツイストネマティック型の液晶が注入され、配向処理されている。そして、液晶層 3 1 は、図 2 に示すように、画素電極 1 0 1 と対向電極 2 3 とに接続されており、その画素電極 1 0 1 と対向電極 2 3 とによって印加される電圧に基づいて配向状態が変化し、画像の表示が行われる。

## [0044]

アレイ基板 1 1 に形成されている各部について説明する。

## [0045]

画素電極101は、ITO(Indium Tin Oxide)などの導電材料を用いて形成された透明電極であり、図2に示すように、画素領域PRにおいて、複数がx方向とy方向とに並ぶようにマトリクス状に配置され、液晶層31に接続する。ここでは、画素電極101のそれぞれは、y方向に間隔を隔てて延在する複数の走査配線201と、x方向に間隔を隔てて延在する複数の信号配線202とによって区画される領域に対応するように形成されている。

#### [0046]

画素スイッチング素子102は、図2に示すように、画素領域PRにおいて、複数の画素電極101のそれぞれに対応するように、×方向とy方向とに複数がマトリクス状に配置されており、それぞれが各画素電極101に接続されている。そして、図4に示すように、画素スイッチング素子102は、アレイ基板11において対向基板21に対面する側の面に、遮光膜12と層間絶縁膜13とを介するように形成されている。また、図4に示すように、画素スイッチング素子102は、アレイ基板11の面において信号配線202が形成される領域に対応するように形成されている。つまり、画素スイッチング素子102は、アレイ基板11の面の垂直方向zにおいて、信号配線202に対して、層間絶縁膜

10

20

30

40

16を介してオーバーラップするように形成されている。

## [ 0 0 4 7 ]

本実施形態においては、画素スイッチング素子102は、図3と図4とに示すように、薄膜トランジスタ(TFT:Thin Film Transistor)であって、半導体層14と、ゲート絶縁膜102xと、ゲート電極102gとを含む。画素スイッチング素子102は、たとえば、ポリシリコンを用いたTFTであって、図4に示すように、半導体層14とゲート絶縁膜102xとゲート電極102gとが、アレイ基板11の側から順次形成されているトップゲート型であり、LDD構造である。

## [0048]

つまり、画素スイッチング素子102においては、図4に示すように、半導体層14は、ポリシリコンであって、チャネル形成領域102cを挟むように第1および第2のソース・ドレイン領域102a,102bが一対で形成されている。

## [0049]

ここでは、半導体層14にチャネル領域102cを挟むように形成された第1および第 2のソース・ドレイン領域102a,102bにおいて、一方の第1のソース・ドレイン 領域102aは、信号配線202に接続され、他方の第2のソース・ドレイン領域102 bは、画素電極101と保持容量素子103とに接続されている。

### [0050]

また、第1および第2のソース・ドレイン領域のそれぞれは、第1および第2の不純物拡散領域102Fa,102Fbと、第1および第2の低濃度不純物領域102La,102Fbとをそれぞれ有する。ここで、第1および第2の不純物拡散領域102Fa,102Fbは、半導体層14においてチャネル形成領域102cを挟む領域に不純物を拡散させることによって形成されている。そして、第1および第2の低濃度不純物領域102La,102Fbとチャネル形成領域102cとの間において、その第1および第2の不純物拡散領域102Fa,102Fbとチャネル形成領域102cとの間において、その第1および第2の不純物拡散領域102Fa,102Fbよりも低い不純物濃度になるように半導体層14に不純物を拡散させることによって形成されている。

#### [0051]

そして、ゲート絶縁膜102×は、そのチャネル形成領域102cに対面するように形成されている。

## [0052]

また、ゲート電極102gは、図4に示すように、ゲート絶縁膜102×を介してチャネル形成領域102cに対応するように形成されており、図2に示すように、走査配線201に接続されている。

## [0053]

そして、画素スイッチング素子102は、走査配線201を介してゲートドライバ301からゲート電極102gに入力される走査信号によって駆動制御される。また、画素スイッチング素子102は、信号配線202を介してソースドライバ302から画素スイッチング素子102にデータ信号が供給される。そして、画素スイッチング素子102は、オン状態の場合には、データ信号を画素電極101と保持容量素子103とのそれぞれに供給する。

#### [0054]

保持容量素子103は、図2に示すように、画素領域PRにおいて、複数の画素電極101のそれぞれに対応するように、×方向とy方向とのそれぞれに複数がマトリクス状に配置されている。そして、保持容量素子103は、液晶層31による静電容量と並列になるように形成され、液晶層31に印加されるデータ信号による電荷を保持する。また、図3に示すように、保持容量素子103は、アレイ基板11において×方向とy方向とのそれぞれに延在するように形成されている。ここで、y方向に延在する部分については、画素スイッチング素子102と同様に、アレイ基板11の面において信号配線202が形成される領域に対応するように形成されている。つまり、アレイ基板11の面の垂直方向z

10

20

30

40

において、信号配線202に対して、層間絶縁膜16を介してオーバーラップするように 形成されている。また、図4に示すように、保持容量素子103は、アレイ基板11において対向基板21に対面する側の面に、遮光膜12と層間絶縁膜13とを介するように形成されている。そして、図4に示すように、保持容量素子103は、上部電極103aと 下部電極103bと誘電体膜103cとを有しており、下部電極103bと誘電体膜103cと上部電極103aとがアレイ基板11の側から順次形成されている。

#### [0055]

ここで、保持容量素子103において上部電極103aは、ゲート電極102gと同様にして導電材料によって形成されており、図2に示すように、保持容量配線203に接続されている。

## [0056]

そして、下部電極 1 0 3 b は、図 2 と図 4 とに示すように、画素スイッチング素子 1 0 2 の第 1 および第 2 のソース・ドレイン領域 1 0 2 a , 1 0 2 b において信号配線 2 0 2 が接続されていない側の第 2 のソース・ドレイン領域 1 0 2 b に接続されている。本実施形態においては、半導体層 1 4 において上部電極 1 0 3 a に対面する領域が、下部電極 1 0 3 b として機能する。

## [0057]

また、誘電体膜103cは、上部電極103aと下部電極103bとが対面する間に、 挟まれるように形成されている。

## [0058]

走査配線201は、図2に示すように、画素領域PRにおいて、×方向に延在するように形成されており、その×方向に並ぶ複数の画素スイッチング素子102に接続している。また、走査配線201は、y方向に並ぶ複数の画素スイッチング素子102に対応するように、y方向に間隔を隔てて並んで複数が形成されている。そして、走査配線201は、ゲートドライバ301に接続されており、ゲートドライバ301からの走査信号を、画素電極101の行を順次選択するように画素スイッチング素子102に供給する。

#### [0059]

信号配線202は、図2と図3とに示すように、画素領域PRにおいてx方向に並ぶ複 数の画素電極101の間隔に対応するようにy方向に延在するように、導電材料によって 形成されており、γ方向に並ぶ複数の画素スイッチング素子102に接続している。また 、信号配線202は、×方向に並ぶ複数の画素スイッチング素子102に対応するように 、×方向において間隔を隔てて並んで複数が形成されている。そして、信号配線202は 、走査信号が供給された画素スイッチング素子102を介してデータ信号を画素電極10 1 に供給する。また、信号配線 2 0 2 は、図 3 と図 4 とに示すように、画素領域 P R にお いて画素スイッチング素子102に対面する領域を含むように形成されており、画素スイ ッチング素子102の第1のソース・ドレイン領域102aに接続されている。本実施形 態においては、図4にて点線で囲った領域R1として示すように、信号配線202は、画 素スイッチング素子102の第1のソース・ドレイン領域102aに接続されており、画 素スイッチング素子102において第2のソース・ドレイン領域102b以外であって第 1のソース・ドレイン領域102aに対面する領域を含むように形成されている。具体的 には、信号配線202は、図4に示すように、第1の不純物拡散領域102Faに接続さ れており、第1の低濃度不純物領域102Laと、ゲート電極102gの一部とに、層間 絶縁膜16のみを介して対面するように形成されている。また、図3に示すように、信号 配線202は、画素電極中継部402が形成される部分に対応するように、xy平面にお いて凹部が形成されている。

## [0060]

保持容量配線203は、図2に示すように、画素領域PRにおいて、x方向に延在して 形成されており、x方向に並ぶ複数の保持容量素子103に接続している。また、保持容 量配線203は、y方向に並ぶ複数の保持容量素子103に対応するように、y方向に間 隔を隔てて並んで複数が形成されている。そして、保持容量配線203は、保持容量素子 10

20

30

40

103の反対側が対向電極23に接続されている。

## [0061]

保持容量素子中継部401は、導電材料によって形成されており、保持容量配線203と保持容量素子103とを接続するように中継する。ここでは、図3に示すように、保持容量素子中継部401は、x方向において画素電極中継部402と並ぶように形成されている。また、図4に示すように、保持容量素子103の上部電極103aのそれぞれに接続している。

## [0062]

画素電極中継部 4 0 2 は、導電材料によって形成されており、画素電極 1 0 1 と画素スイッチング素子 1 0 2 とを接続するように中継する。ここでは、図 3 に示すように、画画素素電極中継部 4 0 2 は、 x 方向に延在しており、 x 方向において保持容量素子中継部 4 0 1 と並ぶように形成されている。また、本実施形態においては、図 4 にて点線で囲った領域 R 2 として示すように、画素電極中継部 4 0 2 は、それぞれが画素スイッチング素子 1 0 2 において第 1 のソース・ドレイン領域 1 0 2 は、それぞれが画素スイッチング素子 1 0 2 において第 1 のソース・ドレイン領域 1 0 2 は外であって第 2 のソース・ドレイン領域 1 0 2 において第 2 の不統物拡散領域 1 0 2 F b に接続されている。 第 2 の不統物拡散領域 1 0 2 F b に接続されて膜 1 6 のみを介して対面するように形成されている。ここでは、画素電極中継部 4 0 2 は に 信号配線 2 0 2 側の端部と、信号配線 2 0 2 の端部との間の距離が、たとえば、0 ・5 μ m 以上になるように形成されている。これは、両者間において生ずる寄生容量が大きくなることを防止するためである。

[0063]

(製造方法)

以下より、上記の液晶パネル1の製造方法について説明する。

## [0064]

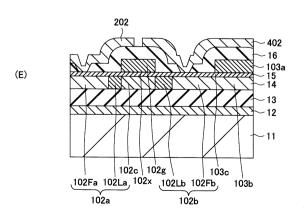

図5は、本発明にかかる<u>参考実施形態1</u>において、アレイ基板11側の各工程を示す断面図である。図6は、本発明にかかる<u>参考実施形態1</u>において、図5に次いで、アレイ基板11側の各工程を示す断面図である。図5と図6とにおいては、図5(A),図5(B),図5(C),図6(D),図6(E)の順にて、アレイ基板11側の各工程を示している。

[0065]

まず、図5(A)に示すように、アレイ基板11に、遮光膜12と層間絶縁膜13と半導体層14と絶縁膜15とを順次形成する。

[0066]

ここでは、アレイ基板11に、たとえば、金属やシリサイドなどの遮光材料からなる導電体膜を、200mm厚程度、堆積して設けた後に、アレイ基板11に形成される画素スイッチング素子102と保持容量素子103との形成領域および走査配線201の形成領域に対応するように、その導電体膜をパターン加工して、遮光膜12を形成する。つまり、遮光膜12を、走査配線201を兼ねるように形成する。その後、その遮光膜12を被覆するように、たとえば、CVD(Chemical Vapor Deposition)法により、シリコン酸化物の層間絶縁膜13を、400mm厚から600mm厚になるように形成する。

[0067]

その後、画素スイッチング素子102のチャネル形成領域102cと、第1および第2のソース・ドレイン領域102a,102bとを形成する領域と、保持容量素子103を形成する領域とを被覆するようにして、層間絶縁膜13の上に、たとえば、CVD法によりアモルファスシリコン膜を設ける。そして、アモルファスシリコン膜を熱処理して水素脱離を行い、ポリシリコン膜の半導体層14を形成する。

[0068]

10

20

30

そして、その半導体層14をパターン加工する。ここでは、図3に示すように、遮光膜12が形成された領域内において、画素スイッチング素子102のチャネル形成領域102 c と第1および第2のソース・ドレイン領域102 a , 102 b の形成領域と、保持容量素子103の下部電極103 b の形成領域とに対応するように、レジストマスクを用いてエッチング処理を施すことによってパターン加工を実施する。本実施形態では、ゲート電極103 g を形成する領域において、直角に折れ曲がるように形成する。

#### [0069]

その後、画素スイッチング素子102のゲート絶縁膜102×の形成領域と、保持容量素子103の誘電体膜103cの形成領域とに対応するように、絶縁膜15を形成する。そして、所定の閾値になるように、半導体層14に不純物を注入する。

[0070]

つぎに、図5(B)に示すように、半導体層14において、保持容量素子103の下部電極103bを形成する領域に不純物を注入する。

[0071]

ここでは、半導体層 1 4 において保持容量素子 1 0 3 の下部電極 1 0 3 b を形成する領域以外の領域を、レジストマスク R 1 で覆う。その後、半導体層 1 4 において保持容量素子 1 0 3 の下部電極 1 0 3 b を形成する領域に、たとえば、リンを、 1 0  $^{15}$  / c m  $^{2}$  になるようにイオン注入する。そして、レジストマスク R 1 を除去する。

[0072]

つぎに、図5 ( C ) に示すように、画素スイッチング素子102のゲート電極102g と、保持容量素子103の上部電極103aとを形成後、画素スイッチング素子102の 第1および第2の低濃度不純物領域102La,102Lbを形成する。

[0073]

ここでは、ゲート絶縁膜102×および誘電体膜103cを構成するシリコン酸化膜の上に、たとえば、CVD法により、ポリシリコン膜を成膜する。その後、そのポリシリコン膜にリンをドーピングし導電体とする。そして、レジストマスクを用いたエッチングにより、そのポリシリコン膜をパターン加工して、半導体層14のチャネル形成領域102cに対応する位置にゲート電極102gを形成する。また、同様にして、レジストマスクを用いたエッチングにより、そのポリシリコン膜を保持容量素子103の上部電極103aとするパターン加工をする。なお、ゲート電極102gを、PDASにて形成しても好適である。

[0074]

この後、ゲート電極 1 0 2 g および上部電極 1 0 3 a をマスクとして、リンをイオンドーピングし、半導体層 1 4 のチャネル形成領域 1 0 2 c を挟むようにして、第 1 および第 2 の低濃度不純物領域 1 0 2 L a , 1 0 2 L b を半導体層 1 4 に形成する。たとえば、リンを、 1 ~ 3 × 1 0  $^{1}$   $^{3}$  / c m  $^{2}$  になるように注入する。つまり、セルフアライン方式によって、半導体層 1 4 においてゲート電極 1 0 2 g と上部電極 1 0 3 a との間に対応する領域と、半導体層 1 4 においてゲート電極 1 0 2 g を介してその領域に対して反対側に位置する領域とのそれぞれに、不純物を注入する。

[0075]

つぎに、図6(D)に示すように、画素スイッチング素子102の第1の不純物拡散領域102Faと第2の不純物拡散領域102Fbとを形成する。

[0076]

ここでは、半導体層 1 4 において画素スイッチング素子 1 0 2 の第 1 の不純物拡散領域 1 0 2 F a と第 2 の不純物拡散領域 1 0 2 F b とを形成する領域以外の領域を、レジストマスクR 2 で覆う。その後、半導体層 1 4 において画素スイッチング素子 1 0 2 の第 1 の不純物拡散領域 1 0 2 F b とを形成する領域に、たとえば、リンを、 1 0  $^{1}$   $^{5}$  / c m  $^{2}$  になるように注入する。そして、レジストマスクR 2 を除去する。

[0077]

10

20

30

つぎに、図6(E)に示すように、信号配線202と画素電極中継部402とを形成する。

#### [0078]

ここでは、信号配線 2 0 2 および画素電極中継部 4 0 2 などの導電層と、画素スイッチング素子 1 0 2 および保持容量素子 1 0 3 との間に介在させる層間絶縁膜 1 6 を、まず、形成する。たとえば、C V D 法によってシリコン酸化物を堆積させることによって、層間絶縁膜 1 6 を形成する。その後、アレイ基板 1 1 を熱処理し、上記のようにしてイオンドーピングされた不純物を活性化させる。

## [0079]

この後、第1の不純物拡散領域102Faと第2の不純物拡散領域102Fbとの表面を露出するように、層間絶縁膜16にコンタクトホールを形成した後、たとえば、スパッタリング法により、アルミニウム膜などの導電体膜を、そのコンタクトホールに埋め込むようにして堆積する。

## [0800]

そして、レジストマスクを用いたエッチング処理を実施することにより、その導電体膜をパターン加工して、信号配線 2 0 2 と画素電極中継部 4 0 2 とのそれぞれを形成する。

## [0081]

本実施形態においては、画素スイッチング素子102において第2のソース・ドレイン領域102b以外であって第1のソース・ドレイン領域102aに対面する領域を含むように信号配線202を形成する。具体的には、第1の低濃度不純物領域102Laと、ゲート電極102gの一部とに、層間絶縁膜16のみを介して対面する部分を含むように形成する。また、これと共に、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bに対面する領域を含むように画素電極中継部402を形成する。具体的には、第2の低濃度不純物領域102Lbと、ゲート電極102gの一部とに、層間絶縁膜16のみを介して対面する部分を含むように形成する。

### [0082]

この後、図4に示すように、信号配線202と画素電極中継部402とを被覆するように、たとえば、プラズマCVD法により、シリコン酸化物を堆積して層間絶縁膜17を形成する。その後、CMP処理などの平坦化処理を施す。そして、特に、図示しないが、画素電極中継部402の表面が露出するようにコンタクトホールを形成後、たとえば、チタン膜などの導電体膜をコンタクトホールに埋め込むようにして堆積して接続導電層(図示なし)を形成する。そして、その接続導電層と電気的に接続するように、スパッタリング法によりITO膜を成膜した後、そのITO膜をパターン加工することによって、画素電極101を形成する。

## [0083]

なお、ここでは、図示を省略しているが、信号配線202および画素電極中継部402 と同様にして、保持容量素子中継部401を形成する。

#### [0084]

一方で、図 4 に示すように、対向基板 2 1 においては、ITO膜で、対向電極 2 3 を形 40 成する。

#### [0085]

その後、図4に示すように、画素電極101が形成されたアレイ基板11と、対向電極23が形成された対向基板21とを、画素電極101と対向電極23とが対向するように貼り合わせる。貼り合わせるに当たり、まず、アレイ基板11と対向基板21とにポリイミドの配向膜(図示なし)を形成する。そして、それぞれの配向膜をラビング処理し、所定のギャップを有するようにして、シール材を用いて接着して貼り合わせる。その後、アレイ基板11と対向基板21との間のギャップに液晶層31を注入し、液晶層31を配向させて液晶セルを形成する。

## [0086]

10

20

10

20

30

40

50

そして、液晶セルを駆動させる駆動回路や、偏光板、バックライトなどの周辺機器を実装して、本実施形態の液晶表示装置を完成する。

#### [0087]

(動作)

以下より、本実施形態の液晶表示装置の動作について説明する。

#### [0088]

上記の液晶パネル1を駆動する場合においては、ゲートドライバ301がy方向に並ぶ走査配線201に走査信号を時間分割して順次走査して供給し、画素スイッチング素子102をオン状態にする。そして、この走査信号の供給のタイミングに合わせて、ソースドライバ302がデータ信号を信号配線202に供給し、オン状態の画素スイッチング素子102を介して画素電極101にデータ信号が印加される。これにより、液晶層31に電圧が印加され、液晶層31の光学特性が変化して、画像の表示が実施される。

#### [0089]

ここでは、前述したように液晶パネル1を駆動させる際、液晶層31の劣化を防止するために、交流による反転駆動が行われている。反転駆動により、画素電極101と対向電極23とに電圧を印加し、その電圧に基づいて液晶層31の配向状態が変化する。液晶層31の配向状態を変化させて、バックライトなどの光源からの光の透過を制御して、画面の表示が行われる。

## [0090]

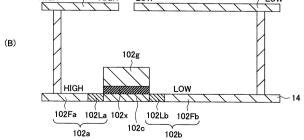

図7は、本発明にかかる<u>参考実施形態1</u>において、液晶パネル1を反転駆動させた際にゲートをオフした後に、液晶パネル1の各部において保持される電位を模式的に示す図である。図7において、図7(A)は、画素電極に高電位が書き込まれた場合を示し、図7(B)は、画素電極に低電位が書き込まれた場合を示している。

#### [0091]

画素電極101が高電位HIGHを保持している場合には、図7(A)に示すように、信号配線202と、画素スイッチング素子102の一対のソース・ドレイン領域102a , 102 b において信号配線202に接続されている側の第1のソース・ドレイン領域102aとのそれぞれの電位は、共に、低電位LOWであって同電位である。そして、画素電極101に接続されている画素電極中継部402と、画素スイッチング素子102の一対のソース・ドレイン領域102a , 102 b において画素電極101に接続されている側の第2のソース・ドレイン領域102 b とのそれぞれの電位は、共に、高電位HIGHであって同電位である。このため、前述した図25(A)に示した場合と異なり、画素スイッチング素子においてドレインとなる第2のソース・ドレイン領域102 b と、画素電極中継部402との間において、層間絶縁膜16を介して対面する部分については、電位差が生じないため、オフ時のリーク電流の発生が少なくなる。

## [0092]

一方で、画素電極101が低電位LOWを保持している場合には、図7(B)に示すように、信号配線202と、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて信号配線202に接続されている側の第1のソース・ドレイン領域102aとのそれぞれの電位は、共に、高電位HIGHであって同電位である。そして、画素電極101に接続されている画素電極中継部402と、画素スイッチング素子102の一対のソース・ドレイン領域102a,102bにおいて画素電極101に接続されている側の第2のソース・ドレイン領域102bとのそれぞれの電位は、共に、低電位LOWであって同電位である。このため、前述した図25(B)に示した場合と異なり、画素スイッチング素子においてドレインとなる第1のソース・ドレイン領域102aと、信号配線202との間において、層間絶縁膜16を介して対面する部分については電位差が生じないため、オフ時のリーク電流の発生が少なくなる。

### [0093]

このように、本実施形態は、アレイ基板 1 1 上に薄膜トランジスタが画素スイッチング 素子 1 0 2 としてマトリクス状に設けられた液晶表示装置において、その薄膜トランジス タを構成する半導体層14に、データを供給する信号配線202と、画素電極101とを、ゲート電極102g上まで張り出すように形成しているために、画素スイッチング素子102のチャネル端からドレイン部に渡る領域の電位と、その領域に対面する導電層の電位とが反転駆動時において同電位になるため、オフ時のリーク電流の発生を抑制することができる。

## [0094]

このため、本実施形態は、オフ時のリーク電流の発生を抑制すると共に、高電位HIGHと低電位LOWでの各駆動時においてオフ時の電位保持特性を同等にすることができる。具体的には、本実施形態は、従来構造に比べて、リーク電流値が約1桁分低減され、反転駆動時に電位差を同等にすることができた。

## [0095]

したがって、本実施形態は、画素領域の開口率を向上させるために、アレイ基板 1 1 の面にて画素スイッチング素子 1 0 2 を信号配線 2 0 2 や画素電極中継部 4 0 2 などの導電層に対面するように形成する場合において、オフ時のリーク電流の発生によって、画像の保持特性が低下することと、反転駆動時においてフリッカや残像が発生することとを防止できるため、画像品質を向上することができる。

## [0096]

なお、上記の実施形態において、アレイ基板11は、本発明の基板に相当する。また、 上記の実施形態において、半導体層14は、本発明の半導体層に相当する。また、上記の 実施形態において、層間絶縁膜16は、本発明の層間絶縁膜に相当する。また、上記の実 施形態において、対向基板21は、本発明の対向基板に相当する。また、上記の実施形態 において、液晶層31は、本発明の液晶層に相当する。また、上記の実施形態において、 画素電極101は、本発明の画素電極に相当する。また、上記の実施形態において、画素 スイッチング素子102は、本発明の画素スイッチング素子に相当する。また、上記の実 施形態において、ゲート絶縁膜102×は、本発明のゲート絶縁膜に相当する。また、上 記の実施形態において、ゲート電極102gは、本発明のゲート電極に相当する。また、 上記の実施形態において、チャネル形成領域102cは、本発明のチャネル形成領域に相 当する。また、上記の実施形態において、第1のソース・ドレイン領域102aは、本発 明の第1のソース・ドレイン領域に相当する。また、上記の実施形態において、第2のソ ース・ドレイン領域 1 0 2 b は、本発明の第 2 のソース・ドレイン領域に相当する。また 上記の実施形態において、第1の不純物拡散領域102Faは、本発明の第1の不純物 拡散領域に相当する。また、上記の実施形態において、第2の不純物拡散領域102Fb は、本発明の第2の不純物拡散領域に相当する。また、上記の実施形態において、第1の 低濃度不純物領域102Laは、本発明の第1の低濃度不純物領域102Laに相当する 。また、上記の実施形態において、第2の低濃度不純物領域102Lbは、本発明の第2 の低濃度不純物領域102Lbに相当する。また、上記の実施形態において、保持容量素 子103は、本発明の保持容量素子に相当する。また、上記の実施形態において、上部電 極103aは、本発明の第1電極に相当する。また、上記の実施形態において、下部電極 1 0 3 b は、本発明の第 2 電極に相当する。また、上記の実施形態において、誘電体膜 1 03 cは、本発明の誘電体膜に相当する。また、上記の実施形態において、信号配線 2 0 2 は、本発明の第1の導電層に相当する。また、上記の実施形態において、画素電極中継 部402は、本発明の第2の導電層に相当する。また、上記の実施形態において、画素領 域PRは、本発明の画素領域に相当する。

## [0097]

## <参考実施形態2>

## (構成)

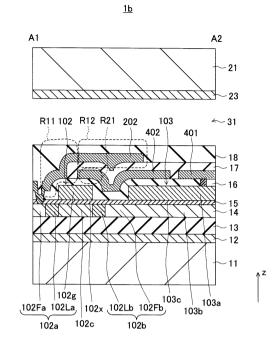

図8,図9は、本発明にかかる<u>参考実施形態2</u>の液晶表示装置において、液晶パネル1 bの要部を示す図である。

## [0098]

ここで、図8は、本発明にかかる参考実施形態2の液晶表示装置において、液晶パネル

10

20

30

40

1 b の一部を示す平面図である。また、図9は、本発明にかかる<u>参考実施形態2</u>の液晶表示装置において、液晶パネル1 b の一部を示す断面図である。図9は、図2において一点鎖線で囲った部分a を示しており、図9のアレイ基板11から層間絶縁膜18までの部分は、図8におけるA1-A2部分について示している。

## [0099]

図8と図9とに示すように、本実施形態の液晶パネル1 b は、信号配線202と画素電極中継部402との形状が、参考実施形態1 と異なる。本実施形態は、この点を除き、参考実施形態1 とほぼ同様である。このため、重複する個所については、説明を省略する。参考実施形態1と異なる部分について説明する。

#### [0100]

信号配線202は、図8と図9とに示すように、参考実施形態1と同様に、画素領域PRにおいて×方向に並ぶ複数の画素電極101の間隔に対応するようにy方向に延在して形成されており、y方向に並ぶ複数の画素スイッチング素子102に接続している。

## [0101]

また、信号配線202は、図8と図9とに示すように、画素領域PRにおいて画素スイッチング素子102に対面する領域を含むように形成されており、画素スイッチング素子102の第1のソース・ドレイン領域102aに接続されている。本実施形態においては、図9にて点線で囲った領域R11として示すように、信号配線202は、それぞれが画素スイッチング素子102の第1のソース・ドレイン領域102aのそれぞれに接続しており、画素スイッチング素子102において第2のソース・ドレイン領域102b以外であって第1のソース・ドレイン領域102aに対面する領域を含むように形成されている。具体的には、信号配線202は、第1の不純物拡散領域102Faに接続されており、第1の低濃度不純物領域102Laと、ゲート電極102gの一部とに、層間絶縁膜16

#### [0102]

また、この他に、本実施形態においては、信号配線202は、画素電極中継部402を介して、画素スイッチング素子102にて第2のソース・ドレイン領域102bに対面する領域を含むように形成されている。具体的には、図9にて点線で囲った領域R12として示すように、信号配線202は、画素スイッチング素子102において第2のソース・ドレイン領域102bに対面する領域に関しては、層間絶縁膜16,17の他に、導電層である画素電極中継部402を介するように形成されている。つまり、信号配線202は、ゲート電極102gの一部と、第2の低濃度不純物領域102Lbと、第2の不純物拡散領域102Fbとに、層間絶縁膜16,17および画素電極中継部402を介して対面するように形成されている。

# [0103]

そして、この信号配線202の上方には、層間絶縁膜18が形成されている。

## [0104]

画素電極中継部402は、図8と図9とに示すように、<u>参考実施形態1</u>と同様に、画素領域PRにおいてy方向に並ぶ複数の画素電極101の間隔に対応するように複数形成されている。本実施形態においては、画素電極中継部402は、それぞれが画素スイッチング素子102の第2のソース・ドレイン領域102bのそれぞれに接続しており(図示なし)、図9にて点線で囲った領域R21として示すように、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bに対面する領域を含むように形成されている。具体的には、画素電極中継部402は、図9に示すように、第2の不純物拡散領域102Fbに接続されており、第2の低濃度不純物領域102Lbと、ゲート電極102gの一部とに、層間絶縁膜16を介して対面するように形成されている。

## [0105]

## (製造方法)

以下より、上記の液晶パネル1bの製造方法について説明する。

10

20

30

40

#### [0106]

上記の液晶パネル 1 b を製造する際には、図 5 ( A ) , 図 5 ( B ) , 図 5 ( C ) , 図 6 (D)に示すように、参考実施形態1と同様の工程を経て、画素スイッチング素子102 の第1の不純物拡散領域102Faと第2の不純物拡散領域102Fbとを形成する。

## [0107]

この後、下記に示すようにして、本実施形態の液晶パネル1bを完成させる。

図10は、本発明にかかる参考実施形態2において、アレイ基板11側の各工程を示す 断面図である。図10においては、図10(A),図10(B),図10(C)の順にて 、アレイ基板11側の各工程を示している。

#### [0109]

上記の工程を経た後、図10(A)に示すように、画素電極中継部402を形成する。

#### [0110]

ここでは、画素電極中継部402と画素スイッチング素子102および保持容量素子1 03との間に介在させる層間絶縁膜16を、まず、形成する。たとえば、CVD法によっ てシリコン酸化物を堆積させることによって、層間絶縁膜16を形成する。その後、アレ イ基板 1 1 を熱処理し、上記のようにしてイオンドーピングされた不純物を活性化させる

## [0111]

この後、第2の不純物拡散領域102Fbの表面を露出するように、層間絶縁膜16に コンタクトホールを形成した後、たとえば、スパッタリング法により、アルミニウム膜な どの導電体膜を、そのコンタクトホールに埋め込むようにして堆積する。

## [0112]

そして、レジストマスクを用いたエッチング処理を実施することにより、その導電体膜 をパターン加工して、画素電極中継部402を形成する。

## [0113]

本実施形態においては、画素スイッチング素子102において第1のソース・ドレイン 領域102a以外であって第2のソース・ドレイン領域102bに対面する領域を含むよ うに画素電極中継部402を形成する。具体的には、第2の低濃度不純物領域102Lb と、ゲート電極102gの一部とに、層間絶縁膜16のみを介して対面する部分を含むよ うに形成する。

## [0114]

つぎに、図10(B)に示すように、層間絶縁膜17を形成する。

### [0115]

ここでは、画素電極中継部402を被覆するように層間絶縁膜17を形成する。たとえ ば、CVD法によってシリコン酸化膜を堆積させた後に、信号配線202を形成する領域 以外をレジストマスクにて覆い、そのシリコン酸化膜をエッチング処理することで、層間 絶縁膜17を形成する。

## [0116]

つぎに、図10(C)に示すように、信号配線202を形成する。

## [0117]

ここでは、第1の不純物拡散領域102Faの表面を露出するように、コンタクトホー ルを形成した後、たとえば、スパッタリング法により、アルミニウム膜などの導電体膜を 、そのコンタクトホールに埋め込むようにして堆積する。

#### [0118]

そして、レジストマスクを用いたエッチング処理を実施することにより、その導電体膜 をパターン加工して、信号配線202を形成する。

本実施形態においては、前述したように、画素スイッチング素子102において第1の ソース・ドレイン領域102aに対面する領域に関しては、層間絶縁膜16,17のみを 10

20

30

40

介するように形成すると共に、画素スイッチング素子102において第2のソース・ドレイン領域102bに対面する領域に関しては、層間絶縁膜16,17の他に、導電層である画素電極中継部402を介するように形成する。

#### [0120]

この後、図9に示すように、信号配線202と画素電極中継部402とを被覆するように、たとえば、プラズマCVD法により、シリコン酸化物を堆積して層間絶縁膜18を形成する。その後、参考実施形態1と同様にして、液晶表示装置を完成させる。

## [ 0 1 2 1 ]

## (動作)

以下より、本実施形態の液晶表示装置の動作について説明する。

## [0122]

上記の液晶パネル1bを駆動する場合においては、<u>参考実施形態1</u>と同様に、図7に示すように、駆動される。

## [0123]

このため、本実施形態は、<u>参考実施形態1</u>と同様に、オフ時のリーク電流の発生を抑制すると共に、高電位HIGHと低電位LOWでの各駆動時においてオフ時の電位保持特性を同等にすることができる。

## [0124]

したがって、本実施形態は、画素領域の開口率を向上させるために、アレイ基板 1 1 の面にて画素スイッチング素子 1 0 2 を信号配線 2 0 2 や画素電極中継部 4 0 2 などの導電層に対面するように形成する場合において、オフ時のリーク電流の発生によって、画像の保持特性が低下することと、反転駆動時においてフリッカや残像が発生することとを防止できるため、画像品質を向上することができる。

## [ 0 1 2 5 ]

なお、上記の本実施形態の各部材は、<u>参考実施形態1</u>と同様に、本発明の構成要素に対応している。

## [0126]

< 実施形態 3 >

## (構成)

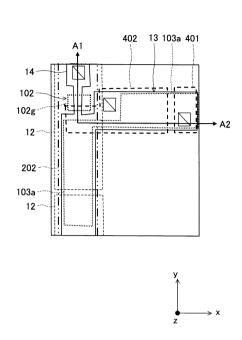

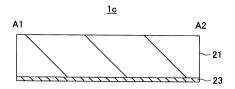

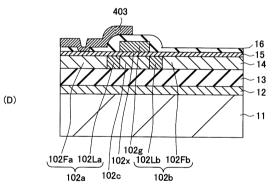

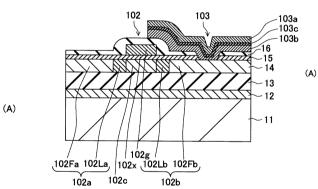

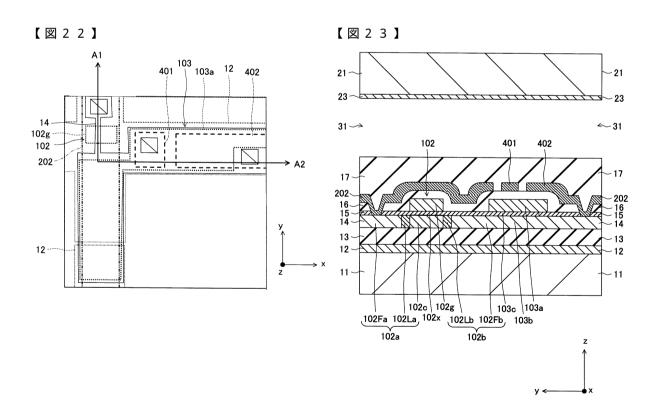

図 1 1 , 図 1 2 は、本発明にかかる実施形態 3 の液晶表示装置において、液晶パネル 1 c を示す図である。

## [0127]

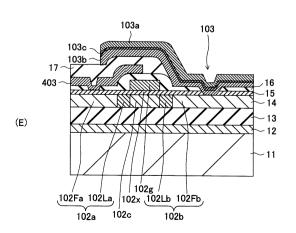

ここで、図11は、本発明にかかる実施形態3の液晶表示装置において、液晶パネル1cの一部を示す平面図である。図12は、本発明にかかる実施形態3の液晶表示装置において、液晶パネル1cの一部を示す断面図である。図11と図12とは、図2において一点鎖線で囲った部分aを示しており、図12のアレイ基板11から層間絶縁膜18までの部分は、図11におけるA1-A2部分について示している。

## [0128]

図11と図12とに示すように、本実施形態の液晶パネル1cは、保持容量素子103 が<u>参考実施形態2</u>と異なる。また、信号配線中継部403を含む。本実施形態は、これらの点を除き、<u>参考実施形態2</u>とほぼ同様である。このため、重複する個所については、説明を省略する。

## [0129]

保持容量素子103は、図11に示すように、×方向とy方向とに並ぶ複数の画素電極101の間隔が交差している部分において、y方向と×方向とのそれぞれへ延在するように形成されている。また、図12に示すように、上部電極103aと、下部電極103 bと、誘電体膜103 c とを含み、画素スイッチング素子102側から、下部電極103 b、誘電体膜103 c , 上部電極103 a が順次形成されている。そして、保持容量素子103は、画素スイッチング素子102に対面する領域を含むように形成されており、画素スイッチング素子102の第2のソース・ドレイン領域102 b に、下部電極103 b が

10

20

30

40

接続されている。本実施形態においては、画素領域PRの垂直方向 z において画素スイッチング素子102と信号配線202とに挟まれるように、保持容量素子103が形成されている。具体的には、図12にて点線で囲った領域R111として示すように、保持容量素子103は、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bを含む領域については、下部電極103bが層間絶縁膜16,17のみを介して対面するように形成されている。また、図12にて点線で囲った領域R112として示すように、保持容量素子103は、画素スイッチング素子102において第1のソース・ドレイン領域102aに対面する領域を含み、この第1のソース・ドレイン領域102aに対面する領域については、下部電極103bが層間絶縁膜16,17の他、導電層である信号配線中継部403を介するように形成されている。

#### [0130]

信号配線中継部403は、図11と図12とに示すように、画素領域PRにおいて×方向に並ぶ複数の画素電極101の間隔に対応するようにy方向に延在するように、導電材料によって形成されており、信号配線202と画素スイッチング素子102とを中継するように接続している。また、信号配線中継部403は、図11と図12とに示すように、画素領域PRにおいて画素スイッチング素子102に対面する領域を含むように形成されており、画素スイッチング素子102に接続されている。本実施形態においては、図12にて点線で囲った領域R211として示すように、信号配線中継部403は、画素スイッチング素子102の第1のソース・ドレイン領域102aに接続されており、画素スイッチング素子102において第2のソース・ドレイン領域102b以外であって第1のソース・ドレイン領域102b以外であって第1のソース・ドレイン領域1025に形成されている。具体的には接続されており、第1の低濃度不純物領域102Laと、ゲート電極102gの一部とに、層間絶縁膜16のみを介して対面するように形成されている。

## [0131]

## (製造方法)

以下より、上記の液晶パネル1cの製造方法について説明する。

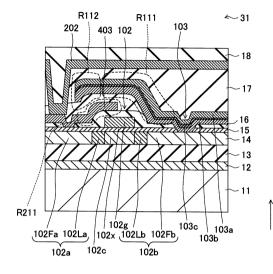

## [0132]

図13は、本発明にかかる実施形態3において、アレイ基板11側の各工程を示す断面図である。図14は、本発明にかかる実施形態3において、図13に次いで、アレイ基板11側の各工程を示す断面図である。図13と図14とにおいては、図13(A),図13(B),図13(C),図14(D),図14(E)の順にて、アレイ基板11側の各工程を示している。

# [0133]

まず、図13(A)に示すように、<u>参考実施形態1</u>と同様にして、アレイ基板11に、 遮光膜12と層間絶縁膜13と半導体層14と絶縁膜15とを順次形成する。

## [0134]

つぎに、図13(B)に示すように、画素スイッチング素子102のゲート電極102 gを形成すると共に、画素スイッチング素子102の第1および第2の低濃度不純物領域 102La,102Lbを形成する。

#### [0135]

ここでは、ゲート絶縁膜102×を構成するシリコン酸化膜の上に、たとえば、CVD法により、ポリシリコン膜を成膜する。その後、そのポリシリコン膜にリンをドーピングし導電体とする。そして、レジストマスクを用いたエッチングにより、そのポリシリコン膜をパターン加工して、半導体層14のチャネル形成領域102cに対応する位置にゲート電極102gを形成する。この後、ゲート電極102gをマスクとして、リンをイオンドーピングし、半導体層14のチャネル形成領域102cを挟むようにして、第1および第2の低濃度不純物領域102La,102Lbを半導体層14に形成する。たとえば、リンを、1~3×10<sup>13</sup>/cm²になるように注入する。

10

20

30

40

#### [0136]

つぎに、図13(C)に示すように、半導体層14において、画素スイッチング素子102の第1および第2の不純物拡散領域102Fbを形成する。

## [0137]

ここでは、半導体層 1 4 において画素スイッチング素子 1 0 2 の第 1 および第 2 の不純物拡散領域 1 0 2 Fa , 1 0 2 Fb を形成する領域以外の領域を、レジストマスク R 1 で覆う。その後、半導体層 1 4 において画素スイッチング素子 1 0 2 の第 1 および第 2 の不純物拡散領域 1 0 2 Fb を形成する領域に、たとえば、リンを、 1 0  $^{1}$   $^{5}$  / c m  $^{2}$  になるようにイオン注入する。そして、レジストマスク R 1 を除去する。

#### [0138]

つぎに、図14(D)に示すように、信号配線中継部403を形成する。

#### [0139]

ここでは、まず、たとえば、CVD法によってシリコン酸化物を堆積させることによって、層間絶縁膜16を形成する。その後、アレイ基板11を熱処理し、上記のようにしてイオンドーピングされた不純物を活性化させる。

#### [0140]

この後、第1の不純物拡散領域102Faの表面を露出するように、層間絶縁膜16にコンタクトホールを形成した後、たとえば、スパッタリング法により、アルミニウム膜などの導電体膜を、そのコンタクトホールに埋め込むようにして堆積する。

## [0141]

そして、レジストマスクを用いたエッチング処理を実施することにより、その導電体膜をパターン加工して、信号配線中継部403を形成する。本実施形態においては、上述したように、画素スイッチング素子102において第2のソース・ドレイン領域102b以外であって第1のソース・ドレイン領域102aに対面する領域を含むように信号配線中継部403を形成する。具体的には、第1の不純物拡散領域102Faに接続されており、第1の低濃度不純物領域102Laと、ゲート電極102gの一部とに、層間絶縁膜16のみを介して対面するように、信号配線中継部403を形成する。

#### [0142]

つぎに、図14(E)に示すように、保持容量素子103を形成する。

#### [ 0 1 4 3 ]

ここでは、まず、たとえば、CVD法によってシリコン酸化物を堆積させることによって、信号配線中継部403を覆うように、層間絶縁膜17を形成する。

#### [0144]

この後、第2の不純物拡散領域102Faの表面を露出するように、層間絶縁膜16にコンタクトホールを形成する。この後、保持容量素子103の下部電極103bと誘電体膜103cと上部電極103aとを順次形成する。本実施形態においては、上述したように、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bを含む領域については、下部電極103bが層間絶縁膜16,17のみを介して対面するように形成する。そして、第1のソース・ドレイン領域102aに対面する領域については、下部電極103bが層間絶縁膜16,17の他、導電層である信号配線中継部403を介するように形成する。

#### [0145]

そして、図12に示すように、保持容量素子103を被覆するように、たとえば、CVD法により、シリコン酸化物の層間絶縁膜18を形成する。そして、信号配線202を<u>参</u>考実施形態1と同様にして形成する。その後、<u>参考実施形態1</u>と同様にして、各部を形成することによって、液晶表示装置を完成させる。

## [0146]

## (動作)

以下より、本実施形態の液晶表示装置の動作について説明する。

## [0147]

10

20

30

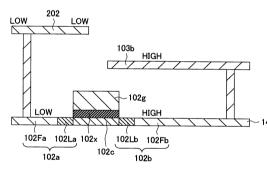

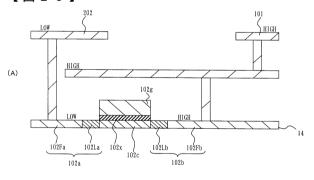

図15は、本発明にかかる実施形態3において、液晶パネル1cを反転駆動させた際にゲートをオフした後に、液晶パネル1cの各部において保持される電位を模式的に示す図である。図15において、図15(A)は、画素電極に高電位が書き込まれた場合を示し、図15(B)は、画素電極に低電位が書き込まれた場合を示している。

## [0148]

図15(A)に示すように、画素電極101が高電位HIGHを保持している場合に、画素スイッチング素子102においてドレインとなる第2のソース・ドレイン領域102 bと、その第2ソース・ドレイン領域102bに対面している保持容量素子103の下部電極103bは、互いに接続されており、同電位である。

## [0149]

一方で、図15(B)に示すように、画素電極101が低電位LOWを保持している場合に画素スイッチング素子102においてドレインとなる第1のソース・ドレイン領域102aと、その第1のソース・ドレイン領域102aに対面している保持容量素子103の下部電極103bは、異なる電位である。しかし、本実施形態においては、互いに対面している第1のソース・ドレイン領域102aと下部電極103bとの間に、その第1のソース・ドレイン領域102aと同電位である信号配線中継部403が層間絶縁膜の他に介在しており、第1のソース・ドレイン領域102aと信号配線中継部403とが対面している。

## [0150]

このため、本実施形態は、オフ時のリーク電流の発生を抑制すると共に、高電位HIGHと低電位LOWでの各駆動時においてオフ時の電位保持特性を同等にすることができる。したがって、本実施形態は、画素領域の開口率を向上させるために、アレイ基板11の面にて画素スイッチング素子102を信号配線202や保持容量素子103などの導電層に対面するように形成する場合において、オフ時のリーク電流の発生によって、画像の保持特性が低下することと、反転駆動時においてフリッカや残像が発生することとを防止できるため、画像品質を向上することができる。

## [0151]

なお、上記の実施形態において、信号配線中継部 4 0 3 は、本発明の第 1 の導電層に相当する。また、上記の実施形態において、下部電極 1 0 3 b は、本発明の第 2 の導電層に相当する。その他の本実施形態の各部材は、参考実施形態 1 と同様に、本発明の構成要素に対応している。

## [0152]

## <参考実施形態4>

## (構成)

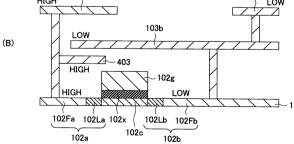

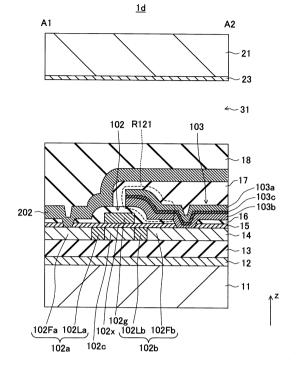

図16,図17は、本発明にかかる<u>参考実施形態4</u>の液晶表示装置において、液晶パネル1dを示す図である。

## [0153]

図16は、本発明にかかる参考実施形態4の液晶表示装置において、液晶パネル1dの一部を示す平面図である。また、図17は、本発明にかかる参考実施形態4の液晶表示装置において、液晶パネル1cの一部を示す断面図である。図16と図17は、図2において一点鎖線で囲った部分aを示しており、図17のアレイ基板11から層間絶縁膜18までの部分は、図16におけるA1-A2部分について示している。

## [0154]

図16と図17とに示すように、本実施形態の液晶パネル1dは、保持容量素子103 が<u>参考実施形態2</u>と異なる。本実施形態は、この点を除き、<u>参考実施形態2</u>とほぼ同様である。このため、重複する個所については、説明を省略する。

#### [0155]

保持容量素子103は、図16に示すように、×方向とy方向とに並ぶ複数の画素電極101の間隔が交差している部分からy方向へ延在するように形成されている。また、図17に示すように、上部電極103aと、下部電極103bと、誘電体膜103cとを含

10

20

30

40

み、画素スイッチング素子102側から、下部電極103b,誘電体膜103c,上部電極103aが順次形成されている。そして、保持容量素子103は、画素スイッチング素子102の第子102に対面する領域を含むように形成されており、画素スイッチング素子102の第2のソース・ドレイン領域102bに、下部電極103bが接続されている。本実施形態においては、画素領域PRの垂直方向zにおいて画素スイッチング素子102と信号配線202とに挟まれるように、保持容量素子103が形成されている。具体的には、図17にて点線で囲った領域R121として示すように、保持容量素子103は、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bを含む領域については、下部電極103bが層間絶縁膜16のみを介して対面するように形成されている。

10

## [0156]

(製造方法)

以下より、上記の液晶パネル1dの製造方法について説明する。

[0157]

上記の液晶パネル1dを製造する際には、図13(A),図13(B),図13(C)に示すように、実施形態3と同様の工程を経て、画素スイッチング素子102の第1の不純物拡散領域102Fbとを形成する。

[0158]

この後、下記に示すようにして、本実施形態の液晶パネル1dを完成させる。

[0159]

20

図18は、本発明にかかる<u>参考実施形態4</u>において、アレイ基板11側の各工程を示す断面図である。図18においては、図18(A),図18(B)の順にて、アレイ基板11側の各工程を示している。

[ 0 1 6 0 ]

上記の工程を経た後、図18(A)に示すように、保持容量素子103を形成する。

[0161]

ここでは、まず、たとえば、CVD法によってシリコン酸化物を堆積させることによって、画素スイッチング素子102を覆うように、層間絶縁膜16を形成する。この後、第2の不純物拡散領域102Faの表面を露出するように、層間絶縁膜16にコンタクトホールを形成する。そして、保持容量素子103の下部電極103bと誘電体膜103cと上部電極103aとを順次形成する。本実施形態においては、上述したように、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bを含む領域については、下部電極103bが層間絶縁膜16のみを介して対面するように形成する。

[0162]

つぎに、図18(B)に示すように、信号配線202を形成する。

[0163]

ここでは、保持容量素子103を被覆するように、たとえば、CVD法により、シリコン酸化物の層間絶縁膜17を形成する。そして、信号配線202を<u>参考実施形態1</u>と同様にして形成する。その後、<u>参考実施形態1</u>と同様にして、各部を形成することによって、液晶表示装置を完成させる。

40

30

[0164]

以下より、本実施形態の液晶表示装置の動作について説明する。

[0165]

図19は、本発明にかかる<u>参考実施形態4</u>において、液晶パネル1dを反転駆動させた際にゲートをオフした後に、液晶パネル1dの各部において保持される電位を模式的に示す図である。図19において、図19(A)は、画素電極に高電位が書き込まれた場合を示し、図19(B)は、画素電極に低電位が書き込まれた場合を示している。

[0166]

図19(A)に示すように、画素電極101が高電位HIGHを保持している場合に、

画素スイッチング素子102においてドレインとなる第2のソース・ドレイン領域102 bと、その第2ソース・ドレイン領域102bに対面している保持容量素子103の下部 電極103bは、互いに接続されており、同電位である。

## [0167]

一方で、図19(B)に示すように、画素電極101が低電位LOWを保持している場合に画素スイッチング素子102においてドレインとなる第1のソース・ドレイン領域102aと、その第1ソース・ドレイン領域102aに対面している信号配線202とは、互いに接続されており、同電位である。

## [0168]

このため、本実施形態は、オフ時のリーク電流の発生を抑制すると共に、高電位HIGHと低電位LOWでの各駆動時においてオフ時の電位保持特性を同等にすることができる。したがって、本実施形態は、画素領域の開口率を向上させるために、アレイ基板11の面にて画素スイッチング素子102を信号配線202や保持容量素子103などの導電層に対面するように形成する場合において、オフ時のリーク電流の発生によって、画像の保持特性が低下することと、反転駆動時においてフリッカや残像が発生することとを防止できるため、画像品質を向上することができる。

## [0169]

なお、上記の本実施形態の各部材は、実施形態3と同様に、本発明の構成要素に対応している。

## [0170]

## <参考実施形態5>

#### (構成)

図 2 0 は、本発明にかかる<u>参考実施形態 5</u>の液晶表示装置において、液晶パネル 1 e の一部を示す平面図である。

## [0171]

図 2 0 に示すように、本実施形態の液晶パネル 1 e は、画素スイッチング素子 1 0 2 と 保持容量素子 1 0 3 とが<u>参考実施形態 4</u> と異なる。本実施形態は、この点を除き、<u>参考実施形態 4</u> とほぼ同様である。このため、重複する個所については、説明を省略する。

## [0172]

本実施形態においては、画素スイッチング素子102は、図20に示すように、走査配線201と信号配線202とが交差する領域の中心にゲート電極102gの中心が対応するように形成されている。

#### [0173]

また、保持容量素子103は、<u>参考実施形態4</u>と同様に、画素スイッチング素子102において第1のソース・ドレイン領域102a以外であって第2のソース・ドレイン領域102bを含む領域に、下部電極103bが層間絶縁膜16のみを介して対面させるために、図20に示すように、画素スイッチング素子102に対応する領域の形状が<u>参考実施</u>形態4と異なるように形成されている。

## [0174]

このため、本実施形態は、<u>参考実施形態 4</u> と同様に、オフ時のリーク電流の発生によって、画像の保持特性が低下することと、反転駆動時においてフリッカや残像が発生することとを防止できること他、画素スイッチング素子102へ外光が入射されることを抑制できるために、光リークすることを防止できる。よって、さらに、画像品質を向上することができる。

## [0175]

なお、上記の本実施形態の各部材は、実施形態3と同様に、本発明の構成要素に対応している。

## [0176]

また、本発明の実施に際しては、上記した実施形態に限定されるものではなく、種々の 変形形態を採用することができる。 10

20

30

40

10

20

30

50

## [0177]

たとえば、本実施形態においては、画素スイッチング素子102として、トップゲート 構造のTFTを用いているが、ボトムゲート構造としてもよい。

【図面の簡単な説明】

[0178]

- 【図1】図1は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の構成を示す断面図である。

- 【図2】図2は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の回路構成を示す回路図である。

- 【図3】図3は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の一部を示す平面図である。

- 【図4】図4は、本発明にかかる<u>参考実施形態1</u>の液晶表示装置において、液晶パネル1の一部を示す断面図である。

- 【図5】図5は、本発明にかかる<u>参考実施形態1</u>において、アレイ基板11側の各工程を示す断面図である。

- 【図6】図6は、本発明にかかる<u>参考実施形態1</u>において、図5に次いで、アレイ基板11側の各工程を示す断面図である。

- 【図7】図7は、本発明にかかる<u>参考実施形態1</u>において、液晶パネル1を反転駆動させた際にゲートをオフした後に、液晶パネル1の各部において保持される電位を模式的に示す図である。

- 【図8】図8は、本発明にかかる<u>参考実施形態2</u>の液晶表示装置において、液晶パネル1 bの一部を示す平面図である。

- 【図9】図9は、本発明にかかる<u>参考実施形態2</u>の液晶表示装置において、液晶パネル1 bの一部を示す断面図である。

- 【図10】図10は、本発明にかかる<u>参考実施形態2</u>において、アレイ基板11側の各工程を示す断面図である。

- 【図11】図11は、本発明にかかる実施形態3の液晶表示装置において、液晶パネル1cの一部を示す平面図である。

- 【図12】図12は、本発明にかかる実施形態3の液晶表示装置において、液晶パネル1cの一部を示す断面図である。

- 【図13】図13は、本発明にかかる実施形態3において、アレイ基板11側の各工程を示す断面図である。

- 【図14】図14は、本発明にかかる実施形態3において、図13に次いで、アレイ基板11側の各工程を示す断面図である。

- 【図15】図15は、本発明にかかる実施形態3において、液晶パネル1cを反転駆動させた際にゲートをオフした後に、液晶パネル1cの各部において保持される電位を模式的に示す図である。

- 【図16】図16は、本発明にかかる<u>参考実施形態4</u>の液晶表示装置において、液晶パネル1dの一部を示す平面図である。

- 【図17】図17は、本発明にかかる<u>参考実施形態4</u>の液晶表示装置において、液晶パネ 40 ル1cの一部を示す断面図である。

- 【図18】図18は、本発明にかかる<u>参考実施形態4</u>において、アレイ基板11側の各工程を示す断面図である。

- 【図19】図19は、本発明にかかる<u>参考実施形態4</u>において、液晶パネル1dを反転駆動させた際にゲートをオフした後に、液晶パネル1dの各部において保持される電位を模式的に示す図である。

- 【図20】図20は、本発明にかかる<u>参考実施形態5</u>の液晶表示装置において、液晶パネル1eの一部を示す平面図である。

- 【図21】図21は、液晶表示装置において、アクティブマトリクス方式の液晶パネル100の回路構成を示す回路図である。

【図22】図22は、液晶表示装置において、アクティブマトリクス方式の液晶パネル100の一部を示す平面図である。

【図23】図23は、アクティブマトリクス方式の液晶パネル100の一部を示す断面図である。

【図24】図24は、液晶パネル100を反転駆動させた際の波形図である。

【図25】図25は、液晶パネル100を反転駆動させた際にゲートをオフした後に、液晶パネル100の各部において保持される電位を示す図である。

【図26】図26は、画素スイッチング素子102を保持容量素子103に対面するように形成する場合において、液晶パネル100を反転駆動させた際にゲートをオフした後に、液晶パネル100の各部において保持される電位を模式的に示す図である。

【図27】図27は、液晶パネルの解像度と、リーク輝点不良率との関係を示す図である

10

20

## 【符号の説明】

## [0179]

1 、1 b 、1 c 、1 d 、1 e …液晶パネル、1 1 …アレイ基板、1 4 …半導体層、1 6 … 層間絶縁膜、2 1 …対向基板、3 1 …液晶層、2 3 …対向電極、1 0 1 …画素電極、1 0 2 c …画素スイッチング素子、1 0 2 x …ゲート絶縁膜、1 0 2 g …ゲート電極、1 0 2 c …チャネル形成領域、1 0 2 a …第 1 のソース・ドレイン領域、1 0 2 b …第 2 のソース・ドレイン領域、1 0 2 F b …第 2 の不純物拡散領域、1 0 2 L b …第 2 の低濃度不純物領域、1 0 2 L b …第 2 の低濃度不純物領域、1 0 3 c …誘電体膜、2 3 …保持容量素子、1 0 3 a …上部電極、1 0 3 b …下部電極、1 0 3 c …誘電体膜、2 0 1 …走査配線、2 0 2 …信号配線、2 0 3 …保持容量配線、3 0 1 …ゲートドライバ、3 0 2 …ソースドライバ、4 0 1 …保持容量素子中継部、4 0 2 …画素電極中継部、4 0 3 …信号配線中継部、P R …画素領域

【図1】 【図3】

# 【図4】

1 **A**1 Α2 21 -**~ 21** 23 -102 R2 31 ~ R1 402 103 401 202 16 15 14 13 11 102g 102Fa 102La 102x 102Lb 102Fb 103a 103ь 102a 102c 102b

# 【図5】

(A)

【図6】

## 【図7】

(A)

【図8】 【図9】

<u>1b</u>

【図10】

【図11】

<u>1c</u>

【図12】

【図13】

(A)

【図14】

【図15】

(A)

(C)

【図16】

【図17】

【図18】

【図19】

(B)

# フロントページの続き

(56)参考文献 特開平05-100250(JP,A)

特開平07-030120(JP,A)

特開平10-111519(JP,A)

特開2004-151546(JP,A)

特開2002-094072(JP,A)

国際公開第01/082273(WO,A1)

(58)調査した分野(Int.CI., DB名)

G02F 1/1368