# (19) 대한민국특허청(KR)

# (12) 공개특허공보(A)

(51)Int. Cl.

HO1L 21/60 (2006.01) HO1L 23/48 (2006.01)

(21) 출원번호

10-2008-0116678

(22) 출원일자

2008년11월24일

심사청구일자

없음

(30) 우선권주장

11/965,383 2007년12월27일 미국(US)

(43) 공개일자

10-2009-0071369

(11) 공개번호

2009년07월01일

(71) 출원인

스태츠 칩팩, 엘티디.

싱가포르, 569059, 테크포인트 #05-17/20, 65 앙 모 키오 스트리트 10

(72) 발명자

카마초, 지그먼드 알.

싱가포르, 싱가포르 789096, 불리온 파크 타워 4, 렌터 루프, 비엘케이 164

메리로, 디오스코로 에이.

싱가포르, 싱가포르 760614, #04-163, 이션스트리 트 61, 비엘케이614

(뒷면에 계속)

(74) 대리인

이만재

전체 청구항 수 : 총 25 항

### (54) 부품들의 웨이퍼 레벨 패키지 집적을 위한 시스템 및 장치

### (57) 요 약

반도체 패키지에서, 기판은 다수 액티브 회로들을 포함하는 액티브 표면을 갖는다. 부착층이 상기 기판 액티브 표면 위에 형성되고, 인지된 우량 유니트(Known Good Unit, KGU)가 부착층에 장착된다. 상호접속 구조체가 KGU 및 기판상의 액티브 회로를 전기적으로 연결시킨다. 상호접속 구조체는 기판상의 접촉 패드 및 KGU상의 접촉 패 드 사이의 와이어 본드, 액티브 표면의 맞은편인 기판의 후방 표면상의 리디스트리뷰션층, 리디스크리뷰션층과 와이어 본드를 전기적으로 연결시키기 위해 기판을 관통하는 관통 홀 비어(THV), 그리고 리디스트리뷰션층과 전 기적 접촉관계에 있는 솔더 범프들을 포함한다. KGU는 그것을 지지하기 위한 KGU 기판과, KGU 기판 위에 위치된 반도체 다이, 그리고 반도체 다이 위에 형성된 캡슐화체를 포함한다.

#### 대 표 도 - 도1

## (72) 발명자

## 타이, 리오넬 치엔 후이

싱가포르, 싱가포르 560413, #09-903, 앙 모 키오 에버뉴 10 비엘케이 413

## 바탄, 헨리 데스칼조

싱가포르, 싱가포르 730352, #06-737, 우드랜즈 에 버뉴 1 비엘케이 352

### 특허청구의 범위

#### 청구항 1

반도체 패키지 제조 방법에 있어서,

다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판을 제공하는 단계;

상기 기판의 상기 액티브 표면 위에 부착층을 형성하는 단계;

상기 부착층에 인지된 우량 유니트(Known Good Unit, KGU)를 장착시키는 단계; 그리고

- (a) 상기 기판상의 접촉 패드 및 상기 KGU상의 접촉 패드 사이에 와이어 본드를 제공하는 단계,

- (b) 상기 액티브 표면의 맞은편인 상기 기판의 후방 표면상에 리디스트리뷰션층을 형성하는 단계,

- (c) 상기 리디스크리뷰션층과 와이어 본드를 전기적으로 연결시키기 위해 상기 기판을 관통하는 관통 홀 비어(THV)를 형성하는 단계, 그리고

- (d) 상기 리디스트리뷰션층과 전기적 접촉관계에 있는 솔더 범프들을 형성하는 단계에 의해 상기 KGU 및 상기 기판상의 액티브 회로들을 전기적으로 연결시키는 상호접속 구조체를 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 2

제 1항에 있어서,

상기 KGU를 지지하기 위한 KGU 기판을 제공하는 단계,

상기 반도체 다이를 상기 KGU 기판 위에 위치시키는 단계, 그리고

상기 반도체 기판 위에 캡슐화체를 형성하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 3

제 1항에 있어서,

상기 KGU 위에 캡슐화체를 형성하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 4

제 1항에 있어서,

상기 THV를 형성하는 단계는 상기 THV 안에 유기 에폭시 재료를 융착시키는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

## 청구항 5

제 1항에 있어서,

상기 KGU는 리드가 없는 평판형 패키지를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 6

제 1항에 있어서,

개별적인 부품들을 상기 기판에 장착시키는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 7

제 1항에 있어서,

상기 반도체 패키지를 프린트 회로 보드에 장착시키는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지

제조 방법.

#### 청구항 8

제 1항에 있어서.

상기 KGU상에 솔더 범프들을 형성하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 9

반도체 패키지 제조 방법에 있어서,

다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판을 제공하는 단계;

상기 기판의 상기 액티브 표면 위에 부착층을 형성하는 단계;

상기 부착층에 인지된 우량 유니트(Known Good Unit, KGU)를 장착시키는 단계; 그리고

상기 KGU 및 상기 기판상의 액티브 회로들을 전기적으로 연결시키는 상호접속 구조체를 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 10

제 9항에 있어서.

상기 상호접속 구조체를 형성하는 단계는:

상기 기판상의 접촉 패드 및 상기 KGU상의 접촉 패드 사이에 와이어 본드를 제공하는 단계;

상기 액티브 표면의 맞은편인 기판의 후방 표면상에 리디스트리뷰션층을 형성하는 단계;

상기 리디스크리뷰션층과 와이어 본드를 전기적으로 연결시키기 위해 상기 기판을 관통하는 관통 홀 비어(THV)를 형성하는 단계; 그리고

상기 리디스트리뷰션층과 전기적 접촉 관계에 있는 솔더 범프를 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 11

제 9항에 있어서,

상기 KGU를 지지하기 위한 KGU 기판을 제공하는 단계,

상기 반도체 다이를 상기 KGU 기판 위에 위치시키는 단계, 그리고

상기 반도체 다이 위에 캡슐화체를 형성하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 12

제 9항에 있어서,

상기 KGU 위에 캡슐화체를 형성하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 13

제 10항에 있어서,

상기 THV를 형성하는 단계는 상기 THV 안에 유기 에폭시 재료를 융착시키는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 14

제 9항에 있어서,

상기 KGU는 리드가 없는 평판형 패키지를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 15

제 9항에 있어서,

개별적인 부품들을 상기 기판에 장착시키는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 16

반도체 패키지 제조 방법에 있어서,

기판을 제공하는 단계;

상기 기판의 제 1 표면에 인지된 우량 유니트(Known Good Unit, KGU)의 제 1 표면을 장착시키는 단계;

상기 KGU 및 기판을 전기적으로 연결시키는 제 1 상호접속 구조체를 형성하는 단계;

상기 기판의 제 1 표면의 맞은편인 상기 기판의 제 2 표면상에 제 2 상호접속 구조체를 형성하는 단계; 그리고

상기 KGU의 제 1 표면의 맞은편인 상기 KGU의 제 2 표면상에 제 3 상호접속 구조체를 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 17

제 16항에 있어서,

상기 제 1 상호접속 구조체를 형성하는 단계는:

상기 기판상의 접촉 패드 및 상기 KGU상의 접촉 패드 사이에 와이어 본드를 제공하는 단계,

상기 기판의 제 2 표면상에 리디스트리뷰션층을 형성하는 단계.

상기 리디스크리뷰션층과 와이어 본드를 전기적으로 연결시키기 위해 상기 기판을 관통하는 관통 홀 비어(THV)를 형성하는 단계, 그리고

상기 리디스트리뷰션층과 전기적 접촉관계에 있는 솔더 범프들을 형성하는 단계를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

#### 청구항 18

제 16항에 있어서,

상기 KGU를 지지하기 위한 KGU 기판을 제공하는 단계,

상기 반도체 다이를 상기 KGU 기판 위에 위치시키는 단계, 그리고

상기 반도체 기판 위에 캡슐화체를 형성하는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 19

제 16항에 있어서,

상기 KGU는 리드가 없는 평판형 패키지를 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 20

제 16항에 있어서,

반도체 소자를 상기 제 2상호접속 구조체에 장착시키는 단계를 또한 포함하는 것을 특징으로 하는 반도체 패키지 제조 방법.

### 청구항 21

반도체 패키지에 있어서,

다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판;

상기 기판의 상기 액티브 표면 위에 형성된 부착층;

상기 부착층에 장착된 인지된 우량 유니트(Known Good Unit, KGU); 그리고

상기 KGU 및 기판상의 액티브 회로들을 전기적으로 연결시키는 상호접속 구조체를 포함하는 것을 특징으로 하는 반도체 패키지.

### 청구항 22

제 21항에 있어서,

상기 상호접속 구조체는:

상기 기판상의 접촉 패드 및 상기 KGU상의 접촉 패드 사이에 접속된 와이어 본드;

상기 액티브 표면의 맞은편인 상기 기판의 후방 표면상에 형성된 리디스트리뷰션층;

상기 리디스크리뷰션층과 와이어 본드를 전기적으로 연결시키기 위해 상기 기판을 관통하여 형성된 관통 홀 비어(THV); 그리고

상기 리디스트리뷰션층과 전기적 접촉관계에 있는 다수 솔더 범프들을 포함하는 것을 특징으로 하는 반도체 패키지.

#### 청구항 23

제 21항에 있어서,

상기 KGU는:

상기 KGU를 지지하기 위한 KGU 기판;

상기 KGU 기판 위에 위치된 반도체 다이; 그리고

상기 반도체 다이 위에 형성된 캡슐화체를 포함하는 것을 특징으로 하는 반도체 패키지.

### 청구항 24

제 21항에 있어서,

상기 KGU 위에 형성된 캡슐화체를 또한 포함하는 것을 특징으로 하는 반도체 패키지.

#### 청구항 25

제 21항에 있어서,

상기 KGU는 리드가 없는 편판형 패키지를 포함하는 것을 특징으로 하는 반도체 패키지.

## 명세서

## 발명의 상세한 설명

#### 기술분야

<!> 본 발명은 일반적으로 반도체 장치, 특히 부품들의 웨이퍼 레벨 집적에 관한 것이다.

### 배경기술

- \*\* 반도체 장치들은 오락, 통신, 네트워크, 컴퓨터, 그리고 가정용 마켓 분야 의 많은 제품들에서 발견된다. 반도체 장치들은 또한 군사, 우주 항공, 자동차, 산업용 콘트롤러 및 사무용 장비에서 발견된다. 반도체 장치들은 이들 응용 분야들 각각에 필요한 다양한 전기적 기능들을 수행한다.

- <3> 반도체 장치들의 제조는 다수 다이를 갖는 하나의 웨이퍼 형성을 포함한다. 각 반도체 다이는 수백 내지 수천의 트랜지스터, 다양한 전기적 기능을 수행하는 다른 액티브 및 패시브 장치들을 포함한다. 주어진 하나의 웨

이퍼에 대해서, 그 웨이퍼로부터의 각 다이는 전형적으로 동일한 적기적 기능을 수행한다. 프론트-엔드(frontend) 제조는 일반적으로 웨이퍼 상에 반도체 장치를 형성하는 것을 의미한다. 최종 웨이퍼는 트랜지스터 및 다른 액티브 및 패시브 부품들을 포함하는 액티브 사이드(active side)를 갖는다. 백-엔드(back-end) 제조는 최종 웨이퍼를 개별적인 다이로 컷팅 또는 싱귤레이팅(singulating)하고 구조적 지지 및 환경적 분리를 위해서 패키징하는 것을 의미한다.

한도체 제조의 한 가지 목표는 신속하고, 신뢰성 있으며, 소형이고 보다 고 밀도의 직접 회로(IC)에 적절한 패키지를 저렴한 비용으로 생산하는 것이다. 플립 칩 패키지(flip chip package), 칩 스케일 패키지(chip scale package, CSP) 또는 웨이퍼 레벨 칩 스케일 패키지(wafer level chip scale package)(WLCSP)는 고속, 고밀도 그리고 큰 핀 수(count)를 요망하는 IC에 이상적으로 적합하다. 플립 칩 스타일 패키징은 다이의 액티브 사이드를 칩 캐리어 기판 또는 프린트 회로 기판(PCB)를 향해 아래로 접하도록 장착시키는 것을 포함한다. 다이상의 액티브 장치들과 캐리어 기판 상의 도전 트랙들 사이의 전기적 및 기계적 상호접속은 다수의 도전성 솔더 범프 또는 볼들을 포함하는 하나의 솔더 범프 구조체를 통해서 달성된다. 그 솔더 범프들은 반도체 기판에 위치된 접촉 패드상에 융착된 솔더 재료에 인가되는 리플로오(reflow) 공정에 의해 형성된다. 이어서 그 솔더 범프들은 캐리어 기판에 솔더된다. 플립 칩 반도체 패키지는, 신호 전파 길이를 감소시키고, 보다 낮은 캐패시턴스 및 전반적으로 양호한 회로 성능을 달성하기 위해서, 다이상의 액티브 장치로부터 캐리어 기판까지의 짧은 전기 도전 경로를 제공한다.

## 발명의 내용

## 해결 하고자하는 과제

당> 많은 응용에서, 두 개 이상의 반도체 장치들 사이에서 웨이퍼 레벨 다이 집적을 이루는 것이 요망된다. 일부 응용은, 예를 들면, 패키지된 인지된 우량 유니트(Known Good Unit, KGU)를 구비한 대규모 회로 칩들의 집적을 필요로 한다. 다른 응용은 시스템-인 패키지 모듈을 형성하도록 패시브 또는 다른 부품들의 집적을 요구할 수 있다.

## 과제 해결수단

- 하나의 실시예에서, 본 발명은, 다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판을 제공하는 단계, 기판의 상기 액티브 표면 위에 부착층을 형성하는 단계, 상기 부착층에 인지된 우량 유니트(Known Good Unit, KGU)를 장착시키는 단계, 그리고 (a) 기판상의 접촉 패드 및 KGU상의 접촉 패드 사이에 와이어 본드를 제공하는 단계, (b) 액티브 표면 맞은편 기판의 후방 표면상에 리디스트리뷰션층을 형성하는 단계, (c) 상기 리디스크리 뷰션층과 와이어 본드를 전기적으로 연결시키기 위해 기판을 관통하는 관통 홀 비어(THV)를 형성하는 단계, 그리고 (d) 상기 리디스트리뷰션층과 전기적 접촉관계에 있는 솔더 범프들을 형성하는 단계에 의해 상기 KGU 및 기판상의 액티브 회로들을 전기적으로 연결시키는 상호접속 구조체를 형성하는 단계를 포함하는 반도체 패키지 제조 방법을 제공한다.

- <7> 다른 하나의 실시예에서, 본 발명은, 다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판을 제공하는 단계, 기판의 상기 액티브 표면 위에 부착충을 형성하는 단계, 상기 부착충에 인지된 우량 유니트(Known Good Unit, KGU)를 장착시키는 단계, 그리고 상기 KGU 및 기판상의 액티브 회로들을 전기적으로 연결시키는 상호접 속 구조체를 형성하는 단계를 포함하는 반도체 패키지 제조 방법을 제공한다.

- <8> 다른 하나의 실시예에서, 본 발명은, 기판을 제공하는 단계, 기판의 제 1 표면에 인지된 우량 유니트(Known Good Unit, KGU)의 제 1 표면을 장착시키는 단계, KGU 및 기판을 전기적으로 연결시키는 제 1 상호접속 구조체를 형성하는 단계, 기판의 제 1 표면 맞은편 기판의 제 2 표면상에 제 2 상호접속 구조체를 형성하는 단계, 그리고 KGU의 제 1 표면 맞은편의 KGU의 제 2 표면상에 제 3 상호접속 구조체를 형성하는 단계를 포함하는 반도체패키지 제조 방법을 제공한다.

- <9> 다른 하나의 실시예에서, 본 발명은, 다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판, 기판의 상기 액 티브 표면 위에 형성된 부착층, 상기 부착층에 장착된 인지된 우량 유니트(Known Good Unit, KGU), 그리고 KGU 및 기판상의 액티브 회로들을 전기적으로 연결시키는 상호접속 구조체를 포함하는 반도체 패키지를 제공한다.

## 直 과

<10> 반도체 패키지는 다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판을 포함한다. 기판 위에, 부착층이

형성된다. KGU가 부착층에 장착되고, 상호접속 구조체가 KGU와 기판상에 형성된 액티브 회로들을 전기적으로 연결시킨다. 이 구조에서, 기판의 액티브 회로들은 KGU안에 형성된 장치들과 연통하고 따라서 KGU에 의해 제공된 기능성을 사용할 수 있다. 따라서 본 방법을 사용하여, KGU의 반도체 패키지로의 집적은 기판의 설계와 그것의 액티브 회로들을 단순화시킨다. 기판안에 복잡한 회로를 포함하는 대신에, 동일한 기능을 포함하는 KGU가 반도체 패키지안에 합체될 수 있다. 예를 들면, 다른 반도체 제조자의 장치에 의해 제공된 기능을 포함하기 원하는 반도체 장치 제조자는, 다른 제조자의 완전하게 패키지된 장치를 직접 합체할 수 있다. 이런 방법으로, 다른 패키지 시스템들에 의해 제공된 복잡한 기능성이 기판 액티브 표면내의 기능성을 복제할 필요 없이 반도체 패키지 안에 합체될 수 있다.

#### 발명의 실시를 위한 구체적인 내용

- <11> 본 발명은 유사한 참조 번호가 동일 또는 유사한 성분들을 나타내는 도면들을 참조하는 다음의 설명에 있는 하나 이상의 실시예들에서 기술될 것이다. 본 발명이 본 발명의 목적을 달성하기 위한 최선 모드 관점에서 기술되지만, 당업자는 첨부된 청구범위와 다음의 설명 및 도면에 의해 지지되는 그들의 균등물에 의해 한정되는 본 발명의 정신 및 범위내에 포함되는 변형, 변화 및 치환물을 커버하는 의도라는 것을 이해할 것이다.

- <12> 반도체 장치들의 제조는 다수 다이를 갖는 하나의 웨이퍼 형성을 포함한다. 각 반도체 다이는 수백 내지 수천의 트랜지스터, 다양한 전기적 기능을 수행하는 다른 액티브 및 패시브 장치들을 포함한다. 주어진 하나의 웨이퍼에 대해서, 그 웨이퍼로부터의 각 다이는 전형적으로 동일한 적기적 기능을 수행한다. 프론트-엔드(frontend) 제조는 일반적으로 웨이퍼 상에 반도체 장치를 형성하는 것을 의미한다. 최종 웨이퍼는 트랜지스터 및 다른 액티브 및 패시브 부품들을 포함하는 액티브 사이드(active side)를 갖는다. 백-엔드(back-end) 제조는 최종 웨이퍼를 개별적인 다이로 컷팅 또는 싱귤레이팅(singulating)하고 구조적 지지 및/또는 환경적 분리를 위해서 패키징하는 것을 의미한다.

- \*13> 반도체 웨이퍼는 일반적으로 그곳에 놓이는 반도체 장치를 갖는 액티브 표면과, 실리콘과 같은 벌크(bulk) 반도체 재료로 형성된 백사이드 표면을 갖는다. 그 액티브 사이드 표면은 다수 반도체 다이를 포함한다. 그 액티브 표면은 적충, 패터닝, 도핑 및 열처리를 포함하는 다수 반도체 공정들에 의해 형성된다. 그 적충 공정에서, 반도체 재료는 열적 산화, 질화, 화학적 중착, 증발 및 스퍼터링을 포함하는 기술들에 의해 기판상에서 성장되거나 또는 융착된다. 포토리소그래피(phtolithograpy)는 표면 영역을 마스킹하고 바람직하지 않은 재료를 에칭제거하여 특수한 구조를 형성하는 것을 포함한다. 도핑 공정은 도펀트(dopant) 재료 농축물을 열확산 또는 이온주입에 의해 주입한다.

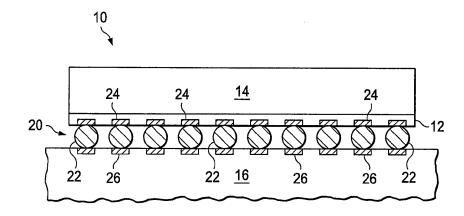

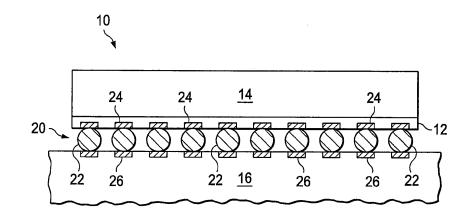

- \*14> 반도체 패키지들, 웨이퍼 레벨 패키지(wafer level package, WLP) 및 칩-스케일 패키지(chip-scale package, CSP)는 통상적으로 고속, 고밀도 및 큰 핀(pin) 수를 요구하는 집적 회로(IC)에 일반적으로 사용된다. 플립 칩스타일(flip chip styel) 반도체 장치(10)는 도 1에 도시된 바와 같이, 다이(14)의 액티브 영역(12)을 칩 캐리어 기판 또는 프린트 회로 보드(16)(PCB)를 향하여 아래로 접하도록 장착시키는 것을 포함한다. 그 액티브 영역(12)은 다이의 전기적 설계에 따른 액티브 및 패시브 장치들, 도전 충들 및 절연 충들을 포함한다. 전기적 및 기계적 상호 접속들이 다수의 개별적인 도전성 솔더 범프들 또는 볼(22)들을 포함하는 솔더 범프 구조체(20)를 통해서 달성된다. 솔더 범프들은 액티브 영역(12)상에 놓인 범프 패드들 또는 상호접속 사이트(24)상에 형성된다. 범프 패드(24)들은 액티브 영역(12)의 도전 트랙들에 의해 액티브 회로에 연결된다. 솔더 범프(22)들은 솔더 리플로우(reflow) 공정에 의해 캐리어 기판(16)상의 접촉 패드 또는 상호접속 사이트(26)에 전기적 또는 기계적으로 연결된다. 신호 전파 길이를 감소시키고, 캐패시턴스를 낮추고, 전반적으로 양호한 회로 성능을 달성하기 위해서 플립 칩 반도체 장치는 다이(14)상의 액티브 장치로부터 캐리어 기판(16)의 도전 트랙까지의 짧은 전기 도전 통로를 제공한다.

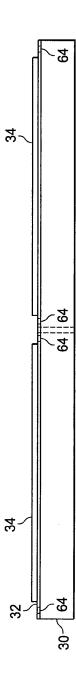

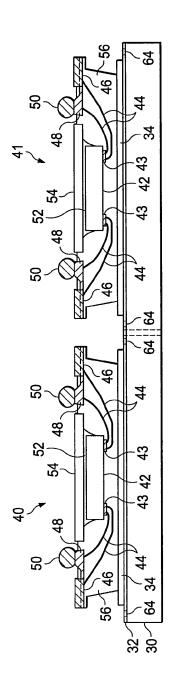

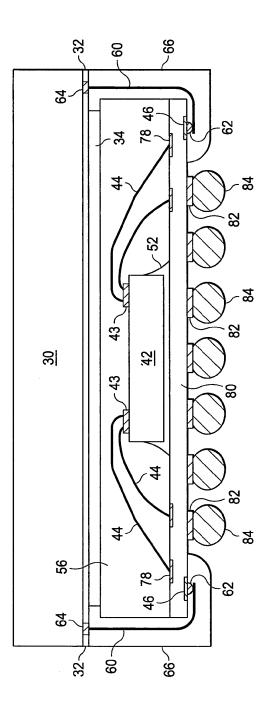

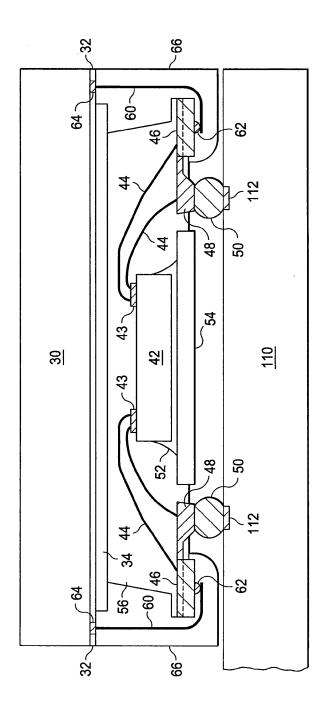

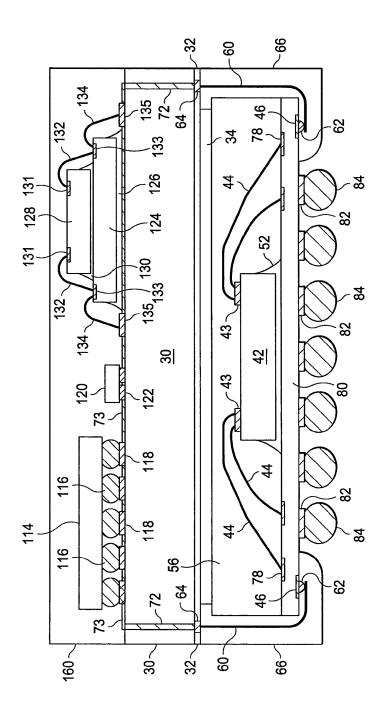

- <15> 도 2a를 참조하면, 칩 스케일 패키지(chip scale package)(CSP), 또는 웨이퍼 레벨 칩 스케일 패키지(wafer level cip scale package)(WLCSP) 제조 공정의 제 1 단계가 도시되었다. 웨이퍼 또는 기판(30)이 그것의 정부면 위에 위치한 패시베이션(32)을 구비한 상태로 형성된다. 그 패시베이션(32)은 폴리이미드(PI), 벤조사이클로 뷰텐(BCB), 또는 폴리벤조옥사졸(PBO)을 포함한다. 웨이퍼(30)는 실리콘 또는 다른 벌크(bulk) 반도체 재료를 포함하고, 프로세서, 마이크로콘트롤러 또는 디지털 신호 프로세서(DSP)용의 하나와 같은 비교적 큰 다이를 포함한다. 웨이퍼(30)내에 형성된 액티브 영역은 장치의 전기적 설계에 따라서 액티브 및 패시브 장치들, 도전층들, 그리고 절연충들을 포함한다. 부착충(34)이 웨이퍼(30)의 패시베이션(32) 위에 위치되고, 열적 에폭시를 포함한다. 다른 실시예에서, 웨이퍼(30)는 웨이퍼 레벨 패키지 또는 다른 반도체 다이 패키지로 대체된다. 접촉 패드(64)가 전해 도금 또는 무전해 도금 공정을 이용하여 웨이퍼(30)위에 형성되고, 도전 재료를 포함한다. 접

촉 패드(64)는 웨이퍼(30)의 액태브 영역내에 형성된 하나 이상의 장치들과 전기적 접촉을 한다. 접촉 패드(64)의 형성은 도전 재료가 그 위에 융착되는 개구들의 형성을 위해 패시베이션(32) 에칭을 포함한다. 접촉 패드(64)는 접촉 패드(64) 위에 추가적인 금속층을 형성하는 것에 의해 금 본딩에 대해 또한 적정화(optimized)될 수 있다. 그 추가적인 금속층은 알루미늄(Al) 또는 금(Au)로 본딩 가능한 다른 하나의 통상적인 접촉 패드 재료를 포함한다.

- <16> 도 2b를 참조하면, 인지된 우량 유니트(Known Good Unit, KGU) 또는 패키지들(40, 41)이 부착층(34)에 부착되고 전기적으로 웨이퍼(30)에 접속된다(도 2c에 도시됨). 패키지들(40, 41)은 하나 이상의 프리-패키지(pre-packaged) 반도체 다이를 포함하고, 그 패키지들(40, 41)을 외부 시스템에 접속시키기 위한 접촉 패드들을 포함한다. 그 패키지들은 필터, 메모리 칩 및 프로세서와 같은 일반적으로 응용되는 집적 회로들을 포함한다. 패키지들이 본 방법을 이용하여 접속된 후에, 패키지들(40, 41)안에 포함된 장치들 및 시스템들은 웨이퍼(30)내에 형성된 장치들과 연통된다. 패키지들(40, 41)의 기능성들이 웨이퍼(30) 및 그안의 장치들에 이용가능하기 때문에, 웨이퍼(30)는 추가적인 기능성을 포함할 필요가 없고 그것의 설계는 단순화된다. 따라서, 본 방법을 사용하여, 기존 패키지에 의해 이미 제공된 특수한 기능을 필요로 하는 웨이퍼(30)는 웨이퍼 안에 형성된 추가적인 회로에 대한 필요성이 없이 그 기능성을 직접 포함할 수 있다.

- <17> 도 2b는 패키지들(40, 41)의 예시적인 구성을 도시하고 있다. 패키지들(40, 41)은 듀얼 로우(dual-row) 리드가 없는 평판형 (quad flat non-leaded)(QFN) 몰디드 패키지들을 포함하고, 웨이퍼(30)와 집적되기 전에 완전히 조립 및 패키지된다. 패키지들(40, 41)은 반도체 다이(42)를 포함한다. 반도체 다이(42)는 그것의 설계에 따라서 액티브 및 패시브 장치들, 도전층들, 그리고 절연층들을 포함하는 액티브 표면을 포함한다.

- <18> 반도체 다이(42)는 그것의 액티브 영역과 전기적 접촉을 하는 접촉 패드(43)를 포함한다. 그 접촉 패드(43)는 전해 도금 또는 무전해 도금 공정과 같은 융착 공정에 의해 형성된다. 접촉 패드들(46, 48)이 패키지들(40, 4 1)의 외측면상에 형성된다. 와이어(44)가 접촉 패드(43)와 접촉 패드들(46, 48) 사이에 전기적 접속을 형성한다.

- <19> 접촉 패드들(46, 48)은 패키지들(40, 41)을 다른 부품들과 전기적으로 연결하는 접촉 패드들의 외부 및 내부 로우(row)를 각각 형성한다. 접촉 패드들(46, 48)은 솔더 범핑 또는 볼 본딩을 사용하여 다른 부품들에 연결된다.

- <20> 다이-부착 부착부(52)는 반도체 다이(42) 및 다이-부착 패들(paddle) 또는 다이 패드(54)를 연결시킨다. 다이 패드(54) 및 접촉 패드들(46, 48)은 패키지들(46, 48)의 구리 리드프래임의 부분을 형성하고, 패키지들의 다른 시스템 부품들과의 전자적 접속을 용이하게 한다. 캡슐화체 또는 몰드 화합물(56)이 반도체 다이(42) 및 와이어 (44) 위에 융착되어 패키지들(40, 41)의 부품들에 대한 또 다른 기계적 지지 및 보호를 제공한다.

- <21> 도 2b를 참조하면, 솔더 범프(50)가 접촉 패드(48) 위에 형성된다. 그 솔더 범프(50)는 접촉 패드(48)상에 융착된 솔더 재료에 인가되는 솔더 리플로어 공정을 사용하여 형성된다. 하나의 실시예에서, 솔더 범프(50)는 패키지들(40, 41)이 웨이퍼(30)에 접속되기 전에 접촉 패드(48)상에 형성된다. 다른 실시예에서, 솔더 범프(50)는 패키지들(40, 41)이 웨이퍼(30)에 연결된 후에 형성된다. 솔더 재료는 볼 드룹(ball drop) 또는 스텐실 (stencil) 프린팅 공정을 사용하여 융착된다. 범프(50)형성에 사용되는 솔더 재료는 각각이 선택적인 융재를 포함하는, Au 또는 Cu 구조체들, 또는 주석/납(Sn/Pb), 구리/아연(Cu/Zn), 또는 구리/은(Cu/Ag) 솔더를 포함한다. 선택적인 언더 범프 메탈라이제이션(under bump metallization)(UBM)이 범프(50) 아래 접촉 패드(48) 위에 형성되어 접촉 패드(48)와 범프(50) 사이의 물리적 그리고 전기적 접속을 강화시킨다. 그 UBM은 먼저 접촉 패드(48) 일부를 에칭하고 증발 또는 스퍼터링 또는 화학적 도금 공정에 의한 진공 융착을 사용하여 하나 이상의 금속층들을 인가함으로써 형성된다. 그 UBM은 각각 1000Å, 3250Å, 그리고 8000Å의 두께를 갖는 티타늄(Ti), 니켈 바나듐산염(NiV), 또는 구리(Cu)와 같은 도전 재료를 포함한다. 구리(Cu)에 대해서, 에천트(etchant)는 약11.15% 질산(HNO3)과 6.3%의 아세트산(CH3COOH)의 A70 또는 약 75.7%의 인산(H3PO4)와 7.35%의 아세트산(CH3COOH)의 A75를 포함한다. 티타늄에 대한 에천트는 1.67%의 과산화 수소 및 잔류 물로된 1.67%의 플로르와 수소일 수 있다.

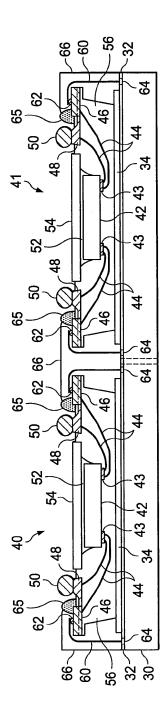

- <22> 도 2c를 참조하면, 와이어 본딩 상호접속이 패키지들(40, 41) 및 웨이퍼(30) 사이에 형성된다. 와이어(60)는 패키지들(40, 41)의 접촉 패드(46)와 접촉 패드(64)를 전기적으로 연결시킨다. 따라서, 웨이퍼(30)안에 형성된 장치들은 반도체 다이(42)안에 형성된 장치들과 연결된다. 와이어(60)는 접촉 패드(64)에 직접 연결되지만, 접촉 패드(46)와는 범프(62)를 경유하여 연결된다. 범프(62)는 전술한 솔더 범프 공정을 이용하여 형성된다. 와이어(60)는 기계적 및 전기적 본드를 형성하도록 열, 압력, 및/또는 초음과 에너지를 이용하는 공정을 사용하여 범 프(62)에 연결된다. 다른 실시예에서, 와이어(60)는 어떤 중간 범프 없이도 접촉 패드(46)에 직접 연결된다. 캡

슐화체 또는 콘포멀(conformal) 코팅(66)이 패키지들(40, 41), 웨이퍼(30) 및 와이어(60) 위에 융착되어 물리적지지 및 전기적 분리를 제공한다. 캡슐화체(66)는 전기 저항성 재료를 포함하고, 프린팅 또는 압축성 몰딩 공정들을 이용하여 융착된다. 선택적인 수지 댐(resin dam)(65)이 캡슐화체(66) 융착 전에 패키지들(40, 41) 위에 융착되어 캡슐화체(66)의 위치를 콘트롤한다. 도 2c 및 도 2d에서, 수지 댐(65)이 캡슐화체(66)의 유동을 제어하여 캡슐화체(66)가 접촉 패드(48) 위로 흐르는 것을 방지한다.

- <23> 도 2d를 참조하면, 웨이퍼(30)가 싱귤래이트되어 웨이퍼(30)상에 형성된 개개 다이와 패키지들(40, 41)을 분리시킨다. 도 2d는 다이상에 연결된 싱글 패키지(68)를 갖는 싱글 다이(30)를 도시하고 있다. 그러나, 다른 실시예에서, 싱글 다이는 하나 이상의 부착층을 경유하여 멀티플 패키지에 연결된다.

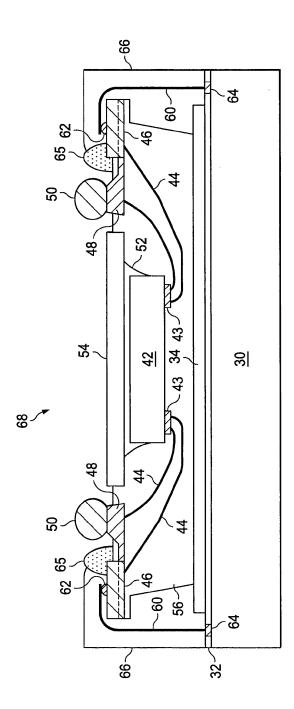

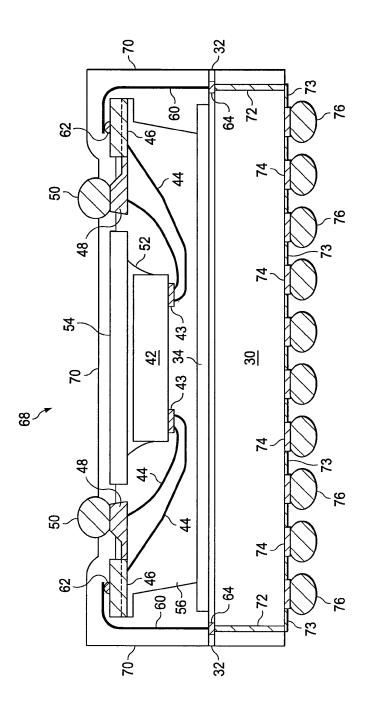

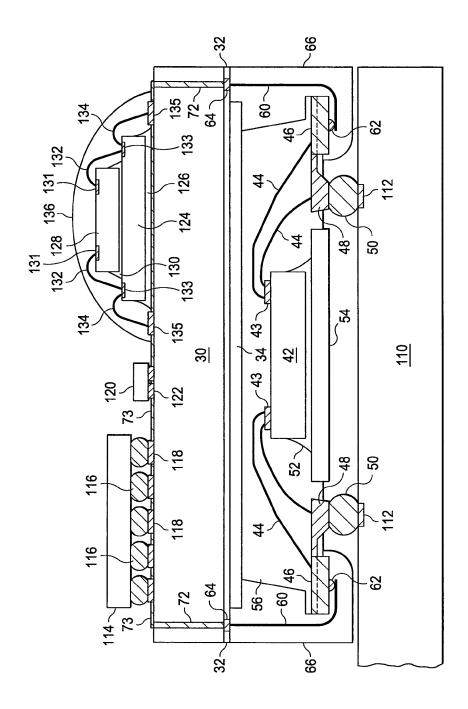

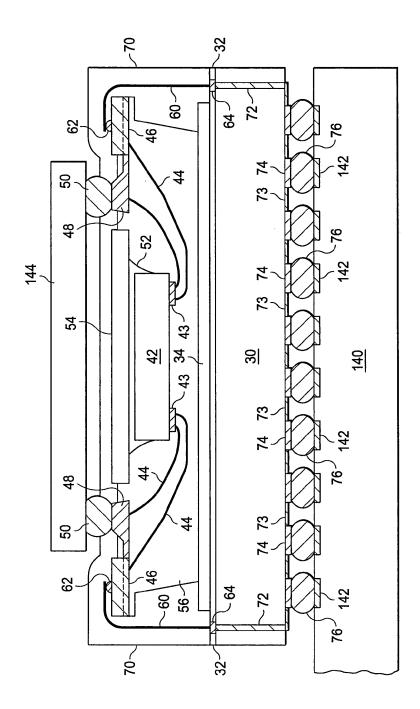

- <24> 도 3은 부착층(34)으로 웨이퍼(30)에 연결된 패키지(68)을 도시하고 있다. 캡슐화체, 몰더 화합물 또는 댐 충진 체(70)가 패키지(68) 위에 형성되어 물리적 지지 및 전기적 분리를 제공한다. 캡슐화체(70)는 완전 콘포멀 코팅 으로서 융착되고, 따라서 도 3에 도시된 바와 같이, 범프(50) 주위에 형성된다. RDL(redistribution layer)(73)이 웨이퍼(30)의 백사이드상에 형성되어 웨이퍼(30)를 다른 시스템 부품들에 연결시킨다. 관통 홀 비 어(through hoe via)(THV)(72)가 에칭 또는 레이저 드릴링하고, 증발, 전해 도금, 무전해 도금 또는 스크린 프 린팅 공정을 사용하여 홀 위에 금속 재료를 융착시키는 것에 의해 웨이퍼(30)에 형성되어 접촉 패드(64) 및 반 도체 다이(42)를 RDL(73)에 전기적으로 연결시킨다. 따라서, THV(72)는 반도체 다이(42)안에 형성된 장치들을 RDL(72) 및 RDL(72)에 연결된 외부 부품들에 전기적으로 연결시킨다. 유기 에폭시 재료가 THV(72)안에 융착되어 접촉 패드(64)에 추가적인 기계적 지지를 제공한다. 추가적인 기계적 지지는 예를 들면, THV(72)의 형성이 하나 이상의 접촉 패드(64) 아래에 불안정한 구조를 초래하는 경우에 중요할 수 있다. 외부 부품들과의 접속을 용이 하게 하기 위해서, 솔더 범프 접촉 패드(74)가 웨이퍼(30)의 백사이드상에 그리고 RDL(72)과의 전기적 접촉관계 로 형성된다. 접촉 패드들(74)은 전해 도금 또는 무전해 도금 공정과 같은 융착 공정에 의해 형성된다. 접촉 패 드(74)는 알루미늄(A1), 알루니늄 합금, 구리(Cu), 니켈(Ni), 금(Au), 은(Ag), 살리사이드(salicide), 또는 폴 리실리콘과 같은 도전 재료를 포함한다. 접촉 패드(74)는 또한 선택적인 UBM을 포함할 수 있다. 범프(76)는 전 술한 솔더 범프 재료를 포함하고, 리플로어되어 접촉 패드(74) 및 범프(76) 사이에 전기적 및 기계적 접속을 제 공한다.

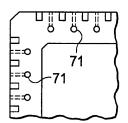

- <25> 도 4는 QFN 접속 구조를 갖는 KGU 또는 패키지에 대한 핀 구조를 도시하고 있다. 도 4에서, KGU 또는 패키지는 내부 로우(internal row)가 대략 원형 모양을 갖는 접속 패드(71)을 포함하는 접속 패드들의 듀얼 로우(dual row)를 포함한다. 원형 모양은 볼드된(balled) 장치들의 KGU 또는 패키지에의 장착을 용이하게 한다.

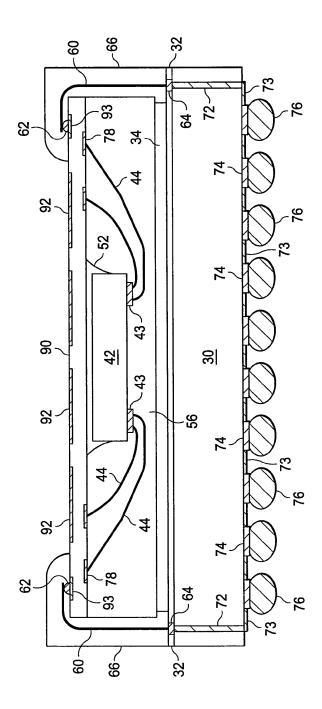

- <26> 도 5는 볼 그리드 어래이(ball grid array)(BGA) 패키지를 갖고, 웨이퍼(30) 위에 장착된 KGU를 도시하는 장치 (10)의 예시적인 실시예를 나타내고 있다. KGU 안에서, 접촉 패드(78)가 기판 또는 프린트 회로 보드(PCB)(80)의 표면상에 형성된다. 반도체 다이(42)는 다이-부착 부착부(52)로 기판(80)상에 물리적으로 장착되고 접촉 패드(43)에 연결된 와이어(44)를 경유하여 접촉 패드(78)에 전기적으로 연결된다. 기판(80)의 제 2 표면상에, 접촉 패드(82)가 형성된다. 접촉 패드들(78, 82)은 도전 재료를 포함하고 전해 도금 또는 무전해 도금 공정에 의해 형성된다. 접촉 패드(82)는 또한 그것의 표면 위에 형성된 UBM을 포함한다. 접촉패드들(78, 82)은 기판(80)안에 형성된 상호접속체 또는 도전층들의 구조에 따라서 전기적 접촉관계에 있다. 범프들(84)이 KGU 상에 형성되고, 접촉 패드(82) 또는 선택적인 UBM에 연결된다. 범프들(84)은 KGU 또는 패키지의 시스템의 외부 부품들에의 전기적 접속을 용이하게 한다. 이 구조에서, 반도체 다이(42)는 웨이퍼(30)의 THV형성 없이도 외부 부품들에 연결될 수 있고, 따라서 장치 제조를 단순화시킨다.

- <27> 도 6은 백사이드 입/출력 리라우팅(rerouting)을 갖는 집적 KGU를 구비한 장치(10)를 도시하고 있다. KGU안에서, 반도체 다이(42)는 기판 또는 PCB(90)의 표면상에 형성된 접촉 패드(78)에 와이어(44)를 경유하여 전기적으로 연결된다. 기판(90)의 제 2 표면상에, 접촉 패드(92)가 형성된다. 접촉 패드(92)는 기판(90)의 상호 접속 구조체에 따라서 접촉 패드(78)와 전기적 접촉관계에 있다. 접촉 패드(92)는 반도체 다이(42)안에 형성된 하나 이상의 장치들과 연결된다. 접촉 패드들(78, 92)은 도전 재료를 포함하고 전해 도금 또는 무전해 도금 공정에 의해 형성된다. 접촉 패드(92)는 또한 그것의 표면상에 형성된 UBM을 포함한다. 접촉 패드(93)가 기판(90)의 제 2 표면상에 형성되고, 접촉 패드(78) 따라서 반도체 다이(42)안에 형성된 하나 이상의 장치들과 전기적 접촉관계에 있다. 범프들(62)이 KGU상에 형성되고, 전술한 적절한 융착 공정 및 재료를 사용하여 접촉 패드(93)에 연결된다. 와이어(60)가 웨이퍼(30)의 패시베이션(32) 위에 형성된 범프들(62) 및 접촉 패드들(64)에 연결된다. THV(72)가 웨이퍼(30)에 형성되고 접촉 패드(64)와 웨이퍼(30)의 백사이드에 형성된 RDL(73)과 전기적으로 연결된다. 접촉 패드(74)는 융착 공정을 이용하여 웨이퍼(30)의 백사이드 위에 형성된다. 범프들(76)이 접촉

패드(74) 또는 그 위에 형성된 선택적인 UBM에 연결된다.

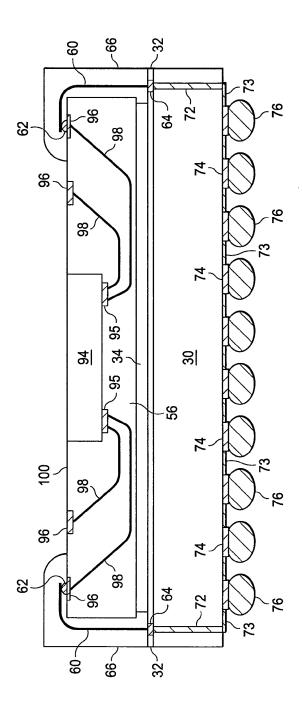

- <28> 도 7은 웨이퍼(30)에 연결된 KGU에서 내부 패키지로서 로우(low)-프로화일, 파인-피치(fine-pitch) 내부 적층 모듈(LFISM)(94)를 도시하고 있다. KGU안에서, 접촉 패드(95)는 LFISM(94)의 표면상에 형성된다. 접촉 패드(95)는 LFISM(94)인에 형성된다. 접촉 패드(95)는 LFISM(94)인에 형성된 하나 이상의 장치들과 전기적 접촉을 이룬다. 접촉 패드(95)는 도전 재료를 포함하고, 전해 도금 또는 무전해 도금 공정을 이용하여 형성된다. 접촉 패드(96)는 캡슐화체(100) 위에 KGU 외측표면에 인접하여 형성된다. 캡슐화체(100)는 전술한 절연 재료를 포함하고, LFISM(94) 위에 융착되어 물리적 지지및 전기적 분리를 제공한다. 와이어(98)는 접촉 패드들(95, 96)에 본딩되고 접촉 패드(96)와 LFISM(94)인에 형성된 장치들과 전기적 접속을 제공한다. 범프들(62)이 적절한 솔더 범프 융착 및 리플로어 공정을 이용하여 하나 이상의 접촉 패드(96)상에 형성된다. KGU 외측에, 와이어(60)가 범프(62)와 웨이퍼(30)상에 형성된 접촉 패드(64)와 연결된다. THV(72)가 접촉 패드(62)에 인접한 웨이퍼(30)에 형성되어 접촉 패드(64)및 RDL(73)에 전기적으로 연결된다. 접촉 패드(74)는 웨이퍼(30)의 백사이드상에 형성되고 RDL(73) 및 접촉 패드(74)위에 형성된 범프들(76)과 전기적으로 연결된다. 추가적인 시스템 부품들이 범프(76)에 연결되고 KGU, 특히 LFISM(94)안에 형성된 장치들과 전기적 접촉관계로 위치될 수 있다.

- 도 8을 참조하면, PCB(110)에 장착된 반도체 장치(10)가 도시되었다. PCB(110)는 FR-4, 폴리미드, BT-에폭시 및 Cu 포일, 도전성 잉크, Au 또는 Ag와 같은 도전 재료와 같은 적층 재료를 포함한다. 접촉 패드(112)가 전해 도금 또는 무전해 도금 공정을 이용하여 PCB(110)의 표면상에 형성된다. 접촉 패드(112)는 Al, 알루니늄 합금, Cu, Ni, Au, Ag, 살리사이드(salicide) 또는 폴리실리콘과 같은 도전 재료를 포함한다. 선택적인 UBM이 접촉 패드(112) 위에 형성될 수 있다. 범프들(50)이 솔더 리플로어 공정을 이용하여 접촉 패드들(48, 112)에 연결된다.

- <30> 도 9를 참조하면, 추가적인 시스템 부품들이 웨이퍼(30)에 연결되고 KGU안에 형성된 장치들과 전기적 접촉 관계로 위치된다. 부품(114)은 웨이퍼(30)에 연결되는 개별적인 부품이며, 메모리 IC, 필터 IC, 마이트로콘트롤러, 프로세서, CSP, 또는 웨이퍼 레벨 칩 스케일 패키지(WLCSP)를 포함할 수 있다. 부품(114)은 BGA, PGA, 플립 칩설계, 다른 표면 장착 기술(surface mount technology)(SMT) 또는 리드-베이스 장착 기술을 이용하여 웨이퍼(30)에 연결된다. 도 9에서, 부품(114)은 범프(116)를 경유하여 웨이퍼(30)의 접촉 패드(118)에 연결된다. 접촉 패드(118)는 도전 재료를 포함하고, 융착 공정을 이용하여 형성된다. 접촉 패드(118)는 웨이퍼(30)에 안에 형성된 장치들, RDL(73), THV(72)와 전기적 접촉 관계에 있다. 선택적인 UBM이 접촉 패드(118)상에 형성되어 접촉 패드(118)와 범프(116) 사이에 물리적 및 전기적 접속을 강화시킨다.

- <31> 패시브 장치(120)가 적절한 SMT를 이용하여 접촉 패드(122)에 연결된다. 패시브 장치(120)는 레지스터, 캐패시터, 인덕터, 다이오드, 필터 또는 그들의 조합을 포함한다. 접촉 패드들(112)이 웨이퍼(30) 표면상에 형성되고, Al, 알루니늄 합금, Cu, Ni, Au, Ag, 살리사이드(salicide) 또는 폴리실리콘과 같은 도전 재료를 포함한다. 접촉 패드(122)가 웨이퍼(30)안에 형성된 하나 이상의 장치들, RDL(73), 또는 THV(72)와 전기적 접촉 관계에 있다.

- <32> 부품(124)이 언더필 재료(126)로 웨이퍼(30) 위에 장착된다. 언더필 재료(126)는 부품(124)에 물리적 지지를 제공하고 웨이퍼(30)와 부품(124) 사이에 히트 브리지(heat bridge)로서 작용한다. 부품(124) 위에, 부품(128)이 언더필 재료(130)를 이용하여 비슷하게 장착된다. 접촉 패드(132)가 부품(128) 표면에 형성된다. 와이어(132)가 접촉 패드들(131, 133)에 본딩된다. 접촉 패드(133)는 부품(124)의 표면상에 형성된다. 와이어(134)가 웨이퍼(30)의 표면상에 형성된 접촉 패드들(133, 135)에 본딩된다. 접촉 패드들(131, 133, 135)은 Al, 알루니늄 합금, Cu, Ni, Au, Ag, 살리사이드(salicide) 또는 폴리실리콘과 같은 도전 재료를 포함한다. 접촉 패드(135)가 웨이퍼(30)안에 형성된 하나 이상의 장치들, RDL(73), 또는 THV(72)와 전기적 접촉 관계로 형성된다. 캡슐화체 또는 콘포멀 코팅(136)이 부품들(124, 128) 위에 융착된다. 캡슐화체(136)는 부품들(124, 128)에 대해서 물리적보호 및 전기적 분리를 제공한다. 다른 실시예에서, 패시브 및 액티브 부품들을 포함하는 부품들의 상이한 조합들이 플립 칩, 와이어 본딩, BGA 또는 PGA 장착 공정을 이용하여 웨이퍼(30)에 연결된다.

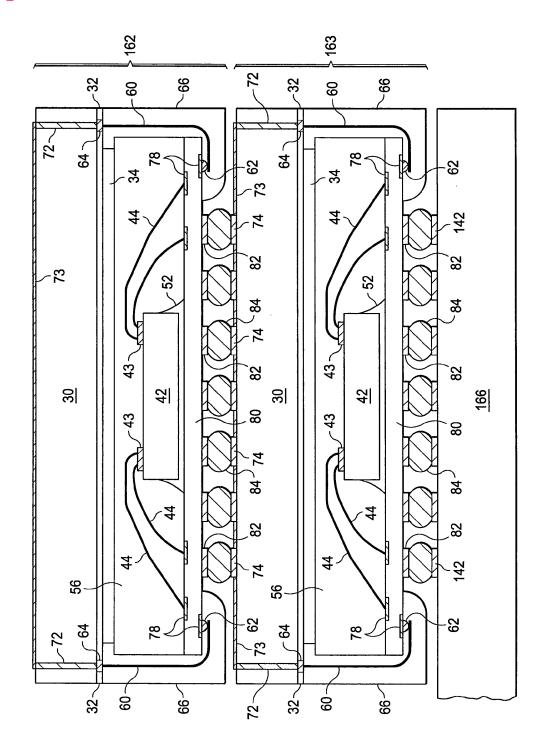

- <33> 도 10을 참조하면, PCB(140)상에 장착된 반도체 장치(10)가 도시되었다. 접촉 패드(142)가 전해 도금 또는 무전해 도금 공정과 같은 적절한 융착 공정에 의해 PCB(140)의 표면상에 형성된다. 범프(76)가 접촉 패드들(74, 142)에 연결된다. 범프(76)는 전술한 솔더 범프 재료를 이용하여 형성된다. 외부 패키지(144)가 접촉 패드(48)위에 형성된 범프(50)에 장착된다. 범프(50)는 와이어(44) 및 반도체 다이(42)안에 형성된 장치들과 전기적 접촉관계에 있다. 다른 실시예에서, 패키지(144)는 BGA, LGA, 플립 칩 또는 다른 장착 공정을 이용하여 접촉 패드(48)에 장착된다. 패키지(144)는 CSP, WLCSP, 패지지-인-패키지(PIP), 또는 하나 이상의 액티브 또는 패시브 장

치들을 포함하는 다른 패키지 또는 IC를 포함한다.

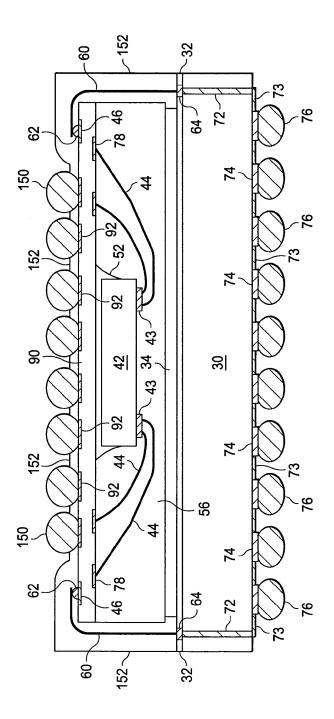

- <34> 도 11에서, 범프(150)는 접촉 패드(92)에 연결된다. 범프(150)는 접촉 패드(92)상에 융착된 솔더 재료에 인가된 솔더 리플로어 공정을 이용하여 형성된다. 그 솔더 재료는 볼 드롭 또는 스텐실 프린팅 공정을 이용하여 융착된다. 범프(150) 형성에 사용된 그 솔더 재료는 각각이 선택적인 융재를 포함하는 Au, 또는 Cu 구조체, 또는 Sn/Pb, CuZn, 또는 CuAg 솔더와 같은 다른 도전 재료를 포함한다. 선택적인 UBM이 범프(150) 아래에 접촉 패드(92) 위에 형성되어 접촉 패드(92)와 범프(150) 사이에 물리적 및 전기적 접속을 강화시킬 수 있다. UBM은 먼저 접촉 패드(92) 일부를 에칭하고 증발 또는 스퍼터링 또는 화학적 도금 공정에 의한 진공 융착을 사용하여 하나 이상의 금속충들을 인가함으로써 형성된다. 캡슐화체 또는 다른 댐 충진 재료(152)가 기판(90)과 범프(150)위의 주위에 융착된다. 캡슐화체(152)는 에폭시 아크릴레이트, 또는 다른 폴리머 재료를 포함하고, 트랜스포 몰딩(transfer molding), 액상 캡슐화체 몰딩, 또는 다른 몰딩 공정을 이용하여 융착된다. 융착 동안에, 크리핑(creeping) 또는 모세관 작용이 캡슐화체(152)가 범프(150)안에 그리고 주위에 유동하게 할 수 있다.

- <35> 도 12는 추가적인 부품들(114, 120, 124, 128)을 구비한 도 5의 실시예를 도시하고 있다. 도 12에서, 캡슐화체(136)는 부품들 위에 융착되지 않고, 대신에 웨이퍼 레벨 몰드 또는 캡슐화체(160)가 부품들(114, 120, 124, 128) 및 웨이퍼(30)위에 융착된다. 캡슐화체(160)는 절연 재료를 포함하고, 프린팅 또는 압축 몰딩 공정들을 이용하여 융착된다.

- <36> 도 13은 보드(board) 레벨 적층 구조에서의 장치들(162, 163)을 도시하고 있다. 범프들(84)이 접촉 패드들(82, 74) 사이에 기계적 및 전기적 접속을 제공한다. 범프들(84)이 솔더 융착 및 리플로어 공정에 의해 형성된다. 도 13에서, 어떤 범프도 장치(162)의 정부면에서는 형성되지 않는다. 그러나 다른 실시예에서, 접촉 패드 및 범프들은 장치(162)의 정부면에 형성되어 장치(162)를 추가적인 스시템 부품들에 접속시킨다.

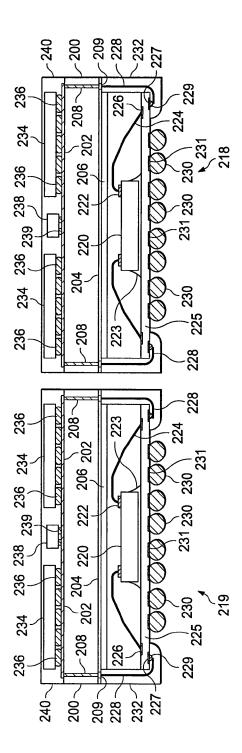

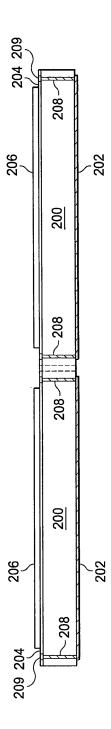

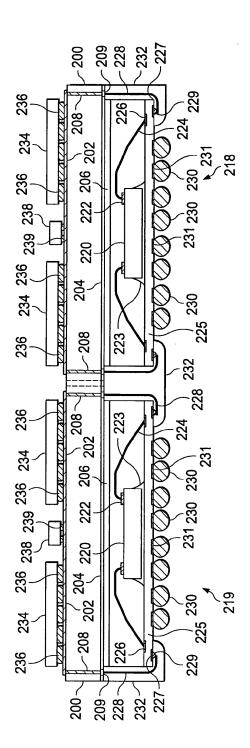

- <37> 도 14a-14d는 CSP 또는 WLCSP에 대한 다른 제공 공정을 도시하고 있다. 웨이퍼 또는 기판(200)이 그것의 정부면에 형성된 패시베이션(204)을 갖는다. 패시베이션(204)은 폴리이미드, BCB 또는 PBO를 포함한다. 웨이퍼(200)는 실리콘 또는 다른 적절한 벌크 반도체 재료를 포함한다. 웨이퍼(200)는 프로세서, 마이크로콘트롤러, 또는 DSP용의 하나와 같은 비교적 큰 다이를 포함한다. 패시베이션(204) 위에, 부착층(206)이 융착된다. 웨이퍼(200)의백사이드상에 웨이퍼 레벨 RDL(202)이 융착된다. RDL(202)은 패시베이션, Cu 트래이스 및 UBM 또는 비스말레이미드-트리아진(bismaleimide-triazine)(BT) 적충 PCB와 같은 적충 플랙스(flex) 테이프를 포함한다. 홀들이 에청 및 레이저 드릴링을 사용하여 웨이퍼(200)에 형성된다. Cu, Au 또는 Ag와 같은 도전 재료가 증발, 전해도금, 무전해도금 또는 스크린 프린팅 공정을 사용하여 홀안에 융착되어 THV(208)을 형성한다. 따라서, THV(208)는 접촉 패드(209) 및 RDL(202) 사이에 전기적 접속을 제공한다. 웨이퍼(200) 위에 접촉 패드(209)가 융착 공정을 사용하여 형성되고, 접촉 패드(209) 위에 추가적인 금속층을 형성하여 금 본당에 대하여 적정화될수 있다. 그 추가적인 금속층은 Al 또는 Au로 본당가능한 다른 통상적인 접촉 패드를 포함할수 있다. 더욱이,유기 에폭시 재료가 THV(208)안에 융착되어 접촉 패드(209)에 대한 추가적인 기계적 지지를 제공할수 있다. 접촉 패드(209)는 패시베이션(204)의 개구를 에칭하고 도전 재료를 개구 위에 융착하여 형성된다.

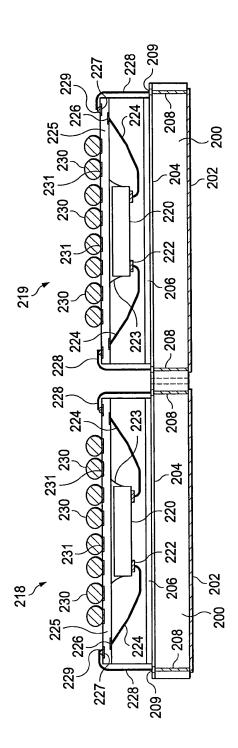

- <38> 도 14b에서, 패키지들(218, 219)은 부착충(206)에, 그리고 그것에 의해 웨이퍼(200)에 연결된다. 패키지들(218, 219)은 전술한 바와 같은 완전히 조립된 패키지를 포함하는 어떤 KGU를 포함한다. 예를 들면, 패키지들(218, 219)은 웨이퍼(200) 형성 전에 제조 및 패키지된 미리 제조된 KGU를 포함한다. 예비 제조된 KGU 또는 패키지들은 웨이퍼(200)에 접속되고 웨이퍼(200) 안에 형성된 장치들과 본 방법에 따른 시스템 부품들과 전기적으로 연통한다.

- <39> 도 14b는 패키지들(218, 219)의 예시적인 구성을 도시하고 있다. 패키지들(218, 219)은 반도체 다이의 설계에 따른 액티브 및 패시브 장치들, 도전층들, 그리고 절연층들을 포함하는 액티브 표면을 갖는 반도체 다이(220)를 포함한다. 패키지들(218, 219)은 플립 칩 접속, QFN 패키징, 와이어 본딩, 플렉스 테입 입/출력 리라우터 (rerouter), 또는 BAG(PGA, BGA 그리고 로우(low) 프로화일 파인 피치 BGA를 포함하는)와 같은 외부 부품에의 접속을 위한 메카니즘을 포함한다.

- <40> 반도체 다이(220)는 전해 도금 또는 무전해 도금 공정과 같은 융착 공정에 의해 형성된 접촉 패드(222)를 포함한다. 반도체 다이(220)는 다이-부착 부착층(223)을 사용하여 기판(225) 위에 장착된다. 기판(225)은 리드프래임, 반도체 재료, 또는 PCB 재료 또는 반도체 다이(220)를 장착하고 그 위에 전기적 접촉을 형성하기 위한 다른구조 또는 재료를 포함한다. 접촉 패드(226)가 기판(225)의 제 1 표면상에 형성된다. 와이어(224)가 접촉 패드들(222, 226) 사이에 전기적 접촉을 형성한다.

- <41> 접촉 패드(227)가 적절한 융착 공정 및 재료를 사용하여 기판(225)의 제 2 표면상에 형성된다. 와이어(228)가 접촉 패드들(227, 209)를 전기적으로 연결시킨다. 접촉 패드(227)는 또한 범프들(229) 및 접촉 패드(227) 위에 형성된 선택적인 UBM을 포함한다. 와이어(228)는 범프(229)에 연결되고 따라서 접촉 패드(227)에 전기적 및 기계적으로 본딩된다.

- <42> 범프들(230)이 또한 접촉 패드(231)위의 기판(225)의 제 2 표면 위에 형성된다. 범프들은 각각이 선택적인 융재를 함유하는 Au, 또는 Cu 구조체 또는 Sn/Pb, CuZn, 또는 CuAg 솔더와 같은 도전 재료를 포함한다. 접촉 패드 (231)가 전해 도금 또는 무전해 도금 공정과 같은 융착 공정을 이용하여 형성된다. 범프들(230)은 장치의 외부부품들과의 접속을 용이하게 한다.

- <43> 도 14c를 참조하면, 캡슐화체 또는 콘포멀 코팅(232)이 패키지들(218, 219) 위에 융착된다. 캡슐화체(232)는 에 폭시 아크릴래이트 또는 다른 폴리러 재료를 포함하고, 트랜스포(transfer) 몰딩, 액상 캡슐화체 몰딩, 또는 다른 몰딩 공정을 사용하여 융착된다. 그것의 도포 방법에 방법에 따라서, 캡슐화체(232)는 기판(225)의 제 2 표면 및 범프들(230) 위에 융착된다. 그러나, 본 실시예에서는, 캡슐화체(232)는 와이어(228) 위에 융착되어 기계적 지지 및 전기적 분리를 제공한다.

- <44> 추가적인 부품들(234)이 RDL(202) 위에 장착된다. 부품들(234)이 필터 칩, 메모리 IC, 마이크로콘트롤러, CSP, WLCSP등을 포함한다. 부품들(234)은 BGA 또는 PGA와 같은 SMT를 사용하여 RDL(202)에 장착된다. 도 14c에서, 부품들은 범프들(236)을 사용하여 장착된다. 범프들(236)은 도전 재료를 포함하고, 솔더 리플로어 공정을 사용하여 형성된다. 범프들(236)은 RDL(202) 및 부품들(234)의 접촉 패드들을 전기적으로 접속시킨다.

- <45> 부품들(238)은 또한 전기적 도전 접촉 포인트(239)를 이용하여 RDL(202)에 장착된다. 접촉 포인트(239)는 도전 재료를 포함한다. 부품들(238)은 BGA와 같은 SMT 또는 플립 칩 장착을 사용하여 RDL(202)에 연결된다.

- <46> 도 14d로 돌아가서, 캡슐화체 및 몰딩 화합물(200)이 부품들(234, 238), RDL(202) 및 웨이퍼(200) 위에 융착된다. 웨이퍼(220)는 싱귤래이트되어 웨이퍼(200)상에 형성된 개별적인 다이를 분리시킨다.

- <47> 요약하면, 반도체 패키지는 다수 액티브 회로들을 포함하는 액티브 표면을 갖는 기판을 포함한다. 기판 위에, 부착층이 형성된다. KGU가 부착층에 장착되고, 상호접속 구조체가 KGU와 기판상에 형성된 액티브 회로들을 전 기적으로 연결시킨다. 이 구조에서, 기판의 액티브 회로들은 KGU안에 형성된 장치들과 연통하고 따라서 KGU에 의해 제공된 기능성을 사용할 수 있다. 따라서 본 방법을 사용하여, KGU의 반도체 패키지로의 집적은 기판의 설 계와 그것의 액티브 회로들을 단순화시킨다. 기판안에 복잡한 회로를 포함하는 대신에, 동일한 기능을 포함하는 KGU가 반도체 패키지안에 합체될 수 있다. 예를 들면, 다른 반도체 제조자의 장치에 의해 제공된 기능을 포함 하기 원하는 반도체 장치 제조자는, 다른 제조자의 완전하게 패키지된 장치를 직접 합체할 수 있다. 이런 방법 으로, 다른 패키지 시스템들에 의해 제공된 복잡한 기능성이 기판 액티브 표면내의 기능성을 복제할 필요 없이 반도체 패키지안에 합체될 수 있다.

- <48> 본 발명의 하나 이상의 실시예들이 상세히 기술되었지만, 다음의 청구범위에 기술된 본 발명의 범위를 이탈하지 않는 한 그 실시예들에 변형과 변화가 가능함을 이해할 것이다.

## 도면의 간단한 설명

- <49> 도 1은 다이 액티브 영역과 칩 캐리어 기판 사이에 전기적 상호접속을 제공하는 솔더 범프를 구비한 플립 칩 반도체 장치를 도시하는 도면;

- <50> 도 2a-2d는 반도체 패키지 제조 방법을 도시하는 도면;

- <51> 도 3은 리디스트리뷰션층을 구비한 반도체 패키지를 도시하는 도면;

- <52> 도 4는 반도체 장치에 대한 접촉 패드 구조를 도시하는 도면;

- <53> 도 5는 입출력 단자들을 갖는 내부 패키지를 구비한 반도체 패키지를 도시하는 도면;

- <54> 도 6은 백사이드 리라우팅을 구비한 반도체 패키지를 도시하는 도면;

- <55> 도 7은 로우 프로화일, 파인-피치 내부 적층 모듈을 포함하는 반도체 패키지를 도시하는 도면;

- <56> 도 8은 장착된 반도체 패키지를 도시하는 도면;

- <57> 도 9는 부착된 개별 부품들을 구비한 반도체 패키지를 도시하는 도면;

- <58> 도 10은 싱글 부착 개별 부품을 구비한 반도체 패키지를 도시하는 도면;

- <59> 도 11은 적층 반도체 패키지를 도시하는 도면;

- <60> 도 12는 부착된 개별 부품들 및 웨이퍼-레벨 모듈을 구비한 반도체 패키지를 도시하는 도면;

- <61> 도 13은 적충된 두 개의 반도체 패키지를 도시하는 도면; 그리고

- <62> 도 14a-14d는 반도체 패키지 제조의 제 2 방법을 도시하는 도면이다.

- <63> <도면의 주요 부분에 대한 부호의 간단한 설명>

<64> 10 : 반도체 장치 14 : 반도체 다이

22 : 솔더 범프 30 : 웨이퍼

<66> 34 : 부착층 40, 41 : 패키지

<67> 44 : 와이어 50 : 솔더 범프

## 도면

<65>

## 도면2a

## 도면2b

## 도면2c

## 도면2d

도면14a

## 도면14b

## 도면14c

## 도면14d