# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.) *H01L 27/146* (2006.01)

(21) 출원번호 10-2014-0106726

(22) 출원일자 **2014년08월18일** 심사청구일자 **없음**  (71) 출원인

(11) 공개번호

(43) 공개일자

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

10-2016-0021473

2016년02월26일

(72) 발명자

이전숙

서울특별시 송파구 올림픽로51길 61-9 (풍납동)

김영찬

경기도 성남시 분당구 느티로 70, 312동 1004호( 정자동, 느티마을3단지)

(뒷면에 계속)

(74) 대리인

윤재석, 한지희, 권영규

전체 청구항 수 : 총 10 항

(54) 발명의 명칭 글로벌 셔터 이미지 센서와 이를 포함하는 이미지 처리 시스템

#### (57) 요 약

본 발명의 실시 예에 따른 글로벌 셔터 이미지 센서는 제1표면과 제2표면을 포함하는 반도체 기판, 상기 반도체 기판 내에 형성되는 광전 변환 영역, 상기 반도체 기판 내에서 상기 광전 변환 영역의 주위에 형성된 저장 다이오드, 상기 반도체 기판 내에서 상기 광전 변환 영역의 위(above)에 형성된 드레인 영역, 상기 반도체 기판 내에서 상기 저장 다이오드의 위(above)에 형성된 플로팅 디퓨전 영역, 상기 광전 변환 영역으로부터 제1전하들을 상기 드레인 영역으로 전송하는 오버플로우 게이트, 상기 광전 변환 영역으로부터 제2전하들을 상기 저장 다이오드로 전송하는 저장 게이트, 및 상기 저장 다이오드로부터 상기 제2전하들을 상기 플로팅 디퓨전 영역으로 전송하는 전송 게이트를 포함하고, 상기 오버플로우 게이트, 상기 광전 변환 영역, 상기 저장 게이트, 상기 저장 다이오드로, 상기 전송 게이트, 및 상기 플로팅 디퓨전 영역은 일렬로 형성된다.

### 대 표 도 - 도2

### (72) 발명자

# 안정착

경기도 용인시 기흥구 동백7로 80, 2201동 1704호 (동백동, 백현마을코아루아파트)

### 정영우

경기도 용인시 기흥구 탑실로 152, 215동 1702호( 공세동, 탑실마을대주피오레2단지아파트)

### 명세서

### 청구범위

#### 청구항 1

제1표면과 제2표면을 포함하는 반도체 기판;

제1픽셀;

제2픽셀; 및

제3픽셀을 포함하고,

상기 제2픽셀의 제1오버플로우 게이트, 제1광전 변환 영역, 및 제1저장 게이트는 상기 제1픽셀의 제1신호 처리 영역의 사이에 형성되고,

상기 제3픽셀의 제2오버플로우 게이트, 제2광전 변환 영역, 및 제2저장 게이트는 상기 제2픽셀의 제2신호 처리 영역의 사이에 형성되고,

상기 제2픽셀의 제1저장 다이오드, 제1전송 게이트, 및 제1플로팅 디퓨전 영역은 상기 제1저장 게이트와 상기 제2광전 변환 영역 사이에 형성되고,

상기 제1오버플로우 게이트, 상기 제1광전 변환 영역, 상기 제1저장 다이오드, 및 상기 제1플로팅 디퓨전 영역 은 일렬로 배열되는 글로벌 셔터 이미지 센서.

#### 청구항 2

제1항에 있어서,

상기 제2신호 처리 영역은 제1소스 팔로워, 제1선택 트랜지스터, 및 제1리셋 트랜지스터를 포함하는 글로벌 셔터 이미지 센서.

#### 청구항 3

제1항에 있어서,

상기 제1오버플로우 게이트, 상기 제1저장 게이트, 및 상기 제1전송 게이트는 상기 제1표면에 형성되고,

상기 제1광전 변환 영역, 상기 제1저장 다이오드, 및 상기 제1플로팅 디퓨전 영역은 상기 반도체 기판 내부에 형성되는 글로벌 셔터 이미지 센서.

## 청구항 4

제1항에 있어서,

상기 제1광전 변환 영역은 상기 제1표면과 상기 제2표면 중에서 어느 하나를 통해 수신된 입사광에 응답하여 전하들을 생성하고,

상기 제1저장 다이오드는 상기 제1광전 변환 영역의 주위에 형성되고,

상기 제1플로팅 디퓨전 영역은 상기 제1저장 다이오드의 위(above)에 형성되는 글로벌 셔터 이미지 센서.

#### 청구항 5

제1항에 있어서.

상기 제1전송 게이트는 상기 제1표면으로부터 상기 제1저장 다이오드로 수직으로 형성되는 글로벌 셔터 이미지 센서.

### 청구항 6

제1항에 있어서,

상기 제1오버플로우 게이트는 상기 제1표면으로부터 상기 제1광전 변환 영역으로 수직으로 형성되는 글로벌 셔터 이미지 센서.

#### 청구항 7

제1항에 있어서,

상기 제1저장 게이트는 상기 제1표면으로부터 상기 제1광전 변환 영역 또는 상기 제1저장 다이오드로 수직으로 형성되는 글로벌 셔터 이미지 센서.

#### 청구항 8

제1항에 있어서.

상기 제1광전 변환 영역과 상기 제1저장 다이오드를 전기적으로 분리하는 DTI(deep trench isolation)를 더 포함하는 글로벌 셔터 이미지 센서.

#### 청구항 9

제4항에 있어서,

리셋 작동 동안, 상기 제1오버플로우 게이트는 상기 제1광전 변환 영역으로부터 상기 전하들을 상기 반도체 기판의 내부에 형성된 드레인 영역으로 전송하고,

전송 작동 동안, 상기 제1저장 게이트는 상기 제1광전 변환 영역으로부터 상기 전하들을 상기 저장 다이오드로 전송하고,

상기 전송 작동 동안, 상기 제1전송 게이트는 상기 제1저장 다이오드로부터 상기 전하들을 상기 제1플로팅 디퓨 전 영역으로 전송하는 글로벌 셔터 이미지 센서.

### 청구항 10

이미지 데이터를 생성하는 글로벌 셔터 CMOS 이미지 센서; 및

상기 이미지 데이터를 처리하는 프로세서를 포함하며,

상기 글로벌 셔터 이미지 센서는,

제1표면과 제2표면을 포함하는 반도체 기판;

제1픽셀;

제2픽셀; 및

제3픽셀을 포함하고,

상기 제2픽셀의 제1오버플로우 게이트, 제1광전 변환 영역, 및 제1저장 게이트는 상기 제1픽셀의 제1신호 처리 영역의 사이에 형성되고,

상기 제3픽셀의 제2오버플로우 게이트, 제2광전 변환 영역, 및 제2저장 게이트는 상기 제2픽셀의 제2신호 처리 영역의 사이에 형성되고,

상기 제2픽셀의 제1저장 다이오드, 제1전송 게이트, 및 제1플로팅 디퓨전 영역은 상기 제1저장 게이트와 상기 제2광전 변환 영역 사이에 형성되고,

상기 제1오버플로우 게이트, 상기 제1광전 변환 영역, 상기 제1저장 다이오드, 및 상기 제1플로팅 디퓨전 영역 은 일렬로 배열되는 이미지 처리 시스템.

#### 발명의 설명

### 기술분야

[0001]

본 발명의 개념에 따른 실시 예는 글로벌 셔터 이미지 센서에 관한 것으로, 특히 광전 변환 소자로부터 생성된 전하들이 동일 방향의 연속선을 유지하면서 전달되도록 하는 글로벌 셔터 이미지 센서와 이를 포함하는 이미지 처리 시스템에 관한 것이다.

### 배경기술

[0002]

일반적으로, 이미지 센서는 디지털 카메라, 휴대폰 등의 가정용 제품이나, 병원에서 사용되는 내시경, 인공위성의 망원경에 이르기까지 매우 광범위한 분야에서 사용되고 있다. 이렇게 다양한 분야에서 사용되고 있는 이미지 센서 중, CMOS(complementary metal-oxide semiconductor(CMOS)) 제조 기술로 생산되는 CMOS 이미지 센서는 광학적 이미지를 전기적 신호로 변환시키는 소자로서, 화소 수만큼 모스(MOS) 트랜지스터를 만들고 이것을 이용하여 차례차례 출력을 검출하는 스위칭 방식을 채용하고 있다.

[0003]

CMOS 이미지 센서의 픽셀 회로의 구동 방식에는 롤링 셔터(rolling shutter) 방식과 글로벌 셔터(global shutter) 방식이 있다. 롤링 셔터 방식의 경우, 한 프레임 내의 각 행의 광소자(예컨대, 포토 다이오드)들에 의해 광전 변환된 신호가 순차적으로 선택되는 한 행씩 플로팅 디퓨전(Floating Diffusion) 노드로 전달되어 해당픽셀의 영상신호가 출력된다.

[0004]

반면, 글로벌 셔터 동작의 경우, 한 프레임 내의 모든 광소자들에 의해 광전 변환된 전체 신호가 한번에 플로팅 디퓨전 노드로 전달된 후 순차적으로 선택되는 행에서 해당 픽셀의 영상신호가 출력된다.

[0005]

다만, 글로벌 셔터 방식의 이미지 센서는 복수의 트랜지스터들을 제한된 픽셀 피치(pixel pitch)에 구현하는데 어려움이 있고, 이에 따라 광전 변환 소자로부터 생성된 전하들이 한 방향으로 이동하지 못하고 이동 경로가 변경되는 경우 상기 전하들이 픽셀 내에서 고립되는 문제점이 있다.

## 발명의 내용

#### 해결하려는 과제

[0006]

상기 문제점을 해결하기 위하여 본 발명이 이루고자 하는 기술적인 과제는, 광전 변환 소자로부터 생성된 전하들이 동일 방향의 연속선을 유지하면서 전달되도록 하는 글로벌 셔터 이미지 센서와 이를 포함하는 이미지 처리시스템을 제공하는 것이다.

#### 과제의 해결 수단

[0007]

본 발명의 실시 예에 따른 글로벌 셔터 이미지 센서는 제1표면과 제2표면을 포함하는 반도체 기판, 상기 반도체 기판 내에 형성되는 광전 변환 영역, 상기 반도체 기판 내에서 상기 광전 변환 영역의 주위에 형성된 저장 다이오드, 상기 반도체 기판 내에서 상기 광전 변환 영역의 위(above)에 형성된 드레인 영역, 상기 반도체 기판 내에서 상기 저장 다이오드의 위(above)에 형성된 플로팅 디퓨전 영역, 상기 광전 변환 영역으로부터 제1전하들을 상기 드레인 영역으로 전송하는 오버플로우 게이트, 상기 광전 변환 영역으로부터 제2전하들을 상기 저장 다이오드로 전송하는 저장 게이트, 및 상기 저장 다이오드로부터 상기 제2전하들을 상기 플로팅 디퓨전 영역으로 전송하는 전송 게이트를 포함하고, 상기 오버플로우 게이트, 상기 광전 변환 영역, 상기 저장 게이트, 상기 저장 다이오드, 상기 전송 게이트, 및 상기 플로팅 디퓨전 영역은 일렬로 형성된다.

[0008]

상기 광전 변환 영역은 상기 제1표면과 상기 제2표면 중에서 어느 하나를 통해 수신된 입사광에 응답하여 상기 제1전하들 및 상기 제2전하들을 생성한다.

[0009]

상기 전송 게이트는 상기 제1표면으로부터 상기 저장 다이오드로 수직으로 형성될 수 있다.

[0010]

상기 오버플로우 게이트는 상기 제1표면으로부터 상기 광전 변환 영역으로 수직으로 형성될 수 있다.

[0011]

상기 저장 게이트는 상기 제1표면)으로부터 상기 광전 변환 영역 또는 상기 저장 다이오드로 수직으로 형성될 수 있다.

[0012]

상기 광전 변환 영역의 위(above)에 그리고 상기 오버플로우 게이트의 한쪽에 형성되고, 상기 플로팅 디퓨전 영역을 리셋하기 위한 리셋 트랜지스터, 및 상기 광전 변환 영역의 위(above)에 그리고 상기 오버플로우 게이트의다른 쪽에 형성되고, 상기 플로팅 디퓨전 영역에 접속된 소스 팔로워를 더 포함한다.

[0013]

실시 예에 따라, 상기 광전 변환 영역은 상기 제1표면으로부터 제1깊이에 형성되고, 상기 저장 다이오드는 상기

제1표면으로부터 제2깊이에 형성될 수 있다.

- [0014] 실시 예에 따라, 상기 광전 변환 영역과 상기 저장 다이오드를 전기적으로 분리하는 분리 영역을 더 포함하고, 상기 분리 영역은 DTI(deep trench isolation)일 수 있다. 상기 분리 영역은 상기 제1표면과 상기 제2표면 중에서 어느 하나로부터 수직으로 형성될 수 있다.

- [0015] 본 발명의 다른 실시 예에 따른 글로벌 셔터 이미지 센서는 제1표면과 제2표면을 포함하는 반도체 기판, 제1픽셀, 제2픽셀, 및 제3픽셀을 포함하고, 상기 제2픽셀의 제1오버플로우 게이트, 제1광전 변환 영역, 및 제1저장 게이트는 상기 제1픽셀의 제1신호 처리 영역의 사이에 형성되고, 상기 제3픽셀의 제2오버플로우 게이트, 제2광전 변환 영역, 및 제2저장 게이트는 상기 제2픽셀의 제2신호 처리 영역의 사이에 형성되고, 상기 제2픽셀의 제1 저장 다이오드, 제1전송 게이트, 및 제1플로팅 디퓨전 영역은 상기 제1저장 게이트와 상기 제2광전 변환 영역사이에 형성되고, 상기 제1오버플로우 게이트, 상기 제1광전 변환 영역, 상기 제1저장 다이오드, 및 상기 제1플로팅 디퓨전 영역은 일렬로 배열된다.

- [0016] 상기 제2신호 처리 영역은 제1소스 팔로워, 제1선택 트랜지스터, 및 제1리셋 트랜지스터를 포함한다.

- [0017] 상기 제1오버플로우 게이트, 상기 제1저장 게이트, 및 상기 제1전송 게이트는 상기 제1표면에 형성되고, 상기 제1광전 변환 영역, 상기 제1저장 다이오드, 및 상기 제1플로팅 디퓨전 영역은 상기 반도체 기판 내부에 형성된다.

- [0018] 상기 제1광전 변환 영역은 상기 제1표면과 상기 제2표면 중에서 어느 하나를 통해 수신된 입사광에 응답하여 전하들을 생성하고, 상기 제1저장 다이오드는 상기 제1광전 변환 영역의 주위에 형성되고, 상기 제1플로팅 디퓨전 영역은 상기 제1저장 다이오드의 위(above)에 형성된다.

- [0019] 상기 제1전송 게이트는 상기 제1표면으로부터 상기 제1저장 다이오드로 수직으로 형성될 수 있다.

- [0020] 상기 제1오버플로우 게이트는 상기 제1표면으로부터 상기 제1광전 변환 영역으로 수직으로 형성될 수 있다.

- [0021] 상기 제1저장 게이트는 상기 제1표면으로부터 상기 제1광전 변환 영역 또는 상기 제1저장 다이오드로 수직으로 형성될 수 있다.

- [0022] 실시 예에 따라, 상기 제1광전 변환 영역과 상기 제1저장 다이오드를 전기적으로 분리하는 DTI(deep trench isolation)를 더 포함할 수 있다.

- [0023] 리셋 작동 동안, 상기 제1오버플로우 게이트는 상기 제1광전 변환 영역으로부터 상기 전하들을 상기 반도체 기판의 내부에 형성된 드레인 영역으로 전송하고,전송 작동 동안, 상기 제1저장 게이트는 상기 제1광전 변환 영역으로부터 상기 전하들을 상기 저장 다이오드로 전송하고, 상기 전송 작동 동안, 상기 제1전송 게이트는 상기 제1저장 다이오드로부터 상기 전하들을 상기 제1플로팅 디퓨전 영역으로 전송할 수 있다.

- [0024] 본 발명의 실시 예에 따른 이미지 처리 시스템은 이미지 데이터를 생성하는 글로벌 셔터 이미지 센서, 및 상기 이미지 데이터를 처리하는 프로세서를 포함하며, 상기 글로벌 셔터 이미지 센서는, 제1표면과 제2표면을 포함하는 반도체 기판, 제1픽셀, 제2픽셀, 및 제3픽셀을 포함하고, 상기 제2픽셀의 제1오버플로우 게이트, 제1광전 변환 영역, 및 제1저장 게이트는 상기 제1픽셀의 제1신호 처리 영역의 사이에 형성되고, 상기 제3픽셀의 제2오버플로우 게이트, 제2광전 변환 영역, 및 제2저장 게이트는 상기 제2픽셀의 제2신호 처리 영역의 사이에 형성되고, 상기 제2픽셀의 제1저장 다이오드, 제1전송 게이트, 및 제1플로팅 디퓨전 영역은 상기 제1저장 게이트와 상기 제2광전 변환 영역 사이에 형성되고, 상기 제1오버플로우 게이트, 상기 제1광전 변환 영역, 상기 제1저장 다이오드, 및 상기 제1플로팅 디퓨전 영역은 일렬로 배열된다.

- [0025] 실시 예에 따라, 상기 이미지 처리 시스템은 상기 글로벌 셔터 이미지 센서와 상기 프로세서 사이에 접속된 카메라 시리얼 인터페이스를 더 포함할 수 있다.

### 발명의 효과

- [0026] 본 발명의 실시 예에 따른 글로벌 셔터 이미지 센서는 광전 변환 소자로부터 생성된 전하들이 상기 글로벌 셔터 이미지 센서 내에서 동일 방향의 연속선을 유지하면서 전달됨으로써 상기 전하들이 픽셀 내에서 고립되는 문제를 해결할 수 있는 효과가 있다.

- [0027] 본 발명의 실시 예에 따른 글로벌 셔터 이미지 센서는 광전 변환 소자와 저장 다이오드를 포함하는 상기 글로벌 셔터 이미지 센서의 픽셀의 감도를 향상시키고 풀-웰 커패시티(full-well capacity)를 증가시킬 수 있는 효과가

있다.

### 도면의 간단한 설명

- [0028] 도 1은 본 발명의 일 실시 예에 따른 이미지 처리 시스템의 블록도를 나타낸다.

- 도 2는 도 1에 도시된 픽셀 어레이의 평면도이다.

- 도 3은 도 1에 도시된 단위 픽셀의 평면도이다.

- 도 4a와 도 4b는 도 3에 도시된 단위 픽셀을 IV-IV' 방향으로 절단한 단면도들을 나타낸다.

- 도 5a와 도 5b는 도 3에 도시된 단위 픽셀을 IV-IV' 방향으로 절단한 단면도들을 나타낸다.

- 도 6은 도 1에 도시된 픽셀 그룹의 평면도이다.

- 도 7a와 도 7b는 도 6에 도시된 단위 픽셀을 VII-VII' 방향으로 절단한 단면도들을 나타낸다.

- 도 8은 도 6에 도시된 제2픽셀의 회로를 개념적으로 나타낸다.

- 도 9는 도 8에 도시된 제어 신호들의 포텐셜 다이어그램(potential diagram)을 나타낸다.

- 도 10은 본 발명의 다른 실시 예에 따른 이미지 처리 시스템의 블록도를 나타낸다.

- 도 11은 본 발명의 또 다른 실시 예에 따른 이미지 처리 시스템의 블록도를 나타낸다.

#### 발명을 실시하기 위한 구체적인 내용

- [0029] 본 명세서에 개시되어 있는 본 발명의 개념에 따른 실시 예들에 대해서 특정한 구조적 또는 기능적 설명은 단지 본 발명의 개념에 따른 실시 예들을 설명하기 위한 목적으로 예시된 것으로서, 본 발명의 개념에 따른 실시 예 들은 다양한 형태들로 실시될 수 있으며 본 명세서에 설명된 실시 예들에 한정되지 않는다.

- [0030] 본 발명의 개념에 따른 실시 예들은 다양한 변경들을 가할 수 있고 여러 가지 형태들을 가질 수 있으므로 실시 예들을 도면에 예시하고 본 명세서에서 상세하게 설명하고자 한다. 그러나, 이는 본 발명의 개념에 따른 실시 예들을 특정한 개시 형태들에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물, 또는 대체물을 포함한다.

- [0031] 제1 또는 제2 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 상기 구성 요소들은 상기 용어들에 의해 한정되어서는 안 된다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로만, 예컨대 본 발명의 개념에 따른 권리 범위로부터 벗어나지 않은 채, 제1구성 요소는 제2구성 요소로 명명될수 있고 유사하게 제2구성 요소는 제1구성 요소로도 명명될수 있다.

- [0032] 어떤 구성 요소가 다른 구성 요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성 요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성 요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성 요소가 다른 구성 요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는 중간에 다른 구성 요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성 요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

- [0033] 본 명세서에서 사용한 용어는 단지 특정한 실시 예를 설명하기 위해 사용된 것으로서, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다" 또는 "가지다" 등의 용어는 본 명세서에 기재된 특징, 숫자, 단계, 동작, 구성 요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성 요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야한다.

- [0034] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 나타낸다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥상 가지는 의미와 일치하는 의미를 갖는 것으로 해석되어야 하며, 본 명세서에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0035] 이하, 본 명세서에 첨부된 도면들을 참조하여 본 발명의 실시 예들을 상세히 설명한다.

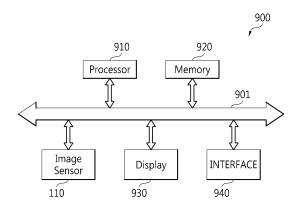

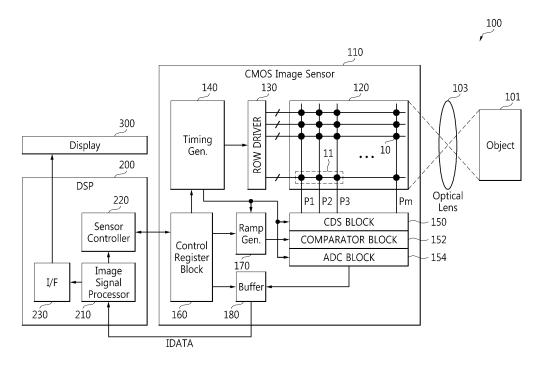

- [0036] 도 1은 본 발명의 일 실시 예에 따른 이미지 처리 시스템의 블록도를 나타낸다.

- [0037] 도 1을 참조하면, 이미지 처리 시스템(100)은 휴대용 전자 장치로 구현될 수 있다. 상기 휴대용 전자 장치는 랩탑 컴퓨터(laptop computer), 이동 전화기, 스마트 폰(smart phone), 태블릿(tablet) PC, PDA(personal digital assistant), EDA (enterprise digital assistant), 디지털 스틸 카메라(digital still camera), 디지털 비디오 카메라(digital video camera), PMP(portable multimedia player), 모바일 인터넷 장치(mobile internet device(MID), 웨어러블 컴퓨터, 사물 인터넷 (internet of things(IoT)) 장치, 또는 만물 인터넷 (internet of everything(IoE)) 장치로 구현될 수 있다.

- [0038] 이미지 처리 시스템(100)은 광학 렌즈(103), CMOS 이미지 센서(110), 디지털 신호 프로세서(digital signal processor(DSP); 200), 및 디스플레이(300)를 포함한다.

- [0039] CMOS 이미지 센서(110)는 광학 렌즈(103)를 통하여 입력된(또는 캡쳐되) 피사체(101)에 대한 이미지 데이터 (IDATA)를 생성할 수 있다.

- [0040] CMOS 이미지 센서(110)는 픽셀(또는 APS(active pixel sensor)) 어레이 (120), 로우 드라이버(130), 타이밍 생성기(140), 상관 이중 샘플링(correlated double sampling(CDS)) 블록(150), 비교기 블록(152), 및 아날로그-디지털 변환 블록(analog-to-digital conversion(ADC) block; 154), 제어 레지스터 블록(160), 램프 신호 생성기(170), 및 버퍼(180)를 포함한다.

- [0041] CMOS 이미지 센서(110)는 글로벌 셔터(global shutter) 작동을 수행할 수 있는 구조로 구현될 수 있다.

- [0042] 픽셀 어레이(120)는 매트릭스(matrix) 형태로 배열된 복수의 픽셀들(10)을 포함한다. 복수의 픽셀들(10) 각각은 작동 전압을 높이지 않고도 플로팅 디퓨전 노드(또는 플로팅 디퓨전 영역)의 커패시턴스를 증가시키지 않고도 상기 플로팅 디퓨전 노드에 저장될 수 있는 전하량을 증가시킬 수 있는 구조를 갖는다. 따라서, 복수의 픽셀들(10) 각각의 구조와 작동은 도 2부터 도 9를 참조하여 상세히 설명될 것이다.

- [0043] 로우 드라이버(130)는, 타이밍 생성기(140)의 제어에 따라, 복수의 픽셀들 (10) 각각의 동작을 제어하기 위한 복수의 제어 신호들을 픽셀 어레이(120)로 전송할 수 있다. 상기 복수의 제어 신호들은 도 8 및 도 9를 참조하 여 상세히 설명될 것이다.

- [0044] 타이밍 생성기(140)는, 제어 레지스터 블록(160)의 제어에 따라, 로우 드라이버(130), CDS 블록(150), ADC 블록 (154), 및 램프 신호 생성기(170)의 작동을 제어한다.

- [0045] CDS 블록(150)은 픽셀 어레이(120)에 구현된 복수의 컬럼 라인들 각각으로부터 출력된 각 픽셀 신호(P1~Pm; m은 2 이상의 자연수)에 대해 상관 이중 샘플링을 수행한다.

- [0046] 비교기 블록(152)은 CDS 블록(150)으로부터 출력된 복수의 상관 이중 샘플된 픽셀 신호들 각각과 램프 신호 생성기(170)로부터 출력된 램프 신호를 서로 비교하고, 비교의 결과에 따라 복수의 비교 신호들을 출력한다.

- [0047] ADC 블록(154)은 비교기 블록(152)으로부터 출력된 복수의 비교 신호들 각각을 디지털 신호로 변환하고, 복수의 디지털 신호들을 버퍼(180)로 출력한다.

- [0048] 제어 레지스터 블록(160)은, DSP(200)의 제어에 따라, 타이밍 생성기 (140), 램프 신호 생성기(170), 및 버퍼 (180)의 작동을 제어한다.

- [0049] 버퍼(180)는 ADC 블록(154)으로부터 출력된 복수의 디지털 신호들에 대응되는 이미지 데이터(IDATA)를 DSP(20 0)로 전송한다.

- [0050] DSP(200)는 이미지 신호 프로세서(210), 센서 컨트롤러(220), 및 인터페이스(230)를 포함한다.

- [0051] 이미지 신호 프로세서(210)는 제어 레지스터 블록(160)을 제어하는 센서 컨트롤러(220)와, 인터페이스(210)를 제어한다. 실시 예에 따라, CMOS 이미지 센서 (110)와 DSP(200) 각각은 칩으로 구현되고, 하나의 패키지, 예컨 대 멀티-칩 패키지 (multi-chip package)로 구현될 수 있다. 다른 실시 예에 따라, CMOS 이미지 센서 (110)와 이미지 신호 프로세서(210) 각각은 칩으로 구현되고 하나의 패키지, 예컨대 멀티-칩 패키지로 구현될 수 있다. 또 다른 실시 예에 따라, CMOS 이미지 센서 (110)와 이미지 신호 프로세서(210)는 하나의 칩으로 구현될 수도 있다.

- [0052] 이미지 신호 프로세서(210)는 버퍼(180)로부터 전송된 이미지 데이터 (IDATA)를 처리하고, 처리된 이미지 데이터 인터페이스(230)로 전송한다.

- [0053] 센서 컨트롤러(220)는, 이미지 신호 프로세서(210)의 제어에 따라, 제어 레지스터 블록(160)을 제어하기 위한 다양한 제어 신호들을 생성한다.

- [0054] 인터페이스(230)는 이미지 신호 프로세서(210)에서 처리된 이미지 데이터를 디스플레이(300)로 전송한다.

- [0055] 디스플레이(300)는 인터페이스(230)로부터 출력된 이미지 데이터를 디스플레이한다. 예컨대, 디스플레이(300)는 TFT-LCD(thin film transistor-liq0id crystal display), LED(light emitting diode) 디스플레이, OLED(organic LED) 디스플레이, 또는 AMOLED(active-matrix OLED) 디스플레이로 구현될 수 있다.

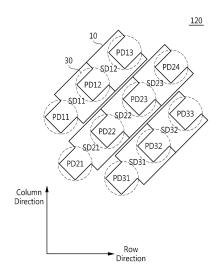

- [0056] 도 2는 도 1에 도시된 픽셀 어레이의 평면도이다.

- [0057] 도 1과 도 2를 참조하면, 픽셀 어레이(120)는 광학 렌즈(103)를 통해 입사된 빛에 따라 광전하들을 생성하고 광전하들에 대응하는 픽셀 신호들을 생성하는 복수의 픽셀들을 포함할 수 있다. 상기 복수의 픽셀들은 n(n은 2 이상의 정수)개의 로우들(rows)과 m(m은 2 이상의 정수)개의 컬럼들(columns)을 가진 매트릭스 형태로 배열될 수 있다. 상기 복수의 픽셀들 각각은 8각형(octagonal) 타입 픽셀로 구현될 수 있으나 이에 한정되는 것은 아니다.

- [0058] 상기 복수의 픽셀들 각각은 광전 변환 영역와, 상기 광전 변환 영역으로부터 출력된 광 전하들을 저장하기 위한 저장 다이오드를 포함할 수 있다. 상기 복수의 픽셀들 각각은 대응되는 픽셀 신호를 컬럼 라인으로 출력할 수 있다. 예컨대, 상기 광전 변환 영역에 구현되는 광전 변환 소자는 포토다이오드(photo diode), 포토트랜지스터 (photo transistor), 포토게이트 (photogate), 또는 핀드 포토다이오드 (pinned photo diode)로 구현될 수 있다.

- [0059] 설명의 편의를 위해, 상기 복수의 픽셀들 중에서 하나의 단위 픽셀(10)의 구조와 작동이 설명되나, 상기 복수의 픽셀들 각각의 구조와 작동은 단위 픽셀(10)의 구조와 작동과 실질적으로 동일 또는 유사하다.

- [0060] 단위 픽셀(10)은 광전 변환 영역(PD12)과 저장 다이오드(SD12)를 포함한다.

- [0061] 실시 예에 따라, 하나의 단위 픽셀(10)에 포함된 광전 변환 영역(PD12)과 저장 다이오드 영역(SD12)의 배열은 픽셀 어레이(120)의 로우 방향을 기준으로 비스듬히(예컨대, 45도) 배치될 수 있다. 마이크로 렌즈(30)는 광전 변환 영역(PD12)의 상부에 구현될 수 있다.

- [0062] 예컨대, 픽셀 어레이(120)의 배열에서, 저장 다이오드(SD22)는 4개의 광전 변환 영역(PD12, PD22, PD23, 및 PD32)에 둘러싸이도록 배치될 수 있다. 이때, 각 광전 변환 영역(PD12, PD22, PD23, 및 PD32)의 상부에는 마이크로 렌즈(30)가 구현되고, 저장 다이오드(SD22)의 상부에는 마이크로 렌즈(30)가 구현되지 않는다.

- [0063] 도 2에서는 광전 변환 영역(PD12)과 저장 다이오드 영역(SD12)이 픽셀 어레이(120)의 로우 방향을 기준으로 일 정한 각도로 배치된 것으로 도시되어 있으나, 본 발명의 실시 예에 따른 광전 변환 영역(PD12)과 저장 다이오드 영역(SD12)의 배열은 이에 한정되는 것은 아니다.

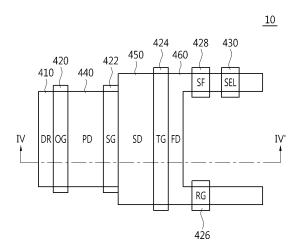

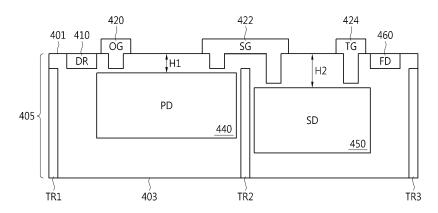

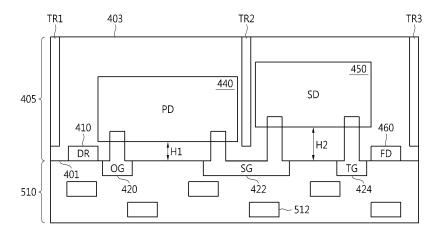

- [0064] 도 3은 도 1에 도시된 단위 픽셀의 평면도이고, 도 4a와 도 4b는 도 3에 도시된 단위 픽셀을 IV-IV' 방향으로 절단한 단면도들을 나타낸다.

- [0065] 도 3의 평면도는 설명의 편의를 위해 단위 픽셀(10)에 포함된 각 구성 요소 (410~460)를 동일한 평면으로 투영 시켜 표현한 것으로, 각 구성 요소(410~460)의 물리적인 배치(또는 구현)는 도 4a부터 도 9를 참조하여 상세히 설명될 것이다.

- [0066] 도 1부터 도 4b를 참조하면, 반도체 기판(405)은 제1표면(401)과 반대쪽 제2표면(403)을 포함한다. 반도체 기판 (405) 내부에, 드레인 영역(410), 광전 변환 영역(440), 저장 다이오드(450), 및 플로팅 디퓨전 영역(460)이 형 성될 수 있다.

- [0067] 드레인 영역(410)은 반도체 기판(405) 내에서 광전 변환 영역(440)의 위 (above)에 형성되고, 저장 다이오드 (450)는 광전 변환 영역(440)의 주위에 형성되고, 플로팅 디퓨전 영역(460)은 반도체 기판(405) 내에서 저장 다이오드(450)의 위 (above)에 형성된다.

- [0068] 실시 예에 따라, 광전 변환 영역(440)은 제1표면(401)으로부터 제1깊이(H1)에 형성되고, 저장 다이오드(450)는 제1표면(401)으로부터 제2깊이(H2)에 형성될 수 있다. 실시 예에 따라, 제1깊이(H1)는 제2깊이(H2)와 같거나 다를 수 있다.

- [0069] 광전 변환 영역(440)은, 제1표면(401)과 제2표면(403) 중에서 어느 하나를 통해 수신된 입사광에 응답하여, 제1 전하들을 생성할 수 있다. 상기 제1전하들은 드레인 영역(410)으로 전송되는 제2전하들과 저장 다이오드(450)로 전송되는 제3전하들을 포함할 수 있다. 실시 예들에 따라, 상기 제1전하들은 상기 제2전하들을 의미할 수 있고 상기 제3전하들을 의미할 수 있다.

- [0070] 오버플로우 게이트(420)는 제1표면(401)으로부터 광전 변환 영역(440)으로 수직으로 형성되어, 광전 변환 영역 (440)으로부터 상기 제2전하들을 드레인 영역 (410)으로 전송할 수 있다.

- [0071] 저장 게이트(422)는 제1표면(401)으로부터 광전 변환 영역(440) 및/또는 저장 다이오드(450)로 수직으로 형성되어, 광전 변환 영역(440)으로부터 상기 제3전하들을 저장 다이오드(450)로 전송할 수 있다.

- [0072] 전송 게이트(424)는 제1표면(401)으로부터 저장 다이오드(450)로 수직으로 형성되어, 저장 다이오드(450)로부터 상기 제3전하들을 플로팅 디퓨전 영역(460)으로 전송할 수 있다.

- [0073] 도 3의 리셋 트랜지스터(426)는 작동 전압을 공급하는 노드와 플로팅 디퓨전 영역(460) 사이에 접속되고 플로팅 디퓨전 영역(460)을 리셋할 수 있다. 소스 팔로워(428)는 플로팅 디퓨전 영역(460)으로 전송된 제3전하들에 상응하는 전압에 응답하여 작동한다. 선택 트랜지스터(430)는 소스 팔로워(428)로부터 출력된 신호들을 컬럼 라인으로 전송할 수 있다.

- [0074] 도 3을 참조하면, 오버플로우 게이트(420), 광전 변환 영역(440), 저장 게이트(422), 저장 다이오드(450), 전송 게이트(424), 및 플로팅 디퓨전 영역(460)은 일렬로 배치될 수 있다.

- [0075] 실시 예에 따라, 단위 픽셀(10)은 이웃하는 픽셀들과 단위 픽셀(10)을 전기적으로 분리하는 제1분리 영역(TR1 및 TR3)을 포함하고, 광전 변환 영역(440)과 저장 다이오드(450)를 전기적으로 분리하는 제2분리 영역(TR2)을 포함할 수 있다. 제1분리 영역(TR1 및 TR3)과 제2분리 영역(TR2) 각각은 DTI(deep trench isolation)로 구현될 수 있다.

- [0076] 실시 예에 따라, 제1분리 영역들(TR1 및 TR3)과 제2분리 영역(TR2)은 백 트렌치 공정(back trench process) 또는 프런트 트렌치 공정(front trench process)을 통해 형성될 수 있다. 즉, 제1분리 영역들(TR1 및 TR3)과 제2분리 영역(TR2)은 제1표면(401)과 제2표면(403) 중에서 어느 하나로부터 수직으로 형성될 수 있다.

- [0077] 실시 예에 따라, 단위 픽셀(10)은 단위 픽셀(10) 내의 복수의 트랜지스터들 각각을 전기적으로 분리하는 STI(shallow trench isolation)를 포함할 수 있다.

- [0078] 도 4a와 도 4b를 참조하면, CMOS 이미지 센서(110)는 FSI(front side illumination) 방식의 CMOS 이미지 센서 일 수 있다. 예컨대, 입사광은 제1표면 (401)을 통해 입사될 수 있다.

- [0079] 오버플로우 게이트(420), 저장 게이트(422), 및 전송 게이트(424)가 수직으로 광전 변환 영역(440) 및/또는 저장 다이오드(450)의 내부까지 확장되는 것을 제외하면, 도 4a에 도시된 단면도와 도 4b에 도시된 단면도는 실질적으로 동일 또는 유사하다.

- [0080] 도 4a를 참조하면, 오버플로우 게이트(420), 저장 게이트(422), 및 전송 게이트(424)는 제1표면(401)으로부터 광전 변환 영역(440) 및/또는 저장 다이오드 (450)의 내부까지 수직으로 확장되지 않는다.

- [0081] 그러나, 도 4b를 참조하면, 오버플로우 게이트(420), 저장 게이트(422), 및 전송 게이트(424)는 제1표면(401)으로부터 광전 변환 영역(440) 및/또는 저장 다이오드(450)의 내부까지 수직으로 확장된다.

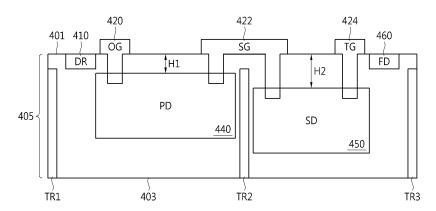

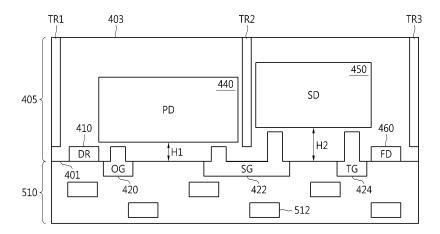

- [0082] 도 5a와 도 5b는 도 3에 도시된 단위 픽셀을 IV-IV' 방향으로 절단한 단면도들을 나타낸다. 도 5a와 도 5b를 참 조하면, CMOS 이미지 센서(110)는 BSI(backside illumination) 방식의 CMOS 이미지 센서일 수 있다. 예컨대, 입사광은 제2표면 (403)을 통해 입사될 수 있다.

- [0083] 도 1부터 도 5b를 참조하면, 반도체 기판(405)은 제1표면(401)과 제2표면 (403)을 포함하고, 반도체 기판(405) 내부에 드레인 영역(410), 광전 변환 영역 (440), 저장 다이오드(450), 및 플로팅 디퓨전 영역(460)이 형성될 수 있다.

- [0084] 배선층(510)은 제1표면(401)의 아래에 형성될 수 있고, 도전 라인들(512) 또는 메탈을 포함할 수 있다.

- [0085] 도 5a를 참조하면, 오버플로우 게이트(420), 저장 게이트(422), 및/또는 전송 게이트(424)는 제1표면(401)으로 부터 광전 변환 영역(440) 및/또는 저장 다이오드(450)의 내부까지 수직으로 확장되지 않는다.

- [0086] 그러나, 도 5b를 참조하면, 오버플로우 게이트(420), 저장 게이트(422), 및/또는 전송 게이트(424)는 제1표면 (401)으로부터 광전 변환 영역(440) 및/또는 저장 다이오드(450)의 내부까지 수직으로 확장될 수 있다.

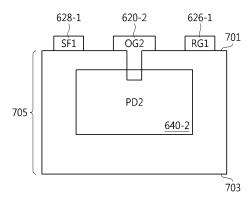

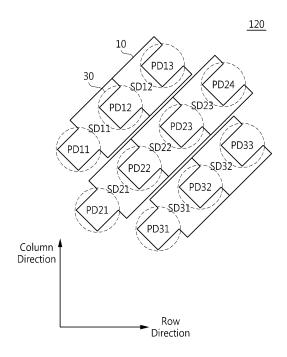

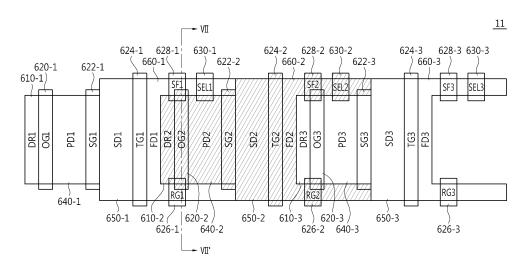

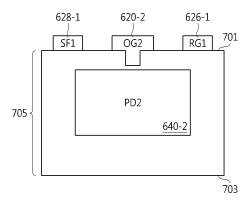

- [0087] 도 6은 도 1에 도시된 픽셀 그룹의 평면도이고, 도 7a와 도 7b는 도 6에 도시된 단위 픽셀을 VII-VII' 방향으로 절단한 단면도들을 나타낸다.

- [0088] 도 6의 평면도는 설명의 편의를 위해 3개의 픽셀들을 포함하는 픽셀 그룹 (11)에 포함된 각 구성 요소(610-1~660-3)를 동일한 평면으로 투영시켜 표현한 것으로, 각 구성 요소(610-1~660-3)의 물리적인 배치(또는 구현)는 도 7a부터 도 9를 참조하여 상세히 설명될 것이다.

- [0089] 도 1을 참조하면 픽셀 그룹(11)은 픽셀 어레이(120)에 포함된 복수의 픽셀들 중에서 연속되어 배치되는 3개의 픽셀들을 포함한다. 상기 3개의 픽셀들 각각의 구조와 작동은 도 3을 참조하여 설명된 픽셀의 구조와 작동과 실질적으로 동일 또는 유사할 수 있다.

- [0090] 도 1부터 도 6을 참조하면, 픽셀 그룹(11)은 제1픽셀, 제2픽셀, 및 제3픽셀을 포함한다. 픽셀 그룹(11)의 각 픽셀의 반도체 기판(405)은 제1표면(401)과 제2표면(403)을 포함하고, 드레인 영역(610-1, 610-2, 또는 610-3), 광전 변환 영역(640-1, 640-2, 또는 640-3), 저장 다이오드(650-1, 650-2, 또는 650-3), 및 플로팅 디퓨전 영역(660-1, 660-2, 또는 660-3)은 반도체 기판(405) 내부에 형성될 수 있다.

- [0091] 도 6을 참조하면, 상기 제1픽셀은 제1드레인 영역(610-1), 제1오버플로우 게이트(620-1), 제1광전 변환 영역 (640-1), 제1저장 게이트(622-1), 제1저장 다이오드(650-1), 제1전송 게이트(624-1), 제1플로팅 디퓨전 영역 (660-1), 제1리셋 게이트(626-1), 제1소스 팔로워(628-1), 및 제1선택 트랜지스터(630-1)를 포함한다.

- [0092] 상기 제1픽셀에 인접하는 상기 제2픽셀은 제2드레인 영역(610-2), 제2오버플로우 게이트(620-2), 제2광전 변환 영역(640-2), 제2저장 게이트(622-2), 제2저장 다이오드(650-2), 제2전송 게이트(624-2), 제2플로팅 디퓨전 영역(660-2), 제2리셋 게이트(626-2), 제2소스 팔로워(628-2), 및 제2선택 트랜지스터(630-2)를 포함한다.

- [0093] 상기 제2픽셀에 인접하는 상기 제3픽셀은 제3드레인 영역(610-3), 제3오버플로우 게이트(620-3), 제3광전 변환 영역(640-3), 제3저장 게이트(622-3), 제3저장 다이오드(650-3), 제3전송 게이트(624-3), 제3플로팅 디퓨전 영역(660-3), 제3리셋 게이트(626-3), 제3소스 팔로워(628-3), 및 제3선택 트랜지스터(630-3)를 포함한다.

- [0094] 본 명세서에서는 설명의 편의를 위해, 상기 제2픽셀의 구조가 설명되나, 상기 제1픽셀과 상기 제3픽셀 각각의 구조는 상기 제2픽셀의 구조와 실질적으로 동일 또는 유사하다.

- [0095] 상기 제2픽셀의 제2오버플로우 게이트(620-2), 제2광전 변환 영역(640-2), 및 제2저장 게이트(622-2)는 상기 제1픽셀의 제1신호 처리 영역의 사이에 형성된다. 상기 제1신호 처리 영역은 상기 제1픽셀의 제1리셋 게이트(626-1), 제1소스 팔로워(628-1), 및 제1선택 트랜지스터(630-1)를 포함한다.

- [0096] 상기 제3픽셀의 제3오버플로우 게이트(620-3), 제3광전 변환 영역(640-3), 및 제3저장 게이트(622-3)는 상기 제2픽셀의 제2신호 처리 영역의 사이에 형성된다. 상기 제2신호 처리 영역은 상기 제2픽셀의 제2리셋 게이트(626-2), 제2소스 팔로워(628-2), 및 제2선택 트랜지스터(630-2)를 포함한다.

- [0097] 상기 제2픽셀의 제2저장 다이오드(650-2), 제2전송 게이트(624-2), 및 제2플로팅 디퓨전 영역(660-2)은 상기 제 2픽셀의 제2저장 게이트(622-2)와 상기 제3픽셀의 제3광전 변환 영역(640-3) 사이에 형성된다.

- [0098] 상기 제2픽셀의 제2오버플로우 게이트(620-2), 제2광전 변환 영역(640-2), 제2저장 다이오드(650-2), 및 제2플로팅 디퓨전 영역(660-2)은 일렬로 배열될 수 있다.

- [0099] 도 1부터 도 6을 참조하면, 제2광전 변환 영역(640-2)은, 제1표면(401)과 제2표면(403) 중에서 어느 하나를 통해 수신된 입사광에 응답하여, 제1전하들을 생성할 수 있다. 상기 제1전하들은 제2드레인 영역(610-2)으로 전송되는 제2전하들과 제2저장 다이오드(650-2)로 전송되는 제3전하들을 포함할 수 있다.

- [0100] 리셋 작동 동안, 제2오버플로우 게이트(620-2)는 상기 제2전하들을 제2광전 변환 영역(640-2)으로부터 제2드레 인 영역(610-2)으로 전송할 수 있다.

- [0101] 전송 작동 동안, 제2저장 게이트(622-2)는 상기 제3전하들을 제2광전 변환 영역(640-2)으로부터 제2저장 다이오 드(650-2)로 전송할 수 있다.

- [0102] 상기 전송 작동 동안, 제2전송 게이트(624-2)는 상기 제3전하들을 제2저장 다이오드(650-2)로부터 제2플로팅 디 퓨전 영역(660-2)으로 전송할 수 있다.

- [0103] 제2리셋 트랜지스터(626-2)는 작동 전압을 공급하는 노드와 제2플로팅 디퓨전 영역(660-2) 사이에 접속되고, 제2플로팅 디퓨전 영역(660-2)을 리셋한다. 제2소스 팔로워(628-2)는 제2플로팅 디퓨전 영역(660-2)으로 전송된 상기 제3전하들에 응답하여 작동하고, 제2선택 트랜지스터(630-2)는 제2소스 팔로워(628-2)로부터 출력된 신호들을 컬럼 라인으로 전송할 수 있다.

- [0104] 도 1부터 도 7b를 참조하면, 반도체 기판(705)은 제1표면(701)과 제2표면 (703)을 포함하고, 상기 제1픽셀의 제 1리셋 트랜지스터(626-1)와 제1소스 팔로워 (628-1)는 제1표면(701)에 형성되고, 제2광전 변환 영역(640-2)은 반도체 기판 (705)의 내부에 형성될 수 있다.

- [0105] 상기 제1픽셀의 제1리셋 트랜지스터(626-1)는 제2광전 변환 영역(640-2)의 위(above)에 그리고 제2오버플로우 게이트(620-2)의 한쪽에 형성되고, 제2플로팅 디퓨전 영역(660-2)을 리셋할 수 있다. 상기 제1픽셀의 제1소스 팔로위(628-1)는 제2광전 변환 영역(640-2)의 위(above)에 그리고 제2오버플로우 게이트(620-2)의 다른 쪽에 형성되고, 제2플로팅 디퓨전 영역(660-2)에 접속될 수 있다.

- [0106] 제2오버플로우 게이트(620-2)가 제2광전 변환 영역(640-2)의 내부까지 수직으로 확장되는 것을 제외하면, 도 7a 에 도시된 단면도와 도 7b에 도시된 단면도는 실질적으로 동일 또는 유사하다.

- [0107] 도 7a를 참조하면, 제2오버플로우 게이트(620-2)는 제1표면(701)으로부터 제2광전 변환 영역(640-2)의 위까지 수직으로 확장된다. 그러나, 도 7b를 참조하면, 제2오버플로우 게이트(620-2)는 제1표면(701)으로부터 제2광전 변환 영역(640-2)의 내부까지 수직으로 확장된다.

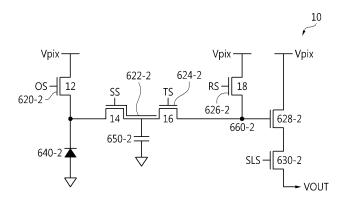

- [0108] 도 8은 도 6에 도시된 제2픽셀의 회로를 개념적으로 나타낸다.

- [0109] 도 6과 도 8을 참조하면, 글로벌 셔터 작동을 수행할 수 있는 단위 픽셀(10)은 광전 변환 영역(640-2), 오버플로우(overflow) 트랜지스터(12), 저장 트랜지스터(storage transistor; 14), 전송 트랜지스터(16), 리셋 트랜지스터(18), 소스 팔로워(628-2), 및 선택 트랜지스터(630-2)를 포함한다.

- [0110] 광전 변화 영역(640-2)은 입사광에 응답하여 전하들을 축적(또는 수집)한다.

- [0111] 오버플로우 트랜지스터(12)는 작동 전압(Vpix)을 공급하는 제1노드와 광전 변환 영역(640-2) 사이에 접속된다. 오버플로우 트랜지스터(12)는 오버플로우 게이트(620-2)를 포함한다. 오버플로우 게이트(620-2)는 광전 변환 영역(640-2)에 의해 생성된 전하들이 오버플로우되는 것을 방지하기 위해 사용된다. 오버플로우 트랜지스터(12)는, 오버플로우 게이트 신호(OS)에 응답하여, 온(on) 또는 오프(off)된다.

- [0112] 예컨대, 단위 픽셀(10)로 입사되는 입사광의 세기가 클 경우, 또는 태양 또는 전구 등을 촬영할 때(즉, 고조도일 때), 오버플로우 트랜지스터(12)는 광전 변환 영역(640-2)에서 생성된 전하들이 저장 다이오드(650-2)로 오버플로우되는 것을 방지하기 위해 사용된다.

- [0113] 저장 트랜지스터(14)는 광전 변환 영역(640-2)과 저장 다이오드(650-2) 사이에 접속되고, 광전 변환 소자(640-2)로부터 전송된 전하들은 저장 트랜지스터(14)를 통해 저장 다이오드(650-2)에 저장된다.

- [0114] 저장 트랜지스터(14)는, 저장 게이트(622-2)로 공급되는 저장 트랜지스터 제어 신호(SS)에 응답하여, 온(on) 또는 오프(off)된다.

- [0115] 전송 트랜지스터(16)는 저장 트랜지스터(14)와 플로팅 디퓨전 노드(660-2) 사이에 접속된다. 저장 다이오드 (650-2)에 저장된 전하들은 전송 트랜지스터(16)를 통해 플로팅 디퓨전 노드(660-2)에 저장(또는 축적)된다. 전송 트랜지스터(16)는, 전송 게이트(624-2)로 공급되는 전송 제어 신호(TS)에 응답하여, 온(on) 또는 오프(off)된다.

- [0116] 리셋 트랜지스터(18)는 작동 전압(Vpix)을 공급하는 제1노드와 플로팅 디퓨전 노드(660-2) 사이에 접속되고, 리셋 게이트(626-2)로 공급되는 리셋 제어 신호 (RS)에 응답하여 플로팅 디퓨전 노드(660-2)의 전하들(예컨대, 전자들)을 상기 제1노드로 전송할 수 있다.

- [0117] 소스 팔로워(628-2)는 작동 전압(Vpix)을 공급하는 제1노드와 선택 트랜지스터(630-2) 사이에 접속되고, 플로팅 디퓨전 노드(660-2)의 전하들에 따라 결정된 전압에 기초하여 작동한다.

- [0118] 선택 트랜지스터(630-2)는 선택 신호(SLS)에 응답하여 소스 팔로워(628-2)의 출력 신호(예컨대, 아날로그 픽셀 신호; VOUT)를 컬럼 라인으로 출력할 수 있다.

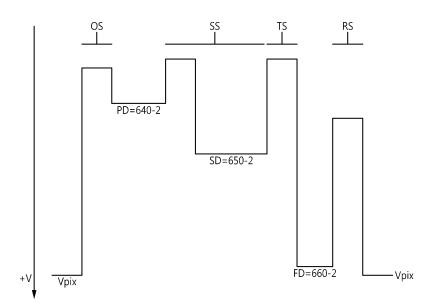

- [0119] 도 9는 도 8에 도시된 제어 신호들의 포텐셜 다이어그램(potential diagram)을 나타낸다.

- [0120] 설명의 편의를 위해, 도 8에 도시된 각 트랜지스터(12, 14, 16, 18, 628-2, 및 630-2)는 NMOS 트랜지스터로 구현되고, 각 트랜지스터(12, 14, 16, 18, 628-2, 및 630-2)는 하이 레벨을 갖는 각 제어 신호(OS, SS, TS, RS, 및 SLS)에 응답하여 턴-온 되다고 가정한다.

- [0121] 도 8과 도 9를 참조하면, 광전 변환 영역(640-2)은 입사광에 응답하여 전하들을 생성한다. 하이 레벨을 갖는 오 버플로우 게이트 신호(OS)가 오버플로우 게이트(620-2)로 공급될 때, 광전 변환 영역(640-2)에 저장된 전하들은 오버플로우 트랜지스터(12)를 통해 작동 전압(Vpix)을 공급하는 제1노드로 방전된다.

- [0122] 하이 레벨을 갖는 저장 트랜지스터 제어 신호(SS)가 저장 게이트(622-2)로 공급되면, 광전 변환 영역(640-2)에 저장된 전하들은 저장 트랜지스터(14)를 통해 저장 다이오드(650-2)로 저장된다.

- [0123] 하이 레벨을 가지는 전송 게이트 신호(TS)가 전송 게이트(16)고 공급될 때, 전하들은 저장 다이오드(650-2)로부 터 플로팅 디퓨전 영역(660-2)으로 전송된다.

- [0124] 하이 레벨을 가지는 리셋 신호(RS)가 리셋 게이트(626-2)로 공급될 때, 플로팅 디퓨전 영역(660-2)으로 전송된 전하들은 작동 전압(Vpix)을 공급하는 제1노드로 전송된다. 따라서, 플로팅 디퓨전 영역(660-2)은 리셋된다.

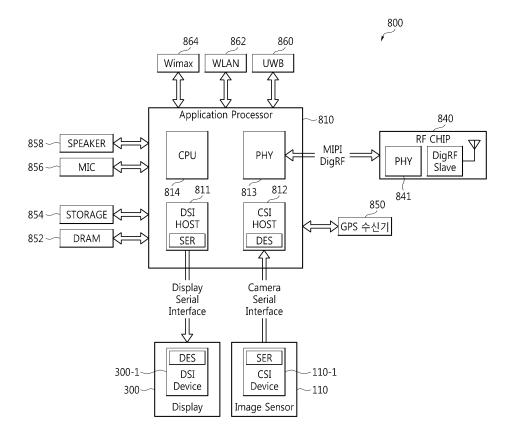

- [0125] 도 10은 본 발명의 다른 실시 예에 따른 이미지 처리 시스템의 블록도를 나타낸다. 도 1부터 도 10을 참조하면, 이미지 처리 시스템(800)은 MIPI<sup>®</sup>(mobile industry processor interface)를 사용(또는 지원)할 수 있는 이미지 처리 시스템으로 구현될 수 있다.

- [0126] 이미지 처리 시스템(800)은 랩탑 컴퓨터, 이동 전화기, 스마트 폰, 태블릿 PC, PDA(personal digital assistant), EDA(enterprise digital assistant), 디지털 스틸 카메라, 디지털 비디오 카메라, PMP(portable media player), 모바일 인터넷 장치(mobile internet device(MID)), 웨어러블 컴퓨터, IoT(internet of things) 장치, 또는 IoE(internet of everything) 장치로 구현될 수 있다.

- [0127] 이미지 처리 시스템(800)은 애플리케이션 프로세서(application processor(AP); 810), CMOS 이미지 센서(110), 및 디스플레이(300)를 포함한다.

- [0128] AP(810)에 구현된 카메라 시리얼 인터페이스(camera serial interface(CSI)) 호스트(812)는 CSI를 통하여 CMOS 이미지 센서(110)의 CSI 장치(110-1)와 시리얼 통신할 수 있다. 실시 예에 따라, CSI 호스트(812)는 디시리얼라 이저(DES)를 포함할 수 있고, CSI 장치(110-1)는 시리얼라이저(SER)를 포함할 수 있다.

- [0129] CMOS 이미지 센서(110)는 도 1부터 도 9를 참조하여 설명한 CMOS 이미지 센서(110)를 의미한다.

- [0130] AP(810)에 구현된 디스플레이 시리얼 인터페이스(display serial interface(DSI)) 호스트(811)는 DSI를 통하여 디스플레이(300)의 DSI 장치(300-1)와 시리얼 통신할 수 있다. 실시 예에 따라, DSI 호스트(811)는 시리얼라이 저(SER)를 포함하고, DSI 장치(300-1)는 디시리얼라이저(DES)를 포함할 수 있다.

- [0131] 예컨대, CMOS 이미지 센서(110)로부터 출력된 이미지 데이터(도 1의 IDATA)는 CSI를 통해 AP(810)로 전송될 수 있다. AP(810)는 이미지 데이터(도 1의 IDATA)를 처리하고, 처리된 이미지 데이터를 DSI를 통해 디스플레이 (300)로 전송할 수 있다.

- [0132] 이미지 처리 시스템(800)은 AP(810)와 통신할 수 있는 RF 칩(840)을 더 포함할 수 있다. 이미지 처리 시스템 (800)의 물리 계층(physical layer(PHY); 813)과 RF 칩(840)의 물리 계층(physical layer(PHY); 841)은 MIPI DigRF에 따라 데이터를 주고받을 수 있다.

- [0133] CPU(814)는 DSI 호스트(811), CSI 호스트(812), 및 PHY(813) 각각의 작동을 제어할 수 있고, 하나 또는 그 이 상의 코어들을 포함할 수 있다.

- [0134] AP(810)는 집적 회로, 시스템 온 칩(system on chip(SoC))으로 구현될 수 있고, CMOS 이미지 센서(110)의 작동을 제어할 수 있는 프로세서 또는 호스트를 의미할 수 있다.

- [0135] CMOS 이미지 센서(110)는 GPS 수신기(850), DRAM(dynamic random access memory)과 같은 휘발성 메모리(852), 플래시-기반 메모리와 같은 불휘발성 메모리로 구현된 데이터 저장 장치(854), 마이크로폰(856), 또는 스피커 (858)를 포함할 수 있다. 데이터 저장 장치(854)는 AP(810)에 착탈 가능한 외장 메모리로 구현될 수 있다. 또한, 데이터 저장 장치(854)는 UFS(universal flash storage), MMC (multimedia card), 임베디드 MMC(embedded MMC(eMMC)), USB 플래시 드라이브, 메모리 카드로 구현될 수 있다.

- [0136] 또한, 이미지 처리 시스템(800)은 적어도 하나의 통신 프로토콜(또는 통신 표준), 예컨대, UWB(ultra-wideband;

860), WLAN(Wireless LAN; 862), WiMAX (worldwide interoperability for microwave access; 864), 또는 LTE<sup>™</sup>(long term evolution; 미도시) 등을 이용하여 외부 장치와 통신할 수 있다.

- [0137] 실시 예에 따라, 이미지 처리 시스템(800)은 NFC 모듈, WiFi 모듈, 또는 블루투스 모듈 중에서 적어도 하나를 더 포함할 수 있다.

- [0138] 도 11은 본 발명의 또 다른 실시 예에 따른 이미지 처리 시스템의 블록도를 나타낸다. 도 1부터 도 11을 참조하면, 이미지 처리 시스템(900)은 CMOS 이미지 센서(110), 프로세서(910), 메모리(920), 디스플레이(930), 및 인터페이스(940)를 포함할 수 있다.

- [0139] 프로세서(910)는 CMOS 이미지 센서(110)의 동작을 제어할 수 있다. 예컨대, 프로세서(910)는 CMOS 이미지 센서 (110)로부터 출력되는 픽셀 신호를 처리하여 이미지 데이터를 생성할 수 있다.

- [0140] 메모리(920)는 CMOS 이미지 센서(110)의 동작을 제어하기 위한 프로그램과 프로세서(910)에 의해 생성된 이미지 데이터를 저장할 수 있다. 프로세서(910)는 메모리(920)에 저장된 프로그램을 실행할 수 있다. 예컨대, 메모리(910)는 휘발성 메모리 또는 불휘발성 메모리로 구현될 수 있다.

- [0141] 디스플레이(930)는 프로세서(910) 또는 메모리(920)로부터 출력되는 상기 이미지 데이터를 디스플레이할 수 있다.

- [0142] 인터페이스(940)는 이미지 데이터를 입출력하기 위한 인터페이스로 구현될 수 있다. 실시 예에 따라, 인터페이스(940)는 유선 인터페이스 또는 무선 인터페이스로 구현될 수 있다.

- [0143] 본 발명은 도면에 도시된 실시 예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 본 기술 분야의 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 타 실시 예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 등록청구범위의 기술적 사상에 의해 정해져야 할 것이다.

#### 부호의 설명

[0144] 10: 단위 픽셀 420: 오버플로우 게이트

11: 픽셀 그룹 422: 저장 게이트

100, 800, 900: 이미지 처리 시스템 424: 전송 게이트

110: CMOS 이미지 센서 426: 리셋 트랜지스터

120: 픽셀 어레이 428: 소스 팔로워

401, 501, 701: 제1표면430: 선택 트랜지스터403, 503, 703: 제2표면440: 광전 변환 영역

405, 505, 705: 반도체 기판 450: 저장 다이오드

410: 드레인 영역 460: 플로팅 디퓨전

### 도면1

# 도면4a

# *도면4b*

# 도면5a

### 도면5b

# 도면7a

# 도면7b