# (19) **日本国特許庁(JP)**

# (12) 公表特許公報(A)

(11)特許出願公表番号

特表2007-525771 (P2007-525771A)

(43) 公表日 平成19年9月6日(2007.9.6)

| (51) Int.C1. |       |           | FI   |       |      | テーマコード (参考) |

|--------------|-------|-----------|------|-------|------|-------------|

| G06F         | 3/08  | (2006.01) | GO6F | 3/08  | Н    | 5B018       |

| G06F         | 12/16 | (2006.01) | GO6F | 12/16 | 340Q | 5BO65       |

| G06F         | 3/06  | (2006.01) | GO6F | 3/06  | 304P |             |

|              |       |           | GO6F | 3/06  | 304F |             |

#### 審查譜求 未譜求 予備審查譜求 未譜求 (全 53 百)

|               |                              | 番 直 請 水  | 不請水 丁佩番宜請水 不請水 (至 53 貝) |

|---------------|------------------------------|----------|-------------------------|

| (21) 出願番号     | 特願2007-500989 (P2007-500989) | (71) 出願人 | 505097789               |

| (86) (22) 出願日 | 平成17年2月25日 (2005.2.25)       |          | ティギ・コーポレイション            |

| (85) 翻訳文提出日   | 平成18年9月25日 (2006. 9. 25)     |          | アメリカ合衆国、バージニア州 2218     |

| (86) 国際出願番号   | PCT/US2005/006008            |          | 2、ビエナ、スイート ジー - 100     |

| (87) 国際公開番号   | W02005/084218                |          | 、チェイン・ブリッジ・ロード 2070     |

| (87) 国際公開日    | 平成17年9月15日 (2005.9.15)       | (74)代理人  | 100058479               |

| (31) 優先権主張番号  | 60/548, 110                  |          | 弁理士 鈴江 武彦               |

| (32) 優先日      | 平成16年2月27日 (2004.2.27)       | (74) 代理人 | 100091351               |

| (33) 優先権主張国   | 米国(US)                       |          | 弁理士 河野 哲                |

|               |                              | (74)代理人  | 100088683               |

|               |                              |          | 弁理士 中村 誠                |

|               |                              | (74)代理人  | 100108855               |

|               |                              |          | 弁理士 蔵田 昌俊               |

|               |                              | (74) 代理人 | 100075672               |

|               |                              |          | 弁理士 峰 隆司                |

|               |                              |          | 最終頁に続く                  |

(54) 【発明の名称】データ操作のためのシステム及び方法

# (57)【要約】

低プロフィールのフォームファクタハウジングに配置されているデータ操作装置のための配置が与えられる。データ操作装置は、データの記憶を行うために構成されるメモリと、メモリがバックアップされるとき、バックアップスペースを提供するために構成されるバックアップ記憶装置とを含んでいる。

【選択図】図1

# 【特許請求の範囲】

# 【請求項1】

低プロフィールフォームファクタのハウジングと、

前記ハウジング中に配置され、データの記憶を行うように構成されているメモリと、

前記ハウジング中に配置され、前記メモリを制御するように構成されているメモリ制御 装置と、

前記ハウジング中に配置され、前記メモリ制御装置に接続され、データリクエストを受信して、そのデータリクエストに応答する情報を返送するインターフェースを提供するように構成されているチャンネル制御装置と、

前記ハウジング中に配置され、前記チャンネル制御装置に接続され、前記メモリをバックアップするための記憶スペースを提供するように構成されているバックアップ記憶装置とを具備しているデータ操作装置。

### 【請求項2】

前記メモリは固体ディスクメモリである請求項1記載のデータ操作装置。

#### 【請求項3】

前記バックアップ記憶装置はエラー記録メッセージを記憶するために使用される請求項 2 記載のデータ操作装置。

### 【請求項4】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中のメモリスペースとして使用される請求項2記載のデータ操作装置。

#### 【請求項5】

前記メモリは1以上のLUN構造を有し、各LUN構造は異なるブロックサイズを有するデータを記憶するために使用されることができる請求項1記載のデータ操作装置。

#### 【請求項6】

前記メモリは複数のメモリ部分に分割され、各メモリ部分はスリープモード、ウェイクアップモードのうちの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である請求項1記載のデータ操作装置。

# 【請求項7】

前記チャンネル制御装置はSCSIチャンネル制御装置またはファイバ制御装置のうちの1つである請求項2記載のデータ操作装置。

# 【請求項8】

前記SCSIチャンネル制御装置と前記ファイバチャンネル制御装置は共通の駆動装置に対応している請求項7記載のデータ操作装置。

# 【請求項9】

前記メモリ制御装置は、

前記チャンネル制御装置に接続され、メモリアクセスを制御するように構成されている プロセッサと、

このプロセッサに接続されている同期ダイナミックランダムアクセスメモリ ( S D R A M ) と、

前記メモリに接続され、メモリに直接アクセスすることのできるダイナミックランダムアクセスメモリ(DRAM)制御装置とを具備している請求項1記載のデータ操作装置。

# 【請求項10】

前記DRAM制御装置は前記プロセッサに接続され、前記プロセッサの制御下で前記メモリにアクセスする請求項9記載のデータ操作装置。

# 【請求項11】

前記メモリ制御装置はさらに、

前記プロセッサに接続されているブートフラッシュメモリと、

実時間クロック信号を前記プロセッサに提供するように構成される実時間クロックと、 前記 DRAM制御装置とメモリとの間に情報コンジットを提供するように構成されるダ

20

10

30

40

イナミックランダムアクセスメモリ ( D R A M ) コネクタとを具備している請求項 9 記載のデータ操作装置。

#### 【請求項12】

前 記 プロ セッサ は 汎 用 目 的 の プロ セッサ で あ る 請 求 項 9 記 載 の デ ー タ 操 作 装 置 。

#### 【 請 求 項 1 3 】

前記汎用目的のプロセッサは市場で入手可能である請求項12記載のデータ操作装置。

#### 【請求項14】

オペレーティングシステムが前記プロセッサに配備され、前記プロセッサにおいて動作 することができる請求項9記載のデータ操作装置。

#### 【請求項15】

前記オペレーティングシステムは商用のオペレーティングシステムである請求項 1 4 記載のデータ操作装置。

#### 【請求項16】

前記商用のオペレーティングシステムはLinux(登録商標)である請求項15記載のデータ操作装置。

#### 【請求項17】

前記プロセッサは、

前記チャンネル制御装置とインターフェースするように構成されているバスインターフェースと。

データのリクエストを処理するために前記バスインターフェースと通信するデータアクセスリクエストハンドラと、

メモリのロードを行うように構成されているメモリロードハンドラと、

データをメモリから前記バックアップ記憶装置へ移動するように構成されているメモリ バックアップハンドラとを具備している請求項9記載のデータ操作装置。

# 【請求項18】

前記データアクセスリクエストハンドラは、

データ操作装置の現在のシステム状態を決定するように構成されているシステム状態決定装置と、

データリクエストがメモリから処理されるべきか否かを決定するように構成されている 動作装置決定装置と、

前記動作装置決定装置が、読取リクエストにしたがって読取られるデータがメモリから 読取られることを決定するとき、メモリ読取動作を行うように構成されているメモリ読取 ハンドラと、

前記動作装置決定装置が、書込みリクエストにしたがって書込まれるデータがメモリへ 書込まれることを決定するとき、メモリ書込みを行うように構成されているメモリ書込み ハンドラと、

前記動作装置決定装置が、読取リクエストにしたがって読取られるデータがバックアップ記憶装置から読取られることを決定するとき、バックアップ記憶装置からの読取動作を行うように構成されているバックアップ記憶装置の読取ハンドラと、

前記動作装置決定装置が、書込みリクエストにしたがって書込まれるデータがバックアップ記憶装置へ書込まれることを決定するとき、バックアップ記憶装置における書込み動作を行うように構成されているバックアップ記憶装置の書込みハンドラとを具備している請求項17記載のデータ操作装置。

# 【請求項19】

前記システム状態決定装置は、少なくとも1つのフラグに基づいて、システム状態を決定する請求項18記載のデータ操作装置。

### 【請求項20】

前記少なくとも1つのフラグは、進行中のメモリロードプロセスを示す回復フラグと、 メモリからバックアップ記憶装置へ移動しているデータを示すバックアップフラグとを含 んでいる請求項19記載のデータ操作装置。 10

20

30

40

30

40

50

# 【請求項21】

メモリロードプロセスが開始するとき、メモリロードフラグはメモリロードハンドラによって設定され、メモリロードプロセスが終了されるとき、リセットされる請求項 2 0 記載のデータ操作装置。

# 【請求項22】

メモリバックアップが開始するとき、バックアップフラグはメモリバックアップハンドラにより設定され、メモリバックアップが終了されるとき、リセットされる請求項 2 0 記載のデータ操作装置。

# 【請求項23】

前記データアクセスリクエストハンドラはさらに、データリクエストを複数のLUN構造のうちの1つにマップするように構成されているLUNマッピング機構を具備し、マップされたLUN構造のブロックサイズはデータリクエストにより要求されるブロックサイズに一致する請求項18記載のデータ操作装置。

# 【請求項24】

前記データアクセスリクエストハンドラはさらに、データ操作装置が初期化されるとき、均一のブロックサイズを有する複数のLUN構造を初期化するように構成されているLUN初期化装置を具備している請求項23記載のデータ操作装置。

# 【請求項25】

前記プロセッサはさらに、

診断ルーチンを行うように構成されている診断機構と、

前記診断機構により発生されるエラー情報をバックアップ記憶装置へ書込むように構成されているエラー記録機構とを具備している請求項17記載のデータ操作装置。

# 【請求項26】

診断機構は、外部の手作業の付勢により、および/またはプロセッサで稼動するオペレーティングシステムにより付勢される請求項25記載のデータ操作装置。

# 【請求項27】

診断機構は局地的および / または遠隔操作で付勢されることができる請求項 2 5 記載のデータ操作装置。

# 【請求項28】

前記プロセッサはさらに、メモリ中の異なるメモリ部分のモードを制御するように構成されているメモリ状態制御装置を具備する請求項17記載のデータ操作装置。

# 【請求項29】

前記メモリは、メモリは二倍のデータ率の同期ダイナミックランダムアクセス(DDR DRAM)メモリの少なくとも1つのメモリボードを具備している請求項1記載のデータ操作装置。

# 【請求項30】

メモリボードは、

少なくとも1つのメモリバンクと、

前記少なくとも1つのメモリバンクをクロックするための1以上の位相ロックループ( PLL)と、

少なくとも 1 つの登録されたバッファとを具備している請求項 2 9 記載のデータ操作装置。

# 【請求項31】

前記バックアップ記憶装置は、バックアップ記憶制御装置と、そのバックアップ記憶制御装置によって制御されるディスクとを具備している請求項1記載のデータ操作装置。

# 【請求項32】

前記バックアップ記憶制御装置はチャンネル制御装置及びメモリ制御装置と通信する請求項31記載のデータ操作装置。

# 【請求項33】

さらに、充電可能なバッテリを介してデータ操作装置へ電力を供給するように構成され

(5)

ているバッテリシステムを具備している請求項1記載のデータ操作装置。

#### 【請求項34】

前記バッテリシステムは、

再充電可能なバッテリと、

再充電可能なバッテリの電力レベルを監視するように構成されているモニタと、

バッテリを充電するように構成されているバッテリ充電装置と、

ある入力電圧を有する再充電可能なバッテリから、データ操作装置により必要とされる 複数の出力電力のうちの1つへ電力を変換するように構成されているDC・DC変換器と を具備している請求項33記載のデータ操作装置。

#### 【請求項35】

前記再充電可能なバッテリは自動的に放電を開始できるように構成されている請求項34記載のデータ操作装置。

### 【請求項36】

バッテリは周期的に放電される請求項35記載のデータ操作装置。

#### 【請求項37】

バッテリはバッテリがフルパワーに到達したときに放電される請求項 3 5 記載のデータ 操作装置。

### 【請求項38】

バッテリの放電は前記プロセッサによって制御される請求項35記載のデータ操作装置

【請求項39】

データの記憶を行うように構成されたメモリと、

前記メモリを制御するように構成されたメモリ制御装置と、

前記メモリ制御装置に接続され、データリクエストを受信して、そのデータリクエスト に応答して情報を返送するためのインターフェースを提供するように構成されているチャ ンネル制御装置とを具備し、

前記メモリは複数のメモリ部分を有し、各メモリ部分はスリープモード、ウェイクアップモードのうちの1つに設定されることが可能であり、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能であるデータ操作装置。

【請求項40】

さらに、チャンネル制御装置に接続され、メモリをバックアップするための記憶スペースを提供するように構成されているバックアップ記憶装置を具備している請求項39記載のデータ操作装置。

【請求項41】

前記メモリは固体ディスクメモリである請求項39記載のデータ操作装置。

【請求項42】

前記バックアップ記憶装置はエラー記録メッセージを記憶するために使用される請求項4 0 記載のデータ操作装置。

【請求項43】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中にメモリスペースとして使用される請求項40記載のデータ操作装置。

【請求項44】

前記メモリは1以上のLUN構造を有し、各LUN構造は異なるブロックサイズを有するデータを記憶するために使用されることができる請求項39記載のデータ操作装置。

【請求項45】

前記チャンネル制御装置はSCSIチャンネル制御装置またはファイバ制御装置のうちの一方である請求項39記載のデータ操作装置。

【請求項46】

前記SCSIチャンネル制御装置と前記ファイバチャンネル制御装置は共通の駆動装置

20

10

30

40

に対応している請求項45記載のデータ操作装置。

#### 【請求項47】

前記メモリ制御装置は、

前記チャンネル制御装置に接続され、メモリアクセスを制御するように構成されている プロセッサと、

このプロセッサに接続されている同期ダイナミックランダムアクセスメモリ ( S D R A M ) と、

前記メモリに接続され、メモリを直接アクセスすることができるダイナミックランダムアクセスメモリ(DRAM)制御装置とを具備している請求項39記載のデータ操作装置

【請求項48】

前記DRAM制御装置は前記プロセッサに接続され、プロセッサの制御下でメモリにアクセスする請求項47記載のデータ操作装置。

【請求項49】

前記プロセッサは市場で入手可能な汎用目的のプロセッサである請求項47記載のデータ操作装置。

【請求項50】

商用のオペレーティングシステムが前記プロセッサに配備され、プロセッサで動作する 請求項47記載のデータ操作装置。

【請求項51】

前記商用のオペレーティングシステムはLinuxである請求項50記載のデータ操作装置。

【請求項52】

前記プロセッサは、現在のシステム状態に基づいて、データリクエストがメモリまたは バックアップ記憶装置から処理されるか、或いはそれらの両者から処理される請求項 4 7 記載のデータ操作装置。

【請求項53】

前記システム状態は、少なくとも1つのフラグに基づいて決定される請求項52記載のデータ操作装置。

【請求項54】

前記少なくとも 1 つのフラグは、進行中のメモリロードプロセスを示す回復フラグと、メモリからバックアップ記憶装置へ移動しているデータを示すバックアップフラグとを含んでいる請求項 5 3 記載のデータ操作装置。

【請求項55】

前記プロセッサはさらに、データリクエストを複数のLUN構造のうちの1つにマップすることが可能であり、マップされたLUN構造のブロックサイズはデータリクエストにより必要とされるブロックサイズに一致する請求項54記載のデータ操作装置。

【請求項56】

前記プロセッサはさらに、

診断ルーチンを行うように構成されている診断機構と、

この診断機構により発生されるエラー情報をバックアップ記憶装置へ書込むように構成されているエラー記録機構とを具備している請求項47記載のデータ操作装置。

【請求項57】

前記プロセッサはさらに、メモリ中の異なるメモリ部分のモードを制御するように構成されているメモリ状態制御装置を具備している請求項47記載のデータ操作装置。

【請求項58】

さらに、充電可能なバッテリを介してデータ操作装置へ電力を提供するように構成されているバッテリシステムを具備しており、充電可能なバッテリは自動的に放電を開始できるように構成されている請求項39記載のデータ操作装置。

【請求項59】

10

20

30

40

20

30

40

50

バッテリは周期的に放電される請求項58記載のデータ操作装置。

#### 【請求項60】

バッテリはバッテリがフルパワーに到達したときに放電される請求項 5 8 記載のデータ操作装置。

# 【請求項61】

データの記憶を行うように構成されたメモリと、

このメモリを制御するように構成されたメモリ制御装置と、

前記メモリ制御装置に接続され、データリクエストを受信して、そのデータリクエスト に対する応答として情報を返送するためのインターフェースを提供するように構成されて いるチャンネル制御装置とを具備し、

前記メモリは複数のLUN構造として組織され、それぞれ少なくとも2つの異なるブロックサイズのデータを記憶することが可能にされているデータ走査装置。

# 【請求項62】

前 記 メ モ リ は 固 体 デ ィ ス ク メ モ リ で あ る 請 求 項 6 1 記 載 の デ ー タ 操 作 装 置 。

#### 【請求項63】

さらに、前記チャンネル制御装置に接続され、メモリをバックアップするための記憶スペースを提供するように構成されるバックアップ記憶装置を具備している請求項 6 1 記載のデータ操作装置。

#### 【請求項64】

前記バックアップ記憶装置はエラー記録メッセージを記憶するために使用される請求項63記載のデータ操作装置。

#### 【請求項65】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中にメモリスペースとして使用される請求項63記載のデータ操作装置。

# 【請求項66】

前記チャンネル制御装置はSCSIチャンネル制御装置またはファイバ制御装置のうちの一方である請求項61記載のデータ操作装置。

#### 【請求項67】

前記SCSIチャンネル制御装置と前記ファイバチャンネル制御装置は共通の駆動装置に対応している請求項66記載のデータ操作装置。

### 【請求項68】

前記メモリ制御装置は、

前記チャンネル制御装置に接続され、メモリアクセスを制御するように構成されるプロセッサと、

このプロセッサに接続されている同期ダイナミックランダムアクセスメモリ (SDRAM)と、

前記メモリに接続され、メモリに直接アクセスすることができるダイナミックランダムアクセスメモリ(DRAM)制御装置とを具備している請求項61記載のデータ操作装置

#### 【請求項69】

前記DRAM制御装置はプロセッサに接続され、プロセッサの制御下でメモリにアクセスする請求項68記載のデータ操作装置。

# 【請求項70】

前記プロセッサは市場で入手可能な汎用目的のプロセッサである請求項 6 8 記載のデータ操作装置。

# 【請求項71】

商用のオペレーティングシステムがプロセッサに配備され、プロセッサで動作している 請求項68記載のデータ操作装置。

# 【請求項72】

前記商用のオペレーティングシステムはLinuxである請求項71記載のデータ操作

装置。

# 【請求項73】

前記プロセッサは、現在のシステム状態に基づいて、データリクエストがメモリまたは バックアップ記憶装置から処理されるか、或いは両者から処理される請求項 6 8 記載のデータ操作装置。

#### 【請求項74】

システム状態は、少なくとも 1 つのフラグに基づいて決定される請求項 7 3 記載のデータ操作装置。

# 【請求項75】

前記少なくとも 1 つのフラグは、進行中のメモリロードプロセスを示す回復フラグと、 メモリからバックアップ記憶装置へ移動しているデータを示すバックアップフラグとを含 んでいる請求項 7 4 記載のデータ操作装置。

#### 【請求項76】

前記プロセッサはさらに、データリクエストを複数のLUN構造のうちの1つにマップすることが可能であり、マップされたLUN構造のブロックサイズはデータリクエストにより必要とされるブロックサイズに一致している請求項68記載のデータ操作装置。

### 【請求項77】

前記プロセッサはさらに、

診断ルーチンを行うように構成されている診断機構と、

この診断機構により発生されるエラー情報をバックアップ記憶装置へ書込むように構成されているエラー記録機構とを具備している請求項68記載のデータ操作装置。

#### 【請求項78】

前記プロセッサはさらに、メモリ中の異なるメモリ部分のモードを制御するように構成されているメモリ状態制御装置を具備している請求項68記載のデータ操作装置。

# 【請求項79】

さらに、充電可能なバッテリを介してデータ操作装置へ電力を提供するように構成されるバッテリシステムを具備しており、充電可能なバッテリは自動的に放電を開始できるように構成されている請求項61記載のデータ操作装置。

# 【請求項80】

バッテリは周期的に放電される請求項79記載のデータ操作装置。

### 【請求項81】

バッテリはバッテリがフルパワーに到達したときに放電される請求項79記載のデータ 操作装置。

# 【請求項82】

低プロフィールのフォームファクタのハウジングと、

前記ハウジング中に配置され、データの記憶を行うように構成されている固体ディスク メモリと、

前記ハウジング中に配置され、固体ディスクメモリを制御するように構成されているメモリ制御装置と、

前記ハウジング中に配置され、前記メモリ制御装置に接続され、データリクエストを受信して、そのデータリクエストに対する応答として情報を返送するためのインターフェースを提供するように構成されているチャンネル制御装置と、

前記ハウジング中に配置され、前記チャンネル制御装置に接続され、固体ディスクメモリをバックアップするための記憶スペースを提供するように構成されるバックアップ記憶装置とを具備しているデータ操作装置。

# 【請求項83】

前記固体ディスクメモリは複数のメモリ部分を有し、各メモリ部分はスリープモード、ウェイクアップモードのうちの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である請求項82記載のデータ操作装置。

30

20

10

40

20

30

40

50

#### 【請求項84】

前記バックアップ記憶装置はエラー記録メッセージを記憶するために使用される請求項 8 2 記載のデータ操作装置。

# 【請求項85】

前記バックアップ記憶装置は、バックアップ記憶装置から固体ディスクメモリへのメモリロード期間中にメモリスペースとして使用される請求項82記載のデータ操作装置。

#### 【請求項86】

前記固体ディスクメモリは 1 以上の L U N 構造に組織化され、各 L U N 構造は異なるブロックサイズを有するデータを記憶するために使用されることができる請求項 8 2 記載のデータ操作装置。

# 【請求項87】

前記チャンネル制御装置はSCSIチャンネル制御装置またはファイバ制御装置のうちの一方である請求項82記載のデータ操作装置。

# 【請求項88】

前記SCSIチャンネル制御装置と前記ファイバチャンネル制御装置は共通の駆動装置に対応している請求項87記載のデータ操作装置。

# 【請求項89】

前記メモリ制御装置は、

前記チャンネル制御装置に接続され、メモリアクセスを制御するように構成されている プロセッサと、

このプロセッサに接続されている同期ダイナミックランダムアクセスメモリ ( S D R A M ) と、

前記固体ディスクメモリに接続され、固体ディスクメモリに直接アクセスすることができるダイナミックランダムアクセスメモリ(DRAM)制御装置とを具備している請求項82記載のデータ操作装置。

# 【請求項90】

前記DRAM制御装置はプロセッサに接続され、前記プロセッサの制御下で固体ディスクメモリにアクセスする請求項89記載のデータ操作装置。

# 【請求項91】

前記プロセッサは市場で入手可能な汎用目的のプロセッサである請求項89記載のデータ操作装置。

# 【請求項92】

商用のオペレーティングシステムがプロセッサに配備され、プロセッサで動作される請求項89記載のデータ操作装置。

# 【請求項93】

前記商用のオペレーティングシステムは L i n u x である請求項 9 2 記載のデータ操作装置。

# 【請求項94】

前記プロセッサは、現在のシステム状態に基づいて、データリクエストが固体ディスクメモリまたはバックアップ記憶装置から処理されるか、或いは両者から処理される請求項89記載のデータ操作装置。

#### 【請求項95】

システム状態は、少なくとも 1 つのフラグに基づいて決定される請求項 9 4 記載のデータ操作装置。

#### 【請求項96】

前記少なくとも1つのフラグは、進行中のメモリロードプロセスを示す回復フラグと、 固体ディスクメモリからバックアップ記憶装置へ移動しているデータを示すバックアップ フラグとを含んでいる請求項96記載のデータ操作装置。

# 【請求項97】

前記プロセッサはさらに、データリクエストを複数のLUN構造のうちの1つにマップ

することが可能に構成され、マップされたLUN構造のブロックサイズはデータリクエストにより必要とされるブロックサイズに一致している請求項96記載のデータ操作装置。

### 【請求項98】

前記プロセッサはさらに、

診断ルーチンを行うように構成されている診断機構と、

診断機構により発生されるエラー情報を前記バックアップ記憶装置へ書込むように構成されているエラー記録機構とを具備している請求項89記載のデータ操作装置。

### 【請求項99】

前記プロセッサはさらに、固体ディスクメモリ中の異なるメモリ部分のモードを制御するように構成されているメモリ状態制御装置を具備している請求項89記載のデータ操作装置。

【請求項100】

さらに、充電可能なバッテリを介してデータ操作装置へ電力を提供するように構成されているバッテリシステムを具備しており、充電可能なバッテリは自動的に放電を開始できるように構成されている請求項82記載のデータ操作装置。

【請求項101】

バッテリは周期的に放電される請求項100記載のデータ操作装置。

【 請 求 項 1 0 2 】

バッテリはバッテリがフルパワーに到達したときに放電される請求項100記載のデータ操作装置。

【請求項103】

高速度のデータ記憶及びアクセスを行うように構成されているデータ操作装置と、

前記データ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を 受信する1以上のホストシステムとを具備し、

前記データ操作装置は、データ記憶を行うように構成されているメモリと、このメモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置とを有している記憶システム。

【請求項104】

高速度のデータ記憶及びアクセスを行うように構成されるデータ操作装置と、

このデータ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を 受信する1以上のホストシステムとを具備し、

データ操作装置は、データ記憶を行うように構成されているメモリと、このメモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置とを有しており、

データリクエストは、データ操作装置のシステム状態にしたがって、メモリおよび / またはバックアップ記憶装置から処理される記憶システム。

【請求項105】

高速度のデータ記憶及びアクセスを行うように構成されているデータ操作装置と、

このデータ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を 受信する1以上のホストシステムとを具備し、

前記データ操作装置は、データ記憶を行うように構成されているメモリと、メモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置と、商用のオペレーティングシステムと共に配備されている汎用目的のプロセッサを使用して構成されているメモリ制御装置とを具備している記憶システム。

【請求項106】

高速度のデータ記憶及びアクセスを行うように構成されているデータ操作装置と、

このデータ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を 受信する1以上のホストシステムとを具備し、

前記データ操作装置は、データ記憶を行うように構成されているメモリと、メモリをバックアップするためのバックアップスペースを提供するように構成されているバックアッ

10

20

30

40

20

30

40

50

プ記憶装置と、商用のオペレーティングシステムと共に配備される汎用目的のプロセッサを使用して構成されているメモリ制御装置と、チャンネル制御装置とを具備し、このチャンネル制御装置はSCSIチャンネル制御装置またはファイバチャンネル制御装置の一方であり、SCSIチャンネル制御装置とファイバチャンネル制御装置は共通の駆動装置に対応している記憶システム。

#### 【 請 求 項 1 0 7 】

前記メモリは固体ディスクメモリである請求項106記載の記憶装置。

### 【請求項108】

前記データ操作装置は、低プロフィールフォームファクタである請求項106記載の記憶システム。

# 【請求項109】

前記データ操作装置は、診断ルーチンを実行するために付勢されることのできる診断機構を含み、付勢は内部および/または外部でトリガーされることが可能である請求項11 7記載の記憶システム。

#### 【請求項110】

前記診断ルーチン期間中に発生されたエラーメッセージはバックアップ記憶装置中に記録される請求項109記載の記憶システム。

### 【請求項111】

前記データ操作装置はさらに、充電可能なバッテリを介してデータ操作装置へ電力を提供するように構成されているバッテリシステムを具備しており、充電可能なバッテリは自動的に放電を開始できるように構成されている請求項109記載の記憶システム。

### 【請求項112】

高速度のデータ記憶及びアクセスを行うように構成されているデータ操作装置と、 このデータ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を 受信する1以上のホストシステムとを具備し、

前記データ操作装置は、データ記憶を行うように構成されているメモリを具備し、そのメモリはそれぞれ異なるブロックサイズのデータを記憶することができる複数のLUN構造に組織されている記憶システム。

# 【請求項113】

高速度のデータ記憶及びアクセスを行うように構成されているデータ操作装置と、 このデータ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を 受信する1以上のホストシステムとを具備し、

前記データ操作装置は、データ記憶を行うように構成されるメモリを有し、

メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードとのうちの一方に設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である記憶システム。

# 【請求項114】

サービスを提供するように構成されているマスターサーバと、

このマスターサーバと通信する1以上のスレーブのデータ操作装置とを具備し、

前記各データ操作装置はマスターサーバにより割当てられたタスクを実行し、応答をサーバに返送するように構成され、

前記各データ操作装置は低プロフィールフォームファクタであり、データ記憶を行うように構成されているメモリと、そのメモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置とを有しているマスター・スレーブ構造。

### 【請求項115】

サービスを提供するように構成されているマスターサーバと、 このマスターサーバと通信する 1 以上のスレーブのデータ操作装置とを具備し、

前記各データ操作装置はマスターサーバにより割当てられたタスクを実行し、応答をサ

- バに返送するように構成され、

前記各データ操作装置は低プロフィールフォームファクタであり、データ記憶を行うように構成されているメモリと、メモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置とを有しているマスター・スレーブ構造。

### 【請求項116】

サービスを提供するように構成されているマスターサーバと、

このマスターサーバと通信する1以上のスレーブのデータ操作装置とを具備し、

前記各データ操作装置はマスターサーバにより割当てられたタスクを実行し、応答をサーバに返送するように構成され、

前記各データ操作装置は低プロフィールフォームファクタであり、データ記憶を行うように構成されているメモリと、そのメモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置と、商用のオペレーティングシステムと共に配備されている汎用目的のプロセッサを使用して構成されているメモリ制御装置とを有しているマスター・スレーブシステム。

#### 【請求項117】

サービスを提供するように構成されるマスターサーバと、

このマスターサーバと通信する1以上のスレーブのデータ操作装置とを具備し、

前記各データ操作装置はマスターサーバにより割当てられたタスクを実行し、応答をサーバに返送するように構成され、

前記各データ操作装置は低プロフィールフォームファクタであり、データ記憶を行うように構成されているメモリと、そのメモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置と、商用のオペレーティングシステムと共に配備されている汎用目的のプロセッサを使用して構成されるメモリ制御装置と、チャンネル制御装置とを具備し、そのチャンネル制御装置はSCSIチャンネル制御装置またはファイバチャンネル制御装置のいずれか一方であり、SCSIチャンネル制御装置とファイバチャンネル制御装置の駆動装置に対応しているマスター・スレーブシステム。

# 【請求項118】

メモリは固体ディスクメモリである請求項117記載のマスター・スレーブシステム。

### 【請求項119】

前記データ操作装置は、診断ルーチンを実行するために付勢されることのできる診断機構を含み、その付勢は内部および/または外部でトリガーされることが可能である請求項1 1 7 記載のマスター・スレープ構造。

# 【請求項120】

診断ルーチン期間中に発生されたエラーメッセージはバックアップ記憶装置に記録される請求項119記載のマスター - スレーブ構造。

# 【請求項121】

前記データ操作装置はさらに、充電可能なバッテリを介してデータ操作装置へ電力を提供するために構成されているバッテリシステムを具備しており、充電可能なバッテリは自動的に放電を開始できるように構成されている請求項117記載のマスター・スレーブ構造。

# 【請求項122】

サービスを提供するように構成されているマスターサーバと、

このマスターサーバと通信する1以上のスレーブのデータ操作装置とを具備し、

前記各データ操作装置はサーバにより割当てられたタスクを実行し、応答をサーバに返送するように構成され、

前記各データ操作装置は低プロフィールフォームファクタであり、データ記憶を行うように構成されているメモリとを具備し、

そのメモリはそれぞれ異なるブロックサイズのデータを記憶することができる複数のL

10

20

30

40

UN構造に組織化されているマスター - スレーブシステム。

# 【請求項123】

サービスを提供するように構成されているマスターサーバと、

このマスターサーバと通信する1以上のスレーブのデータ操作装置とを具備し、

前記各データ操作装置はサーバにより割当てられたタスクを実行し、応答をサーバに返送するように構成され、

前記各データ操作装置は低プロフィールフォームファクタであり、データ記憶を行うように構成されるメモリを有し、

前記メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードの一方に設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能であるマスター・スレーブシステム。

### 【請求項124】

データ操作装置を初期化し、

データリクエストを受信し、

データ操作装置のシステム状態を決定し、

決定されたシステム状態に基づいて、データリクエストを処理するステップを含んでおり、

前記データ操作装置は、データ記憶のためのメモリと、データ操作装置がメモリをバックアップするときのバックアップスペースのためのバックアップ記憶装置を提供し、

前記データリクエストは、システム状態に基づいて、メモリと、バックアップ記憶装置の一方から処理されるか、或いは両方から処理されるデータ操作装置の処理方法。

# 【請求項125】

前記初期化は、

前記データ操作装置に配備されているオペレーティングシステムをブートし、

1以上のメモリ部分を有するメモリを初期化し、

バックアップ記憶装置を駆動するバックアップディスク駆動装置を初期化し、

共通の駆動装置に対応するSCSI/ファイバ駆動装置を初期化し、

初期化状態に基づいてシステム状態を設定するステップを含んでいる請求項124記載の方法。

### 【請求項126】

前記受信は、

データリクエストをSCSI/ファイバインターフェースを介して獲得し、

データリクエストを翻訳し、

翻訳されたデータリクエストを、システム状態に基づいて、バックアップディスク駆動装置と、メモリを駆動するメモリ駆動装置の少なくとも一方へ転送するステップを含んでいる請求項124記載の方法。

# 【請求項127】

前記決定は、以下の複数のシステム状態の1つを決定し、複数のシステム状態は、

ブートシステム状態と、

サービス中のシステム状態と、

回復システム状態と、

バックアップシステム状態と、

サービス中・バックアップ係属状態と、

サービス中・バックアップ状態と、

回復・バックアップ係属状態と、

アイドルシステム状態と、

オフシステム状態とを含んでいる請求項124記載の方法。

#### 【請求項128】

前記処理は、

20

10

30

40

決定されたシステム状態が、バックアップシステム状態、アイドルシステム状態、オフシステム状態のうちの 1 つに対応しないならば、データリクエストに基づいてデータアクセスを実行し、

システム状態が、バックアップシステム状態、アイドルシステム状態、オフシステム状態のうちの1つに対応するならば、データリクエストの処理を拒否するステップを含んでいる請求項124記載の方法。

# 【請求項129】

前記実行は、

システム状態が、サービス中システム状態およびサービス中 - バックアップ係属システム状態の一方に対応するならば、メモリからのデータリクエストに基づいて、データアクセスを実行し、

システム状態が、回復システム状態、サービス・バックアップシステム状態、回復・バックアップ係属システム状態のうちの1つに対応するならば、メモリまたはバックアップ記憶装置のいずれか一方からのデータリクエストにしたがって、データアクセスを実行するステップを含んでいる請求項128記載の方法。

#### 【請求項130】

前記メモリからのデータアクセスの実行は、

データリクエストにより要求されるブロックサイズに一致するブロックサイズに対応するメモリ中の複数の L U N 構造のうちの 1 つにデータリクエストをマップし、

データリクエストが読取リクエストであるならば、メモリ中のマップされた L U N 構造からデータを読取り、

データリクエストが書込みリクエストであるならば、メモリ中のマップされたLUN構造へデータを書込むステップを含んでいる請求項129記載の方法。

#### 【請求項131】

さらに、前記読取後、メモリから読取られたデータを受信し、

前記書込み後、メモリからの確認を受信するステップを含んでいる請求項130記載の方法。

#### 【請求項132】

メモリまたはバックアップ記憶装置のいずれか一方からのデータアクセスの前記実行は

データリクエストが読取リクエストであり、 読取られるデータがメモリに存在しないならば、バックアップ記憶装置からデータを読取り、

データリクエストが読取リクエストであり、読取られるデータがメモリに存在するならば、メモリからデータを読取り、

データリクエストが書込みリクエストであるならば、メモリおよびバックアップ記憶装 置の両者へデータを書込むステップを含んでいる請求項129記載の方法。

### 【請求項133】

メモリおよびバックアップ記憶装置の両者へのデータの前記書込みは、

データリクエストにより要求されるブロックサイズに対応するブロックサイズを有する 複数の L U N 構造のうちの 1 つに書込みリクエストをマップし、

バックアップ記憶装置およびメモリ中のマップされたLUN構造へデータを書込み、

前記データの書込み後、バックアップ記憶装置から書込み確認を受信するステップを含んでいる請求項132記載の方法。

# 【請求項134】

さらに、バックアップ動作を行うステップを含んでいる請求項128記載の方法。

# 【請求項135】

さらに、診断動作を行うステップを含んでいる請求項128記載の方法。

### 【請求項136】

前記診断の実行は、ある時間間隔にしたがって、手作業のコマンドおよび実時間クロックプリセットの少なくとも一方により付勢される請求項135記載の方法。

20

10

30

40

#### 【請求項137】

前記診断の実行は、

試験されているコンポーネントに信号を送信し、

その信号を受信した後、コンポーネントに関して測定された結果を予想された結果と比較し、

コンポーネントからの結果が予想された結果と一致しない場合には、バックアップ記憶 装置中にエラーメッセージを記録するステップを含んでいる請求項135記載の方法。

# 【請求項138】

さらに、データリクエストに対する応答として、前記処理の結果に関連する情報を送信 するステップを含んでいる請求項124記載の方法。

【請求項139】

前記メモリは固体ディスクメモリである請求項124記載の方法。

#### 【請求項140】

前記メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードの一方に設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である請求項124記載の方法。

# 【請求項141】

データリクエストを、ホストシステムから、データ操作装置へ送信し、

そのデータ操作装置によって、データリクエストを受信し、

前記データ操作装置の現在のシステム状態にしたがって、前記データ操作装置によりデータリクエストを処理し、

前記データ操作装置によって、データリクエストに対する応答としての結果を、前記ホストシステムへ送信するステップを含み、

前記データ操作装置はデータ記憶のためのメモリと、メモリのバックアップのためのバックアップ記憶装置を備えており、

メモリとバックアップ記憶装置の両者は低プロフィールフォームファクタのハウジング中に配置されている記憶方法。

# 【請求項142】

バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中に 一時的なメモリとして使用されることができる請求項141記載の方法。

# 【請求項143】

前記データ操作装置はSCSIおよびファイバインターフェースの一つを介して、データリクエストを受信し、SCSIおよびファイバインターフェースは共通の駆動装置を共有する請求項141記載の方法。

# 【請求項144】

前記メモリは固体ディスクメモリである請求項141記載の方法。

# 【請求項145】

前記メモリは複数のLUN構造を有し、それぞれ少なくとも2つの異なるブロックサイズのデータを記憶することが可能である請求項141記載の方法。

# 【請求項146】

メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である請求項141記載の方法。

# 【請求項147】

前記データ操作装置は、条件が満たされるとき、そのバッテリの電力を自動的に放電することができる請求項141記載の方法。

# 【請求項148】

データ操作装置は、診断ルーチンを実行することができる請求項141記載の方法。

10

20

30

40

# 【請求項149】

診 断 ル ー チ ン 期 間 中 に 発 生 さ れ る エ ラ ー メ ッ セ ー ジ は 、 バ ッ ク ア ッ プ 記 憶 装 置 に 書 込 ま れる請求項148記載の方法。

### 【請求項150】

前 記 デ ー タ 操 作 装 置 は 汎 用 目 的 の プ ロ セ ッ サ を 使 用 し 、 商 用 の オ ペ レ ー テ ィ ン グ シ ス テ ムは汎用目的のプロセッサで動作される請求項141記載の方法。

# 【請求項151】

データリクエストを、ホストシステムから、データ操作装置へ送信し、

そのデータ操作装置によって、そのデータリクエストを受信し、

デ ー 夕 操 作 装 置 の 現 在 の シ ス テ ム 状 態 に し た が っ て 、 デ ー 夕 操 作 装 置 に よ っ て デ ー タ リ クエストを処理し、

データ操作装置によって、データリクエストに対する応答としての結果を、ホストシス テムへ送信するステップを含み、

データ操作装置はデータ記憶のためのメモリと、メモリのバックアップのためのバック アップ記憶装置を備え、

前 記 メ モ リ は 複 数 の L U N 構 造 を 有 し 、 そ れ ぞ れ 少 な く と も 2 つ の 異 な る ブ ロ ッ ク サ イ ズのデータを記憶することが可能である記憶方法。

# 【請求項152】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間 中に一時的なメモリとして使用されることができる請求項151記載の方法。

#### 【請求項153】

データ操作装置はSCSIとファイバインターフェースの一方を介して、データリクエ ストを受信し、SCSIとファイバインターフェースは共通の駆動装置を共有している請 求項151記載の方法。

# 【請求項154】

前 記 メ モ リ は 固 体 デ ィ ス ク メ モ リ で あ る 請 求 項 1 5 1 記 載 の 方 法 。

# 【請求項155】

前記メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクア ップモードの1つに設定されることができ、スリープモード下では、メモリ部分は低電力 消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はア クセス可能である請求項151記載の方法。

# 【請求項156】

データ操作装置は、条件が満たされるとき、そのバッテリの電力を自動的に放電するこ とができる請求項151記載の方法。

# 【請求項157】

前 記 デ ー 夕 操 作 装 置 は 、 診 断 ル ー チ ン を 実 行 す る こ と が で き る 請 求 項 1 5 1 記 載 の 方 法

# 【請求項158】

診 断 ル ー チ ン 期 間 中 に 発 生 さ れ る エ ラ ー メ ッ セ ー ジ は 、 バ ッ ク ア ッ プ 記 憶 装 置 に 書 込 ま れる請求項157記載の方法。

# 【請求項159】

前記データ操作装置は汎用目的のプロセッサを使用している請求項151記載の方法。

# 【請求項160】

商用のオペレーティングシステムが配備され、汎用目的のプロセッサで動作される請求 項159記載の方法。

# 【請求項161】

データリクエストを、ホストシステムから、データ操作装置へ送信し、

そのデータ操作装置によって、データリクエストを受信し、

デ ー 夕 操 作 装 置 の 現 在 の シ ス テ ム 状 態 に し た が っ て 、 デ ー 夕 操 作 装 置 に よ り そ の デ ー タ リクエストを処理し、

20

10

30

40

データ操作装置によって、データリクエストに対する応答としての結果を、ホストシステムへ送信するステップを含み、

データ操作装置はデータ記憶のためのメモリと、メモリのバックアップのためのバック アップ記憶装置とを備えており、

メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップ モードの 1 つに設定されることができ、スリープモード下では、メモリ部分は低電力消費 状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセ ス可能である記憶方法。

# 【請求項162】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中に一時的なメモリとして使用されることができる請求項161記載の方法。

#### 【請求項163】

前記データ操作装置はSCSIとファイバインターフェースの一つを介して、データリクエストを受信し、SCSIとファイバインターフェースは共通の駆動装置を共有している請求項161記載の方法。

#### 【請求項164】

前記メモリは固体ディスクメモリである請求項161記載の方法。

### 【請求項165】

前記メモリは複数のLUN構造を有し、それぞれ少なくとも2つの異なるブロックサイズのデータを記憶することが可能である請求項161記載の方法。

#### 【請求項166】

前記データ操作装置は、条件が満たされるとき、そのバッテリの電力を自動的に放電することができる請求項161記載の方法。

#### 【請求項167】

前記データ操作装置は、診断ルーチンを実行することができる請求項161記載の方法

# 【請求項168】

診断ルーチン期間中に発生されるエラーメッセージは、バックアップ記憶装置に書込まれる請求項167記載の方法。

### 【請求項169】

前記データ操作装置は汎用目的のプロセッサを使用する請求項161記載の方法。

# 【請求項170】

商用のオペレーティングシステムが配備され、汎用目的のプロセッサで動作される請求 項 1 6 9 記載の方法。

# 【請求項171】

データリクエストを、ホストシステムから、データ操作装置へ送信し、

データ操作装置によって、そのデータリクエストを受信し、

データ操作装置の現在のシステム状態を決定し、

現在のシステム状態にしたがって、データ操作装置によってデータリクエストを処理し

データ操作装置によって、データリクエストに対する応答としての結果を、ホストシステムへ送信するステップを含み、

前記データ操作装置はデータ記憶のための固体ディスクメモリと、固体ディスクメモリ のバックアップのためのバックアップ記憶装置とを備えており、

固体ディスクメモリとバックアップ記憶装置の両者は、低プロフィールのフォームファクタのハウジング中に配置される記憶方法。

# 【請求項172】

前記バックアップ記憶装置は、バックアップ記憶装置から固体ディスクメモリへのメモリロード期間中に一時的なメモリとして使用されることができる請求項171記載の方法

20

30

# 【請求項173】

前記データ操作装置はSCSIとファイバインターフェースの一方を介して、データリクエストを受信し、SCSIとファイバインターフェースは共通の駆動装置を共有している請求項171記載の方法。

# 【請求項174】

前記メモリは複数のLUN構造を有し、それぞれ少なくとも2つの異なるブロックサイズのデータを記憶することができる請求項171記載の方法。

# 【請求項175】

前記メモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である請求項171記載の方法。

### 【請求項176】

前記データ操作装置は、予め定められた条件が満たされるとき、そのバッテリの電力を自動的に放電することができる請求項171記載の方法。

#### 【請求頃177】

データ操作装置は、診断ルーチンを実行することができる請求項171記載の方法。

# 【請求項178】

診断ルーチン期間中に発生されるエラーメッセージは、バックアップ記憶装置に書込まれる請求項177記載の方法。

#### 【請求項179】

前記データ操作装置は汎用目的のプロセッサを使用する請求項171記載の方法。

### 【請求項180】

商用のオペレーティングシステムが配備され、汎用目的のプロセッサで動作される請求 項179記載の方法。

#### 【請求項181】

マスターサーバをスレーブデータ操作装置と接続し、

マスターサーバによって、指定されたタスクを実行するようにスレーブデータ操作装置 を付勢するステップを含み、

前記スレーブデータ操作装置は、低プロフィールのフォームファクタのハウジング中に配置され、記憶を行うように構成されているメモリと、そのメモリをバックアップするためのバックアップスペースを提供するように構成されるバックアップ記憶装置とを有しているマスター・スレーブ方法。

# 【請求項182】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中に一時的なメモリとして使用されることができる請求項181記載の方法。

### 【請求項183】

前記データ操作装置はSCSIとファイバインターフェースの一方を介してデータリクエストを受信し、SCSIとファイバインターフェースは共通の駆動装置を共有している請求項181記載の方法。

# 【請求項184】

前記データ操作装置は、予め定められた条件が満たされるとき、そのバッテリの電力を 自動的に放電することができる請求項181記載の方法。

# 【請求項185】

前記データ操作装置は、診断ルーチンを実行することができる請求項181記載の方法

### 【請求項186】

診断ルーチン期間中に発生されるエラーメッセージは、バックアップ記憶装置に書込まれる請求項 1 8 5 記載の方法。

# 【請求項187】

50

10

20

30

前記データ操作装置は、商用のオペレーティングシステムを配備している汎用目的のプロセッサを使用する請求項181記載の方法。

# 【請求項188】

マスターサーバをスレーブデータ操作装置と接続し、

マスターサーバによって、指定されたタスクを実行するようにスレーブデータ操作装置 を付勢するステップを含み、

前記スレーブデータ操作装置は、データの記憶を行うように構成されているメモリを有し、そのメモリは複数のLUN構造を有し、それぞれ少なくとも2つの異なるブロックサイズのデータを記憶することができるマスター・スレーブ方法。

#### 【請求項189】

マスターサーバをスレーブデータ操作装置と接続し、

マスターサーバによって、指定されたタスクを実行するようにスレーブデータ操作装置 を付勢するステップを含み、

前記スレーブデータ操作装置は、データの記憶を行うように構成されているメモリを有し、そのメモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能であるマスター・スレーブ方法。

#### 【請求項190】

マスターサーバをスレーブデータ操作装置と接続し、

マスターサーバによって、指定されたタスクを実行するようにスレーブデータ操作装置 を付勢するステップを含み、

前記スレーブデータ操作装置は、低プロフィールフォームファクタのハウジング中に配置され、データ記憶を行うように構成されている固体ディスクメモリと、固体ディスクメモリをバックアップするためのバックアップスペースを提供するように構成されるバックアップ記憶装置とを有しているマスター・スレーブ方法。

# 【請求項191】

データ操作装置によって、データを受信し、

受信されたデータを処理し、

前記解析および / またはデータからの結果をネットワークノードに送信するステップを 含み、

前記データ操作装置は、低プロフィールフォームファクタのハウジング中に配置され、 データ記憶を行うように構成されているメモリと、そのメモリをバックアップするための バックアップスペースを提供するように構成されているバックアップ記憶装置とを有して いる方法。

# 【請求項192】

ネットワークノードはネットワークスイッチを含んでいる請求項191記載の方法。

# 【請求項193】

ネットワークノードはルータを含んでいる請求項191記載の方法。

# 【請求項194】

データ操作装置によって、データを受信し、

受信されたデータを処理し、

解析および/またはデータからの結果をネットワークノードに送信するステップを含み

メモリはデータ記憶を行うように構成されているメモリを有し、そのメモリは複数のLUN構造を有し、そのそれぞれは2以上の異なるブロックサイズのデータを記憶することができるように構成されている方法。

# 【請求項195】

データ操作装置によって、データを受信し、 受信されたデータを処理し、 10

20

30

40

前記解析および / またはデータからの結果をネットワークノードに送信するステップを 含み、

データ操作装置はデータ記憶を行うように構成されているメモリを有し、そのメモリは複数のメモリ部分を有し、各メモリ部分はスリープモードと、ウェイクアップモードの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である方法。

# 【請求項196】

データ操作装置によって、データを受信し、

受信されたデータを処理し、

前記解析および / またはデータからの結果をネットワークノードに送信するステップを 含み、

データ操作装置は、低プロフィールフォームファクタのハウジング中に配置され、データ記憶を行うように構成されている固体ディスクメモリと、固体ディスクメモリをバックアップするためのバックアップスペースを提供するように構成されているバックアップ記憶装置とを有している方法。

# 【発明の詳細な説明】

# 【技術分野】

# [0001]

本発明はデータ操作のためのシステム及び方法と、データ操作装置を含むシステムに関する。

### 【背景技術】

# [0002]

本出願は、その全体がここで参考文献として含まれる2004年2月27日出願の米国暫定特許出願第60/548,110号明細書に基づき、その優先権を得ている。

#### 【発明の開示】

【発明が解決しようとする課題】

#### [00003]

本発明はデータ操作のためのシステム及び方法を提供することを目的としている。

### 【課題を解決するための手段】

### [0004]

本発明のデータ操作装置は、低プロフィールフォームファクタのハウジングと、前記ハウジング中に配置され、データの記憶を行うように構成されているメモリと、前記ハウジング中に配置され、前記メモリ制御装置に接続され、データリクエストを受信して、そのデータリクエストに応答する情報を返送するインターフェースを提供するように構成されているチャンネル制御装置と、前記ハウジング中に配置され、前記チャンネル制御装置に接続され、前記メモリをバックアップするための記憶スペースを提供するように構成されているバックアップ記憶装置とを具備していることを特徴としている。

# 【発明を実施するための最良の形態】

# [0005]

ここで請求されている本発明は幾つかの実施形態で例示される。これらの例示的な実施 形態は図面を参照にして詳細に説明される。これらの実施形態は図面に示されている例示 的な実施形態だけに限定されない。同じ参照符号は図面全体を通して類似の部分を表して いる。

以下説明する処理は、適切にプログラムされた汎用目的コンピュータ単独で、または特別目的のコンピュータと接続して実行されることができる。このような処理は単一のプラットフォームによって、または分配された処理プラットフォームによって実行されることができる。さらに、このような処理及び機能は、特別目的のハードウェアの形態、または汎用目的またはネットワークのプロセッサによって稼動されるソフトウェアまたはファー

10

20

30

40

20

30

40

50

ムウェアの形態で実行されることができる。したがって、図面で示され以下説明される動作ブロックは、特別目的の回路であってもよく、或いはプロセッサで実行されるソフトウェアのセクションであってもよい。このような処理で扱われるデータ、または、このような処理の結果として生成されるデータは、技術では通常であるように任意のメモリに記憶されることができる。例示によって説明すると、このようなデータは所定のコンピュータシステムまたはサブシステムのRAMのような一時的なメモリに記憶されることができる。さらに、又はその代わりに、このようなデータは長期の記憶装置、例えば磁気ディスク、再書込み可能な光学ディスク等に記憶されることができる。ここでの説明のために、コンピュータの読取可能な媒体は、このような既存のメモリ技術と、このような構造及びこのようなデータを表すハードウェアまたは回路を含めた任意の形態のデータ記憶機構を含むことができる。

[0006]

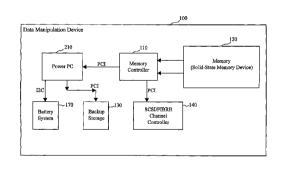

図 1 は、本発明の 1 実施形態によるデータ操作装置(DMD)100の高レベルの機能ブ ロック図を示している。DMD100は、SCSIチャンネル制御装置またはファイバチャ ン ネ ル 制 御 装 置 で あ る こ と の で き る チ ャ ン ネ ル 制 御 装 置 140 と 、 技 術 内 で 利 用 可 能 な 他 の イン ターフェース 制 御 装 置 上 に 、 メ モ リ 120の デ ー タ 記 憶 及 び ア ク セ ス を 制 御 す る メ モ リ 制 御 装 置 110と、 バック アップ 記 憶 システム 130と、 パワーPC( 210)及 びバッテリシス テムのような低電力 С Р U 150を具備している。 D M D 100中の S С S I / ファイバ / イン ターフェースチャンネル制御装置140は外界とのインターフェースを行うためのものであ る。 D M D 100と外界との間の相互動作特性は、 D M D 100が配備される目的と、配備の文 脈におけるDMD100の機能的役割にしたがうことができる。例えば、DMD100が高速度 の固体ディスク記憶をエミュレートするために配備されるとき、SCSI/ファイバ(ま たは技術内の他のインターフェース)チャンネル制御装置140は1以上のホストシステム とインターフェースすることができる。この場合、 D M D 100は S C S I / ファイバチャ ン ネ ル 制 御 装 置 140を 通 し て 、 ホ ス ト シ ス テ ム か ら デ ー タ リ ク エ ス ト を 受 信 し 、 そ の 後 、 リクエストされたことに基づいて、高速度でデータをアクセスする。 D M D 100が指定さ れたアプリケーションを実行するためのスレーブデータ操作装置として配備されるとき、 これはSCSI / ファイバインターフェースチャンネル制 御装置140を介して、マスター サーバとインターフェースすることができ、マスターサーバは例えば D M D 100に記憶さ れているデータ中で大量の問い合わせ検索を行うためにDMD100を呼び出すことができ る。

[0007]

DMD100では、チャンネル制御装置140はSCSIまたはファイバチャンネル或いはデータバスへのその他のインターフェースにアクセスするための共通の駆動装置を提供できる。即ち、DMD100の各構成は同一の駆動装置を使用していずれかの任意の共通のインターフェース制御装置を配備できる。制御装置の配備は、配備されたDMDプロダクトが使用される位置および態様にしたがって決定されることができる。

[0008]

共通の駆動装置はUltra320にしたがうことのできるSCSIインターフェースをサポートすることができ、Fat SCSI、Ultra SCSI、Ultra2 SCSI、Ultra160 SCSIとは後方の適合性を有する。16ビットの並列のSCSIバスは毎秒160メガの転送を行うことができ、これは320Mバイト/秒の同期データ転送レートを生成することができる。共通の駆動装置はまた二重の2Gビットファイバチャンネル(FC)インターフェースをサポートすることができ、1GビットのFCとの後方の適合性を提供する。DMD100はまた商用の回線インターフェース(CLI)用のRS-232インターフェース(図1には示されていない)を提供することができる。【0009】

チャンネル制御装置により受信されるデータリクエストはメモリ制御装置110に導かれ、メモリ制御装置110はその後、データリクエストを処理する。データリクエストは読取 リクエストまたは書込みリクエストを含むことができ、これは例えば新しいデータのピー スを書込むか、既存のデータのピースを更新することを含んでいる。データリクエストが受信されるときのシステム状態にしたがって、メモリ制御装置110は、適切な記憶装置からのデータリクエストを実行できる。例えば、メモリ制御装置110は、メモリ120から、バックアップ記憶装置130から、又はその両者からリクエストされたデータアクセスを直接実行することができる。

#### [ 0 0 1 0 ]

データリクエストが終了されるとき、DMD100は、チャンネル制御装置140を通って、応答を、基本をなすリクエストしたホストシステムへ返送する。応答には、リクエストまたは書込み確認に基づいてDMD100から読取られたデータのピースを含むことができ、この応答はDMD100に書込まれるようにリクエストされたデータが、リクエストされたように書込まれたことを示す。読取リクエストに対する応答はまた、読取動作が成功したことを示す類似の確認を含むことができる。

#### [0011]

DMD100は異なる目的で配備されることができる。例えば、これは標準的な低プロフィールの3.5 "高密度ディスク(HDD)をエミュレートするために使用されることができる。この場合、これはSCSI/ファイババスを介して、このような標準的な装置としてそれ自体を外界に対して識別でき、それによって外界からの相互動作するパーティがDMD100と相互動作するための適切な標準及び広く利用可能な装置または駆動装置を呼び出すことができる。DMD100はその後、装置が固体ディスク(SSD)として使用されることを可能にするため、固体メモリ120を使用することができる。

#### [0012]

メモリ制御装置110はメモリ120で実行される動作を制御する。通常の状態下では、ホストシステムからのデータリクエストはメモリ120に関して実行される。メモリロードがまだ終了されていないときのようなある状態では、データアクセス動作はメモリ120以外のどこかから実行される必要がある可能性がある。例えばDMD100が回復システム状態にあるとき、読取リクエストは一時的にバックアップ記憶装置130から実行されることができる。この場合、パワーPC(210)を通して、メモリ制御装置110はまたバックアップ記憶装置130で実行されるデータ動作を制御できる。メモリ制御装置110に関する詳細を図2及び3を参照して説明する。

# [0013]

バッテリ170と関連してバックアップ記憶装置130は自蔵されたおよび非揮発性バックアップ記憶装置をDMD100に提供する。このような記憶プロセスは、例えば、DMD100への電力が低いか中断しているとき、メモリ120に記憶されているデータをバックアップするために使用されることができる。バックアップ記憶装置130はまた診断手順の期間中に得られた診断情報の記憶または記録に使用されることができ、それによってこのような記録された診断情報は、これが例えばシステムの問題を決定するために必要とされるときオフラインで検索またはアクセスされることができる。このような記憶スペースはまたメモリロードがまだ終了していないときに転移メモリスペースとしても使用されることができる。この特徴に関する詳細を図4及び8を参照して説明する。

# [0014]

DMD100中のバッテリシステム170はDMD100に対してオフライン電力を提供する。 バッテリシステムは、パワーが不変的に低いか遮断されているとき、メモリからバックアップ記憶装置130へのデータのバックアップを容易にするために重要である可能性がある。バッテリシステムに関する詳細を図5を参照して説明する。

# [0015]

メモリ120は 1 以上のメモリボード上に組織化された複数のメモリバンクを具備することができる。各メモリバンクは固定したメモリ容量およびダイナミックランダムアクセス(DRAM)を提供できる。異なるメモリバンクはコヒーレントな方法でアドレスされることができる。メモリ120はまた複数の論理装置番号(LUN)構造に組織され、それぞれのこのような構造は可変のブロックサイズをサポートできる。メモリ割当ては種々の規

20

10

30

40

準にしたがってメモリ制御装置110により実行されることができる。メモリ組織に関する 詳細を図 5 および 7 を参照して説明する。

#### [0016]

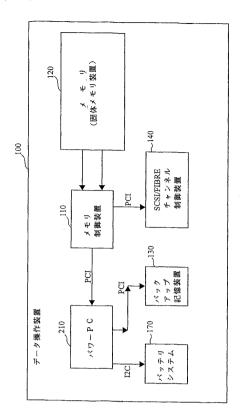

図 2 は本発明の 1 実施形態によるメモリ制御装置110の高レベルの機能プロック図を示している。メモリ制御装置110はプロセッサ210、 P C I X バスインターフェース(I / F)250、エラー補正回路(E C C)270を有する D R A M 制御装置260、 D R A M コネクタ280を備えている。プロセッサ210は市販の汎用目的の低電力中央処理装置(C P U)を使用して実現されることができる。例えば I B M 社の 4 0 0 M H z の 3 2 ビットパワー P C405GPrマイクロ制御装置がプロセッサ210として使用されることができ、これは 4 0 0 M H z のクロックレートで 6 0 0 M I P S が可能な実時間クロック240を有する。 3 2 ビットパワー P C405GPrマイクロ制御装置(プロセッサ210)はプロセッサローカルバス上に単一の装置を有し、これはある量(例えば 3 2 M B)の S D R A M (220)に 3 2 ビットのバス幅を提供する。プロセッサ210はまたローカルバス上にその固有のブートフラッシュ装置(230)を有し、これはある量(例えば 3 2 M B)の非揮発性フラッシュメモリに16ビットのバス幅を提供する。実時間クロックは、タイムスタンプエラーログ、バッテリ充電のための長い間隔のタイミング、電力損失濾波等のような異なる目的のために設けられることができる。

# [0017]

PCIXバスI / F250はPCIXバスの転送レートおよびバースト長を、メモリ120に必要な転送レートおよびバースト長(例えば二重のデータレート同期ダイナミックランダムアクセス(DDR SDRAM))に適合するために使用されることができる。DRAM制御装置260はメモリアクセスに関する種々の機能を行うことができる。例えば、ECC回路270を通して、単一ビットエラー補正および二重ビットエラー検出を行い、メモリ120からの64ビットデータにわたって8ビットECCをサポートできる。DRAM制御装置260はメモリエラーを検出したときはいつでもプロセッサ210に対して中断信号を生成することもできる。さらに、リフレッシュサイクルおよびリフレッシュサイクルタイミングを提供することもできる。1実施形態では、DRAM制御装置はまた、メモリモードを制御するために信号をメモリバンクに送信することによって、プロセッサ210により制御される電力節約戦略を実行することができる。これについては図3を参照して詳細に説明する。DRAMコネクタ280はメモリ制御装置110とメモリ120との間の物理的な接続を行う

# [0018]

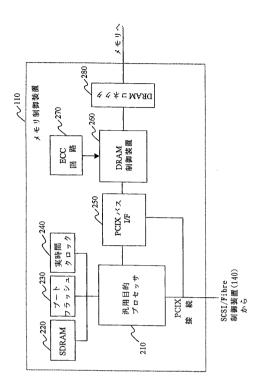

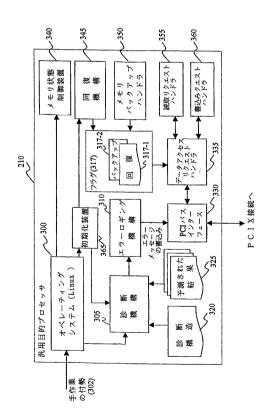

図3は本発明の1実施形態によるプロセッサ210の高レベルの機能ブロック図を示している。プロセッサ210は、そこにインストールされて稼動するオペレーティングシステム300と、初期化装置365と、PCIXバスインターフェース330と、データアクセスリクエストハンドラ335と、メモリ状態制御装置340と、回復機構345と、メモリバックアップハンドラ350と、読取リクエストハンドラ355と、書込みリクエストハンドラ360とを使用する。プロセッサ210は種々の診断ルーチンを実行する診断機構305と、エラーメッセージをバックアップ記憶装置130に書込むためのエラー記録機構310も含むことができる。

# [0019]

オペレーティングシステム300はLinux(登録商標)のような市販の製品であってもよい。システムのスタートップ(またはリセット)時に、オペレーティングシステム300はバックアップ記憶装置130からロードされることができる。ブート時に、オペレーティングシステム300は種々の初期化を実行するために初期化装置365を呼び出すことができる。初期化装置365はメモリアレイ、バックアップ記憶装置、SCSI/ファイバ/他のインターフェースシステムの初期化を行うことができる。これらの装置のブート画像は初期化期間中にそれぞれの装置にダウンロードされることができる。初期化された装置が適切に機能していることを確実にするために、初期化装置365はある診断ルーチンを実行するために診断機構305を呼び出すことができる。

# [0020]

50

40

20

30

40

50

診断機構305は、幾つかの予め定められた診断構造(320)にしたがって診断ルーチンを実行できる。このような構造はアプリケーションの要求を満たすためにダイナミックに改訂されることができる。 DMD100にコンポーネントが付加されるか、そこから除去されるとき、診断構造はそれに従って変更される必要がある。例えば、さらに多くのメモリボードが付加されるならば、診断の構造は付加的な装置を反映することができる。

#### [0021]

診断機構305が診断ルーチンを実行するとき、試験されるように構成された装置に信号を送り、その後、試験されたコンポーネントからの応答を幾つかの予想された結果325と比較する。測定された結果が予想された結果と異なるならば、エラーメッセージが発生されることができ、エラー記録機構310は診断情報をバックアップ記憶装置130中に記録するために呼び出されることができる。幾つかの実施形態では、診断機構305はオペレーティングシステム300のシェルを介して手作業の付勢(302)によって呼び出されることもできる。

# [0022]

診断が適切に終了されたならば、初期化装置365は種々の駆動装置からの信号を受信するために登録でき、バックアップ記録装置130からメモリ120へのデータのコピーを含めた復旧動作を行うために回復機構345を呼び出すことができる。復旧動作が終了されるとき、初期化装置365はその後、システム状態をデータアクセス動作に適切な状態に変化できる。

# [0023]

DMD100のシステム状態は複数のフラグ315を通して表明されることができる。例えば初期化装置365がシステム状態を回復へ変更するとき、システムがデータを復旧しているか、またはメモリロードが実行されていることを示す"回復"フラグ315-1を設定することができる。回復機構345がメモリの負荷(ロード)を終了するとき、メモリロードが終了されたことを示す同じフラグ315-1をリセットすることができる。同様に、システムがバックアップ動作を実行しているならば(例えばメモリ120からバックアップ記憶装置130へデータを移動するならば)、"バックアップ"フラグが設定されることができる。異なるシステム状態はデータが現在記憶されている場所を示すことができる。それ故、システム状態に応じて、データリクエストは異なって処理されることができる。

### [0024]

PCIXバスインターフェース330は制御装置140、バックアップ記憶装置130、およびメモリアレイ120と通信するために使用される。制御装置140がホストシステムからメモリ制御装置110へデータリクエストを転送するとき、そのデータリクエストはPCIX接続を介して制御装置140と、プロセッサ210のPCIXバスインターフェース330との間で通信される。

# [0025]

データリクエストを受信するとき、PCIXバスインターフェース330はデータリクエストをデータアクセスリクエストハンドラ335へ送信する。データアクセスリクエストハンドラ335など信する。データアクセスリクエストハンドラ335など信する。データアクセスリクエストハンドラ355を付勢し、リクエストが書込みリクエストであるならば、書込みリクエストハンドラ360を付勢する。システム状態にしたがって、読取及び書込みリクエストハンドラ355、360は異なった動作を行うことができる。例えばデータ読取リクエストが回復動作(メモリロード)が終了される前に受信されるならば、読取リクエストハンドラ355は、読取命令をメモリ120へ送る代わりに、バックアップ記憶装置130へ導くことができる。データ書込みリクエストがメモリロードが終了される前に受信されるならば、書込みリクエストハンドラ360は、書込み命令をメモリ120とバックアップ記憶装置130の両者へ送り、その後、バックアップ記憶装置130からのみ確認を受信する。

#### [0026]

メモリバックアップハンドラ350はメモリのバックアップ動作を実行する。このハンドラは、持続的な電力損失が検出されるとき、或いはバッテリの電力があるレベルまで低下

20

30

40

50

したときのような、あるシナリオにおいて付勢される。これが付勢されるとき、システム状態がバックアップシステム状態に転移することを示す"バックアップ"フラグを設定することができる。このシステム状態下で、DMD100はホストシステムから受信されたデータリクエストを拒否することができる。このシステム状態は、例えば定常の電力が戻ったことが検出されるまで変化できない。

#### [ 0 0 2 7 ]

メモリ状態制御装置340はメモリバンクの電力節約方式を実行できる。本発明の1実施形態では、電力消費およびしたがって熱発生を減少させるために、DMD100は電力節約方式を使用し、その方式では、異なるメモリバンクが異なるモードに置かれ、そのううのいくつかは低い電力消費をもたらす。電力節約方式の構成はシステム状態に応じている。幾つかの実施形態では、システムが"標準"または"回復"モードであるとき、プロセックを"休眠"または"パワーダウン"モードにする。DDR SDRAMメモリバンクを除く全てのメモリバンクを"休眠"または"パワーダウン"モードにする。DDR SDRAMメモリにより、ウェイクアップ時間は(SDR SDRAMの30マイクロ秒と比較して)の調であることができる。このような非常に短いウェイクアップ時間はさらに高速度の記憶アクセスを容易にする。"休眠"モードにあるとき、インアクチブなメモリバンクロであることができる。電力節約方式はまた、標準的なサイズのDDRチップにも適用される。この特別なDDRメモリチップは、ダイが物理的に単ーフォームファクタ内に位置されているが、各ダイが単ーチップとしてアドレスされることを可能にする方法で、多数のメモリダイのスタックにより開発される。

### [0028]

システムが"バックアップ"モードであるとき、プロセッサ210はさらに、インアクチブなメモリバンクへのクロッキングの送信を停止し、インアクチブなメモリバンクを"自己リフレッシュ"動作モードにすることによって電力消費を減少できる。"自己リフレッシュ"モードを出るために長い時間(約20マイクロ秒)がかかるが、このような長いウェイクアップ時間はバックアップ状態では許容可能である。

# [0029]

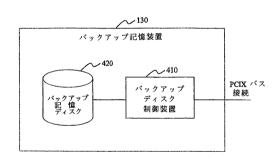

図4は、本発明の1実施形態によるバックアップ記憶装置130の機能ブロック図を示している。バックアップ記憶装置130はバックアップ記憶ディスク420およびバックアップディスク制御装置410を含んでいる。制御装置410はPCIXバスに接続され、ディスク420との間のデータの記憶およびアクセスの制御を行う。ディスクは回転ディスクまたは高密度ディスク(HDD)として構成されることができる。ディスクの容量はアプリケーションの要求にしたがって決定されることができる。バックアップ記憶装置130はバックアップ目的だけではなく、メモリロードがまだ終了されていないときのメモリとして、記録診断情報またはエラーメッセージ、或いはDDR120メモリに書込まれるミラーデータとして使用されるような他の目的でも使用されることができる。

# [0030]

通常のシステムでは、典型的な回復期間は単位ギガバイト当り1乃至2分間の範囲である。回復期間中、システムは典型的に、任意のデータリクエストに応答することはできない。これは遅延を生じる。本発明の幾つかの実施形態では、バックアップ記憶装置130はメモリのロードが終了される前にメモリとして使用されるので、それは遅延を除去する。さらに、1実施形態では、DMD100はその固有のSDRAMを有するLinuxオペレーティングシステム下で動作しており、これはさらにこの動作速度を改良する。例えばメモリの12ギガバイトでは、動作を終了するために約5分間かかる可能性がある。メモリのロードの終了前に、メモリとしてバックアップ記憶装置130を使用することに関する詳細を図8、15、19を参照して説明する。

#### [0031]

バックアップ記憶装置130はまた、故障の場合のエラーメッセージ、診断ルーチンが実 行されるときに得られる診断情報をログするために使用されることもできる。システムの

20

30

40

50

故障の場合、バックアップ記憶装置130中にログされているエラー情報は故障の原因を評価するために除去されることができる。

### [0032]

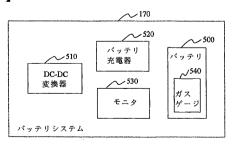

図 5 は、本発明の 1 実施形態によるバッテリシステム 150の機能ブロック図を示している。バッテリシステム 150は組込みのガスゲージ 540、 D C - D C 変換器 510、モニタ 530、バッテリ充電器 520を具備している。モニタ 530はガスゲージ 540を通して、バッテリ 500の状態を観察する。監視結果は、システム状態が変更されるのを必要とするか否かの決定に使用されることができる。例えばバッテリ電力が持続的に低下し、ある低いしきい値に到達すると、システム状態は"正常"状態から"バックアップ"状態へ変更されうことができる。

# [0033]

バッテリ500は7.2vのようなある電圧を出力できる。バッテリ充電器520はこれが必要とされるとき、バッテリの再充電を行う。DC-DC変換器510は例えば7.2vのバッテリ出力電圧または12vのSCSI電力を、システムで必要とされる異なる電圧に変換する。例えばDC-DC変換器510は7.2vまたは12vの入力電圧を採取して、1.2v、1.25v、1.8v、2.5v、3.0vまたは3.3vに変換できる。

#### [ 0 0 3 4 ]

本発明の幾つかの実施形態では、バッテリシステム150はメモリ制御装置110中の汎用目的のプロセッサ210により制御されることができる。監視方式はバッテリの寿命を延長させる目的で、汎用目的のプロセッサ210の制御下で、実行されることができる。この方式下では、モニタ530はバッテリ500の電力レベルを監視する。観察された電力レベルは汎用目的のプロセッサ210へ送信される。電力レベルがあるレベル(例えばフルパワー)に到達するとき、汎用目的のプロセッサ210は電力がある低いレベル(例えば90%)に低下するまで、充電を停止できる。これによって、これが既に(バッテリ寿命を短くすることで知られる)フルパワーレベルであるとき、バッテリの連続的な充電が阻止される。さらに、監視された電力レベルが低いしきい値に到達するとき、汎用目的のプロセッサ210は装置の運転を自動的に停止させることができる。

#### [0035]

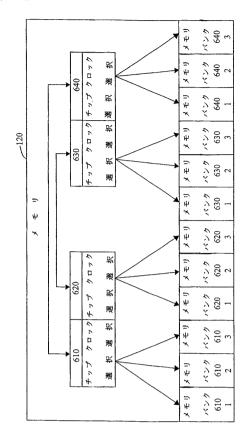

図 6 は、本発明の 1 実施形態によるメモリ120の例示的な組織を示している。メモリ120は 1 以上のメモリボードを備えることができる。各メモリボードは複数のメモリバンクを含むことができる。例えば 1 つのメモリボードはメモリバンク610-1、610-2、610-3、620-1、620-2、620-3を含むことができる。別のメモリボードはメモリバンク630-1、630-2、630-3、640-1、640-2、640-3を含むことができる。

# [0036]

各メモリボードはまた複数のレジスタおよび、位相ロックループ(PLL)クロックのようなクロックを含むことができる。したがって、1つのメモリボードはクロッキングを各メモリバンク610-1、610-2、610-3、620-1、620-2、620-3へ提供するためにチップ選択/クロック選択装置610と620を含んでいる。他のメモリボードはクロッキングを各メモリバンク630-1、630-2、630-3、640-1、640-2、640-3へ提供するためにチップ選択/クロック選択装置630と640を含んでいる。

# [ 0 0 3 7 ]

メモリ120は複数のLUN構造に論理的に組織化されることもできる。DMD100は、可変のブロックサイズを処理できる多数のLUN構造をサポートできる。異なるLUN構造は異なるブロックサイズを促すことができる。さらに、各LUN構造は異なるブロックサイズをサポートすることができる。このような能力によって、DMD100はそれぞれあるブロックサイズを備えている多数の記憶装置を有するように見えることができる。これによってDMD100は異なるブロックサイズを必要とするホストシステムとインターフェースすることが可能である。

# [0038]

可変のブロックサイズがサポートされるとき、必要とされるブロックサイズを有するホ

30

40

50

ストシステムからのデータリクエストは、最初に、一致するプロックサイズを有するLUN構造にマップされることができる。図7は本発明の1実施形態による種々のフラグ315および多数のLUN構造700に関するデータアクセスリクエストハンドラ335の高レベルの機能ブロック図を示している。前述したように、データリクエストは(例えばメモリ120から、バックアップ記憶装置から、又はその両者から)の異なる内部記憶媒体中で処理されることができ、システム状態に基づいて決定が行われることができる。さらに、データリクエストが処理される場所に応じて、適切なLUN構造がしたがって識別されることができる。

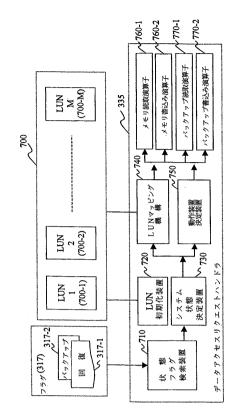

# [0039]

図 7 に示されている例示的な実施形態では、メモリは例えば M 個のLUN構造、即ちLUN1 700-1,LUN2 700-2, ...,LUNM 700-Mに組織化される。データアクセスリクエストハンドラ335は、システムフラグ検索装置710、LUN初期化装置720、システム状態決定装置730、LUNマッピング機構740、動作装置決定装置750、種々のデータアクセス演算子を具備し、種々のデータアクセス演算子は例えばメモリ読取演算子760-1、メモリ書込み演算子760-2、バックアップ記憶読取演算子770-1、バックアップ記憶書込み演算子770-2を含んでいる。

# [0040]

LUN初期化装置720は多数のLUN構造700を初期化することができる。例えば、システムが最初にセットアップされるとき、全てのLUN構造は統一したまたは標準的なブロックサイズ(例えば512バイト)で設定されることができ、この初期ブロックサイズは異なるブロックサイズ値を有するデータリクエストを満足するために後に変更されることができる。例えば、幾つかのシステム(例えばUnisys製品)は180バイトのブロックサイズで動作することができ、幾つか(例えばTandem製品)は514バイトのブロックサイズで動作することができる。

# [0041]

データリクエストを受信するとき、データアクセスリクエストハンドラ335は最初に、システムフラグ検索装置710を介して、フラグ315にアクセスすることができ、これはシステムの動作状態を示している。システムフラグ検索装置710はその後、現在のシステム状態を識別するために、検索されたフラグ値をシステム状態決定装置730へ転送することができる。決定されたシステム状態に基づいて、動作装置決定装置750は、読取 / 書込み動作がどこの装置(例えばメモリ120またはバックアップ記憶装置130、或いはその両者)から / どこの装置へ行われるかを決定することができる。例えば、システムフラグが標準のシステム状態を示すとき、動作装置決定装置750は動作装置としてメモリ120を選択する可能性があり、即ち読取リクエストのいずれかまたは書込みリクエストであるデータリクエストはメモリ120から処理される。

# [0042]

メモリのロードがまだ終了されていないことを示すシステムフラグ "回復"が出されるとき、オペレーティングシステム決定装置750は読取及び書込みリクエストを異なって処理するように選択することができる。例えば、読取られるデータが依然としてバックアップ記憶装置130にある可能性があるので、読取リクエストはバックアップ記憶装置130から実行されることができる。書込みリクエストに関しては、システムは、データの統合性を確実にするために、同一のデータをメモリ120とバックアップ記憶装置130の両者に書込むことができる。システム状態決定装置730により決定されるシステム状態は、データリクエストを特定のLUN構造へマップするために、LUNマッピング機構740により使用されることもできる。

# [0043]

読取 / 書込み動作がどこから / どこへ実行されるかに関する決定に基づいて、動作装置 決定装置750は適切なデータリクエスト演算子を呼び出すことができる。例えば、データ 読取 / 書込みリクエストがメモリ120から処理されるとき、メモリ読取 / 書込み演算子760 -1 / 760-2が付勢されることができる。データ読取 / 書込みリクエストがバックアップ記

20

30

40

50

憶装置130から処理されるとき、そのバックアップ読取 / 書込み演算子770-1 / 770-2が付勢されることができる。

### [0044]

さらに、LUNマッピングの結果にしたがって、LUNマッピング機構740はまた、関連情報を、呼出された演算子へ供給することができる。例えば、LUNマッピング機構740は、マップされたLUN構造に関する情報を、付勢された演算子に転送することができる。

# [0045]

付勢された演算子が幾つかのデータ動作命令を適切な装置へ送信し、データ動作が終了された後、その装置から応答を受信することができる。このような応答には、(例えば応夕が読み取られるとき)データのピース、確認(例えば書込みの確認)、またはの応答には、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、できる。に、ないできる。に、ないできる。に、ないできる。に、ないできる。に、ないできる。に、ないできる。に、ないでするならば、リクエストしているホストシスに、または確認メッセージなしに、動作装置からに、リクエストしているホストシスに、または確認メッセージなしに、動作装置からに、リクエストしているホストシスに、または確認メッセージなしに、動作表面に、リクエストしているホストシスに、ただータ及び確認は、それらが存在するならば、リクエストしているホストシスに、をに、またはできる。に、できる。に、できる。には、このできる。に、できる。ことができる。には、このできる。には、このできる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。ことができる。このできる。ことができる。ことができる。このできる。このできる。ことができる。ことができる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる。このできる

# [0046]

書込み動作が呼び出されるとき、動作がメモリ120のみから(例えば正常のシステム状態において)、またはメモリ120とバックアップ記憶装置130の両者から(例えば回復システム状態において)処理されるかに応じて、書込み演算子は異なる動作をすることができる。正常のシステム状態ではメモリ書込み演算子760-2が書込み動作のために呼出される。メモリ書込み演算子760-2は最初に、書込まれるデータと共に書込み命令を送信し、その後、メモリ120から確認またはエラーメッセージを受信するのを待機する。応答を受信すると、メモリ書込み演算子760-2は、受信された情報をPCIXバスインターフェース330へ転送する。

# [0047]

(以下の図 8 を参照して説明する)幾つかの他のシステム状態では、書込み動作はメモリ120とバックアップ記憶装置130との両者で行われる。この場合、メモリ書込み演算子76 0-2とバックアップ書込み演算子770-2の両者が呼び出される。両方の書込み演算子は、書込み命令(例えば書込む場所)と共に、書込まれるデータをそれらのそれぞれの動作装置(即ち、メモリ120とバックアップ記憶装置130)へ送信する。メモリ120はバックアップ記憶装置130よりも非常に高速度で動作できるので、バックアップ書込み演算子770-2だけがバックアップ記憶装置130から受信された書込み確認またはエラーメッセージをPCIXバスインターフェース330へ転送するように構成されることができるが、メモリ書込み演算子760-2もメモリ120からこのような情報を受信できる。

#### [0048]

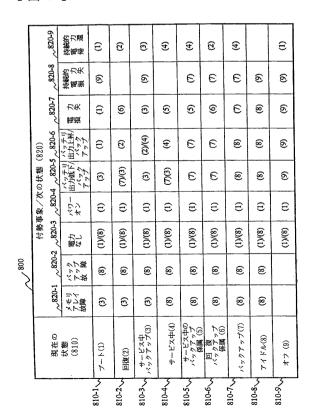

図8は、本発明の1実施形態による、DMD100における異なる動作条件下の種々の例示的なシステム状態および転移を示している。状態転移表800は行及び列を含んでいる。行は現在のシステム状態810に対応し、列は現在の状態が異なる状態に転移するか同じシステム状態のままである事象または状態820に対応している。現在のシステム状態が行により表され、事象/状態が基本をなす列により表されるとすると、特定の行及び特定の列に対応する表800の各エントリは、次のシステム状態を表す。

#### [0049]

表800では、(1)と符号を付されたブート状態810-1、(2)と符号を付された回復状

20

30

40

50

態 810-2、(3)と符号を付されたサービス中のバックアップ状態 810-3、(4)と符号を付されたサービス中の状態 810-4、(5)と符号を付されたサービス中のバックアップ係属状態 810-6、(7)と符号を付された回復バックアップ係属状態 810-6、(7)と符号を付されたバックアップ状態 810-7、(8)と符号を付されたアイドル状態 810-8、(9)と符号を付されたオフ状態 810-9を含む 9つの例示的なシステム状態が存在する。メモリアレイ故障 820-1、バックアップ故障 820-2、電力なし 820-3、電力オン 820-4、バッテリ出力低下 / バックアップ 820-5、バッテリ出力上昇 / バックアップ 820-6、電力損失 820-7、持続的電力損失 820-8、持続的電力帰還 820-9を含む、システム状態の転移をトリガーできる種々の事象 / 状態が存在する。

#### [0050]

各システム状態は特定のシステム動作状態を示している。例えば、ブート状態(1)は DMD100が例えば電力オン、リセットによって、または幾つかのソフトウェア手段を介して、トリガーされるブートプロセスを受けていることを示す。回復状態(2)は DMD100が、バックアップ記憶装置からメモリヘデータを回復しているか、または単にメモリをロードしていることを示している。サービス中バックアップ状態(3)はメモリ120が(例えばメモリ故障、バックアップ用のバッテリが不十分であるため)適切に機能しておらず、データリクエストがバックアップ記憶装置からサービスされていることを示している。サービス中状態(4)は DMD100が正常の状態下で動作していることを示している。即ち全てのデータリクエストはメモリ120から処理される。

# [0051]

サービス中のバックアップ係属状態(5)はデータリクエストがサービスされているが係属バックアップを有する状態を示すことができる。即ちデータリクエストは依然として、メモリ120から処理されているが、監視され、近い将来にバックアップ手順をトリガーする可能性がある幾つかの状態(例えば電力の低下)が存在する。回復バックアップ係属状態(6)は、システムがメモリのロードを行っており(バックアップ記憶装置からメモリヘデータを回復しており)、状態が持続的に悪いならば(例えば持続的な電力損失)、幾つかの既存の状態/事象(例えば電力の損失が)が近い将来にバックアップ手順をトリガーする可能性があることを示している。バックアップ状態(7)は単に、メモリ120からバックアップ記憶装置130ヘデータを移動することにより、バックアップ手順を実行していることを示している。アイドル状態(8)は、システムが現在アイドルであり、何等のデータリクエストも受取っていないことを示している。オフ状態(9)はDMD100が現在オフであることを示している。

#### [0052]

各システム状態は、データリクエストを処理する方法に関して、DMD100に異なる動作をさせることができる。例えば、システム状態中のサービス中状態(4)およびサービス中のバックアップ係属状態(5)では、データリクエストは常にメモリ120からサービスされる。システム状態中の回復状態(2)、サービス中のバックアップ状態(3)、回復バックアップ係属状態(6)では、データリクエストはリクエストの性質および、リクエストされたデータの位置にしたがって、メモリ120、またはバックアップ記憶装置130、或いは両者からサービスされることができる。システム状態中のブート状態(1)、バックアップ状態(7)、アイドル状態(8)、オフ状態(9)では、データリクエストはサービスされない。

# [ 0 0 5 3 ]

システム状態は、ある状態 / トリガー事象下で変化する。固定された現在の状態では、DMD100は、異なる事象が生じるとき、異なるシステム状態に転移できる。例えば、ブート状態 (1) では、メモリの故障 (820-1) が生じるならば、システム状態はブート状態 (1) からサービス中のバックアップ状態 (3) に転移する。即ち、全てのデータリクエストは、メモリアレイの故障のために、バックアップ記憶装置 130から処理される。ブート期間中にバックアップ記憶装置 130の故障 (820-2) が生じるならば、ブートプロセスはバックアップ記憶装置 130なしでは、さらに動作することができないので、システム状

態はブート状態(1)からアイドル状態(8)へ転移できる。現在のシステム状態が正常(サービス中状態(4))であり、電力損失(820-7)が検出されたならば、システム状態はサービス中のバックアップ係属状態(5)へ転移できる。この状態では、システムは依然としてサービス中であるが、可能な係属バックアップが存在する。この状態では、電力損失が持続している(820-8)ならば、システム状態はさらにバックアップ状態(7)に転移する。空欄のエントリを有しているあるセルが表800に存在しており、これは現在の状態では、列により表されている基本をなす事象が適用されないことを示している。例えば、システムがオフ状態であるとき、メモリアレイの故障820-1およびバックアップ記憶装置の故障820-2のような、ある事象はシステム状態に影響しない。

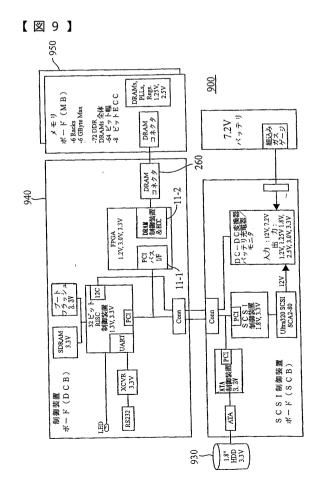

#### [0054]

図 9 は、本発明の 1 実施形態による D M D 100の異なるコンポーネントの例示的な組織的配置 900を示している。例示的な組織的配置 900は S C S I / ファイバ制御装置ボード ( S C B ) 910、 D R A M 制御装置ボード ( D C B ) 940、メモリボード ( M B ) 950、バックアップ記憶スペースを提供する高密度ディスク 930、バッテリ 920を含む 5 つの別々の物理的部分を含んでいる。

#### [0055]

前述した同じ論理組織の幾つかのコンポーネントは異なるボード上でグループ化されることができる。例えば、バックアップ記憶ディスク制御装置410は、取付け(ATA)制御装置(7)を使用して実現されることができ、図9に示されている例示的な配置では、これは(例えば((9)として符号を付されている)東芝1.8 " 20GBの高密度ディスクを使用して構成される)バックアップ記憶ディスク930から物理的に別々に配置されることができる。同様に、DC-DCコンバータ510(図5参照)、バッテリ充電器520、及びモニタ530は、バッテリ500およびガスゲージ540とは分離されてSCB910上に配置されてもよい。サイズ、熱消費、コンポーネントが容易に置換されることができる位置に配置される必要があるか否かのような、論理的または機能的な組織化の考察以外の要因に基づいて、例示的な配置が行われることができる。その代わりに、またはそれに加えて、物理的な組織的配置は、システム全体のコンパクトさに関する考察に基づいて設計されることができる。

# [0056]

SCSI / ファイバ制御装置ボード(SCB)910はATA制御装置チップ7と、SCSI / ファイバ制御装置チップ6と、電力管理装置および変換器チップ3とを含んでおり、電力管理装置および変換器チップ3はDC-DC変換器、バッテリ充電器、モニタを含んでいる。DRAM制御装置(DCB)940は、汎用目的のプロセッサチップ(例えば32ビットの405GPr)12、SDRAMチップ16、ブートフラッシュメモリ17、実時間クロック18、フィールドプログラム可能なゲートアレイ(FPGA)チップ11を含んでおり、このフィールドプログラム可能なゲートアレイ(FPGA)チップ11はPCIXバスI / F11-1およびECC回路11-2を有するDRAM制御装置の両者としてプログラムされている(図2を参照して説明)。

# [0057]

各ボードはまた、異なるボード及びコンポーネント間での接続を容易にするための、ある異なる部分を含むことができる。例えばSCB910は、ATA制御装置チップ7とバックアップディスク9との間の接続を容易にするATAコネクタ8と、SCB910とDCB940との間のPCIX接続を容易にするPCIXコネクタ10と、SCSI/ファイバ制御装置とSCSI/ファイババックプレーン(1)との間の物理的な接続を行うSCSI/ファイバコネクタ2と、SCB910をバッテリ5へ接続するバッテリコネクタ4とを含んでいる。同様に、DCB940は、SCB910上のPCIXコネクタへの接続を容易にする対応するPCIXコネクタ10と、DRAM制御装置11-2とメモリボード950との間の接続を行うDRAMコネクタ19と、外部とDMD100との間に直列接続点を設けるRS232コネクタと、システム状態およびアクティビティを示す手段を与えるLED灯14と、外部からシステムをリセットする要求を満たすリセットボタン15とを含んでいる。

10

20

30

### [0058]

1 実施形態にしたがって、FPGA11はPCIXコネクタ10に直接接続されている。これによって、DMD100は汎用目的のプロセッサ12を通らずに高速度の記憶アクセスを実現するためにその搭載FPGAを通してデータ転送を行うことが可能である。さらに、PCIXコネクタ10もまたSCSI制御装置6に接続されているので、FPGA11は、汎用目的のプロセッサ12を通らずに、直接、外部ソースとの間でデータを転送することができる。このことにより、記憶装置が高速度でアクセス可能であるだけでなく、共用もされることができる。さらに、汎用目的のプロセッサ12は、商用のオペレーティングシステム(例えばLinux)と共に配備される市販のCPUを使用して構成されることができるので、DMD100は完全なコンピュータであり、これは通常の汎用コンピュータで通常動作する種々のアプリケーションをサポートできる。この場合、アプリケーションは汎用目的のプロセッサ12で動作でき、アプリケーションに必要なデータはプロセッサ12のSDRAMに転送されることができる。

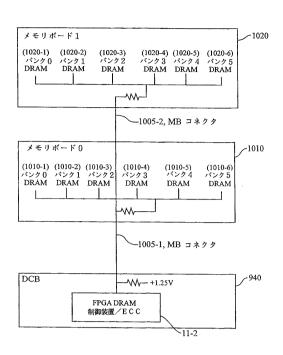

# [ 0 0 5 9 ]

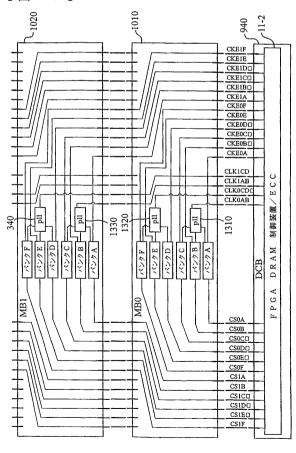

図10乃至13は、本発明の1実施形態によるメモリボードとそれらの内部組織の例示的な配置を示している。1実施形態では、メモリ120は、それぞれ3または6つのメモリバンクを含むことができる1以上のメモリボードを具備することができる。1つのメモリボード内および異なるメモリボード内の異なるメモリバンクは、統一したアドレス及びクロッキングを行うために、ある方法で接続されることができる。図10は2つの例示的なメモリボード、即ちメモリボード0の1010とメモリボード1の1020がDCB940上のDRAM制御装置と接続される態様を示している。メモリボード0の1010は6つのメモリバンク、即ち、バンク0の1010-1、バンク1の1010-2、バンク2の1010-3、バンク3の1010-4、バンク4の1010-5、バンク5の1010-6を有している。6つのバンクは共に連結され、メモリボードコネクタ1005-1を通してDCB940に接続されている。同様に、メモリボード1の1020は6つのメモリバンク、即ち、バンク0の1020-1、バンク1の1020-2、バンク2の1020-3、バンク3の1020-4、バンク4の1020-5、バンク5の1020-6を有している。メモリボード1の1020上の6つのバンクは同様に共に連結され、メモリコネクタ1005-2を介してメモリボード0の1010に接続されることができる。メモリボード1の1020はメモリボード0の1010を通してDCB940に接続されている。

### [0060]

メモリボードコネクタ1005-1と1005-2は異なるタイプの信号通過を可能にする。例えばこれはデータの通過を可能にする。これはまた、アドレス情報の通過を可能にできる。さらに、これは制御信号の通過を可能にする。幾つかの実施形態では、メモリボードコネクタは、64ビットデータ及び8ビットECCと、データストローブと、データマスク信号とを有する72ビットデータバスを含んでいる。これらは類似した方法で経路を設定されることができる。メモリボードコネクタはまたアドレスバスと、制御信号用の付加的なパスも含んでいる。アドレス及び制御信号はレジスタバッファによって各ボードで終端されることができ、このレジスタバッファはボードに特有のクロックによりクロックされることができる。

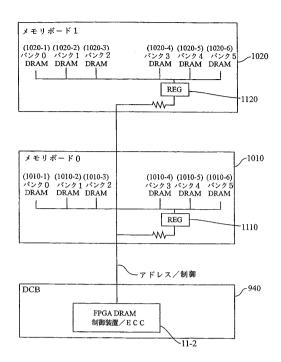

# [0061]

図11は、本発明の1実施形態によるメモリボードのレジスタバッファの例示的な配置を示している。図11では、各メモリボードは1つのレジスタバッファを有する。メモリボード0 1010はレジスタバッファ1110を有し、メモリボード1 1020はレジスタバッファ1120を有する。それぞれ基本を成すメモリボードに指定されたアドレス及び制御信号を受信するために、異なってクロックされることができる。各メモリボードは異なるクロック(CK)、クロックエネーブル(CKE)信号、チップ選択(CS)信号を使用することができる。各メモリバンクは別々のCKEとCS信号を有することができる。各メモリボードは、位相ロックループ(PLL)クロックとして構成されることができる1以上のクロックを有することができる。

# [0062]

50

20

30

30

40

50

図 1 2 は、本発明の 1 実施形態によるメモリボード中の P L L クロックの例示的な配置を示している。この例では、メモリボード1200は 2 つの P L L クロック1210と1220とを有し、それぞれ例えば 3 つのメモリバンクとして動作する。例示的な実施形態では、 P L L クロック1210はクロッキングバンク 3 の1200-4と、バンク 4 の1200-5と、バンク 5 の1200-6との機能を行い、 P L L クロック1220はクロッキングバンク 0 の1200-1と、バンク 1 の1200-2と、バンク 2 の1200-3の機能を行う。

### [0063]

DCB-MB-MBを横切って通過する経路選択信号に適応するために、メモリボードはピンシフトを容易にするように設計されることができる。本発明の1実施形態による2個のメモリボード間の1つの例示的なピンシフト方式が図13に示されている。6個のメモリバンク(A、B、C、D、E、F)を有する2個のメモリボード間で信号を経路選択するために、各メモリボードは各側に28個のピンを有することができる。メモリボード0の1010をDCB940へ接続するために使用される28個のピンの中で、14個のピンがDCB940とメモリボード0の1010との間の信号の経路選択に使用される。

#### [0064]

メモリボード 0 の1010への接続専用である第 1 のセットの 1 4 個のピンの中で、 6 個のピンは、 6 個のメモリバンク(C K E 0 A、 C K E 0 B、 C K E 0 C、 C K E 0 D、 C K E 0 E、 C K E 0 F)のそれぞれの C K E 信号用であり、 6 個のピンは、 6 個のメモリバンク(C S 0 A、 C S 0 B、 C S 0 C、 C S 0 D、 C S 0 E、 C S 0 F)のそれぞれの C S 信号用であり、 2 個のピンは 2 つの P L L クロックをクロッキングするためのものであり、 ここで、 P L L 1310のクロッキング用の C L K 0 A B はバンク A、 B、 C に応答し、 P L L 1320のクロッキング用の C L K 0 C D はバンク D、 E、 F に応答する。 これらのピンは(第 1 の位置として最も右側から開始する)(C K E 0 A - C K E 0 F 用の)位置 7 - 1 2 と、 (C K E A B と C K E 0 C D 用の)位置 1 5 - 1 6 と、 (C S 0 A - C S 0 F 用の)位置 1 7 - 2 2 に位置される。

# [ 0 0 6 5 ]

残りの14個のピンはDCB940とメモリボード1の1020とを接続するためのものである。位置1-6の6個のピンは、メモリボード1の1020上の6個のバンクのクロックエネーブル信号CKE1A-CKE1F用のものであり、位置13-14の2個のピンは(メモリボード1の1020のそれぞれクロッキングバンクA、B、C、D、E、Fに対して応答する)2つのPLLクロック1330と1340のための2つのクロッキング信号CKE1AB-CKE1CD用のものであり、位置23-28の別の6個のピンは、第2のボード1020上の6個のバンクに対応するチップ選択信号CS1A-CS1F用のものである。第2のメモリボード1020に専用の信号は、対応する信号が第1のメモリボード1010へ経路選択される同じピン位置に到達するように、第1のメモリボード1010を通って導かれる。即ち、クロックエネーブル信号CKE1A-CKE1Fは(CKE0A-CKE0Fの位置と同の)位置7-12においてメモリボード1の1020へ経路設定され、クロッキング信号CLK/ABおよびCLK/CDは(CLK0ABおよびCLKCDに対して同一の)位置15-16においてメモリボード1の1020へ経路設定され、チップ選択信号CS1A-CS1Fは(CS0A-CS0Fと同一の)位置17-22においてメモリボード1の1020へ経路設定される。

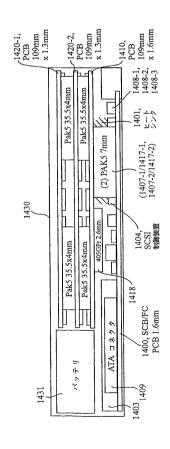

# [0066]

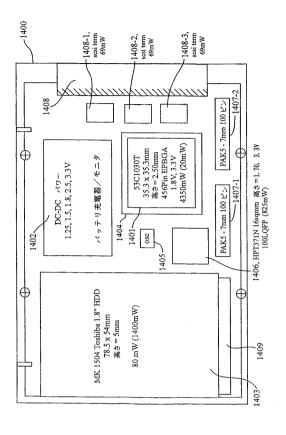

図14aは、本発明の1実施形態によるSCSI制御装置ボードSCB1400の例示的な物理的レイアウトを示している。SCB1400は、456のピンを有する53C1030TのようなSCSI制御装置チップ1404、SCSI制御装置から熱を抽出するために、SCSI制御装置の近く(例えばSCSI制御装置の上部の)に置かれた随意選択的なヒートシンク1401、チップHP1371NのようなATA制御装置1406、東芝1.8″HDDディスクのようなバックアップ記憶ディスク1403、(HDDディスク1403の下の)ATAコネクタ1409、バッテリモニタ及び充電器を有するDC-DC電力変換器1402、ホストシステムがSCSI制御

30

40

50

装置と通信するためのホストSCSIコネクタ1408(またはSCSIバックプレーン)、SCSIバックプレーンをSCSI制御装置へ接続するSCSIコネクタ1408-1、1408-2、1408-3を含んでいるが、それらに限定されない複数のコンポーネントを有している。SCB1400は発振器1405、100個のピン1407-1および1407-2を有する2個のPCIXコネクタPK5も含むことができる。種々のコンポーネントの例示的なサイズ及びそれらの動作電力レベルが図14aに示されている。

### [0067]

図14bは、本発明の1実施形態によるDRAM制御装置ボードまたはDCB1410の例示的な物理的レイアウトを示している。DCB1410は、456個のピンを有する405GPrのような汎用目的のプロセッサチップ1418、SDRAMチップ1411、フラッシュメモリチップ1412、実時間クロックチップ1413、PCIXバスI/FおよびDRAM制御装置としてプログラムされているFPGAチップ1414、RS232インターフェース1415、DRAMコネクタ用の2つのスロット、即ちPAK5-140スロット1416-1およびPAK5-120スロット1416-2、SCB1400へのPCIXコネクタ用の2つのスロット、即ちSCB1400上の対応部1407-1および1407-2に対応するPK5 1417-1および1417-2を物理的に構成している。同様に、DCB1410の異なるコンポーネントに対する例示的なサイズ及びそれらの動作電力レベルも示されている。

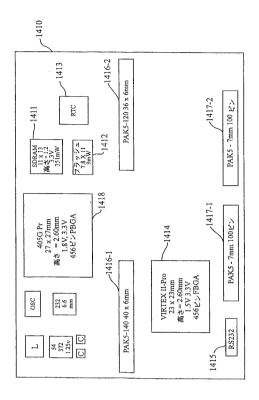

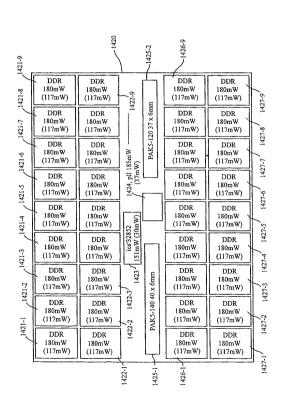

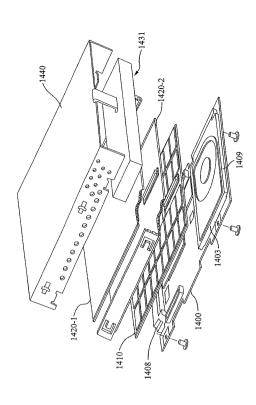

### [0068]

図14cは、本発明の1実施形態によるメモリボード1420上のメモリチップの例示的な物理的レイアウトを示している。この例では、9個のスタック(1421-1,…,1421-9,1422-1,…,1422-9,1426-1,…,1426-9,1427-1,…,1427-9)を有する各行を備えた4個の別々の行(1421、1422、1426、1427)にそれぞれ配置されている3チップの全体で36のメモリスタックが存在している。スタックの4つの行は物理ボードの各側に存在する18のスタックの2つのグループに集合される。2つのグループの間には、2つのPLLクロック1424、レジスタバッファ1423、DRAMコネクタ用の2つのスロット、即ち(DCB1410上の対応するコネクタ1416-1と1416-2に対応する)PAK5-140 1425-1とPAK5-120 1425-2が存在する。各コンポーネントの例示的な物理的サイズおよびそれらの動作電力レベルが示されている。各メモリスタックは、ある数のバイトのメモリ容量を表すことができる。前述したように、DMD100には多数のメモリボードが含まれている。

### [0069]

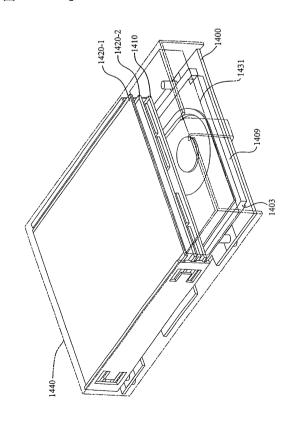

図14dは、本発明の1実施形態によるコンパクトボックス1430中のDMD100の異なるボードの例示的な物理的配置を示している。熱の減少、コンポーネントの置換の容易さ、接続の効率について考慮して、コンパクトな方法で配置されたボード及びコンポーネントの複数の層が存在する。本発明の1実施形態によれば、DMD100の全てのコンポーネントは、任意の装置の任意の駆動ベイ中に配備可能である低プロフィールの3.5 "フォームファクタでパッケージされることができる。上部の2つの層は2つのメモリボード1420-1と1420-2を含んでおり、それぞれ図14cを参照して説明したような、メモリチップ配置を有している。2つのメモリボード1420-1と1420-2は対応するDRAMコネクタ1425-1と1425-2またはPAK5 140とPAK5 120コネクタを介して接続される。メモリボードの下にはDBC1410が存在し、それは上方のメモリボード(1420-2)にそのDRAMコネクタ1416-1と1416-2を介して、メモリボード1420上のそれらの対応部分、即ち1425-1と1425-2(図14c参照)に接続している。

# [0070]

DCB1410の下にはコンパクトボックス1430の底部にSCB1400が位置している。汎用目的のプロセッサチップ405 GPr(1418)はDCB1410の底部に設置されている。内部バックアップディスク1430は、その下にATAコネクタ1409を有するSCB1400の左側に存在する。SCSI制御装置チップ1404は、上部にヒートシンク1401を有するSCB1400の右側に存在する。ホストSCSIコネクタ1408はコンパクトボックス1430の右下に位置されている。SCSIコネクタ1408-1、1408-2、1408-3はホストSCSIコネクタ1408をSCSI制御装置チップ1404へ接続する。SCВ1400は、両ボード上の対応部分(1407-1対

30

40

50

1417-1と1407-2対1417-2)として位置され整列されているPCIXコネクタを介してDCB1410と通信する。PCIXコネクタの2つの対はSCSI制御装置チップ1404とヒートシンク1401の前方に整列されている。ATA制御装置1404はこれらのコネクタの後方にある。

# [0071]

2 つのメモリボード1420-1と1420-2および D C B 1410は S C B 1400よりも狭く、コンパクトボックス1430の右側方向に設置されている。これらの小さいボードの左側にはバッテリ1431が存在し、これは S C B 1400の左上にある。

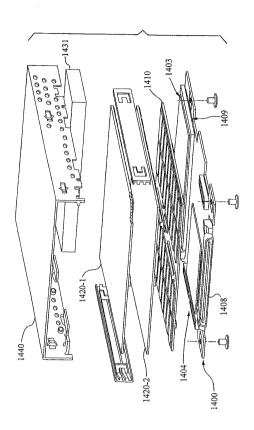

#### [0072]

図14eおよびhは、本発明の1実施形態によるDMD100ボックスの異なる方向から見た構造図を示している。図14eでは、DMDボックス1440は熱の散逸を助けるために分散して設けられた種々の穴を有する。この図では、バッテリ1431は右上にあり、2つのメモリボード1420-1と1420-2およびDCB1410の近くであり、SCB1400上のバックアップ記憶ディスク1403および(バックアップ記憶ディスク1403下の)そのATAコネクタ1409の上方に配置されている。ホストSCSIコネクタ1408はSCB1400上のバックアップ記憶ディスク1403と反対側に存在する。

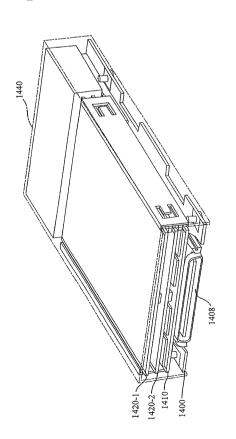

### [0073]

本発明の1実施形態では、DMD100は低プロフィールの3.5 "フォームファクタを有するボックス中に非常にコンパクトな方法でパッケージされている。前述したように、DMD100は十分に完全なコンピュータである。これは低プロフィールの3.5 "フォームファクタを有するコンパクトなパッケージングにより、任意の装置の任意の駆動ベイに配備可能にされ、以下さらに詳細に説明するように、種々のアプリケーションで使用されることができる。

# [ 0 0 7 4 ]

図 1 4 f は、図 1 4 e と比較して、 9 0 度回転されている図を示している。この図では、 S C S I 制御装置チップ1404はホスト S C S I コネクタ1408の近くにあり、 S C S I コネクタ1408-1、1408-2、1408-3(見えない)を介して、ホスト S C S I コネクタ1408に接続されていることが認められる。

# [ 0 0 7 5 ]

図 1 4 g は、図 1 4 f を畳んだ図である。ボードが設置され、コンパクトボックス1430が閉じられるとき、ボックスのバックプレーンから見られるのは、ホストSCSIコネクタ1408であり、それはSCB1400と同じ層に位置され、DCB1410と2つのメモリボード1420-1と1420-2の下にある。

# [0076]

図 1 4 h は、ボードが設置されるときの、コンパクトボックス1430の反対側を示している。バッテリ1431はボックスのエッジにあり、これは 3 つの小さいボードと、メモリボード1420-1と1420-2の近くであり、SCB1400上のバックアップ記憶ディスク1403とそのATAコネクタ1409の上にある。

# [0077]

前述したようにDMD100は低プロフィールの3.5 "フォームファクタのデータプロセッサであり、任意の装置の任意のドライブベイ中に配備可能である。図15の(a)および(b)は標準的な低プロフィールの3.5 "高密度ディスク(HDD)のような高速度ディスク記憶エミュレータとして配備されているDMD100を示している。DMD100を使用することによって、高速度の転送での大容量のデータ記憶のための効率的な手段を提供することができる。図15の(a)は、DMD100が複数のホストシステム、即ちホストシステム1 1510とホストシステム2 1520 , ... , ホストシステムK 1530に対する高速度ディスク記憶エミュレータとして配備されるときの例示的な構造を示している。この配備では、ホストシステムはデータリクエストを、SCSI / ファイバチャンネル制御装置140(図1参照)を介してDMD100へ送信することができる。データリクエストを受信した

30

40

50

とき、 D M D 100はそのデータリクエストを処理し、リクエストされたデータにアクセス し、その後、リクエストしているホストシステムへ応答を返送する。

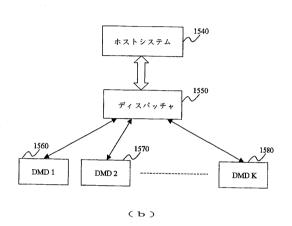

### [0078]

図15の(b)は、DMD100が高速度ディスク記憶エミュレータとして配備されるときの異なる例示的な構造を示している。この構造では、単一のホストシステム1540は複数のDMD、即ち大容量データ記憶用のDMD1 1560、DMD2 1570,…,DMDK1580を配備することができる。多数のDMD間で調整するため、ディスパッチャ1550が配備され、ホストシステム1540からのデータリクエストを誘導し、DMDからの応答をホストシステム1540からのデータリクエストを誘導し、DMDからの応答をれているデータは、決定された種々の規準にしたがって、例えばアプリケーションの要求にしたがって、分配されることができる。例えば、データベースの異なる論理部分が異なるDMDに記憶されてもよく、分配マップが設定されることができ、ディスパッチャ1550によって、リクエストを誘導して応答を転送する方法を決定するために使用されることができる。幾つかのDMDは故障を許容する目的で設けられることもできる。その代わりに、ディスパッチャはデータリクエストを特定のDMDへ発送する前に、負荷の平衡を実行するように構成されることができる。

# [0079]

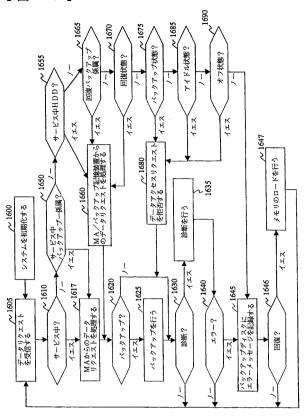

図16は、本発明の1実施形態にしたがって、DMD100が、(固体の高速度ディスクをエミュレートする)高速度ディスクエミュレータとして使用され、データリクエストを処理する例示的なプロセスのフローチャートである。そのシステムは最初にステップ1600で初期化される。初期化の終了時に、適切なシステム状態が設定される。初期化プロセスに関する詳細を図17を参照して説明する。初期化後、システムは1605で、ホストシステムからデータリクエストを受信する。データリクエストの受信に関する詳細を図18を参照して説明する。データリクエストがDMD100に記憶されているあるデータをアクセス(即ち読取または書込み)するとき、(図9を参照して説明したように)汎用目的のプロセッサ12を通過せずに、FPGA12を通って直接データ転送が行われることができる。このようなデータリクエストをサービスするため、システムは現在のシステム状態を決定する。それぞれ1610および1650で決定されたシステム状態がサービス中(状態(4))であるか、サービス中バックアップ係属(システム状態(5))であるならば、データリクエストはしたがって1615で、メモリ120から処理される。メモリ120からのデータリクエストの処理プロセスを図19を参照して説明する。

# [0080]

システム状態が、それぞれ1650、1665、1670で決定されたサービス中バックアップ(システム状態(3))、回復バックアップ係属状態(システム状態(6))、又は回復(システム状態(2))であるならば、データリクエストは、したがって1660で、リクエストされた位置にしたがって、メモリ120またはバックアップ記憶装置130からのデータが処理される。メモリ120またはバックアップ記憶装置130から処理されるデータリクエストに関する詳細を図20を参照して説明する。システム状態が、それぞれ1675、1685、1690で決定されたバックアップ状態(システム状態(7))、アイドル状態(システム状態(8)、オフ状態(システム状態(9))のうちの1つであるならば、システムは1680で、データリクエストのサービスを拒否する。

#### [0081]

データリクエストが処理された(1615または1660でサービスされた)後、システムは1620において、バックアップが実行される必要があるか否かをチェックする。バックアッププロセスが初期化される必要がある状態については、図8(システム状態の転移)を参照して説明される。バックアップが必要とされるならば、DMD100は1625で、バックアッププロセスを呼び出す。バックアップ(または回復)プロセス期間中、あるフラグは正しいシステム状態の転移を可能にするために適時に設定されることができる。例えば、バックアッププロセスが開始されるとき、システムはそれがバックアッププロセスの終了前の全ての次のデータリクエストを拒否するようにバックアップフラグを設定することができ

20

30

40

50

る。終了時、フラグはシステム状態の転移が初期化されることができるように、適切にリ セットされることができる。

### [0082]

システムはまた、ある診断ルーチンが実行される必要があるか否かを、1630でチェックできる。診断ルーチンを実行する場合に関する例示的な規準は前述したとおりである。例えば、このようなルーチンが規則的に実行されるように、規則的な間隔が設定されることができる。診断ルーチンはまた、ある事象の検出時に幾つかのソフトウェアアプリケーションによりトリガーされることができる。責任者がこれらを外部で付勢することもできる。診断ルーチンはステップ1635で実行される。診断期間中に、1640で検出されたエラーが存在することが決定されたならば、ステップ1645で、バックアップ記憶装置130にエラーメッセージが書込まれるか記録される。

#### [0083]

システムは1646で、回復プロセス(メモリのロード)が初期化される必要があるか否かをチェックされる。メモリのロードプロセスが初期化される例示的な状態について図8(システム状態の転移)を参照して説明する。回復が必要とされるならば、プロセスは1647で実行される。このプロセス期間中、データがバックアップ記憶装置130からメモリ120へ移動されることを示すためにあるフラグが設定されることができ、それによってこのようなシステム状態の下で受信されたデータリクエストは適切に処理されることができる。回復プロセスの終了時に、フラグはシステム状態が適切に変更されることができるようにリセットされる。

#### [0084]

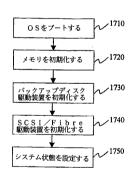

図17は、本発明の1実施形態による、DMD100が初期化される例示的なプロセスのフローチャートである。オペレーティングシステム(OS)は最初に、1710でブートされる。OSのブートが終了すると、プロセッサ210は、1720においてメモリ120を、1730においてバックアップ記憶駆動装置を、また1740においてSCSI/ファイバ駆動装置を含む種々の駆動装置を初期化する。初期化の状態に基づいて、システムはその後、1750で適切なシステム状態を設定する。

#### [0085]

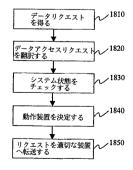

図18は、本発明の1実施形態による、プロセッサ210がデータリクエストを受信し、そのリクエストを適切な駆動装置へ転送する例示的なプロセスのフローチャートである。プロセッサ210が1810で、そのPCIXインターフェースを介してデータリクエストを受信するとき、これは最初に、1820でデータリクエストを翻訳する。データリクエストを適切な駆動装置へ転送する前に、プロセッサ210は1830で、現在のシステム状態を決定する。現在のシステム状態およびデータリクエストの特性に基づいて、プロセッサ210は1840で、データリクエストを処理する適切なオペレーティング装置を決定し、それに続いて1850で、データリクエストを、このように決定されたオペレーティング装置へ転送する。

# [0086]

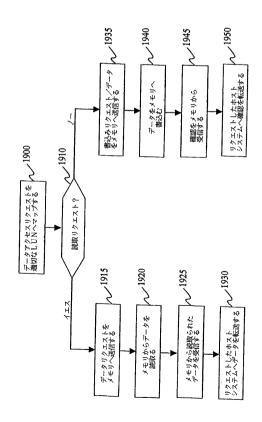

図19は、本発明の1実施形態にしたがって、データリクエストがメモリ120から処理される例示的なプロセスのフローチャートである。データリクエストを受信するとき、DMD100は最初に、1900で、例えば必要とされるプロックサイズに基づいて、データリクエストを適切なLUN構造へマップする。データリクエストの性質がその後1910で解析される。データリクエストが読取リクエストであるならば、読取リクエストは1915で、メモリ120へ送信される。そのデータはその後、1920で読取られる。メモリ120から読取られたデータが1925で受信されるとき、これは1930でデータリクエストを行ったホストシステムへ戻される。データリクエストが書込みリクエストであるならば、書込みリクエストは書込まれるデータと共に1935でメモリ120へ送信される。そのデータは1940でメモリ120へ書込まれる。データ書込みが終了されるとき、確認が1945でメモリ120から受信され、その後、1950でデータリクエストを行ったホストシステムへ転送される。

#### [0087]

図20は、本発明の1実施形態によって、データリクエストがメモリ120またはバック

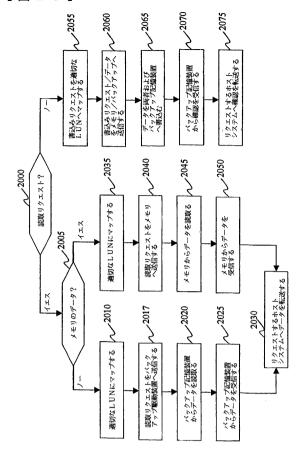

アップ記憶装置130から処理される例示的なプロセスのフローチャートである。前述したように、システム状態がサービス中バックアップ(システム状態(3))、回復バックアップ係属状態(システム状態(6))、又は回復(システム状態(2))であるならば、データリクエストは、データがリクエストされた位置にしたがって、メモリ120またはバックアップ記憶装置130から処理される。このような状態でデータリクエストを処理するために、DMD100は最初に、2000でデータリクエストが読取リクエストであるかまたは書込みリクエストであるかを決定する。

## [0088]

データリクエストが読取リクエストであるならば、読取られるデータの位置は2005で決定される。読取られるデータがバックアップ記憶装置130に位置されているならば、読取リクエストが2015でバックアップ記憶装置130へ送信される前に、適切なLUN構造がデータリクエストにしたがって、2010でマップされる。データが2020で、バックアップ記憶装置130から読取られた後、そのデータは、2025でバックアップ記憶装置130から受信され、その後、2030で読取リクエストを行ったホストシステムへ転送される。

#### [0089]

読取られるデータがメモリ120に位置されているならば、データリクエストが2040でメモリ120へ送信される前に、2035で適切なLUN構造へマップされる。データが2045でメモリ120から読取られた後、データは2050で受信され、その後、2030でリクエストを行ったホストシステムへ転送される。

### [0090]

データリクエストが書込みリクエストであることが2000で決定されたならば、DMD10 0はメモリ120とバックアップ記憶装置130との両者で書込み動作を行うことができる。この場合、書込みリクエストは最初に、2055でメモリ120とバックアップ記憶装置130との両者の適切なLUN構造にマップされる。マッピングは必要とされるブロックサイズにしたがって行われることができる。マップされたLUN構造に基づいて、書込み命令と、書込まれるデータが、2060でメモリ120とバックアップ記憶装置130との両者に送られ、2065で、データはその後、両者の記憶スペースに書込まれる。書込み確認が2070で、バックアップ記憶装置130から受信されたとき、DMD100はその確認を書込みリクエストを行ったホストシステムへ転送する。

# [ 0 0 9 1 ]

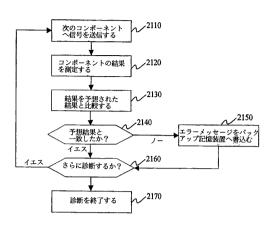

図21は、本発明の1実施形態による、診断が行われ、エラーメッセージがバックアップ記憶装置130に記録される例示的なプロセスのフローチャートである。この例示的な実施形態では、診断は一時に1つのコンポーネントで実行される。DMD100のコンポーネントを試験するために、信号が最初に2110でプロセッサ210からコンポーネントへ送信される。プロセッサ210はその後、2120でコンポーネントが信号を受信した後の結果を測定する。測定された結果は、その後2130で予め記憶されている予想された結果と比較される。測定された結果が予想された結果と一致しないことが2140で決定されたならば、それはそのコンポーネントが故障していることを示している可能性がある。この場合、試験に関するエラーメッセージが、2150でバックアップ記憶装置130に書き込まれる。診断プロセスは、2160で試験される全てのコンポーネントが試験されたことが決定されるまで継続される。診断プロセスは2170で終了する。

### [0092]

ここで説明されたDMD100はさらに他の目的で配備されることができる。例えばDMDはデータオフロードエンジンまたは装置として配備されることができる。このような応用では、サーバはそのI/O集約的なタスクをDMDへオフロードすることができる。このようなDMDはDMDとサーバ中のプロセッサとの間でデータを共有するために必要とされる可能性がある。データはDMDとサーバとの両者にアクセス可能な位置に配置される必要がある可能性がある。このように配備されたDMDは、DMD中のデータ転送/移動が汎用目的のプロセッサを通らずにFPGAによって直接的に実行されることができるので、指定されたタスクの要求にしたがって、高速度のデータ操作を行うことができる。

20

10

30

40

50

20

30

40

50

ここで説明される D M D がオープンアーキテクチャであり、小さい寸法であるので、このようなアプリケーションは実行可能である。それ故、これは任意の特別な装置またはソフトウェア接続を必要とせずに、サーバに容易に埋設または接続されることが可能である。 【 0 0 9 3 】

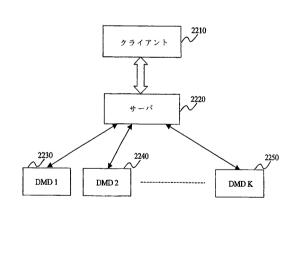

図22は、1以上のスレーブDMDがデータオフロードエンジンまたは装置としてマスター装置により配備される例示的な構造を示している。この実施形態では、複数のワMD(例えばDMD1 2230、DMD2 2240、…,DMDk 2250)が1以上のクライアント(例えばクライアント2210)に接続されたサーバ2220により配備される。クライアント2210がサービスリクエストをサーバ2220に送信するとき、リクエストの特性にしたがっしたがリカーが大容量であるので、これはデータの操作と処理を非常にいた中分に完全なコンピュータ装置であるので、これはデータの操作と処理を非常にいて十分に完全なコンピュータ装置であるので、これはデータの操作と処理を非常にいたですることができる。例えばリクエストが大容量データへース中の検索に基づいた方法では、スレーブDMDがデータへであらば、マスターサーバの性能がある。代わりに、例のフーは停止し、レーブDMDがデータへースの異なる部分を記憶し、データへ、スロアに記した方法では、スレーブDMDがデータへ、スの異なる部分を記憶し、データへ、スコに記り、カーションを実行するように構成されているが、マスターサーバ2220は(ブラットでは、スロースのデータの適切な部分を有することができる。MDの1つに、必要な大容量検索を高速度で実行するように命令のことでは、複数の1つに、必要な大容量検索を高速度でによりました。

[0094]

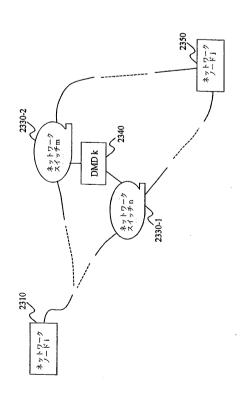

図 2 3 は、DMD100の別の応用を示している。この例では、DMDはネットワーク制 御機構として配備されている。この構造では、ネットワークノードi~2310は、1以上の ネットワークスイッチにより決定されたダイナミックネットワークパスを介して、別のネ ットワークノード j 2350へ接続されている。これを行うため、 DMD 2340は高速度のデ ー 夕 操 作 能 力 を 1 以 上 の ネ ッ ト ワ ー ク ス イ ッ チ ( 例 え ば ネ ッ ト ワ ー ク ス イ ッ チ m の 2330-1 , ... , ネットワークスイッチ n の 2330 - 2 ) へ 提供するために配 備されることができる。こ のようなデータ操作タスクは、セキュリティ及び監視等のこのようなトラフィック制御お よびネットワーク管理を行う種々のネットワーク制御決定を含んでいる。ネットワーク化 において、スイッチはしばしば、トラフィックロードおよびネットワークの健全さに関す る情報に基づいて、トラフィックをダイナミックに指令するように要求される。このよう なダイナミックなネットワーク情報はしばしば、ネットワークトラフィックの現在の状態 を効率的に反映するために、迅速な速度で解析され、その後フラッシュアウトされる。さ らに、情報はしばしば、異なるスイッチ間で共用され、非常に高速度で操作されることを 必要とされる。ここで説明されたDMD100はこれらの要求を満足するのに適している。 このような設定で配備されるDMDは例えばソフトウェアまたはファームウェアの形態で 必要なトラフィック制御および/または管理特性を有していてもよい。FPGAはそこに 記憶されているデータをアクセスするパスを指令し、DMDが非常に高速度でデータ操作 タスクを実行することを許容する。

[0095]

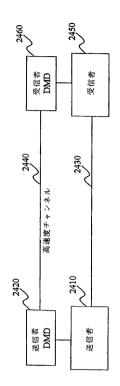

図24は、DMD100の別の例示的な応用を示している。この実施形態では、DMDはデータの送信及び受信のための高速度のデータ操作用として配備されることができる。これはデータ送信が、光ファイバネットワークのような高速度ネットワーク接続におけるマルチメディアまたはビデオ情報のような高帯域幅のチャンネルにわたる高容量のデータに関連するとき特に適している。この応用では、送信者2410は受信者2450によって、送信機サイトに記憶されたあるデータを送信するようにリクエストされることができる。例えばビデオ・オン・デマンド(VoD)アプリケーションでは、ユーザはケーブルネットワークを介して映画を送信するようにサービスプロバイダにリクエストできる。このようなデータの容量が大きく、送信時間がしばしば重要であるので、送信者2410は1以上のDMD(例えばDMD2420)を、データ記憶のためだけでなく、高速度送信のために配備することができる。即ち、配備されたDMD2420は高速度接続2440(例えばケーブルネットワーク)に直接接続されることができ、データ送信の前に行われる種々のデータ動作を行う。

10

20

30

40

50

例えばリクエストされたデータは送信前に暗号化される必要がある可能性がある。DMD自体は受動的記憶装置ではなく、完全なコンピュータ装置であるので、この設定で配備されるDMDには必要な暗号化アプリケーションが設けられることができる。さらに、汎用目的のプロセッサおよび説明したその他の特徴(例えば代わりのメモリモード方式)を通らずに、データのアクセスを指令するためのFPGAパスによって、DMDは非常に高速度で、データをメモリへ、及びメモリから転送することができ、これはマルチメディア及びビデオ応用でしばしば必要である。

## [0096]

同様に、受信サイトで、別のDMD2460が高速度受信及び記憶を行うために配備されることができる。さらに、DMD2460はデータの暗号解読を行うように構成されることもでき、これは受信されたデータをDMD2460へ保存する前に、または記憶されたデータがDMDの記憶装置から受信装置によって検索されるときに行われることができる。例えばユーザはビデオ・オン・デマンドサービスを介して映画をリクエストすることができ、受信された映画は最初にその暗号化された形態で受信機サイトに記憶され、後で視聴のため検索され、解読されることができる。

### [0097]

前述した実施例は単なる例示である。ここで説明したDMD100は、小型でコンパクトなオープンアーキテクチャ、商用のCPUおよびOSを使用するための通常のデータ処理能力、プロセッサ及び変わりのメモリモード方式によらない直接的なFPGAのメモリアクセス、自蔵された機上バックアップ記憶装置を含むが、それらに限定されない種々の特有の特徴を有している。これらの特徴によってDMD100は種々の異なる応用シナリオで配備され、またモジュラ方法での大きい固体ディスクシステムの核として使用される。このような高度にモジュール化されたシステムは、単一の装置内の多数のファイル構造、効率的なデータ統合構造、故障隔離、迅速なバックアップ及び回復、及び故障許容度を処理することができる。

### [0098]

本発明をある例示された実施形態を参照して説明したが、ここで使用した用語は、限定の用語ではなく、説明の用語である。本発明の技術的範囲を逸脱せずに、特許請求の範囲内で、変更を行うことができる。本発明は特定の構造、作用、材料を参照してここで説明したが、本発明は説明した特定の要項に限定されるものではなく、広範囲の形態で実施されることができ、そのうちの幾つかは説明した実施形態のものとはかなり異なる可能性があり、特許請求の技術的範囲内であるような全ての等価の構造、動作、材料に及んでいる

【図面の簡単な説明】

### [0099]

- 【図1】本発明の1実施形態によるデータ操作装置の高レベルの機能ブロック図。

- 【図2】本発明の1実施形態によるメモリにおけるデータ記憶及びアクセスを制御するためのメモリ制御装置の高レベルの機能ブロック図。

- 【 図 3 】本発明の 1 実施形態によるデータ操作装置に配備されたプロセッサの高レベルの機能ブロック図。

- 【 図 4 】 本 発 明 の 1 実 施 形 態 に よ る デ ー タ 操 作 装 置 に お け る バ ッ ク ア ッ プ 記 憶 装 置 の 機 能 ブ ロ ッ ク 図 。

- 【 図 5 】 本 発 明 の 1 実 施 形 態 に よ る デ ー タ 操 作 装 置 の バ ッ テ リ シ ス テ ム の 機 能 ブ ロ ッ ク 図

【図6】本発明の1実施形態によるメモリの例示的な組織を示す図。

- 【 図 7 】 本 発 明 の 1 実 施 形 態 に よ る 種 々 の フ ラ グ お よ び L U N 構 造 に 関 す る デ ー タ ア ク セ ス リ ク エ ス ト ハ ン ド ラ の 高 レ ベ ル の 機 能 ブ ロ ッ ク 図 。

- 【図8】本発明の1実施形態による異なる動作条件下での例示的なシステム状態および転移を示す図。

- 【図9】本発明の1実施形態によるデータ操作装置の異なるコンポーネントの例示的な配

置図。

- 【図10】本発明の1実施形態によるメモリボードとその内部組織の例示的な配置図。

- 【図11】本発明の1実施形態によるメモリボード上の登録されたバッファの例示的な配置図。

- 【図12】本発明の1実施形態によるメモリボード上の位相ロックループクロックの例示的な配置図。

- 【図13】本発明の1実施形態による2つの異なるメモリボード間の例示的なピンシフト配置図。

- 【図14a】本発明の1実施形態によるSCSI制御装置ボードSCBの例示的な物理的なレイアウト図。

- 【図14b】本発明の1実施形態によるDRAM制御装置ボードまたはDCBの例示的な物理的なレイアウト図。

- 【図14c】本発明の1実施形態によるメモリボード上のメモリチップの例示的な物理的なレイアウト図。

- 【図14d】本発明の1実施形態によるコンパクトボックス中のデータ操作装置の異なるボードの例示的な物理的な配置図。

- 【図14e】本発明の1実施形態によるデータ操作装置の異なるボード及びコンポーネントの例示的な物理的アセンブリの異なる分解斜視図。

- 【図14f】本発明の1実施形態によるデータ操作装置の異なるボード及びコンポーネントの例示的な物理的アセンブリの異なる分解斜視図。

- 【図14g】本発明の1実施形態による異なる接続ポートを有するデータ操作装置を収納している例示的なボックスの異なる斜視図。

- 【図14h】本発明の1実施形態による異なる接続ポートを有するデータ操作装置を収納 している例示的なボックスの異なる斜視図。

- 【図15】本発明の1実施形態にしたがって、1以上のデータ操作装置が高速度ディスク記憶エミュレータとして使用されている記憶システムについての異なる例示的な実施形態を示す図。

- 【図16】本発明の1実施形態にしたがって、データ操作装置が、データ記憶およびアクセス用の高速度ディスクをエミュレートするために使用される例示的なプロセスのフローチャート。

- 【図17】本発明の1実施形態にしたがって、データ操作装置が初期化される例示的なプロセスのフローチャート。

- 【図18】本発明の1実施形態にしたがって、データ操作装置のプロセッサがデータアクセスリクエストを受信し、そのリクエストを適切な装置へ転送する例示的なプロセスのフローチャート。

- 【図19】本発明の1実施形態にしたがって、データリクエストがメモリから処理される 例示的なプロセスのフローチャート。

- 【図 2 0 】本発明の 1 実施形態にしたがって、データリクエストがメモリまたはバックアップ記憶装置から処理される例示的なプロセスのフローチャート。

- 【図21】本発明の1実施形態にしたがって、診断が行われ、エラーメッセージがバックアップ記憶装置に記録される例示的なプロセスのフローチャート。

- 【図22】本発明の1実施形態にしたがって、1以上のデータ操作装置が高速度データオフロードタスクを実行するためのスレーブ処理装置として配備されている例示的な配備構造を示す図。

- 【図23】本発明の1実施形態にしたがって、データ操作装置が高速度トラフィック制御およびネットワーク管理処理を実行するためネットワークスイッチを補助するために配備されている例示的な配備構造を示す図。

- 【図24】本発明の1実施形態にしたがって、データ操作装置が高速度ネットワーク接続上で高帯域幅のデータ送信を処理するために配備されている例示的な配備構造を示す図。

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

# 【図10】

【図11】

# 【図12】

【図13】

### 【図14a】

### 【図14b】

# 【図14c】

# 【図14d】

【図14e】

【図14f】

【図14g】

【図14h】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

### 【図24】

## 【手続補正書】

【提出日】平成18年10月26日(2006.10.26)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

【補正の内容】

【特許請求の範囲】

【請求項1】

低プロフィールフォームファクタのハウジングと、

前記ハウジング中に配置され、データの記憶を行うように構成されているメモリと、

前記ハウジング中に配置され、前記メモリを制御するように構成されているメモリ制御 装置と、

前記ハウジング中に配置され、前記メモリ制御装置に接続され、データリクエストを受信して、そのデータリクエストに応答する情報を返送するインターフェースを提供するように構成されているチャンネル制御装置と、

前記ハウジング中に配置され、前記チャンネル制御装置に接続され、前記メモリをバックアップするための記憶スペースを提供するように構成されているバックアップ記憶装置とを具備しているデータ操作装置。

# 【請求項2】

前 記 メ モ リ は 固 体 デ ィ ス ク メ モ リ で あ る 請 求 項 1 記 載 の デ ー タ 操 作 装 置 。

## 【請求項3】

前記バックアップ記憶装置はエラー記録メッセージを記憶するために使用される請求項 2 記載のデータ操作装置。

【請求項4】

前記バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中のメモリスペースとして使用される請求項2記載のデータ操作装置。

### 【請求項5】

前記メモリは1以上のLUN構造を有し、各LUN構造は異なるブロックサイズを有するデータを記憶するために使用されることができる請求項1記載のデータ操作装置。

### 【請求項6】

前記メモリは複数のメモリ部分に分割され、各メモリ部分はスリープモード<u>と</u>、ウェイクアップモードの<u>1つに独立して</u>設定されることができ、スリープモード下では、メモリ部分は低電力消費状態であり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能である請求項1記載のデータ操作装置。

### 【請求項7】

前記チャンネル制御装置はSCSIチャンネル制御装置またはファイバ制御装置のうちの1つである請求項2記載のデータ操作装置。

### 【請求項8】

前記SCSIチャンネル制御装置と前記ファイバチャンネル制御装置は共通の駆動装置に対応している請求項フ記載のデータ操作装置。

### 【請求項9】

前記メモリ制御装置は、

前記チャンネル制御装置に接続され、メモリアクセスを制御するように構成されている プロセッサと、

このプロセッサに接続されている同期ダイナミックランダムアクセスメモリ( S D R A M ) と、

前記メモリに接続され、メモリに直接アクセスすることのできるダイナミックランダムアクセスメモリ(DRAM)制御装置とを具備している請求項1記載のデータ操作装置。

# 【請求項10】

前 記 プロ セッサ は 汎 用 目 的 の プロ セッサ で あ る 請 求 項 9 記 載 の デ ー タ 操 作 装 置 。

# 【請求項11】

前記汎用目的のプロセッサは市場で入手可能である請求項10記載のデータ操作装置。

## 【請求項12】

オペレーティングシステムが前記プロセッサに配備され、前記プロセッサにおいて動作 することができる請求項 9 記載のデータ操作装置。

# 【請求項13】

前記オペレーティングシステムは商用のオペレーティングシステムである請求項<u>1 2</u>記載のデータ操作装置。

### 【請求項14】

前記プロセッサは、

前記チャンネル制御装置とインターフェースするように構成されているバスインターフェースと、

データのリクエストを処理するために前記バスインターフェースと通信するデータアク セスリクエストハンドラと、

メモリのロードを行うように構成されているメモリロードハンドラと、

データをメモリから前記バックアップ記憶装置へ移動するように構成されているメモリ バックアップハンドラとを具備している請求項 9 記載のデータ操作装置。

# 【請求項15】

前記プロセッサはさらに、

診断ルーチンを行うように構成されている診断機構と、

前記診断機構により発生されるエラー情報をバックアップ記憶装置へ書込むように構成されているエラー記録機構とを具備している請求項14記載のデータ操作装置。

### 【請求項16】

診断機構は、外部の手作業の付勢により、および/またはプロセッサで稼動するオペレ

ーティングシステムにより付勢される請求項15記載のデータ操作装置。

### 【請求項17】

診断機構は局地的および/または遠隔操作で付勢されることができる請求項<u>15</u>記載のデータ操作装置。

## 【請求項18】

前記プロセッサはさらに、メモリ中の異なるメモリ部分のモードを制御するように構成されているメモリ状態制御装置を具備している請求項14記載のデータ操作装置。

## 【請求項19】

さらに、充電可能なバッテリを介してデータ操作装置へ電力を供給するように構成されているバッテリシステムを具備している請求項1記載のデータ操作装置。

## 【請求項20】

前記バッテリシステムは、

再充電可能なバッテリと、

再充電可能なバッテリの電力レベルを監視するように構成されているモニタと、

バッテリを充電するように構成されているバッテリ充電装置と、

ある入力電圧を有する再充電可能なバッテリから、データ操作装置により必要とされる 複数の出力電圧のうちの1つへ電力を変換するように構成されているDC・DC変換器と を具備している請求項19記載のデータ操作装置。

### 【請求項21】

前記再充電可能なバッテリは自動的に放電を開始できるように構成されている請求項<u>2</u>0 記載のデータ操作装置。

### 【請求項22】

バッテリは周期的に放電される請求項21記載のデータ操作装置。

#### 【 請 求 項 2 3 】

バッテリはバッテリがフルパワーに到達したときに放電される請求項 <u>2 1</u>記載のデータ操作装置。

# 【請求項24】

バッテリの放電は、前記プロセッサによって制御される請求項 <u>2 1</u>記載のデータ操作装置。

# 【請求項25】

<u>メモリは、前記ハウジング中に配置され、データの記憶を行うように構成されている固</u>体ディスクメモリを含んでいる請求項 1 記載のデータ操作装置。

### 【請求項26】

<u>さらに、前記データ操作装置と通信し、データリクエストを送信し、データ操作装置から応答を受信する1以上のホストシステムを具備している請求項1記載のデータ操作装置</u>

### 【請求項27】

さらに、サービスを提供するように構成されているマスターサーバと、

<u>このマスターサーバと通信するスレーブのデータ操作装置として動作する1以上のデー</u>タ操作装置とを具備している請求項1記載のデータ操作装置。

# 【請求項28】

データリクエストを、ホストシステムから、データ操作装置へ送信し、<u>前記データ操作装置はデータ記憶のためのメモリと、メモリのバックアップのためのバックアップ記憶装置を備えており、メモリは複数のメモリ部分を含み、各メモリ部分はスリープモードと、ウェイクアップモードの1つに設定されることができ、スリープモード下では、メモリ部分は低電力消費状態にあり、アクセス可能ではなく、ウェイクアップモード下では、メモリ部分はアクセス可能であり、</u>

そのデータ操作装置によって、データリクエストを受信し、

前記データ操作装置の現在のシステム状態にしたがって、前記データ操作装置によりデータリクエストを処理し、

前記データ操作装置によって、データリクエストに対する応答としての結果を、前記ホストシステムへ送信し、

<u>アクセスされる少なくとも1つのメモリ部分をウェイクアップモードに設定し、残りの</u>前記メモリ部分はスリープモードに設定し、

<u>アクセス後、前記少なくとも1つのメモリ部分をスリープモードに設定するステップを</u>含んでいる記憶方法。

### 【請求項29】

バックアップ記憶装置は、バックアップ記憶装置からメモリへのメモリロード期間中に、一時的なメモリとして使用されることができる請求項28記載の方法。

### 【請求項30】

前記データ操作装置はSCSIおよびファイバインターフェースの一つを介して、データリクエストを受信し、SCSIおよびファイバインターフェースは共通の駆動装置を共有している請求項28記載の方法。

# 【請求項31】

前記メモリは固体ディスクメモリである請求項28記載の方法。

#### 【請求項32】

前記メモリは複数のLUN構造を有し、それぞれ少なくとも2つの異なるブロックサイズのデータを記憶することが可能である請求項28記載の方法。

#### 【 請 求 項 3 3 】

前記データ操作装置は、条件が満たされるとき、そのバッテリの電力を自動的に放電<u>可</u>能に構成されている請求項28記載の方法。

### 【請求項34】

データ操作装置は、診断ルーチンを実行可能に構成されている請求項28記載の方法。

### 【請求項35】

診断ルーチン期間中に発生されるエラーメッセージは、バックアップ記憶装置に書込まれる請求項34記載の方法。

# 【請求項36】

前記データ操作装置は汎用目的のプロセッサを使用している請求項28記載の方法。

## 【請求項37】

商用のオペレーティングシステムが配備され、汎用目的のプロセッサで動作される請求 項36記載の方法。

# 【国際調査報告】

| INTERNATIONAL SEARCH REPOR                                                                                                                                                                                                                                      |                                                                                   | International application No.                                                                                                                                                                                                                                              |                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

|                                                                                                                                                                                                                                                                 |                                                                                   | PCT/US05/06008                                                                                                                                                                                                                                                             | PCT/US05/06008        |  |

| A. CLASSIFICATION OF SUBJECT MATTER  IPC(7): G06F 12/16, 15/16, 15/177, 1/24/ 1/26  US CL: 711/102, 162, 166; 709/208; 713/1, 323; 714/5  According to International Patent Classification (IPC) or to both national classification and IPC  B. FIELDS SEARCHED |                                                                                   |                                                                                                                                                                                                                                                                            |                       |  |