# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-191013 (P2006-191013A)

(43) 公開日 平成18年7月20日(2006.7.20)

| (51) Int.C1. |         |           | F 1  |        |       | テーマコード                    | (参考)     |

|--------------|---------|-----------|------|--------|-------|---------------------------|----------|

| HO1L         | 29/786  | (2006.01) | HO1L | 29/78  | 617L  | 2H092                     |          |

| G02F         | 1/1368  | (2006.01) | GO2F | 1/1368 |       | $4\mathrm{M}1\mathrm{O}4$ |          |

| HO1L         | 21/28   | (2006.01) | HO1L | 29/78  | 617T  | 5F033                     |          |

| HO1L         | 23/52   | (2006.01) | HO1L | 21/28  | 301R  | 5 F 1 1 O                 |          |

| HO1L         | 21/3205 | (2006.01) | HO1L | 21/88  | R     |                           |          |

|              |         |           |      | 審      | 査請求 有 | 請求項の数 21 OL               | (全 22 頁) |

(21) 出願番号 特願2005-355648 (P2005-355648)

(22) 出願日 平成17年12月9日 (2005.12.9)

(31) 優先権主張番号 10-2005-001797

(32) 優先日 平成17年1月7日(2005.1.7)

(33) 優先権主張国 韓国(KR)

(71) 出願人 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国443-742京畿道水原市霊通

区梅灘洞416

(74)代理人 100094145

弁理士 小野 由己男

(74)代理人 100106367

弁理士 稲積 朋子

(74)代理人 100117422

弁理士 堀川 かおり

(72) 発明者 裴 良 浩

大韓民国京畿道水原市勸善區谷伴亭洞ギボ

アートヴィル#204

最終頁に続く

(54) 【発明の名称】薄膜トランジスタ基板、その製造方法及び液晶表示装置

# (57)【要約】

## 【課題】

本発明は、アルミニウム配線で発生するヒールロック を減少させる、薄膜トランジスタ基板及びその製造方法 を提供する。

# 【解決手段】

本発明による薄膜トランジスタ基板は、下部アルミニウム層と、前記下部アルミニウム層の上に形成されている窒化アルミニウム層と、前記窒化アルミニウム層の上に形成されている上部アルミニウム層を含むことを特徴とする。

【選択図】図1

## 【特許請求の範囲】

## 【請求項1】

下部アルミニウム層と:

前記下部アルミニウム層上に形成された窒化アルミニウム層と;

前記室化アルミニウム層上に形成された上部アルミニウム層とを含むことを特徴とする 薄膜トランジスタ基板。

#### 【請求項2】

前記上部アルミニウム層の厚さは 2 5 0 0 以下である請求項 1 に記載の薄膜トランジスタ基板。

#### 【請求項3】

前記上部アルミニウム層の厚さは1500 以下である請求項2に記載の薄膜トランジスタ基板。

## 【請求項4】

前記下部アルミニウム層と前記上部アルミニウム層との厚さの合計は、4000 以上である請求項1~3のいずれか1つに記載の薄膜トランジスタ基板。

#### 【請求項5】

前記室化アルミニウム層の厚さは、前記下部アルミニウム層の厚さの5%以上である請求項1~4のいずれか1つに記載の薄膜トランジスタ基板。

#### 【請求項6】

前記室化アルミニウム層の厚さは、100~400 である請求項1~5のいずれか1つに記載の薄膜トランジスタ基板。

#### 【請求項7】

前記上部アルミニウム層上に形成されたモリブデン層をさらに含む請求項1~6のいずれか1つに記載の薄膜トランジスタ基板。

#### 【請求項8】

前記室化アルミニウム層の窒素含有量は、0.01~60原子%である請求項1~7のいずれか1つに記載の薄膜トランジスタ基板。

#### 【請求項9】

ゲート配線とデータ配線とを含む薄膜トランジスタ基板であって、

前記ゲート配線とデータ配線との少なくとも一方が、下部アルミニウム層、窒化アルミニウム層及び上部アルミニウム層がこの順に形成されてなる薄膜トランジスタ基板。

# 【請求項10】

前記上部アルミニウム層上に形成されたモリブデン層をさらに含む請求項9に記載の薄膜トランジスタ基板。

## 【請求項11】

前記下部アルミニウム層と前記上部アルミニウム層との厚さの合計は、4000 以上である請求項9又は10に記載の薄膜トランジスタ基板。

## 【請求項12】

前記室化アルミニウム層の厚さは、前記下部アルミニウム層の厚さの5%以上である請求項9~11のいずれか1つに記載の薄膜トランジスタ基板。

# 【請求項13】

前記室化アルミニウム層の厚さは、100~400 である請求項9~12のいずれか 1つに記載の薄膜トランジスタ基板。

# 【請求項14】

前記室化アルミニウム層の窒素含有量は、0.01~60原子%である請求項9~13のいずれか1つに記載の薄膜トランジスタ基板。

### 【請求項15】

絶縁基板上に下部アルミニウム層を蒸着する工程と;

窒素の前駆体ガスが存在する雰囲気下で前記下部アルミニウム層上に窒化アルミニウム 層を蒸着する工程と;

50

40

10

20

前記室化アルミニウム層上に上部アルミ層を蒸着する工程を含むことを特徴とする薄膜トランジスタ基板の製造方法。

## 【請求項16】

前記上部アルミニウム層上にモリブデン層を形成する工程をさらに含む請求項15に記載の薄膜トランジスタ基板の製造方法。

#### 【請求項17】

前記上部アルミニウム層、前記室化アルミニウム層及び下部アルミニウム層の蒸着を連続的に行う請求項15又は16に記載の薄膜トランジスタ基板の製造方法。

#### 【請求項18】

前記室化アルミニウム層の蒸着を、スパッタリングにより行う請求項15~17のいずれか1つに記載の薄膜トランジスタ基板の製造方法。

### 【請求項19】

前記室素の前駆体ガスは、窒素ガス、アンモニア、一酸化窒素、二酸化窒素からなる群から選択される少なくとも1種である請求項15~18のいずれか1つに記載の薄膜トランジスタ基板の製造方法。

#### 【請求項20】

前記室素の前駆体ガスは、窒素ガス、アンモニア、一酸化窒素、二酸化窒素からなる群から選択される少なくとも1種であり、アルゴンと共に存在する請求項15~19のいずれか1つに記載の薄膜トランジスタ基板の製造方法。

## 【請求項21】

ゲート配線とデータ配線とを含み、前記ゲート配線とデータ配線との少なくとも一方が、下部アルミニウム層、窒化アルミニウム層及び上部アルミニウム層がこの順に形成されてなる第1基板と;

前記第1基板と対向する第2基板と;

前記第1基板と前記第2基板の間に位置する液晶層を含むことを特徴とする液晶表示装置。

## 【発明の詳細な説明】

#### 【技術分野】

# [0001]

本発明は、薄膜トランジスタ基板、その製造方法及び液晶表示装置に関し、さらに詳細にはアルミニウム層間に形成された窒化アルミニウム層を含む薄膜トランジスタ基板、その製造方法及び液晶表示装置に関する。

### 【背景技術】

## [0002]

液晶表示装置は、薄膜トランジスタ基板とカラーフィルター基板との間に液晶が注入されている液晶パネルを含む。液晶パネルは非発光素子であるため、薄膜トランジスタ基板 後面には光を供給するためのバックライトユニットが位置している。バックライトから照 射された光は、液晶の配列状態により透過量が調整される。

最近の液晶表示装置では、画面の大面積化、高解像度及び高開口率が要求されている。これに応じて、薄膜トランジスタ基板に形成される配線(ゲート配線、データ配線)が長くなる反面、その幅は縮小されている。このような傾向により、配線材料の比抵抗が高い場合、RC遅延が発生し、画質が歪曲される問題が深刻化されている。

## [0003]

今までの配線材料として使われたクロム(Cr)、モリブデン-タングステン合金(MoW)等の金属は、10μ / cm以上の高い比抵抗を有するため、20インチ以上の液晶表示装置に適用することは困難である。よって、比抵抗がより小さい配線材料の使用が要求されている。

比抵抗が低い金属としては銀、銅、アルミニウムなどがある。なかでも銀、銅は、ガラス基板との接着性が顕著に低い。特に銅は非晶質シリコン内に侵入して、素子を壊したり、逆にシリコンが銅内に侵入して、比抵抗値を低下させる問題がある。

20

10

30

1

40

#### [00004]

このような銀及び銅の短所により、現在最も一般的に使われている配線物質は、アルミニウムである。アルミニウムは比抵抗が 3 μ / c m程度と非常に低く、配線形成工程が容易であり、また低価格という長所がある。

しかし、アルミニウムの短所は、ヒールロック(hillock)が発生して、配線間の短絡を誘発することである。例えば、ゲート配線で発生したヒールロックはゲート絶縁膜を突き抜けて、上部のデータ配線と接触して配線間の短絡を誘発する。(たとえば、特許文献1参照)

このようなヒールロックによる問題点は、低抵抗化にむけてアルミニウム配線がより厚膜になると、より一層深刻になる。

【特許文献 1 】特開平 0 5 - 3 1 5 3 2 9 号

【発明の開示】

【発明が解決しようとする課題】

[0005]

本発明の目的は、ヒールロックの発生を減少させるアルミニウム配線を有する薄膜トランジスタ基板、この基板を備える液晶表示装置を提供することである。

本発明の他の目的は、ヒールロックの発生を減少させるアルミニウム配線を有する薄膜トランジスタ基板の製造方法を提供することである。

【課題を解決するための手段】

[0006]

本発明の薄膜トランジスタ基板は、下部アルミニウム層と、前記下部アルミニウム層上に形成された窒化アルミニウム層と、前記窒化アルミニウム層上に形成された上部アルミニウム層とを含むことを特徴とする。

また、本発明の別の薄膜トランジスタ基板は、ゲート配線とデータ配線とを含む薄膜トランジスタ基板であって、前記ゲート配線とデータ配線との少なくとも一方が、下部アルミニウム層、窒化アルミニウム層及び上部アルミニウム層がこの順に形成されてなることを特徴とする。

[0007]

これらの薄膜トランジスタ基板においては、前記上部アルミニウム層の厚さは 2 5 0 0 以下、及び / 又は 1 5 0 0 以下であることが好ましい。

また、前記下部アルミニウム層と前記上部アルミニウム層との厚さの合計は、4000 以上であることが好ましい。

前記室化アルミニウム層の厚さは、前記下部アルミニウム層の厚さの 5 % 以上、及び / 又は 1 0 0 ~ 4 0 0 であることが好ましい。

[0008]

前記上部アルミニウム層上に形成されたモリブデン層をさらに含むことが好ましい。 前記室化アルミニウム層の窒素含有量は、0.01~60原子%であることが好ましい

また、本発明の薄膜トランジスタ基板の製造方法は、

絶縁基板上に下部アルミニウム層を蒸着する工程と;

窒素の前駆体ガスが存在する雰囲気下で前記下部アルミニウム層上に窒化アルミニウム層を蒸着する工程と:

前記室化アルミニウム層上に上部アルミ層を蒸着する工程を含むことを特徴とする。

[0009]

この製造方法においては、前記上部アルミニウム層上にモリブデン層を形成する工程を さらに含むことが好ましい。

また、前記上部アルミニウム層、前記窒化アルミニウム層及び下部アルミニウム層の蒸着を連続的に行うことが好ましい。

さらに、前記室化アルミニウム層の蒸着を、スパッタリングにより行うことが好ましい

10

20

30

40

50

## [0010]

前記窒素の前駆体ガスは、窒素ガス、アンモニア、一酸化窒素、二酸化窒素からなる群から選択される少なくとも1種であるか、さらに、アルゴンと共に存在することが好ましい。

本発明の液晶表示装置は、ゲート配線とデータ配線とを含み、前記ゲート配線とデータ 配線との少なくとも一方が、下部アルミニウム層、窒化アルミニウム層及び上部アルミニ ウム層がこの順に形成されてなる第1基板と、

前記第1基板と対向する第2基板と、

前記第1基板と前記第2基板の間に位置する液晶層を含むことを特徴とする。

#### 【発明の効果】

[0011]

一般に、アルミニウム配線で発生するヒールロックの発生原因は次のようである。

薄膜トランジスタ基板の製造において、アルミニウム配線の形成後、絶縁膜、半導体層などがプラズマ強化化学気相蒸着(PECVD)工程によって蒸着される。PECVD工程は、高温で行われるが、この過程においてアルミニウムが圧縮応力を有するようになって、アルミニウム表面で拡散されやすい結晶粒界を通してアルミニウムが移動するが、絶縁膜を突き抜けて側面や上部側に移動したアルミニウムをヒールロックという。

### [0012]

本発明によれば、アルミニウム配線の中にアルミニウムの移動を防止できる窒化アルミニウム層を形成することにより、アルミニウム配線のヒールロック発生を抑制することができるアルミニウム配線を有する薄膜トランジスタ基板、この基板を備える液晶表示装置を提供することができる。

また、本発明の薄膜トランジスタ基板の製造方法によれば、このようなアルミニウム配線を、特異な工程を追加することなく、簡便に形成することができる。

【発明を実施するための最良の形態】

## [0013]

以下、本発明を、添付図を参照して説明する。

## 実施の形態 1

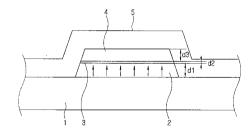

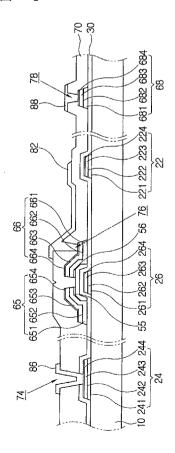

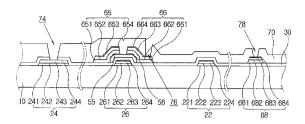

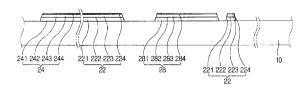

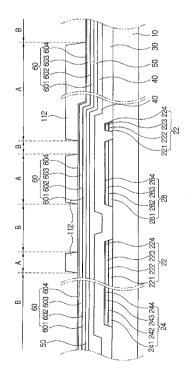

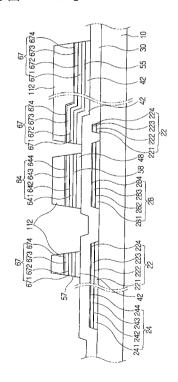

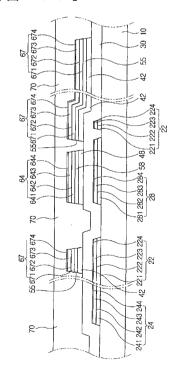

図1は、本発明の第1実施例によるアルミニウム配線を説明するための断面図である。 図1のアルミニウム配線は、下部アルミニウム層2、窒化アルミニウム層3及び上部アルミニウム層4の3層で形成されている。配線は基板1上に形成されており、アルミニウム配線の上部には絶縁膜5が形成されている。

# [0014]

室化アルミニウム層 3 は、下部アルミニウム層 2 の移動を防いで、ヒールロックの発生を減少させる。このために窒化アルミニウム層 3 の厚さ(d2)は下部アルミニウム層 2 の厚さ(d1)の 5 %以上であることが望ましい。一方、窒化アルミニウム層 3 の厚さ(d2)は、窒化アルミニウム層 3 が絶縁層になる可能性を考慮して、下部アルミニウム層 2 の厚さ(d1)の 3 0 %以下であることが望ましい。窒化アルミニウム層 3 が絶縁層になると、下部アルミニウム層 2 と上部アルミニウム層 4 とが電気的に絶縁されて、アルミニウム配線の比抵抗が増加する。

# [ 0 0 1 5 ]

具体的には、室化アルミニウム層3の厚さは100~400 であることが望ましい。 室化アルミニウム層3において、窒素の含有量は0.01~60原子%であることが望ま しい。これは、下部アルミニウム層2の移動を適切に防止するとともに、絶縁体層ではな く、誘電体層として適切に機能させるためである。

本 発 明 の 窒 化 ア ル ミ ニ ウ ム 層 3 は 、 炭 素 や 酸 素 の よ う な 成 分 を さ ら に 含 む こ と も で き る

## [0016]

上部アルミニウム層 4 の厚さ( d 4 )は 1 5 0 0 以下であることが望ましい。上部アルミニウム層 4 の移動は絶縁膜 5 を突き抜けるヒールロックになる可能性があるが、上部

10

20

30

40

アルミニウム層4の厚さ(d4)が1500 以下で比較的小さいと、短絡を誘発する水準のヒールロックは発生しない。

下部アルミニウム層 2 と上部アルミニウム層 3 を合わせたアルミニウム層の厚さの合計 (d 1 + d 3) は、4 0 0 0 以上であることが望ましい。これは大面積、高解像度の要求を満足させる低抵抗配線を作るためである。一方、アルミニウム層の厚さが 4 0 0 0 以下の場合、モリブデン層と同じ金属層でアルミニウム層をキャッピング(capping)という方法でヒールロックを防止することができる。

# [0017]

実施の形態 2

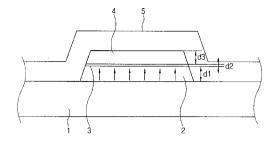

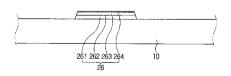

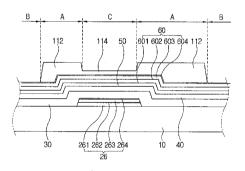

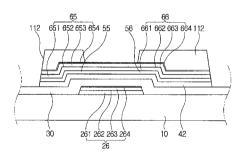

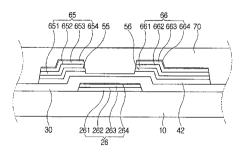

図2は、本発明の第2の実施形態によるアルミニウム配線を説明するための断面図である。

ここでは、上部アルミニウム層 4 の上にモリブデン層 6 がさらに形成されている。下部アルミニウム層 2 の厚さ(d4)と窒化アルミニウム層 3 の厚さ(d5)との関係と、窒化アルミニウム層 3 の形成は実施の形態 1 と同一である。

#### [0018]

上部アルミニウム層 4 の厚さ(d6)は、実施の形態 1 よりさらに厚くなってもよく、これは上部アルミニウム層 4 をモリブデン層 6 がキャッピングしていて、上部アルミニウム層 4 の移動を防止するためである。但し、上部アルミニウム層 4 の厚さ(d6)があまり大きい場合、モリブデン層 6 が上部アルミニウム層 4 の移動を適切に防止することができないため、上部アルミニウム層 4 の厚さ(d6)は 2 5 0 0 以下であることが望ましい。

#### [0019]

この実施形態でも、下部アルミニウム層 2 と上部アルミニウム層 4 とを合わせたアルミニウム層の厚さ( d 4 + d 6 )は、 4 0 0 0 以上であることが望ましい。

モリブデン層6の厚さ(d7)は、300~500 で形成することができる。また、ここでのモリブデン層6の代わりに、モリブデン合金層、ニッケル層、クロム層、チタニウム層を使用することも可能である。モリブデン層6は、上部アルミニウム層4の移動を防止し、かつ、透明伝導膜との接触抵抗が低いという長所を有する。配線は、その後の画素電極などとの連結のため、ITO、IZOのような透明伝導膜と接する。アルミニウムは透明伝導膜との接触抵抗が不良であるため、信号伝達に問題が発生する。その反面、実施形態2のようにモリブデン層6を配線の上部に形成すると、透明伝導膜はモリブデン層6と接触するようになり、信号伝達問題は解消される。

#### [0020]

以上のような本発明の実施形態によるアルミニウム配線は、種々変形される。例えば、 アルミニウム層と窒化アルミニウム層とが互いに反復しながら4重層以上で形成されても よい。

実施の形態3(実施の形態1のアルミニウム配線の形成方法)

まず、基板1上に下部アルミニウム層2を形成する。下部アルミニウム層2はスパッタリング法で形成することができる。

## [0021]

スパッタリング法では、高電圧が印加されるアルミニウムで形成されたターゲット電極が設置されたチャンバー内にアルゴンガスを注入してプラズマ放電を起こす。プラズマ放電により、励気されたアルゴン両イオンがターゲット電極でアルミニウム原子をはじき出し、このアルミニウム原子が基板素材表面で相互結合して、薄膜状に形成される。

所望の厚さで下部アルミニウム層 2 が形成されると、チャンバーに窒素ソースガスを導入して、窒素雰囲気下で窒化アルミニウム層 3 を形成する。窒素ソースガスとしては、窒素ガス(N<sub>2</sub>)、アンモニア(NH<sub>4</sub>)、一酸化窒素(NO)、二酸化窒素(NO<sub>2</sub>)等がある。この窒素ソースガス中、少なくとも1種以上をチャンバー内に導入すると、窒素がアルミニウムと共に蒸着され、窒化アルミニウム層 3 が形成される。

## [0022]

50

20

30

20

30

40

50

窒化アルミニウム層 3 が所望の厚さで形成されると、窒素ソースガスの注入を停止して、上部アルミニウム層 4 を蒸着する。必要に応じてチャンバー内に残存する窒素ソースガスを除去する別途の工程を行ってもよい。

以上の工程は、同一チャンバー内で連続的に形成されるため、追加の工程を要しない。 窒化アルミニウム層 3 はチャンバー内に窒素ソースガスのみを導入する比較的に簡単な 方法で形成される。

#### [0023]

以後パターニングによって、所望の形状のアルミニウム配線を形成して、上部に絶縁膜5を形成する。絶縁膜5形成の工程で、アルミニウム配線に高温が加えられても下部アルミニウム層2の移動を窒化アルミニウム層3が防止するので、ヒールラックを有効に防止することができる。

以下に、本発明による薄膜トランジスタ基板とその製造方法を図面に基づいて説明する

# [0024]

#### 実 施 例 1

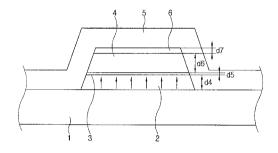

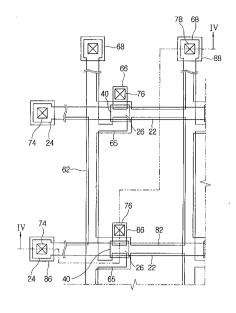

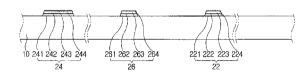

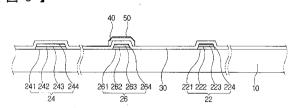

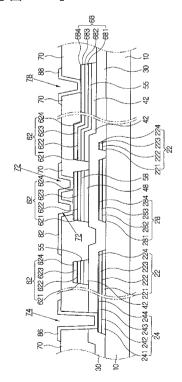

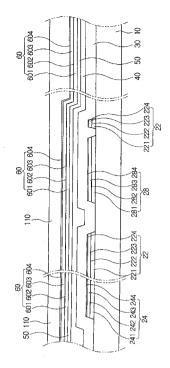

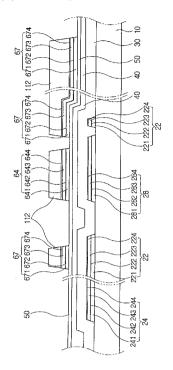

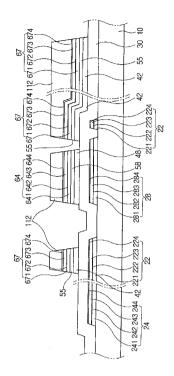

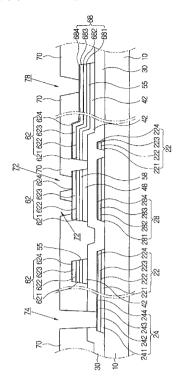

図3は、本発明の実施例1による薄膜トランジスタ基板の平面図であり、図4は、図3に図示した薄膜トランジスタ基板のIV-IV線断面図である。また、図5~図8は本発明の実施例1による薄膜トランジスタ基板の製造工程を示す断面図である。

基板素材 1 0 の上にゲート配線 2 2 、 2 4 、 2 6 が形成されている。ここでゲート配線 2 2 、 2 4 、 2 6 は、各々下部アルミニウム層 2 2 1 、 2 4 1 、 2 6 1 、窒化アルミニウム層 2 2 2 3 、 2 4 3 、 2 6 3 、モリブデン層 2 2 4 、 2 4 4 、 2 6 4 の 4 層で形成されている。

## [ 0 0 2 5 ]

ゲート配線22、26は、横方向に伸張されているゲート線22及びゲート線22に接続されている薄膜トランジスタのゲート電極26を含む。ここでゲート線22の一側の端部24は、外部回路との接続のために幅が拡張されている。

基板素材 1 0 の上には窒化ケイ素(SiNx)などで形成されたゲート絶縁膜 3 0 がゲート配線 2 2 、 2 4 、 2 6 を覆っている。

## [0026]

ゲート電極 2 4 のゲート絶縁膜 3 0 上には非晶質ケイ素などの半導体で形成された半導体層 4 0 が構成されており、半導体層 4 0 の上にはシリサイドまたは n 型不純物が高濃度でドーピングされている n \*水素化非晶質ケイ素などの物質で構成された抵抗性接触層 5 5、5 6 が各々形成されている。

抵抗性接触層 5 5 、 5 6 及びゲート絶縁膜 3 0 の上には、第 1 データ金属層 6 5 1 、 6 6 1 、 6 8 1 及び第 2 データ金属層 6 5 2 、 6 6 2 、 6 8 2 の 2 重層で形成されているデータ配線 6 5 、 6 6 、 6 8 が構成されている。データ配線 6 5 、 6 6 、 6 8 も下部アルミニウム層 6 5 1 、 6 6 1 、 6 8 1 、 窒化アルミニウム層 6 5 2 、 6 6 2 、 6 8 2 、上部アルミニウム層 6 5 3 、 6 6 3 、 6 8 3 、モリブデン層 6 5 4 、 6 6 4 、 6 8 4 の 4 層で形成されている。

## [0027]

データ線62も、図示していないがデータ配線65、66、68と共に4層である。 データ配線62、65、66は、縦方向で形成されて、ゲート線22と交差して、画素 を定義するデータ線62、データ線62の分枝であり、抵抗性接触層55の上部まで延び ているソース電極65、ソース電極65と分離しており、ゲート電極26を中心として、 ソース電極65の反対側の抵抗性接触層56上部に形成されているドレイン電極66を含 む。この時、データ線62の一側の端部68は、外部回路との接続のため、幅が拡張され ている。

## [0028]

データ配線 6 2 、 6 5 、 6 6 、 6 8 及びそれらが覆っていない半導体層 4 0 の上部には、窒化ケイ素 (SiNx)、PECVD (plasma Enhanced Chemi

cal vapor deposition)方法により蒸着されたa-Si:C:O膜、またはa-Si:O:F膜(低誘電率CVD膜)、及びアクリル界有機絶縁膜などで形成された保護膜70が形成されている。PECVD方法により蒸着されたa-Si:C:O膜とa-Si:O:F膜(低誘電率CVD膜)とは誘電常数が4以下(誘電常数は2~4の間の値を有する。)で、誘電率が非常に低い。従って、厚さが薄くても寄生容量問題が発生しない。

#### [0029]

また、他の膜との接着性及びステップカバレッジが優れている。さらに、無機質 C V D 膜であるため、耐熱性が有機絶縁膜に比べて優れる。また、 P E C V D 方法により蒸着された a - S i : C : F 膜 (低誘電率 C V D 膜)とは、蒸着速度やエッチング速度が窒化ケイ素膜に比べて、 4 ~ 1 0 倍早いため、工程時間面でも非常に有利である。

#### [0030]

保護膜70にはドレイン電極66及びデータ線の端部68を各々示すコンタクトホール76、78が形成されており、ゲート絶縁膜30と共にゲート線の端部24を示すコンタクトホール74が形成されている。

保護膜70の上にはコンタクトホール76を通して、ドレイン電極66と電気的に連結されており、画素領域に位置する画素電極82が形成されている。また、保護膜70の上にはコンタクトホール74、78を通して、各々ゲート線の端部24及びデータ線の端部68と連結されている接触補助部材86、88が形成されている。

## [0031]

ここで、画素電極82と接触補助部材86、88とは、ITOまたはIZOなどの透明 伝導膜で形成されている。即ちドレイン電極66はモリブデン層664を通して、画素電極82と接触するようになる。

ここで、画素電極82は図3及び図4で示したように、ゲート線22と重なり、維持蓄電器をなし、維持容量が不足する場合には、ゲート配線22、24、26と同一層に維持容量用配線を追加することもできる。

#### [0032]

また、画素電極 8 2 はデータ線 6 2 とも重なるように形成して、開口率を極大化することができる。このように開口率を極大化するために、画素電極 8 2 をデータ線 6 2 と重なるように形成しても、保護膜 7 0 の低誘電率 C V D 膜などで形成すると、これらの間から生じる寄生容量を、問題にならないほど小さく維持することができる。

この実施例の薄膜トランジスタ基板の製造方法は以下の通りである。

## [0033]

まず、図 5 に図示したように、基板素材 1 0 の上に下部アルミニウム層 2 2 1 、 2 4 1 、 2 6 1 、 窒化アルミニウム層 2 2 2 、 2 4 2 、 2 6 2 、上部アルミニウム層 2 2 3 、 2 4 3 、 2 6 3 、モリブデン層 2 2 4 、 2 4 4 、 2 6 4 の 4 層で構成されたゲート金属層を蒸着し、マスクを利用したフォトエッチング工程でパターニングして、ゲート線 2 2 及びゲート電極 2 6 を含んで横方向に伸張されているゲート配線 2 2 、 2 4 、 2 6 を形成する

# [ 0 0 3 4 ]

次に、図6に図示したように、窒化ケイ素で形成されたゲート絶縁膜30、非晶質ケイ素で形成された半導体層40、ドーピングされた非晶質ケイ素層50の3重膜を連続積層し、半導体層40とドーピングされた非晶質ケイ素層50をフォトエッチングして、ゲート電極24上のゲート絶縁膜30の上に島形の半導体層40と抵抗性接触層50とを形成する。

## [0035]

次に、図 7 に図示したように、下部アルミニウム層 6 2 1 、 6 5 1 、 6 6 1 、 窒化アルミニウム層 6 2 2 、 6 5 2 、 6 6 2 、上部アルミニウム層 6 2 3 、 6 5 3 、 6 6 3 、モリブデン層 6 2 4 、 6 5 4 、 6 6 4 、マスクを利用したフォトエッチング工程にパターニン

20

10

30

40

グして、ゲート線 2 2 と交差するデータ線 6 2 、データ線 6 2 と連結されてゲート電極 2 6 上まで延びているソース電極 6 5 、及びソース電極 6 5 と分離されてゲート電極 2 6 を中心にソース電極 6 5 と対向するドレイン電極 6 6 を含むデータ配線を形成する。

### [0036]

続いて、データ配線62、65、66、68で覆わないドーピングされた非晶質ケイ素層パターン50をエッチングしてゲート電極26を中心に両側に分離させる一方、両側のドーピングされた非晶質ケイ素層55、56の間の半導体層パターン40を露出させる。その後に、露出された半導体層40の表面を安定化させるために酸素プラズマを実施することが望ましい。

#### [ 0 0 3 7 ]

次に、図8で示したように、窒化ケイ素膜、a-Si:C:O膜またはa-Si:O:F膜を化学気相蒸着(CVD)法により形成したり、有機絶縁膜を塗布して、保護膜70を形成する。

続いて、フォトエッチング工程にゲート絶縁膜30と共に保護膜70をパターニングして、ゲート線の端部24、ドレイン電極66及びデータ線の端部68を表すコンタクトホール74、76、78を形成する。

## [0038]

次に、図3及び図4に図示した通り、ITOまたはIZO膜を蒸着及びフォトエッチングし、コンタクトホール76を通してドレイン電極66と連結される画素電極82と、コンタクトホール74、78を通してゲート線の端部24及びデータ線の端部68と各々連結される接触補助部材86、88を各々形成する。ITOまたはIZOを積層する前の予熱(pre-heating)工程で使用する気体は窒素であることが望ましい。

## [0039]

以上の第 1 実施例は薄膜トランジスタ基板の製造において、マスクを 5 枚使用した。 実施例 2

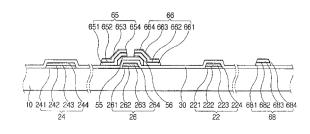

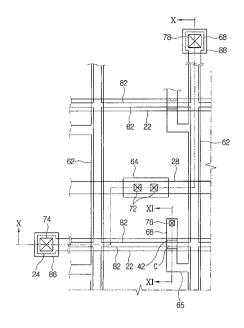

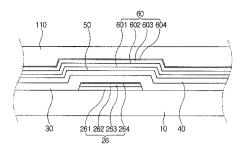

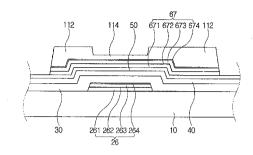

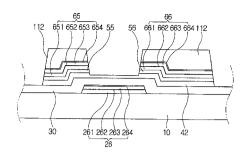

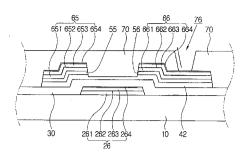

図9は本発明の第2実施例による薄膜トランジスタ基板の平面図であり、図10は図9のX-X線断面図、図11は図9のXI-XI線断面図である。また、図12a~図19bは、本発明の実施例2による薄膜トランジスタ基板の製造過程を示す断面図である。

# [0040]

基板素材 1 0 の上には、実施例 1 と同じように、下部アルミニウム層 2 2 1 、 2 4 1 、 2 6 1、 室化アルミニウム層 2 2 2 、 2 4 2 、 2 6 2 、上部アルミニウム層 2 2 3 、 2 4 3 、 2 6 3 、モリブデン層 2 2 4 、 2 4 4 、 2 6 4 によって構成されるゲート配線 2 2 、 2 4 、 2 6 が形成されている。

また、基板素材10の上には、ゲート線22と平行するように維持電極線28が形成されている。維持電極線28もゲート配線22、24、26のように4層になっている。

# [0041]

維持電極線28は、後述する画素電極82と連結された維持蓄電器用導電体64と重なり、画素の電荷保存能力を向上させる維持蓄電器をなし、後述する画素電極82とゲート線22の重複で発生する維持容量が充分な場合、形成しなくてもよい。維持電極線28には、通常、上部基板の共通電極と同じ電圧が印加される。

ゲート配線 2 2 、 2 4 、 2 6 及び維持電極線 2 8 の上には窒化ケイ素 ( S i N x ) などで構成されたゲート絶縁膜 3 0 が形成されて、ゲート配線 2 2 、 2 4 、 2 6 及び維持電極線 2 8 を覆っている。

# [ 0 0 4 2 ]

ゲート絶縁膜30の上には水素化非晶質ケイ素(hydrogenated amorphous silicon)などの半導体で構成された半導体パターン42、48が形成されており、半導体パターン42、48の上にはリン(P)などのn型不純物が高濃度でドーピングされている非晶質ケイ素などで構成された抵抗性接触層(ohmic contact layer)パターンまたは中間層パターン55、56、58が形成されている。

10

20

30

30

40

50

#### [0043]

抵抗性接触層パターン55、56、58の上には、下部アルミニウム層621、641、641、651、661、681、室化アルミニウム層622、642、652、662、682、上部アルミニウム層623、643、653、663、683、モリブデン層624、644、654、664、684の4層で構成されたデータ配線62、64、65、66、68が形成されている。データ配線は縦方向で形成されており、データ線62の一側の端部に連結され、外部からの画像信号の印加を受信するデータ線の端部68を有するデータ線62、データ線62の分枝である薄膜トランジスタのソース電極65で形成されたデータ線部62、68、65と分離されて、ゲート電極26または薄膜トランジスタのチャンネル部(E)に対してソース電極65の反対の側に位置する薄膜トランジスタのドレイン電極66と維持電極線28の上に位置している維持蓄電器用導電体64も形成しない。

# [0044]

接触層パターン55、56、58は、その下部の半導体パターン42、48とその上部のデータ配線62、64、65、66、68の接触抵抗を下げる役割を果たし、データ配線62、64、65、66、68と完全に同じ形態を有する。即ち、データ線部の中間層パターン55はデータ線部62、68、65と同一で、ドレイン電極用の中間層パターン56はドレイン電極66と同一で、維持蓄電器用の中間層パターン58は維持蓄電器用導電体64と同一である。

#### [0045]

一方、半導体パターン42、48は薄膜トランジスタのチャンネル部(C)を除くと、データ配線62、64、65、66、68及び抵抗性接触層パターン55、56、58と同形である。具体的には、維持蓄電器用半導体パターン48と維持蓄電器用導電体64及び維持蓄電器用接触層パターン58は同形だが、薄膜トランジスタ用半導体パターン42はデータ配線及び接触層パターンの残り部分と少々異なる。即ち、薄膜トランジスタのチャンネル部(C)でデータ線部62、68、65、特にソース電極65とドレイン電極66が分離されていて、データ線部中間層55とドレイン電極用接触層パターン56も分離されているが、薄膜トランジスタ用半導体パターン42は、ここで切れずに接続され、薄膜トランジスタのチャンネルを形成する。

## [0046]

データ配線62、64、65、66、68の上には窒化ケイ素またはPECVD法により、蒸着されたa‐Si:C:O膜またはa‐Si:O:F膜(低誘電率CVD膜)、または有機絶縁膜で形成された保護膜70が形成されている。保護膜70はドレイン電極66、データ線の端部68及び維持蓄電器用導電体64を出すコンタクトホール76、78、72を有し、またゲート絶縁膜30と共にゲート線の端部24を出すコンタクトホール74を有している。

## [0047]

保護膜70の上には薄膜トランジスタから画像信号を受信して、上板の電極と共に電気場を形成する画素電極82が形成されている。画素電極82はITOまたはIZOなどの透明伝導物質で形成され、コンタクトホール76を通して、ドレイン電極66と物理的/電気的に連結され、画像信号を受信する。

また、画素電極 8 2 は、隣りのゲート線 2 2 及びデータ線 6 2 と重なり、開口率を高めているが、必ずしも重ならなくてもよい。また、画素電極 8 2 は、コンタクトホール 7 2 を通して、維持蓄電器用導電体 6 4 とも接続され、導電体パターン 6 4 で画像信号を伝達する。

### [0048]

一方、ゲート線の端部24及びデータ線の端部68の上には、コンタクトホール74、78を通して各々これらと連結される接触補助部材86、88が形成されている。この接触補助部材86、88は、端部24、68と外部回路装置との接着性を補完してゲート線

20

30

40

50

及びデータ線各々の端部24、68を保護する役割を果たし、透明伝導膜で形成されている。

## [0049]

以下に、この薄膜トランジスタ基板の製造方法を説明する。

図12a及び図12bのように実施例1と同一に下部アルミニウム層221、241、261、281、窒化アルミニウム層222、242、262、282、上部アルミニウム層223、243、263、283、モリブデン層224、244、264、284、フォトエッチングしてゲート線22、ゲート電極26を含むゲート配線と維持電極線28を形成する。この時、外部回路と接続されるゲート線22の一側の端部24は幅が拡張されている。

## [0050]

次に、図13a及び13bに示した通ように、窒化ケイ素で形成されたゲート絶縁膜30、半導体層40、中間層50を化学気相蒸着法を利用して、各々1、500 ~5、000 、500 ~2、000 、300 ~600 の厚さで連続蒸着し、続いてデータ配線を形成するため、下部アルミニウム層601、窒化アルミニウム層302、上部アルミニウム層603、モリブデン層604の4中層で形成された導電体層60を形成した後、その上に感光膜110を1μm~2μmの厚さで塗布する。

### [0051]

その後、マスクを通し、感光膜110に光を照射した後に現像して、図13a及び13bに図示した通り、感光膜パターン112、114を形成する。この時、感光膜パターン112、114の中で薄膜トランジスタのチャンネル部(C)、即ちソース電極65とドレイン電極66の間に位置した第1部分114は、データ配線部(A)、即ちデータ配線62、64、65、66、68が形成される部分に位置した第2部分112より厚さが小さくなるようにして、その他の部分(B)の感光膜は全て除去する。

### [0052]

この時、チャンネル部(C)に残っている感光膜114の厚さとデータ配線部(A)に残っている感光膜112の厚さの比は、後述する食刻工程においての工程条件に応じて異なり、第1部分114の厚さを第2部分112の厚さの1/2以下にすることが望ましい。例えば、4、000 以下であることがよい。

このように、位置により感光膜の厚さに差を付ける方法として、種々の方法がある。例えば a 、 A 領域の光透過量を調節するために、主として、スリット、または格子形態のパターンを形成するか、半透明膜を用いる方法が挙げられる。

# [0053]

この時、スリットの間に位置したパターンの線幅、またはパターンの間の間隔、即ちスリットの幅は、露光時に使用する露光器の分解能より小さい方が望ましい。半透明膜を利用する場合には、マスクを製作する時、透過率を調節するために他の透過率を有する薄膜を利用したり、厚さが異なる薄膜を利用することができる。

このようなマスクを通し、感光膜に光を照射すると、光に直接露出する部分では高分子が完全に分解され、スリットパターンや半透明膜が形成されている部分では光の照射量が少ないため、高分子は完全分解されない状態であり、遮光膜で遮った部分では高分子がほとんど分解されない。続いて、感光膜を現像すると、高分子が分解されない部分だけ残って、光が少なく照射された中央の部分には光に全く照射されない部分より薄い厚さの感光膜が残こる。この時、露光時間を長くすると、すべての高分子が分解されるため、そうならないようにしなければならない。

#### [0054]

このような薄い厚さの感光膜 1 1 4 は、リフローが可能な物質で形成された感光膜を利用して、光が完全に透過できる部分と光が完全に透過できない部分に分けられた通常のマスクで露光した後の現象と、リフローさせて感光膜が残留しない部分に感光膜の一部を流すことによって形成することもできる。

続いて、感光膜パターン114及びその下部の膜、即ち導電体層60、中間層50及び

半導体層 4 0 に対するエッチングを行う。この時、データ配線部(A)にはデータ配線及びその下部の膜がそのまま残り、チャンネル部(C)には半導体層のみ残し、その他の部分(B)には上の導電体層 6 0、中間層 5 0 及び半導体層 4 0 が全て除去されて、ゲート絶縁膜 3 0 が露出する。

## [0055]

図14a及び14bに図示したように、その他の部分(B)で露出している導電体層60を除去して、その下部の中間層50を露出させる。この工程では乾式エッチングまたは湿式エッチング方法のいずれをも使用することができる。この時に導電体層60はエッチングされ、感光膜パターン112、114はほとんどエッチングされない条件下で行うことが好ましい。

[0056]

しかし、乾式エッチングの場合、導電体層60だけがエッチングされ、感光膜パターン112、114はエッチングされない条件を探すことが難しいため、感光膜パターン112、114も共にエッチングされる条件下で行うことができる。この場合には湿式エッチングの場合より、第1部分114が除去されて、下部の導電体層60を露出させないようにする。

### [0057]

このようにすると、図15a及び図15bに図示したように、チャンネル部(C)及びデータ配線部(A)の導電体層、即ちソース/ドレイン用導電体パターン67と維持蓄電器用導電体64だけ残って、その他の部分(B)の導電体層60は全て除去されて、その下部の中間層50が出る。この時、残った導電体パターン67、64は、ソース及びドレイン電極65、66が分離されず連結されていることを除いてデータ配線62、64、65、66、68の形態と同一である。また乾式エッチングを使用した場合、感光膜パターン112、114もある程度の厚さでエッチングされる。

#### [0058]

続いて、図16a及び16bに図示したように、その他の部分(B)の露出された中間層50及びその下部の半導体層40を感光膜の第1部分114と共に乾式エッチングで同時に除去する。この時のエッチングは、感光膜パターン112、114と中間層50及び半導体層40(半導体層と中間層はエッチング選択性がほとんどない)が同時にエッチングされ、ゲート絶縁膜30はエッチングされない条件下で行うことが好ましく、特に感光膜パターン112、114と半導体層40に対するエッチング比がほとんど同じ条件でエッチングすることが望ましい。例えば、SF $_6$ とHCIの混合気体、またはSF $_6$ とO $_2$ の混合気体を使用すると、ほとんど同じ厚さで二つの膜をエッチングすることができる。感光膜パターン112、114と半導体層40に対するエッチング比が同じ場合、第1部分114の厚さは半導体層40と中間層50の厚さを合わせたのと同一または、それより小さくなければならない。

# [0059]

このようにすると、図16a及び16bに図示したように、チャンネル部(C)の第1部分114が除去されて、ソース/ドレイン用導電体パターン67が現れ、その他の部分(B)の中間層50及び半導体層40が除去されて、その下部のゲート絶縁膜30が出す

一方、データ配線部(C)の第2部分112もエッチングされるため、厚さが薄くなる。また、この工程で半導体パターン42、48が完成される。符号57と58は各々ソース/ドレイン用導電体パターン67下部の中間層パターンと維持蓄電器用導電体64下部の中間層パターンを示す。

# [0060]

続いて、アッシングによって、チャンネル部( C )のソース / ドレイン用導電体パターン 6 7 表面に残っている感光膜のカスを除去する。

次に、図17a及び17bに図示した通り、チャンネル部( C )のソース / ドレイン用 導電体パターン 6 7及びその下部のソース / ドレイン用中間層パターン 5 7をエッチング 10

20

30

40

して除去する。この時、エッチングは、ソース / ドレイン用導電体パターン 6 7 と中間層パターン 5 7 全てに対し乾式エッチングのみで行うこともでき、ソース / ドレイン用導電体パターン 6 7 に対しては湿式エッチングで、中間層パターン 5 7 に対しては乾式エッチングで行うこともできる。

## [0061]

前者の場合、ソース / ドレイン用導電体パターン 6 7 と中間層パターン 5 7 のエッチング選択比が大きい条件下でエッチングすることが望ましい。これはエッチング選択比が大きくない場合、エッチング終点を探し難いため、チャンネル部(C)に残る半導体パターン 4 2 の厚さを調節することが容易ではないからである。

湿式エッチングと乾式エッチングを交互に行う後者の場合には、湿式エッチングされるソース / ドレイン用導電体パターン 6 7 の側面はエッチングされるが、乾式エッチングされる中間層パターン 5 7 は、ほとんどエッチングされないため、階段形状に構成される。中間層パターン 5 7 及び半導体パターン 4 2 をエッチングする時に使用するエッチャントしては、  $CF_4$  と HC 1 の混合気体,または  $CF_4$  と  $O_2$  の混合気体があり、  $CF_4$  と  $O_2$  を使用すると、均一な厚さで半導体パターン 4 2 を残せる。

#### [0062]

この時、図16bに示したように、半導体パターン42の一部が除去されて、厚さが小さくなる可能性もあり、感光膜パターンの第2部分112も、この時ある程度の厚さでエッチングされる。この時のエッチングは、ゲート絶縁膜30がエッチングされない条件で行うことが好ましく、第2部分112が食刻されてその下部のデータ配線62、64、65、66、68が出ることがないように感光膜パターンが厚いことが望ましい。

## [0063]

このようにすると、ソース電極 6 5 とドレイン電極 6 6 が分離しながら、データ配線 6 2 、 6 4 、 6 5 、 6 6 、 6 8 とその下部の接触層パターン 5 5 、 5 6 、 5 8 が完成される

最後にデータ配線部(A)に残っている感光膜第2部分112を除去する。しかし、第 2部分112の除去はチャンネル部(C)ソース/ドレイン用導電体パターン67を除去 した後、その下の中間層パターン57を除去する前に行われることもできる。

# [0064]

前記の説明のように、湿式エッチングと乾式エッチングを交互にするか、乾式エッチングのみを使用することができる。後者の場合には、一種類のエッチングのみを使用することで工程を比較的簡便にすることができるが、適切なエッチング条件を探すことが難しい。反面、前者の場合には比較的にエッチング条件を探し易いが工程が後者に比べて煩雑となる。

# [0065]

図18a及び図18bに図示した通り、窒化ケイ素でもa-Si:C:O膜またはa-Si:O:F膜を化学気相蒸着(CVD法)により、成長させたり有機絶縁膜を塗布して、保護膜70を形成する。

図19a~図19bに図示した通り、保護膜70をゲート絶縁膜30と共にフォトエッチングして、ドレイン電極66、ゲート線の端部24、データ線の端部68及び維持蓄電器用導電体64を各々露出するコンタクトホール76、74、78、72を形成する。

#### [0066]

最後に、図10及び図11に図示した通り、400 ~500 厚さのITO層または IZO層を蒸着し、フォトエッチングして、ドレイン電極66及び維持蓄電器用導電体6 4と接続された画素電極82、ゲート線の端部24とゲート接触補助部材86及びデータ 線の端部68と接続されたデータ接触補助部材88を形成する。

一方、ITOまたはIZOを積層する前の予熱工程で使用する気体として窒素を使用することが望ましい。これはコンタクトホール72、74、76、78を通して現れた金属膜24、64、66、68の上に金属酸化膜が形成されることを防止するためである。

# [0067]

50

40

20

20

30

40

50

この実施例では、実施例1による効果だけでなく、データ配線62、64、65、66、68とその下部の接触層パターン55、56、58及び半導体パターン42、48を一つのマスクを利用して形成し、この過程でソース電極65とドレイン電極66を分離することによって製造工程を単純化することができる。なお、実施例2では、マスクを4枚使用した。

【産業上の利用可能性】

[0068]

本発明による薄膜トランジスタ基板は、液晶表示装置または有機電気発光装置(organic light emitting diode)等の表示装置に使われる。

有機電気発光装置は、電気的な信号を受けて、発光する有機物を利用した自発光型素子である。有機電気発光装置には陰極層(画素電極)、ホール注入層、ホール輸送層、発光層、電子輸送層、電子注入層、両極層(対向電極)が積層されている。本発明による薄膜トランジスタ基板のドレイン電極は、陰極層と電気的に連結されて、データ信号を印加することができる。

【図面の簡単な説明】

[0069]

- 【図1】本発明の実施形態1によるアルミニウム配線を説明するための断面図である。

- 【図2】本発明の実施形態2によるアルミニウム配線を説明するための断面図である。

- 【 図 3 】 本 発 明 の 実 施 形 態 1 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 平 面 図 で あ る 。

- 【図4】図3のIV-IVに沿って示した断面図である。

- 【 図 5 】 本 発 明 の 実 施 例 1 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 を 示 す 断 面 図 で あ る 。

- 【 図 6 】 本 発 明 の 実 施 例 1 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 を 示 す 断 面 図 で あ る 。

- 【図7】本発明の実施例1による薄膜トランジスタ基板の製造工程を示す断面図である。

- 【図8】本発明の実施例1による薄膜トランジスタ基板の製造工程を示す断面図である。

- 【 図 9 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 平 面 図 で あ る 。

- 【図10】図9のX-X線断面図である。

- 【図11】図9のXI-XI線断面図である。

- 【 図 1 2 a 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 示 す 断 面 図 で あ る

【図12b】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【 図 1 3 a 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 示 す 断 面 図 で あ る

【図13b】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【図14a】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【 図 1 4 b 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 示 す 断 面 図 で あ る

【 図 1 5 a 】本発明の実施例 2 による薄膜トランジスタ基板の製造工程示す断面図である

【 図 1 5 b 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 示 す 断 面 図 で あ る

【図16a】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【図16b】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【図17a】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【図17b】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

```

【図18a】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【 図 1 8 b 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 示 す 断 面 図 で あ る

【 図 1 9 a 】 本 発 明 の 実 施 例 2 に よ る 薄 膜 ト ラ ン ジ ス タ 基 板 の 製 造 工 程 示 す 断 面 図 で あ る

【図19b】本発明の実施例2による薄膜トランジスタ基板の製造工程示す断面図である

【符号の説明】

10

[0070]

1 基板

2、221、601、621、651 下部アルミニウム層

3、223、302、622、652 室化アルミニウム層

4、224、603、624、653 上部アルミニウム層

絶縁膜

6、604、654、664 モリブデン層

1 0

基板素材

2 2

ゲート線

2 4

ゲート線の端部

20

2 6

ゲート電極

2 8

維持電極線

3 0

ゲート絶縁膜

4 0

半導体層

半導体パターン

4 2

5 0

中間層

5 5

接触層パターン

5 6 、 5 7 中間層パターン

5 8

接触層パターン

6 0

導電体層

30

6 2

データ線

6 4

維持蓄電器用導電体

6 5

ソース電極

ドレイン電極

6 6

6 7

導電体パターン

6 8

データ線の端部

7 0

保護膜

72、74、76 コンタクトホール

8 2

画素電極

8 6 接触補助部材

40

1 1 2 、 1 1 4 感光膜パターン

```

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12a】

【図12b】

【図13a】

【図13b】

【図14a】

【図14b】

【図15a】

【図15b】

【図16a】

【図16b】

【図17a】

【図17b】

【図18a】

【図18b】

【図19a】

【図19b】

# フロントページの続き

(72) 発明者 李 制 勳

大韓民國ソウル特別市陽川區木4洞724-12デイルヴィラ#401

(72)発明者 趙 範 錫

大韓民國ソウル特別市永登浦區大林3洞607-1コロンアパ-ト#101-2402

(72)発明者 鄭 敞 午

大韓民國京畿道水原市霊通區網浦洞エルジーヴィレッジ#201-203

F ターム(参考) 2H092 JA24 JA37 JA41 JB22 JB31 JB56 KB04 NA13 NA28

4M104 AA01 AA08 AA09 BB02 BB36 BB38 CC01 CC05 DD15 DD17

DD22 DD42 DD64 DD65 FF09 FF18 FF21 GG08 HH03 HH05

HH08 HH13

5F033 HH08 HH20 HH32 HH38 JJ01 JJ38 KK08 KK20 KK32 LL09

MM08 MM13 MM17 PP16 QQ08 QQ09 QQ10 QQ11 QQ19 QQ21

QQ37 QQ73 RR01 RR06 RR11 VV06 VV15 WW00 WW02 WW04

XX02 XX14 XX16 XX20 XX24 XX28

5F110 AA26 BB01 CC07 EE01 EE02 EE03 EE04 EE06 EE15 EE44

FF03 FF29 GG02 GG15 GG25 GG44 HK01 HK03 HK04 HK05

HK09 HK16 HK22 HK25 HK34 HL07 HL22 NN02 NN22 NN24

NN27 NN28 NN35 NN36 NN73 QQ09