## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-268794 (P2008-268794A)

(43) 公開日 平成20年11月6日(2008.11.6)

| <b>GO9G 3/28 (2006.01)</b> GO9G 3/28 H 5CO8O<br><b>GO9G 3/20 (2006.01)</b> GO9G 3/20 622M 5C58O        |      |

|--------------------------------------------------------------------------------------------------------|------|

| CAAC 2/20 /2006 01)                                                                                    |      |

| <b>GO9G 3/20 (2006.01)</b> GO9G 3/20 622M 5C58O                                                        |      |

| GO9G 3/20 641E                                                                                         |      |

| G O 9 G 3/28 J                                                                                         |      |

| GO9G 3/20 622C                                                                                         |      |

| 審査請求 未請求 請求項の数 2 OL (全 15 頁) 最終頁                                                                       | 頁に続く |

| (21) 出願番号 特願2007-115180 (P2007-115180) (71) 出願人 000005821 (22) 出願日 平成19年4月25日 (2007. 4. 25) 松下電器産業株式会社 |      |

| 大阪府門真市大字門真1006番地<br>  (74) 代理人 100097445                                                               |      |

弁理士 岩橋 文雄

(74) 代理人 100109667

弁理士 内藤 浩樹

(74)代理人 100109151

弁理士 永野 大介

(72) 発明者 中村 信彦

大阪府門真市大字門真1006番地 松下

電器産業株式会社内

Fターム(参考) 5C080 AA05 BB05 DD05 DD09 DD22

FF07 FF12 HH04 HH06 JJ02 JJ03 JJ04 JJ06

最終頁に続く

(54) 【発明の名称】プラズマディスプレイ装置の駆動方法

### (57)【要約】

【課題】スパークやショートを生じる恐れがなく、壁電 荷の減少を防ぎ安定した書込み放電を発生させることが でき、かつ走査電極群のそれぞれに対応した走査電極駆 動回路の一部を共有化して回路構成を簡略化したプラズ マディスプレイ装置の駆動方法を提供する。

【解決手段】第1走査電極群に属する走査電極で書込み 放電を発生させる第1書込み期間に第3スイッチング素 子をオフにして第1走査電極駆動部の基準電圧と第2走 査電極駆動部の基準電圧とに異なる電圧を与え、第2走 査電極群に属する走査電極で書込み放電を発生させる第 2書込み期間に第3スイッチング素子をオンにして第1 走査電極駆動部の基準電圧と第2走査電極駆動部の基準 電圧とに共通の電圧を与え、複数の走査電極に維持パル スを印加して放電セルで維持放電を発生させる維持期間 に第3スイッチング素子もオンにする。

【選択図】図6

#### 【特許請求の範囲】

### 【請求項1】

複数の走査電極を有し複数の放電セルを配置したプラズマディスプレイパネルを用いたプラズマディスプレイ装置の駆動方法であって、

前記プラズマディスプレイ装置は、前記複数の走査電極を第1走査電極群と第2走査電極群とに分け、前記第1走査電極群に属する走査電極を駆動する第1走査電極駆動部と、前記複数の走査電極に印加する維持パルスを発生させる維持パルス発生部と、前記第1走査電極駆動部の基準電圧に前記維持パルスを重畳する第1スイッチング素子と、前記第2走査電極駆動部の基準電圧に前記維持パルスを重畳する第2スイッチング素子と、前記第1走査電極駆動部の基準電圧と前記第2走査電極駆動部の基準電圧と前記第2走査電極駆動部の基準電圧とを接続する第3スイッチング素子とを備え、

前記放電セルで初期化放電を発生させる初期化期間と、前記第1走査電極群に属する走査電極で書込み放電を発生させる第1書込み期間と、前記第2走査電極群に属する走査電極で書込み放電を発生させる第2書込み期間と、前記複数の走査電極に前記維持パルスを印加して前記放電セルで維持放電を発生させる維持期間とを有するサブフィールドを複数配置して1フィールド期間を構成し、

前記第1書込み期間に第3スイッチング素子をオフにして、前記第1走査電極駆動部の基準電圧と前記第2走査電極駆動部の基準電圧とに異なる電圧を与え、

前記第2書込み期間に第3スイッチング素子をオンにして、前記第1走査電極駆動部の基準電圧と前記第2走査電極駆動部の基準電圧とに共通の電圧を与え、

前記維持期間に第1スイッチング素子および第2スイッチング素子をオンにして、前記第1走査電極駆動部の基準電圧と前記第2走査電極駆動部の基準電圧とに前記維持パルスを 重畳するとともに、第3スイッチング素子もオンにすることを特徴とするプラズマディス プレイ装置の駆動方法。

### 【請求項2】

前記初期化期間に第3スイッチング素子をオンにすることを特徴とする請求項1に記載の プラズマディスプレイ装置の駆動方法。

【発明の詳細な説明】

#### 【技術分野】

[0001]

本発明は、プラズマディスプレイパネルを用いたプラズマディスプレイ装置の駆動方法に関する。

# 【背景技術】

[0002]

プラズマディスプレイパネル(以下、「パネル」と略記する)として代表的な交流面放電型パネルは、対向配置された前面板と背面板との間に多数の放電セルが形成されている

# [0003]

前面板には走査電極と維持電極とからなる表示電極対がガラス製の前面基板上に互いに平行に複数対形成され、背面板にはデータ電極がガラス製の背面基板上に平行に複数形成されている。そして、表示電極対とデータ電極とが立体交差するように前面板と背面板とが対向配置されて密封され、内部の放電空間には放電ガスが封入されている。ここで表示電極対とデータ電極との対向する部分に放電セルが形成される。

## [0004]

パネルを駆動する方法としては、サブフィールド法、すなわち、1フィールド期間を複数のサブフィールドに分割した上で、発光させるサブフィールドの組み合わせによって階調表示を行う方法が一般に用いられている。各サブフィールドは、初期化期間、書込み期間および維持期間を有する。初期化期間では初期化放電を発生し、続く書込み動作に必要な壁電荷を各電極上に形成する。書込み期間では、走査電極のそれぞれに走査パルスを順

10

20

30

40

次印加するとともに表示を行うべき放電セルのデータ電極に選択的に書込みパルスを印加して書込み放電を発生させる。そして維持期間では、表示電極対に交互に維持パルスを印加し、書込み放電を起こした放電セルで維持放電を発生させ発光させることにより画像表示を行う。

### [00005]

しかしサブフィールド法を用いてパネルを駆動する場合に、走査電極に走査パルスを印加しなくてもデータ電極に書込みパルスを印加するだけで書込み動作に必要な壁電荷が減少し、正常な書込み放電を発生しないことがあった。この課題を解決するために、例えば特許文献1には、走査電極を4つの走査電極群に分割するとともに、各走査電極群に属する走査電極に走査パルスを順次印加する4つの期間に書込み期間を分割し、走査パルスを印加しない走査電極群には、走査パルスを印加する走査電極群よりも高い電圧を印加する駆動方法が開示されている。

【特許文献1】特開2003-43989号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

しかしながら、上記の駆動方法によれば、隣り合う走査電極の電圧差が過大となるタイミングが生じ、パネルの電極端子間やプリント基板の配線パターン間でスパークが発生する、またはマイグレーションによりパネルの走査電極引き出し部分でショートする等の可能性があった。また、走査電極群のそれぞれに対応した走査電極駆動回路から駆動電圧が供給されるので、走査電極群毎に駆動電圧波形にわずかな差異が生じ、走査電極群の境界に対応する画像表示領域に輪郭が発生して画像表示品質が低下する等の課題があった。さらに走査電極群のそれぞれに対応した走査電極駆動回路を独立に設けるため回路規模が大きくなり、それらの制御も複雑になるといった課題があった。

[00007]

本発明はこれらの課題に鑑みてなされたものであり、スパークやショートを生じる恐れがなく、壁電荷の減少を防ぎ安定した書込み放電を発生させることができ、かつ走査電極群のそれぞれに対応した走査電極駆動回路の一部を共有化して回路構成を簡略化したプラズマディスプレイ装置の駆動方法を提供することを目的とする。

【課題を解決するための手段】

[0008]

本 発 明 は 、 複 数 の 走 査 電 極 を 有 し 複 数 の 放 電 セ ル を 配 置 し た パ ネ ル を 用 い た プ ラ ズ マ デ ィスプレイ装置の駆動方法であって、プラズマディスプレイ装置は、複数の走査電極を第 1走査電極群と第2走査電極群とに分け、第1走査電極群に属する走査電極を駆動する第 1走査電極駆動部と、第2走査電極群に属する走査電極を駆動する第2走査電極駆動部と 複数の走査電極に印加する維持パルスを発生させる維持パルス発生部と、第1走査電極 駆 動 部 の 基 準 電 圧 に 維 持 パ ル ス を 重 畳 す る 第 1 ス イ ッ チ ン グ 素 子 と 、 第 2 走 査 電 極 駆 動 部 の基準電圧に維持パルスを重畳する第2スイッチング素子と、第1走査電極駆動部の基準 電圧と第2走査電極駆動部の基準電圧とを接続する第3スイッチング素子とを備え、放電 セルで初期化放電を発生させる初期化期間と、第1走査電極群に属する走査電極で書込み 放電を発生させる第1書込み期間と、第2走査電極群に属する走査電極で書込み放電を発 生 さ せ る 第 2 書 込 み 期 間 と 、 複 数 の 走 査 電 極 に 維 持 パ ル ス を 印 加 し て 放 電 セ ル で 維 持 放 電 を 発 生 さ せ る 維 持 期 間 と を 有 す る サ ブ フ ィ ー ル ド を 複 数 配 置 し て 1 フ ィ ー ル ド 期 間 を 構 成 し、第1書込み期間に第3スイッチング素子をオフにして、第1走査電極駆動部の基準電 圧と第2走査電極駆動部の基準電圧とに異なる電圧を与え、第2書込み期間に第3スイッ チング素子をオンにして、第1走査電極駆動部の基準電圧と第2走査電極駆動部の基準電 圧とに共通の電圧を与え、維持期間に第1スイッチング素子および第2スイッチング素子 をオンにして、第1走査電極駆動部の基準電圧と第2走査電極駆動部の基準電圧とに維持 パルスを重畳するとともに、第3スイッチング素子もオンにすることを特徴とする。この 方法により、スパークやショートを生じる恐れがなく、壁電荷の減少を防ぎ安定した書込 10

20

30

40

10

20

30

40

50

み放電を発生させることができ、かつ走査電極群のそれぞれに対応した走査電極駆動回路の一部を共有化して回路構成を簡略化したプラズマディスプレイ装置の駆動方法を提供することができる。

#### [0009]

また本発明のプラズマディスプレイ装置の駆動方法は、初期化期間に第3スイッチング 素子をオンにしてもよい。

#### 【発明の効果】

## [0010]

本発明によれば、スパークやショートを生じる恐れがなく、壁電荷の減少を防ぎ安定した書込み放電を発生させることができ、かつ走査電極群のそれぞれに対応した走査電極駆動回路の一部を共有化して回路構成を簡略化したプラズマディスプレイ装置の駆動方法を提供することが可能となる。

# 【発明を実施するための最良の形態】

## [0011]

以下、本発明の実施の形態におけるパネルの駆動方法およびプラズマディスプレイ装置について、図面を用いて説明する。

### [0012]

#### (実施の形態)

図1は、本発明の実施の形態におけるパネル10の構造を示す分解斜視図である。ガラス製の前面基板21上には、走査電極22と維持電極23とからなる表示電極対24が複数形成されている。そして走査電極22と維持電極23とを覆うように誘電体層25が形成され、その誘電体層25上に保護層26が形成されている。背面基板31上にはデータ電極32が複数形成され、データ電極32を覆うように誘電体層33が形成され、さらにその上に井桁状の隔壁34が形成されている。そして、隔壁34の側面および誘電体層33上には赤色、緑色および青色の各色に発光する蛍光体層35が設けられている。

### [0013]

これら前面基板 2 1 と背面基板 3 1 とは、微小な放電空間を挟んで表示電極対 2 4 とデータ電極 3 2 とが交差するように対向配置され、その外周部をガラスフリット等の封着材によって封着されている。そして放電空間には、例えばネオンとキセノンの混合ガスが放電ガスとして封入されている。放電空間は隔壁 3 4 によって複数の区画に仕切られており、表示電極対 2 4 とデータ電極 3 2 とが交差する部分に放電セルが形成されている。そしてこれらの放電セルが放電、発光することにより画像が表示される。

#### [0014]

なお、パネル10の構造は上述したものに限られるわけではなく、例えばストライプ状の隔壁を備えたものであってもよい。

#### [0015]

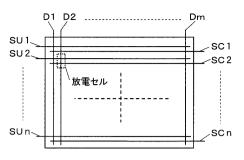

図 2 は、本発明の実施の形態におけるパネル 1 0 の電極配列図である。パネル 1 0 には、行方向に長い n 本 ( n は偶数 ) の走査電極 S C 1 ~ S C n (図 1 の走査電極 2 2 ) および n 本の維持電極 S U 1 ~ S U n (図 1 の維持電極 2 3 ) が配列され、列方向に長い m 本のデータ電極 D 1 ~ D m (図 1 のデータ電極 3 2 ) が配列されている。そして、 1 対の走査電極 S C i (i = 1 ~ n) および維持電極 S U i と 1 つのデータ電極 D j (j = 1 ~ m) とが交差した部分に放電セルが形成され、放電セルは放電空間内に m × n 個形成されている。

# [0016]

なお、本実施の形態においてはnを偶数とし、奇数番目の走査電極SC1、SC3、・・、SCn・1が第1走査電極群に属し、偶数番目の走査電極SC2、SC4、・・・、SCnが第2走査電極群に属するものとして説明する。

#### [0017]

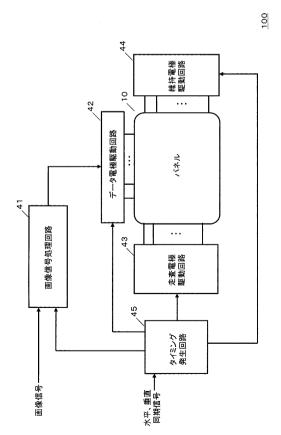

図3は、本発明の実施の形態におけるプラズマディスプレイ装置100の回路ブロック図である。プラズマディスプレイ装置100は、パネル10、画像信号処理回路41、デ

ータ電極駆動回路42、走査電極駆動回路43、維持電極駆動回路44、タイミング発生 回路45および各回路ブロックに必要な電源を供給する電源部(図示せず)を備えている

## [0018]

画像信号処理回路41は、入力された画像信号をサブフィールド毎の発光・非発光を示す画像データに変換する。データ電極駆動回路42はサブフィールド毎の画像データを各データ電極D1~Dmに対応する信号に変換し各データ電極D1~Dmを駆動する。

### [0019]

タイミング発生回路 4 5 は水平同期信号および垂直同期信号をもとにして各回路ブロックの動作を制御する各種のタイミング信号を発生し、それぞれの回路ブロックへ供給する。走査電極駆動回路 4 3 はタイミング信号にもとづいて各走査電極 S C 1 ~ S C n をそれぞれ駆動し、維持電極駆動回路 4 4 はタイミング信号にもとづいて維持電極 S U 1 ~ S U n を駆動する。

# [0020]

次に、パネル10を駆動するための駆動電圧波形とその動作について説明する。プラズマディスプレイ装置100は、サブフィールド法、すなわち1フィールド期間を複数のサブフィールドに分割し、サブフィールド毎に各放電セルの発光・非発光を制御することによって階調表示を行う。それぞれのサブフィールドは初期化期間、書込み期間および維持期間を有する。初期化期間では初期化放電を発生し、続く書込み放電に必要な壁電荷を各電極上に形成する。書込み期間では、発光させるべき放電セルで選択的に書込み放電を発生し壁電荷を形成する。そして維持期間では、書込み放電を発生した放電セルで維持放電を発生させて発光させる。

# [0021]

なお、本実施の形態においては、書込み期間を、第1走査電極群に属する走査電極のそれぞれに走査パルスを順次印加する第1書込み期間と、第2走査電極群に属する走査電極のそれぞれに走査パルスを順次印加する第2書込み期間とに分割する。そして、第1走査電極群に属する走査電極は奇数番目の走査電極SC1、SC3、・・・、SCn・1であり、第2走査電極群に属する走査電極は偶数番目の走査電極SC2、SC4、・・・、SCnである。そこで以下、第1書込み期間を「奇数期間」、第2書込み期間を「偶数期間」と略記する。

#### [0022]

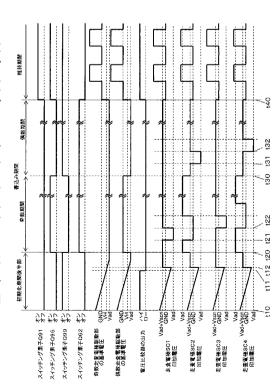

次に、パネル10を駆動するための駆動電圧波形とその動作について説明する。図4は本発明の実施の形態におけるパネル10の各電極に印加する駆動電圧波形を示す図である。1フィールド期間は、例えば10のサブフィールドで構成されているが、図4には2つのサブフィールドの駆動電圧波形を示している。

#### [0023]

第1サブフィールドの初期化期間の前半部では、データ電極D1~Dmに書込みパルス電圧Vwを印加し、維持電極SU1~SUnに電圧0(V)を印加し、走査電極SC1~SCnには、維持電極SU1~SUnに対して放電開始電圧以下の電圧Vi1から、放電開始電圧を超える電圧Vi2に向かって緩やかに上昇する傾斜波形電圧を印加する。この傾斜波形電圧が上昇する間に、走査電極SC1~SCnと維持電極SU1~SUn、データ電極D1~Dmとの間でそれぞれ微弱な初期化放電が起こる。そして、走査電極SC1~SCn上に負の壁電圧が蓄積されるとともに、データ電極D1~Dm上および維持電極SU1~SUn上には正の壁電圧が蓄積される。ここで、電極上の壁電圧とは電極を覆う誘電体層上、保護層上、蛍光体層上等に蓄積された壁電荷により生じる電圧を表す。

# [0024]

初期化期間の後半部では、データ電極 D 1 ~ D m に電圧 0 ( V )を印加し、維持電極 S U 1 ~ S U n に正の電圧 V e 1を印加し、走査電極 S C 1~ S C n には、維持電極 S U 1~ S U n に対して放電開始電圧以下となる電圧 V i 3 から放電開始電圧を超える電圧 V i 4 に向かって緩やかに下降する傾斜波形電圧を印加する。この間に、走査電極 S C 1~ S

10

20

30

40

Cnと維持電極SU1~SUn、データ電極D1~Dmとの間でそれぞれ微弱な初期化放電が起こる。そして、走査電極SC1~SCn上の負の壁電圧および維持電極SU1~SUn上の正の壁電圧が弱められ、データ電極D1~Dm上の正の壁電圧は書込み動作に適した値に調整される。

### [0025]

なお、1フィールドを構成するサブフィールドのうち、いくつかのサブフィールドでは初期化期間の前半部を省略してもよく、その場合には、直前のサブフィールドで維持放電を行った放電セルに対して選択的に初期化動作が行われる。図4には、第1サブフィールドの初期化期間では前半部および後半部を有する初期化動作、第2サブフィールドおよびそれ以降の初期化期間では後半部のみを有する初期化動作を行う駆動電圧波形を示した。

[ 0 0 2 6 ]

続く書込み期間の奇数期間では、維持電極SU1~SUnに電圧Ve2を印加し、奇数番目の走査電極SC1、SC3、・・・、SCn-1のそれぞれには第2の電圧Vs2を、偶数番目の走査電極SC2、SC4、・・・、SCnのそれぞれには第4の電圧Vs4を印加する。ここで、第4の電圧Vs4は第2の電圧Vs2より高い電圧である。

#### [0027]

次に、1番目の走査電極SC1に負の走査パルスを印加するために走査パルス電圧Vadを印加する。そして、データ電極D1~Dmのうち1行目に発光させるべき放電セルのデータ電極Dk(k=1~m)に正の書込みパルス電圧Vwを印加する。このとき本実施の形態においては、走査電極SC1に隣接する走査電極、すなわち2番目の走査電極SC2に第4の電圧Vs4より低い第3の電圧Vs3を印加する。これは隣接する走査電極SC1と走査電極SC2との間に過大な電圧差が印加されるのを防ぐためである。

[0028]

すると書込みパルス電圧Vwを印加した放電セルのデータ電極Dk上と走査電極SC1上との交差部の電圧差は、外部印加電圧の差(Vw・Vad)にデータ電極Dk上の壁電圧と走査電極SC1上の壁電圧の差とが加算されたものとなり放電開始電圧を超える。そして、データ電極Dkと走査電極SC1との間および維持電極SU1と走査電極SC1との間に書込み放電が起こり、走査電極SC1上に正の壁電圧が蓄積され、維持電極SU1上に負の壁電圧が蓄積され、データ電極Dk上にも負の壁電圧が蓄積される。このようにして、1行目に発光させるべき放電セルで書込み放電を起こして各電極上に壁電圧を蓄積する書込み動作が行われる。一方、書込みパルス電圧Vwを印加しなかったデータ電極D1~Dmと走査電極SC1との交差部の電圧は放電開始電圧を超えないので、書込み放電は発生しない。

[0029]

次に、3番目の走査電極SC3に走査パルス電圧Vadを印加するとともに、データ電極D1~Dmのうち3行目に発光させるべき放電セルのデータ電極Dkに正の書込みパルス電圧Vwを印加する。このとき走査電極SC3に隣接する2番目の走査電極SC2および4番目の走査電極SC4にも第3の電圧Vs3を印加する。するとその放電セルのデータ電極Dkと走査電極SC3との間および維持電極SU3と走査電極SC3との間に書込み放電が起こり、各電極上に壁電圧を蓄積する書込み動作が行われる。

[0030]

以下、奇数番目の走査電極SC5、SC7、・・・、SCn-1についても同様に書込み動作を行う。そしてこのとき書込み動作を行う奇数番目の走査電極SCp+1(p=偶数、1<p<n)に隣接する偶数番目の走査電極SCpおよび走査電極SCp+2にも第3の電圧Vs3を印加する。

# [0031]

続く書込み期間の偶数期間では、奇数番目の走査電極SC1、SC3、・・・、SCn-1に第2の電圧Vs2を印加したまま、偶数番目の走査電極SC2、SC4、・・・、SCnにも第2の電圧Vs2を印加する。

# [0032]

30

10

20

40

次に、2番目の走査電極SC2に負の走査パルスを印加するために走査パルス電圧Vadを印加するとともに、データ電極D1~Dmのうち2行目に発光させるべき放電セルのデータ電極Dkに正の書込みパルス電圧Vwを印加する。するとその放電セルのデータ電極Dkと走査電極SC2との交差部の電圧差は放電開始電圧を超え、2行目に発光させるべき放電セルで書込み放電を起こして各電極上に壁電圧を蓄積する書込み動作が行われる

#### [0033]

次に、4番目の走査電極SC4に走査パルス電圧Vadを印加するとともに、4行目に発光させるべき放電セルのデータ電極Dkに正の書込みパルス電圧Vwを印加する。するとその放電セルで書込み放電が起きる。

[0034]

以下同様に、偶数番目の走査電極SC6、SC8、・・・、SCnについても同様に走査パルス電圧Vadを印加して書込み動作を行う。

## [0035]

このように駆動することで、電圧(Vs3-Vad)を超える電圧差を隣接する走査電極間に印加することはないので、絶縁破壊やマイグレーションを発生する恐れがない。また奇数期間において奇数番目の走査電極の書込み動作をすでに終えているため、偶数期間において奇数番目の走査電極の壁電荷がたとえ減少したとしても、画像表示品質を損なう恐れがない。

# [0036]

続く維持期間では、まず走査電極SC1~SCnに正の維持パルス電圧Vmを印加するとともに維持電極SU1~SUnに電圧0(V)を印加する。すると書込み放電を起こした放電セルでは、走査電極SCi上と維持電極SUi上との電圧差が維持パルス電圧Vmに走査電極SCi上の壁電圧と維持電極SUi上の壁電圧との差が加算されたものとなり放電開始電圧を超える。そして、走査電極SCiと維持電極SUiとの間に維持放電が起こり、このとき発生した紫外線により蛍光体層35が発光する。そして走査電極SCi上に負の壁電圧が蓄積され、維持電極SUi上に正の壁電圧が蓄積される。さらにデータ電極Dk上にも正の壁電圧が蓄積される。書込み期間において書込み放電が起きなかった放電セルでは維持放電は発生せず、初期化期間の終了時における壁電圧が保たれる。

## [0037]

続いて、走査電極SC1~SCnには電圧0(V)を、維持電極SU1~SUnには維持パルス電圧Vmをそれぞれ印加する。すると、維持放電を起こした放電セルでは、維持電極SUi上と走査電極SCi上との電圧差が放電開始電圧を超えるので再び維持電極SUiと走査電極SCiとの間に維持放電が起こり、維持電極SUi上に負の壁電圧が蓄積され走査電極SCi上に正の壁電圧が蓄積される。以降同様に、走査電極SC1~SCnと維持電極SU1~SUnとに交互に輝度重みに応じた数の維持パルスを印加し、表示電極対24の電極間に電位差を与えることにより、書込み期間において書込み放電を起こした放電セルで維持放電が継続して行われる。

# [0038]

そして、維持期間の最後には電圧Vrに向かって緩やかに上昇する傾斜波形電圧を走査電極SC1~SCnに印加して、データ電極Dk上の正の壁電圧を残したまま、走査電極SCi上および維持電極SUi上の壁電圧を弱めている。こうして維持期間における維持動作が終了する。

# [0039]

次に、走査電極駆動回路43の詳細な構成について説明する。なお本実施の形態においては、第2の電圧Vs2と走査パルス電圧Vadとの差が、第4の電圧Vs4と第3の電圧Vs3との差に等しいとして説明する。この電圧の差を以下、電圧Vscnと記す。すなわち、(Vs2-Vad)=(Vs4-Vs3)=Vscnである。

## [0040]

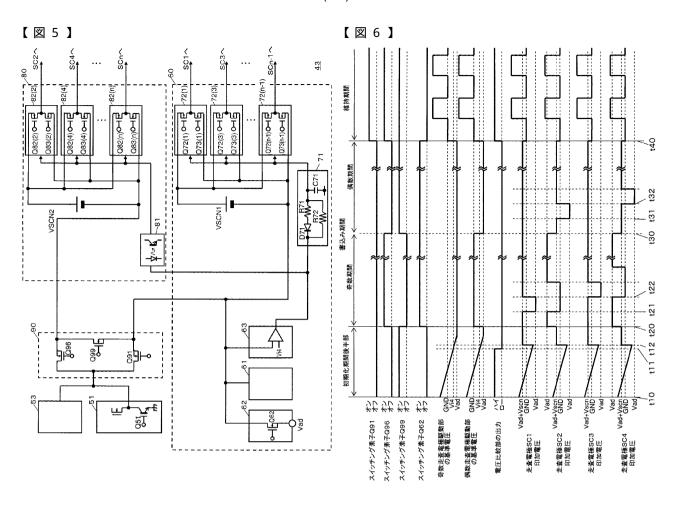

図5は、本発明の実施の形態における走査電極駆動回路43の回路図である。走査電極

10

20

30

40

駆動回路43は、維持パルス発生部51、上り傾斜電圧発生部53、第1走査電極駆動部60、第2走査電極駆動部80、複合スイッチ部90を備えている。なお、本実施の形態においては、第1走査電極駆動部60は奇数番目の走査電極を駆動するので、以下「奇数走査電極駆動部60」と記し、第2走査電極駆動部80は偶数番目の走査電極を駆動するので、以下「偶数走査電極駆動部80」と記する。

#### [0041]

維持パルス発生部51は、維持パルス電圧Vmを出力するスイッチング素子、電圧0(V)を出力するスイッチング素子および電力を回収するための回路を備え、維持期間において走査電極SC1~SCnに印加する維持パルスを発生する。図5には電圧0(V)を出力するスイッチング素子Q51のみを示している。上り傾斜電圧発生部53は初期化期間の前半部および維持期間の最後に走査電極SC1~SCnに印加する緩やかに上昇する傾斜波形電圧を発生する。

[0042]

奇数走査電極駆動部60は、下り傾斜電圧発生部61と、走査パルス電圧印加部62と、電圧比較部63と、信号遅延部71と、第1フローティング電源VSCN1(以下、単に「電源VSCN1」と略記する)と、第1出力部(以下、単に「出力部」と略記する)72(1)、72(3)、・・・、72(n-1)とを備えている。

[0043]

下り傾斜電圧発生部61は、初期化期間の後半部において奇数走査電極駆動部60の基準電圧を緩やかに低下させる。走査パルス電圧印加部62はスイッチング素子Q62を有し、書込み期間において奇数走査電極駆動部60の基準電圧を走査パルス電圧Vadに接続する。

[0044]

電圧比較部63はコンパレータを有し、初期化期間の後半部において奇数走査電極駆動部60の基準電圧と電圧Vi4とを比較する。

[0045]

信号遅延部71は抵抗R71、R72、ダイオードD71、コンデンサC71を有し、信号伝達部81の遅延時間と同等の時間だけ電圧比較部63の出力を遅延して奇数走査電極駆動部60に伝達する。

[0046]

電源 V S C N 1 は電圧 V S C n の電源であり、その低電圧側が奇数走査電極駆動部 6 0 の基準電圧に接続されている。出力部 7 2 (1)、 7 2 (3)、・・・、 7 2 (n - 1) のそれぞれは、電源 V S C N 1 の低電圧側の電圧または高圧側の電圧を奇数番目の走査電極 S C 1、 S C 3、・・・、 S C n - 1 のそれぞれに印加する。出力部 7 2 (1)、 7 2 (3)、・・・、 7 2 (n - 1)は、電源 V S C N 1 の高圧側の電圧を出力するスイッチング素子 Q 7 2 (1)、 Q 7 2 (3)、・・・、 Q 7 2 (n - 1)と、電源 V S C N 1 の低圧側の基準電圧を出力するスイッチング素子 Q 7 3 (1)、 Q 7 3 (3)、・・・、 Q 7 3 (n - 1)とを有する。

[0047]

偶数走査電極駆動部80は、信号伝達部81と、第2フローティング電源VSCN2(以下、単に「電源VSCN2」と略記する)と、第2出力部(以下、単に「出力部」と略記する)82(2)、82(4)、・・・、82(n)を備えている。

[0048]

信号伝達部 8 1 はフォトカプラを有し、電圧比較部 6 3 の出力を偶数走査電極駆動部 8 0 に伝達する。

[0049]

電源 V S C N 2 は電圧 V s c n の電源であり、その低電圧側が偶数走査電極駆動部 8 0 の基準電圧に接続されている。出力部 8 2 (2)、8 2 (4)、・・・、8 2 (n)のそれぞれは、電源 V S C N 2 の低電圧側の電圧または高圧側の電圧を偶数番目の走査電極 S C 2、S C 4、・・・、S C n のそれぞれに印加する。出力部 8 2 (2)、8 2 (4)、

10

20

30

40

10

20

30

40

50

・・・、82(n)は、電源VSCN2の高圧側の電圧を出力するスイッチング素子Q82(2)、Q82(4)、・・・、Q82(n)と、電源VSCN2の低圧側の基準電圧を出力するスイッチング素子Q83(2)、Q83(4)、・・・、Q83(n)とを有する。

# [0050]

複合スイッチ部90は、維持パルス発生部51または上り傾斜電圧発生部53の出力を奇数走査電極駆動部60の基準電圧に重畳する第1スイッチング素子Q91と、維持パルス発生部51または上り傾斜電圧発生部53の出力を偶数走査電極駆動部80の基準電圧に重畳する第2スイッチング素子Q96と、奇数走査電極駆動部60の基準電圧と偶数走査電極駆動部80の基準電圧とを接続する第3スイッチング素子Q99とを備える。なお、第1スイッチング素子、第2スイッチング素子、第3スイッチング素子のそれぞれを、以下、単に「スイッチング素子」と略記する。

#### [0051]

なお、電源VSCN1、電源VSCN2は、例えばDC-DCコンバータ等を用いて構成してもよいが、ダイオードとコンデンサを有するブートストラップ回路を用いて簡単に構成することができる。本実施の形態においては、電源VSCN1および電源VSCN2の電圧はともに電圧Vscnであるので、第2の電圧Vs2は、Vs2=(Vad+Vscn)であり、第4の電圧Vs4は、Vs4=(Vs3+Vscn)である。また、走査パルス電圧Vad=-140(V)、電圧Vscn=150(V)、第3の電圧Vs3=0(V)である。しかしこれらの電圧は一例であり、パネルの特性等に合わせて最適な値に設定することが望ましい。

#### [0052]

本実施の形態においては、図5に示したように、走査パルス電圧印加部62、下り傾斜電圧発生部61および電圧比較部63は、奇数走査電極駆動部60の基準電圧に重畳するように設けられているが、これらの機能を持つ回路を偶数走査電極駆動部80には設けていない。しかし本実施の形態においては、奇数走査電極駆動部60の基準電圧と偶数走査電極駆動部80の基準電圧とを接続するスイッチング素子Q99を介して、初期化期間の後半部において偶数走査電極駆動部80の基準電圧を緩やかに低下させ、書込み期間において偶数走査電極駆動部80の基準電圧に走査パルス電圧Vadを重畳している。このように構成することにより、奇数走査電極駆動部60および偶数走査電極駆動部80の両方に走査パルス電圧印加部、下り傾斜電圧発生部および電圧比較部を設ける必要がないので、回路構成を簡略化することができる。

#### [0053]

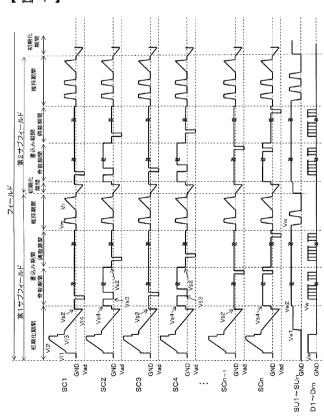

次に、走査電極駆動回路43の動作について説明する。図6は、本発明の実施の形態における走査電極駆動回路43の動作を示す図であり、初期化期間の後半部から維持期間にかけてのタイミングチャートである。

#### [0054]

初期化期間の後半部では、時刻 t 1 0 において、スイッチング素子 Q 9 1 、 Q 9 6 をオフにして、維持パルス発生部 5 1 および上り傾斜電圧発生部 5 3 の出力を奇数走査電極駆動部 6 0 および偶数走査電極駆動部 8 0 の基準電圧から切り離す。また、スイッチング素子 Q 6 2 をオフにして、走査パルス電圧 V a d を奇数走査電極駆動部 6 0 の基準電圧から切り離す。そしてスイッチング素子 Q 9 9 をオンにして、奇数走査電極駆動部 6 0 の基準電圧と偶数走査電極駆動部 8 0 の基準電圧とを接続する。

# [0055]

次に、下り傾斜電圧発生部 6 1 を動作させて、奇数走査電極駆動部 6 0 および偶数走査電極駆動部 8 0 の基準電圧を緩やかに低下させる。このとき出力部 7 2 ( 1 )、 7 2 ( 3 )、・・・、 7 2 ( n - 1 )、 8 2 ( 2 )、 8 2 ( 4 )、・・・、 8 2 ( n ) は、電源 V S C N 1 および電源 V S C N 2 の高圧側の電圧を出力するスイッチング素子 Q 7 2 ( 1 )、 Q 7 2 ( 3 )、・・・、 Q 7 2 ( n - 1 )、 Q 8 2 ( 2 )、 Q 8 2 ( 4 )、・・・、 Q 7 3 8 2 ( n )をオフ、低圧側の基準電圧を出力するスイッチング素子 Q 7 3 ( 1 )、 Q 7 3

(3)、・・・、Q73(n-1)、Q83(2)、Q83(4)、・・・、Q83(n)をオンさせて、走査電極SC1~SCnに下り傾斜波形電圧を印加する。

# [0056]

時刻 t 1 1 において、奇数走査電極駆動部 6 0 の基準電源が電圧 V i 4 以下になると電圧比較部 6 3 の出力はローレベルとなる。そしてその信号は信号伝達部 8 1 を介して偶数走査電極駆動部 8 0 の出力部 8 2 ( 2 )、8 2 ( 4 )、・・・、8 2 ( n )に伝えられるとともに、信号遅延部 7 1 を介して奇数走査電極駆動部 6 0 の出力部 7 2 ( 1 )、7 2 ( 3 )、・・・、7 2 ( n - 1 )にも伝えられる。

### [0057]

そして時刻 t 1 2 において、電源 V S C N 1 および電源 V S C N 2 の高圧側の電圧を出力するスイッチング素子 Q 7 2 (1)、 Q 7 2 (3)、・・・、 Q 7 2 (n - 1)、 Q 8 2 (2)、 Q 8 2 (4)、・・・、 Q 8 2 (n)をオン、低圧側の基準電圧を出力するスイッチング素子 Q 7 3 (1)、 Q 7 3 (3)、・・・、 Q 7 3 (n - 1)、 Q 8 3 (2)、 Q 8 3 (4)、・・・、 Q 8 3 (n)をオフにして、走査電極 S C 1 ~ S C n に印加する電圧を上昇させる。

#### [0058]

次に書込み期間の奇数期間には、時刻 t 2 0 において、スイッチング素子Q 6 2 をオンにして、奇数走査電極駆動部 6 0 の基準電圧を走査パルス電圧 V a d に固定する。したがって、奇数番目の走査電極SС1、SС3、・・・、SСn - 1 には第 2 の電圧(V a d + V s c n)が印加される。またスイッチング素子Q 9 9 をオフにするとともにスイッチング素子Q 9 6 をオンにして、維持パルス発生部 5 1 の出力に偶数走査電極駆動部 8 0 の基準電圧を接続する。このとき維持パルス発生部 5 1 のスイッチング素子Q 5 1 はオンにされており、偶数走査電極駆動部 8 0 の基準電圧は第 3 の電圧 0 (V)になる。したがって偶数番目の走査電極SС2、SС4、・・・、SСnには第 4 の電圧(V s 3 + V s c n)が印加される。

# [0059]

そして時刻 t 2 1 において、出力部 7 2 ( 1 ) のスイッチング素子 Q 7 2 ( 1 ) をオフ、スイッチング素子 Q 7 3 ( 1 ) をオンにして、走査電極 S C 1 に走査パルス電圧 V a d を印加する。また出力部 8 2 ( 2 ) のスイッチング素子 Q 8 2 ( 2 ) をオフ、スイッチング素子 Q 8 3 ( 2 ) をオンにして、走査電極 S C 2 に第 3 の電圧 0 ( V ) を印加する。

#### [0060]

次に時刻 t 2 2 において、出力部 7 2 ( 1 )のスイッチング素子 Q 7 2 ( 1 )をオン、スイッチング素子 Q 7 3 ( 1 )をオフに戻し、出力部 7 2 ( 3 )のスイッチング素子 Q 7 2 ( 3 )をオフ、スイッチング素子 Q 7 3 ( 3 )をオンにして、走査電極 S C 3 に走査パルス電圧 V a dを印加する。また出力部 8 2 ( 4 )のスイッチング素子 Q 8 2 ( 4 )をオフ、スイッチング素子 Q 8 3 ( 4 )をオンにして、走査電極 S C 4 に第 3 の電圧 0 ( V )を印加する。

### [0061]

以下、同様にして奇数番目の走査電極SC1、SC3、・・・、SCn-1に走査パルスを順次印加するとともに、走査パルス電圧Vadを印加している走査電極に隣接する走査電極には、第3の電圧0(V)を印加する。

#### [0062]

次に書込み期間の偶数期間には、時刻 t 3 0 において、スイッチング素子Q 9 6 をオフにするとともに、スイッチング素子Q 9 9 をオンにして、偶数走査電極駆動部 8 0 の基準電圧を奇数走査電極駆動部 6 0 の基準電圧に等しい走査パルス電圧 V a d にする。

# [0063]

そして時刻 t 3 1 において、出力部 8 2 ( 2 )のスイッチング素子 Q 8 2 ( 2 )をオフ、スイッチング素子 Q 8 3 ( 2 )をオンにして、走査電極 S C 2 に走査パルス電圧 V a dを印加する。

# [0064]

50

10

20

30

次に時刻 t 3 2 において、出力部 8 2 ( 2 ) のスイッチング素子 Q 8 2 ( 2 ) をオン、スイッチング素子 Q 8 3 ( 2 ) をオフに戻し、出力部 8 2 ( 4 ) のスイッチング素子 Q 8 2 ( 4 ) をオフ、スイッチング素子 Q 8 3 ( 4 ) をオンにして、走査電極 S C 4 に走査パルス電圧 V a d を印加する。

## [0065]

以下、同様にして偶数番目の走査電極SC2、SC4、・・・、SCnに走査パルスを順次印加する。なお、書込み期間において出力部72(1)、72(3)、・・・、72(n・1)、82(2)、82(4)、・・・、82(n)を制御する信号はタイミング発生回路45から供給される。

## [0066]

次の維持期間には、時刻 t 4 0 において、電源 V S C N 1 および電源 V S C N 2 の高圧側の電圧を出力するスイッチング素子Q 7 2 (1)、Q 7 2 (3)、・・・、Q 7 2 (n - 1)、Q 8 2 (2)、Q 8 2 (4)、・・・、Q 8 2 (n)をオフにするとともに、スイッチング素子Q 6 2 をオフにする。そしてスイッチング素子Q 9 1、Q 9 6 をオンにして維持パルス発生部 5 1 の出力を奇数走査電極駆動部 6 0 および偶数走査電極駆動部 8 0 の基準電圧に接続する。このときスイッチング素子Q 9 9 もオンにする。さらに、電源 V S C N 1 および電源 V S C N 2 の低圧側の基準電圧を出力するスイッチング素子Q 7 3 (1)、Q 7 3 (3)、・・・、Q 7 3 (n - 1)、Q 8 3 (2)、Q 8 3 (4)、・・・、Q 8 3 (n)をオンにする。

# [0067]

そしてその後、維持パルス発生部51で発生させた維持パルスをスイッチング素子Q91、スイッチング素子Q73(1)を介して奇数番目の走査電極SC1に印加する。走査電極SC3、・・・、SCn-1についても同様である。また維持パルス発生部51で発生させた維持パルスをスイッチング素子Q96、スイッチング素子Q83(2)を介して偶数番目の走査電極SC2に印加する。走査電極SC4、・・・、SCnについても同様である。

## [0068]

このように、本実施の形態におけるプラズマディスプレイ装置は、走査パルスを印加しない走査電極群には、走査パルスを印加する走査電極群よりも高い電圧を印加して壁電荷の減少を抑制している。また、電圧Vscnを超える電圧差を隣接する走査電極間に印加することはないので、絶縁破壊やマイグレーションを発生する恐れがない。しかも、奇数走査電極駆動部60および偶数走査電極駆動部80の両方に走査パルス電圧印加部、下り傾斜電圧発生部および電圧比較部を設ける必要がないので、回路構成を簡略化することができる。

# [0069]

# [0070]

50

10

20

30

また本実施の形態においては、第1走査電極群に属する走査電極を奇数番目の走査電極SC1、SC3、・・・、SCn-1、第1書込み期間を奇数期間とし、第2走査電極群に属する走査電極を偶数番目の走査電極SC2、SC4、・・・、SCn、第2書込み期間を偶数期間とした。しかし、第1走査電極群に属する走査電極を偶数番目の走査電極SC2、SC4、・・・、SCn、第1書込み期間を偶数期間とし、第2走査電極群に属する走査電極を奇数番目の走査電極SC1、SC3、・・・、SCn-1、第2書込み期間を奇数期間としてもよく、さらにこれらを例えばフィールド毎に切換えてもよい。

## [0071]

なお、本実施の形態において用いた具体的な数値等は単に一例を挙げたに過ぎず、パネルの特性やプラズマディスプレイ装置の仕様等に合わせて、適宜最適な値に設定することが望ましい。

10

【産業上の利用可能性】

## [0072]

本発明は、スパークやショートを生じる恐れがなく、壁電荷の減少を防ぎ安定した書込み放電を発生させることができ、かつ走査電極群のそれぞれに対応した走査電極駆動回路の一部を共有化して回路構成を簡略化できるので、プラズマディスプレイ装置の駆動方法として有用である。

【図面の簡単な説明】

- [0073]

- 【図1】本発明の実施の形態におけるパネルの構造を示す分解斜視図

- 【図2】本発明の実施の形態におけるパネルの電極配列図

- 【 図 3 】 本 発 明 の 実 施 の 形 態 に お け る プ ラ ズ マ デ ィ ス プ レ イ 装 置 の 回 路 ブ ロ ッ ク 図

- 【図4】本発明の実施の形態におけるパネルの各電極に印加する駆動電圧波形を示す図

- 【図5】本発明の実施の形態における走査電極駆動回路の回路図

- 【図6】本発明の実施の形態における走査電極駆動回路の動作を示す図

【符号の説明】

[0074]

- 10 パネル

- 22 走査電極

- 2 3 維持電極

- 2 4 表示電極対

- 3 2 データ電極

- 4 1 画像信号処理回路

- 4 2 データ電極駆動回路

- 43 走査電極駆動回路

- 4 4 維持電極駆動回路

- 4 5 タイミング発生回路

- 5 1 維持パルス発生部

- 53 上り傾斜電圧発生部

- 60 第1走査電極駆動部(奇数走査電極駆動部)

- 6 1 下り傾斜電圧発生部

- 62 走査パルス電圧印加部

- 63 電圧比較部

- 7 1 信号遅延部

- 80 第2走査電極駆動部(偶数走査電極駆動部)

- 8 1 信号伝達部

- 90 複合スイッチ部

- 100 プラズマディスプレイ装置

20

30

【図1】 21 23 24

【図2】

【図3】

10 <

【図4】

フロントページの続き

(51) Int.CI.

F I

G 0 9 G 3/20 6 4 2 A

F ターム(参考) 5C580 AA03 BA01 BA02 BA03 BA09 BA13 BA16 BB20 BB27 BB28 CA06 CB10