# (19) 대한민국특허청(KR) (12) 등록특허공보(B1)

| (51) Int. CI. <sup>6</sup><br>HO4B 3/23 |                                      | (45) 공고일자<br>(11) 등록번호<br>(24) 등록일자 | 2003년01월14일<br>10-0356383<br>2002년09월30일 |  |  |

|-----------------------------------------|--------------------------------------|-------------------------------------|------------------------------------------|--|--|

| (21) 출원번호                               | 10-1996-0703189                      | (65) 공개번호                           | <b>≒</b> 1996−0706721                    |  |  |

| (22) 출원일자<br>번역문제출일자                    | 1996년06월13일<br>1996년06월13일           | (43) 공개일자                           | 1996년 12월09일                             |  |  |

| (86) 국제출원번호                             | PCT/US1994/13775                     | (87) 국제공개번호                         |                                          |  |  |

| (86) 국제출원일자                             | 1994년 12월06일                         | (87) 국제공개일자                         |                                          |  |  |

|                                         |                                      |                                     |                                          |  |  |

| (30) 우선권주장                              | 08/165509 1993년12월13일 [              | 미국(US)                              |                                          |  |  |

| (73) 특허권자                               | 아마티 커뮤니케이션스 코퍼레이션                    |                                     |                                          |  |  |

|                                         | 미합중국, 캘리포니아 94040,<br>303            | 마운틴 뷰, 1975 엘                       | 카미노 리얼 웨스트, 수트                           |  |  |

| (72) 발명자                                | 쵸우 재키 에스                             |                                     |                                          |  |  |

|                                         | 미합중국, 캘리포니아 94040,<br>빙험 죤 에이 씨      | 마운틴 뷰, 333 에스                       | 큐엘라 애비뉴#304                              |  |  |

|                                         | 미합중국, 캘리포니아 94301,<br>플라우워즈 마크 브레드포드 | 팔로 알토, 웹스터 스                        | 트리트 2353                                 |  |  |

|                                         | 미합중국, 캘리포니아 94087,<br>씨오플 죤 엠        | 써니베일, 스프리그 를                        | 코트 1364                                  |  |  |

| (74) 대리인                                | 미합중국, 캘리포니아 95014,<br>강명구            | 쿠퍼티노, 크리크라인                         | ! 드라이브 7879                              |  |  |

| 11 11 71 · OI=11 TI                     |                                      |                                     |                                          |  |  |

심사관: 민혜정

(54) 송신시스템의 클리핑 및 양자화 효과소거 및 소거보상방법, 그리고 이를 이용한 디지털 송신시스템

## 명세서

## 기술분야

본 발명은 디지탈 송신 시스템에 관한 것이며, 특히, 상기 디지탈 송신 시스템의 클리핑 및 양자 효과를 줄이는 것과 관계된다. 비록 상기 발명의 반향 소거기를 포함 하는것과 포함하지 않는 것 모두에 서 어떤 형태의 변조를 사용하는 송신 시스템에 적용될 수 있을지라도, 송신시스템에서 다중반송파 (multicarrier) 변조와 적당한 반향 소거(echo cancellation)를 사용하는 것은 매우 큰 이점을 갖는다.

## 배경기술

- 신호(signal)가 송신기와 수신기를 하이브리드 회로를 통해 연결해주는 두가닥의 도선을 통해 양 방향으로 전달되는 시스템내에 반향 소거기가 갖추어져 있다는 것은 잘 알려져 있다. 하이브리드 회로내 에서 수신기와 균형이 맞지 않게 결합되는 송신기에 의해 전달되는 신호를 실질적으로 완벽히 제거하기 위한 장치에 있어 반향 소거기는 매우 바람직한 장치이다.

- <3> 종래의 반향 소거기는 소거되어져야 할 신호에서 비-선형 왜곡에 대해서는 보상하지 않는다. 예를 들자면, 비-선형 왜곡은 양자화 및 클리핑의 결과로서, 아날로그와 디지탈 신호 사이의 변환에서 발생한다.

- 상기 관점에 대해, 1988년 5월 24일 등록되고 "디지탈화 되어질 신호의 비선형 왜곡을 보상하기 위한 장치 및 상기 장치로 구성되는 반향 소기기"라는 제목을 갖는 Tol et al. 미국특허 No. 4,746,902 에서는 하이브리드 회로를 통해 수신되도록 공급되어지는 아날로그-디지탈 변환기의 디지탈 출력단자내의 반향 소거장치가 양자회로의 출력에 의해 지정되는 주소의 메모리에 저장된 보상값과 더해진다는 것을 나 타낸다. 양자화 회로는 반향 신호의 선형평가(linear estimate) 또는, 아날로그와 디지탈 형태의 수신신 호에 의해 작동된다. 상기 장치는 클리핑에서 기인하는 비선형 왜곡에는 주소지정을 하지 않으며, 정확한 보상의 증가와 작은 양자화 스텝들을 위해 더욱 증가된 메모리의 크기를 요구한다.

- C5> 다중 반송파 변조를 사용하는 송신장치는 더욱 중요성이 커지고 있다. 다중 반송파 변조의 원리는 1990년 5월 John A. C. Bingham에 의해 설명되었고, IEEE 커뮤니케이션 매거진(IEEE communication Magazine) Vol 28, No. 5, 페이지 5-14 에 "데이타 전송을 위한 다중 반송파 변조; 그의 시대가도래했다."의 제목으로 개재되 있다. 용어 "이산 멀티톤(discrete multitone"(DMT)는 이산적 퓨리에 변환의 사용이 효과적인 다중 반송파 변조에 관한 언급할때 사용된다.

- C6> 다중 반송파 변조를 사용하는 송신장치의 한 예는 비대칭성 디지탈 가입자선(ADSL: asymmetric digital subscriber line) 장치이다. 예를 들자면 S. Fleming et al.에 의해 작성되고, 1993년 7월 12일, xpffpvhsl vpdlwl 20-26 dp "ADSL: 정보 고속도로의 진입로"라는 제목으로 게재된 기사에서 네개의 비대 칭성 1.5 메가비트/초의 채널들이 전화국에서 가입자로의 하부방향으로 정보를 전달하며, 또한 가입자선 인 2개의 전화선을 통해 다양한 정보 채널과 평면 일반 전화 서비스가 대칭적으로-즉, 양방향으로-수행되는 ADSL 장치에 대해 설명하고 있다.

- <7> 다중 반송파 변조를 사용하는 ADSL 장치 또는 다른 송신 시스템 내에 반향 제거장치를 추가시키는 것이 고려되어졌다. 상기 관점에 있어서, 반향 소거기의 특별한 형태가, 1993년 5월 1993 국제통신회의 페이지 772-776 에서 "이산 멀티톤 변조를 위한 고속 전이중 반향 소거기"라는 제목으로 M. Ho et al에 의해 작성된 원고에 나타나 있다.

- CS> 다중 반송파를 사용하는 송신 시스템은 전형적으로, 단일 반송파 송신장치보다 최고치대 평균치의 비율이 높게 신호를 전송하기 때문에 일반적으로 고 정밀도, 즉, 더 많은 비트수를 갖는 -,의 디지탈대 아날로그 변환기 및 아날로그대 디지탈 변환기를 필요로 한다. 주어진 아날로그대 디지탈 및 디지탈대 아날로그 변환기에서, 신호 레벨은 전체 변환 영역을 이용하도록 조정되어져야 한다. 지나친 신호레벨은 일반적으로 임펄스 클리핑 잡음을 발생시키며, 반대로 모든 클리핑을 피하는 신호레벨은 대부분의 아날로그대 디지탈 변환기 및 디지탈대 아날로그 변환기의 정밀도를 떨어뜨릴 뿐만아니라 매우 큰 양자화잡음을 발생시키는 양자화 과정을 일으킨다. 따라서 클리핑 잡음과 양자화 잡음사이에 타협점이 만들어져야 한다.

- 물론, 상기의 타협점이 클리핑과 양자화가 발생하는 예를 들어 아날로그대 디지탈 및 디지탈대 아날로그 변환기를 사용하는 - 다른 송신장치에서도 만들어져야 한다.

- <10> 상기에서 지적되었듯이, 클리핑 및 양자화 잡음은 종래의 반향 소거장치를 사용해서 제거될 수 없으며, 이로 인해 송신장치의 작동효율이 떨어지게 된다. 클리핑 잡음과 양자화 잡음은 반향 제거기의 존재 유무에 상관없이 원거리 수신자의 작업에 영향을 미치게 된다. 그리므로 본 발명의 목적은 디지탈 송신장치내의 클리핑 및 양자 효과를 제거하는 방법 및 상기 송신장치를 위한 개선된 터미널을 제공하는 것이다.

#### 발명의 상세한 설명

- <11> 상기 발명은 전송신호 경로위의 전송신호가 하이브리드 회로를 통한 양방향 전송경로에 연결되며, 수신신호 경로위의 수신신호가 상기 하이브리드 회로로부터 전달되며, 상기의 결점을 수반하는 전송작업에 우선하여 클리핑 및 양자화를 소거시키는 기지정된 방법에서의 전송신호의 처리 및/또는 기지정된 방법으로 상기 결점을 보상하는 것을 포함하는 방법이 없이 전송신호의 경로가 전송신호의 클리핑및 양자화를 발생시키는 작업을 포함하는 송신장치에 있어서 클리핑 및 양자 효과를 제거하는 방법을 제공한다.

- <12> 본 발명에서 전송신호의 클리핑 및 양자화 효과 예로, 디지탈대 아날로그 변환기에서 발생하는 - 는 전송작업 이전에 클리핑 및 양자화를 분리해서 삽입하는 것을 포함하는 방법으로 감소될 수 있으며, 그후 디지탈대 아날로그 변환 또는 그외 다른 작업에서 더 이상의 클리핑 또는 양자화가 발생하지 않는다.

- <13> 가급적이면 상기 동작은 기지정된 디지탈 영역내에서 및/또는 기지정된 디지탈 신호의 정밀도를 가지고, 전송신호에 대한 디지탈 신호처리작업을 포함하며, 상기 동작에 우선하여 전송신호의 처리단계에 는 상기 영역에서 전송신호를 제한하며, 상기 정밀도내로 전송신호를 종결시키는 동작을 갖는다.

- <14> 발명의 한 실시예에서, 상기 장치는 송수신 신호 경로와 신호 처리 작업에 대한 보상단계 사이에 반향 소거동작를 포함하며, 상기 보상단계는, 신호처리 과정 이전의 송신 신호와 상기 처리 과정 이후의 송신신호 사이의 차로부터 오차 신호를 발생시키고, 상기 오차신호로부터 추정반향 응답을 발생시킨후, 수신신호로부터 상기 추정반향 응답을 제거하는 단계로 구성된다. 발명의 또다른 실시에에서, 송수신 장 치는 송수신 경로와 오직 상기 신호처리 과정후의 전송신호에 대해서만 반향소거를 수행하는 단계로 구성 된 신호처리에 대한 보상 단계 사이에서 반향 소거기를 갖는다.

- <15> 상기의 실시예들의 하나와 결합될 수 있는 발명의 또다른 실시예는, 상기 동작이 기지정된 디지 탈 영역내에서 전송신호에 대한 디지탈 신호처리 동작을 갖추며, 상기 신호처리동작에 우선하여, 전송신호의 처리단계가 기지정된 영역에 일치하도록 상기 영역에 전송신호를 제한하는 동작 또는 송신신호를 비례 조작하는 단계를 포함한다. 상기 신호처리에 대한 보상단계는 후에 상기 제한에 관련하여 송신신호의 정형단계 또는 송신신호가 전송되는 수신지점에서 보완적인 비례를 위한 비례수치로 전송되는 단계를 갖는다.

- <16> 선택적으로 보여졌듯이, 본 발명은 송신신호를 위한 송신경로와 수신신호를 위한 수신경로가 하이브리드 회로를 통해 양방향으로 연결되고, 반향 소거기가 송신경로와 수신 경로 사이에 있는 송신 장치안에서 기지정된 영역에 대한 신호의 클리핑 및/또는 기지정된 정밀도에 대한 신호의 양자화에 기인하는 송신신호의 비선형 왜곡을 보상하는 방법을 제공한다.

- <17> 상기 비선형 왜곡에 대한 보상의 방법의 한면은 기지정된 영역에 대해 송신신호를 제한 및/또는 기지정된 정밀도에 대해 송신 신호를 종결하는 단계, 상기의 제한 및/또는 종결이전의 전송 신호와 상기 제한 및/또는 종결 이후의 송신신호 사이의 차이로부터 오차신호를 발생시키는 단계, 상기 오차신호로부 터 추정 반향을 발생 수신경로상의 수신신호로부터 대응되는 추정반향을 제거하는 단계로 구성된다. 상기 비선형 왜곡에 대한 보상방법의 또다른 면은, 기지정된 영역에 대해 송신신호의 제한 및/또는 기지정된 정밀도에 대해 송신신호의 종결단계, 그리고 오직 상기 제한 및/또는 종결후에 송신신호를 반향 소거기로 보내는 단계로 구성된다.

- <18> 상기 발명의 또다른 면은, 송수신 경로가 하이브리드 회로를 통해 양방향 전송경로로 결합되며,

상기 전송신호가 기지정된 영역에서 클리핑 하기 쉬운 샘플들을 갖는 송신장치에서 클리핑 효과를 감소시 키는 방법을 제공하며, 상기 방법은 기정된 영역에서 전송신호의 샘플의 진폭을 제한하는 단계, 그리고 기지정된 영역에서 진폭이 제한되어진 각 샘플에 대해 상기의 제한된 진폭값에 따라 기지정된 방법으로 적어도 하나의 이웃 샘플의 진폭을 수정하는 단계로 구성된다. 반향 소거기가 송신경로와 수신경로 사이 에 제공될 수 있으며, 이경우 상기 방법은 오직 상기 제한 이후에 송신신호를 반향 소거기에 전달하는 추 가적인 단계를 구성할 수 있다.

- <19> 상기 발명의 또다른 추가적인 면은 송수신 경로가 하이브리드 회로를 통해 양방향 송신경로로 결합되는 송신장치에서, 기지정된 영역에 대해 클리핑하기 쉽고, 또한 기지정된 정밀도에서 양자화 되기 쉬운 샘플로 구성되는 송신신호의 클리핑 및 양자화 효과를 감소시키는 방법을 제공하며, 상기 방법은, 상기 영역에 따라 송신신호의 진폭을 스케일링하는 단계, 그리고 송신신호가 전달되는 수신위치에서의 역스케일링을 위해 상기 스케일링 값을 전송하는 단계로 구성된다. 따라서 다중 반송파 심볼의 한개 또는 그이상의 샘플들이 클리핑하기 쉽다면, 송신기에서 심복들의 모든 샘플의 진폭이 동등한 비율로 스케일링되며, 수신기에서 심볼의 모든 샘플 진폭이 거꾸로 역스케일링 된다.

- <20> 상기의 경우에서 다시 송신경로와 수신경로 사이에 반향 소거기가 첨가될 수 있다. 이경우에서 반향 소거기의 추가는 오직 상기 스케일링 후에 반향 소거기로 송신신호를 보내는 추가적인 단계를 구성 할 수 있다.

- <21> 상기 발명은 또한, 송신신호를 위한 송신경로, 수신신호를 위한 수신경로, 송수신 경로를 양방향 전송경로로 결합하는 하이브리드 회로, 그리고 송신경로와 수신경로 사이에 결합되는 반향 소거기로 구성 되는 송신장치 터미널을 제공하며, 상기 송신경로는 기지정된 디지탈 신호 영역 및 정밀도내에서 송신신 호에 수행된 기능을 포함하며, 상기의 기지정된 영역에 대한 송신신호의 제한 및/또는 상기의 정밀도에 대한 디지탈 신호의 양자화에 대한 기능에 앞서 제한 및/또는 종결단위 또한 포함한다. 그리고 송신경로 로부터 반향 소거기로 들어가는 반향 입력신호는 제한 및/또는 종결단위 후에 송신경로로부터 입력된다.

- <22> 상기 터미널은 반향소거기에 복조된 신호를 보내기 위해 제한 및/또는 종결단위 다음에 송신경로 위에서 송신신호를 변조하는 것에 반응하는 복조기를 포함할 수 있다.

- <23> 상기 발명은 추가적으로, 송신신호를 위한 송신경로, 수신 신호를 위한 수신경로, 송신경로 및 수신경로를 양방향 전송경로로 결합하는 하이브리드 회로, 그리고 송신경로와 수신경로 사이에 위치하는 반향 소거기로 구성되는 전송 시스템 터미널을 갖출 수 있다. 게다가 상기의 전송경로는 기지정된 디지탈 영역내에서 및/또는 기지정된 디지탈 신호의 정밀도를 가지고 전송신호에 수행되는 기능과 상기 영역에 대한 송신신호의 제한 및/또는 상기 정밀도에서 디지탈 신호의 양자화를 위한 상기의 기능에 앞서는 제한 및/또는 종결기를 포함하며, 상기 터미널은 제한 및/또는 종결전후에서의 차이에 대응하는 추정반향에 응 답하는 유니트를 포함하며, 상기 수신경로는 수신신호로부터 대응되는 추정 반향을 제거하기 위한 유니트 를 포함한다.

- <24> 상기에 기술된 터미널들중의 하나의 경우에서, 기지정된 디지탈 영역내에서 및/또는 기지정된 디지탈 신호의 정밀도를 가지고 전송신호위에 작용되는 기능들은 디지탈대 아날로그 변환기를 가질 수있다. 상기 제한 및/또는 종결 유니트는 각 샘플의 진폭이 상기 영역에서 제한되도록 상기 영역에 대해 전송신호를 제한하도록, 제한된 진폭의 양에 따라 기지정된 방법으로 적어도 하나의 이웃 샘플의 진폭을 수정하기 위해 배열될 수 있다.

- <25> 상기 발명은 또한, 전송신호를 위한 전송경로, 수신신호를 위한 수신경로, 양방향 송신경로에 송신 및 수신경로를 연결하기 위한 하이브리드 회로로 구성되는 송신 시스템 터미널을 가지며, 상기 터미널을 구성하는 송신경로는 기지정된 디지탈 영역내에서 송신 신호의 샘플에 작용하는 기능과, 상기 기능에 앞서 상기 영역에 대해 송신신호 샘플의 진폭을 제한하도록, 그리고 상기 영역에서 제한되어진 각 샘플의 진폭에 대해 제한된 진폭의 양에 따라 기지정된 방법으로 적어도 하나의 이웃하는 샘플의 진폭을 수정하기 위해 배열되는 유니트를 포함한다. 선택적으로 상기의 기능에 앞서는 유니트는 상기 영역에 대해 전송신호 샘플의 진폭을 스케일링 하기 위해, 수신기에서 역스케일링을 위해 상기 스케일링 값을 전송신호의 부분으로써 전달되도록 하기 위해 배열되어질 수 있다.

- <26> 각 경우에서, 유리하게 상기 터미널은 송신경로와 수신경로 사이에 결합된 반향 소거기를 포함하며, 송신 경로로부터 반향 소거기로의 각 입력신호는 상기 유니트 다음의 송신경로로부터 전달되어진다.

- <27> 본 발명의 특기할만한 면은, 송신경로가, 진동수 영역에서 시간 영역으로 전송신호 샘플을 변환하기 위한 역 고속 퓨리에 변환(이하 IFFT 로 표기), 시간영역내에서 송신신호 샘플을 송신을 위한 아날로그 신호로 변환하며 IFFT 보다는 낮게 기지정된 디지탈 신호영역 및/또는 디지탈 정밀도를 갖는 디지탈 대 아날로그 변환기(이하 DAC 로 표기),를 포함하며;

- <28> 수신경로가, 수신신호를 디지탈 신호샘플로 변환하기 위한 아날로그대 디지탈 변환기(이하 ADC 로 표기), 수신신호를 시간 영역에서 진동수 영역으로 변환하기 위한 고속 퓨리에 변환(이하 FFT 로 표기), 수신신호로부터 반향 신호를 제거하기 위한 감산기를 포함하며;

- <29> 하이브리드 회로가 양방향 송신경로에서 송신신호를 보내고 수신신호를 받을 수 있도록 송신경로 와 수신경로를 양방향 송신 경로에 연결시키며; 그리고

- <30> 반향 소거기가 송신경로와 연결된 적어도 하나의 입력단자와 상기 반향신호를 제공하는 적어도 하나의 출력단자를 가지며;

- <31> 그것에 더하여

- <32> 상기 송신경로가 또한 DAC 의 디지탈 신호영역 및/또는 디지탈 정밀도에 대해서 IFFT 로부터의 신호 샘플을 제한 및/또는 종결시키기 위해 배열되는 제한 및/또는 종결 유니트를 포함하며, 그리고

- <33> 각 송신경로로부터 반향 소거기로의 각 입력이 제한 및 종결 유니트 다음의 송신경로로부터 운반

되는.

- <34> 상기의 송신경로, 수신경로, 하이브리드 회로, 반향 소거기로 구성되는 다중 반송파 변조를 사용하는 송신장치를 위한 터미널을 제공하는 것이다.

- <35> 상기 터미널의 형태에서, 반향 소거기가 진동수 영역 반향 소거기와 FFT 로의 출력으로부터 진동 수 영역 반향 소거기의 진동수 영역 반향 신호출력을 제거하기 위한 감산 유니트(subtraction unit)로 구 성되는 수신경로 내부의 감산기로 구성 되며, 상기 터미널이 또한 제한 및/또는 종결의 출력으로부터 제 한 및/또는 종결된 신호 샘플을 진동수 영역 반향 소거기에 대한 입력신호를 구성하는 진동수 영역으로 변환하기 위해 배열되어진 FFT 를 포함한다.

- <36> 본 발명의 또다른 독특한 면은,

- <37> 송신경로가, 진동수 영역으로부터의 송신신호 샘플을 시간영역으로 변환하기 위한 IFFT, 시간영역에서 송신신호 샘플을 송신을 위한 아날로그 신호로 변환하며 IFFT 보다 작은 기지정된 디지탈 신호영역 및/또는 디지탈 정밀도를 갖는 디지탈 대 아날로그 변환기(이하 DAC 로 표기), 상기 DAC 의 디지탈 신호영역 및/또는 디지탈 정밀도에 대해 IFFT 로부터의 신호샘플을 제한 및/또는 종결하기 위해 장치되어지는 제한 및 종결기를 포함하고;

- <38> 수신경로가, 수신신호를 디지탈 신호 샘플로 변환하기 위한 ADC와, 시간 영역에서 진동수 영역으로 변환하기 위한 FFT, 수신신호로부터 대응되는 반향신호 및 추정반향을 제거하기 위한 적어도 하나의 감산기를 포함하고;

- <39> 하이브리드 회로가, 송신신호를 보내고, 수신신호를 받아들이기 위해, 송신 및 수신경로를 양방 향 송신경로에 연결시키며;

- <40> 반향 소거기가, 송신경로에 결합되는 적어도 하나의 입력단자 및 반향신호를 제공하는 적어도 하나의 출력단자와, 추정 반향 응답을 발생시키기 위해 제한 및 종결 유니트 전후의 송신신호 샘플의 차이에 대응되는 반향 응답 추정 유니트를 가지며,

- <41> 본 발명이 상기의 송신경로, 수신경로, 하이브리드 회로 및 반향소거기로 구성되는 다중변조를 사용하는 송신시스템을 위한 터미널을 제공한다는 것이다.

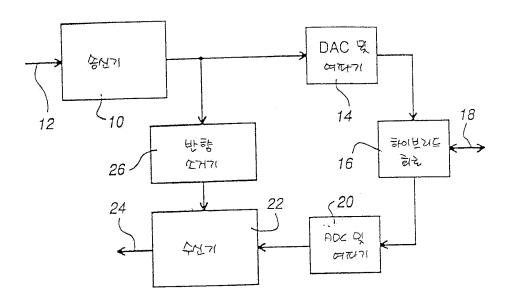

- <42> 비록 제1도내에서 다양한 블록들이 이산된 유니트로 보여질지라도, 실제로 상기의 유니트들에 의해 표현되는 기능들이 매우 다양한 방법으로 수행될 수 있다는 것은 명백하다. 특히, 상기 기능들의 다수가, 가장 편리하게 한개 또는 그 이상의 디지탈 신호 프로세서에 의해 수행되어질 수 있다는 것이 관찰됐다. 상기 내용은, 특히, 송신 시스템이 이산적 멀티톤 변조(DMT)를 사용하는 다중 반송파 변조 송신 시스템의 경우이다.

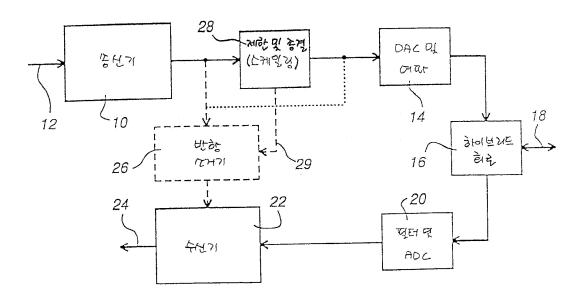

- <43> 제 1 도에 있어서, 종래의 디지탈 송신 시스템은, 코딩 및 변조 기능을 포함하고, 송신을 위한 입력신호가 입력선(12)을 통해 들어오며, 출력은 DAC 및 여파 유니트(14)와 하이브리드 회로(16)을 통해 양방향 송신경로(18) - 예, 두선 원거리 통신선 - 로 연결 되어지도록 되어 있는 송신기(TX.)(10)을 포함 한다. 양방향 송신경로(18)에 의해 수신된 신호는 하이브리드 회로(16)와 여파기 및 ADC 유니트(20)를 통 해 수신기(RX.)(22)로 연결되며, 상기 수신기는 디코딩 및 복조 기능을 포함하며 출력선(24)을 통해 수신 될 출력신호를 생성한다.

- 선4> 반향소거기(26)는 송신기(10)의 출력에 연결되는 입력단자와 수신기(22)에 연결되는 출력단자를 갖는다. 수신기(22)에서, 반향 소거기(26)의 출력은 존재할 수 있는 송신신호 성분을 제거하기 위해 여파 및 아날로그 대 디지탈 변환 유니트로부터 빼진다. 종래의 기술에 있어서, 반향소거기(26)는 최적 소거를 위한 시간에 걸쳐 적용되는 계수를 가질 수 있다. 게다가, 간략성을 위해 도면에는 나타나지 않았지만, 상기 반향 소거기(26)는, 예로 송신기(10)내의 변조기능 전후 모두와 송신 경로에 연결되는 것과 마찬가지로, 송신경로와 연결되는 다수의 입력단자를 가질 수 있으며, 또한 상기 반향 소거기(26)는 수신기(22)의 복조 가능 전후에 모두 연결되는 것과 같이 수신경로와 연결되는 다수의 출력단자를 가질 수 있다. 따라서 반향 소거기(26)는 비변조 및 변조 송신경로 신호의 하나 또는 양쪽 모두에 동작될 수 있다.

- <45> 도입부에서 설명되었듯이, DAC 및 여파 유니트(14)와 ADC 및 여파유니트(20)내에서의 디지탈과 아날로그 신호사이의 변환에서 부과되는 디지탈 영역 및 디지탈 정밀도 제한이 비선형 왜곡이며, 반향소 거기(26)에 의해 제거되지 않는 클리핑 잡음 및 양자화 잡음을 발생시킨다. 양자화 및 클리핑 잡음은 송신되는 디지탈 신호의 정밀도가 증가함에 따라 현저히 증가한다. 예, 다중 반송파 변조를 사용하는 송신 시스템 -

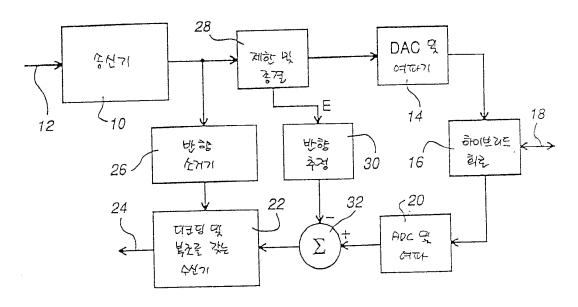

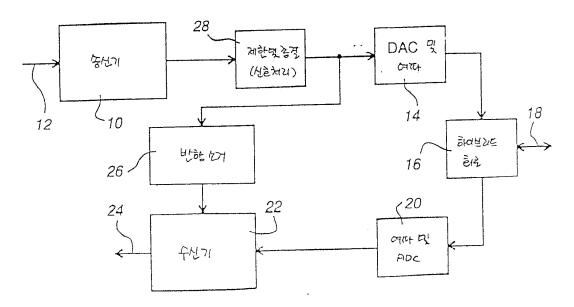

- <46> 제 2 도는 상기 발명의 실시예에 따르는 디지탈 송신 시스템의 블록선도를 나타낸다. 제 2 도의 송신 시스템에 신호 제한 및 종결 유니트(28), 반향 추정 유니트(30), 그리고 감산유니트(32)가 추가된 것을 나타낸다. 상기 반향 추정 유니트(30)는 자신의 압력 단자에 제공되는 에러신호 E 의 반향 임펄스 응답을 발생시키고, 송신기(10)의 입력선(12)를 통해 공급되며 반향소거기(26) 내에서 계수 결정을 위해 수행되는 의사-랜덤 비트 시퀀스에 대응하여 초기에 수립된 계수에 따라 횡방향 필터로 작동한다.

- <47> 제 2 도에서 분리되어 나타나지만 DAC 및 여파 유니트(14)내의 DAC 와 일체를 구성할 수도 있는 제한 및 종결유니트(28)는 송신기(10)으로부터 제공되는 송신되어져야 할 원래의 디지탈 신호의 각 샘플을 제한 및 종결하며, 그결과로 발생되는 제한 및 종결된 디지탈 신호 샘플을 DAC 및 여파유니트(14)내의 DAC 에 공급하며, 그리고 원래의 디지탈 신호샘플과 제한 및 종결된 신호샘플 사이의 차이로서의 에러신호 E 를 발생시킨다. 상기 반향 추정유니트(30)는 여파 및 ADC 유니트(20)의 출력신호로부터 출력신호로부터 감산유니트(32)에 의해 빼지는 결과신호를 생성하기 위해 에러신호 E 와 반향 임펄스 상에서 정상합성적분을 수행한다.

- <48> 제한 및 종결유니트(28)내의 종결단계는 DAC 및 여파 단위(14)에 구성된 DAC 의 정밀도 또는 비트수에 대한 신호의 양자화에 대응된다. 예로, 송신기(10)내에서 수행되는 코딩 및 변조는 24비트의 디지탈 정밀도를 갖는 디지탈 신호 프로세싱에 의해 실행될 수 있으며, 상기 DAC는 오직 10 에서 16 비트의

분해능 또는 정밀도를 가질 수 있다. 따라서 24비트로부터 10내지 16비트 신호로의 양자화가 존재하며, 최하위 비트 위치에 들어 있는 정보는 잃어버릴 수 있다. 상기의 정보 손실이 신호의 종결을 구성한다.

- <49> 제한 및 종결유니트(28)내의 제한 단계는 DAC 에 제공되는 큰 크기의 클리핑에 대응되며, 따라서 최상위 신호 비트와 관계된다. 만일 송신기(10)로부터의 부호화 및 변조된 신호가 DAC 의 영역을 초과하 는 크기를 갖는다면, 그때 제한 및 종결유니트(28)내의 제한기가 상기 영역의 최대치에 대해 신호를 제한 하거나 잘라 버린다.

- <50> 종래의 기술에 있어 상기 제한 및 종결의 단계가 DAC 의 작동 내에서 본래적으로 수행되 왔다는 것은 높이 평가할만하다. 본 발명의 실시예는 제한 및 종결단계가 제한 및 종결 유니트(28)에 의해 수행 되며, 반향 추정 유니트(30)에 따라 에러신호 E 가 발생되며 상기 반향 추정 유니트(30)를 통해, 수신된 신호로부터 잡음을 제거할 수 있도록 빼지도록 감산유니트(32)에 공급되며 그리하여 클리핑 및 양자화 잡 음(DAC 내에서 각각 제한 및 종결에 기인하는)을 보상한다는 점에서 상기 종래의 기술과 차이를 나타낸다.

- <51> 제한 및 종결과정의 하나 또는 양쪽 모두가 제한 및 종결단위(28)에 의해 수행된다. 바꾸어 말하면, 에러신호 E 는 송신기(10)로부터 나오는 원래의 디지탈 신호와 종결없이 제한되어진 신호, 또는, 제한없이 종결되어진 신호, 또는, 제한 및 종결되어진 신호중의 하나와의 차이를 표현할 수 있다. 상기 선택중 세번째가 가장 바람직하지만, 디지탈 신호 프로세싱의 계산적 요구가 에러 신호 E 가 종결처리를 고려하게 될때 매우 높아질 수 있다.

- <52> 따라서, 상기 발명의 실시에는, 상기 제한 및 종결유니트(28)가 오직 제한의 단계만을 포함하며, 상기 에러신호 E 가 송신기(10)의 출력과 DAC 에 제공되는 제한된 신호사이의 각 샘플에 대한 차이만을 나타내는 경우에서, 클리핑 잡음을 제거하는데 매우 큰 중요성을 갖는다.

- <53> 제 2 도에서 보여지듯 시스템의 선택적 배열에 따라, 상기 감산 유니트(32)는 하이브리드 회로 (16)와 여파 및 ADC 유니트(20) 사이에서 아날로그 감산기로 대치될 수 있으며, 상기 감산기는 DAC 를 경유하여 반향 추정 유니트의 출력에 연결되어진다.

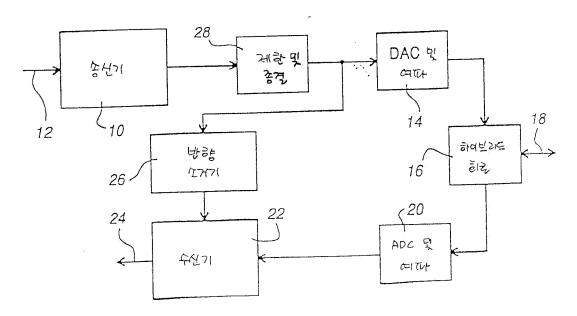

- <54> 제 3 도는 상기 발명의 또다른 실시예에 따르는 송신 시스템의 블록선도이며, 상기 블록선도내의 유니트(28)는 상기에서 논의 되었듯이 제한 및 종결을 수행하며, 그리고 제 2 도에서의 반향 추정 유니트 (30)와 감산유니트(32)는 생략되었다. 제 3 도의 시스템에서, 반향 소거기(26)로의 입력은 제한 및 종결 유니트(28)의 바로 옆 출력으로부터 받아들여지며, 종래기술의 제 1 도에서와 같이 송신기(10)의 출력단 자로부터 직접 받아들이지 않는다.

- <55> 제 3 도의 시스템에 있어서, 다수의 입력신호를 받아들이는 반향 소거기(26)의 배열은 제시된 도면보다 더욱 복잡하게 된다. 예로, 만일 반향소거기(26)가 2개의 입력단자를 갖는다면, 하나는 변조전의신호를 위한 것이고 또다른 하나는 변조된 신호를 위한 것이며, 이때 제 3 도의 시스템에서 반향소거기로입력되는 변조된 신호는 상기에서 나타난 제한 및 종결유니트(28)의 출력으로부터 얻어진다. 변조전의 신호 즉 비변조된 신호는 또한 제한 및 종결 후의 제한 및 종결유니트(28)의 출력으로부터 얻어진다. 따라서 상기의 경우, 제한 및 종결유니트(28)의 출력신호는 복조되며 (추가적 복조기능 필요), 변조, 제한, 종결 및 복조된 결과신호가 반향 소거기의 비변조된 신호입력단자에 공급된다. 상기 예는 제 7 도의 참조이하에서 다시 설명된다.

- <56> 그러므로, 제 3 도의 시스템내에서 DAC 및 여파 유니트(14)내의 DAC 에 공급되며 DAC 의 특성을 고려하여 제한 및 종결유니트(28)에서 제한 및 종결되어진 신호는 DAC 내에서 더이상의 양자화 잡음 또는 클리핑 잡음이 생성되기 어렵다. 상기와 같은 신호가 반향 소거기(26)에 공급되며, 그에 따라 DAC 에 제공되는 같은 신호에 작용되고, 더이상의 양자화 및 클리핑에 의한 비선형 왜곡이 발생하지 않게 된다. 따라서 상기 시스템에서 양자화 및 클리핑은 반향 소거기에 관한한 완벽하게 제거된다.

- <57> 제 3 도의 시스템에서 제한 및 종결유니트(28)가 DAC 및 여파 유니트(14)내에 있는 DAC 의 영역 및 정밀도와 일치하도록 제한 및 종결을 수행하더라도, 만일 원한다면 명백히 상기 기능중의 하나가 홀로 수행되어질 것이다. 디지탈 신호 프로세싱 기술을 사용하는 제한 및 종결유니트(28)를 수행하는데 있어서, 제한 및 종결에 대한 계산적인 요구가 매우 작다. 상기에서 언급되고 앞으로 논의 되어지듯, 만일 반향소거기(26)가 복조된 신호입력을 필요로 한다면, 그때 추가적인 계산이 제한 및 종결유니트(28)의 출력으로 부터의 복조신호를 위해 요구되어진다. 제 3 도의 시스템내의 복조기능 및 제 2 도의 시스템내에 반향 추정유니트(30)를 위한 상대적인 계산적 요구가 특정한 환경에서 다른 것에 우선하여 한 시스템에 결정될 수 있다.

- <58> 명백하게, 제 3 도의 시스템은 제 2 도의 시스템내에서 생성되는 에러신호 E 와 송신기(10)의 출력단자로부터 제한 및 종결유니트(28)의 입력단자에 공급되는 원래의 신호 모두를 반향 소거기(26)로 공급되도록 하고 상기 신호들에 의해 반향소거기(26) 내에서 제한 및 종결유니트(28)의 출력신호를 계산하도록 수정되어질 수 있다. 바로 앞문장에서의 내용은 제한 및 종결유니트(28)로부터 반향소거기로 직접출력신호를 얻는 것과 기능적으로 같지만, 그러나 더 많은 계산을 포함하며, 따라서 바람직하지 않다.

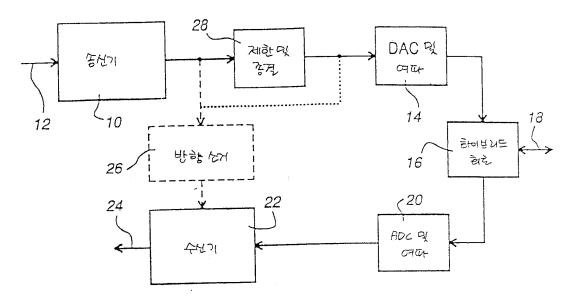

- <59> 제 4 도와 5 도의 시스템은 제한 및 정형유니트(28)의 추가를 제외하면 제 1 도와 유사한 시스템을 나타낸다. 제 4 도 및 5도의 시스템에서 반향 소거기는 반드시 필요한 것은 아니며 생략될 수 있다. 상기 이유때문에, 제 4 도 및 5도에서 반향 소거기(26)와 연결부가 대시선으로 표시되었다. 선택적이며 유익한 반향 소거기(26)의 입력의 연결은 제 4 도 및 5도에서 점선으로 나타냈으며, 상기 방식이 제 3 도의 참조와 함께 상기에서 설명되어진 제한 및 종결유니트(28)의 출력단자 바로옆에 반향소거기(26)를 연결한 것과 대응된다.

- <60> 제 4 도의 시스템에서, 제한 및 정형유니트(28)는 DAC 및 여파 유니트(14)내의 DAC 에 공급되는 신호샘플의 제한 및 정형 모두를 제공한다. 제한 기능은 제 2 도 및 3도에서 DAC 의 범위를 초과하는 신 호샘플의 크기를 그 범위의 최대값에서 제한하여 DAC내에서 더이상의 제한 또는 클리핑이 없도록 하는 제 안 및 종결유니트(제 2 도 및 3 도의 28)의 제한기능과 같다. 게다가, 샘플이 상기 방법으로 제한될때마

다, 제 3 도의 시스템내의 제한 및 종결유니트(제 3 도의 28)가 한개 또는 그 이상의 이웃 샘플들(즉 제한된 샘플에 앞서거나 뒷서는 샘플)의 크기를 수정하며, 그리하여 클리핑 잡음의 스펙트럼 내용을 변화시킨다. 클리핑 잡음의 진동수 스펙트럼은 그렇지 않으면 상대적으로 평평하며 상기의 수정에 의해 정형화되어진다.

- <61> 상기 크기의 수정 또는 정형은, 클리핑 에러, 즉 기지정된 방법에서 제한된 샘플과 제한되지 않은 원래의 샘플 사이의 차에 관계되는 양을 수정되어야 할 각 이웃 샘플들에 더하거나 빼줌으로써 제한 및 정형기(28)내에서 수행된다. 예로써 [-0.5, 1, -0.5]에 대응하는 펄스에 의해 클리핑 에러를 정형화하는 것이 요구될 수 있다. 상기의 경우, 제한 및 정형유니트(28)가 제한 기능의 수행내에서 X의 양만큼샘플의 양의 값을 감소시킬때마다(즉, 비정형된 클리핑 에러는 음의 값 -X를 갖는다), 상기 제한 및 정형유니트(28)는 또한 제한되는 샘플의 바로 앞 및 바로 뒤의 이웃샘플들에 X/2 만큼 더해준다. 유사하게,만일 상기 제한 및 정형유니트(28)가 X만큼의 양으로 샘플의 음의 값을 증가시킨다면(즉, 비정형된 클리핑 에러가 양의 값 X를 갖는다), 상기 제한 및 정형유니트(28)는 또한 제한된 샘플의 앞, 뒤의 이웃 샘플들에서 X/2 만큼을 빼준다.

- <62> 따라서 상기 제한 및 정형유니트(28)내에서 정형 기능은 클리핑 잡음을 재정형화 하며, 그리하여 원거리 수신자에게 양방향 송신경로(18)를 연결하는 것을 손쉽게 한다. 최적의 정형은 시스템의 독특한 특성에 의존하게 될 것이지만, 어떤 행태의 원하는 정형도 유사한 방법으로 제한 및 정형유니트(28)에 의 래 수행되어질 수 있다.

- <63> 제 5 도의 시스템에서, 진폭 스케일링 유니트(28)는 DAC 및 여파 유니트(14)내의 DAC 에 제공되는 신호 샘플들의 진폭 스케일링을 제공한다. 제 5 도에 나타난 시스템은 다중 반송파 송신장치이며, 각다중 반송파 심볼은 다수의 서브채널 또는 다른 진동수에서 각각의 송신 심볼의 하나 또는 그 이상의 비트들을 운반하는 반송파로 구성된다. 예로써, 상기 시스템은, 다수(예 256 채널) 채널의 DNT(이산 멀티톤 -discrete multiton) 변조를 사용할 수 있다. 하기에 설명되어질 것이지만, 송신 심볼의 한개 또는 그 이상이 비트들이 유지되며, 그리고 클리핑을 피하거나 더 낮고 더 좋은 준위로 진폭을 감소시키기 위해 송신 심볼내의 모든 신호 샘플의 진폭을 스케일링 하는 것에 일치하는 스케일링 값을 전송하는데 사용된다. 송신 심볼의 수신기는 심볼내의 상기 스케일링 값에 따라 진폭을 역스케일링 한다.

- <64> 좀더 특별히 그리고 예로서, 제 5 도의 시스템내의 진폭 스케일링 유니트(28)는 각 다중 반송파 심볼이 감소되거나 클리핑을 피하기 위해 0(즉 신호진폭이 변하지 않는 경우), 1,2, 또는 3db 중의 어느 에너지로 스케일링 될지를 결정하며, 상기 에너지 스케일링의 2비트 값을 사용하지 않는 채널의 모두 또 는 일부에 삽입하며, 그리고 다중 반송파 심볼의 모든 신호 진폭의 대응되는 스케일링에 영향을 미친다. 상기 2비트 에너지 스케일링 값은 양방향 송신경로(18) 끝단부에 있는 수신기의 위상 검출기에서 검출되 어지는 직각 위상정보로서 송신된다. 검출되는 스케일링 값에 따라, 수신기는 다중 반송파 심볼의 모든 신호 진폭을 거꾸로 역스케일링 하는 작업을 수행한다. 생략되는 경우는 0dB 의 에너지에 대응하는 클리 핑 하지 않는 심볼이다. 그렇지 않으면 크게 클리핑 되어질 심볼이 3dB의 에너지내로 스케일링 되어지고, 따라서 클리핑이 제거되거나, 더 좋은 준위로 좀더 감소되어진다.

- <65> 상기의 진폭 스케일링 유니트(28)에 의한 스케일링은, 클리핑 잡음을 제거하는 동안 양자화 잡음 이 증가하는 결과로 귀결될 것이다. 그렇지만, 일반적으로 클리핑 잡음이 양자화 잡음보다 더욱 나쁜 영 항을 미치기 때문에, 클리핑 및 양자화에 반대로 미치는 영향을 갖는 결합에서 잡음의 감소가 나타난다. 상기와 유사한 배열이 원한다면, 거꾸로 또는 추가적으로, 클리핑이 일어나지 않도록 다중 반송파의 에너 지를 증가시키고 그리하여 양자화 잡음을 감소시키도록 사용되어질 수 있다는 것을 고려할 수 있다. 따라 서 제 5 도의 진폭 스케일링 유니트(28)에 의한 상기 스케일링이 클리핑 효과 및 양자화 잡음 사이에서 최적의 타협점을 제공하도록 수행되어질 수 있다. 제 5 도에서는 나타나지 않았지만, 제 5 도의 시스템내 의 진폭 스케일링 유니트(28)는 또한 만일 필요하다면 2도에서 4도의 참조로 상기에서 묘사되어진 것과 같은 방법으로 스케일링 되어진 다중 반송파 심볼 신호 진폭 위에서 제한의 기능을 수행할 수도 있다.

- 상기에서 설명되었듯이, 제 4 도 및 5도의 도면에서 반향소거기(26)가 반드시 필요한 것은 아니라는 사실을 나타내기 위해 대시선으로 나타내졌다. 만일 반향소거기(26)가 제공된다면, 그때 상기 유니트(26)는 4도 및 5도에서, 대시선으로 나타내어진 것처럼 송신기(10)의 출력 바로 측부에 연결되거나 또는 점선으로 표시 되는 유니트(28)의 출력 바로 다음에서 연결될 수 있다. 제 5 도의 시스템에서 전자의경우 제어선(29)(대시선으로 나타나지며 두번째 경우에서는 필요하지 않다)은 반향 응답에 대응되는 진폭스케일링에 제어선을 통해 영향을 미치도록 반향 소거 유니트를 제어하기 위해 진폭 스케일링 유니트(28)로부터 반향 소거 유니트(26)로 연결되도록 구성된다.

- <67> 좀더 일반적으로, 제 5 도의 다중 반송파 시스템내에서의 진폭 스케일링 유니트(28)의 스케일링 기능 및/또는, 제 4 도의(단일 반송파 또는 다중 반송파) 시스템내에서의 제한 및 정형유니트(28)의 제한 및 정형기능, 및/또는 제 2 도 또는 3도의(단일 반송파 또는 다중 반송파) 시스템내에서의 제한 및 종결유니트(28)의 제한 및 종결기능은 홀로 사용되어지거나, 독특한 상황에서 적당하게 요구되어지는 것에 따라 결합되어 사용될 수도 있다. 각 경우에서, 유니트(28)의 각 기능은 디지탈 신호 프로세싱 기술에 의해미리 수행되어진다.

- <68> 하기의 테이블은 발명의 실시예에 따라 유익하게 구성될 수 있는 제 2 도에서 제 5 도까지의 시 스템의 다양한 결합을 요약 했으며, 반향소거기(26)(EC)가 구성되어지는지 그렇지 않은지를 지적하고, 해 당 시스템이 단일 반송파(SC) 변조를 사용할 수 있는지(모든 결합은 다중 반송파 변조를 사용할 수 있음) 없는지를 나타낸다:

| M25 | 21/35 | A145 | 제55 | 반항외유년?  | 型豐  |

|-----|-------|------|-----|---------|-----|

| x   |       |      |     | 7       | 吊   |

| . x |       | x    |     | 7       | 유   |

| х   |       | x    | x   | 7.      | 무   |

| х   |       |      | х   | o Ti    | - 早 |

|     | х     |      |     | q       | 71  |

|     | x     | x    |     | 市       | 吊   |

|     | x     | x    | x   | 71      | 平   |

|     | x     |      | x   | 4       | 一年  |

|     |       | х    |     | 선택적     | 4   |

|     |       | x    | x   | रास्य   | 早   |

|     |       |      | x   | राष्ट्र | 毕   |

- <70> 예로서, 제 6 도는 제 3 도와 4도의 시스템을 결합한 형태의 시스템을 나타낸다. 제 6 도의 시스템에서, 유니트(28)는 신호 처리유니트(28)로 나타나며, 제 2 도에서 4도까지의 시스템에서는 유니트(28)의 제한 기능을, 제 4 도에서는 유니트(28)의 정형기능을, 제 2 도 또는 3도의 시스템에서는 종결기능을 수행한다.

- <71> 게다가, 반향 소거유니트(26)의 입력은 3도의 시스템에서의 제한 및 종결유니트(28)로서의 유니트(28)의 출력으로부터 나온다. 따라서 상기의 경우, 유니트(28)에 의한 클리핑 잡음의 재정형은 반향 소거유니트(26)에 영향을 미치게 되며, 동시에 반향 소거 유니트가 같은 신호를 공급받는 동안, 3도의 참고 사항에서와 같이 DAC 및 여파 유니트(14)내의 DAC 에 제공되어짐으로써, 더이상의 클리핑 및 양자화 잡음이 발생되지 않게 한다.

- <72> 상기의 내용과 같이 상기 발명이 클리핑 및 양자화 잡음이 발생하기 쉬운 어떠한 송신 시스템에 도 적용될 수 있을지라도, 반향 소거기와 이산적 멀티톤 변조(DMT)와 같은 다중 반송파 변조를 사용하는 송신시스템에서 특히 이점을 나타내며, 상기의 중요성을 증가시키는 예로써 ADSL(asymmetric digital subscriber line) 송신 시스템이 있다.

- <73> ADSL 송신 시스템에 있어서, 중앙국(central office) 이하 CO로 표기 의 터미널로부터 원거리 또는 가입자의 터미널로 흐르는 하류 방향내에서, 원거리 터미널로부터 CO 터미널로 흐르는 상부 방향보다 더 많은 정보가 송신된다. 상기의 정보 송신 특성은 정수곱 k 를 CO 터미널 송신의 샘플률에 취함으로써 손쉽게 달성될 수 있다. 상기의 두 송신 방향에 대한 다른 샘플링 률은 원거리 터미널의 내삽기능및 CO 터미널의 분할기능에 의해 반향 소거 프로세스 내에 축적되어진다.

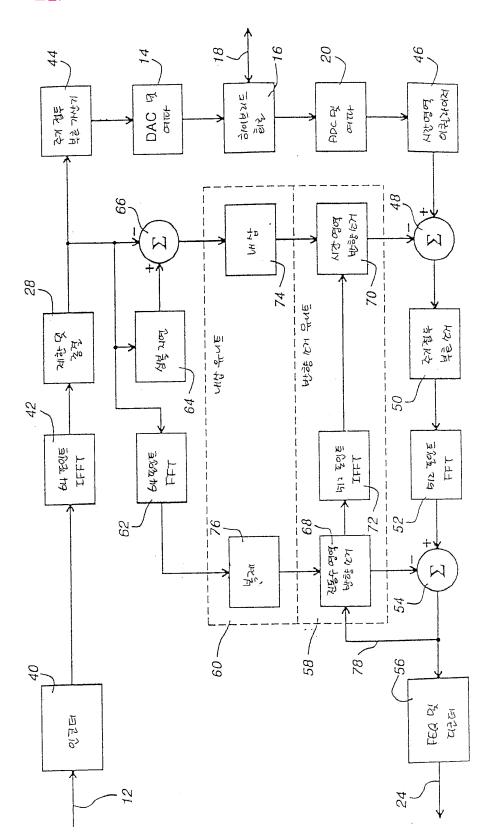

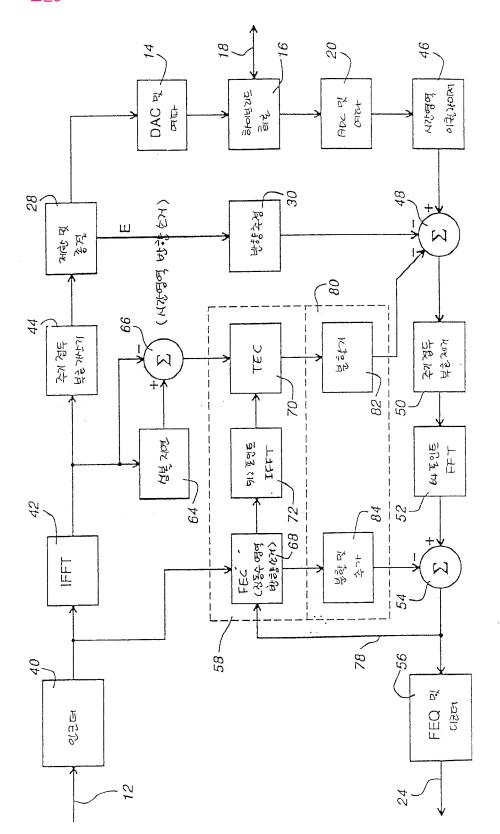

- <74> 제 7 도는 DMT 변조를 사용하는 ADSL 송신 시스템의 원거리 터미널에 적용된 3도의 시스템의 예를 나타내며, 8도는 DMT 변조를 사용하는 ADSL 송신 시스템의 원거리 터미널에 적용된 2도의 시스템 예를 나타낸다. 각 경우에서 정수곱 k=8 이며, 느린 상향 정보 샘플링률에 대한 64 포인트의, 고속 하류 방향 정보 샘플링률에 대한 512 포인트의 FFT 및 IFFT 들을 사용하며, 고속 샘플링률에서 반향 소거작용이 수행되는 시스템들로 제시되었다.

- <75> 제 7 도 및 8 도에서, 제 2 도 및 3도에서와 같은 참고 사항들이 어디에 적용될지에 대해 사용되었다. DAC 및 여파 유니트(14)와 ADC 및 여파 유니트(20) 내에서 하이브리드 회로(16)과 여파기를 제외하면, 실질적으로 7도와 8도 각각에서 제시된 모든 기능들은 한개 또는 그 이상의 디지탈 신호처리기를 사용함으로써 보다 유용하게 수행될 수 있다.

- <76> 원거리 터미널을 나타내는 7도에 있어서, 입력선(12)위의 상향 정보 신호는 인코더(40)에 의해 부호화 되어지며, 64포인트의 IFFT(42)에 의해 시간영역(즉, 변조)으로 변환된다. 상기의 결과 신호 샘플 들은 3도에서 나타나는 제한 및 종결유니트(28)에 의해 제한되고 종결되어진다. 주기 접두부호가 주기 가 산유니트(44)에 의해 유니트(28)로부터의 제한되고 종결되어진 결과 신호 샘플들에 더해지고, 상기 결과 신호가 DAC 및 여파유니트(14) 그리고 하이브리드 회로(16)를 통해 두개의 도선으로 된 가입자선인 양방 향 송신경로(18)에 전달된다.

- <77> 양방향 송신경로(18)을 통해 수신된 신호는 하이브리드 회로(16)을 통해 여파 및 ADC 유니트(2 0)에 연결되어진다. 상기 유니트(20)의 출력신호는 차례대로, 시간 영역 이퀼라이져 (이하 TEQ) 유니트 (46), 감산유니트(48), 그리고 주기 접두부호를 없애는 주기 접두 부호소거 유니트(50), 신호를 진동수 영역으로 변환하는 512 포인트의 FFT(52), 또다른 감산유니트(54), 진동수 영역 이퀼라이져(FEQ), 디코더 (decoder) 유니트(56)을 통해 출력선(24)위의 하류 방향 정보신호를 발생시키기 위해 연결되어진다.

- <78> 비록 유니트 40 에서 유니트 56 까지의 상세한 설명이 상기 발명에서는 중요하지 않더라도, 주기 접두 부호 유니트(44)에 의해 추가되는 주기 접두 부호가, 송신된 데이타 심볼로부터 그 다음의 데이타 심볼의 혼동을 피하기 위한 보호간격을 제공하기 위해 데이타 블록의 단부로부터 정보의 반복을 이루는 것은 중요하다. 상기 TEQ 유니트(46)는 주기 접두 부호의 길이보다 작게 상기 간섭을 제한하는 한정적인

임펄스 응답 디지탈 여파기를 포함하며, 그리하여 주기 접두 부호 소거유니트(50)에 의한 접두부호의 소거가 간섭을 제거한다. 상기 FEQ 및 디코더 유니트(56)내의 FEQ 가 각 서브체널 또는 시스템의 반송파에 개별적으로 동작하며, 각 반송파의 저하 및 지연을 위해 적당하게 조정한다. 신호들에 대해 인코더(40)와 IFET(42)는 트렐리스(trellis) 코드화 변조를 수행할 수 있으며, FFT(52)와 FEQ 및 디코더 유니트(56)내의 디코더는 트렐리스 코드화 복조를 수행한다.

- 7도에서 나타나는 나머지의 유니트들은 반향 소거기(26)를 구성하며, 반향 소거 유니트(58), 내 삽유니트(60), 64 포인트 FFT(62), 지연유니트(64)를 포함하는 지연 보상 유니트와 감산유니트(66)를 포 함한다. 반향 소거 유니트(58)는 진동수 영역 반향 소거기(FEC)(68), 시간영역 반향 소거기(TEC)(70), 그 리고 512 포인트 IFFT(72)를 포함한다. 내삽유니트(60)는 시간 영역 신호에 대한 내삽유니트(74) 그리고 진동수 영역 신호에 대한 복제 유니트(76)를 포함한다.

- <80> 제한 및 종결유니트(28)에 의해 제한되고 종결되어진 출력신호는 FFT(62)에 의해 진동수 영역으로 변환되어지며, FEC(68)에 대한 입력신호를 생성하기 위해 복제유니트(76)에 의해 진동수 영역내에서 인자 k에 의해 복제된다. FEC(68)의 출력신호는 진동수 영역내에서 반향 소거를 위한 감산유니트(54)에 의해 FFT(52)의 출력신호로부터 빼내진다. 감산유니트(54)의 출력은 계수의 적당한 조절을 위해 FEC(68)로 피드백 경로(78)를 통해 피드백되며, 상기 출력은 TEC(70)의 적합한 계수 조정을 위해 IFFT(72)에 의해 시간영역으로 변환된다. 상기의 적합한 조정은 상대적으로 느린 비율로 수행되며, 예로 10개의 송신데이타 심볼마다 IFFT(72)의 계산적인 요구를 감소시키기 위해 조정된다.

- <81> 상기의 제한 및 종결 유니트(28)에 의해 제한되고 종결된 출력 신호는 또한 감산유니트(66)와 지연유니트(64)로 전달되며, 이것은 한개 심볼의 지연을 일으킨다. 감산 유니트(66)는 현재의 심볼을 이전의 심볼로부터 빼주며, 감산유니트(66)의 출력에서 시간영역 신호의 보상된 지연을 일으키기 위해 지연유니트(64)에 의해 지연된다. 상기 신호는 입력신호를 전달하기 위해 시간영역내의 인자 k에 의해 TEC(70)에 내삽되어지며, 출력신호는 시간영역 내에서 반향소거를 제공하기 위해 감산유니트(48)에 의해 TEQ(46)의 출력신호로부터 빼진다.

- <82> 반향 소거에 대한 상세한 설명은 M. Ho et al.의 논문에 잘나타나 있다.

- <83> 상기 CO 터미널은 7도의 반향 소거기의 입력촉부에서 내삽유니트(60)가 제거되고 8에 대해 설명된 분할 유니트가 반향 소거기의 출력 촉부 위에 대신 제공되는 것을 제외하면 7도의 원거리 터미널의 연결방법과 유사한 방법으로 배열되어진다. 하부 방향으로의 송신 정보의 보다 빠른 샘플링 률을 위해, 7도의 64 포인트 FFT(62)에 대응되는, 복조기능이 512 포인트 FFT에 의해 수행되어지며, 그 결과로 계산적요구가 현저히 증가한다. 계산적인 요구에서 작은 증가를 포함할 수 있는 2도의 선택적인 시스템의 하나는 CO 터미널을 위해 적용될 수 있다.

- <84> 8도에 있어서, CO 터미널 안에서 7도의 내삽유니트가 제거되며, 대신 분할유니트(80)가 제공된다. 분할유니트(80)는 분할인자 k를 가지고 분할기 유니트(82)로 구성되며, 상기 분할유니트(80)를 통해 TEC(70)의 시간영역 신호출력이 시간영역에서의 반향 소거를 감산유니트(48)의 감산 입력과 진동수 영역내에서 등가적인 기능을 수행하며 진동수 영역내의 반향 소거를 수행하기 위한 감산유니트(54)의 감산 입력에 FEC(68)의 신호출력을 연결하는 분할 및 추가 유니트(84)에 연결된다.

- <85> 2도의 시스템에 의해, 유니트(28)가 송신되어진 신호를 제한 및 종결하고 출력이 감산유니트(48) 2도에서 유니트 32 에 대응 -의 다른 감산 입력에 연결되는 반향 추정 유니트(30)에 전달되는 에러신호 E 를 발생시킨다. 상기 TEC(70)는 지연유니트(64)와 감산유니트(66)를 포함하는 지연 보상 유니트를 통해 IFFT 42 의 출력으로부터 진동수 영역 신호를 공급받으며, 7도의 FFT(62)는 제거되었다.

- <86> 상기 발명의 특별한 실시예가 상세히 설명되었지만, 다양한 수정,변형 및 적용이 청구항에서 제한된 발명의 영역으로부터 수행될 수 있다.

### 도면의 간단한 설명

- 제 1 도는 반향 소거 장치를 포함하는 종래의 양방향 디지탈 송신 시스템의 블록선도;

- <88> 제 2 도 내지 제 6 도는 발명의 실시예에 따라 클리핑 및 양자 효과가 소거되어진 양방향 디지탈 전송 시스템의 블록선도; 그리고

- <89> 제 7 도와 제 8 도는 발명의 실시예에 따라, 비대칭성 디지탈 가입자 선(ADSL) 송신 시스템을 포함하는 송신 시스템의 기능 블록 선도.

- <90> 부호설명

<87>

- <91> 10...송신기(TX.) 12...입력선

- <92> 14...DAC 및 여파 유니트 16...하이브리드 회로

- <93> 18...양방향 송신경로 20...ADC 및 여파 유니트

- <94> 22...수신기(RX.) 24...출력선

- <95> 26...반향 소거기

- <96> 28...1도에서 3도까지 제한 및 종결 유니트/4도에서 제한 및 정형 유니트/5도 진폭 스케일링 유니트/제6도 신호처리 유니트

- <97> 30...반향 추정 유니트 32,48,54,66...감산 유니트

- <98> 46...인코더(encoder)

- <99> 42...IFFT(역고속 퓨리에 변환)

- <100> 44...주기 가산기

- <101> 46...시간영역 이퀼라이져(TEQ.-time domain equlizer)

- <102> 50...주기 접두 부호 소거 유니트

- <103> 52...FFT(고속 퓨리에 변환)

- <104> 56...FEQ(진동수 영역 이퀼라이져) 및 디코더 유니트

- <105> 58...반향 소거 유니트

- <106> 60,74...내삽기(interpolation)

- <107> 62...62포인트 FFT 64...지연 유니트

- <108> 68...FEC(진동수 영역 반향 소거기 frequency-domain echo canceller)

- <109> 70...TEC(시간 영역 반향 소거기 Time-domain echo canceller)

- <110> 76...분할 유니트(decimation unit)

- <111> 78...복제 유니트(replication unit)

- <112> 82...분할기(decimator)

- <113> 84...분할 및 추가(divide & add)

### (57) 청구의 범위

### 청구항 1

송신신호 경로에서의 송신신호가 하이브리드 회로(16)를 통해 양방향 송신경로(18)에 연결되고, 수신신호 경로에서의 수신신호가 상기 하이브리드 회로를 통해 상기 양방향 송신경로로부터 수신되며, 상 기 송신경로가 송신신호의 클리핑 및 양자화를 발생시킬 송신신호에 대하여 디지털-아날로그(digital-toanalog) 변환작업을 포함하는 송신시스템의 클리핑 및 양자화(clipping and/or quantization)를 감소시키 는 방법에 있어서,

상기 디지털-아날로그 변환작업 이전에 송신신호의 신호특성을 변경시키어 상기 디지털-아날로그 변환작업에 의한 송신신호의 클리핑 및 양자화를 감소시키거나 소거하도록 하고, 상기 변경에 대하여 송 신신호를 보상하며, 그리고 상기 보상된 송신신호를 송신하고,

상기 디지털-아날로그 변환작업 이전의 송신신호 변경이 송신신호를 상기 디지털-아날로그 변환 작업과 관련된 사전에 정해진 디지털 영역으로 제한시킴을 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

#### 청구항 2

제 1 항에 있어서, 상기 송신시스템이 송신 및 수신신호 경로 사이에서 반향 소거기(echo cancellation)(26)를 포함하며 상기 보상단계가,

상기 프로세싱 이전 송신신호와 그 이후 송신신호 사이 차이로부터 에러신호(error signal)를 발생시키고,

상기 에러신호로부터 추정반향 응답(estimated echo response)을 발생시키며, 그리고

상기 수신신호로부터 상기 추정반향 응답을 빼주는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

#### 청구항 3

제 2 항에 있어서, 상기 디지털-아날로그 작업 이전에 송신신호의 처리단계가 상기 송신신호를 상기 디지털영역으로 제한하는 것을 포함하며, 상기 보상단계가 상기 제한과 관련하여 송신신호를 정형화 (shaping)하는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

## 청구항 4

제 2 항에 있어서, 상기 디지털-아날로그 변환작업 이전 송신신호의 처리단계가 상기 디지털 영역에 따라 송신신호의 진폭을 스케일링함을 포함하고, 상기 보상단계가 송신신호가 전송되는 수신기에서보상 스케일링(complementary scaling)을 위해 상기 스케일링 값을 송신하는 단계를 더욱 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

## 청구항 5

제 1 항에 있어서, 상기 시스템이 송,수신 신호 경로 사이에 반향 소거기(26)를 포함하며, 상기 변환처리의 보상단계가 오직 상기 변환 처리된후의 송신신호에 응답하여서만 반향소거를 수행하는 단계로 구성되는 것임을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

## 청구항 6

제 5 항에 있어서, 상기 변환처리 후에 상기 송신신호를 복조시키어 반향소거를 수행하기 위한

복조된 신호를 발생시키도록 함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

#### 청구항 7

제 5 항에 있어서, 디지털-아날로그 변환작업 이전에 송신신호를 처리하는 단계가 상기 송신신호를 상기 디지털 영역으로 제한함을 포함하며, 상기 처리에 대한 보상단계가 상기 제한과 관련하여 송신신호를 정형화하는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

#### 청구항 8

제 5 항에 있어서, 상기 디지털-아날로그 변환작업 이전 송신신호의 처리단계가 상기 디지털 영역에 따라 송신신호의 진폭을 스케일링함을 포함하고, 상기 보상단계가 송신신호가 전송되는 수신기에서보상 스케일링(complementary scaling)을 위해 상기 스케일링 값을 송신하는 단계를 더욱 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

#### 청구항 9

제 1 항에 있어서, 상기 디지털-아날로그 변화작업이 사전에 정해진 디지털영역내에서 상기 송신 신호에 대한 디지털 신호 처리 작업을 포함하며, 상기 디지털-아날로그 변환작업 이전에 송신신호를 처리 하는 단계가 상기 송신신호를 상기 디지털 영역으로 제한함을 포함하며, 상기 처리에 대한 보상단계가 상 기 제한과 관련하여 송신신호를 정형화하는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자 화 효과 소거방법.

### 청구항 10

제 1 항에 있어서, 상기 디지털-아날로그 변환작업이 사전에 정해진 디지털영역내에서 송신신호에 대한 디지털 신호 처리 작업을 포함하며, 상기 디지털-아날로그 변환작업 이전 송신신호의 처리 단계가 상기 디지털 영역에 따라 진폭을 스케일링함을 포함하며, 그리고 상기 처리에 대한 보상단계가 송신신호를 받는 수신기에서 보상 스케일링을 위해 상기 스케일링 값을 전송하는 것을 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거방법.

## 청구항 11

송신신호를 위한 송신경로와 수신신호를 위한 수신경로가 하이브리드회로(16)를 통해 양방향 송 신경로(8)에 연결되며, 디지털-아날로그 변환기가 상기 송신경로내에 있게되는 송신시스템에서.

상기 신호를 사전에 정해진 디지털 영역으로 클리핑 및 양자화함에 기인하는 송신신호의 비선형 왜곡에 대한 보상방법에 있어서, 상기 방법이;

상기 디지털-아날로그 변환 이전에 송신신호를 상기 사전에 정해진 디지털 영역으로 제한시키는 단계.

상기 제한단계 전후에서의 송신신호 차이로부터 에러신호를 발생시키는 단계,

상기 에러신호로부터 추정 반향 응답을 발생시키는 단계, 그리고

수신경로에서의 수신신호로부터 상기 추정 반향 응답을 빼주는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거 보상방법.

#### 청구항 12

송신신호를 위한 송신경로와 수신신호를 위한 수신경로가 하이브리드회로(16)를 통해 양방향 송 신경로(8)에 연결되며, 디지털-아날로그 변환기가 상기 송신경로내에 있게되며, 반향 소거기가 상기 송신 경로와 수신경로 사이에 제공되는 송신시스템에서.

상기 신호를 사전에 정해진 디지털 영역으로 클리핑 및 양자화함에 기인하는 송신신호의 비선형 왜곡에 대한 보상방법에 있어서, 상기 방법이;

상기 디지털-아날로그 변환 이전에 송신신호를 상기 사전에 정해진 디지털 영역으로 제한시키는 단계, 그리고

상기 제한단계 이후에 상기 송신신호를 상기 반향 소거기로 공급시키는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거 보상방법.

#### 청구항 13

제 12 항에 있어서, 상기 제한 단계 이후에 송신신호를 복조하여 복조된 송신신호를 상기 반향소 거기로 공급하도록 하는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 소거 보상 방법.

### 청구항 14

송신 및 수신경로가 하이브리드 회로(16)를 통해 양방향 송신경로(18)에 연결되며, 송신신호가 DAC에 의해 사전에 정해진 영역으로 클리핑을 받게되는 샘플들을 포함하는 송신 시스템의 클리핑 효과 감소 방법에 있어서, 상기 방법이;

DAC 사전에 정해진 영역으로 송신 신호샘플의 진폭을 제한하는 단계, 그리고

사전에 정해진 영역으로 제한된 진폭을 갖는 각 샘플에 대해, 상기 진폭 제한의 양(amount)에 따라 하나 이상의 이웃 샘플의 진폭을 수정하는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양

자화 효과 감소방법.

#### 청구항 15

제 14 항에 있어서, 반향소거기(26)가 송신, 수신경로 사이에 제공되며, 상기 방법이 상기 제한 후에만 반향소거기에 송신신호를 공급하는 단계를 더욱 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 감소방법.

#### 청구항 16

송신 및 수신경로가 하이브리드 회로(17)를 통해 양방향 송신경로(18)에 연결되며, 송신신호가 사전에 정해진 영역으로 클리핑을 받으며 상기 사전에 정해진 영역내에서 사전에 정해진 정밀도로 양자화 를 받는 샘플을 포함하는 송신시스템의 클리핑 및 양자화 효과 감소방법에 있어서, 상기 방법이;

상기 영역에 따라 송신신호의 진폭을 스케일링하는 단계,

송신신호가 수신되는 수신기에서 보상 스케일링을 위해 상기 스케일링 값을 전송하는 단계를 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 감소방법.

### 청구항 17

제 16 항에 있어서, 반향소거기(26)가 송신경로와 수신경로 사이에 제공되며, 상기 방법이 상기 스케일링 후에만 반향소거기로 송신신호를 공급하는 단계를 더욱 포함함을 특징으로 하는 송신시스템의 클리핑 및 양자화 효과 감소방법.

#### 청구항 18

송신신호를 위한 송신경로, 수신신호를 위한 수신경로, 송신경로와 수신경로를 양방향 송신경로 (18)에 연결하는 하이브리드회로(16), 송신경로와 수신경로 사이에 결합되는 반향소거기(echo canceller)(26), 그리고 상기 송신경로가 사전에 정해진 디지털영역 내에서 사전에 정해진 디지털 정밀도로 송신신호에 작용할 수 있기 위한 DAC(디지털/아날로그 변환기) 및 여파유니트(14)를 포함하는 송신 시스템 터미널에 있어서.

제한 및 종결유니트(limiting and/or truncation unit)(28)가 상기 DAC 및 여파유니트(14)에 앞서서 상기 디지털 영역내로 송신신호를 제한하고, 상기 디지털 신호를 상기 디지털 정밀도로 양자화(quantizing)하도록 하며,

상기 송신경로로부터 반향 소거기(26)로 전달되는 각 입력신호가 상기 제한 및 종결유니트(28) 이후의 송신경로로부터 얻어지게 됨을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신 시스템.

#### 청구항 19

제 18 항에 있어서, 반향소거유니트(58)에 복조된 신호를 전달하기 위해 제한 및 종결유니트(28) 이후의 송신경로에서의 변조된 송신신호에 응답하는 복조기(62)를 포함함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

#### 청구항 20

제 18 항에 있어서, 사전에 정해진 디지털 영역내에서 사전에 정해진 디지털신호 정밀도로 송신 신호에 작용하도록 하기 위한 기능이 DAC(디지털/아날로그 변환기) 유니트(14)를 포함함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

## 청구항 21

제 18 항에 있어서, 사전에 정해진 디지털 영역내에서 사전에 정해진 디지털신호 정밀도로 송신 신호에 작용하도록 하기 위한 기능이 DAC(디지털/아날로그 변환기) 유니트(14)를 포함함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

## 청구항 22

제 18 항에 있어서, 상기 제한 및 종결유니트(28)가 상기 사전에 정해진 디지털 영역으로 송신신호 샘플들을 제한하도록, 그리고 진폭이 상기 디지털 영역으로 제한된 각 샘플들에 대해서, 상기 진폭 제한의 폭에 따라 하나 이상의 이웃 샘플을 수정하도록 배열되는 것을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

## 청구항 23

송신신호를 위한 송신경로, 수신신호를 위한 수신경로, 송신경로와 수신경로를 양방향 송신경로 (18)에 연결하는 하이브리드회로(16), 송신경로와 수신경로 사이에 결합되는 반향소거기(echo canceller)(26), 그리고 상기 송신경로가 사전에 정해진 디지털영역 내에서 사전에 정해진 디지털 정밀도로 송신신호에 작용할 수 있기 위한 DAC(디지털/아날로그 변환기) 및 여파유니트(14)를 포함하는 송신 시스템 터미널에 있어서,

상기 디지털 영역내로 송신신호를 제한하고, 상기 디지털 신호를 상기 디지털 정밀도로 양자화 (quantizing)한 뒤에 제한 및 종결유니트(limiting and/or truncation unit)(28)가 있게되며,

상기 제한 및 종결 유니트(28) 이전 및 이후 송신신호 사이의 차이(E)에 응답하여 이같은 차이로 부터 추정된 반향 응답을 발생시키도록 하는 반향 추정유니트(30)를 더욱더 포함하고, 그리고 상기 수신경로가 상기 수신신호에서 상기 추정된 반향 응답을 빼기위한 감산유니트(32)를 포함함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

### 청구항 24

제 23 항에 있어서, 사전에 정해진 디지털 영역내에서 사전에 정해진 디지털신호 정밀도로 송신 신호에 작용하도록 하기 위한 기능이 DAC(디지털/아날로그 변환기) 유니트(14)를 포함함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

#### 청구항 25

제 23 항에 있어서, 상기 제한 및 종결유니트(28)가 상기 사전에 정해진 디지털 영역으로 송신신호 샘플들을 제한하도록, 그리고 진폭이 상기 디지털 영역으로 제한된 각 샘플들에 대해서, 상기 진폭 제한의 폭에 따라 적어도 하나의 이웃 샘플을 수정하도록 배열되는 것을 특징으로 하는 클리핑 및 양자화효과 소거기 포함의 디지털 송신시스템.

#### 청구항 26

송신신호를 위한 송신경로, 수신신호를 위한 수신경로, 송신경로와 수신경로를 양방향 송신경로 (18)에 연결하는 하이브리드회로(16), 송신경로와 수신경로 사이에 결합되는 반향소거기(echo canceller)(26), 그리고 상기 송신경로가 사전에 정해진 디지털영역 내에서 사전에 정해진 디지털 정밀도로 송신신호 샘플들에 작용할 수 있기 위한 DAC(디지털/아날로그 변환기) 및 여파유니트(14)를 포함하는 송신 시스템 터미널에 있어서,

제한 및 종결유니트(limiting and/or truncation unit)(28)가 상기 DAC 및 여파유니트(14)에 앞서서 상기 디지털 영역내로 송신신호 샘플들을 제한하고, 상기 진폭이 상기 디지털 영역으로 제한된 각샘플에 대해서 상기진폭 제한 폭에 따라 하나 이상의 이웃하는 샘플 진폭을 수정하도록 함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

## 청구항 27

제 26 항에 있어서, 송신경로와 수신경로사이에 결합된 반향소거기(26)를 포함하며, 상기 송신경 로로부터 상기 반향소거기로의 입력신호 각각이 상기 디지털 영역으로 송신신호 샘플들의 진폭을 제한하 도록 하는 제한 및 종결유니트(28)이후의 송신경로로부터 얻어지게 됨을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

#### 청구항 28

송신신호를 위한 송신경로, 수신신호를 위한 수신경로, 송신경로와 수신경로를 양방향 송신경로 (18)에 연결하는 하이브리드회로(16), 송신경로와 수신경로 사이에 결합되는 반향소거기(echo canceller)(26), 그리고 상기 송신경로가 사전에 정해진 디지털영역 내에서 사전에 정해진 디지털 정밀도로 송신신호 샘플들에 작용할 수 있기 위한 DAC(디지털/아날로그 변환기) 및 여파유니트(14)를 포함하는 송신 시스템 터미널에 있어서,

제한 및 종결유니트(limiting and/or truncation unit)(28)가 상기 DAC 및 여파유니트(14)에 앞서서 상기 디지털 영역에 따라 송신신호 샘플들 진폭을 스케일링(scale)하며, 수신기에서 보상 스케일링(complementary scaling)을 위해 상기 송신신호의 일부로서 상기 스케일링 값을 제공하도록 함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

#### 청구항 29

제 28 항에 있어서, 송신경로와 수신경로 사이에 결합된 반향소거기(26)를 포함하며, 상기 송신 경로부터 상기 반향 소거기로의 입력신호 각각이 상기 디지털 영역에 따라 송신신호 샘플들의 진폭을 스 케일링하도록 하는 제한 및 종결유니트(28)이후의 송신경로로부터 얻어지게 됨을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

### 청구항 30

송신신호 샘플들을 진동수 영역으로부터 시간 영역으로 변환하기 위한 IFFT(역 고속 푸리에 변환)(42) 그리고 송신을 위해 시간 영역내 신호샘플들을 아날로그 신호로 변환시키는 DAC(14)를 포함하며, 상기 DAC 가 IFFT 보다 낮은 사전에 정해진 디지털 신호영역 및 디지털 정밀도를 갖도록된 송신경로.

수신신호를 디지털 신호 샘플로 변환하는 ADC(20), 시간 영역으로부터 주파수 도메인으로 수신신호 샘플들을 변환하기 위한 FFT(52)를 포함하며, 상기 수신신호로부터 반향신호를 빼기 위한 감산기(54)를 더욱 포함하는 수신경로.

송신경로와 수신경로에 결합되어 양방향 송신경로(18)로 신호를 보내기도 하고 이로부터 신호를 수신할 수 있도록 된 하이브리드회로(16), 그리고

송신경로에 결합된 적어도 하나의 입력단자와 상기 반향신호를 제공하는 하나의 출력단자를 갖는 반향소거기(58)로 구성되는 다중 반송파 변조를 사용하는 송신시스템에 있어서.

송신경로가 DAC(14)의 디지털 신호영역 및 디지털 정밀도로 ITTF(42)로부터 나오는 신호샘플들을 제한하고 종결하도록 배열된 제한 및 종결 유니트를 포함하여, 상기 송신경로로부터 나오는 반향소거기 (58)의 각 입력이 제한 및 종결유니트(28) 이후의 송신경로로부터 얻어지게 됨을 특징으로 하는 클리핑및 양자화 효과 소거기 포함의 디지털 송신시스템.

## 청구항 31

제 30 항에 있어서, 상기 반향소거기(58)가 진동수-영역 반향소거기(68)를 포함하며, 수신경로내의 감산기가 FFT(52)의 출력으로부터 진동수-영역 반향소거기의 진동수-영역 반향 신호 출력을 빼기 위해 배열되는 감산유니트(54)를 포함하고, 상기 송신시스템이 진동수-영역 반향소거기(68)로의 입력신호를 구성하기 위해 제한 및 종결유니트(28)의 출력으로부터 나오는 제한되고 종결된 신호샘플들을 진동수-영역으로 변환하기 위해 배열되는 FFT(62)를 포함함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의디지털 송신시스템.

#### 청구항 32

송신신호 샘플들을 진동수-영역으로부터 시간 영역으로 변환하기 위한 IFFT(역 고속 푸리에 변환)(42) 그리고 송신을 위해 시간 영역내 신호 샘플들을 아날로그 신호로 변환시키는, DAC(14)를 포함 하며, 그리고 상기 DAC가 IFFT 보다 낮은 사전에 정해진 디지털 신호영역 및 디지털 정밀도를 갖도록된 송신경로.

수신신호를 디지털 신호 샘플로 변환하는 ADC(20), 시간 영역으로부터 진동수 영역으로 수신신호 샘플들을 변환하기 위한 FFT(52)를 포함하며. 그리고 상기 수신신호로부터 반향신호를 빼기 위한 감산기 (48,54)를 포함하는 수신경로.

송신경로와 수신경로에 결합되어 양방향 송신경로(18)로 신호를 보내기도 하고 이로부터 신호를 수신할 수도 있도록된 하이브리드회로(16), 그리고

송신경로에 결합된 적어도 하나의 입력단자와 상기 반향신호를 제공하는 하나의 출력단자를 갖는 반향소거기(58)로 구성되는 다중 반송파 변조를 사용하는 송신시스템에 있어서,

송신경로가 DAC(14)의 디지털 신호영역 및 디지털 정밀도로 IFFT(42)로부터 나오는 신호 샘플들을 제한하고 종결하도록 배열된 제한 및 종결 유니트(28)를 포함하며,

상기 제한 및 종결 유니트(28) 이전과 이후 송신신호 샘플들 사이의 차이(E)에 응답하여 상기 차이로부터 한 추정 반향응답을 발생시키기 위한 반향 응답 추정 유니트(30)가 제공되고, 그리고

상기 감산기(48,54)가 상기 수신신호로부터 상기 추정된 반향 응답을 빼도록함을 특징으로 하는 클리핑 및 양자화 효과 소거기 포함의 디지털 송신시스템.

#### 요약

송신시스템이 양방향 송신경로(18)에 하이브리드회로(16)를 통해 연결되는 송신 및 수신경로를 포함한다. 상기 송신경로는 주어진 영역 및 정밀도를 갖는 DAC(14)를 포함하며, 송신경로 신호가 DAC 에 앞서 상기영역 및 정밀도에 대해 제한되며 종결된다. 반향소거기(26)가 송신경로와 수신경로 사이에 연결 될수 있으며, 제한 및 종결전후의 송신경로 신호의 차가 수신경로 신호로부터 빼지는 추정 반향응답을 발 생시키기 위해 사용되며, 또는 반향소거기로 들어가는 모든 입력이 제한 및 종결다음의 송신경로로부터 나올수도 있다. 송신신호 샘플들의 진폭은 제한에 의해 정형화될수 있다. 만일 시스템이 다중 반송파를 사용한다면, 진폭은 클리핑을 감소시키기 위해 스케일링될수 있으며, 스케일링 값을 원거리 수신자에게 송신한다.

### 도면