# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

*H01L 29/786* (2006.01) *G02F 1/136* (2006.01) *H01L 21/336* (2006.01)

(21) 출원번호 **10-2011-0046116**

(22) 출원일자 **2011년05월17일** 심사청구일자 **2016년05월17일**

(65) 공개번호 **10-2012-0128274**

(43) 공개일자 2012년11월27일

(56) 선행기술조사문헌

US20100117076 A1\*

US20100117077 A1\*

KR100767917 B1\*

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2018년02월21일

(11) 등록번호 10-1830170

(24) 등록일자 2018년02월12일

(73) 특허권자

## 삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성로 1 (농서동)

(72) 발명자

#### 왕성민

서울특별시 도봉구 노해로70길 12 5동 405호 (창 동,동아아파트)

#### 안기완

서울특별시 양천구 목1동 하이페리온 102동 (뒷면에 계속)

(74) 대리인 **박영우**

전체 청구항 수 : 총 10 항

심사관 : 김종호

(54) 발명의 명칭 산화물 반도체 소자, 산화물 반도체 소자의 제조 방법, 산화물 반도체소자를 포함하는 표시 장치 및 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법

#### (57) 요 약

산화물 반도체 소자는, 기판 상에 배치되는 게이트 전극, 리세스 구조를 포함하는 게이트 절연층, 게이트 절연층의 일측 상에 배치되는 소스 전극, 게이트 절연층의 타측 상에 배치되는 드레인 전극. 게이트 절연층, 소스 전극 및 드레인 전극 상에 배치되는 액티브 패턴을 포함할 수 있다. 리세스 구조는 게이트 전극의 상부에 위치할 수 있으며, 액티브 패턴은 리세스 구조를 채울 수 있다. 산화물 반도체 소자가 리세스 구조를 갖는 게이트 절연층을 구비함에 따라, 전하 이동도, 문턱 전압 산포, 동작 전류 등의 다양한 전기적인 특성들을 향상시킬 수 있다.

#### 대 표 도 - 도1

# (72) 발명자

# 윤주선

서울특별시 송파구 신천로 45, 장미아파트 15동 1307호 (신천동)

# 김기홍

서울특별시 영등포구 도영로 2-5, 코오롱아파트 101동 1701호 (대림동)

# 명 세 서

# 청구범위

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

#### 청구항 20

기판 상에 게이트 전극을 형성하는 단계;

상기 기판 상에 상기 게이트 전극을 덮는 게이트 절연층을 형성하는 단계;

상기 게이트 절연층 상에 전극층을 형성하는 단계;

상기 전극층 상에 마스크 패턴을 형성하는 단계;

상기 마스크 패턴을 이용하여 상기 전극층을 식각하여 상기 게이트 절연층 상에 소스 전극 및 드레인 전극을 형성하는 단계;

상기 소스 전극 및 상기 드레인 전극 사이의 상기 게이트 절연층에 리세스 구조를 형성하는 단계; 및

상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전극 상에 액티브 패턴을 형성하는 단계를 포함하며,

상기 리세스 구조를 형성하는 단계는,

상기 소스 및 드레인 전국 사이의 상기 게이트 절연층에 대해 플라즈마 처리를 수행하여 상기 게이트 절연층에 예비 리세스 구조를 형성하는 단계;

상기 소스 및 드레인 전극으로부터 상기 마스크 패턴을 제거하는 단계; 및

상기 예비 리세스 구조를 갖는 게이트 절연층에 대해 세정 처리를 수행하는 단계를 포함하는 산화물 반도체 소자의 제조 방법.

## 청구항 21

삭제

#### 청구항 22

제20항에 있어서, 상기 플라즈마 처리는 황 불화물을 함유하는 가스, 염소 불화물을 함유하는 가스, 염화수소를 함유하는 가스, 붕소 염화물을 함유하는 가스, 탄화수소를 함유하는 가스, 산소를 함유하는 가스 및 오존을 함유하는 가스로 이루어진 그룹으로부터 선택된 하나 이상의 가스로부터 생성되는 플라즈마를 사용하여 수행되는 것을 특징으로 하는 산화물 반도체 소자의 제조 방법.

# 청구항 23

제20항에 있어서, 상기 세정 처리는 금속 화합물을 제거할 수 있는 용액을 사용하여 수행되는 것을 특징으로 하는 산화물 반도체 소자의 제조 방법.

# 청구항 24

제23항에 있어서, 상기 금속 화합물을 제거할 수 있는 용액은 불화수소를 함유하는 용액, 염화수소를 함유하는

용액, 인산을 함유하는 용액, 수산화칼륨을 함유하는 용액, 브롬화수소를 함유하는 용액 및 브롬화요오드를 함 유하는 용액으로부터 선택된 하나 이상을 포함하는 것을 특징으로 하는 산화물 반도체 소자의 제조 방법.

#### 청구항 25

삭제

## 청구항 26

삭제

# 청구항 27

삭제

## 청구항 28

제20항에 있어서, 상기 전극층을 형성하는 단계는,

상기 게이트 절연층 상에 제1 전극막을 형성하는 단계: 및

상기 제1 전극막 상에 제2 전극막을 형성하는 단계를 더 포함하는 것을 특징으로 하는 산화물 반도체 소자의 제조 방법.

## 청구항 29

제28항에 있어서, 상기 제2 전극막을 형성하는 단계는 상기 제1 전극막을 질화 처리하는 단계를 포함하는 것을 특징으로 하는 산화물 반도체 소자의 제조 방법.

## 청구항 30

제29항에 있어서, 상기 제2 전극막을 형성하는 단계는, 상기 제1 전극막을 질소를 포함하는 분위기 하에서 열처리하는 단계 또는 상기 제1 전극막을 질소를 함유하는 가스로부터 생성된 플라즈마로 처리하는 단계를 포함하는 것을 특징으로 하는 산화물 반도체 소자의 제조 방법.

# 청구항 31

제28항에 있어서, 상기 소스 전극 및 드레인 전극을 형성하는 단계는, 상기 제2 전극막 및 상기 제1 전극막을 부분적으로 식각하여, 상기 게이트 전극의 일측 상에 제1 전극 패턴 및 제2 전극 패턴을 형성하고, 상기 게이트 전극의 타측 상에 제3 전극 패턴 및 제4 전극 패턴을 형성하는 단계를 더 포함하는 것을 특징으로 하는 산화물반도체 소자의 제조 방법.

# 청구항 32

삭제

## 청구항 33

삭제

## 청구항 34

삭제

#### 청구항 35

삭제

## 청구항 36

삭제

#### 청구항 37

삭제

## 청구항 38

기판 상에 게이트 전극을 형성하는 단계;

상기 기판 상에 상기 게이트 전극을 덮는 게이트 절연층을 형성하는 단계;

상기 게이트 절연층 상에 전극층을 형성하는 단계;

상기 전극층 상에 마스크 패턴을 형성하는 단계;

상기 마스크 패턴을 이용하여 상기 전극층을 식각하여 상기 게이트 절연층 상에 소스 전극 및 드레인 전극을 형성하는 단계;

상기 소스 전극 및 상기 드레인 전극 사이의 상기 게이트 절연층에 리세스 구조를 형성하는 단계;

상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전극 상에 액티브 패턴을 형성하는 단계;

상기 드레인 전극에 전기적으로 연결되는 제1 전극을 형성하는 단계;

상기 제1 전극 상에 발광층을 형성하는 단계; 및

상기 발광층 상에 제2 전극을 형성하는 단계를 포함하며,

상기 리세스 구조를 형성하는 단계는,

상기 소스 및 드레인 전극 사이의 상기 게이트 절연층에 대해 플라즈마 처리를 수행하여 상기 게이트 절연층에 예비 리세스 구조를 형성하는 단계;

상기 소스 및 드레인 전극으로부터 상기 마스크 패턴을 제거하는 단계; 및

상기 예비 리세스 구조를 갖는 게이트 절연층에 대해 세정 처리를 수행하는 단계를 포함하는 표시 장치의 제조 방법.

## 청구항 39

삭제

#### 청구항 40

삭제

# 청구항 41

삭제

#### 청구항 42

제38항에 있어서, 상기 전극층을 형성하는 단계는,

상기 게이트 절연층 상에 제1 전극막을 형성하는 단계; 및

상기 제1 전극막을 질화 처리하여 상기 제1 전극막 상에 제2 전극막을 형성하는 단계를 더 포함하며,

상기 소스 전극 및 상기 드레인 전극을 형성하는 단계는,

상기 제2 전극막 및 상기 제1 전극막을 부분적으로 식각하여, 상기 게이트 전극의 일측 상에 제1 전극 패턴 및 제2 전극 패턴을 형성하고, 상기 게이트 전극의 타측 상에 제3 전극 패턴 및 제4 전극 패턴을 형성하는 단계를 더 포함하는 것을 특징으로 하는 표시 장치의 제조 방법.

## 발명의 설명

## 기술분야

[0001] 본 발명은 산화물 반도체 소자, 산화물 반도체 소자의 제조 방법, 산화물 반도체 소자를 포함하는 표시 장치 및 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법에 관한 것이다. 보다 상세하게는, 본 발명은 리세스 구조(recess structure)를 갖는 게이트 절연충을 포함하는 산화물 반도체 소자, 이러한 산화물 반도체 소자의 제조 방법, 상기 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법에 관한 것이다.

#### 배경기술

- [0002] 종래의 바텀 게이트(bottom gate) 구조를 갖는 박막 트랜지스터(TFT)는, 기판 상에 위치하는 게이트 전국, 상기 게이트 전국 상에 위치하는 게이트 절연충, 상기 게이트 절연충 상에 배치되는 소스 전국과 드레인 전국, 그리고 상기 소스 전국과 상기 드레인 전국에 사이의 게이트 절연충과 상기 소스 및 드레인 전국에 접촉되는 액티브 충(active layer)을 포함한다.

- [0003] 종래의 바텀 게이트 구조를 갖는 트랜지스터의 제조 방법에 있어서, 게이트 절연층 상에 소스 전극 및 드레인 전극을 형성하기 위한 금속층이 형성되기 때문에, 상기 금속층을 증착하는 동안 상기 게이트 절연층에 내부 응력(internal stress)이 생성되기 쉽다. 이와 같이 내부 응력이 생성된 게이트 절연층 상에 액티브층을 형성할 경우, 상기 트랜지스터의 전압-전류 특성이 열화되는 문제점이 발생한다. 또한, 상기 금속층을 식각하여 상기소스 및 드레인 전극을 형성하는 동안, 상기 게이트 절연층의 표면에 식각 손상이 발생하고, 금속 입자들, 금속화합물 등과 같은 반응 부산물들이 상기 게이트 절연층 상에 잔류하게 되며. 이에 따라 상기 액티브층과 상기게이트 절연층 사이의 계면 상태가 불균일해져 결국 상기 트랜지스터가 문턱 전압(Vth)의 산포의 증가, 전하 이동도(mobility), 구동 전류(Ion)의 감소 등과 같은 다양한 전기적인 특성들이 열화되는 문제점이 나타난다. 특히, 액티브층이 반도체 산화물로 이루어진 산화물 반도체 소자의 경우에는 전기적인 특성 변화에 매우 민감하기때문에, 전술한 바와 같이 전기적인 특성이 열화된 산화물 반도체 소자를 액정 표시(LCD) 장치, 유기 발광 표시(OLED) 장치 등의 표시 장치에 적용하기는 어렵다.

## 발명의 내용

# 해결하려는 과제

- [0004] 본 발명의 일 목적은 리세스 구조를 갖는 게이트 절연층을 구비하여 향상된 전기적인 특성을 확보할 수 있는 산화물 반도체 소자를 제공하는 것이다.

- [0005] 본 발명의 다른 목적은 리세스 구조를 갖는 게이트 절연충을 구비하여 향상된 전기적인 특성을 확보할 수 있는 산화물 반도체 소자의 제조 방법을 제공하는 것이다.

- [0006] 본 발명의 또 다른 목적은 리세스 구조를 포함하여 전기적인 특성이 개선된 산화물 반도체 소자를 포함하는 표 시 장치를 제공하는 것이다.

- [0007] 본 발명의 또 다른 목적은 리세스 구조를 포함하여 전기적인 특성이 개선된 산화물 반도체 소자를 포함하는 표 시 장치의 제조 방법을 제공하는 것이다.

- [0008] 그러나, 본 발명이 해결하고자 하는 과제는 상술한 목적들에 한정되는 것이 아니며, 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위에서 다양하게 확장될 수 있을 것이다.

## 과제의 해결 수단

- [0009] 전술한 본 발명의 일 목적을 달성하기 위하여, 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자는 게이트 전국, 리세스 구조를 갖는 게이트 절연층, 소스 전국, 드레인 전국 및 액티브 패턴을 포함할 수 있다. 상기 게이트 전국은 기판 상에 배치될 수 있으며, 상기 게이트 절연층은 상기 게이트 전국을 덮으며 상기 기판 상에 배치될 수 있다. 상기 리세스 구조는 상기 게이트 전국의 상부에 위치할 수 있다. 상기 소스 전국 및 상기 드레인 전국은 각기 상기 게이트 절연층의 일측 및 타측 상에 배치될 수 있다. 상기 액티브 패턴은 상기 리세스 구조를 채울 수 있으며, 상기 소스 전국 및 상기 드레인 전국 상에 배치될 수 있다. 상기 리세스 구조는 상기 게이트 절연층에 플라즈마 처리 및/또는 세정 처리를 수행하여 형성될 수 있다.

- [0010] 예시적인 실시예들에 있어서, 상기 소스 전극 및 상기 드레인 전극은 각기 금속, 합금, 금속 질화물, 도전성 금

속 산화물, 투명 도전성 물질 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0011] 예시적인 실시예들에 따르면, 상기 액티브 패턴은 이성분계 화합물, 삼성분계 화합물 또는 사성분계 화합물을 함유하는 반도체 산화물을 포함할 수 있다. 예를 들면, 상기 액티브 패턴은 인듐, 아연, 갈륨, 주석, 티타늄, 알루미늄, 하프늄, 지르코늄, 마그네슘 등을 함유하는 반도체 산화물을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 포함될 수 있다. 다른 예시적인 실시예들에 있어서, 상기 액티브 패턴은 상기 반도체 산화물에 리튬, 나트륨, 망간, 니켈, 팔라듐, 구리, 탄소, 질소, 인, 티타늄, 지르코늄, 바나듐, 루테늄, 게르마늄, 주석, 불소 등이 첨가된 조성을 가질 수 있다. 이들은 단독으로 또는 서로 조합되어 첨가될 수 있다.

- [0012] 예시적인 실시예들에 있어서, 상기 리세스 구조는 상기 기판에 대해 제1 경사 각도를 갖는 측벽을 포함할 수 있고, 상기 소스 전극 및 상기 드레인 전극은 각기 상기 기판에 대해 제2 경사 각도를 갖는 측벽을 포함할 수 있다. 이 경우, 상기 제2 경사 각도는 상기 제1 경사 각도보다 실질적으로 클 수 있다. 예를 들면, 상기 제1 경사 각도와 상기 제2 경사 각도 사이의 비는 약 1.0: 0.5 내지 약 1.0: 9.0 정도가 될 수 있다.

- [0013] 예시적인 실시예들에 있어서, 상기 액티브 패턴의 하부는 상기 리세스 구조를 채울 수 있으며, 상기 액티브 패턴의 중앙부는 상기 소스 및 드레인 전국에 접촉될 수 있다. 여기서, 상기 액티브 패턴의 중앙부의 측벽의 경사 각도가 상기 액티브 패턴의 하부의 측벽 경사 각도보다 실질적으로 클 수 있다. 예를 들면, 상기 액티브 패턴의 하부의 측벽의 경사 각도와 상기 액티브 패턴의 중앙부의 측벽의 경사 각도 사이의 비는 약 1.0: 0.5 내지 약 1.0: 9.0 정도가 될 수 있다.

- [0014] 예시적인 실시예들에 있어서, 상기 게이트 절연층은 실질적으로 평탄한 상면을 가질 수 있다. 이 경우, 상기 리세스 구조의 깊이와 상기 게이트 절연층의 두께 사이의 비는 약 1.0: 1.7 내지 약 1.0: 30.0 정도가 될 수 있다.

- [0015] 다른 예시적인 실시예들에 있어서, 상기 게이트 절연층은 상기 게이트 전극에 인접하는 단차부들을 포함할 수 있다. 여기서, 상기 리세스 구조의 깊이와 상기 게이트 절연층의 두께 사이의 비는 약 1.0: 1.7 내지 약 1.0: 10.0 정도가 될 수 있다. 또한, 상기 소스 전극 및 상기 드레인 전극은 각기 상기 게이트 절연층의 단차부들에 인접하는 단차부를 포함할 수 있다.

- [0016] 예시적인 실시예들에 있어서, 상기 소스 전극은 제1 전극 패턴 및 제2 전극 패턴을 포함할 수 있고, 상기 드레인 전극은 제3 전극 패턴 및 제4 전극 패턴을 포함할 수 있다. 예를 들면, 상기 제1 전극 패턴 및 상기 제3 전극 패턴은 각기 금속, 합금, 투명 도전성 물질 등을 포함할 수 있다. 또한, 상기 제2 전극 패턴 및 상기 제4 전극 패턴은 각기 금속 질화물을 포함할 수 있다.

- [0017] 상술한 본 발명의 다른 목적을 달성하기 위하여, 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법에 있어서, 기판 상에 게이트 전극을 형성한 후, 상기 기판 상에 상기 게이트 전극을 덮는 게이트 절연 충을 형성할 수 있다. 상기 게이트 절연충 상에 전극충을 형성한 다음, 상기 전극충 상에 마스크 패턴을 형성할 수 있다. 상기 마스크 패턴을 식각 마스크로 이용하여 상기 전극충을 식각함으로써 상기 게이트 절연충 상에 소스 전극 및 드레인 전극을 형성한 후, 상기 소스 전극 및 상기 드레인 전극 사이의 상기 게이트 절연충에 리세스 구조를 형성할 수 있다. 상기 게이트 절연충, 상기 소스 전극 및 상기 드레인 전극 상에는 액티브 패턴이 형성될 수 있다.

- [0018] 예시적인 실시예들에 있어서, 상기 리세스 구조는 플라즈마 처리 및/또는 세정 처리를 수행하여 수득될 수 있다. 예를 들면, 상기 플라즈마 처리는 황 불화물을 함유하는 가스, 염소 불화물을 함유하는 가스, 염화수소를 함유하는 가스, 붕소 염화물을 함유하는 가스, 탄화수소를 함유하는 가스, 산소를 함유하는 가스, 오존을 함유하는 가스 등으로부터 생성되는 플라즈마를 사용하여 수행될 수 있다. 이들 가스는 단독으로 또는 서로 조합되어 사용될 수 있다. 또한, 상기 세정 처리는 금속 화합물을 제거할 수 있는 용액을 사용하여 수행될 수 있다. 예를 들면, 상기 금속 화합물을 제거할 수 있는 용액은 불화수소를 함유하는 용액, 염화수소를 함유하는 용액, 인산을 함유하는 용액, 수산화칼륨을 함유하는 용액, 브롬화요오드를 함유하는 용액을 포함할 수 있다. 이들 용액은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0019] 예시적인 실시예들에 있어서, 상기 리세스 구조의 형성 후에 상기 소스 및 드레인 전극으로부터 상기 마스크 패턴을 제거할 수 있다.

- [0020] 예시적인 실시예들에 따른 상기 리세스 구조를 형성하는 과정에 있어서, 상기 소스 및 드레인 전극 사이의 상기 게이트 절연층에 플라즈마 처리를 수행하여 상기 게이트 절연층에 예비 리세스 구조를 형성할 수 있다. 상기 소스 및 드레인 전극으로부터 상기 마스크 패턴을 제거한 후, 상기 예비 리세스 구조를 갖는 게이트 절연층에 세

정 처리를 수행할 수 있다.

- [0021] 예시적인 실시예들에 따른 상기 리세스 구조를 형성하는 과정에 있어서, 상기 소스 및 드레인 전극 사이의 상기 게이트 절연층에 대해 플라즈마 처리를 수행하여 상기 게이트 절연층에 예비 리세스 구조를 형성한 후, 상기 예비 리세스 구조를 갖는 게이트 절연층에 대해 세정 처리를 수행하여 상기 게이트 절연층에 상기 리세스 구조를 형성할 수 있다. 상기 리세스 구조의 형성 후에 상기 소스 및 드레인 전극으로부터 상기 마스크 패턴을 제거할수 있다.

- [0022] 예시적인 실시예들에 따른 상기 전극층을 형성하는 과정에 있어서, 상기 게이트 절연층 상에 제1 전극막을 형성한 다음, 상기 제1 전극막 상에 제2 전극막을 형성할 수 있다. 여기서, 상기 제2 전극막은 상기 제1 전극막의 상부를 질화 처리하여 수득될 수 있다. 예를 들면, 상기 제2 전극막은, 상기 제1 전극막을 질소를 포함하는 분위기 하에서 열처리하거나 상기 제1 전극막을 질소를 함유하는 가스로부터 생성된 플라즈마로 처리하여 형성될수 있다. 또한, 상기 제2 전극막 및 상기 제1 전극막을 부분적으로 식각하여, 상기 게이트 전극의 일측 상에 제1 전극 패턴 및 제2 전극 패턴을 포함하는 상기 소스 전극을 형성할 수 있으며, 상기 게이트 전극의 타측 상에제3 전극 패턴 및 제4 전극 패턴을 포함하는 상기 드레인 전극을 형성할 수 있다. 상기 리세스 구조물 형성하는 과정에 있어서, 상기 소스 및 상기 드레인 전극으로부터 상기 마스크 패턴을 제거한 후, 상기 소스 및 상기 드레인 전극으로부터 상기 마스크 패턴을 제거한 후, 상기 소스 및 상기 드레인 전극으로부터 상기 마스크 패턴을 수행할 수 있다.

- [0023] 상술한 본 발명의 또 다른 목적을 달성하기 위하여, 본 발명의 예시적인 실시예들에 따른 표시 장치는, 기판, 상기 기판 상에 배치되는 게이트 전극, 상기 게이트 전극을 덮으며 상기 기판 상에 배치되는 게이트 절연층, 상기 게이트 절연층의 일측 상에 배치되는 소스 전극, 상기 게이트 절연층의 타측 상에 배치되는 드레인 전극, 상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전극 상에 배치되는 액티브 패턴, 상기 드레인 전극에 전기적으로 연결되는 제1 전극, 상기 제1 전극 상에 배치되는 발광층, 그리고 상기 발광층 상에 배치되는 제2 전극을 포함할 수 있다. 상기 게이트 절연층은 상기 게이트 전극 상부에 위치하는 리세스 구조를 포함할 수 있다. 상기 액티브 패턴은 상기 리세스 구조를 채우며 상기 소스 전극 및 상기 드레인 전극 상에 배치될 수 있다.

- [0024] 전술한 본 발명의 또 다른 목적을 달성하기 위하여, 본 발명의 예시적인 실시예들에 따른 표시 장치의 제조 방법에 있어서, 기판 상에 게이트 전극을 형성한 후, 상기 기판 상에 상기 게이트 전극을 덮는 게이트 절연층을 형성할 수 있다. 상기 게이트 절연층 상에 전극층을 형성한 다음, 상기 전극층 상에 마스크 패턴을 형성할 수 있다. 상기 마스크 패턴을 이용하여 상기 전극층을 식각하여 상기 게이트 절연층 상에 소스 전극 및 드레인 전극을 형성할 수 있다. 상기 소스 전극 및 상기 드레인 전극 사이의 상기 게이트 절연층에 리세스 구조를 형성할수 있다. 상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전극 상에 액티브 패턴을 형성할수 있다. 상기 드레인 전극에 전기적으로 연결되는 제1 전극을 형성한 후, 상기 제1 전극 상에 발광층 및 제2 전극을 형성할수 있다. 상기 리세스 구조는 플라즈마 처리 및/또는 세정 처리를 수행하여 형성될수 있다.

## 발명의 효과

[0025] 본 발명의 예시적인 실시예들에 따르면, 플라즈마 처리 및/또는 세정 처리를 통해 소스 및 드레인 전극 사이의 게이트 절연층에 리세스 구조를 형성하기 때문에, 상기 소스 및 드레인 전극을 형성하는 동안 상기 게이트 절연층에 생성되는 내부 응력을 제거할 수 있으며, 상기 게이트 절연층에 발생되는 식각 손상과 이에 기인하는 잔류 응력도 효과적으로 제거할 수 있다. 또한, 상기 게이트 절연층과 액티브 패턴 사이에 잔류하는 금속 원자들, 금속 화합물 등의 식각 부산물들을 상기 게이트 절연층으로부터 완전히 제거할 수 있다. 상기 리세스 구조를 채우면서 상기 액티브 패턴에 형성되는 상기 산화물 반도체 소자의 채널 영역이 균일하고 평탄해지며, 상기 산화물 반도체 소자의 동작 전류의 저하, 문턱 전압 산포의 증가, 상기 채널 영역에서의 전하 이동도의 감소 등의 전기적인 특성들의 열화를 방지하여 향상된 전기적인 특성을 확보할 수 있다. 또한, 상기 리세스 구조로 인하여 상기 게이트 절연층이 상대적으로 얇은 두께를 갖기 때문에 상기 산화물 반도체 소자의 전하 이동도, 구동 전류 등의 전기적인 특성들을 보다 향상시킬 수 있다. 상기 산화물 반도체 소자를 유기 발광 표시 장치, 플랙서블 디스플레이 장치 등과 같은 표시 장치에 적용할 경우, 상기 표시 장치의 두께를 감소시킬 수 있고, 상기 표시 장치에 의해 디스플레이되는 영상의 해상도를 증가시킬 수 있으며, 화면의 구동 속도도 향상시킬 수 있다.

## 도면의 간단한 설명

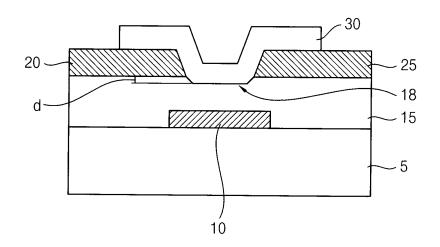

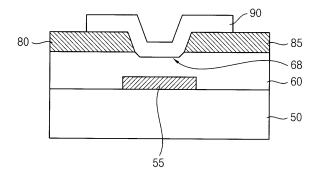

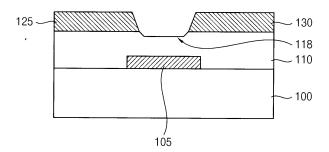

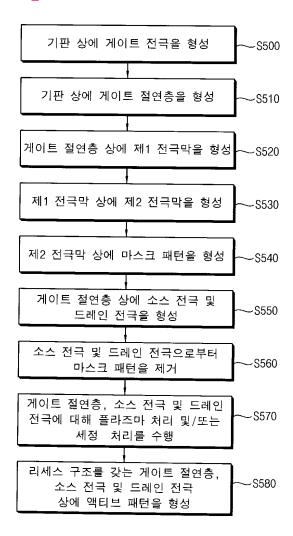

[0026] 도 1은 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자를 설명하기 위한 단면도이다.

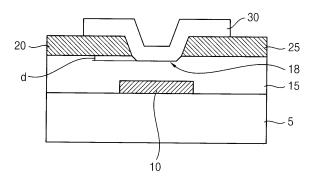

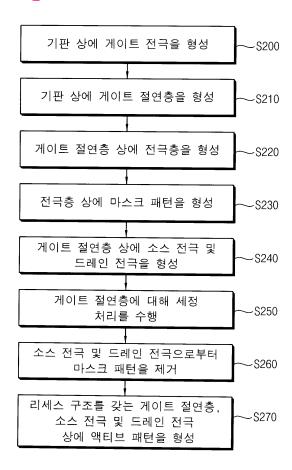

도 2는 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정

순서도이다.

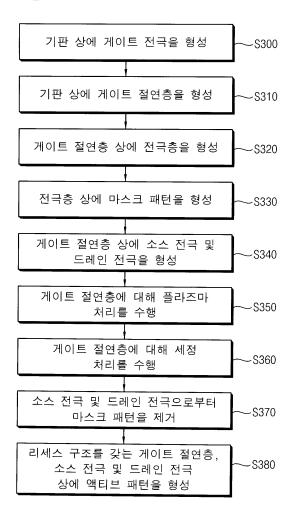

도 3은 본 발명의 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다.

도 4 내지 도 8은 본 발명의 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다.

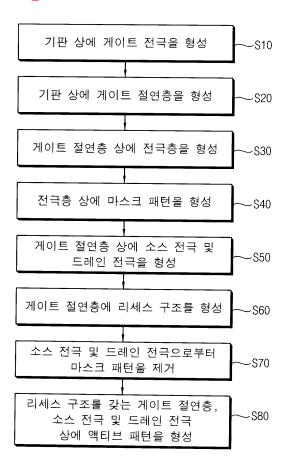

도 9는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다.

도 10 내지 도 12는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다.

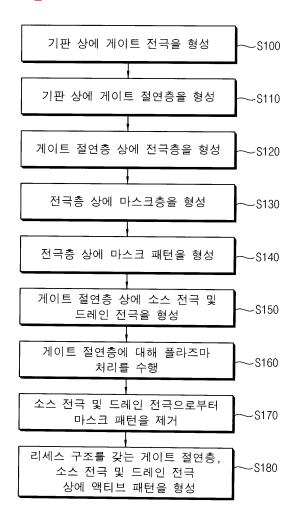

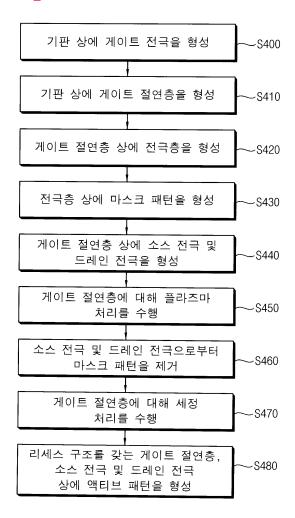

도 13은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다.

도 14는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다.

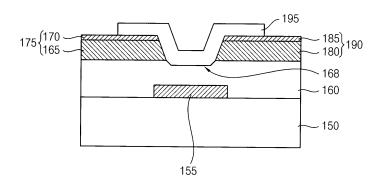

도 15는 본 발명의 다른 예시적인 실시예들에 따른 산화물 반도체 소자를 설명하기 위한 단면도이다.

도 16은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다.

도 17 내지 도 20은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다.

도 21은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자를 설명하기 위한 단면도이다.

도 22 및 도 23은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다.

도 24는 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자를 포함하는 표시 장치를 설명하기 위한 단면 도이다.

도 25 내지 도 28은 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법을 설명하기 위한 단면도들이다.

# 발명을 실시하기 위한 구체적인 내용

- [0027] 이하, 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자, 산화물 반도체 소자의 제조 방법, 산화물 반도체 소자를 포함하는 표시 장치 및 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법에 대하여 첨부된 도면들을 참조하여 상세하게 설명하지만, 본 발명이 하기 실시예들에 의해 제한되는 것은 아니며, 해당 분야에서 통상의 지식을 가진 자라면 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 본 발명을 다양한 다른 형태로구현할 수 있을 것이다.

- [0028] 본 명세서에 있어서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예들을 설명하기 위한 목적으로 예시된 것이며, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본 명세서에 설명된 실시예들에 한정되는 것으로 해석되지 않으며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다. 어떤 구성 요소가 다른 구성 요소에 "연결되어" 있거나 "접속되어" 있다거나 "접촉되어" 있다고 기재된 경우, 다른 구성 요소에 직접적으로 연결되어 있거나 접속 또는 접촉되어 있을 수도 있지만, 중간에 또 다른 구성 요소가 존재할 수도 있다고 이해되어야 할 것이다. 또한, 어떤 구성 요소가 다른 구성 요소에 "직접 연결되어" 있다거나 "직접 접촉되어"있다고 기재된 경우에는, 중간에 또 다른 구성 요소가 존재하지 않는 것으로 이해될 수 있다. 구성 요소들 간의 관계를 설명하는 다른 표현들, 예를 들면, "~사이에"와 "직접 ~사이에" 또는 "~에 인접하는"과 "~에 직접 인접하는" 등도 마찬가지로 해석될 수 있다.

- [0029] 본 명세서에서 사용되는 용어는 단지 예시적인 실시예들을 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도는 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 명세서에서, "포함하다", "구비하다" 또는 "가지다" 등의 용어는 실시된 특징, 숫자, 단계, 동작, 구성 요소, 부품 또는

이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성 요소, 부품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다. 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가지고 있다. 일반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥 상 가지는 의미와 일치하는의미를 가지는 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지는 않는다.

- [0030] 제1, 제2, 제3, 제4 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 이러한 구성 요소들은 상기 용어들에 의해 한정되는 것은 아니다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소로부터 구별하는 목적으로 사용된다. 예를 들어, 본 발명의 권리 범위로부터 벗어나지 않고, 제1 구성 요소가 제2, 제3 또는 제4구성 요소 등으로 명명될 수 있으며, 유사하게 제2 내지 제4구성 요소도 서로 교호적으로 명명될 수 있다.

- [0031] 산화물 반도체 소자 및 산화물 반도체 소자의 제조 방법

- [0032] 도 1은 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자를 설명하기위한 단면도이다. 도 2는 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다.

- [0033] 도 1을 참조하면, 상기 산화물 반도체 소자는 기판(5) 상에 제공될 수 있으며, 게이트 전극(10), 게이트 절연층 (15), 소스 전극(20), 드레인 전극(25) 및 액티브 패턴(30)을 포함할 수 있다.

- [0034] 기판(5)은 투명 절연 기판을 포함할 수 있다. 예를 들면, 기판(5)은 유리 기판, 투명 플라스틱 기판, 투명 금속 산화물 기판 등으로 구성될 수 있다. 예시적인 실시예들에 있어서, 기판(5) 상에는 버퍼층(도시되지 않음)이 형성될 수 있다. 상기 버퍼층은 기판(5)으로 불순물들이 확산되는 현상을 방지할 수 있으며, 기판(5) 전체의 평탄도를 향상시키는 역할을 수행할 수 있다. 즉, 기판(5)의 상면이 상대적으로 불균일할 경우에도, 상기 버퍼층이 평탄한 상면을 가지면서 기판(5) 상에 배치될 수 있다. 또한, 기판(5) 상에 상기 버퍼층이 존재할 경우, 게이트전극(10)을 형성하는 동안 발생되는 응력(stress)을 감소시켜 게이트 전극(10)을 보다 용이하게 형성할 수 있다. 상기 버퍼층은 실리콘 화합물을 포함할 수 있다. 예를 들면, 상기 버퍼층은 실리콘 산화물(SiOx), 실리콘산질화물(SiOxNy) 등으로 이루어질 수 있다. 상기 버퍼층은 실리콘 화합물로 이루어진 단층 구조 또는 다층 구조를 가질 수 있다.

- [0035] 도 1 및 도 2를 참조하면, 게이트 전극(10)은 기판(5) 상에 형성된다(단계 S10). 게이트 전극(10)에는 상기 산화물 반도체 소자가 적용되는 표시 장치의 게이트 라인(도시되지 않음)이 연결될 수 있다. 게이트 전극(10)은 금속, 합금, 금속 질화물, 도전성 금속 산화물, 투명 도전성 물질 등을 포함할 수 있다. 예를 들면, 게이트 전극(10)은 알루미늄(A1), 알루미늄을 함유하는 합금, 알루미늄 질화물(A1Nx), 은(Ag), 은을 함유하는 합금, 텅스텐(W), 텅스텐 질화물(WNx), 구리(Cu), 구리를 함유하는 합금, 니켈(Ni), 크롬(Cr), 몰리브데늄(Mo), 몰리브데늄을 함유하는 합금, 티타늄(Ti), 티타늄 질화물(TiNx), 백금(Pt), 탄탈륨(Ta), 네오디뮴(Nd), 스칸듐(Sc), 탄탈륨 질화물(TaNx), 스트론튬 루테늄 산화물(SrRuxOy), 아연 산화물(ZnOx), 인듐 주석 산화물(ITO), 주석 산화물(SnOx), 인듐 산화물(InOx), 갈륨 산화물(GaOx), 인듐 아연 산화물(IZO) 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0036] 예시적인 실시예들에 있어서, 게이트 전극(10)은 상술한 금속, 합금, 금속 질화물, 도전성 금속 산화물 또는 투명 도전성 물질로 이루어진 단층 구조를 가질 수 있다. 또한, 게이트 전극(10)은 전술한 금속, 합금, 금속 질화물, 도전성 금속 산화물 및/또는 투명 도전성 물질로 구성된 다층 구조로 형성될 수도 있다. 게이트 전극(10)이상기 투명 도전성 물질을 포함하는 경우, 후술하는 바와 같이 상기 산화물 반도체 소자의 구성 요소들이 전체적으로 투명한 물질들로 이루어질 수 있으므로 상기 산화물 반도체 소자를 투명한 플렉서블 디스플레이 장치 등에용이하게 적용될 수 있다.

- [0037] 종래의 표시 장치에 적용되는 트랜지스터의 게이트 전극은 알루미늄, 은, 구리 등과 같은 낮은 저항을 갖는 금속으로 이루어진다. 그러나. 이와 같이 낮은 저항을 갖는 금속은 내열성이 상대적으로 낮거나 또는 상대적으로 부식되기 쉽다는 문제가 있다. 이러한 문제점을 고려하여 예시적인 실시예들에 따르면, 전기 전도성이 상대적으로 높은 제1 금속과 내열성이 우수한 제2 금속을 조합하여 게이트 전극(10)을 구현할 수 있다. 즉, 게이트 전극(10)은 알루미늄, 은, 구리 등의 낮은 저항을 갖는 제1 금속막과 몰리브데늄, 티타늄, 크롬, 탄탈륨, 루테늄, 텅스텐, 네오디뮴, 스칸듐 등의 내열성이 상대적으로 우수한 제2 금속막이나 금속 화합물막이 조합된 다층 구조

를 가질 수 있다. 예를 들면, 게이트 전극(10)은, 알루미늄막과 몰리브데늄막, 은막과 몰리브데늄막, 구리막과 몰리브데늄막, 구리막과 티타늄 질화물막, 구리막과 탄탈륨 질화물막, 티타늄 질화물막과 몰리브데늄막 등과 같은 다양한 막들의 조합을 포함하는 다층 구조를 가질 수 있다. 또한, 게이트 전극(10)은 상대적으로 우수한 전기 전도성을 갖는 제1 금속 중에서 하나 이상을 함유하는 제1 금속막, 상대적으로 우수한 내열성을 갖는 제2 금속 중에서 하나 이상을 함유하는 제2 금속막 및/또는 내열성이 상대적으로 우수한 금속 화합물들 가운데 하나이상을 함유하는 금속 화합물막 가운데 적어도 하나를 포함하는 다층 구조를 가질 수도 있다.

- [0038] 도 1 및 도 2에 도시한 바와 같이, 게이트 절연층(15)은 게이트 전극(10)을 덮으며 기판(5) 상에 형성된다(단계 S20). 예시적인 실시예들에 있어서, 게이트 절연층(15)은 게이트 전극(10)을 충분히 덮으면서, 게이트 전극(10)의 주변에서 단차부가 생성되지 않고 실질적으로 평탄한 상면을 가질 수 있다. 이 경우, 게이트 절연층(15)은 상대적으로 두꺼운 두께로 형성될 수 있다. 예를 들면, 게이트 절연층(15)은 기판(5)의 상면으로부터 약 500Å 내지 약 3,000Å 정도의 두께를 가질 수 있다.

- [0039] 게이트 절연층(15)은 실리콘 화합물, 금속 산화물 등을 포함할 수 있다. 예를 들면, 게이트 절연층(15)은 실리 콘 산화물, 실리콘 질화물(SiNx), 실리콘 산질화물, 알루미늄 산화물(AlOx), 탄탈륨 산화물(TaOx), 하프늄 산화물(HfOx), 지르코늄 산화물(ZrOx), 티타늄 산화물(TiOx) 등으로 이루어질 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 또한, 게이트 절연층(15)은 상술한 실리콘 화합물 및/또는 금속 산화물을 포함하는 단층 구조 또는 다층 구조를 가질 수 있다.

- [0040] 소스 전극(20)과 드레인 전극(25)은 각기 아래에 위치하는 게이트 전극(10)을 중심으로 게이트 절연층(15)의 일 측 및 타측 상에 위치할 수 있다. 게이트 절연층(15)이 평탄한 상면을 가질 경우, 소스 전극(20) 및 드레인 전극(25)도 단차부를 갖지 않고 실질적으로 평탄한 상면을 가질 수 있다. 소스 전극(20)에는 상기 표시 장치의 데이터 라인(도시되지 않음)이 연결될 수 있으며, 드레인 전극(25)에는 상기 표시 장치의 화소 전극(도시되지 않음)이 전기적으로 접촉될 수 있다.

- [0041] 예시적인 실시예들에 따른 소스 전극(20) 및 드레인 전극(25)을 형성하는 과정에 있어서, 도 2에 도시한 바와 같이, 게이트 절연층(15) 상에 전극층을 형성한 후(단계 S30), 상기 전극층 상에 마스크 패턴을 형성한다(단계 S40). 이러한 마스크 패턴을 식각 마스크로 이용하여 상기 전극층을 패터닝함으로써, 게이트 절연층(15) 상에 소스 전극(20) 및 드레인 전극(25)을 형성한다(단계 S50).

- [0042] 소스 전극(20) 및 드레인 전극(25)은 각기 금속, 합금, 금속 질화물, 도전성 금속 산화물, 투명 도전성 물질 등을 포함할 수 있다. 예를 들면, 소스 전극(20)과 드레인 전극(25)은 알루미늄(A1), 구리(Cu), 몰리브데늄(Mo), 티타늄(Ti), 크롬(Cr), 탄탈륨(Ta), 텅스텐(W), 네오디뮴(Nd), 스칸듐(Sc), 이들의 합금, 이들의 질화물, 스트론튬 루테늄 산화물(SrRuxOy), 인듐 주석 산화물, 인듐 아연 산화물, 아연 산화물, 주석 산화물, 탄소 나노 튜브 등을 포함할 수 있다. 또한, 소스 전극(20) 및 드레인 전극(25)은 각기 금속, 합금, 금속 질화물, 도전성 금속 산화물 및/또는 투명 도전성 물질로 이루어진 단층 구조 또는 다층 구조를 가질 수 있다.

- [0043] 예시적인 실시예들에 있어서, 알루미늄, 구리 등과 같은 상대적으로 낮은 전기 저항을 갖는 도전성 물질로 소스 전극(20)과 드레인 전극(25)을 구성할 경우에는 상기 산화물 반도체 소자의 전기적인 특성 측면에서 상대적으로 유리할 수 있다. 그러나, 상대적으로 낮은 전기 저항을 갖는 도전성 물질은 내열성이 상대적으로 낮거나 또는 쉽게 부식될 수 있다. 따라서, 소스 전극(20)과 드레인 전극(25)은 상기 도전성 물질에 내열성 물질이 추가적으로 포함된 조성을 가질 수 있다. 소스 전극(20)과 드레인 전극(55)에 포함되는 상기 내열성 물질의 예로는 몰리 브데늄, 티타늄, 크롬, 탄탈륨, 텅스텐, 네오디뮴, 루테늄, 스칸듐 등을 들 수 있다. 예를 들면, 소스 전극(20) 및 드레인 전극(25)은 상기 내열성 물질을 함유하는 제1 도전막, 상기 낮은 저항이 물질을 함유하는 제2 도전막, 상기 내열성 물질을 함유하는 제3 도전막으로 이루어진 다층 구조를 가질 수 있다. 소스 전극(20)과 드레인 전극(25)이 다층 구조를 가질 경우, 상기 도전성 물질로 인하여 소스 전극(20) 및 드레인 전극(25)이 낮은 저항을 가지면서도, 상기 내열성 물질의 존재에 따라 소스 전극(20) 및 드레인 전극(25)의 힐록(Hillock) 현상을 방지할 수 있다.

- [0044] 다시 도 1 및 도 2를 참조하면, 게이트 절연충(15)에 리세스 구조(recess structure)(18)를 형성한다(단계 S60). 이와 같이, 게이트 절연충(15)의 상부에 리세스 구조(18)를 형성한 후, 소스 및 드레인 전극(20, 25)으로 부터 상기 마스크 패턴을 제거한다(단계 S70). 예를 들면, 상기 마스크 패턴이 포토레지스트를 포함하는 경우, 상기 마스크 패턴은 스트리핑(stripping) 공정 및/또는 애싱(ashing) 공정을 이용하여 제거될 수 있다.

- [0045] 예시적인 실시예들에 있어서, 리세스 구조(18)는 게이트 절연층(15)의 상면으로부터 소정의 깊이(d)로 형성될

수 있다. 예를 들면, 리세스 구조(18)는 게이트 절연층(15)의 상면으로부터 약 100Å 내지 약 300Å 정도의 깊이(d)로 형성될 수 있다. 이에 따라, 리세스 구조(18)의 깊이와 게이트 절연층(15)의 두께 사이의 비율은 약 1.0: 1.7 내지 약 1.0: 30.0 정도가 될 수 있다. 또한, 리세스 구조(18)는 게이트 전극(10)에 비하여 상대적으로 작은 면적을 가질 수 있다. 그렇지만, 이와 같은 리세스 구조(18)의 치수는 상기 산화물 반도체 소자의 사이즈, 전기적인 특성 등에 따라 변화될 수 있다.

- [0046] 도 1에 예시적으로 도시한 산화물 반도체 소자에 있어서, 리세스 구조(18)가 소스 및 드레인 전극(20, 25) 사이에서 노출되는 부분의 게이트 절연층(15)에 전체적으로 형성되지만, 이러한 리세스 구조(18)는 노출되는 부분의 게이트 절연층(18)의 일부에만 형성될 수도 있다. 게이트 절연층(15)의 리세스 구조(18)는 실질적으로 원형의 형상, 실질적으로 타원형의 형상, 실질적으로 다각형의 형상 등의 다양한 평면 구조를 가질 수 있다. 또한, 리세스 구조(18)는 기판(5)에 실질적으로 직교하는 축선(axis)에 대해 상대적으로 작은 제1 각도로 경사진 측벽을 가질 수 있다. 예를 들면, 리세스 구조(18)는 게이트 전극(10)에 실질적으로 직교하는 방향에 대하여 약 10° 내지 약 60° 정도의 제1 각도로 경사진 측벽을 가질 수 있다. 이러한 게이트 절연층(15)의 리세스 구조(18)에는 액티브 패턴(30)의 하부가 위치할 수 있다. 즉, 액티브 패턴(30)은 리세스 구조(18)를 채우면서 게이트 절연층(15) 상에 배치될 수 있다. 따라서, 액티브 패턴(30)은 리세스 구조(18)에 부분적으로 매립되는 형상을 가질수 있다.

- [0047] 예시적인 실시예들에 따르면, 게이트 절연층(15)의 리세스 구조(18)는 소스 및 드레인 전극(20, 25) 사이로 노출되는 게이트 절연층(15)에 대해 플라즈마 처리(plasma treatment)를 수행하여 수득될 수 있다. 즉, 리세스 구조(18)는 잔류 응력이 생성되거나 식각 손상을 입거나 또는 식각 부산물(etched by-product)들 등이 잔류하는 게이트 절연층(15)의 일부를 상기 플라즈마 처리로 제거함으로써 형성될 수 있다. 예를 들면, 상기 플라즈마 처리는 황 불화물(SFx)을 함유하는 가스, 염소 불화물(CFx)을 함유하는 가스, 염화수소(HCl)를 함유하는 가스, 붕소 염화물(BClx)을 함유하는 가스, 탄화수소(CxHy)를 함유하는 가스, 산소(02)를 함유하는 가스, 오존(03)을 함유하는 가스 등을 포함하는 가스로부터 생성되는 플라즈마를 사용하여 수행될 수 있다. 이들 가스는 단독으로 또는 서로 혼합되어 사용될 수 있다.

- [0048] 다른 예시적인 실시예들에 있어서, 리세스 구조(18)는 소스 및 드레인 전극(20, 25) 사이에 노출된 게이트 절연 충(15)을 세정 처리(cleaning treatment)를 통해 부분적으로 제거하여 수득될 수 있다. 상기 세정 처리는 금속 화합물을 제거할 수 있는 용액과 순수(water) 또는 탈이온수(deionized water)의 혼합 용액을 사용하여 수행될 수 있다. 즉, 상기 세정 처리는 희석된 금속 화합물을 제거할 수 있는 용액을 사용하여 수행될 수 있다. 예를 들면, 상기 세정 처리는 불화수소(HF)를 함유하는 용액, 염화수소(HC1)를 함유하는 용액, 인산(H<sub>2</sub>PO<sub>4</sub>)을 함유하는 용액, 수산화칼륨(KOH)을 함유하는 용액, 브롬화수소(HBr)를 함유하는 용액, 트롬화요오드(HI)를 함유하는 용액 등의 금속 화합물을 제거할 수 있는 용액을 사용하여 수행될 수 있다. 이들 용액들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0049] 또 다른 예시적인 실시예들에 따르면, 게이트 절연층(15)의 리세스 구조(18)는 전술한 플라즈마 처리와 세정 처리를 모두 수행하여 수득될 수 있다. 예를 들면, 게이트 절연층(15)의 일부에 대하여 상술한 플라즈마 처리와 세정 처리를 순차적으로 수행하여 리세스 구조(18)를 형성할 수 있다. 또한, 게이트 절연층(15)의 일부에 대해 전술한 플라즈마 처리를 수행하고, 상기 소스 및 드레인 전극(20, 25)으로부터 상기 마스크 패턴을 제거한 다음, 게이트 절연층(15)의 일부에 대해 상술한 세정 처리를 수행하여 리세스 구조(18)를 수득할 수도 있다.

- [0050] 도 1 및 도 2에 도시한 바와 같이, 액티브 패턴(30)은 리세스 구조(18)를 갖는 게이트 절연충(15), 소스 전극 (20) 및 드레인 전극(25) 상에 형성된다(단계 S80). 액티브 패턴(30)은 리세스 구조(18)를 채우면서 게이트 절 연충(15) 상에 배치될 수 있기 때문에, 액티브 패턴(30)의 하부 측벽은 리세스 구조(18)의 측벽과 실질적으로 동일한 경사 각도를 가질 수 있다. 즉, 액티브 패턴(30)의 하부는 기판(5)에 실질적으로 직교하는 축선에 대하여 상대적으로 작은 제1 경사 각도를 가질 수 있다.

- [0051] 전술한 바와 같이, 게이트 절연층(15)이 리세스 구조(18)를 포함하는 경우, 소스 전극(20) 및 드레인 전극(25) 사이에 위치하는 부분의 게이트 절연층(15)의 두께가 소스 및 드레인 전극(20, 25) 아래에 위치하는 부분들의 게이트 절연층(15)의 두께에 비하여 상대적으로 얇아질 수 있다. 즉, 게이트 전극(10) 상에 위치하는 게이트 절연층(15)의 두께가 리세스 구조(18)의 깊이(d)만큼 감소될 수 있다. 리세스 구조(18)를 채우는 액티브 패턴(3 0)에는 상기 산화물 반도체 소자의 채널 영역이 형성되기 때문에, 상기 채널 영역 아래의 게이트 절연층(15)이 상대적으로 얇은 두께를 가질 경우에는 상기 산화물 반도체 소자의 전하 이동도, 구동 전류 등의 전기적은 특성

들을 보다 향상시킬 수 있다.

- [0052] 예시적인 실시예들에 있어서, 소스 전극(20)과 드레인 전극(25)은 각기 게이트 절연막(15)에 대하여 상대적으로 큰 제2 각도로 경사진 측벽을 가질 수 있다. 예를 들면, 소스 전극(20)과 드레인 전극(25)의 측벽들은 각기 기판(5)에 실질적으로 직교하는 방향에 대해 약 30° 내지 약 90° 정도의 경사 각도를 가질 수 있다. 따라서, 리세스 구조(18)의 제1 경사 각도와 소스 및 드레인 전극(20, 25)의 제2 경사 각도 사이의 비는 약 1.0: 0.5 내지약 1.0: 9,0 정도가 될 수 있다. 전술한 바와 같이, 리세스 구조(18), 소스 전극(20) 및 드레인 전극(25)이 각기 경사진 측벽을 가질 수 있기 때문에, 이와 같은 리세스 구조(18), 소스 전극(20) 및 드레인 전극(25)의 프로파일들을 따라 액티브 패턴(30)을 보다 용이하게 형성할 수 있다.

- [0053] 예시적인 실시예들에 따르면, 액티브 패턴(30)은 게이트 절연층(15)의 리세스 구조(18)를 채우면서 소스 전극 (20)과 드레인 전극(25) 상에 배치될 수 있다. 이에 따라, 액티브 패턴(30)의 전체적인 측벽은 상이한 경사 각도를 갖는 부분들을 포함할 수 있다. 이 경우, 게이트 절연층(15)에 접촉되는 액티브 패턴(30)의 하부 측벽은 기판(5)에 대해 실질적으로 직교하는 축선으로부터 상대적으로 작은 제1 각도로 경사질 수 있다. 또한, 소스 및 드레인 전극(20, 25)에 각기 접촉되는 액티브 패턴(30)의 중앙부 측벽은 기판(5)에 대해 실질적으로 직교하는 방향으로부터 상대적으로 큰 제2 각도로 경사질 수 있다. 즉, 액티브 패턴(30)의 중앙부 측벽은 리세스 구조(18), 소스 전극(20) 및 드레인 전극(25)의 경사 구조와 실질적으로 동일하거나 실질적으로 유사한 경사 구조를 가질 수 있다. 이에 따라, 액티브 패턴(30)의 하부 측벽과 중앙부 측벽 사이의 경사 각도의 비는 약 1.0: 0.5 내지 약 1.0: 9.0 정도가 될 수 있다.

- [0054] 액티브 패턴(30)의 일측과 타측은 각기 소스 전극(20)과 드레인 전극(25) 상으로 연장될 수 있다. 이에 따라, 액티브 패턴(30)의 중앙부는 게이트 전극(10)의 상부에서 게이트 전극(10)과 실질적으로 중첩될 수 있으며, 액티브 패턴(30)의 양측부는 각기 게이트 전극(10)의 양측 상부에서 부분적으로 중첩될 수 있다. 액티브 패턴(30)이 소스 전극(20), 드레인 전극(25) 및 게이트 절연층(15) 상에 위치하기 때문에, 액티브 패턴(30)의 양측에는 단차부들이 생성될 수 있다. 예를 들면, 액티브 패턴(30)은 양측에 단차부들이 형성되어 실질적으로 "U"자에가까운 형상의 단면 형상을 가질 수 있다.

- [0055] 예시적인 실시예들에 있어서, 액티브 패턴(30)은 인듐(In), 아연(Zn), 갈륨(Ga), 주석(Sn), 티타늄(Ti), 알루미늄(Al), 하프늄(Hf), 지르코늄(Zr), 마그네슘(Mg) 등을 함유하는 이성분계 화합물(ABx), 삼성분계 화합물(ABxCy), 사성분계 화합물(ABxCyDz) 등을 포함하는 반도체 산화물로 구성될 수 있다. 이 때, 액티브 패턴(30)의 전자 캐리어 농도는 약 1 x 10 12 개/cm 14 x 10 18 개/cm 18 정도가 될 수 있다. 예를 들면, 액티브 패턴(30)은 인듐-갈륨-아연 산화물(IGZO), 갈륨 아연 산화물(GaZnxOy), 인듐 주석 산화물(ITO), 인듐아연 산화물(IZO), 아연 마그네슘 산화물(ZnMgxOy), 아연 주석 산화물(ZnSnxOy), 아연 지르코늄 산화물(ZnZrxOy), 아연 산화물(ZnOx), 갈륨 산화물(GaOx), 티타늄 산화물(TiOx), 주석 산화물(SnOx), 인듐 산화물(InOx), 인듐-갈륨-하프늄 산화물(IGHO), 주석-알루미늄-아연 산화물(TAZO), 인듐-갈륨-주석 산화물(IGSO) 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 다른 예시적인 실시예들에 따르면, 액티브 패턴(30)은 상술한 반도체 산화물에 리튬(Li), 나트륨(Na), 망간(Mn), 니켈(Ni), 팔라듐(Pd), 구리(Cu), 탄소(C), 질소(N), 인(P), 티타늄(Ti), 지르코늄(Zr), 바나듐(V), 루테늄(Ru), 게르마늄(Ge), 주석(Sn), 불소(F) 등이 도핑된 조성을 가질수 있다. 이들은 단독으로 또는 서로 조합되어 첨가될 수 있다. 또한, 액티브 패턴(30)은 상술한 반도체 산화물을 포함하는 단층 구조 또는 다층 구조를 가질 수 있다.

- [0056] 다른 예시적인 실시예들에 따르면, 소스 및 드레인 전극(20, 25)과 게이트 절연층(15) 사이에는 식각 저지층(도시되지 않음), 보호층(도시되지 않음) 등과 같은 게이트 절연층(15)을 보호할 수 있는 추가적인 층(들)이 배치될 수 있다. 이 때, 상기 식각 저지층 또는 상기 보호층은 소스 및 드레인 전극(20, 25)과 게이트 절연층(15)에 대해 식각 선택비를 갖는 물질로 이루어질 수 있다. 예를 들면, 상기 식각 저지층 또는 상기 보호층은 실리콘산화물, 실리콘 질화물, 실리콘 산질화물, 반도체 산화물 등을 포함할 수 있다.

- [0057] 전술한 바에 있어서는 산화물 반도체 소자에 대하여 설명하였으나, 예시적인 실시예들에 따른 리세스 구조를 갖는 게이트 절연층은 아몰퍼스 실리콘, 폴리 실리콘, 부분 결정화 실리콘, 미세 결정들을 포함하는 실리콘 등으로 이루어진 액티브 패턴(영역)을 포함하는 트랜지스터에도 적용될 수 있다. 여기서, 상기 트랜지스터는 상기 액티브 패턴(영역)의 구성 물질을 제외하면 도 1을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가질 수 있다.

- [0058] 본 발명의 예시적인 실시예들에 따르면, 플라즈마 처리 및/또는 세정 처리를 통해 소스 및 드레인 전극(20, 25) 사이의 게이트 절연층(15)에 리세스 구조(18)를 형성하기 때문에, 소스 및 드레인 전극(20, 25)을 형성하는 동

안 게이트 절연층(15)에 발생되는 내부 응력을 제거할 수 있으며, 게이트 절연층(15)에 발생되는 식각 손상과이에 기인하는 잔류 응력도 효과적으로 제거할 수 있다. 또한, 게이트 절연층(15)과 액티브 패턴(30) 사이에 잔류하는 금속 원자들, 금속 화합물 등의 식각 부산물들을 게이트 절연층(15)으로부터 완전히 제거할 수 있다. 이에 따라, 리세스 구조(18)를 채우면서 액티브 패턴(30)에 형성되는 상기 산화물 반도체 소자의 채널 영역이 균일하고 평탄해지며, 상기 산화물 반도체 소자의 동작 전류의 저하, 문턱 전압(Vth) 산포의 증가, 상기 채널 영역에서의 전하 이동도의 감소 등의 전기적인 특성들의 열화를 방지하여 향상된 전기적인 특성을 확보할 수 있다. 또한, 리세스 구조(18)로 인하여 게이트 전극(10) 상에서 게이트 절연층(15)이 상대적으로 얇은 두께를 갖기 때문에 상기 산화물 반도체 소자의 전하 이동도, 구동 전류 등의 전기적인 특성들을 보다 향상시킬 수 있다.

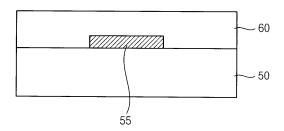

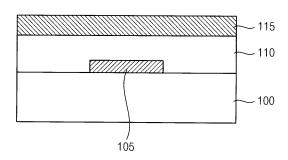

- [0059] 도 3은 본 발명의 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서 도이다. 도 4 내지 도 8은 본 발명의 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다. 도 3 내지 도 8에 있어서, 도 1을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 산화물 반도체 소자의 제조 방법을 예시적으로 설명하지만, 도 3 내지 도 8을 참조하여 설명하는 도시한 산화물 반도체 소자의 제조 방법은 게이트 전극, 게이트 절연층, 소스 전극, 드레인 전극, 액티브 패턴 등이 다양한 구조로 배치된 구성을 가지는 다른 산화물 반도체 소자들에도 적용가능함을 이해할 수 있을 것이다.

- [0060] 도 3 및 도 4를 참조하면, 유리, 투명 플라스틱, 투명 세라믹 등과 같은 투명 절연 물질로 구성된 기판(50) 상에 게이트 전극(55)을 형성한다(단계 S100). 게이트 전극(55)은 기판(50) 상에 스퍼터링(sputtering) 공정, 스프레이(spray) 공정, 화학 기상 증착(CVD) 공정, 원자층 적층(ALD) 공정, 진공 증착(evaporation) 공정, 프린팅(printing) 공정 등을 통해 형성될 수 있다. 예시적인 실시예들에 따르면, 기판(50) 상에 제1 도전층(도시되지 않음)을 형성한 후, 상기 제1 도전층을 패터닝하여 기판(50) 상에 게이트 전극(55)을 형성할 수 있다. 이때, 게이트 전극(55)과 동시에 기판(50) 상에 게이트 라인(도시되지 않음)이 형성될 수 있다. 예를 들면, 상기게이트 라인은 기판(50) 상에서 제1 방향을 따라 연장될 수 있으며, 게이트 전극(55)은 상기 게이트 라인으로부터 분기되는 구조를 가질 수 있다.

- [0061] 게이트 전극(55)은 알루미늄, 알루미늄 합금, 텅스텐, 구리, 니켈, 크롬, 몰리브데늄, 티타늄, 백금, 탄탈륨, 루테늄 등과 같은 금속, 이러한 금속을 포함하는 합금, 이와 같은 금속의 질화물, 도전성 금속 산화물 등을 사용하여 형성될 수 있다. 또한, 게이트 전극(55)은 단층 구조 또는 다층 구조로 형성될 수 있다. 예를 들면, 게이트 전극(55)은 도전성을 갖는 물질 및/또는 내열성을 갖는 물질을 포함하는 단층 구조 또는 다층 구조를 가질수 있다. 다른 예시적인 실시예들에 따르면, 게이트 전극(55)은 투명 도전성 물질을 기판(50) 상에 중착한 다음, 중착된 투명 도전성 물질을 패터닝하여 기판(50) 상에 형성될 수 있다. 예를 들면, 상기 투명 도전성 물질은 인듐 주석 산화물(ITO), 인듐 아연 산화물(IZO), 아연 산화물, 주석 산화물, 갈륨 산화물, 인듐 산화물 등을 사용하여 형성될 수 있다.

- [0062] 다른 예시적인 실시예들에 따르면, 기판(50) 상에 버퍼층(도시되지 않음)을 형성한 후, 이러한 버퍼층 상에 게이트 전극(55)을 형성할 수 있다. 이 때, 상기 버퍼층은 실리콘 산화물, 실리콘 산질화물 및/또는 실리콘 질화물을 포함하는 단층 구조 또는 다층 구조로 기판(50) 상에 형성될 수 있다. 상기 버퍼층은 기판(50)의 평탄도를향상시킬 수 있으며, 게이트 전극(55) 등을 형성하는 동안 금속 원자들이 기판(50)으로 확산되는 현상을 방지할수 있다. 또한, 상기 버퍼층은 기판(50)과 게이트 전극(55) 사이에 발생되는 스트레스를 완화시킬 수 있다.

- [0063] 도 3 및 도 4에 도시한 바와 같이, 기판(50) 상에 게이트 전극(55)을 커버하는 게이트 절연층(60)을 형성한다 (단계 S110). 게이트 절연층(60)은 화학 기상 증착 공정, 열산화 공정, 플라즈마 증대 화학 기상 증착(PECVD) 공정, 고밀도 플라즈마-화학 기상 증착(HDP-CVD) 공정 등을 이용하여 형성될 수 있다. 또한, 게이트 절연층(60)은 실리콘 화합물, 금속 산화물 등을 사용하여 형성될 수 있다. 예를 들면, 게이트 절연층(60)은 실리콘 산화물, 실리콘 산질화물, 하프늄 산화물, 지르코늄 산화물, 알루미늄 산화물, 탄탈륨 산화물 등을 사용하여 형성될 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0064] 예시적인 실시예들에 있어서, 게이트 절연층(60)은 상기 산화물 반도체 소자에 입사되는 광의 투과 정도를 고려하여 상대적으로 두꺼운 두께로 형성될 수 있다. 또한, 게이트 절연층(60)은 게이트 전극(55)을 충분히 커버하면서 평탄한 상면을 가질 수 있다. 이 경우, 화학 기계적 연마(CMP) 공정 및/또는 에치-백(etch-back) 공정 등의 평탄화 공정을 적용하여 게이트 절연층(60)의 상면을 평탄화시킬 수 있다.

- [0065] 도 3 및 도 5를 참조하면, 게이트 절연층(60) 상에 전극층(65)을 형성한다(단계 S120). 전극층(65)은 금속, 합

금, 금속 질화물, 도전성 금속 산화물, 투명 도전성 물질 등을 스퍼터링 공정, 프린팅 공정, 진공 증착 공정, 화학 기상 증착 공정, 원자층 적층 공정 등으로 게이트 절연층(60) 상에 증착하여 형성될 수 있다. 예를 들면, 전극층(65)은 알루미늄, 구리, 몰리브데늄, 티타늄, 크롬, 탄탈륨, 텅스텐, 네오디뮴, 스칸듐, 이들의 합금, 이들의 질화물, 각기 인듐 주석 산화물, 인듐 아연 산화물, 아연 산화물, 주석 산화물, 탄소 나노 튜브 등을 사용하여 형성될 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 이와 같은 전극층(65)은 금속, 합금, 금속 질화물, 도전성 금속 산화물, 투명 도전성 물질 등을 포함하는 단층 구조 또는 다층 구조로 형성될 수 있다.

- [0066] 다른 예시적인 실시예들에 있어서, 게이트 절연층(60)과 전극층(65) 사이에는 식각 저지층 및/또는 보호층이 형성될 수 있다. 예를 들면, 상기 식각 저지층 및/또는 상기 보호층은 산화물, 질화물, 산질화물, 반도체 산화물 등을 사용하여 형성될 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 상기 식각 저지층 및/또는 상기 보호층은 후속하여 전극층(65)을 식각하는 동안 게이트 절연층(60)을 포함하는 하부 구조물을 보호하는 기능을 수행할 수 있다.

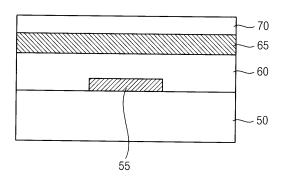

- [0067] 전국층(65) 상에는 마스크층(70)이 형성된다(단계 S130). 예시적인 실시예들에 있어서, 마스크층(70)은 포토레지스트를 스핀 코팅(spin coating) 공정으로 전국층(65) 상에 도포하여 형성될 수 있다. 다른 예시적인 실시예들에 따르면, 마스크층(70)은 산화물, 질화물, 산질화물 등의 전국층(65)에 대해 상대적으로 높은 식각 선택비 (etching selectivity)를 갖는 물질을 사용하여 형성될 수 있다. 예를 들면, 마스크층(70)은 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물 등을 사용하여 형성될 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 이 경우, 마스크층(70)은 화학 기상 증착 공정, 원자층 적층 공정, 플라즈마 증대 화학 기상 증착 공정, 고밀도 플라즈마-화학 기상 증착 공정 등을 이용하여 형성될 수 있다. 또한, 마스크층(70)은 전술한 산화물, 질화물 및/또는 산질화물을 포함하는 단층 구조 또는 다층 구조로 형성될 수 있다.

- [0068] 도 3 및 도 6을 참조하면, 마스크층(70)을 부분적으로 식각하여 전극층(65) 상에 마스크 패턴(75)을 형성한다 (단계 S140). 마스크 패턴(75)은 전극층(65) 중에서 아래에 게이트 전극(55)이 위치하는 부분을 노출시킨다. 마스크층(70)이 포토레지스트를 포함하는 경우, 마스크 패턴(75)은 노광(exposure) 과정 및 현상(developing) 과정을 통해 형성될 수 있다. 마스크층(70)이 상술한 산화물, 질화물 및/또는 산질화물을 포함하는 경우, 마스크 패턴(75)은 사진 식각 공정을 이용하여 전극층(65) 상에 형성될 수 있다. 예시적인 실시예들에 있어서, 마스크 패턴(75)에 의해 노출되는 부분의 전극층(65)의 면적은 게이트 전극(55)의 면적에 비하여 실질적으로 작을 수 있다.

- [0069] 마스크 패턴(75)을 식각 마스크로 이용하여 전극층(65)을 부분적으로 식각함으로써, 게이트 절연층(60) 상에 소스 전극(80) 및 드레인 전극(85)을 형성한다(단계 S150). 예시적인 실시예들에 있어서, 소스 전극(80)과 드레인 전극(85)은 각기 기판(50)에 실질적으로 직교하는 축선에 대하여 상대적으로 큰 경사 각도로 기울어진 측벽을 가질 수 있다. 예를 들면, 소스 및 드레인 전극(80, 85)은 각기 약 30° 내지 약 90° 정도의 상대적으로 큰 경사 각도를 갖는 측벽을 포함할 수 있다. 소스 및 드레인 전극(80, 85)이 형성되면, 아래에 게이트 전극(65)이 위치하는 부분의 게이트 절연층(60)이 노출된다. 소스 및 드레인 전극(80, 85)에 의해 노출되는 부분의 게이트 절연층(60)은 게이트 전극(55)에 비하여 실질적으로 작은 면적을 가질 수 있다. 소스 및 드레인 전극(80, 85)의 단부들은 각기 게이트 전극(55)의 양측부들과 부분적으로 중첩될 수 있다.

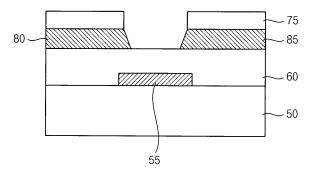

- [0070] 도 3 및 도 7을 참조하면, 전극층(65)을 패터닝하여 소스 및 드레인 전극(80, 85)을 형성하는 동안, 소스 및 드레인 전극(80, 85) 사이로 노출되는 게이트 절연층(60)이 식각 손상을 입을 수 있으며, 게이트 절연층(60)의 표면에는 잔류 응력이 발생될 수 있다. 또한, 게이트 절연층(60)의 표면 상에는 식각 부산물(88)들이 잔류하게 된다. 이와 같은 식각 부산물(88)들은 전극층(65)을 구성하는 금속 원자들이 식각 용액 또는 식각 가스와 반응하여 생성된 금속 화합물을 포함할 수 있다.

- [0071] 소스 및 드레인 전극(80, 85) 사이에서 노출되는 게이트 절연층(60)에 대해 화살표들로 나타낸 바와 같이 플라즈마 처리를 수행한다(단계 S160). 이러한 플라즈마 처리에 의해 게이트 절연층(60)이 부분적으로 제거됨으로써, 도 8에 도시한 바와 같이 게이트 절연층(60)에 리세스 구조(68)가 형성된다. 즉, 식각 손상을 입거나 내부 응력 또는 잔류 응력 등이 존재하는 게이트 절연층(60)의 일부와 게이트 절연층(60)의 표면에 잔류하는 식각 부산물(88)들이 상기 플라즈마 처리에 의해 제거될 수 있다. 예를 들면, 리세스 구조(68)는 게이트 절연층(65)의 상면으로부터 약 100Å 내지 약 300Å 정도의 깊이로 형성될 수 있다. 또한, 리세스 구조(68)는 기판(50)에 실질적으로 직교하는 방향으로부터 약 10° 내지 약 60° 정도의 상대적으로 작은 경사 각도로 기울어

진 측벽을 가질 수 있다. 예시적인 실시예들에 따르면, 상기 플라즈마 처리는 황 불화물을 함유하는 가스, 염소 불화물을 함유하는 가스, 염화수소를 함유하는 가스, 붕소 염화물을 함유하는 가스, 탄화수소를 함유하는 가스, 산소를 함유하는 가스, 오존을 함유하는 가스 등으로부터 생성되는 플라즈마를 사용하여 수행될 수 있다. 이들 가스는 단독으로 또는 서로 혼합되어 사용될 수 있다. 예를 들면, 상기 플라즈마 처리는 황 불화물을 함유하는 제1 가스와 산소를 함유하는 제2 가스의 혼합 가스로부터 생성되는 플라즈마를 사용하여 수행될 수 있다.

- [0072] 게이트 절연층(60)에 대해 전술한 플라즈마 처리를 수행한 후, 소스 및 드레인 전극(80, 85)으로부터 마스크 패턴(75)을 제거한다(단계 S170). 마스크 패턴(75)이 포토레지스트를 포함하는 경우, 스트리핑 공정 및/또는 애싱 공정을 이용하여 마스크 패턴(75)을 제거할 수 있다. 한편, 마스크 패턴(75)이 산화물, 질화물 및/또는 산질화물을 포함하는 경우에는 인산을 함유하는 식각 용액이나 식각 가스, 불산을 함유하는 식각 용액이나 식각 가스 등을 사용하여 마스크 패턴(75)을 제거할 수 있다.

- [0073] 도 3 및 도 8을 참조하면, 리세스 구조(68)를 채우면서 게이트 절연층(60), 소스 전극(80) 및 드레인 전극(85) 상에 액티브층(도시되지 않음)을 형성한다. 예시적인 실시예들에 있어서, 상기 액티브층은 인듐, 아연, 갈륨, 주석, 티타늄 등을 함유하는 이성분계(binary) 화합물, 삼성분계(ternary) 화합물, 사성분계(quaternary) 화합물 등을 포함하는 반도체 산화물을 사용하여 형성될 수 있다. 다른 예시적인 실시예들에 따르면, 상기 액티브층 상기 반도체 산화물에 리튬, 나트륨, 망간, 니켈, 팔라듐, 구리, 탄소, 질소, 인, 티타늄, 지르코늄, 바나듐, 루테늄, 게르마늄, 주석, 불소 등이 도핑된 조성물을 사용하여 형성될 수 있다. 이들은 단독으로 또는 서로 조합되어 첨가될 수 있다. 또 다른 예시적인 실시예들에 따르면, 상기 액티브층은 아몰퍼스 실리콘, 폴리 실리콘, 부분 결정화 실리콘, 미세 결정들을 포함하는 실리콘 등을 사용하여 형성될 수도 있다. 또한, 상기 액티브층은 스퍼터링 공정, 화학 기상 증착 공정, 프린팅 공정, 스프레이 공정, 진공 증착 공정, 원자층 적층 공정, 졸-겔 공정, 플라즈마 증대 화학 기상 증착 공정 들을 이용하여 형성될 수 있다. 예를 들면, 상기 액티브층은 약 1 x  $10^{12}$ 개/cm³ 내지 약 1 x  $10^{18}$ 개/cm³ 정도의 전자 캐리어 농도를 가질 수 있다.

- [0074] 상기 액티브층을 부분적으로 식각하여 게이트 절연층(60), 소스 전극(80) 및 드레인 전극(85) 상에 액티브 패턴 (90)을 형성한다(단계 S180). 이에 따라, 기판(50) 상에는, 게이트 전극(55), 리세스 구조(68)를 갖는 게이트 절연층(60), 소스 전극(80), 드레인 전극(85) 및 액티브 패턴(90)을 포함하는 산화물 반도체 소자가 제공된다. 예를 들면, 액티브 패턴(90)은 사진 식각 공정 또는 추가적인 식각 마스크를 사용하는 식각 공정을 이용하여 수 득될 수 있다.

- [0075] 예시적인 실시예들에 있어서, 액티브 패턴(90)은 리세스 구조(68)를 매립하며 소스 및 드레인 전극(80, 85) 상에 형성되기 때문에, 액티브 패턴(90)의 하부 측벽은 상대적은 작은 경사 각도를 가질 수 있지만. 액티브 패턴 (90)의 중앙부 측벽은 상대적으로 큰 경사 각도로 형성될 수 있다. 즉, 액티브 패턴(90)은 전체적으로 2가지 이상의 경사 각도를 가지는 측벽을 포함할 수 있다. 또한, 액티브 패턴(90)은 리세스 구조(68)를 갖는 게이트 절연층(60), 소스 전극(80) 및 드레인 전극(85)의 프로파일(profile)들을 따라 형성되므로, 액티브 패턴(90)에는 소스 및 드레인 전극(80, 85)에 인접하는 단차부들이 생성될 수 있다. 여기서, 액티브 패턴(90)의 양측부는 각기 소스 및 드레인 전극(80, 85) 상으로 연장될 수 있다. 이에 따라, 액티브 패턴(90)의 하부는 게이트 전극(55)보다 실질적으로 작은 면적을 가질 수 있는 반면, 액티브 패턴(90)의 상부는 게이트 전극(55)에 비하여 실질적으로 넓은 면적을 가질 수 있다.

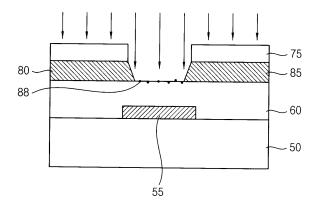

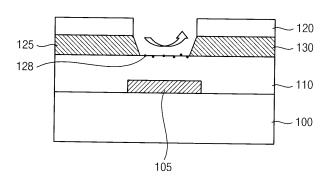

- [0076] 도 9는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다. 도 10 내지 도 12는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다. 도 9 내지 도 12에 있어서, 도 1을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 산화물 반도체 소자의 제조 방법을 예시적으로 설명하지만, 도 9 내지 도 12를 참조하여 설명하는 산화물 반도체 소자의 제조 방법은 게이트 전극, 게이트 절연층, 소스 전극, 드레인 전극, 액티브 패턴 등이 다양한 구조로 배치된 구성을 가지는 다른 산화물 반도체 소자들의 제조 방법에도 적용 가능함을 이해할 수 있을 것이다.

- [0077] 도 9 및 도 10을 참조하면, 투명 절연 기판을 포함하는 기판(100) 상에 게이트 전극(105)을 형성한 후(단계 S200), 기판(100) 상에 게이트 전극(105)을 덮는 게이트 절연층(110)을 형성한다(단계 S210).

- [0078] 게이트 전극(105)은 금속, 합금, 금속 질화물, 도전성 금속 산화물, 투명 도전성 물질 등을 사용하여 형성될 수 있으며, 게이트 절연층(110)은 실리콘 화합물, 금속 산화물 등을 사용하여 형성될 수 있다. 게이트 절연층(110)은 게이트 전극(105)을 충분히 커버하도록 상대적으로 두꺼운 두께로 형성될 수 있다. 여기서, 게이트 절연층(110)은 실질적으로 평탄한 상면을 가질 수 있으며, 이와 같은 게이트 절연층(110)의 평탄한 상면을 구현하기

위하여 게이트 절연층(110)에 대해 평탄화 공정이 추가적으로 수행될 수 있다.

- [0079] 게이트 절연충(110) 상에는 전극충(115)이 형성된다(단계 S220). 전극충(115)은 금속, 합금, 금속 질화물, 도전성 금속 산화물, 투명 도전성 물질 등을 포함할 수 있다. 전극충(115)은 단충 구조 또는 다충 구조로 형성될 수 있다. 예시적인 실시예들에 있어서, 게이트 절연충(110)이 실질적으로 평탄한 상면을 가질 경우, 전극충(115)도 실질적으로 게이트 절연충(110)으로부터 유래되는 실질적으로 평탄한 상면을 가질 수 있다.

- [0080] 도 9 및 도 11을 참조하면, 전극층(115) 상에 마스크 패턴(120)을 형성한다(단계 S230). 예를 들면, 마스크 패턴(120)은 포토레지스트, 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물 등을 사용하여 형성될 수 있다. 마스크 패턴(120)은 게이트 전극(105) 상부에 위치하는 부분의 전극층(115)을 노출시킬 수 있다. 이 경우, 마스크 패턴(120)에 의해 노출되는 전극층(115)의 면적은 게이트 전극(105)의 면적보다 실질적으로 작을 수 있다.

- [0081] 마스크 패턴(120)을 식각 마스크로 이용하는 식각 공정을 통해 전극층(115)을 패터닝하여 게이트 절연층(110) 상에 소스 전극(125)과 드레인 전극(130)을 형성한다(단계 S240). 소스 전극(125)과 드레인 전극(130)은 소정의 간격을 개재하여 각기 게이트 절연층(110)의 일측 및 타측 상에 형성될 수 있다. 소스 및 드레인 전극(125, 130)의 형성에 따라 게이트 절연층(110)의 일부가 소스 및 드레인 전극(125, 130) 사이에서 노출된다.

- [0082] 전극층(115)을 식각하는 동안 노출되는 게이트 절연층(110)에는 식각 손상, 잔류 응력, 내부 응력 등이 발생할수 있고, 금속 화합물을 포함하는 식각 부산물(128)들이 게이트 절연층(110) 표면에 잔류할 수 있다. 이러한 결함들이 생성된 게이트 절연층(110)에 액티브 패턴(도시되지 않음)을 형성할 경우, 상기 산화물 반도체 소자의 채널 영역이 형성되는 게이트 절연층(110)과 상기 액티브 패턴 사이의 계면이 열화되어 상기 산화물 반도체 소자의 다양한 특성들이 저하되는 문제가 발생한다.

- [0083] 소스 및 드레인 전극(125, 130) 사이의 게이트 절연층(110)에 대해 화살표로 도시한 바와 같이 세정 처리를 수행한다(단계 S250). 이와 같은 세정 처리에 의해 노출된 게이트 절연층(110)이 부분적으로 도 12에 도시한 바와 같이 제거되어 게이트 절연층(110)에 리세스 구조(118)가 형성된다. 즉, 게이트 절연층(110)의 결함들이 상기세정 처리에 의해 제거되면서, 게이트 절연층(110)에 소정의 깊이를 갖는 리세스 구조(118)가 마련된다. 예시적인 실시예들에 있어서, 상기 세정 처리는 금속 화합물을 제거할 수 있는 용액과 순수 또는 탈이온수(deionized water)의 혼합 용액을 사용하여 수행될 수 있다. 예를 들면, 상기 금속 화합물을 제거할 수 있는 용액은 불화수소를 함유하는 용액, 염화수소를 함유하는 용액, 인산을 함유하는 용액, 수산화칼륨을 함유하는 용액, 브롬화수소를 함유하는 용액, 보롬화요오드를 함유하는 용액 등을 포함할 수 있다. 이들 용액들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0084] 도 9 및 도 12를 참조하면, 게이트 절연충(110)에 리세스 구조(118)를 형성한 다음, 소스 및 드레인 전극(125, 130)으로부터 마스크 패턴(120)을 제거한다(단계 S260). 마스크 패턴(120)은 건식 식각 공정 또는 습식 식각 공정을 이용하여 제거될 수 있다. 마스크 패턴(120)이 제거되면, 소스 및 드레인 전극(125, 130)이 노출된다.

- [0085] 리세스 구조(118)를 갖는 게이트 절연충(110), 소스 전극(125) 및 드레인 전극(130) 상에 액티브충(도시되지 않음)을 형성한 후, 사진 식각 공정 또는 추가적인 마스크를 이용하는 식각 공정을 통해 상기 액티브충을 패터닝함으로써, 게이트 절연충(110)과 소스 및 드레인 전극(125, 130) 상에 상기 액티브 패턴을 형성한다. 이에따라, 도 1을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는산화물 반도체 소자가 기판(100) 상에 제공될 수 있다.

- [0086] 도 13은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다. 도 13에 예시적으로 도시한 산화물 반도체 소자의 제조 방법은 게이트 절연층에 대해 플라즈마 처리와 세정 처리가 수행되는 점을 제외하면 도 2를 참조하여 설명한 산화물 반도체 소자의 제조 방법과 실질적으로 동일하거나 실질적으로 유사한 단계들을 포함할 수 있다.

- [0087] 도 13을 참조하면, 기판 상에 게이트 전극을 형성한 다음(단계 S300), 상기 기판 상에 상기 게이트 전극을 덮는 게이트 절연층을 형성한다(단계 S310). 이 때, 상기 게이트 절연층은 상기 게이트 전극이 노출되지 않도록 상대 적으로 두꺼운 두께를 가질 수 있으며, 실질적으로 평탄한 상면을 포함할 수 있다.

- [0088] 상기 게이트 절연층 상에 전극층을 형성한 후(단계 S320), 상기 전극층 상에 마스크 패턴을 형성한다(단계 S330). 상기 전극층은 상기 게이트 절연층의 구조에 따라 실질적으로 평탄한 상면을 가질 수 있다. 상기 마스크 패턴에 의해 상기 전극층 중에서 아래에 상기 게이트 전극이 위치하는 부분이 노출된다.

- [0089] 상기 마스크 패턴을 식각 마스크로 이용하여 상기 전극층을 패터닝함으로써, 상기 게이트 절연층 상에 소스 전

극과 드레인 전극을 형성한다(단계 S340). 상기 소스 및 드레인 전극은 상기 게이트 전극을 중심으로 상기 게이트 절연층 상에 소정의 간격으로 이격된다. 따라서, 상기 게이트 절연층의 일부가 상기 소스 및 드레인 전극 사이에서 노출된다. 상기 전극층을 식각하여 소스 및 드레인 전극을 형성하는 동안, 상기 게이트 절연층에는 식각 손상, 잔류 응력, 내부 응력 등이 생성될 수 있는 한편, 상기 전극층과 식각 용액 또는 식각 가스의 반응에 따라 금속 화합물을 함유하는 식각 부산물들이 상기 게이트 절연층 상에 잔류할 수 있다.

- [0090] 도 13에 도시한 바와 같이, 상기 게이트 절연층에 대해 플라즈마 처리를 수행한다(단계 S350). 이에 따라, 상기 소스 및 드레인 전극 사이의 상기 게이트 절연층이 일차적으로 식각되어 상기 게이트 절연층에 예비 리세스 구조가 형성된다. 예시적인 실시예들에 있어서, 플라즈마 처리 시간, 플라즈마 생성 가스의 유량 등과 같은 상기 플라즈마 처리의 공정 조건들을 조절함으로써, 상기 예비 리세스 구조가 도 1을 참조하여 설명한 리세스 구조 (18)에 비하여 실질적으로 작거나 실질적으로 유사한 깊이를 가질 수 있다. 상기 플라즈마 처리 동안, 상기 게이트 절연층에 발생된 결함들과 상기 게이트 절연층 상에 잔류하는 식각 부산물들이 일차적으로 제거된다. 예를 들면, 상기 게이트 절연층의 결함들과 상기 식각 부산물들이 상기 게이트 절연층으로부터 부분적으로 제거되거나 완전히 제거될 수 있다.

- [0091] 상기 플라즈마 처리가 수행된 상기 게이트 절연층에 대하여 이차적으로 세정 처리를 수행한다(단계 S360). 이러한 세정 처리는 금속 화합물을 제거할 수 있는 용액과 순수나 탈이온수를 사용하여 수행될 수 있다. 예시적인 실시예들에 따르면, 상술한 플라즈마 처리와 후속하는 세정 처리를 통해 상기 게이트 절연층의 결함들과 상기 게이트 절연층 상에 잔류하는 식각 부산물들을 상기 게이트 절연층으로부터 효과적이면서도 완전하게 제거할 수 있다. 또한, 상기 플라즈마 처리에 따라 상기 게이트 절연층에 형성된 상기 예비 리세스를 확장시켜 상기 소스 및 드레인 전국 사이의 상기 게이트 절연층에 리세스 구조를 형성할 수 있다. 여기서, 상기 리세스 구조는 도 1을 참조하여 설명한 리세스 구조(18)와 실질적으로 동일하거나 실질적으로 유사한 깊이를 가질 수 있다.

- [0092] 다시 도 13을 참조하면, 상기 소스 및 드레인 전국으로부터 상기 마스크 패턴을 제거한 다음(단계 S370), 상기 리세스 구조를 매립하면서 상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전국 상에 액티브층을 형성한다 (단계 S380). 상기 액티브층은 이성분계 화합물, 삼성분계 화합물, 사성분계 화합물 등을 포함하는 반도체 산화물을 사용하여 형성될 수 있다. 상기 액티브층에는 리튬, 나트륨, 망간, 니켈, 팔라듐, 구리, 카드뮴, 탄소, 인, 티타늄, 지르코늄, 바나듐, 루테늄, 게르마늄, 주석 등이 추가적으로 도핑될 수 있다.

- [0093] 사진 식각 공정, 추가적인 식각 마스크를 이용하는 식각 공정 등을 통하여 상기 액티브층을 패터닝함으로써, 상기 소스 전국, 상기 드레인 전국 및 상기 게이트 절연층 상에 액티브 패턴을 형성한다(단계 S380). 따라서, 도 1 또는 도 8을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 산화물 반도체 소자가 상기 기판 상에 제공될 수 있다. 이 경우, 상기 액티브 패턴에는 상기 소스 및 드레인 전 극에 인접하는 단차부들이 형성될 수 있다.

- [0094] 본 발명의 예시적인 실시예들에 따르면, 전술한 플라즈마 처리 및 세정 처리를 순차적으로 수행함으로써, 상기 게이트 절연층에 존재하는 결함들과 상기 게이트 절연층 상에 잔류하는 식각 부산물들을 완전히 제거할 수 있다. 따라서, 상기 게이트 절연층과 상기 액티브 패턴 사이의 계면이 불균일해지는 현상을 방지할 수 있으며, 상기 산화물 반도체 소자의 채널 영역이 형성되는 부분의 게이트 절연층의 두께를 감소시킴으로써, 전하이동도, 문턱 전압 산포, 구동 전류 등의 산화물 반도체 소자의 다양한 전기적인 특성들을 향상시킬 수 있다.

- [0095] 도 14는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다. 도 14에 예시적으로 도시한 산화물 반도체 소자의 제조 방법은 게이트 절연층에 대해 플라즈마 처리와 세정 처리가 수행되는 점을 제외하면 도 2를 참조하여 설명한 산화물 반도체 소자의 제조 방법과 실질적으로 동일하거나 실질적으로 유사한 단계들을 포함할 수 있다.

- [0096] 도 14를 참조하면, 기판 상에 게이트 전극을 형성한 다음(단계 S400), 상기 게이트 전극을 덮으면서 상기 기판 상에 게이트 절연층을 형성한다(단계 S410). 예를 들면, 상기 게이트 절연층은 상기 게이트 전극을 충분히 커버하도록 상대적으로 두꺼운 두께를 가질 수 있다.

- [0097] 상기 게이트 절연층 상에 전극층을 형성한 후(단계 S420), 상기 전극층 상에 마스크 패턴을 형성한다(단계 S430). 상기 게이트 절연층이 실질적으로 평탄한 상면들 가질 경우, 상기 전극층도 상기 게이트 절연층의 형상에 따라 실질적으로 평탄한 상면을 구비할 수 있다. 상기 마스크 패턴은 사진 공정, 추가적인 마스크를 이용하는 공정 등을 통해 상기 전극층 상에 제공될 수 있다.

- [0098] 상기 마스크 패턴을 이용하여 상기 전극층을 부분적으로 식각함으로써 상기 게이트 절연층의 일측과 타측 상에

소스 전극과 드레인 전극을 형성한다(단계 S440). 상기 소스 및 드레인 전극은 상기 산화물 반도체 소자의 채널 영역의 길이와 실질적으로 동일하거나 실질적으로 유사한 간격을 개재하여 상기 게이트 절연층 상에서 서로 이격될 수 있다.

- [0099] 상기 소스 및 드레인 전극의 형성에 따라 노출되는 부분의 상기 게이트 절연층에 대해 플라즈마 처리를 수행한다(단계 S450). 이 경우, 상기 플라즈마 처리는 도 3을 참조하여 설명한 플라즈마 처리와 실질적으로 동일하거나 실질적으로 유사할 수 있다. 상기 플라즈마 처리에 따라, 상기 게이트 절연층에 생성된 결함들과 식각 부산물들이 일차적으로 제거되면서 상기 소스 및 드레인 전극 사이의 상기 게이트 절연층에는 예비 리세스 구조가형성된다. 이 때, 상기 예비 리세스 구조는 도 1을 참조하여 설명한 리세스 구조(18)의 깊이 보다 실질적으로 작거나 실질적으로 유사한 깊이를 가질 수 있다.

- [0100] 상기 게이트 절연층에 상기 예비 리세스 구조를 형성한 다음, 상기 소스 및 드레인 전국으로부터 상기 마스크 패턴을 제거한다(단계 S460). 상기 마스크 패턴은 건식 식각 공정 또는 습식 식각 공정을 이용하여 제거될 수 있다.

- [0101] 상기 예비 리세스 구조를 갖는 게이트 절연층에 대하여 세정 처리를 수행한다(단계 S470). 여기서, 상기 세정 처리는 도 9를 참조하여 설명한 세정 처리와 실질적으로 동일하거나 실질적으로 유사할 수 있다. 이러한 세정 처리에 따라 상기 게이트 절연층의 결함들 및 식각 부산물들이 완전히 제거되는 한편, 상기 예비 리세스 구조의 치수가 실질적으로 확장되면서 상기 소스 및 드레인 전극 사이의 상기 게이트 절연층에는 리세스 구조가 형성된다. 예시적인 실시예들에 따르면, 상기 마스크 패턴을 제거한 후에 상기 세정 처리를 수행하기 때문에 상기 마스크 패턴을 제거하는 동안 추가적으로 발생되는 상기 게이트 절연층의 손상이나 상기 마스크 패턴으로부터 유래되는 식각 부산물들을 효율적으로 제거할 수 있다.

- [0102] 상기 리세스 구조를 포함하는 상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전극 상에 액티브 패턴을 형성한다(단계 S480). 예시적인 실시예들에 있어서, 상기 리세스 구조를 채우면서 상기 소스 및 드레인 전극 상에 액티브층을 형성한 후, 사진 식각 공정 또는 추가적인 식각 마스크를 이용하는 식각 공정을 적용하여 상기 액티 브층을 부분적으로 식각함으로써, 상기 게이트 절연층, 상기 소스 전극 및 상기 드레인 전극 상에 상기 액티브 패턴을 형성할 수 있다. 이에 따라, 도 1 또는 도 8을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 산화물 반도체 소자가 상기 기판 상에 제공될 수 있다.

- [0103] 본 발명의 예시적인 실시예들에 따르면, 상기 마스크 패턴을 제거한 후에 상기 세정 처리를 플라즈마 처리된 게 이트 절연층에 대하여 수행하기 때문에, 상기 게이트 전극의 결함이나 식각 부산물들을 완전하게 제거할 수 있을 뿐만 아니라, 상기 마스크 패턴을 제거하는 동안 추가적으로 발생되는 상기 게이트 절연층의 손상이나 상기 마스크 패턴으로부터 유래되는 식각 부산물들을 효과적으로 제거할 수 있다. 이에 따라, 상기 산화물 반도체 소자의 채널 영역의 균일성을 보다 향상시켜 상기 산화물 반도체 소자의 다양한 전기적인 특성들을 더욱 개선할수 있다.

- [0104] 도 15는 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자를 설명하기 위한 단면도이다. 도 15 에 도시한 산화물 반도체 소자는, 소스 전극(175) 및 드레인 전극(190)의 구조를 제외하면, 도 1을 참조하여 설명한 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가질 수 있다.

- [0105] 도 15를 참조하면, 상기 산화물 반도체 소자는, 게이트 전극(155), 리세스 구조(168)를 갖는 게이트 절연층 (160), 소스 전극(175), 드레인 전극(190) 및 액티브 패턴(195)을 포함한다.

- [0106] 게이트 전극(155)은 기판(150) 상에 배치될 수 있고, 게이트 절연층(160)은 기판(150) 상에 위치하여 게이트 전 극(155)을 커버할 수 있다. 게이트 절연층(160)은 실질적으로 평탄한 상면을 가질 수도 있지만, 후술하는 바와 같이 게이트 전극(155)에 인접하는 단차부를 가질 수도 있다.

- [0107] 게이트 절연충(160)에는 리세스 구조(168)가 마련되며, 액티브 패턴(195)은 리세스 구조(168)를 채우면서 소스 및 드레인 전극(175, 190) 상에 배치될 수 있다. 여기서, 리세스 구조(168)는 도 1을 참조하여 설명한 리세스 구조(18)와 실질적으로 동일하거나 실질적으로 유사한 치수와 형상을 가질 수 있다.

- [0108] 예시적인 실시예들에 있어서, 소스 전극(175)은 제1 전극 패턴(165)과 제2 전극 패턴(170)을 구비할 수 있으며, 드레인 전극(190)은 제3 전극 패턴(180)과 제4 전극 패턴(185)을 포함할 수 있다. 제1 및 제3 전극 패턴(165, 180)은 각기 금속, 합금, 투명 도전성 물질을 등을 포함할 수 있으며, 제2 및 제4 전극 패턴(170, 185)은 각기 금속 질화물, 금속 산화물 등을 포함할 수 있다. 예를 들면, 제1 및 제3 전극 패턴(165, 180)은 크롬, 알루미늄, 구리, 몰리브데늄, 티타늄, 탄탈륨, 텅스텐, 네오디뮴, 스칸듐, 이들의 합금, 스트론튬 루데늄 산화

물, 인듐 주석 산화물, 인듐 아연 산화물, 아연 산화물, 주석 산화물, 탄소 나노 튜브 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 또한, 제2 및 제4 전극 패턴(170, 185)은 각기 제1 및 제3 전극 패턴(165, 180)으로부터 유래되는 금속 질화물, 투명 도전성 물질의 질화물 등을 포함할 수 있다. 예를 들면, 제2 및 제4 전극 패턴(170, 185)은 크롬 질화물(CrNx), 알루미늄 질화물(AlNx), 티타늄 질화물(TiNx), 탄탈륨 질화물(TaNx), 텅스텐 질화물(WNx), 몰리브데늄 질화물(MoNx), 네오디뮴 질화물(NdNx), 스칸듐 질화물(ScNx), 루테늄 질화물(RuNx), 이들의 합금의 질화물, 스트론튬 루테늄 산질화물, 인듐 주석 산질화물, 인듐 아연 산질화물, 아연 산질화물, 주석 산질화물, 탄소 나노 튜브의 질화물 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 제2 및 제4 전극 패턴(170, 185)이 금속 질화물 또는 투명 도전성 물질의질화물을 포함하는 경우, 후속하는 플라즈마 처리 및/또는 세정 처리 동안 제1 및 제3 전극 패턴(165, 180)을 효과적으로 보호할 수 있으므로, 소스 및 드레인 전극(175, 190)의 추가적인 손상이나 열화를 방지하여 상기 산화물 반도체 소자의 전기적 특성을 보다 향상시킬 수 있다.

- [0109] 도 16은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 공정 순서도이다. 도 17 내지 도 20은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다. 도 16 내지 도 20에 있어서, 도 15를 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 산화물 반도체 소자의 제조 방법을 예시적으로 설명하지만, 도 16 내지 도 20을 참조하여 설명하는 도시한 산화물 반도체 소자의 제조 방법은 게이트 전극, 게이트 절연층, 소스 전극, 드레인 전극, 액티브 패턴 등이 다양한 구조로 배치된 구성을 가지는 다른 산화물 반도체 소자들에도 적용 가능함을 이해할 수 있을 것이다.

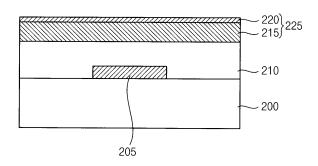

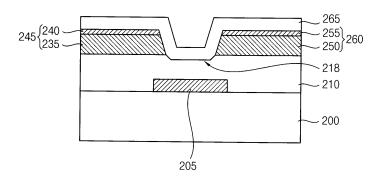

- [0110] 도 16 및 도 17을 참조하면, 기판(200) 상에 게이트 전극(205)을 형성한 후(단계 S500), 게이트 전극(205)과 기판(200) 상에 게이트 절연층(210)을 형성한다(단계 S510). 게이트 절연층(210)은 실질적으로 평탄한 표면을 가질 수 있다.

- [0111] 게이트 절연층(210) 상에 제1 전극막(215)을 형성한 다음(단계 S520), 제1 전극막(215) 상에 제2 전극막(220)을 형성한다(단계 S530). 따라서, 게이트 절연층(210) 상에는 제1 및 제2 전극막(215, 220)을 포함하는 전극층 (225)이 형성된다.

- [0112] 제1 전극막(215)은 금속, 합금, 투명 도전성 물질 등을 사용하여 형성될 수 있다. 예를 들면, 제1 전극막(215)은 크롬, 알루미늄, 티타늄, 탄탈륨, 텅스텐, 몰리브데늄, 네오디뮴, 스칸듐, 루테늄, 이들의 합금, 스트론튬루테늄 산화물, 인듐 주석 산화물, 인듐 아연 산화물, 아연 산화물, 주석 산화물, 탄소 나노 튜브 등을 사용하여 형성될 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다. 제1 전극막(215) 스퍼터링 공정, 화학 기상 증착 공정, 원자층 적층 공정, 진공 증착 공정, 프린팅 공정, 스프레이 공정 등을 이용하여 게이트 절연층(210) 상에 형성될 수 있다.

- [0113] 제2 전극막(220)은 금속 질화물, 투명 도전성 물질의 질화물 등을 사용하여 형성될 수 있다. 예를 들면, 제2 전 극막(220)은 크롬 질화물(CrNx), 알루미늄질화물, 티타늄 질화물, 탄탈륨 질화물, 텅스텐 질화물, 몰리브데늄 질화물, 네오디뮴 질화물, 스칸듐 질화물, 루테늄 질화물, 이들의 합금의 질화물, 스트론튬 루테늄 산질화물, 인듐 주석 산질화물, 인듐 아연 산질화물, 아연 산질화물, 주석 산질화물, 탄소 나노 튜브의 질화물 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0114] 제2 전극막(220)은 제1 전극막(215)에 대해 질화 처리(nitration treatment)를 수행하여 형성될 수 있다. 즉, 제1 전극막(215)에 대해 질화 처리를 수행하여 제1 전극막(220)의 일부가 제2 전극막(220)으로 변화될 수 있다. 예를 들면, 상기 질화 처리는 제1 전극막(215)을 질소를 포함하는 분위기 하에서 열처리하는 공정을 포함할 수 있다. 예를 들면, 상기 질소를 포함하는 분위기는 질소(N2) 가스, 일산화질소(N0) 가스, 일산화이질소(N20) 가스, 이산화일질소(N02) 가스, 암모니아(NH3) 가스 등을 포함할 수 있다. 이들 가스는 단독으로 또는 서로 조합되어 사용될 수 있다. 다른 예시적인 실시예들에 따르면, 상기 질화 처리는 질소를 포함하는 가스로부터 생성되는 플라즈마를 이용하여 제1 전극막(215)을 처리하는 공정을 포함할 수 있다. 예를 들면, 상기 플라즈마를 생성하기 위한 가스는 질소 가스, 일산화질소 가스, 일산화이질소 가스, 이산화일질소 가스, 암모니아 가스 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

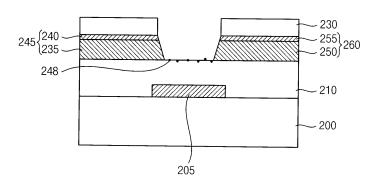

- [0115] 도 16 및 도 18을 참조하면, 제2 전극막(220) 상에 마스크 패턴(230)을 형성한 다음(단계 S540), 마스크 패턴 (230)을 식각 마스크로 이용하여 전극층(225)을 부분적으로 식각함으로써, 게이트 절연층(210) 상에 소스 전극 (245)과 드레인 전극(260)을 형성한다(단계 S550). 소스 전극(245)은 게이트 절연층(210)의 일측 상에 형성되는

제1 전극 패턴(235)과 제2 전극 패턴(240)을 포함하며, 드레인 전극(260)은 게이트 절연층(210)의 타측 상에 형성되는 제3 전극 패턴(250) 과 제4 전극 패턴(255)을 구비한다. 즉, 제1 전극막(215)은 제1 전극 패턴(235) 및 제3 전극 패턴(250)으로 패터닝되며, 제2 전극막(220)은 제2 전극 패턴(240) 및 제4 전극 패턴(255)으로 패터닝된다.

- [0116] 도 18에 도시한 바와 같이, 전극층(2250을 식각하여 소스 및 드레인 전극(245, 260)을 형성하는 동안 식각 부산물(248)들이 게이트 절연층(210) 상에 생성될 수 있으며, 게이트 절연층(210)에는 식각 손상, 잔류 응력 등이발생할 수 있다.

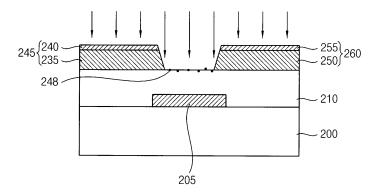

- [0117] 도 16 및 도 19를 참조하면, 소스 및 드레인 전극(245, 260)으로부터 마스크 패턴(230)을 제거한 후(단계 S560), 소스 전극(245)과 드레인 전극(260) 사이의 게이트 절연층(210)에 대해 플라즈마 처리 및/또는 세정 처리를 수행한다(단계 S570). 이에 따라, 소스 및 드레인 전극(245, 260) 사이의 게이트 절연층(210)에는 리세스 구조(218)(도 20 참조)가 형성된다. 여기서, 상기 플라즈마 처리는 도 3 및 도 7을 참조하여 설명한 플라즈마 처리와 실질적으로 동일하거나 실질적으로 유사할 수 있다. 또한, 상기 세정 처리는 도 9 및 도 11을 참조하여 설명한 세정 처리와 실질적으로 동일하거나 실질적으로 유사할 수 있다.

- [0118] 예시적인 실시예들에 따르면, 마스크 패턴(230)을 제거한 후에 게이트 절연층(210)에 대해 상기 플라즈마 처리 및/또는 세정 처리를 수행하더라도 제2 및 제4 전극 패턴(240 255)에 의해 제1 및 제3 전극 패턴(235, 250)이 보호되기 때문에, 제1 및 제3 전극 패턴(235, 250)이 식각 손상을 입는 것을 효과적으로 방지할 수 있다.

- [0119] 도 16 및 도 20을 참조하면, 리세스 구조(218)를 구비하는 게이트 절연층(210), 소스 전극(245) 및 드레인 전극 (260) 상에 액티브층(265)을 형성한다. 즉, 상기 액티브층은 리세스 구조(218)를 매립하면서 게이트 절연층 (210, 제2 전극 패턴(240) 및 제4 전극 패턴(255) 상에 형성된다.

- [0120] 사진 식각 공정, 추가적인 식각 마스크를 이용하는 식각 공정 등을 적용하여 게이트 절연층(210), 소스 전극 (245) 및 드레인 전극(260) 상에 리세스 구조(218)를 채우는 액티브 패턴(도시되지 않음)을 형성한다(단계 S580). 따라서, 기판(200) 상에는 도 15를 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질 적으로 유사한 구성을 가지는 산화물 반도체 소자가 제공될 수 있다.

- [0121] 도 21은 본 발명의 또 다른 예시적인 실시예들에 따른 산화물 반도체 소자를 설명하기 위한 단면도이다.

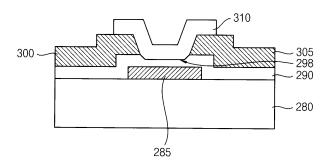

- [0122] 도 21을 참조하면, 상기 산화물 반도체 소자는, 게이트 전극(285), 리세스 구조(298)를 갖는 게이트 절연층 (290), 소스 전극(300), 드레인 전극(305) 및 액티브 패턴(310)을 포함한다.

- [0123] 예시적인 실시예들에 있어서, 게이트 절연층(290)은 게이트 전극(285)의 프로파일을 따라 기판(280) 상에 균일하게 형성될 수 있다. 이 경우, 게이트 절연층(290)은 게이트 전극(285)의 양측부에 인접하는 단차부들을 포함할 수 있다. 또한, 게이트 절연층(290)은 상대적으로 얇은 두께를 가질 수 있다. 예를 들면, 게이트 절연층(290)은 게이트 전극(285)의 상면으로부터 약 500Å 내지 약 1,000Å 정도의 두께를 가질 수 있다. 게이트 절연층(290)이 상기 단차부들을 가질 경우, 상기 산화물 반도체 소자의 전체적인 구성 요소들이 각기 단차부를 포함하는 구조를 가질 수 있다.

- [0124] 게이트 전극(285) 상에 위치하는 게이트 절연층(290)에는 리세스 구조(298)가 제공된다. 리세스 구조(298)의 형 상은 도 1을 참조하여 설명한 리세스 구조(18)와 실질적으로 동일하거나 실질적으로 유사할 수 있다. 예시적인 실시예들에 있어서, 리세스 구조(298)는 약 100Å 내지 약 300Å 정도의 깊이를 가질 수 있다. 따라서, 리세스 구조(298)의 깊이와 게이트 절연층(290)의 두께 사이의 비는 약 1.0: 0.7 내지 약 1.0: 10.0 정도가 될 수 있다. 즉, 게이트 절연층(290)이 단차부를 포함할 경우에는, 리세스 구조(298)의 깊이와 게이트 절연층(290)의 두께 사이의 비율이 감소할 수 있다. 리세스 구조(298)는 기판(280)에 실질적으로 직교하는 방향에 대해 상대적으로 작은 제1 각도로 경사진 측벽을 가질 수 있다.

- [0125] 소스 전극(300)과 드레인 전극(305)은 각기 리세스 구조(298)를 개재하여 게이트 절연층(290) 상에 위치할 수 있다. 예를 들면, 소스 전극(300)과 드레인 전극(305)은 리세스 구조(298)의 폭에 실질적으로 대응되는 거리만 큼 서로 이격될 수 있다. 예시적인 실시예들에 있어서, 소스 및 드레인 전극(300, 305)은 게이트 절연층(290)의 단차부들에 기인하는 단차부들을 포함할 수 있다. 예를 들면, 소스 및 드레인 전극(300, 305)은 각기 게이트 절연층(290)의 단차부들에 인접하는 단차부들을 포함할 수 있다. 또한, 소스 및 드레인 전극(300, 305)은 각기 게이트 전극(285)에 실질적으로 직교하는 축선에 대해 상대적으로 큰 제2 각도로 경사진 측벽을 구비할 수 있다. 다른 예시적인 실시예들에 따르면, 소스 및 드레인 전극(300, 305)은 각기 도 15를 참조하여 설명한 소스 및 드

레인 전극(175, 190)과 실질적으로 동일하거나 실질적으로 유사한 구성을 가질 수 있다.

- [0126] 액티브 패턴(310)은 리세스 구조(298)를 매립하면서 소스 및 드레인 전극(300, 305) 상에 배치된다. 이 경우, 액티브 패턴(310)은 리세스 구조(298)의 측벽과 소스 및 드레인 전극(300, 305)의 측벽들에 접촉되면서 게이트 절연층(290) 상에 위치할 수 있다. 따라서, 액티브 패턴(310)의 하부는 상대적으로 작은 제1 각도로 기울어진 측벽을 가질 수 있고, 액티브 패턴(310)의 중앙부는 상대적으로 큰 제2 각도로 경사진 측벽을 가질 수 있다. 또한, 액티브 패턴(310)은 게이트 절연층(290)에 접촉하면서 소스 및 드레인 전극(300, 305) 상에 배치되기 때문에, 게이트 절연층(290)의 단차부들에 인접하는 단차부들을 포함할 수 있다. 다른 예시적인 실시예들에 따르면, 액티브 패턴(310)의 양측부는 각기 소스 전극(300)과 드레인 전극(305) 상으로 연장될 수 있다. 이 경우, 액티브 패턴(310)은 소스 및 드레인 전극(300, 305)의 단차부들에 각기 인접하는 추가적인 단차부들을 구비할 수 있다. 예를 들면, 리세스 구조(298)를 채우는 액티브 패턴(310)은 실질적으로 이중 단차 구조를 가질 수 있다.

- [0127] 도 22 및 도 23은 본 발명의 또 다른 실시예들에 따른 산화물 반도체 소자의 제조 방법을 설명하기 위한 단면도들이다. 도 22 및 도 23에 있어서, 도 21을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 산화물 반도체 소자의 제조 방법을 예시적으로 설명하지만, 도 22 및 도 23을 참조하여 설명하는 도시한 산화물 반도체 소자의 제조 방법은 게이트 전극, 게이트 절연층, 소스 전극, 드레인 전극, 액티브 패턴 등이 다양한 구조로 배치된 구성을 가지는 다른 산화물 반도체 소자들에도 적용 가능함을 이해할 수 있을 것이다.

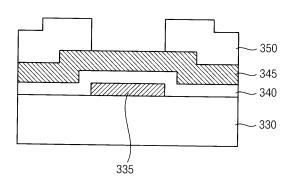

- [0128] 도 22를 참조하면, 투명 절연 물질을 포함하는 기판(330) 상에 게이트 전극(335)을 형성한다. 예시적인 실시예들에 있어서, 게이트 전극(335)은 기판(180)의 전면 상에 도전층(도시되지 않음)을 형성한 후, 이와 같은 도전층을 패터닝하여 수득될 수 있다. 예를 들면, 게이트 전극(335)은 금속, 합금, 금속 질화물, 투명 도전성 물질등을 사용하는 스퍼터링 공정, 화학 기상 증착 공정, 원자층 적층 공정, 진공 증착 공정, 프린팅 공정 등을 통해 기판(330) 상에 형성될 수 있다. 다른 예시적인 실시예들에 따르면, 게이트 전극(335)을 형성하기 전에 기판(330) 상에 버퍼층(도시되지 않음)을 추가적으로 형성할 수 있다.

- [0129] 게이트 전극(335)과 기판(330) 상에는 게이트 절연층(340)이 형성된다. 게이트 절연층(340)은 게이트 전극(335)의 프로파일을 따라 기판(330) 상에 균일한 두께로 형성될 수 있다. 게이트 절연층(190)이 기판(330) 상에서 균일한 두께를 가질 경우, 게이트 절연층(340)에는 게이트 전극(335)에 인접하는 단차부들이 형성될 수 있다. 예를 들면, 게이트 절연층(340) 중에서 게이트 전극(335)의 양측부에 인접하는 부분들에 단차부들이 생성될 수 있다. 게이트 절연층(340)은 실리콘 화합물 및/또는 금속 산화물을 사용하여 상대적으로 얇은 두께로 형성될 수 있다.

- [0130] 게이트 절연층(340) 상에 전극층(345)을 형성한다. 전극층(345)은 게이트 절연층(340)의 프로파일을 따라 균일하게 형성될 수 있다. 따라서, 전극층(345)에도 게이트 절연층(340)의 단차부들에 인접하는 단차부들이 생성될수 있다. 다른 예시적인 실시예들에 있어서, 전극층(345)은 도 17을 참조하여 설명한 전극층(225)과 실질적으로 동일하거나 실질적으로 유사한 구조로 형성될 수 있다.

- [0131] 전극층(345) 상에 마스크 패턴(350)을 형성한다, 마스크 패턴(350)은 포토레지스트, 산화물, 질화물, 산질화물 등을 사용하여 형성될 수 있다. 또한, 마스크 패턴(350)은 단층 구조 또는 다층 구조를 가질 수 있다.

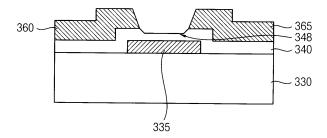

- [0132] 도 23을 참조하면, 마스크 패턴(350)을 이용하여 전극층(345)을 부분적으로 식각한다. 이에 따라, 게이트 절연 층(340)의 일측 및 타측 상에는 소스 전극(360)과 드레인 전극(365)이 형성된다. 예시적인 실시예들에 있어서, 소스 전극(360) 및 드레인 전극(365)은 각기 게이트 절연층(340)의 단차부들에 인접하는 단차부들을 구비할 수 있다. 소스 및 드레인 전극(360, 365)의 형성에 따라, 소스 및 드레인 전극(360, 365) 사이의 게이트 절연(340)의 일부가 노출된다. 소스 및 드레인 전극(360, 365)을 형성하기 위한 식각 공정 동안 노출된 부분의 게이트 절연층(340)에는 식각 손상, 잔류 응력 등이 발생할 수 있으며, 식각 부산물들이 형성될 수 있다.

- [0133] 노출된 부분의 게이트 절연층(340)에 대하여 플라즈마 처리 및/또는 세정 처리를 수행하여 리세스 구조(348)를 형성한다. 즉, 노출된 부분의 게이트 절연층(340)을 부분적으로 식각하여 소스 및 드레인 전극(360, 365) 사이에 리세스 구조(348)를 형성한다. 이 경우, 상기 플라즈마 처리는 도 3 및 도 7을 참조하여 설명한 플라즈마 처리와 실질적으로 동일하거나 실질적으로 유사할 수 있다. 또한, 상기 세정 처리는 도 9 및 도 11을 참조하여 설명한 세정 처리와 실질적으로 동일하거나 실질적으로 유사할 수 있다.

- [0134] 도시하지는 않았으나, 게이트 절연충(340), 소스 전극(360) 및 드레인 전극(365) 상에 액티브 패턴을 형성하여, 기판(330) 상에 산화물 반도체 소자를 형성한다. 이 경우, 상기 산화물 반도체 소자는 도 21을 참조

하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 실질적으로 유사한 구성을 가질 수 있다.

#### [0135] 산화물 반도체 소자의 특성 평가

[0136] 이하, 본 발명의 실험예들 및 비교예에 따른 산화물 반도체 소자들의 전기적인 특성들에 대하여 설명한다.

## [0137] <u>실험예 1</u>

[0138] 기판 상에 게이트 전극을 형성한 후, 상기 게이트 전극을 덮는 게이트 절연층을 상기 기판 상에 형성하였다. 상기 게이트 절연층 상에 전극층을 형성한 다음, 상기 전극층을 패터닝하여 상기 게이트 절연층 상에 소스 전극과 드레인 전극을 형성하였다. 육불화황(SF<sub>6</sub>) 가스와 산소(O<sub>2</sub>) 가스의 혼합 가스로부터 생성된 플라즈마를 이용하여 상기 소스 및 드레인 전극 사이의 게이트 절연층에 대해 플라즈마 처리를 수행하였다. 상기 플라즈마 처리에 따라 리세스 구조가 형성된 게이트 절연층과 상기 소스 및 드레인 전극 상에 액티브 패턴을 형성하여 산화물 반도체 소자를 제조하였다.

## [0139] <u>실험예 2</u>

[0140] 기판 상에 게이트 전극을 형성한 다음, 상기 게이트 전극을 커버하는 게이트 절연층을 상기 기판 상에 형성하였다. 상기 게이트 절연층 상에 전극층을 형성한 후, 상기 전극층을 패터닝하여 상기 게이트 절연층 상에 소스 전극과 드레인 전극을 형성하였다. 불산을 포함하는 용액을 사용하여 상기 소스 및 드레인 전극 사이의 게이트 절연층에 대해 세정 처리를 수행하였다. 상기 세정 처리에 따라 리세스 구조가 형성된 게이트 절연층과 상기 소스및 드레인 전극 상에 액티브 패턴을 형성하여 산화물 반도체 소자를 수득하였다.

#### [0141] 실험예 3

[0142] 기판 상에 게이트 전극을 형성하고, 상기 게이트 전극을 덮는 게이트 절연층을 상기 기판 상에 형성하였다. 상기 게이트 절연층 상에 전극층을 형성한 후, 상기 전극층을 패터닝하여 상기 게이트 절연층 상에 소스 전극과 드레인 전극을 형성하였다. 육불화황 가스와 산소 가스의 혼합 가스로부터 생성된 플라즈마를 이용하여 상기 소스 및 드레인 전극 사이의 게이트 절연층에 대해 일차적으로 플라즈마 처리를 수행하였다. 상기 플라즈마 처리된 게이트 절연층에 대하여 불산을 포함하는 용액을 사용하여 세정 처리를 수행하였다. 상기 플라즈마 처리 및 세정 처리에 따라 리세스 구조가 형성된 게이트 절연층과 상기 소스 및 드레인 전극 상에 액티브 패턴을 형성하여 산화물 반도체 소자를 수득하였다.

## [0143] 비교예

[0146]

[0144] 기판 상에 게이트 전극을 형성한 다음, 상기 게이트 전극을 덮는 게이트 절연층을 상기 기판 상에 형성하였다. 상기 게이트 절연층 상에 전극층을 형성한 다음, 상기 전극층을 패터닝하여 상기 게이트 절연층 상에 소스 전극과 드레인 전극을 형성하였다. 상기 소스 및 드레인 전극의 형성 후에 상기 게이트 절연층에 대해 플라즈마 처리나 세정 처리를 수행하지 않고, 상기 게이트 절연층과 상기 소스 및 드레인 전극 상에 액티브 패턴을 형성하여 산화물 반도체 소자를 제조하였다.

[0145] 다음 표 1은 비교예와 실험예 1 내지 실험예 3에 따른 산화물 반도체 소자들의 전하 이동도 및 문턱 전압 산포 정도를 측정한 결과들이다.

#### 丑 1

|   |        | 비교예                      | 실험예 1                    | 실험예 2                    | 실험예 3                    |

|---|--------|--------------------------|--------------------------|--------------------------|--------------------------|

| 7 | 전하 이동도 | 4.10 cm <sup>2</sup> /Vs | 8.20 cm <sup>2</sup> /Vs | 4.55 cm <sup>2</sup> /Vs | 8.43 cm <sup>2</sup> /Vs |

| 1 | 문턱 전압  | 0.98 V/decade            | 0.78 V/decade            | 0.83 V/decade            | 0.78 V/decade            |

| 1 | 산포도    |                          |                          |                          |                          |

- [0147] 상기 표 1에 나타낸 바와 같이, 실험예 1 내지 실험예 3에 따라 게이트 절연층에 대해 플라즈마 처리 및/또는 세정 처리를 수행한 경우에는, 플라즈마 처리나 세정 처리를 수행하지 않은 비교예에 비하여 전하 이동도의 값이 평균적으로 약 1.73배 정도 증가하는 반면, 문턱 전압 산포는 평균적으로 약 18.7% 정도 감소하였다. 특히, 실험예 3에 따라 플라즈마 처리와 세정 처리를 모두 수행한 경우, 산화물 반도체 소자의 전하 이동도의 증가와 문턱 전압 산포의 감소가 가장 현저하였다. 따라서, 게이트 절연층에 대해 플라즈마 처리 및/또는 세정 처리를 수행하여 리세스 구조를 형성한 다음, 게이트 절연층 상에 액티브 패턴을 형성할 경우에는 산화물 반도체 소자의 전기적인 특성들이 크게 향상됨을 확인할 수 있었다.

- [0148] 표시 장치 및 표시 장치의 제조 방법

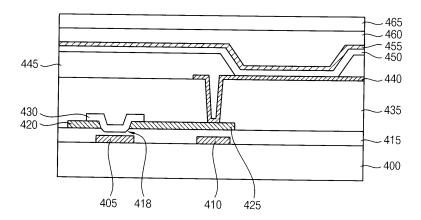

- [0149] 도 24는 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자를 포함하는 표시 장치의 단면도이다. 도 24에 있어서, 발광층(450)을 포함하는 표시 장치를 예시적으로 도시하지만, 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자는 액정 표시 장치, 플렉서블 디스플레이 장치 등에도 작용 가능함을 이해할 수 있을 것이다. 또한, 도 24에 도시한 표시 장치에 포함되는 산화물 반도체 소자는 도 1을 참조하여 설명한 산화물 반도체 소자와 실질적으로 동일하거나 유사한 구성을 가지지만, 도 15 또는 도 21을 참조하여 설명한 산화물 반도체 소자도도 24에 도시한 표시 장치에 적용 가능함을 이해할 수 있을 것이다.

- [0150] 도 24를 참조하면, 산화물 반도체 소자는 제1 기판(400) 상에 배치된다. 예시적인 실시예들에 있어서, 상기 산화물 반도체 소자는, 게이트 전극(405), 리세스 구조(418)를 갖는 게이트 절연층(415), 소스 전극(420), 드레인 전극(425) 그리고 액티브 패턴(430)을 포함한다.

- [0151] 제1 기판(400) 상에는 상기 산화물 반도체 소자의 게이트 전극(405)에 연결되는 게이트 라인(410)이 배치된다. 이 경우, 게이트 라인(410)은 게이트 전극(405)과 실질적으로 동일하거나 실질적으로 유사한 물질을 포함할 수 있다. 게이트 라인(410)은 제1 기판(400) 상에서 제1 방향을 따라 연장될 수 있다.

- [0152] 게이트 절연층(415)은 게이트 전극(405)과 게이트 라인(410)을 덮으며 제1 기판(400) 상에 배치된다. 게이트 절연층(415)은 실질적으로 평탄한 상면을 가질 수도 있지만, 도 21을 참조하여 설명한 게이트 절연층(290)과 같이 게이트 전극(405)과 게이트 라인(410)에서 인접하는 단차부들을 포함할 수 있다. 다른 예시적인 실시예들에 있어서, 게이트 전극(405) 및 게이트 라인(410)과 제1 기판(400) 사이에는 버퍼층(도시되지 않음)이 배치될 수 있다. 이러한 버퍼층으로 인하여 수분 또는 불순물의 확산이 방지될 수 있으며, 게이트 전극(405) 및 게이트 라인(410)이 제1 기판(400) 상에 상대적으로 용이하게 형성될 수 있다.

- [0153] 소스 전극(420)과 드레인 전극(425)은 게이트 전극(405)을 중심으로 게이트 절연층(415)의 일측과 타측 상에 위치한다. 즉, 소스 및 드레인 전극(420, 425)은 리세스 구조(418)를 중심으로 서로 대응되는 위치에 배치될 수있다. 소스 전극(420)에는 데이터 라인(도시되지 않음)이 접속될 수 있으며, 드레인 전극(425)은 게이트 절연층(415) 상에서 게이트 라인(410) 상부까지 연장될 수 있다. 이 때, 상기 데이터 라인은 게이트 라인(410)이 연장되는 상기 제1 방향에 대하여 실질적으로 직교하는 제2 방향을 따라 연장될 수 있다.

- [0154] 액티브 패턴(430)은 리세스 구조(418)를 매립하며 게이트 절연층(415), 소스 전극(420) 및 드레인 전극(425) 상에 배치된다. 예시적인 실시예들에 있어서, 액티브 패턴(430)의 하부는 기판(400)에 실질적으로 수직한 방향에 대하여 상대적으로 작은 제1 각도로 경사진 측벽을 가질 수 있다. 또한, 액티브 패턴(430)의 중앙부는 게이트 전극(405)에 실질적으로 수직한 방향에 대하여 상대적으로 큰 제2 각도로 기울어진 측벽을 구비할 수 있다.

- [0155] 상술한 구성을 가지는 산화물 반도체 소자를 커버하는 절연충(435)이 제1 기판(400) 상에 배치된다. 절연충 (435)은 그 상부에 배치되는 발광 구조물의 광 효율을 향상시키기 위하여 실질적으로 평탄한 상면을 가질 수 있다. 절연충(435)은 드레인 전극(425)이 연장되는 부분을 노출시키는 홀을 포함한다. 절연충(435)은 투명 절연물질을 포함할 수 있다. 예를 들면, 절연충(435)은 아크릴계 수지, 에폭시 수지, 페놀 수지, 폴리아미드계수지, 폴리이미드계 수지, 불포화 폴리에스테르계 수지, 폴리페닐렌계 수지, 폴리페닐렌설파이드계 수지, 벤조사이클로부텐(BCB) 등을 포함할 수 있다. 이들은 단독으로 또는 서로 조합되어 사용될 수 있다.

- [0156] 절연층(435) 상에는 상기 발광 구조물이 배치된다. 예시적인 실시예들에 있어서, 상기 발광 구조물은 제1 전극 (440), 발광층(450) 및 제2 전극(455)을 포함한다. 제1 전극(440)과 제2 전극(455)은 상기 표시 장치의 발광 형태에 따라 각기 투명 도전성 물질, 반투과형 도전성 물질, 반사형 도전성 물질 등을 포함할 수 있다. 즉, 제1 전극(440)과 제2 전극(455)을 구성하는 물질들의 종류에 따라, 상기 표시 장치가 전면 발광 구조, 배면 발광 구

조, 양면 발광 구조 등의 발광 형태를 가질 수 있다.

- [0157] 예시적인 실시예들에 따르면, 제1 전극(440)은 화소 전극에 해당될 수 있으며, 상기 산화물 반도체 소자에 전기적으로 연결될 수 있다. 즉, 제1 전극(440)은 절연층(435)의 홀을 통해 노출되는 드레인 전극(425)에 접촉될 수 있다. 여기서, 제1 전극(440)은 노출된 드레인 전극(425), 상기 홀의 측벽 및 절연층(435) 상에 위치할 수 있다. 다른 예시적인 실시예들에 있어서, 상기 홀 내에는 제1 전극(440)과 드레인 전극(425)을 서로 전기적으로 연결시키기 위한 콘택 구조물(contact structure), 패드 구조물(pad structure) 등이 배치될 수 있다. 이 때, 상기 콘택 구조물 또는 상기 패드 구조물은 단층 구조 또는 다층 구조를 가질 수 있다.

- [0158] 절연층(435) 상에는 아래에 위치하는 상기 산화물 반도체 소자를 커버하는 화소 정의층(445)이 배치된다. 즉, 화소 정의층(445)은 절연층(435) 가운데 아래에 상기 산화물 반도체 소자가 위치하는 부분 상에 배치될 수 있다. 여기서, 화소 정의층(445)은 제1 전극(440)과 드레인 전극(425)이 접촉되는 영역까지 연장될 수 있다. 화소 정의층(445)은 상기 표시 장치의 인접하는 화소들을 분리시키는 역할을 수행할 수 있으며, 투명 절연 물질을 포함할 수 있다. 예를 들면, 화소 정의층(445)은 폴리아크릴계 수지, 폴리이미드계 수지, 실리카 계열의 무기물 등을 포함할 수 있다.

- [0159] 화소 정의층(445)은 제1 전극(440)을 노출시키는 개구를 포함한다. 이 경우, 상기 발광 구조물의 발광층(450)과 제2 전극(455)은 화소 정의층(445)의 개구의 프로파일을 따라 노출된 제1 전극(440), 상기 개구의 측벽 및 화소 정의층(445) 상에 균일하게 형성될 수 있다.

- [0160] 예시적인 실시예들에 있어서, 제1 전극(440)을 부분적으로 노출시키는 화소 정의층(445)의 개구는 상기 표시 장치의 각 화소마다 배치될 수 있다. 이 때, 제1 전극(440)은 화소 정의층(445)의 개구 내에만 배치될 수도 있으며, 제1 전극(440)의 일부가 화소 정의층(445)과 실질적으로 중첩되도록 화소 정의층(445) 아래에 위치할 수도 있다. 화소 정의층(445)이 배치되는 영역은 실질적으로 상기 표시 장치의 비발광 영역에 해당될 수 있으며, 화소 정의층(445)의 개구가 위치하는 부분은 실질적으로 상기 표시 장치의 발광 영역에 해당될 수 있다.

- [0161] 다시 도 24를 참조하면, 발광층(450)은 저분자 유기물, 고분자 유기물 등을 포함할 수 있다. 예시적인 실시예들 에 있어서, 발광층(450)은 발광층, 정공 주입층(HIL), 정공 수송층(HTL), 전자 수송층(ETL), 전자 주입층(EIL) 등을 포함하는 다층 구조를 가질 수 있다. 도 24에 예시적으로 도시한 바에 있어서, 발광층(450)은 제1 전극 (440)과 화소 정의층(445) 상에 배치되지만, 발광층(450)의 위치가 이에 한정되는 것은 아니다. 예를 들면, 발광층(450)은 화소 정의층(445)의 개구 내에만 위치할 수도 있다.

- [0162] 상기 발광 구조물의 제2 전극(455) 상에는 보호층(460)이 배치된다. 보호층(460)은 하부 구조물들을 보호하는 동시에 상기 표시 장치의 밀봉 부재의 역할도 수행할 수 있다. 예를 들면, 보호층(460)은 유리, 투명 플라스틱, 투명 세라믹 등과 같은 투명절연 물질을 포함할 수 있다. 보호층(460) 상에는 제1 기판(400)에 대응하는 제2 기판(465)이 배치된다. 제2 기판(465)은 투명 절연 물질을 포함할 수 있다. 다른 예시적인 실시예들에 있어서, 보호층(460)의 구성 물질, 구조 등에 따라 보호층(460) 상에 제2 기판(465)이 제공되지 않을 수도 있다.

- [0163] 본 발명의 예시적인 실시예들에 따르면, 상기 표시 장치가 동작 전류의 증가, 문턱 전압 산포의 감소, 채널 영역에서의 전하 이동도의 증가 등의 향상된 전기적인 특성을 가지는 산화물 반도체 소자를 구비할 수 있으므로, 상기 표시 장치의 두께와 같은 치수를 감소시킬 수 있으며, 상기 표시 장치를 통해 나타나는 영상의 해상도를 증가시킬 수 있는 한편, 상기 표시 장치가 디스플레이하는 영상의 디스플레이 속도를 개선할 수 있다.

- [0164] 도 25 내지 도 28은 본 발명의 예시적인 실시예들에 따른 산화물 반도체 소자를 포함하는 표시 장치의 제조 방법을 설명하기 위한 단면도들이다. 표 25 내지 도 28에 있어서, 도 24를 참조하여 설명한 표시 장치와 실질적으로 동일하거나 실질적으로 유사한 구성을 가지는 표시 장치의 제조 방법에 대하여 설명하지만, 발광충, 화소 정의충, 제1 전국 등의 구성 요소의 적절한 변경이나 대체를 통하여 도 25 내지 도 28에 도시한 표시 장치의 제조 방법을 액정 표시 장치, 전기 영동 표시 장치 등과 다른 표시 장치들의 제조에도 적용할 수 있음을 이해할 수있을 것이다.

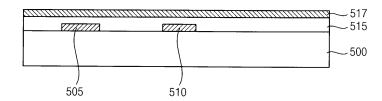

- [0165] 도 25를 참조하면, 제1 기판(500) 상에 게이트 전극(505)과 게이트 라인(510)을 형성한다. 예시적인 실시예들에 있어서, 제1 기판(500) 상에 도전층(도시되지 않음)을 형성한 후, 사진 식각 공정을 이용하여 상기 도전층을 부분적으로 식각함으로써, 제1 기판(500) 상에 게이트 전극(505)과 게이트 라인(510)을 형성할 수 있다.

- [0166] 제1 기판(500) 상에 게이트 전극(505)과 게이트 라인(510)을 덮는 게이트 절연층(515)을 형성한다. 게이트 절연 층(515)은 게이트 전극(505) 및 게이트 라인(510)을 충분히 커버하도록 제1 기판(500) 상에 상대적으로 두꺼운 두께로 형성될 수 있다. 다른 예시적인 실시예에 따르면, 게이트 절연층(515)은 게이트 전극(505) 및 게이트 라

인(510)의 프로파일들을 따라 상대적으로 얇은 두께로 제1 기판(500) 상에 상대적으로 얇은 두께로 형성될 수 있다.

- [0167] 게이트 절연층(515) 상에는 전극층(517)이 형성된다. 전극층(517)은 게이트 절연층(515) 상에 균일하게 형성될수 있다. 다른 예시적인 실시예들에 있어서, 전극층(517)은 도 17을 참조하여 설명한 전극층(225)과 실질적으로 동일하거나 실질적으로 유사하게 2이상의 전극막을 포함하는 구조를 가질 수도 있다.

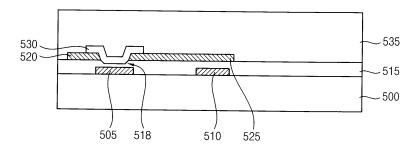

- [0168] 도 26을 참조하면, 전극층(517)을 패터닝하여 게이트 절연층(515) 상에 소스 전극(520)과 드레인 전극(525)을 형성한다. 소스 및 드레인 전극(520, 525)은 게이트 전극(505)을 중심으로 서로 이격되어 게이트 절연층(515) 상에 형성된다. 드레인 전극(525)은 아래에 게이트 라인(510)이 위치하는 부분의 게이트 절연층(515) 상으로 연장될 수 있다.

- [0169] 소스 및 드레인 전극(520, 525)을 형성하는 동안 발생되는 게이트 절연층(515)의 결함들과 게이트 절연층(515) 상에 존재하는 식각 부산물들을 제거하기 위하여, 게이트 절연층(515)에 대해 플라즈마 처리 및/또는 세정 처리를 수행한다. 따라서, 게이트 절연층(515)의 결함들과 상기 식각 부산물들이 제거되면서 게이트 절연층(515)에는 리세스 구조(518)가 형성된다.

- [0170] 리세스 구조(518)를 갖는 게이트 절연층(515), 소스 전극(520) 및 드레인 전극(525) 상에 액티브 패턴(530)을 형성한다. 액티브 패턴(530)은 반도체 산화물, 아몰퍼스 실리콘, 폴리 실리콘, 마이크로 결정들을 포함하는 실리콘 등을 사용하여 형성될 수 있다. 액티브 패턴(530)의 형성에 따라, 제1 기판(500) 상에는 게이트 전극(505), 게이트 절연층(515), 소스 전극(520), 드레인 전극(525) 및 액티브 패턴(530)을 포함하는 산화물 반도체소자가 제공된다.

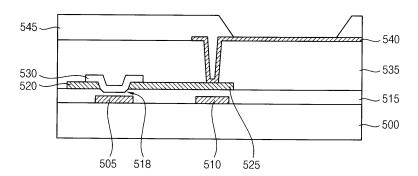

- [0171] 상기 산화물 반도체 소자를 덮는 절연층(535)을 제1 기판(500) 상에 형성한다. 절연층(535)은 투명 절연 물질을 사용하여 형성될 수 있다. 절연층(535)은 실질적으로 평탄한 표면을 가질 수 있다. 이 경우, 절연층(535)에 대하여 평탄화 공정을 수행하여 절연층(535)의 상면을 평탄화시킬 수 있다.

- [0172] 도 27을 참조하면, 절연층(535)을 부분적으로 식각하여 드레인 전극(525)의 일부를 노출시키는 홀을 형성한다. 예를 들면, 절연층(535)의 홀은 사진 식각 공정을 통해 수득될 수 있다.

- [0173] 노출된 드레인 전극(525), 상기 홀의 측벽 및 절연층(535) 상에 제1 전극층(도시되지 않음)을 형성한다. 상기 제1 전극층은 상기 홀의 프로파일을 따라 드레인 전극(525)과 절연층(535) 상에 균일한 두께로 형성될 수 있다. 상기 제1 전극층은 투명도전성 물질, 반투과형 도전성 물질, 반사형 도전성 물질 등을 사용하여 형성될 수 있다.

- [0174] 상기 제1 전극층을 패터닝하여 드레인 전극(525)에 접속되는 제1 전극(540)을 형성한다. 제1 전극(540)은 상기 표시 장치의 화소 전극에 해당될 수 있다. 제1 전극(540)은 노출된 드레인 전극(525), 상기 홀의 측벽 및 절연 층(535) 상에 형성될 수 있다. 이 경우, 제1 전극(540)은 아래에 상기 산화물 반도체 소자가 위치하는 부분의 절연층(535) 상에는 형성되지 않을 수 있다. 다른 예시적인 실시예들에 따르면, 상기 홀의 측벽과 노출된 드레인 전극(525) 상에 콘택 구조물 또는 패드 구조물 등을 형성한 후, 절연층(535) 상에 상기 콘택 구조물 또는 상기 패드 구조물에 접속되는 제1 전극(540)을 형성할 수 있다.

- [0175] 절연층(535)과 제1 전극(540) 상에 화소 정의층(545)을 형성한다. 화소 정의층(545)은 투명 절연 물질을 사용하여 형성될 수 있다. 예를 들면, 화소 정의층(545)은 폴리아크릴계 수지, 폴리이미드계 수지 등의 유기물, 실리카 계열의무기물 등을 사용하여 형성될 수 있다.

- [0176] 화소 정의층(545)을 부분적으로 식각하여 제1 전극(540)을 노출시키는 개구를 형성한다. 예를 들면, 상기 개구는 사진 식각 공정을 이용하여 형성될 수 있다. 화소 정의층(545)의 개구는 제1 기판(500)에 대하여 소정의 각도로 경사진 측벽을 가질 수 있다. 이러한 개구의 측벽 경사에 따라 후속하여 발광층(550) 및/또는 제2 전극(555)(도 28 참조)을 용이하게 형성할 수 있다.

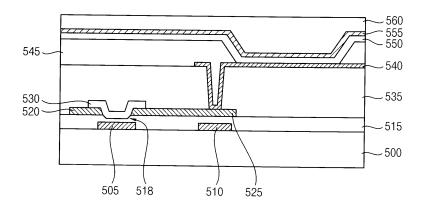

- [0177] 도 28을 참조하면, 제1 전극(540), 상기 개구의 측벽 및 화소 정의층(545) 상에 발광층(550)을 형성한다. 발광 층(550)은 상기 개구의 프로파일을 따라 노출된 제1 전극(540), 상기 개구의 측벽 및 화소 정의층(545) 상에 균일하게 형성될 수 있다. 발광층(550)은 저분자 유기물, 고분자 유기물 등을 사용하여 형성될 수 있다. 또한, 발광층(550)은 발광층, 정공 주입층, 정공 수송층, 전자 수송층, 전자 주입층 등을 포함하는 다층 구조로 형성될 수 있다.

- [0178] 발광층(550) 상에는 제2 전극(555)이 형성된다. 제2 전극(555)은 투명 도전성 물질, 반투과형 도전성 물질, 반

사형 도전성 물질 등을 사용하여 형성될 수 있다. 제2 전극(555)은 발광층(550) 상에 균일하게 형성될 수 있다. 다른 예시적인 실시예들에 있어서, 발광층(550)이 제1 전극(540) 상에만 형성되는 경우, 제2 전극(555)도 화소 정의층(545)의 개구 내에만 형성될 수 있다. 예를 들면, 발광층(550)은 제1 전극(540)과 상기 개구의 측벽 상에만 형성될 수 있으며, 제2 전극(555)은 이러한 발광층(550) 상에 형성될 수 있다. 이 경우, 발광층(550)과 화소 정의층(545) 상에 제2 전극층(도시되지 않음)을 형성한 다음, 상기 제2 전극층을 패터닝하여 제2 전극(555)을 수득할 수 있다.

[0179] 제2 전극(550) 상에 보호층(560)을 형성한다. 보호층(560)은 유리, 투명 플라스틱, 투명 세라믹 등과 같은 투명 절연 물질을 사용하여 형성될 수 있다. 다른 예시적인 실시예들에 있어서, 보호층(560) 상에는 제1 기판(500)에 실질적으로 대응하는 제2 기판(도시되지 않음)이 형성될 수 있다. 이 때, 상기 제2 기판은 투명 절연 물질로 이루어질 수 있다.

## 산업상 이용가능성

[0180] 본 발명의 예시적인 실시예들에 따르면, 리세스 구조를 갖는 게이트 절연층을 구비하여 다양한 전기적인 특성들이 향상된 산화물 반도체 소자를 유기 발광 표시 장치, 액정 표시 장치, 투명 플렉서블 디스플레이 장치 등의 표시 장치에 적용할 경우, 상기 표시 장치가 나타내는 영상의 품질과 화면의 구동 속도를 향상시킬 수 있으며, 상기 표시 장치의 두께를 감소시킬 수 있다.

## 부호의 설명

[0181] 5, 50, 100, 150, 200, 280, 330: 기판

10, 55, 105, 155, 205, 285, 335, 405, 505: 게이트 전극

15, 60, 110, 160, 210, 290, 340, 415, 515: 게이트 절연층

18, 68, 118, 168, 218, 298, 358, 418, 518: 리세스 구조

20, 80, 125, 175, 245, 300, 360, 420, 520: 소스 전극

25, 85, 130, 190, 260, 305, 365, 425, 525: 드레인 전극

30, 90, 195, 310, 430, 530: 액티브 패턴

65, 115, 225, 345, 517: 전극층 70: 마스크층

75, 120, 230, 350: 마스크 패턴 88, 128, 248: 식각 부산물

165, 235: 제1 전극 패턴 170, 240: 제2 전극 패턴

180, 250: 제3 전극 패턴 185, 255: 제4 전극 패턴

215: 제1 전극막 220: 제2 전극막

265: 액티브층 400, 500: 제1 기판

410, 510: 게이트 라인 435, 535: 절연층

440. 540: 제1 전극 445, 545: 화소 정의층

450, 550: 발광층 455, 555: 제2 전극

460, 560: 보호층 465: 제2 기판

# 도면1

# 도면4

# 도면7

# 도면10

## 도면17

# 도면20

# 도면21

# 도면24

# *도면25*