# Walters

[56]

[54] IMPLANTABLE DIGITAL CARDIAC PACER HAVING EXTERNALLY SELECTIBLE **OPERATING PARAMETERS AND "ONE** SHOT" DIGITAL PULSE GENERATOR FOR **USE THEREIN**

[75] Inventor: Robert A. Walters, Pittsburgh, Pa.

ARCO Medical Products Company, [73] Assignee:

Leechburg, Pa.

[21] Appl. No.: 663,372

[22] Filed: Mar. 3, 1976

# Related U.S. Application Data

Continuation-in-part of Ser. No. 654,584, Feb. 2, 1976, [63] which is a continuation-in-part of Ser. No. 625,295, Oct. 23, 1975, abandoned.

| [51] | Int. Cl. <sup>2</sup>          | : A61N 1/36 |

|------|--------------------------------|-------------|

|      | U.S. Cl 128/419                |             |

|      | Field of Search 128/419 E, 419 |             |

| r1   | 128/419 PT, 419 R, 421, 422, 4 |             |

273; 328/193

# References Cited U.S. PATENT DOCUMENTS

| 3,557,796 | 1/1971 | Keller, Jr. et al | 128/419 PG |

|-----------|--------|-------------------|------------|

| 3,727,616 | 4/1973 | Lenzkes           |            |

| 3,805,796 | 4/1974 | Terry, Jr. et al  | 128/419 PG |

| 3,833,005 | 9/1974 | Wingrove          | 128/419 PG |

Primary Examiner-William E. Kamm

Attorney, Agent, or Firm-Richard A. Bachand

#### ABSTRACT [57]

An implantable cardiac pacer is instructable to vary the stimulation pulse interval, the stimulation pulse width, the stimulation pulse amplitude, the pacer sensitivity, the refractory period and the mode (demand or asynchronous).

-[11]

A master parameter control circuit is provided to vary selected parameters of the heart pacer in accordance with an externally applied control signal.

An external control unit produces two sequential series of pulses, the first series being an access comprising at least one digital "0" state which must be detected by an access code detecting circuit within the master parameter control before the following parameter code will be accepted to vary the pacer parameters. The parameter code, generated subsequently to the access code, determines the selected set of pacer parameters, and can be selected from external controls upon the external control unit.

The master parameter control circuit includes means for recognizing the access code to enable the master parameter control circuit to only thereafter accept the selected parameter code. The entire parameter code must then be entirely received prior to changing the pacer parameters.

24 Claims, 12 Drawing Figures

FIG. 3B

F/G. 3C

IMPLANTABLE DIGITAL CARDIAC PACER HAVING EXTERNALLY SELECTIBLE OPERATING PARAMETERS AND "ONE SHOT" DIGITAL PULSE GENERATOR FOR USE THEREIN

# CROSS REFERENCE TO RELATED APPLICATIONS

This application is a contnuation-in-part of application Ser. No. 654,504, filed Feb. 2, 1976, which is a continuation-in-part of application Ser. No. 625,295, filed Oct. 23, 1975, now abandoned.

## BACKGROUND OF THE INVENTION

### 1. Field of the Invention

This invention relates to heart pacers, and more particularly to heart pacers of the type of which the operating parameters can be remotely varied and controlled. 20

## 2. Description of the Prior Art

Heart pacers are often provided with various means to control selected operating parameters so that, for example, the pacer can be adjusted to respond to and provide signals to a patient in accordance with his indi- 25 vidual needs. After the pacer has been implanted, however, effecting changes in any particular operating parameter of the pacer may become a severe problem. Such changes are often necessitated, for instance, by an improvement or deterioration in the patient's condition 30 which may require certain adjustments, for instance, that rate at which stimulation pulses are provided to the patient, the pulse width and amplitude of the pulses provided, the refractory period exhibited by the pacer, the operating mode of the pacer, such as demand mode, fixed rate mode, and the like.

In the past, there have been various proposals to effect changes in selected heart pacer parameters of an implanted heart pacer without major surgical interven- 40 tion. For example, it has been proposed to provide a magnetic field responsive switch which can be activated by a magnet external to the patient, typically to change the pacer from a demand mode to a fixed rate mode. Additionally, pacers have been proposed which 45 provide receptacles for receiving engaging surgical needles which can be inserted into the patient for adjustment of, for example, the value of a resistor or the like.

Implantable cardiac pacers have been advanced in the prior art which have certain operating parameters 50 which can be adjusted without physically invading the user's body. Some prior art pacers typically include first and second digital pulse counters. The first counter receives a first predetermined set of input pulses, after which it produces an enabling signal to direct subse- 55 quent input pulses to the second counter. The second counter includes a plurality of outputs to activate various switches, each in parallel, for example, with a respective resistor in a plurality of series connected resistors to thereby control the input current to a transistor 60 of a multivibrator to modify its time constant. Another output of the second counter controls a switch which bypasses a portion of the driving current to the output amplifier of the pacer to thereby control its output current.

Such prior art circuit, as above described, typically responds to an access code, which may be merely a sequential series of, for instance, seven or more consec-

utive pulses. One requirement of such circuit, however, is that seven access code pulses appear in a series to enable the first counter to count them. Thus, for example, if the wearer of a cardiac pacer embodying such circuit were to become exposed to a field to which the circuit responds, the circuit may erroneously detect the field pulses as the access code, and more importantly, thereafter reset the various parameters controlled by the circuit.

Additionally, prior art parameter adjustment circuits typically provide means for modifying the pulse rate only (and incidentally the width) and output current produced by the pacer, with no consideration given to many of the other important pacer parameters above 15 mentioned.

One other disadvantage of prior art parameter adjustment circuts is that once the access pulses have been counted and the second counter is enabled, the data pulses applied to it produce immediate changes in the various output lines. These changes may undesirably produce immediate changes in the selection of the various timing resistors during the time while the data is still being received.

# SUMMARY OF THE INVENTION

In light of the above, it is, therefore, an object of the invention to provide a digital cardiac pacer including means external to or remote from the pacer for controllably varying selected operating parameters of the pacer.

It is still another object of the invention to provide a digital cardiac pacer which can be, after implantation, externally to the user, controlled to vary any selected one or ones of the following operating parameters; the the sensitivity to naturally produced heart signals, and 35 stimulation pulse width, the stimulation pulse amplitude, the demand or fixed rate modes stimulation pulse rate, the refractory period, the heart signal sensitivity, and the mode.

> It is another object of the invention to provide a digital cardiac pacer which includes a memory for retaining pacer operating parameter determining signals which can be completely loaded into the memory prior to their execution.

> It is still another object of the invention to provide a digital cardiac pacer and means for controllably varying the operating parameters thereof including a unique access code recognition circuit to assure that the operating parameter determining signals are not inadvertently

> It is another object of the invention to provide a circuit for use in a digital cardiac pacer for controlling the sensitivity to heart frequency signals.

> It is another object of the invention to provide a digital cardiac pacer in which the operating parameters can be independently varied.

> It is another object of the invention to provide a one shot digital pulse generator for use in a heart pacer of the type which receives externally transmitted pules to produce a pulse of controlled amplitude and width upon the reception of an externally transmitted pulse.

> These and other objects, features, and advantages will become apparent to those skilled in the art from the following detailed description when read in conjunction with the accompanying drawings and appended claims.

> The invention, in a broad aspect thereof, presents an implantable digital cardiac pacer having externally selectible operating parameters. The pacer includes an

65

external instruction device adapted to transmit a train of parameter selection pulses. The pacer includes means for receiving the train of pulses and generating a digital signal in response to the train. Memory means are included within the pacer for storing the digital signal, and means interconnect the pulse receiving means and the memory means to control the loading of the digital signal into the memory means. Means are also provided for varying at least one of the operating parameters of the pacer, and means connect the memory means and 10 the parameter varying means to enable to the parameter varying means to control the at least one operating parameter in response to the digital signal generated. In another aspect of the invention, an implantable heart pacer includes externally controllable means for vary- 15 ing selected operating parameters, including the sensitivity, the refractory period, the stimulation pulse amplitude, the stimulation pulse width, the stimulation pulse rate, and the operating mode, i.e., fixed rate or demand.

Also included is a digital "one shot" pulse generator incorporating first and second triggerable flip-flops interconnected by a digital counter which controls the width of the pulse generated by the digital one shot generator.

In one embodiment of the invention, means are provided for detecting an externally access code, which includes a digital signal including at least one zero logic state to enable a subsequently transmitted series of data pulses to be received for controlling the operating parameters of the pacer.

## BRIEF DESCRIPTION OF THE DRAWING

The invention as illustrated in the accompanying 35 drawing, wherein;

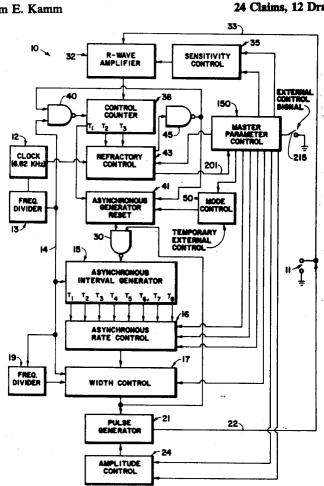

FIG. 1 is a box diagram of a heart pacer, in accordance with the invention, having various controllable parameters.

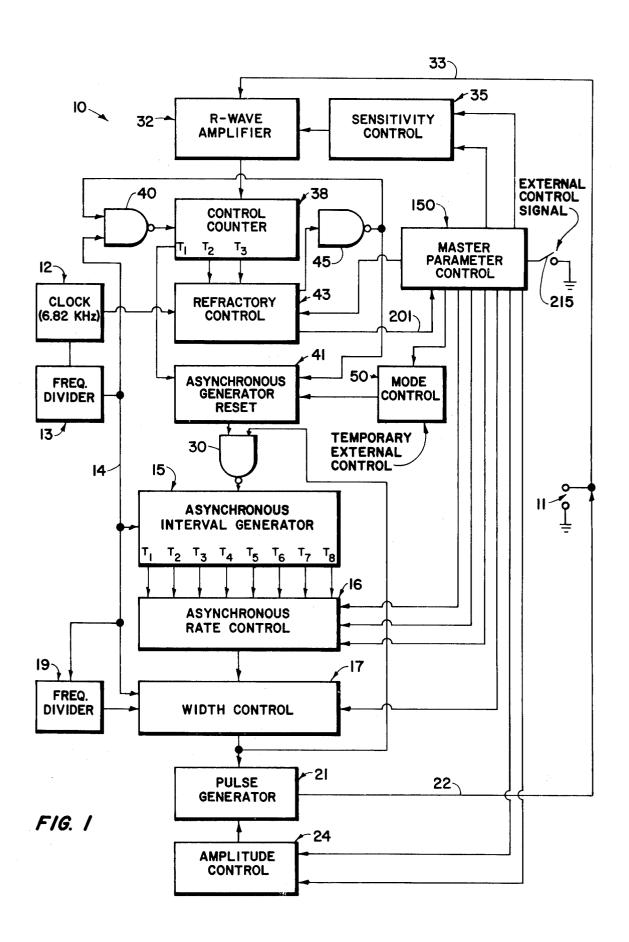

FIG. 2 is a box diagram illustrating the circuitry of the master parameter control circuit, including the access code recognition circuitry, the instruction memory, and the circuitry for loading the instruction code into the memory, in accordance with one aspect of the invention.

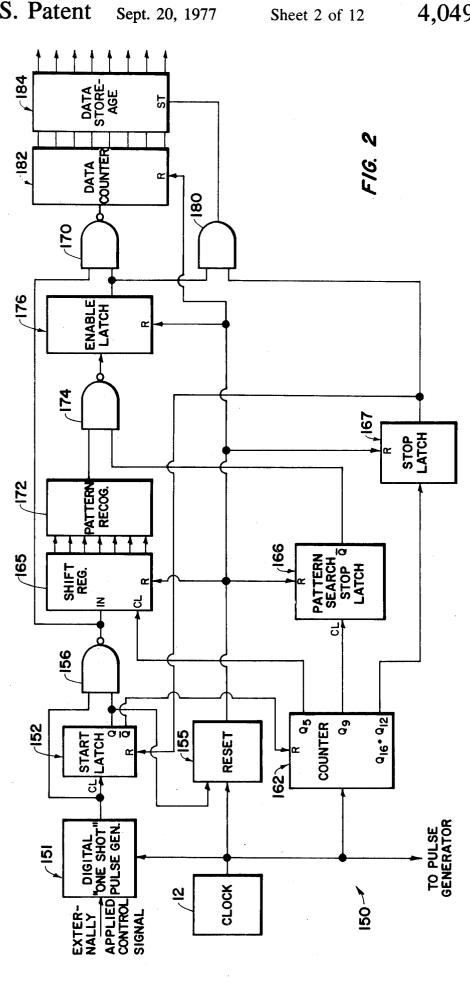

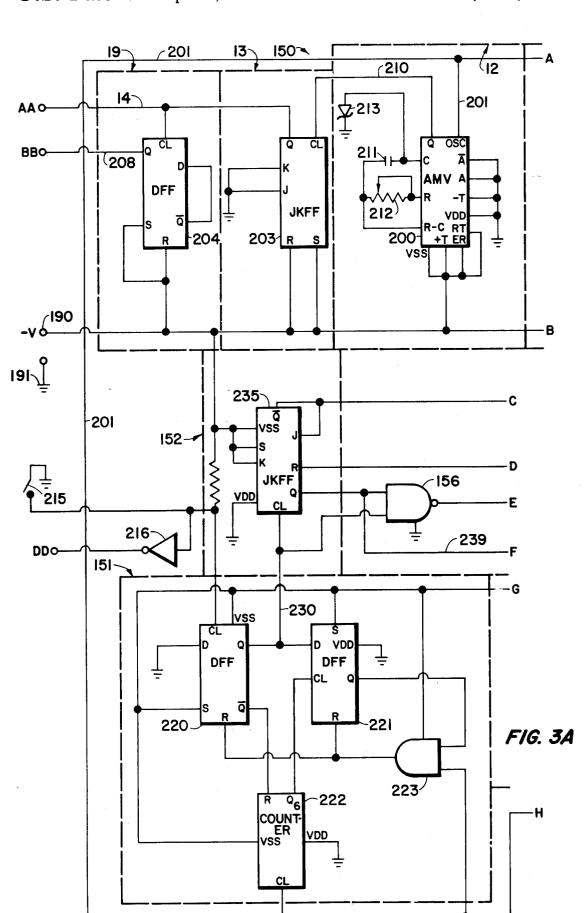

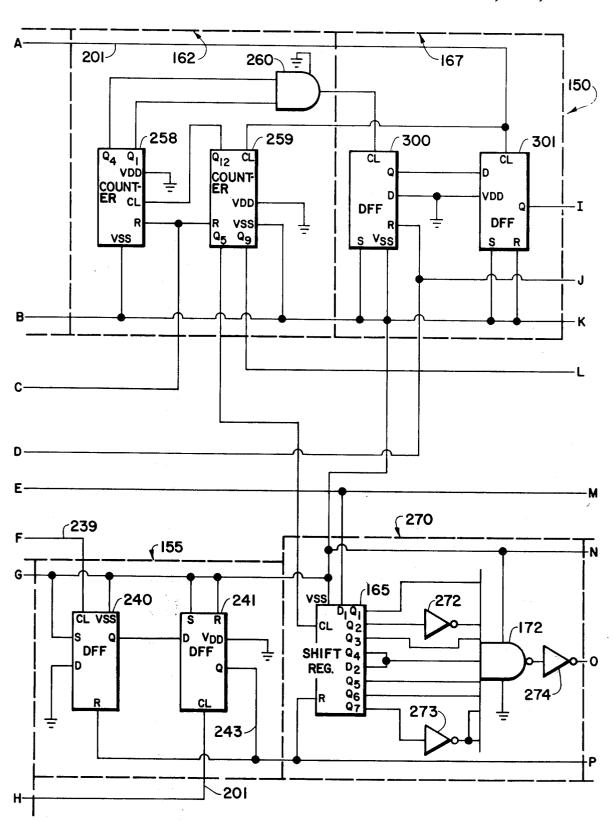

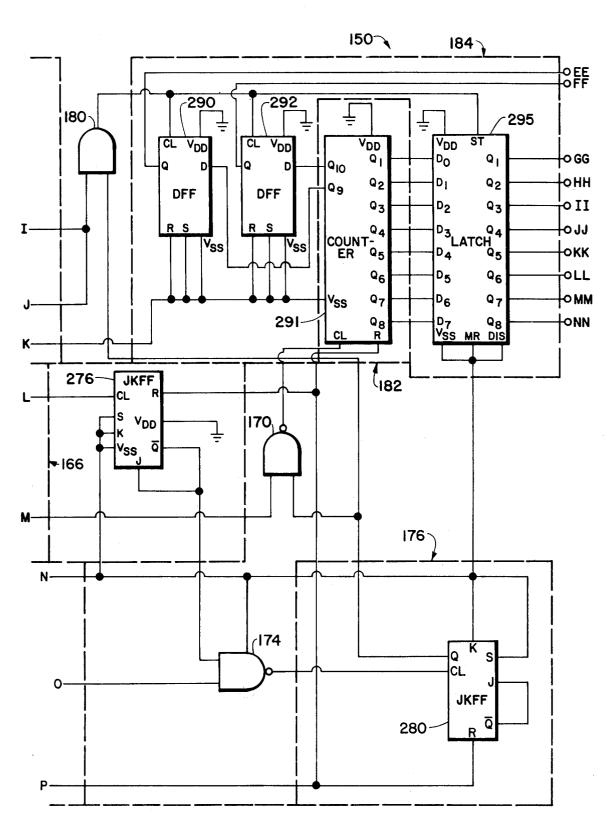

FIGS. 3A, 3B and 3C are a detailed electrical schematic diagram of the master parameter control circuit of FIG. 2.

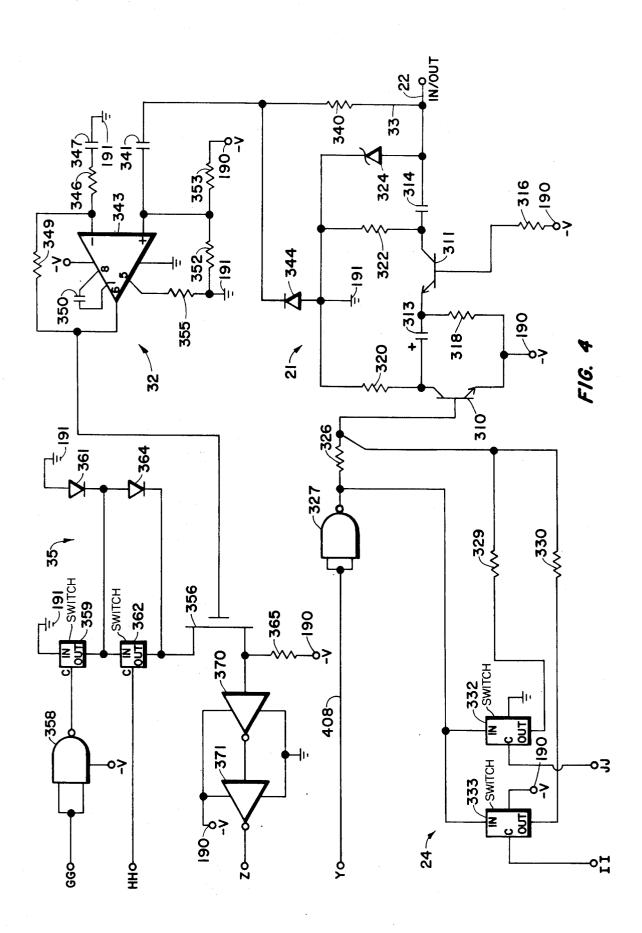

FIG. 4 is a detailed electrical schematic diagram of the pulse generator and amplitude control circuits and 50 of the R-wave amplifier and sensitivity control circuits of the cardiac pacer of FIG. 1.

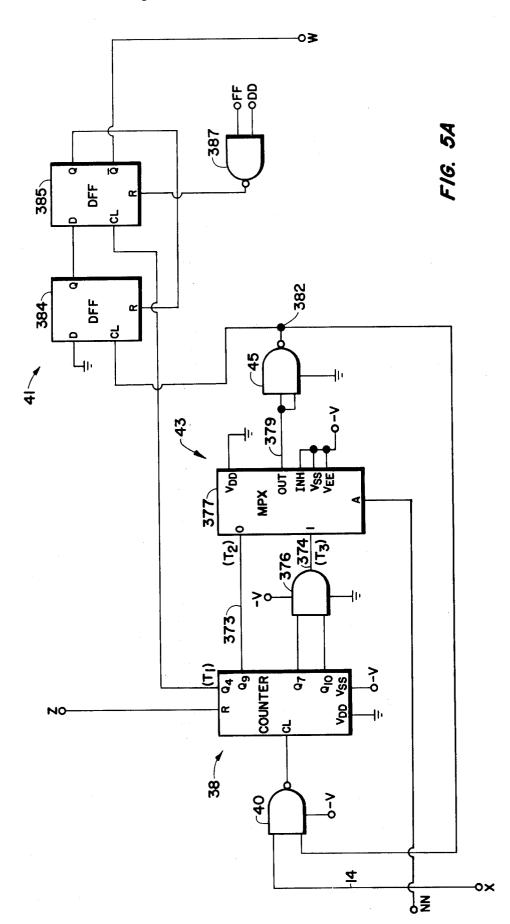

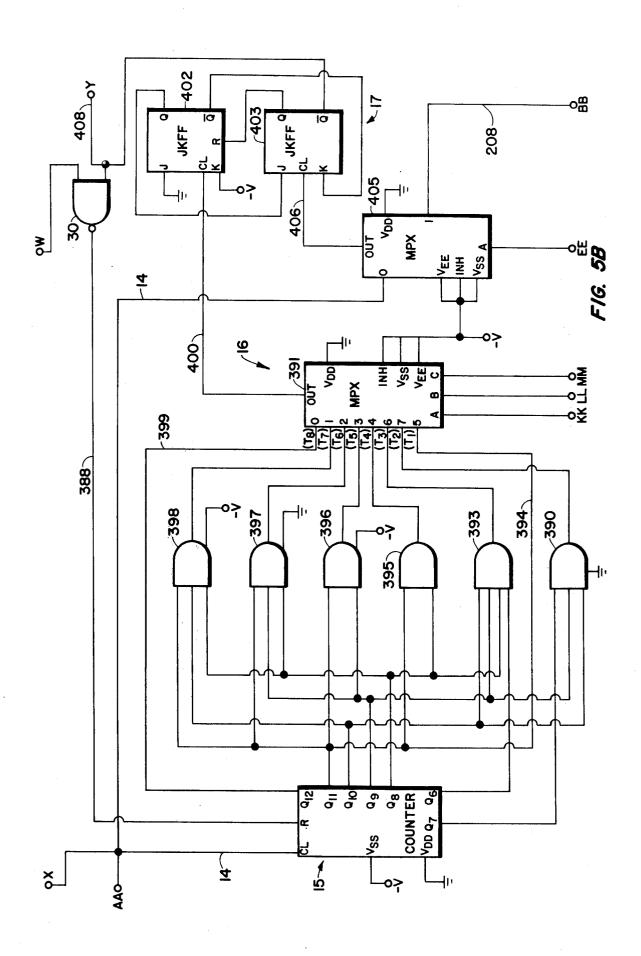

FIGS. 5A and 5B are a detailed electrical schematic diagram of the control counter circuit, refractory control circuits, asynchronous generator resetting circuit, 55 mode control circuit, asynchronous interval generator circuit, asynchronous rate control circuit, and width control circuit of the cardiac pacer of FIG. 1.

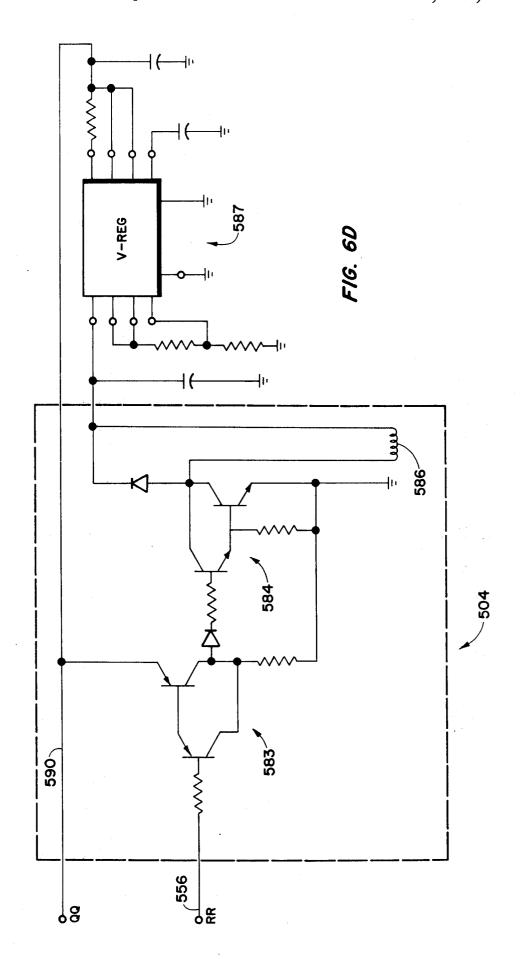

And FIGS. 6A, 6B, 6C, and 6D are a detailed electrical schematic diagram of an external control unit for use 60 in transmitting the access and parameter codes to the master parameter control circuit of FIGS. 3A, 3B, and 3C.

In the various figures of the drawing, like reference numerals are used to denote like parts. Additionally, 65 interconnections between the various circuits of the drawing are denoted by corresponding letters (A, B, C, etc.).

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

The cardiac pacer 10, in accordance with a preferred embodiment of the invention is shown in box diagram form in FIG. 1. (The various electrical circuits of the cardiac pacer in FIG. 1 ar illustrated and described below in detail with particular reference to FIGS. 2-5B).

With general reference to FIG. 1, the cardiac pacer 10 receives naturally produced cardiac and other signals from and supplies stimulation signals to a terminal 11, adapted to be connected to heart electrodes, such connections being well known in the art.

15 The cardiac pacer 10 operates in conjunction with a digital clock 12, which supplies clock pulses at a frequency of, for example, 6.82 KHz. Pulses from the clock 12 are divided by a frequency divider 13 to be supplied on line 14 to an asynchronous interval generator 15, having a plurality of outputs T1-T8, conducted to an asynchronous rate control circuit 16. Each of the outputs T1-T8 represents a different asynchronous interval within the range of interest, and the synchronous rate control 16 selects one of the outputs T1-T8 from the asynchronous interval generator 15, as controlled by a master parameter control 150.

The selected output from the asynchronous interval generator 15 is conducted to a width control circuit 17, which produces an output pulse of selected width as controlled by the master parameter control 150. This capability is enabled by the clock pulses upon the line 14 being applied directly to the width control 17, and to a frequency divider 19, which produces additional clock pulses at a submultiple of the frequency of the clock 12, for application to the width control circuit 17, thereby providing signals from which the various widths of the output pulse can be selected.

The output pulses from the width control circuit 17 are applied to trigger a pulse 21 to produce an output pulse upon output line 22 for delivery to the heart terminals 11. The amplitude of the pulse generated by the pulse generator 21 is controlled by an amplitude control circuit 24, which, in turn, is also controlled by the master parameter control circuit 150.

The output of the width control circuit 17, in addition to its connection to the pulse generator 21, is conducted via a NAND gate 30 to a resetting terminal of the asynchronous interval generator 15. Thus, upon the reaching of a predetermined selected count of the asynchronous generator 15, upon the production of an output pulse from the width control circuit 17, the asynchronous interval generator is reset to begin counting a subsequent asynchronous interval.

The portion of the cardiac pacer thus described serves as a so-called fixed rate pacer, producing pulses asynchronously at a rate controlled by the selected output of the asynchronous interval generator 15. To provide a demand pacer capability, an R-wave amplifier 32 is provided. The heart terminals 11 are connected via line 33 to an input of the R-wave amplifier 32 to conduct naturally occurring heart pulses to the R-wave amplifier 32. Other signals, such as stimulation pulses produced by the pulse generator 21 upon the line 22, and electromagnetic interferring noise as may be detected by the heart electrodes or other associated circuitry may also be detected upon the line 33, but are filtered or rejected or initiate a interference or fixed rate mode, as will become apparent below. The sensitivity of

4,042

the R-wave amplifier 32 is controlled by a sensitivity control circuit 35, which, in turn, is controlled by the master parameter control 150.

The R-wave amplifier 32 produces an output signal upon the detection of a naturally produced R-wave, a 5 stimulation pulse, or an interference signal, for delivery to a control counter 38. The control counter 38 also receives clock pulses from the clock 12 via a NAND gate 40, and produces outputs at times  $T_1$ ,  $T_2$  and  $T_3$ , respectively after being reset. The output generated at 10 time T<sub>1</sub> is conducted to an asynchronous generator reset circuit 41 which produces an output delivered via NAND gate 30 to reset the count of the asynchronous interval generator 15. Thus, in operation, if an R-wave, a stimulation pulse, or an interference signal is received 15 by the R-wave amplifier 32 prior to the time which a signal appears on a selected output of the asynchronous interval generator 15, the asynchronous interval generator 15 is reset to begin its count anew, in a fashion known in the art as demand operation.

In addition, one or the other of the outputs  $T_2$  or  $T_3$  of the control counter is selected by a refractory control circuit 43, as controlled by the master parameter circuit 150. The selected output is conducted to an inverting NAND gate 45, for application to the NAND gate 40 25 controlling the passage of the clock pulses upon the line 14, and to the asynchronous generator reset circuit 41 to produce a state therein allowing the passage of a subsequently produced asynchronous generator reset pulse from the control counter 38. Thus, the refractory cir- 30 cuit functions to produce an "alert state" within the asynchronous generator reset circuit 41 after the control counter 38 has reached a predetermined refractory count determined by the refractory control circuit 43. Upon producing the alert state, a logic state is applied to 35 the input of the NAND gate 40 disabling the passage of the clock pulses upon the line 14, terminating the counting by the control counter 38. Thereafter, the production of an output by the R-wave amplifier 32 produces a pulse resetting the control counter 38 and enabling it 40 to begin its count again. When the count has reached time T1, the asynchronous generator reset 41, previously enabled by the refractory control circuit 43, produces a reset pulses to reset the count of the asynchronous interval generator 15. Prior to the reaching of the 45 "alert state," however, the pacer is in a "control state" during which the reception of a signal from the R-wave amplifier 32 does not produce an asynchronous interval generator resetting pulse, but instead the control counter 38 is merely reset to count the preselected re- 50 fractory period from the beginning.

In addition, a mode control circuit 50 is provided which is controlled by the master parameter control 150. The mode control circuit 50, which operated, disables the operation of the asynchronous generator reset 55 circuit 41, to thereby cause the pacer circuit 10 to operate in a fixed rate mode. Additionally, the mode control 50 can be operated by a temporary external control, such as an electromagnet or the like, to cause the circuit to operate in a fixed rate mode for testing purposes, as is 60 well known in the art.

The master parameter control 150, below described in detail, is programmed via an external control signal applied to a receiving element 215, such as a magnetically activated reed switch or the like, as below described.

As indicated, the cardiac pacer 10, in accordance with the present invention, includes a facility for vary-

ing its operating parameters; more particularly, the stimulation pulse width, the stimulation pulse amplitude, the refractory period, the heart signal sensitivity, and the mode (i.e. fixed rate or demand) and the asynchronous pulse generation rate. These operating parameters, furthermore, can be varied after the pacer has been emplanted into the body of the patient. To facilitate this parameter controlability, the master parameter control circuit 150 is employed. The master parameter control circuit 150 is shown in box diagram form in FIG. 2, and in detail in FIGS. 3A-3C.

As will become apparent, the master parameter control circuit 150 is responsive to an externally applied input from an instruction device as below described. The instruction device provides an initial access sequence of electromagnetic pulses followed by a sequence of electromagnetic pulses for determining the operating parameters of the pacer. The control circuit 150 must first recognize the access sequence before the 20 control sequence will be accepted and loaded into the control circuit memory. More particularly, with reference now to FIG. 2, the externally applied input signal is received and applied to a digital one shot pulse generator 151, which provides an output pulse of controlled amplitude and width for each externally applied input pulse to overcome problems associated with bounce of the signal input detection switch (described below). The output from the digital one shot generator 151 is applied to a start latch circuit 152 and a NAND gate 156. The output of the NAND gate 156 is conducted to the input of a shift register 165, the various outputs of which are connected to a pattern recognition circuit 172.

Concurrently, clock pulses from the clock 12 are applied to the digital one shot generator 151, a reset circuit 155 and a counter 162. Three outputs of the counter 162 which occur at various different times are conducted to the shift register 165, a pattern search stop latch 166, and a stop circuit 167. Additionally, the output from the NAND gate 156 is conducted into an input of the shift register 165, as well as to a second NAND gate 170.

An output from the pattern recognition circuit 172, as well as an output from the pattern search stop latch 166 are inputted to a NAND gate 174. The output of the NAND gate 174 is conducted to the input of an enable latch 176, and the output of the enable latch 176 is conducted to another input of the NAND gate 170 and to an AND gate 180. The output of the stop latch 167 is conducted to another input of the AND gate 180 and to a reset terminal of the start latch 152. The output of the NAND gate 170 is conducted to the input of a data counter 182, and the outputs of the data counter 182 are conducted to a data storage memory circuit 184. The output of the AND gate 180 is connected to a "store" terminal of the data storage memory circuit 184.

Briefly, in operation, upon the application of the externally applied input to the digital one shot pulse generator 151, the start latch 152 is activated. The start latch 152 activates the reset circuit 155 which initializes the shift register 165, the pattern search stop latch 166, the enable latch 176, the stop latch 167, and the data counter 182. Additionally, the activation of the start latch 152 permits the counter 162 to begin its count. The counter 162, as will be below described in detail, produces outputs which are submultiples of the clock frequency.

The data from the digital one shot pulse generator is then applied via NAND gate 156 (enabled to pass the

data because of the output of the start latch 152) to the pattern recognition shift register 165. The first seven data bits are clocked into the shift register 165 at a submultiple frequency of the clock 160 (1/32 thereof in the embodiment illustrated). The data in the shift regis- 5 ter 165 is continuously applied to the combinational logic pattern recognition circuit 172, which produces an output if and only if the pre-selected recognition code appears in the shift register 165. Concurrently, the pattern search stop latch 166 is activated by another output 10 from the counter 162 at another submultiple of the frequency of the clock 160 (for example, 1/256 of the clock frequency, the time required to clock the first seven data bits into the shift register 165). The output from the pattern search stop latch 166, when applied 15 together with the output from the pattern recognition circuitry 172 to the NAND gate 174 activates the enable latch 176. The data appearing at the output of the NAND gate 156, therefore, is applied by the NAND gate 170 to the data counter 182, thence to the data 20 storage circuit 184.

At a time at which the data is completely loaded into the data storage 184, the stop latch 167 is activated to produce a signal which is applied to a store terminal of the data storage circuit 184 via AND gate 180. Concurrently, the output from the stop latch 167 is applied to the start latch 152 to reset it to an initial condition to preclude further transmission of data into the circuit 150.

At this point, the data from the external instruction 30 device is stored in the data storage circuit 184 for changing the operating parameters of the pacer circuit.

The control pulse receiving circuit of FIG. 2 is shown in greater detail in FIGS. 3A-3C. More particularly, the clock 12 (FIG. 3A) includes an astable multivibrator 35 200 which provides an oscillator output upon line 201 to supply clock pulses to the remainder of the circuit. A frequency divider circuit 13 is also provided, including a J-K master-slave flip-flop 203 to which a divided frequency output from the astable multivibrator 200 is 40 applied to the clock input thereof; and a D-type flip-flop 204 to which the Q output of the J-K flip-flop 203 is applied to a clock input thereof. The  $\overline{Q}$  output of the flip-flop 204 is connected to the D input, whereby the output alternates between high and low states with 45 successive clock pulses to divide the clock frequency by two. The output of the D flip-flop 204 is conducted from the circuit on line 208 (the connection continuing from point BB to the width control circuit 17, FIG. 5B). Since the Q output of the astable multivibrator 200 is at 50 one-half of the oscillation frequency generated, the output from the D flip-flop 204 will be the clock frequency divided by four. The set and reset terminals of the D flip-flop 204 and the J-K flip-flop 203 are connected to a low state 190 to assure the continuous opera- 55 tion of the respective flip-flops.

The  $V_{so}$  the positive trigger, the external reset, and the retrigger terminals of the clock 200 are tied low; and the astable, negative trigger and the  $V_{dd}$  are tied high. The integrated circuit 200, therefore, operates as an 60 astable multivibrator with the output thereof appearing on line 201, and a one-half submultiple frequency appearing on line 210, applied to the flip-flop 203, as above indicated. Thus, the output on line 201 is the primary clock frequency; the output on line 14 (point AA) is the 65 first divided of the primary clock frequency established by the divider circuit 13; and the output on line 208 (point BB) is the second divided clock frequency, estab-

8

lished by the divider circuit 19. The frequency of the clock 12 is determined by the values of the capacitor 211 and resistor 212 connected between the capacitor and resistor terminals, respectively, and the R-C common terminal of the astable multivibrator 200. The frequency can be adjusted by varying the value of the resistance of the resistor 212. In the embodiment illustrated, the resistor is about  $2M\Omega$ , and the capacitor is about 100 pf; consequently, the clock frequency can be adjusted to be about 6.82KHz. A zener diode 213 is connected between the capacitor terminal of the multivibrator 200 and ground, to cause the oscillator frequency to decrease with decreasing battery voltage.

The data from the external instruction device (below described) is received by a magnetically actuated reed switch 215 and is conducted to the digital one shot generator 151 (FIG. 3A). The pulse generator 151 assures that the pulse received from the reed switch 215 is of proper shape and width for handling by the remainder of the circuitry, and includes two D-type flip-flops 220 and 221, a ripple-carry binary counter 222, and an AND gate 223. The data is applied to the clock input of the D flip-flop 220, the D input of which is tied high. The output Q of the flip-flop 220 is connected to the D input of the D flip-flop 221, and the Q output of the D flip-flop 221 is conducted through the AND gate 223 to the reset terminals of the flip-flops 220 and 221. The primary clock pulses appearing on line 201 are additionally applied to the AND gate 223 to synchronize the resetting of the D flip-flops 220 and 221. The  $\overline{Q}$  output of the D flip-flop 220 is applied to a reset terminal of the counter 222. The clock terminal of the counter 222 is connected to the line 201 to receive primary clock pulses therefrom. The output of the counter 222 is taken at, for example, output Q<sub>6</sub> and applied to the clock terminal of the D flip-flop 221.

Thus, when a data pulse is received from the switch 215, it serves to clock the high state on the D terminal to the Q output, thence to the D input of the flip-flop **221.** As the Q output goes high, the  $\overline{Q}$  output goes low, thereby removing the high reset state from the counter 222, enabling it to begin counting the clock pulses applied thereto upon line 201. When the output line Q6 goes high (in 26 times the clock frequency divided by two, seconds), the high state on the D input of the flipflop 221 will be clocked through to the Q output thereof to be applied to an input of the AND gate 223. Upon the occurrence of the next clock pulse on line 201, the high state will be applied to the reset terminals of the flipflops 220 and 221 to return them to their initial states. Thus, the pulse appearing on output line 230 will be of constant width, that being estblished by the time for the output Q6 of the counter 222 to assume a high state from the time the pulse is received from switch 215. The amplitude of the output pulse on line 230 will, of course, be constant, equal to that of the high state.

The output from the digital one shot generator is applied to the start latch circuit 152 (FIG. 3A). The start latch circuit 152 includes a J-K master-slave flip-flop 235 to the clock input of which the output from the digital one shot generator 151 is applied. The K input of the flip-flop 235 is tied low, and the J input is connected to the  $\overline{Q}$  output. The Q output, therefore, is high continuously after the reception of the first clock pulse, until the flip-flop 235 is reset. The reset terminal is connected to the stop latch circuit 167 (FIG. 3B), below described. The Q output of the flip-flop 235 is applied to one input terminal of a NAND gate 156, and the data generated

upon the output line 230 of the pulse generator 151 is applied to the other input terminal. The output of the NAND gate 156 is applied to the shift register 165 (FIG. 3B) and to one input terminal of the NAND gate 170 (FIG. 3C) for transmission to the data counter 182 5 (FIG. 3C), as described below.

The O output of the J-K flip-flop 235 is applied to the reset circuit 155 (FIG. 3B), which includes two D-type flip-flops 240 and 241. The D input of the flip-flop 240 is tied high, and the output upon line 239 from the start 10 latch circuit is connected to the clock input. Thus, when the state upon line 239 changes from low to high, the high state upon the D input is transferred to the Q output of the flip-flop 240 to appear upon the D input to the flip-flop 241. The clock terminal of the flip-flop 241 is 15 connected to receive primary clock pulses appearing upon the line 201. Thus, upon activation of the start latch 235, the high state upon the D input of the flip-flop 240 is transferred through, with the occurrence of a present a high resetting state upon the output line 243, which is connected to the reset terminals of the flip-flop 240, the shift register 165, the enable latch 176 (FIG. 3C), the pattern search stop latch 166 (FIG. 3C), and the data counter 182 (FIG. 3C), as below described. 25 The reset pulse, however, is of self-limiting duration, being terminated upon its appearance at the reset terminal of the flip-flop 240 after the occurrence of a subsequent primary clock pulse upon line 201.

is applied to the reset terminals of the counter circuits of the counter 162 (FIG. 3B). The counter 162 includes a ripple-carry binary counter 258, a ripple-carry binary counter 259 and an AND gate 260. Both the counters flip-flop 235. Thus, when the start latch 235 is activated, the reset state normally appearing on the reset terminals 258 and 259 is removed, initiating the count of the counter 162.

The primary clock pulses upon line 201 are connected 40 to the clock input of the counter 259, and the outputs developed upon lines Q<sub>5</sub>, Q<sub>9</sub> and Q<sub>12</sub> are conducted to the shift register 165 (FIG. 3B), the pattern search stop latch 166 (FIG. 3C), and the clock terminal of the counter 258, respectively. Thus, the outputs from the 45 counter 259 occur at submultiples of the clock frequency appearing upon line 201; for example, since the clock frequency is about 6.82KHz (having a period of about 0.1466 milliseconds), the pulses upon line Q<sub>5</sub> are of period of approximately 4.69 milliseconds, the out- 50 puts on line Q<sub>9</sub> are of period approximately 75.07 milliseconds, and the outputs on line Q12 are of period approximately 600.58 milliseconds.

The output from output terminal Q<sub>1</sub> of the counter 258 is connected to one terminal of the AND gate 260 55 and the output from line Q4 is connected to the other input thereof. Since the counter 258 receives its clock pulses from the Q<sub>12</sub> output of the counter 259, the outputs  $Q_1$  and  $Q_4$  of the counter 258 at the output of the AND gate 260 will change from low to high states in 60 period of about 5,405.28 milliseconds. As will become apparent, the data received upon the switch 215 will be received at a frequency period appearing on output terminal Q<sub>5</sub> of the counter 259, or 4.69 milliseconds. Therefore, the change in state at the output of the AND 65 gate 260 will be 1152 data pulses after the counters are permitted to begin their count, to activate the stop latch circuit 167 (FIG. 3B), below described.

In its operation, the circuit first seeks an access code pattern of pulses received by the input switch 215. For this purpose, a pattern recognition circuit 270 (FIG. 3B) is provided, including a shift register 165 and a pattern recognizing NAND gate 172. The output Q5 of the counter 259 is applied to the clock input of the shift register 165. The data produced by the one shot pulse generator 151 (FIG. 3A) is applied via NAND gate 156 to the "data" input of the shift register 165. The data is clocked into the shift register 165 at the frequency of the pulses generated upon the terminal Q5 of the counter 259. Thus, it can be seen that if the pulses transmitted to the circuit are not at the frequency produced upon the line Q5 of the counter 259, the data will not be properly clocked into the shift register 165, and will not be recognized by the pattern recognition circuit 172 below described. This clocking requirement therefore imposes a frequency constraint upon the input data in addition to the other requirements (especially the patclock pulse, to the Q output of the flip-flop 241, to 20 tern of high and low states) thereby increasing the statistical odds against inadvertent actuation of the parameter determining code circuitry.

10

As the data is shifted into the shift register 165, it appears as the output terminals  $Q_1$ ,  $Q_2$ ,  $Q_3$ ,  $Q_4$ ,  $Q_5$ ,  $Q_6$ , and Q7. The output terminals of the shift register 165 are connected to the input terminals of the NAND gate 172. If desired, various ones of the output lines of the shift register 165 can be inverted, such as by inverters 272 and 273, to thereby provide a facility of uniquely The Q output of the start latch flip-flop 235 (FIG. 3A) 30 coding the required recognition pattern to the circuit.

The NAND gate 172 produces a low output only upon the concurrence of all of the inputs thereto. Thus, only at the time when the outputs of the shift register 165 correspond to the predetermined access code will 258 and 259 are reset by the  $\overline{Q}$  output of the start latch 35 they produce a state change at the output terminal of the NAND gate 172. The output at the NAND gate 172 is inverted by an inverter 274 to be applied to an input of the NAND gate 174 (FIG. 3C).

After a sufficient time for the access pattern to be recognized, the circuit is disabled from continuing its access pattern search by the pattern search stop latch 166 (FIG. 3C). The pattern search stop latch 166 includes a J-K master-slave flip-flop 276 which receives its clock input from the output Q<sub>9</sub> of the counter 259. The K input of the flip-flop 276 is tied low, and the J input is tied to the  $\overline{Q}$  output. Thus, upon the reception of a clock pulse upon the clock terminal, the Q output will change from a normally low to a high state, where it will remain until the flip-flop 276 is reset. The  $\overline{\mathbb{Q}}$  output is connected to the other terminal of the NAND gate 174 to prevent further transmission of signals from the pattern recognition circuit 270 therethrough. Since the clock input to the flip-flop 276 is derived from the output terminal Q9 of the flip-flop 259, the pattern search stop latch will be activated approximately 37.55 milliseconds after the start latch 152 has been activated. This corresponds to a period which includes eight data bits transmitted at the rate determined by the output Q<sub>5</sub> of the counter 259. Thus, once the access pattern search is begun, if it is not recognized within the first eight pulses, the circuit will discontinue its search and not accept further data until the time required for an entire programming cycle has elapsed.

Immediately prior to the activation of the pattern search stop latch 166, if the access pattern is recognized, the output from the pattern recognition circuit 270 is applied through the NAND gate 174 to the enable latch circuit 176 (FIG. 3C), which includes a J-K master-

slave flip-flop 280. The flip-flop 280 has its K input tied low and the  $\overline{Q}$  output tied to the J input. The signal from the pattern recognition circuit is applied to the clock input. Thus, once the enable pulse pattern is recognized, the enable latch produces a high state output 5 upon the Q output terminal thereof, which will continue until reset. The Q output terminal of the flip-flop 280 is connected to one input of the NAND gate 170 to control the transmission of the data transmitted through the gate 156 (FIG. 3C). The Q output of the flip-flop 280 is 10 additionally connected to an input of the AND gate 180 to be compared with the output of the stop latch circuit 167 (FIG. 3B), below described. Thus, once the enable latch 176 changes state upon the recognition of the access pattern, the data upon the line 230 is applied to 15 191 by a resistor 320. The emitter of the transistor 310 is the data counter circuit 182 (FIG. 3C).

The data counter 182 includes a ripple-carry counter 291. The data from the one shot pulse generator 151 (FIG. 3A) is applied to the clock input of the counter 291. Thus, as the data is entered into the counter 291, 20 the output states Q<sub>1</sub>-Q<sub>10</sub> will reflect the number of pulses received. It should be noted that the output produced on the terminals  $Q_1$ – $Q_{10}$  is the binary equivalent to the number of pulses received at the clock input, with the most significant digit being located upon the line Q<sub>10</sub>.

The data upon lines  $Q_1-Q_{10}$  of the counter 291 are connected directly to the data storage circuit 184 (FIG. 3C). The data storage circuit 184 includes a latch 295 and two D-type flip-flops 290 and 292 for storing the signals applied thereto. The various outputs  $Q_1-Q_8$  of 30 voltage to the output line 22, as above described. the counter 291 are applied to the various data inputs of the latch 295, the store terminals of which are connected to the output of the AND gate 180, which, as above described, receives its inputs from the outputs of the stop latch circuit 167 (FIG. 3B) and the enable latch 35 circuit 176 (FIG. 3C). The Q9 and Q10 outputs of the counter 291 are connected to the respective D inputs of flip-flops 290 and 292, respectively. The Q outputs of the flip-flops 290 and 292 constitute two additional control data states at points EE and FF.

The stop latch circuit 167 (FIG. 3B) includes two D-type flip-flops 300 and 301. The primary clock pulses upon the line 201 are connected to the clock input of the flip-flop 301, and as above indicated, the  $Q_1$  and  $Q_4$ outputs of the counter 258 are conducted through the 45 AND gate 260 to the clock input of the other flip-flop 300. The D input of the flip-flop 300 is connected high, and the Q output is connected to the D input of the flip-flop 301. The Q output of the flip-flop 301 is con-180 and to the reset terminal of the flip-flop 300.

Thus, when all of the data which has been received by the circuit within the time period defined by the change in concurrence of state changes of the outputs Q1 and Q<sub>4</sub> of the counter 258 is received, the stop latch circuit 55 167 and the enable latch circuit 176 (FIG. 3C) will produce a signal to the store terminals of the latch 295 (FIG. 3C) to thereby enter the data appearing at the data terminal inputs thereof. The data will then be thereafter stored in the latch circuit until another signal 60 set, including a proper access code, is subsequently applied to the circuit. The outputs appearing upon the latch 295 are, thereafter, available for conduction to various modification circuits to change the operating parameters of the heart pacer with which the circuit is 65 employed.

The electrical schematic diagram of the pulse generator 21 (See FIG. 1) is shown in detail in FIG. 4. The

pulse generator 21 functions as a voltage multiplying circuit, and includes two n-p-n transistors 310 and 311. The collector and emitter of the transistor 311 interconnect one side of a capacitor 313 in series with the output line 22 via a capacitor 314. A resistor 316 connects the base of the transistor 311 to a negative terminal 190 and a resistor 322 connects the collector of the transistor 311 to a ground terminal 191, to reverse bias the collectorbase junction of the transistor 311.

The side of the capacitor 313 which is connected to the emitter of the transistor 311 is also connected to a negative potential at terminal 190 by a resistor 318. The opposite plate of the capacitor 313 is connected to the collector of the transistor 310 and to a ground potential connected directly to the negative terminal 190. Thus, when the transistors 310 and 311 in their normally nonconducting states, the capacitor 313 becomes charged, as indicated, by the voltage between the negative terminal 190 and the ground terminal 191 through resistors

When the transistor 310 is biased into condition, as below described, the negative potential upon its emitter is connected in series with the previously charged capacitor 313, thereby multiplying the voltage developed between the emitter of the transistor 311 with respect to ground. Additionally, this increased negative potential forward biases the base-emitter junction of the transistor 311, causing it to conduct, delivering the multiplied

A zener diode 324 is connected between the output line 22 and ground 191 to protect against defibrillation and other undesirably high voltages which may be en-

The production of the stimulation pulse, as above indicated, is controlled by the application of a base current to the transistor 310. This base current is established in a resistive path in series between the base of the transistor 310 and the output of a NAND gate 327. The inputs to the NAND gate 327 are interconnected so that the NAND gate inverts the signal derived from the output of the width control circuit 17 (see FIG. 1), as below described in detail.

The resistance of the resistive path, and, consequently, the base current of the transistor 310 is controlled by an amplitude control circuit 24. The amplitude control circuit 24 includes three resistors 326, 329, ad 330. The resistors 329 and 330 are connected in parallel with each other and with the resistor 326 by bilateral nected to one of the input terminals of the AND gate 50 switches 332 and 333, respectively. The switches 332 and 333 receive digital operating signals upon lines II and JJ, respectively, which are derived at the output of the data storage circuit 295 in the master parameter control 150 (see FIG. 3C). Thus, in operation, the presence of a logic 00 upon the respective terminals II and JJ results in the entire value of the resistor 326 being presented to control the base current of the transistor 310. The presence of a logic 01 upon the terminals II and JJ will cause the switch 332 to close to result in the resistive value of the parallel combination of the resistors 329 and 326 in the base circuit. The presence of the logic value 10 upon the terminals II and JJ will result switch 333 closing to produce the parallel combination of the resistors 330 and 326 in the base circuit. And the presence of a logic 11 upon the terminals II and JJ will result in both switches 332 and 333 closing to produce the parallel combination of all three resistors 329, 330, and 326 in the base circuit. Thus, the collector-emitter

current of the transistor 310 is controlled by the logic value presented upon the terminals II and JJ.

The amount the transistor 310 is biased into conduction, as controlled by the logic state upon the terminals II and JJ, determines the amplitude of the output pulse 5 delivered to the output line 22. That is, the voltage drop between the collector and emitter determines the voltage which is seen in series with the voltage previously impressed upon the capacitor 313.

The output line 22, which, in addition to delivering 10 stimulation pulses from the pulse generator 21, as above described, serves to conduct naturally produced heart pulses to the detection portion of the pacer 10 upon line 33. A resistor 340 is connected in series with a capacitor 341 to a non-inverting input of an operational amplifier 15 343. The resistor 340 and the capacitor 341, in addition to coupling the signal to the input, serve as a low frequency filter, the capacitor 341 presenting a high impedance to the low frequency components of the detected signal upon the line 22. A diode 344 is connected 20 from between the resistor 340 and the capacitor 341 to a ground terminal 191, to clamp the amplitude of the stimulation pulse to an acceptable voltage, to prevent overloading the amplifier 343.

A resistor 346 is connected in series with a capacitor 25 347 between a ground terminal 191 and an inverting input to the operational amplifier 343. A feedback resistor 349 is connected between the output of the amplifier 343 and its inverting input. The resistor 346 and the capacitor 347 also serve as a low frequency filter to the 30 signal produced at the output of the operational amplifier 343. A feed-forward compensation capacitor 350 is provided for determining the high 3db frequency rolloff point. Finally, the non-inverting input of the amplitwo resistors 352 and 353 connected in series between a negative terminal 190 and a ground terminal 191. An offset balance resistor 355 is connected between the ground terminal 191 and an offset balance terminal of the amplifier 343. The output of the amplifier 343 is 40 connected to the gate of an FET transistor 356 to control the source-drain current therethrough. Thus, upon the reception of a naturally produced heart pulse (or other signal having similar frequency characteristics), the amplifier 343 produces an output voltage to turn on 45 the FET 356. The extent to which the FET 356 is turned on is, of course, dependent on the output voltage of the amplifier 343, which, in turn, is determined by the amplitude of the signal sensing upon the line 22.

The sensitivity of the pacer 10 to the signal produced 50 by the R-wve amplifier 32 is controlled by the sensitivity control circuit 35 (see FIG. 1). The sensitivity control circuit 35 includes a NAND gate 358, the inputs of which are interconnected to the output terminals GG of the data storage latch 295 (see FIG. 3C) so that the 55 NAND gate 358 inverts the signal thereat. The output from the NAND gate 358 is connected to a control terminal of a bilateral switch 359 which is connected in parallel with a Schottky diode 361.

Another terminal HH of the latch 295 (FIG. 3C) is 60 connected to a second bilateral switch 362, which is connected in parallel with a silicon diode 364. Additionally, the anode of the diode 361 is connected to a ground terminal 191, and the cathode of the diode 364 is connected to the source of the FET 356. A resistor 365 is 65 connected between the drain of the FET 356 and a negative terminal 190. Thus, a current path is defined from the ground terminal 191 through the diodes 361

and 364, the source and drain of the FET 356 and the resistor 365 to the negative terminal 190. Since the forward resistances of the Schottky and silicon diodes 361 and 364 are on the order of about 0.2 and 0.7 ohms, respectively, the current through the resistor 365 when the FET 356 is in a conducting state can be controlled by the operation of one or the other, neither or both of the bilateral switches 359 and 362. For example, if the logic level 00 were applied to the respective terminals GG and HH, the bilateral switch 359 is turned on and the bilateral switch 362 is turned off, to provide a current path from the ground terminal 191 through the switch 359 and diode 364 to the source of the FET 356. A logic level 01 on the terminals GG and HH turn both switches 359 and 362 on, bipassing both diodes 361 and 364 in the current path from the ground terminal 191 to the source. A logic level 10 on the respective terminals GG and HH turns the switch 359 off and the switch 362 off, providing a current path through both diodes 361 and 364 from the ground terminal 191 to the source. Finally, a logic level 11 on the input terminals GG and HH turns the switch 359 off and the switch 362 on, thereby providing a current path from the ground terminal 191 through the diode 361 and switch 362 to the source of the FET 356. Thus, by the application of the appropriate logic level to the terminals GG and HH, the potential applied to the source of the FET 356 can be controllably varied to determine the voltage level at which the FET 356 is turned on. When the FET 356 is turned on, a voltage is developed across the resistor 365, which is applied to an input of a pair of inverters 370 and 371 for application to the control counter 38 (see

FIG. 1). The control counter circuit 38, refractory control 43, fier 343 is connected to a voltage divider comprising 35 asynchronous generator reset circuit 41, asynchronous interval generator 15, asynchronous rate control 16, and width control circuit 17 as set forth in FIG. 1 are shown in detail in FIGS. 5A and 5B. Pulses which represent first divided clock pulses at a one-fourth divided frequency from the primary clock pulses supplied by the clock 12 (see FIG. 3A) are conducted to the various circuit components upon line 14, as shown.

The output from the R-wave amplifier 32 is conducted by the line Z to the reset terminal of the control counter 38, as shown in FIG. 5A. Thus, upon the detection of an appropriate signal by the R-wave amplifier 32, a reset signal is applied to the control counter 38. First divided clock pulses upon the line 14 are conducted to one input of the NAND gate 40, the output of which is connected to the clock input of the counter 38. The counter 38, is a ripple carry counter, and produces outputs upon its various respective output terminals corresponding to a predetermined respective count of clock pulses applied to its clock terminal. The primary function of the control counter 38, as described briefly above, is to define a refractory state or control interval during which the reception of a naturally occurring heart pulse has no resetting effect, and after which the reception of such pulse produces a resetting pulse, indicating that the heart is properly functioning. There are two selectible output lines from the counter 38, one being taken upon the line 373 from the Q<sub>9</sub> output, and the other being taken upon the line 374, being taken from the  $Q_7$  and the  $Q_{10}$  outputs via a AND gate 376. The signals upon the lines 373 and 374 represent a change in state corresponding to clock pulses of  $2^9 \div 2$ = 256 and  $2^{10} + 2^7 \div 2 = 576$ . The clock pulses upon line 14, being of approximately 0.587 milliseconds, pro-

duce changes in states upon the line 373 and 374 after 150.15 milliseconds and 337.83 milliseconds, respectively. Thus, a capability of choice between the respective times of changes in state upon the lines 373 and 374 to determine the refractory period of the pacer is made 5 available. The selection between the signals upon the lines 373 and 374 is made by a multiplexer 377. The line 373 is connected to the O input and the line 374 is connected to the 1 input, respectively, of the multiplexer of the latch 295 (FIG. 3C) to present the signal thereupon to the multiplier 377. The truth table of the multiplexer 377 provides that upon the application of a zero state to the A terminal, the signal on the O input terminal is applied upon the output terminal to the line 379. A 15 1 state applied to the A terminal connects the signal upon the 1 input to the output line 379. Therefore, the signal presented upon the output Q<sub>8</sub> of the latch 295 (FIG. 3C) representing the refractory control signal determines whether the refractory period of the circuit 20 is 150.14 milliseconds as determined by the signal on the line 373 or 337.83 milliseconds as determined by the signal on the line 374. The output from the multiplexer 377 upon the line 379 is conducted to an inverting NAND gate 45 the output of which is connected to the 25 asynchronous generator reset circuit 41 and to one of the terminals of the NAND gate 40 at the input of the control counter 38. In operation, after the counter 38 is reset, it begins to count clock pulses applied to its clock input via the NAND gate 40. Upon reaching the prede- 30 termined count upon the selected output line 373 or 374, an output signal is generated upon the line 379 to the inverting NAND gate 45, producing a change in state upon the output line 382 from a normally high to a low state. Upon the change in state upon the line 382, the 35 NAND gate 40 is disabled from passing additional clock pulses to the counter 38 thereby stopping its count. The control counter 38, therefore, is caused to discontinue its count until it is reset by a subsequently received pulse from the R-wave amplifier 32.

In addition to the outputs produced upon the terminals Q9, Q7 and Q10, an output is produced upon the terminal Q<sub>4</sub> of the counter 38 which is conducted to the asynchronous generator reset circuit 41, as next immediately described.

The asynchronous generator reset circuit 41 includes two D-type flip-flops 384 and 385. The D input of the flip-flop 384 is connected to a high state, and the Q output thereof is connected to the D input of the flipflop 385. The Q output of the flip-flop 85 is connected to 50 the reset terminal of the flip-flop 384, and the  $\overline{Q}$  output of the flip-flop 385 represents the output of the asynchronous generator reset circuit 41, to be conducted to one input of the NAND gate 30 (FIG. 5B). The output of the NAND gate 45 upon the line 382, representing 55 the selected refractory period signal, is applied to the clock input of the flip-flop 384. The output upon the terminal Q4 of the counter is applied to the clock input of the other flip-flop 385. Thus, in operation, after the control counter 38 is reset, it begins its count, reaching 60 first a count to produce an output upon the terminal Q4 to thereby clock the high state on the D input thereof through to the D input of the flip flop 385. When the counter 38 subsequently reaches the count on the selected output upon line 373 or line 374, a clock pulse is 65 applied to the clock input of the flip-flop 385, thereby producing a change in state upon its outputs, the Q output changing from low to high states and the  $\overline{Q}$

output changing from high to low states. The change in output from high to low states upon the  $\overline{Q}$  output, applied to the NAND gate 30 (FIG. 5B), defines the reset signal for delivery to the asynchronous interval generator 15 (FIG. 5B).

Thus, it can be seen that if a reset signal is received upon the reset terminal of the counter 38 prior to its reaching the count on the selected output line 373 or 374, the counter is reset to begin its count completely 377. The A input is connected to the terminal Q<sub>8</sub> (NN) 10 anew, without producing an output pulse from the flipflop 385. This resetting condition can be prolonged indefinitely, if, for example, an interference signal is caused to continually reset the counter 38 within the refractory period determined by the master parameter control 150. After the predeterined count has been reached, however, the flip-flop 385 having been previously "armed" by the signal upon the terminal Q<sub>4</sub> of the counter produces a reset signal upon the output terminal  $\overline{Q}$  of the flip-flop 385.

At this point, it should be noted that the generation or not of a reset signal from the asynchronous generator reset circuit 41 controls the demand operation of the overall pacer circuit 10. Thus, for example, if no reset signal is generated, the asynchronous interval generator 15 is permitted to continuously count, producing stimulation signals at the predetermined selected rate.

A NAND gate 387 is provided, having its output connected to the reset terminal of the flip-flop 385. One input of the NAND gate 387 is connected to the inverter 216 (see FIG. 3A). The other input to the NAND gate 387 is connected to the output Q (FF) of the D-flipflop 292 (FIG. 3C). Thus, if the reed switch 215 (FIG. 3A) is closed by, for example, the nearness of a magnet for testing purposes or the like, a high output state is produced by the NAND gate 387 to continuously supply a reset voltage to the flip-flop 385, to thereby disable the generation of resetting pulses, causing the pacer circuit 10 to operate asynchronously. Additionally, the presence of a 0 signal upon the output Q (FF) of the flip-flop 292 likewise produces a constant resetting voltage upon the output of the NAND gate 387, to constrain the pacer circuit 10 to asynchronous or fixed rate

The resetting signal from the asynchronous generator 45 reset circuit 41, delivered to the NAND gate 30, as above described, is delivered upon a line 388 to a resetting terminal of the asynchronous interval generator 15 (FIG. 5B). The asynchronous interval generator 15, which is of the ripple carry counter type, receives clock pulses upon line 14 to its clock terminal to produce outputs at various output terminals thereof. In the embodiment illustrated, for example, outputs are derived at terminals Q6-Q12. The output signals themselves are logic combinations of selected outputs, the selection of one of which can be employed to determine the asynchronous interval rate of the pacer circuit 10. More particularly, outputs from the Q<sub>7</sub>, Q<sub>9</sub> and Q<sub>10</sub> terminals of the counter 15 are combined by an AND gate 390 to produce a change in output state after about 489.41 milliseconds. The output from the AND gate 390 is conducted to input 7 of a multiplexer 391. The outputs upon terminals  $Q_6$ ,  $Q_8$ ,  $Q_9$  and  $Q_{10}$  are combined by an AND gate 393 to produce a change in output state after approximately 544.29 milliseconds. The output from the AND gate 393 is connected to input terminal 6 of the multiplier 391. The output terminal  $Q_{11}$  of the counter 15 is connected directly by line 394 to input 5 of the multiplexer 391, and presents a signal which changes

states after approximately 600.58 milliseconds. The output terminals Q<sub>8</sub> and Q<sub>11</sub> are combined by an AND gate 395, the output of which is connected to input terminal 4 of the multiplexer 391, and which produces a change in state after approximately 675.66 milliseconds. The 5 output terminals Q<sub>9</sub> and Q<sub>11</sub> are combined in the AND gate 396, the output of which is connected to input terminal 3 of the multiplexer 391 to produce a change in state after about 750.73 milliseconds. The terminals Q<sub>8</sub>, Q<sub>9</sub> and Q<sub>11</sub> are combined in the AND gate 397, the 10 output of which is connected to input terminal 2 of the multiplexer 391 and produces a change in state after about 825.81 milliseconds. The terminals Q<sub>8</sub>, Q<sub>10</sub> and Q<sub>11</sub> are combined in an AND gate 398, the output of which is connected to terminal 1 of the multiplexer 391 and which produces a change in state after about 975.96 milliseconds. Finally, output terminal Q<sub>12</sub> is connected directly to input terminal 0 of the multiplexer 391 on line 399, which produces a change in state after about 1201.17 milliseconds.

The control terminals A, B, and C of the multiplexer 391 are connected to three respective rate control terminals Q<sub>5</sub>, Q<sub>6</sub> and Q<sub>7</sub> (KK, LL, MM) of the latch 295 (see FIG. 3C). The control signals which determine which of the inputs 0-7 is connected to the output line 400, is in accordance with the truth table below set forth:

| A  | В | С   | OUT | _   |

|----|---|-----|-----|-----|

| 0  | 0 | 0   | 0   | — 3 |

| ·ŏ | Ŏ | Ĭ   | i   |     |

| Õ  | ī | Ō   | 2   |     |

| Ó  | i | 1   | 3   |     |

| 1  | Ō | 0   | 4   |     |

| 1  | 0 | 1   | . 5 |     |

| 1  | 1 | 0 ' | 6   |     |

| 1  | 1 | 1   | 7   | 3   |

Thus, the output time upon one of the various multiplexer lines is selected by a logic input to the input terminals of the multiplexer, and, therefore, the asynchronous rate of the pacer circuit 10 can be selected 40 among any of the above set forth various times.

The output signal upon the line 400 from the multiplexer 391 is conducted to the width control circuit 17, as follows. The width control circuit 17 includes two J-K masterslave flip-flops 402 and 403. The J input of 45 the flip-flop 402 is connected high, and the K input is connected low. The Q and Q outputs of the flip-flop 402 are connected respectively to the J and K inputs of the flip-flop 403. The Q output of the flip-flop 403 is connected to the reset terminal of the flip-flop 402, and the 50 Q output of the flip-flop 403 constitutes the output of the width control circuit 17. The signal upon the line 400 from the multiplexer 391 constitutes the clock signal to the flip-flop 402, which, upon its ocurrence, produces output Q. The output from a width determining multiplexer circuit (below described) is connected to the clock input of the flip-flop 403 to clock the input upon the J-K terminals to the output terminals Q and  $\overline{Q}$ . More clock pulses upon the line 14 at its 0 input terminal. Additionally, it receives second divided clock pulses at a second divided frequency from the flip-flop 204 (FIG. 3A) upon line 208 (BB) at its 1 input terminal. The control terminal A receives its input from the width 65 control signal at the Q output (EE) of the D-flip-flop 290 (FIG. 3C). Thus, depending on whether the signal upon the control terminal is high or low determines

18

whether the clock pulses at the input terminals 0 or 1 are respectively applied to the output terminal upon the line 406 for delivery to the clock terminal of the flipflop 403. It can be seen that the selection of the clock pulses at the lower frequency produces a longer change in state upon the output  $\overline{Q}$  of the flip-flop 403 than the higher frequency of clock pulses upon the input line 0 of the multiplexer 405, thereby providing a facility for controlling the width of the pacer produced stimulation pulse. The output from the flip-flop 403 upon the  $\overline{Q}$ output is conducted upon the line 408 to provide the drive signal to the pulse generator circuit 21 (FIGS. 1 and 4). The output upon the terminal  $\overline{Q}$  of the flip-flop 403 is additionally conducted to one of the input of the NAND gate 30, to constitute an additional resetting signal to the asynchronous interval generator 15. Thus, upon the generation of an asynchronous signal, the asynchronous interval generator is reset to reinitiate its timing of its next subsequent asynchronous interval.

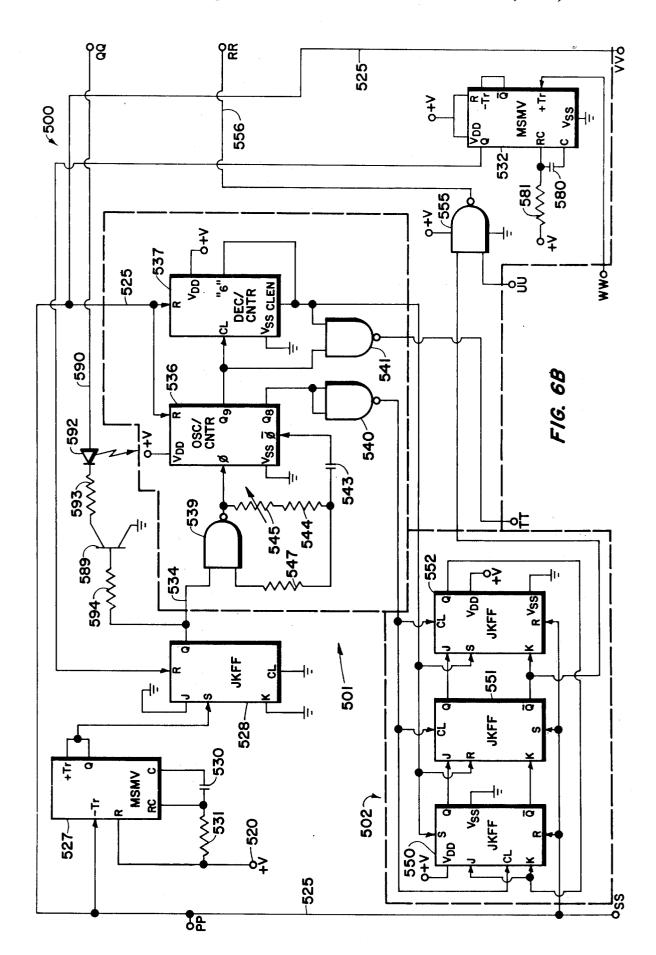

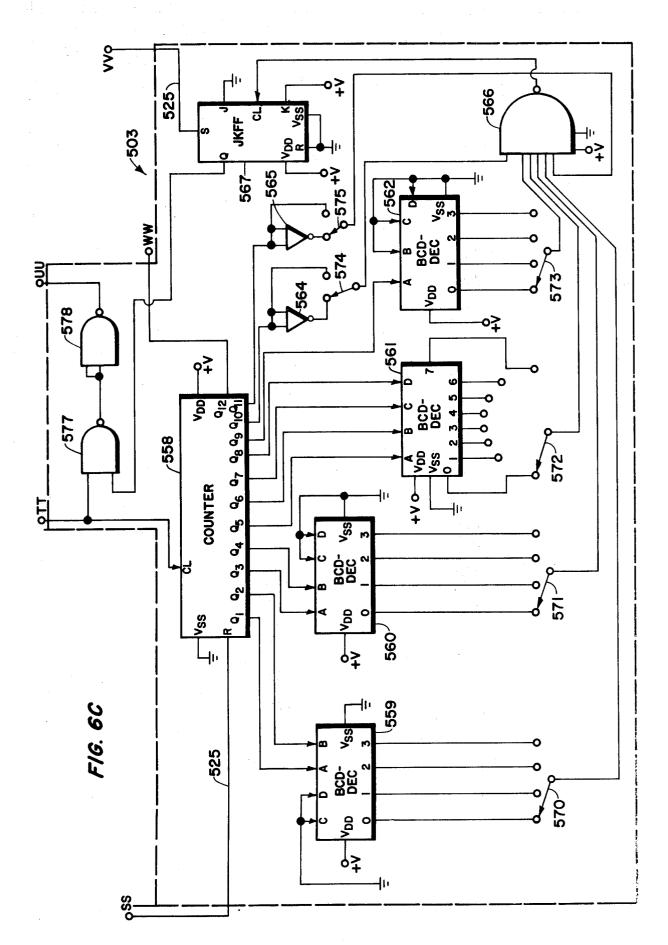

The external control unit, designated by the general reference numeral 500 for generating and transmitting the access code and the pulses for determining the parameters of the pacer 10, above described, is shown in detail in FIGS. 6A, 6B, 6C, and 6D. The connections between the figures are indicated by corresponding letters. As will become apparent, unlike the circuitry of the implantable pacer 10 above described with reference to FIGS. 1-5, the circuitry illustrated in FIGS. 30 6A-6D is configured with ground denoting a 0 or low logic state and  $+\nu$  representing a high or 1 logic state.

The external control unit 500 includes four main sections, each encircled with dashed lines. An oscillator section 501 (FIG. 6B) provides clock pulses to the re-35 mainder of the external control unit circuitry. The access code generator 502 (FIG. 6B) generates a particular sequence of pulses for access into the master parameter control circuit 150 (FIGS. 1 and 3A-3C). A parameter code generator 503 (FIG. 6C) generates a controllable number of pulses, each number corresponding to an individual set of selectible pacer parameters. Finally, a pulse output circuit 504 (FIG. 6D) produces the electromagnetic pulses for transmission to the master parameter control in accordance with the access code generator 502 and the parameter code generated by the parameter code generator 503.

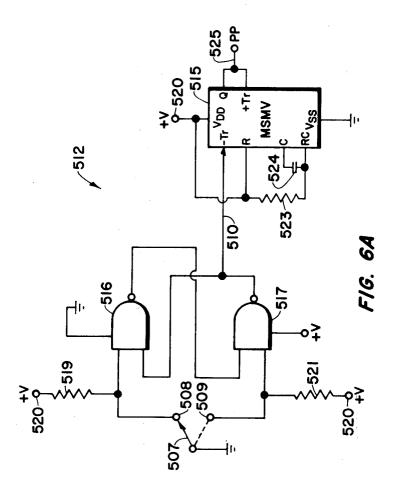

More particularly, the clock pulse generator 501 (FIG. 6B) is activated by closing the switch 507 (FIG. 6A). The switch 507, when moved from the upper position 508 to the lower position 509 produces a change from a low to high state upon the output line 510 of an antibounce circuit, generally denoted by the reference numeral 512. Upon the return of the switch 507 to the upper position 508, the state on line 510 changes from a high state upon the output Q and a low state upon the 55 high to low, to thereby trigger a monostable multivibrator 515, which, as below described, produces a resetting signal upon the line 525 to the various circuit elements of the control unit and a subsequent start pulse.

The antibounce circuit 512 includes two NAND gates particularly, the multiplexer 405 receives first divided 60 516 and 517 and the monostable multivibrator 515, which is connected to be non-retriggerable after its initial trigger signal has been received.

> One input of the NAND gate 516 is connected via a resistor 519 to a positive terminal 520 to thereby define a normally high state thereupon. This terminal is additionally connected to the upper terminal 508 of the start switch 507. The other input to the NAND gate 516 is connected to the output of the NAND gate 517. In a

similar fashion, one input of the NAND gate 517 is connected by a resistor 521 to a positive terminal 520 and also to the lower terminal 509 of the switch 507. The other input of the NAND gate 517 is connected to the output of the NAND gate 516. The output of the 5 NAND gate 517 is the output of the circuit, and is directed to the monostable multivibrator 515.

As shown, the monostable multivibrator 515 is triggered upon a negative going pulse (i.e., a pulse changing from high to low states). Upon the occurrence of such 10 state change, the output Q changes from low to high states, where it remains for a time period depending upon the value of a resistor 523 and a capacitor 524 connected from the RC terminal to the R and C terminals respectively. The R terminal is connected to the 15 positive terminal 520. The positive trigger input is connected to the Q output to provide for the trailing edge (negative going) triggering, non-retriggering capability of the monostable multivibrator 515, as mentioned.

negative going signal upon the trigger input of the multivibrator 515, the Q output changes from low to high states, during which a resetting signal is delivered to the various circuit components upon the line 525, as below described, to provide an initial starting state therefore, 25 high state. When, however, the signal on line 534 is low, After the output Q from the multivibrator 515 has remained in the high state for the time determined by the time constant defined by the capacitor 524 and the resistor 523, it changes in state from high to low. This state change triggers a second monostable multivibrator 527 30 (FIG. 6B), which procudes a signal to a J-K masterslave flip-flop 528, which serves as a start latch.

The monostable multivibrator 527 is connected in a fashion similar to the monostable multivibrator 515, to be triggered by a negative going pulse applied to the 35 minus trigger input for a time period defined by the RC time constant of the capacitor 530 and resistor 531 connected from the RC terminal to the C and R terminals respectively. Additionally, the R terminals is connected to a positive terminal 520. The positive trigger input is 40 connected to the Q output to provide for the non-triggerable capability of the monostable multivibrator 527.

The J and K inputs of the flip-flop 528 are tied low, together with the clock input. The output from the monostable multivibrator 527 is connected to the set 45 terminal and the output is derived upon the Q terminal. The reset terminal is connected to the output of a pulse generator 532 which produces a pulse upon the completion of the pulse generating sequence of the control unit 500, as below described in detail. The output upon the 50 537 produces a reset state continually upon the flip-flop terminal Q of the flip-flop 528 provides the enable signal upon the line 534 to the clock pulse generator 501.

The clock pulse generator 501 includes a fourteen stage ripple carry binary counter/divider and oscillator 536, a decade counter 537 and three NAND gates 539, 55 540, and 541. The oscillator/counter 536 and the decade counter 537 each have their reset terminals connected to the reset line 525, above described. The oscillator/counter 536 has its clock and inverted clock terminals  $(\phi \text{ and } \overline{\phi})$  interconnected by a capacitor 543, a fixed 60 resistor 544 and a variable resistor 545 connected in series. A second fixed resistor 547 is connected between the junction of the capacitor 543 and resistor 544 to one input of the NAND gate 539. The other input of the NAND gate 539 is connected to the output of the start 65 latch flip-flop 528 upon the line 534. The output at Q<sub>8</sub> of the oscillator/counter 536 is connected to an inverting NAND gate 540, to provide clock pulses to the access

code generator 502, below described. The frequency derived at the terminal Q<sub>9</sub> of the oscillator/counter 536 corresponds to the internal clock frequency of the pacer by which the received access and parameter controlling codes are clocked into the various registers. This clock frequency is derived at the Q<sub>5</sub> output of the counter 259 (FIG. 3B).

The output upon the terminal Q<sub>9</sub> is connected to the clock input of the decade counter 537 and to one input of the NAND gate 541. The output from the NAND gate 541, representing the clock pulses appearing at the Q<sub>9</sub> terminal of the oscillator 536, are connected to one input terminal of the NAND gate 577 (FIG. 6C), as well as to the clock input of the counter 558 (FIG. 6C). The output at the "6" terminal of the decade counter 537 is connected to the clock enable input, to thereby inhibit the count of the decade counter 537 after the 6 counter is reached. The output upon the 6 line of the counter 537 is additionally connected to another input of the It can thefore be seen that upon the application of a 20 NAND gate 541 and to the various set and reset terminals of the parameter code generator 503 (FIG. 6C), below described.

In operation, the block pulse generator 501 will produce pulses so long as the signal on the line 534 is in a the clock input to the counter/oscillator 536 cannot vary, thereby stopping the generation of output pulses. The decade counter 537 serves to switch between the access code generator output 502 (FIG. 6B) after the access code has been generated and delivered to the output to the parameter code generator 503 (FIG. 6C) output for its subsequent delivery to the output. This is achieved by the NAND gate 541 which serves to selected between the output of the access code generator and the following parameter code sequence. Thus, prior to the time at which the counter 537 reaches a 6 count, the input to the NAND gate from the 6 output of the counter 537 is in a low state, thereby disabling the passage of the clock pulses upon the line Q<sub>9</sub> of the oscillator 536. Therefore, the input of the NAND gate 555 due to the parameter code sequence remains in a high state, allowing only the access code generated by the access code generator 502 to be delivered to the output line 556. Upon the reaching of the 6 count by the counter 537, the clock pulses produced upon the line Q<sub>9</sub> of the oscillator 536 are permitted to pass the NAND gate 541, to be delivered to the output line 556 via NAND gates 577, 578 (connected as an inverter), (FIG. 6C) and 555 (FIG. 6B). The high state on the 6 output of the counter 551 of the access code generator 502, to thereby produce a continuously high state on the  $\overline{Q}$  output thereof, to permit the parameter code sequence to pass the NAND gate 555, as below described.

The access code generator 502 includes three J-K master-slave flip-flops 550, 551 and 552. The J and K inputs of the flip-flop 550 are connected to the Q output of the flip-flop 552. The Q and  $\overline{Q}$  outputs of the flip-flop 550 are connected, respectively, to the J and K inputs of the flip-flop 551, and the Q and  $\overline{Q}$  outputs of the flip-flop 551 are connected, in turn, to the J and K inputs, respectively, of the flip-flop 552. The reset terminals of the flip-flops 550 and 552 as well as the set terminal of the flip-flop 551 are connected to the reset line 525. The set terminals of the flip-flops 550 and 552, as well as the reset terminal of the flip-flop 551 are connected to the 6 output of the decade counter 537. The output from the access code generator circuit is taken from the  $\overline{\mathbf{Q}}$  termi-

nal of the flip-flop 551. Thus, in operation, the flip-flops 550-552 of the access code generator are initialized by the signal on the reset line 525. Upon the reception of clock pulses from the clock pulse generator 501, and the output  $\overline{Q}$  output of the flip-flop 551 will produce the 5 following logic sequence: 1000010 — at a frequency half that of the Q8 output of the oscillator/counter 536 (at the same frequency of  $Q_9$ ).

The  $\overline{Q}$  output of the flip-flop 551 is connected to one input of a NAND gate 555. Thus, assuming the other 10 input to the NAND gate 555 is in a high state (which it is until the counter 6 of the decade counter 537 is reached, as will become apparent below), the inverted output upon the line 556 will be: 1000010, which is reinverted by the transmitting coil, below described.

As above described the one shot pulse generator 151 (FIG. 3A) of the master parameter control circuit 150 produces an output pulse only upon a change in input state from low to high. Therefore the code generated by the one shot pulse generator in response to a transmitted 20 digital signal of 01100010 is 1000010. This is the precise code recognized by the access code recognition circuit 270 (FIG. 3B).

The parameter code generator 503 (FIG. 6C) includes a twelve stage ripple carry counter 558, four BCD to 25 decimal decoders 559, 560, 561 and 562, two inverters 564 and 565, a NAND gate 566 capable of comparing at least six inputs and a J-K master-slave flip-flop 567. More particularly, the counter 558 receives clock pulses from the output of the NAND gate 541 (FIG. 6B), 30 being the clock frequency produced by the oscillator 536 divided by 29. The reset terminal is connected to the reset line 525, and the  $Q_1$ - $Q_{11}$  outputs are connected to the externally controlled parameter selection circuit, below described. The  $Q_{12}$  output is connected to a mas- 35 ter stop latch 532, as above reference, to stop the oscillator after the completion of the parameter code count. Still more particularly, the Q1 and Q2 outputs of the cunter 558 are connected to the A and B inputs of the the BCD to decimal decoder 559 are connected to a ground terminal to thereby present a low state thereupon. A four position switch 570 has each of its four terminals connected to the 0, 1, 2, and 3 terminals of the BCD to decimal decoder, respectively. The wiper por- 45 tion of the switch 570 is connected to one of the inputs of the six input NAND gate 566.

The outputs  $Q_3$  and  $Q_4$  of the counter 558 are connected to the input terminals A and B, respectively, of the BCD to decimal decoder 560. The C and D inputs 50 are connected to a ground or low state. The 0, 1, 2, and 3 outputs of the BCD to decimal decoder 560 are connected to respective terminals of a four position switch 571. The wiper of the switch 571 is connected to another input of the six input NAND gate 566. The output 55 terminals Q<sub>5</sub>-Q<sub>8</sub> of the counter 558 are connected to respective inputs A-D of the BCD to decimal decoder 561. The outputs 0-7 of the BCD to decimal decoder are connected to respectively terminals of a eight position switch 572, the wiper arm of which is also con- 60 nected to an input of the six input NAND gate 566. The output terminal Q<sub>9</sub> of the counter 558 is connected to the A input of the BCD to decimal decoder 562, and the B-D inputs of the BCD to decimal decoder 562 are connected to ground or a low state. The outputs 0-3 of 65 the BCD to decimal decoder 562 are connected to a respective one of a four terminal switch 573, the wiper arm of which is connected to one of the inputs of the six