## (19) **日本国特許庁(JP)**

## (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-162490 (P2006-162490A)

(43) 公開日 平成18年6月22日 (2006.6.22)

(51) Int.C1. **GO 1 R 31/28 (2006.01)**

HO 1 L 21/822 (2006.01) HO 1 L 27/04 (2006.01) FI テーマコード (参考)

GO1R 31/28 G 2G132 HO1L 27/04 T 5FO38

#### 審査請求 未請求 請求項の数 3 OL (全8頁)

(21) 出願番号 特願2004-356182 (P2004-356182) (22) 出願日 平成16年12月9日 (2004.12.9) (71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(74) 代理人 100107906

弁理士 須藤 克彦

(72) 発明者 関口 俊明

大阪府守口市京阪本通2丁目5番5号 三

洋電機株式会社内

F ターム (参考) 2G132 AA01 AA11 AB01 AC14 AK08

AK23

5F038 DF01 DT06 EZ20

(54) 【発明の名称】 スキャンテスト回路

## (57)【要約】

【課題】回路規模の増大を抑えながら、LSIの故障検 出率の向上を図ることができるスキャンテスト回路を提 供する。

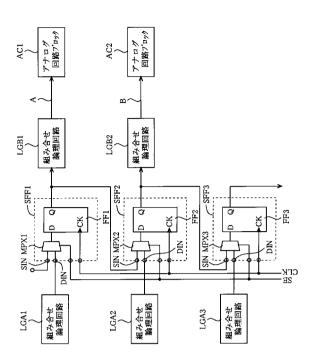

【解決手段】組み合わせ論理回路LGB1の出力データ(観測ポイントA)及び組み合わせ論理回路LGB2の出力データ(観測ポイントB)が入力された排他的論理和回路EXOR1の出力データがデータ入力端子DINに入力されたスキャンフリップフロップ回路SFF4を従来の回路に追加した。スキャンフリップフロップ回路SFF4は、スキャンフリップフロップ回路SFF2とSFF3との間に挿入され、スキャンイネーブル信号SEに応じて、シフトレジスタの一部のフリップフロップを形成するように構成されている。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

スキャンイネーブル信号に応じて、シフトレジスタを構成してシフト動作を行うか、第 1 の論理回路の出力データを取り込むキャプチャ動作を行うかを切り換え可能な複数の第 1 のスキャンフリップフロップ回路と、

前記スキャンフリップフロップ回路の出力データがそれぞれ入力された複数の第2の論理回路と、

前記複数の第2の論理回路のうち、少なくとも2つの第2の論理回路の出力データが入力された排他的論理和回路と、

前記排他的論理和回路の出力データが入力された第2のスキャンフリップフロップ回路とを備え、

前記第2のスキャンフリップフロップ回路を前記複数の第1のスキャンフリップフロップ回路が構成するシフトレジスタに組み込んだことを特徴とするスキャンテスト回路。

## 【請求項2】

前記第2の論理回路の出力データがアナログ回路ブロックに入力されることを特徴とする請求項1に記載のスキャンテスト回路。

#### 【請求項3】

前記スキャンフリップフロップ回路は、前記スキャンイネーブル信号が前記第 1 のレベルの時に前記第 1 の論理回路の出力データを選択し、前記スキャンイネーブル信号が前記第 2 のレベルの時に前段のスキャンフリップフロップ回路の出力データを選択するマルチプレクサを備えることを特徴とする請求項 1 に記載のスキャンテスト回路。

【発明の詳細な説明】

### 【技術分野】

[ 0 0 0 1 ]

本発明は、大規模集積回路のテストを容易化するためのスキャンテスト回路に関する。

#### 【背景技術】

### [0002]

一般に大規模集積回路(以下、LSIという)の市場出荷時にはLSIテスタによる良否判定テストが行われる。この際に使用されるテストパターンは、LSIを構成する複数の論理回路の中で、できる限り多くの故障箇所を見つけ出すことが必要である。

#### [0003]

しかしながら、LSIの大規模化に伴い、全ての論理回路をテストしようとするとテストベクタ量やテスト時間が膨大になる。そこで、この問題を解決するために、いわゆるテスト容易化設計(Design For Testability)が行われている。

#### [0004]

テスト容易化設計は、LSIのテストの方針をLSIの設計の段階で固め、LSIの中にテスト回路を組み込んでおく設計手法である。LSIのテストを容易に行えるかどうかの基本的な指標として、観測性(Observability)と制御性(Controllability)という概念がある。「観測性が良い」回路とは、回路内のあるノードについて、その論理値を外部から観測しやすいものをいい、「制御性が良い」回路とは、回路内のあるノードの論理値を外部からのデータ入力によって設定しやすいものをいう。回路の観測性と制御性が良いほど、有効なテストパターンを容易に作成でき、その結果LSIを構成する論理回路の故障検出率も向上する。この観測性と制御性を高めたテスト回路の1つにスキャンテスト回路がある。

#### [0005]

スキャンテスト回路とは、LSI内の各論理回路に対応して、フリップフロップ回路を配置した回路であり、複数のフリップフロップ回路をチェーン状に接続してシフトレジスタを構成し、各フリップフロップに取り込まれたデータを次々とシフトするシフト動作と、各論理回路の出力を各フリップフロップに取り込むキャプチャ動作とを行うものである

30

20

10

50

40

0

10

20

30

40

50

[0006]

即ち、最初のシフト動作によって、各フリップフロップのデータをテスト信号として各論理回路に与え、次にキャプチャ動作によって各論理回路の出力データを各フリップフロップに取り込む。そして、次のシフト動作によって各フリップフロップに取り込まれた各論理回路の出力データを最終段のフリップフロップから時系列的に得る。そして、そのようにして得られた各論理回路の出力データとその期待値とを比較することにより、各論理回路の良否判定が行われる(特許文献1)。

[0007]

図5は、スキャンテスト回路の一例を示す回路図である。組み合せ論理回路LGA1,LGA2,LGA3のそれぞれに対応して、スキャンフリップフロップ回路SFF1,SFF2,SFF3が配置されている。組み合せ論理回路LGA1,LGA2,LGA3は、アンド回路やナンド回路を含むデジタル回路から構成されている。

[00008]

スキャンフリップフロップ回路SFF1は、マルチプレクサMPX1とD型フリップフロップ回路FF1(遅延フリップフロップ回路)を備えており、マルチプレクサMPX1は、スキャンイネーブル信号SEに応じて、スキャン入力端子SINからのスキャンテスト信号か、データ入力端子DINから入力される組み合せ論理回路LGA1からの出力データのいずれかを選択し、Dフリップフロップ回路FF1のデータ入力端子Dに選択したデータを出力する。

[0009]

また、スキャンフリップフロップ回路SFF2は同様にマルチプレクサMPX2とDフリップフロップ回路FF2を備えており、マルチプレクサMPX2は、スキャンイネーブル信号SEに応じて、前段のスキャンフリップフロップ回路SFF1からの出力データか、組み合せ論理回路LGA2の出力データのいずれかを選択し、D型フリップフロップ回路FF2のデータ入力端子Dに選択したデータを出力する。

[0010]

また、スキャンフリップフロップ回路SFF3も同様にマルチプレクサMPX3とD型フリップフロップ回路FF3を備えており、マルチプレクサMPX3は、スキャンイネーブル信号SEに応じて、前段のスキャンフリップフロップ回路SFF2からの出力データか、組み合せ論理回路LGA3の出力データのいずれかを選択し、D型フリップフロップ回路FF3のデータ入力端子Dに選択したデータを出力する。

[0011]

また、D型フリップフロップ回路FF1,FF2,FF3のクロック入力端子CKには、共通のクロックCLKが入力される。なお、図5では3つの組み合せ論理回路及び3つのスキャンフリップフロップ回路SFF1,SFF2,SFF3を示したが、実際のLSIでは組み合せ論理回路及びこれに対応したスキャンフリップフロップの数は、数千個から数万個に及ぶ。

[0012]

また、スキャンフリップフロップ回路SFF1,SFF2の出力端子Qからの出力データは、それぞれ次段の組み合せ組み合せ論理回路LGB1,LGB2に出力され、さらに、組み合せ論理回路LGB1,LGB2の出力データがさらに次段のアナログ回路ブロックAC1,AC2は、例えば差動アンプのようなアナログ回路によって構成されている。

【特許文献1】特開2001-59856号公報

【発明の開示】

【発明が解決しようとする課題】

[0013]

上述したスキャンテスト回路では、組み合わせ論理回路LGA1,LGA2,LGA3の出力データをキャプチャ動作によりそれぞれスキャンフリップフロップ回路SFF1,SFF2,SFF3に取り込み、続いて、シフト動作により取り込んだデータをシフトす

(4)

ることで、最終段のスキャンフリップフロップから各組み合わせ論理回路の出力データを 得ることができる。

[0014]

しかしながら、アナログ回路ブロックAC1,AC2についてはスキャンテスト回路が設けられていないので、これらのアナログ回路ブロックAC1,AC2へ出力される組合せ論理回路LGB1,LGB2の出力データについては観測することができず、故障検出率が低下する原因となっていた。

[0015]

一方、そのような組み合せ論理回路LGB1,LGB2の出力データが現れる図5の観測ポイントA,Bにスキャンフリップフロップをそれぞれ追加すると回路規模が大きくなるという問題がある。

10

【課題を解決するための手段】

[0016]

そこで、本発明のスキャンテスト回路は、スキャンイネーブル信号に応じて、シフトレジスタを構成してシフト動作を行うか、第1の論理回路の出力データを取り込むキャプチャ動作を行うかを切り換え可能な複数の第1のスキャンフリップフロップ回路と、前記スキャンフリップフロップ回路の出力データがそれぞれ入力された複数の第2の論理回路の 当力データが入力された排他的論理和回路と、前記排他的論理和回路の出力データが入力された第2のスキャンフリップフロップ回路とを備え、前記第2のスキャンフリップフロップ回路を前記複数の第1のスキャンフリップフロップ回路が構成するシフトレジスタに組み込んだことを特徴とするものである。

20

[0017]

本発明によれば、従来は観測できなかった第2の論理回路の出力データを観測することが可能となる。また、排他的論理和回路と第2のスキャンフリップフロップ回路を追加すればよいので、回路規模の増大を最小限に抑えることができる。

【発明の効果】

[ 0 0 1 8 ]

本発明のスキャンテスト回路によれば、回路規模の増大を抑えながら、LSIの故障検出率の向上を図ることができる。

30

【発明を実施するための最良の形態】

[0019]

以下、本発明の第1の実施形態に係るスキャンテスト回路について、図面を参照しながら説明する。図1はこのスキャンテスト回路の回路図である。図5の回路と異なる点は、組み合わせ論理回路LGB1の出力データ(観測ポイントA)及び組み合わせ論理回路LGB2の出力データ(観測ポイントB)が入力された排他的論理和回路EXOR1と、その排他的論理和回路EXOR1の出力データがデータ入力端子DINに入力されたスキャンフリップフロップ回路SFF4を追加した点である。

[0020]

スキャンフリップフロップ回路SFF4は、前述したスキャンフリップフロップ回路SFF2とSFF3との間に挿入され、スキャンイネーブル信号SEに応じて、シフトレジスタの一部のフリップフロップを形成するように構成されている。即ち、スキャンフリップフロップ回路SFF4は、マルチプレクサMPX4とD型フリップフロップ回路FF4を備えており、マルチプレクサMPX4は、スキャンイネーブル信号SEに応じて、前段のスキャンフリップフロップ回路SFF2からの出力データか、排他的論理和回路EXOR1の出力データのいずれかを選択し、D型フリップフロップ回路FF4のボータ入力端子Dに選択したデータを出力する。そして、D型フリップフロップ回路FF4の出力端子Qからの出力データは、次段のスキャンフリップフロップ回路SFF3のスキャン入力端子SINに入力される。

[0021]

50

40

20

30

40

50

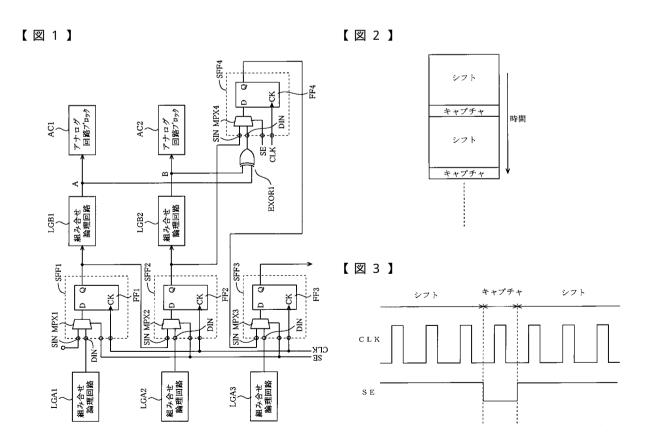

次に、上述したスキャンテスト回路の動作について図1、図2、図3を参照しながら説明する。図2はスキャンテスト回路における動作モードを時系列的に示す図である。図3は、D型フリップフロップ回路FF1,FF2,FF3、FF4のクロック入力端子CKに入力されるクロックCLKの波形図である。

[0022]

スキャンイネーブル信号SEがローレベルのとき、スキャンテスト回路はキャプチャモードに設定される。即ち、スキャンフリップフロップ回路SFF1のマルチプレクサMPX1は、組み合せ論理回路LGA1からの出力データを選択し、スキャンフリップフロップ回路SFF2のマルチプレクサMPX2は、組み合せ論理回路LGA2からの出力データを選択し、スキャンフリップフロップ回路SFF3のマルチプレクサMPX3は組み合せ論理回路LGA3からの出力データを選択する。そして、クロックCLKの立ち上がりに同期して、組み合せ論理回路LGA1,LGA2,LGA3からの出力データが、D型フリップフロップ回路FF1,FF2,FF3に取り込まれ、かつ保持される。

[0023]

また、D型フリップフロップ回路FF1,FF2に保持されたデータは、次段の組み合せ論理回路LGB1,LGB2にそれぞれ出力され、組み合せ論理回路LGB1,LGB2は観測ポイントA,Bにそれぞれ演算結果である出力データを出力する。組み合せ論理回路LGB1,LGB2の出力データは、それぞれ排他的論理和回路EXOR1に入力される。そして、スキャンフリップフロップ回路SFF4のマルチプレクサMPX4は排他的論理和回路EXOR1の出力データを選択する。したがって、排他的論理和回路EXOR1の出力データは、D型フリップフロップ回路FF4に取り込まれ、かつ保持される。

[0024]

ここで、組み合せ論理回路LGB1,LGB2の出力データをそれぞれ排他的論理和回路EXOR1に入力しているのは、排他的論理和回路EXOR1は、オア回路やアンド回路に比してデータの観測性に優れているからである。即ち、例えば2入力のアンド回路では1つの入力データ値が「0」であると、もう1つの入力データ値が「0」か「1」を問わず、その出力データは「0」になってしまう。これに対して、2入力の排他的論理和回路EXOR1は、2つの入力データが一致したときに「0」を出力し、2つの入力データが不一致のときに「1」を出力する。したがって、2つの入力の中、1つの入力データ値が変化したときに、その出力が変化するので、観測ポイントA,Bのデータ変化をより高精度に検出することができる。

[0025]

その後、スキャンイネーブル信号SEがハイレベルに変化すると、スキャンテスト回路はシフトモードに設定される。即ち、スキャンフリップフロップ回路SFF2のマルチプレクサMPX2はスキャンフリップフロップ回路SFF1の出力データを選択し、スキャンフリップフロップ回路SFF4のマルチプレクサMPX4はスキャンフリップフロップ回路SFF3のマルチプレクサMPX3はスキャンフリップフロップ回路SFF3のマルチプレクサMPX3はスキャンフリップフロップ回路SFF4の出力データを選択する。

[0026]

これにより、Dフリップフロップ回路FF1,FF2,FF4,FF3はチェーン状に接続されてシフトレジスタを構成する。したがって、クロック入力端子CKから入力されるクロックCLKに同期して、Dフリップフロップ回路FF1,FF2,FF4,FF3に保持されているデータが順次シフトされていく。本実施形態では、4つのスキャンフリップフロップ回路によってスキャンチェーンが形成されるが、実際のLSIでは数千~数万個のスキャンフリップフロップ回路によってスキャンチェーンが形成される。

[0027]

そして、最終段のスキャンフリップフロップ回路の出力がLSIの出力端子から出力される。これにより、各フリップフロップの保持されたデータを前記出力端子において時系列的に観測することができる。そして、本実施形態によれば、従来は観測できなかった組み合せ論理回路LGB1,LGB2の出力データは、キャプチャ動作によって排他的論理

和回路EXOR1を介してスキャンフリップフロップ回路SFF4に取り込まれるので、 上述のシフトレジスタのシフト動作によって観測することが可能となる。

#### [0028]

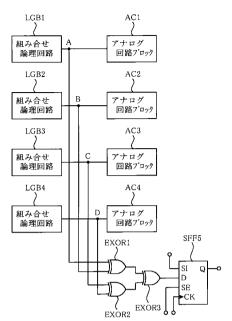

次に、本発明の第2の実施形態に係るスキャンテスト回路について説明する。上述の第1の実施形態では、2つの組み合わせ論理回路LGB1,LGB2の出力データを観測するものであるが、本実施形態のスキャンテスト回路は4つの組み合わせ論理回路の出力データを観測するものである。図4に示すように、4つの組み合わせ論理回路LGB1,LGB2,LGB3,LGB4が設けられ、これらの組み合わせ論理回路LGB1,LGB2,LGB3,LGB4の出力データはそれぞれアナログ回路ブロックAC1,AC2,AC3,AC4に出力される。

[0029]

そして、組み合せ論理回路LGB1,LGB2の出力データ(観測ポイントA,B)はそれぞれ排他的論理和回路EXOR1に入力され、組み合せ論理回路LGB3,LGB4の出力データ(観測ポイントC,D)はそれぞれ排他的論理和回路EXOR2に入力される。2つの排他的論理和回路EXOR3に入力される。

[0030]

そして、排他的論理和回路EXOR3の出力データは、追加されたスキャンフリップフロップ回路SFF5のデータ入力端子DINに入力される。スキャンフリップフロップ回路SFF4と同様の構成を有しており、組み合わせ論理回路LGB1,LGB2,LGB3,LGB4に対応して設けられた不図示のスキャンフリップフロップ回路が形成するシフトレジスタに組み込まれる。

[0031]

本実施形態によれば、組み合わせ論理回路LGB1,LGB2,LGB3,LGB4の出力データの1つが変化すると、排他的論理和回路EXOR3の出力データが変化するので、組み合わせ論理回路LGB1,LGB2,LGB3,LGB4の出力データを小規模な回路で効率よく観測することができる。

[0032]

また、観測したい組み合わせ論理回路の数がさらに増えた場合には、同様に、複数の排他的論理和回路の中、2つの組み合わせ論理回路をペアとして、複数ペアを構成し、1つのペアの2つの出力データを1つの排他的論理和回路に入力する。そして、そのようにして構成した複数の排他的論理和回路の出力をそれぞれ1つの排他的論理和回路に入力し、その1つの他的論理和回路の出力データを追加されたスキャンフリップフロップ回路のデータ入力端子DINに入力すればよい。

【図面の簡単な説明】

[0033]

【図1】本発明の第1の実施形態に係るスキャンテスト回路を示す回路図である。

【 図 2 】 本発明の第 1 の実施形態に係るスキャンテスト回路における動作モードを示す図 である。

【図3】本発明の第1の実施形態に係るスキャンテスト回路のクロック波形図である。

【 図 4 】 本 発 明 の 第 2 の 実 施 形 態 に 係 る ス キ ャ ン テ ス ト 回 路 を 示 す 回 路 図 で あ る 。

【図5】従来例に係るスキャンテスト回路を示す回路図である。

【符号の説明】

[ 0 0 3 4 ]

LGA1~LGA3、LGB1~LGB4 組み合せ論理回路

AC1~AC4 アナログ回路ブロック

SFF1~SFF5 スキャンフリップフロップ回路

$MPX1 \sim MPX4$   $\forall u \in \mathcal{I}$

MPX2 第2のマルチプレクサ

10

20

30

40

50

M P X 3 第 3 のマルチプレクサ F F 1 ~ F F 4 D型フリップフロップ回路 E X O R 1 ~ E X O R 3 排他的論理和回路

# 【図4】

# 【図5】