#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

#

# (10) International Publication Number WO 2011/055638 A1

### (43) International Publication Date 12 May 2011 (12.05.2011)

(51) International Patent Classification: H01L 27/146 (2006.01) G06F 3/041 (2006.01) G02F 1/133 (2006.01) H01L 29/786 (2006.01) G02F 1/1333 (2006.01)

(21) International Application Number:

PCT/JP2010/068649

(22) International Filing Date:

15 October 2010 (15.10.2010)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

JP

2009-255452 6 November 2009 (06.11.2009) (71) Applicant (for all designated States except US): SEMI-CONDUCTOR ENERGY LABORATORY CO., LTD.

[JP/JP]; 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): KUROKAWA, Yoshiyuki [JP/JP]; c/o SEMICONDUCTOR ENERGY LABORATORY CO., LTD., 398, Hase, Atsugi-shi, Kanagawa, 2430036 (JP). IKEDA, Takayuki. TAMU-RA, Hikaru. YAMAZAKI, Shunpei.

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: DISPLAY DEVICE

(57) Abstract: The display device has a display panel where a photosensor and a transistor including an oxide semiconductor layer are arranged. The display device detects a shadow of the object, which is projected on the display panel when the object approaches the display panel and blocks ambient light, with a photosensor, whereby a position or motion of the object is detected. Even when the object is not in contact with the display panel, the object can be detected.

#### **DESCRIPTION**

#### **DISPLAY DEVICE**

## 5 TECHNICAL FIELD

[0001]

The technical field of the present invention relates to a display device and a driving method thereof.

#### 10 BACKGROUND ART

[0002]

In recent years, a display panel provided with a touch sensor has attracted attention. Examples of the touch sensor includes a resistive touch sensor, a capacitive touch sensor, and an optical touch sensor which are different in operation principle. An object (e.g., a pen or a finger) touches a display device, whereby data can be input to the display device.

[0003]

15

20

30

As an example of a device including such an optical touch sensor, a display device having an image capturing function, which is provided with a contact type area sensor that captures an image, is given (e.g., see Patent Document 1).

[Reference]

[0004]

[Patent Document 1] Japanese Published Patent Application No. 2001-292276

## 25 DISCLOSURE OF INVENTION

[0005]

In the case of a display panel provided with the above touch sensor as an input device, the surface of the display panel continues to be touched by an object. Therefore, the display panel gets dirty easily and has a possibility that the display quality is degraded. The display panel needs to have proper mechanical strength. Further, there is a problem in that the users of the display panel tend to be tired when the surface of the display panel is hard, for example.

[0006]

In view of the above problems, it is an objective to make it possible that a device detects a position and motion of an object even when the object is not in contact with a display panel.

5 [0007]

A circuit including a transistor is provided for a display panel having a touch sensor as an input device.

[8000]

10

15

20

When a transistor including single crystal silicon is used, the size of an area sensor is limited by the size of a single crystal silicon substrate. In other words, formation of a large area sensor or a large area sensor also serving as a display device using a single crystal silicon substrate is costly and impractical.

[0009]

On the other hand, the size of a substrate can be easily increased when a thin film transistor (TFT) including amorphous silicon is employed. However, field-effect mobility of an amorphous silicon thin film is low; thus, there is a limit on a circuit design; therefore, an area occupied by a circuit is increased.

[0010]

Further, thin film transistors including polycrystalline silicon are formed in many cases by employing a method with which crystallization is performed by excimer laser annealing and therefore vary in their characteristics because of excimer laser annealing. Therefore, it is difficult to generate intensity distribution of detected light into electrical signals with high reproducibility with a photosensor using circuits including thin film transistors which vary in their characteristics.

25 [0011]

An object of an embodiment of the present invention is to provide a display panel including as an input device a touch sensor which can be mass-produced over a large substrate and has uniform and stable electric characteristics.

[0012]

Another object of an embodiment of the present invention is to provide a display device including a highly-functional touch sensor capable of fast response as an input device.

[0013]

A display device including a touch sensor as an input device is provided with a circuit having a transistor including an oxide semiconductor layer.

[0014]

5

10

15

20

25

30

However, a difference from the stoichiometric composition in the oxide semiconductor arises in a thin film formation process. For example, electric conductivity of the oxide semiconductor changes due to the excess or deficiency of oxygen. Further, hydrogen or moisture that enters the oxide semiconductor thin film during the formation of the thin film forms an oxygen (O)-hydrogen (H) bond and serves as an electron donor, which is a factor of changing electric conductivity. Furthermore, since the O-H bond is a polar molecule, it serves as a factor of varying the characteristics of an active device such as a thin film transistor manufactured using an oxide semiconductor.

[0015]

In order to prevent variation in electric characteristics of the thin film transistor including an oxide semiconductor layer, which is disclosed in this specification, impurities such as hydrogen, moisture, a hydroxyl group, or a hydride (also referred to as a hydrogen compound) which cause the variation are intentionally removed from the oxide semiconductor layer. Additionally, the oxide semiconductor layer is highly purified to become i-type (intrinsic) by supplying oxygen which is a major component of an oxide semiconductor, which is simultaneously reduced in a step of removing impurities.

[0016]

Therefore, it is preferable that the oxide semiconductor contains hydrogen and carriers as little as possible. In the thin film transistor disclosed in this specification, a channel formation region is formed in the oxide semiconductor layer, in which hydrogen contained in the oxide semiconductor is set less than or equal to  $5 \times 10^{19}$  /cm<sup>3</sup>, preferably, less than or equal to  $5 \times 10^{18}$  /cm<sup>3</sup>, more preferably, less than or equal to  $5 \times 10^{17}$  /cm<sup>3</sup> or less than  $5 \times 10^{16}$  /cm<sup>3</sup>; hydrogen contained in the oxide semiconductor is removed as much as possible to be close to 0; and the carrier concentration is less than  $5 \times 10^{14}$  /cm<sup>3</sup>, preferably, less than or equal to  $5 \times 10^{12}$  /cm<sup>3</sup>.

[0017]

5

10

15

20

25

30

It is preferable that an off-state current be as small as possible in reverse characteristics of a thin film transistor. An off-state current (also referred to as a leakage current) is a current that flows between a source and a drain of a thin film transistor in the case where a given gate voltage between -1 V to -10 V is applied. A current value per 1 µm in a channel width (w) of a thin film transistor including an oxide semiconductor, which is disclosed in this specification, is less than or equal to 100 aA/µm, preferably, less than or equal to 10 aA/µm, more preferably, less than or equal to 1 aA/µm. Further, since there is no pn junction and no hot carrier degradation, electric characteristics of the thin film transistor is not adversely affected.

The above concentration range of hydrogen can be obtained by secondary ion mass spectrometry (SIMS) or on the basis of data of SIMS. In addition, the carrier concentration can be measured by Hall effect measurement. As an example of an equipment used for Hall effect measurement, the specific resistance/hole measuring system ResiTest 8310 (manufactured by TOYO Corporation) can be given. With the specific resistance/Hall measuring system ResiTest 8310, the direction and strength of a magnetic field are changed in a certain cycle and in synchronization therewith, only a Hall electromotive voltage caused in a sample is detected, so that AC (alternate current) Hall measurement can be performed. Even in the case of a material with low mobility and high resistivity, a Hall electromotive voltage can be detected.

As the oxide semiconductor layer used in this specification, any of a four-component metal oxide such as an In-Sn-Ga-Zn-O film, a three-component metal oxide such as an In-Ga-Zn-O film, an In-Sn-Zn-O film, an In-Al-Zn-O film, a Sn-Ga-Zn-O film, an Al-Ga-Zn-O film, and a Sn-Al-Zn-O film, or a two-component metal oxide such as an In-Zn-O film, a Sn-Zn-O film, an Al-Zn-O film, a Zn-Mg-O film, a Sn-Mg-O film, and an In-Mg-O film, or a one-component metal oxide such as an In-O film, a Sn-O film, and a Zn-O film can be used. Further, SiO<sub>2</sub> may be contained in the above oxide semiconductor layer.

[0020]

Note that as the oxide semiconductor layer, a thin film expressed by  $InMO_3(ZnO)_m$  (m > 0) can be used. Here, M represents one or more metal elements selected from Ga, Al, Mn, and Co. For example, M can be Ga, Ga and Al, Ga and Mn, Ga and Co, or the like. An oxide semiconductor layer whose composition formula is represented by  $InMO_3$  ( $ZnO)_m$  (m > 0), which includes Ga as M, is referred to as the In-Ga-Zn-O oxide semiconductor described above, and a thin film of the In-Ga-Zn-O oxide semiconductor is also referred to as an In-Ga-Zn-O-based non-single-crystal film. [0021]

According to an embodiment, a display device has a display panel where a photosensor and a thin film transistor including an oxide semiconductor layer are arranged. The display device detects a shadow projected on the display panel when the object approaches the display panel and blocks ambient light. A position or motion of the shadow is detected, whereby a position or motion of the object is detected.

[0022]

According to another embodiment, a display device has a display panel where a photosensor and a thin film transistor including an oxide semiconductor layer are arranged. The display device detects light emitted from the display panel and reflected by an object with the photosensor when the object approaches the display panel. That is, when an image of a contactless object is shot by the photosensor, a position or motion of the object is detected.

[0023]

5

10

15

20

25

30

Thus, even in the case where an object is not in contact with a display panel, the object can be detected.

[0024]

Another embodiment is a display device having a display panel where pixels each including a photosensor and a thin film transistor including an oxide semiconductor layer are arranged in matrix; and an image processing portion. The display device has a function of detecting a contactless object. The photosensor is configured to detect a shadow of an object projected on the display panel. The image processing portion is configured to detect a position of the object on the basis of a position of the shadow of the object, and motion of the object on the basis of motion of the shadow.

[0025]

5

10

15

20

30

Another embodiment is a display device having a display panel where pixels each including a photosensor and a thin film transistor including an oxide semiconductor layer are arranged in matrix; and an image processing portion. The display device has a function of detecting a contactless object. The photosensor is configured to detect a shadow of an object projected on the display panel. The image processing portion is configured to detect a position of the object on the basis of a position of the shadow of the object, and motion of the object on the basis of motion of the shadow. The image processing portion is configured to recognize a region including the largest number of pixels detecting the shadow among a plurality of regions obtained by dividing the display panel, as positional data of the object.

Another embodiment is a display device having a display panel where pixels each including a photosensor and a thin film transistor including an oxide semiconductor layer are arranged in matrix; and an image processing portion. The display device has a function of detecting a contactless object. The photosensor is configured to detect a shadow of an object projected on the display panel. The image processing portion is configured to detect a position of the object on the basis of a position of the shadow of the object, and motion of the object on the basis of motion of the shadow. The image processing portion is configured to recognize a region including the largest number of pixels detecting the shadow among a plurality of regions obtained by dividing the display panel, as positional data of the object. The image processing portion is configured to detect the motion of the object by comparing the successive positional data.

25 [0027]

Another embodiment is a display device having a display panel including a photodetection portion where pixels each include a first photosensor and a first thin film transistor including an oxide semiconductor layer and an area sensor where pixels each include a second photosensor and a second thin film transistor including an oxide semiconductor layer; and an image processing portion. The display device has a function of detecting a contactless object. The first photosensor is configured to detect a shadow of an object projected on the display panel. The image processing portion is

configured to detect a position of the object on the basis of a position of the shadow of the object, and motion of the object on the basis of motion of the shadow.

[0028]

Another embodiment is a display device having a display panel including a photodetection portion where pixels each include a first photosensor and a first thin film transistor including an oxide semiconductor layer and an area sensor where pixels each include a second photosensor and a second thin film transistor including an oxide semiconductor layer; and an image processing portion. The display device has a function of detecting a contactless object. The first photosensor is configured to detect a shadow of an object projected on the display panel. The image processing portion is configured to detect a position of the object on the basis of a position of the shadow of the object, and motion of the object on the basis of motion of the shadow. The image processing portion is configured to recognize a region including the largest number of pixels detecting the shadow among a plurality of regions obtained by dividing the display panel, as positional data of the object.

[0029]

5

10

15

20

25

30

Another embodiment is a display device having a display panel including a photodetection portion where pixels each include a first photosensor and a first thin film transistor including an oxide semiconductor layer and an area sensor where pixels each include a second photosensor and a second thin film transistor including an oxide semiconductor layer; and an image processing portion. The display device has a function of detecting a contactless object. The first photosensor is configured to detect a shadow of an object projected on the display panel. The image processing portion is configured to detect a position of the object on the basis of a position of the shadow of the object, and motion of the object on the basis of motion of the shadow. The image processing portion is configured to recognize a region including the largest number of pixels detecting the shadow among a plurality of regions obtained by dividing the display panel, as positional data of the object. The image processing portion is configured to detect the motion of the object by comparing the successive positional data.

[0030]

Another embodiment is a display device having a display panel including a

photodetection portion where pixels each include an infrared light sensor and a thin film transistor including an oxide semiconductor layer and an area sensor where pixels each include a visible light sensor. The photodetection portion is configured to detect light emitted from the display panel and reflected by an object when the object is not in contact with the display panel. The area sensor is configured to detect light emitted from the display panel and reflected by the object when the object is in contact with the display panel.

[0031]

5

In the above structure, the number of the second photosensors is larger than that of the first photosensors.

[0032]

In the above structure, the second photosensors are provided on the periphery of the first photosensor.

[0033]

When a contactless object can be detected, the frequency at which the object touches a display panel can be reduced and thus degradation in display quality can be prevented.

[0034]

20

With a thin film transistor including an oxide semiconductor layer, a display device including a highly-functional touch panel capable of fast response as an input device can be provided.

#### **BRIEF DESCRIPTION OF DRAWINGS**

[0035]

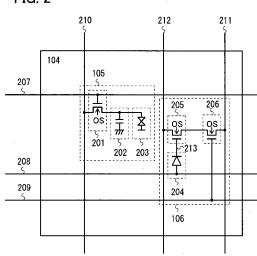

FIG. 1 illustrates a structure of a display panel.

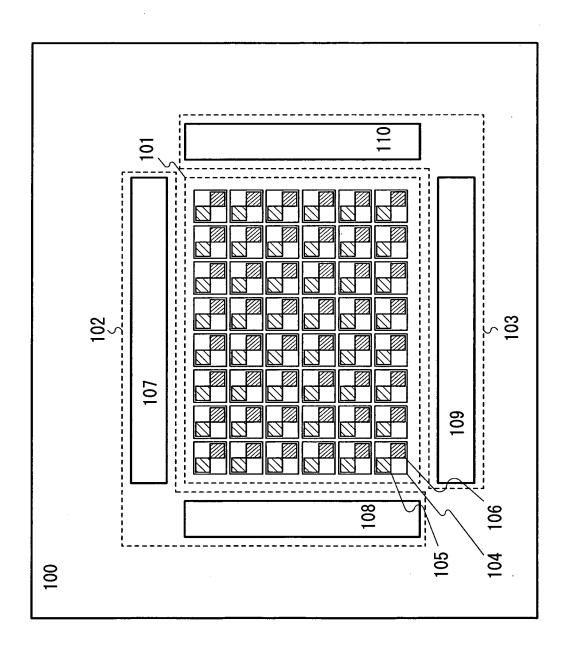

FIG. 2 illustrates a structure of a display panel.

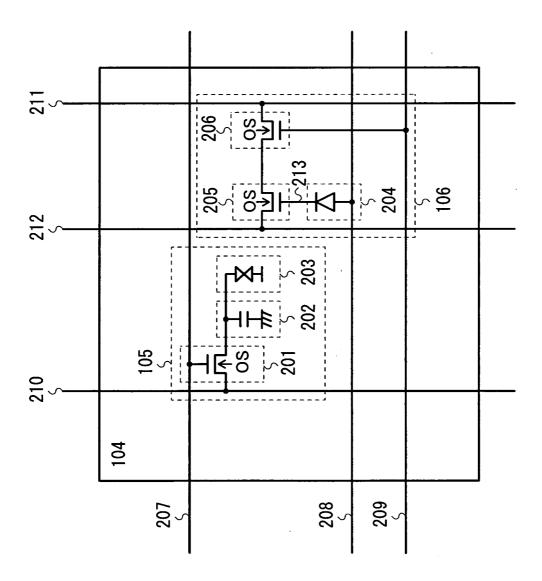

FIG. 3 illustrates a structure of a display panel.

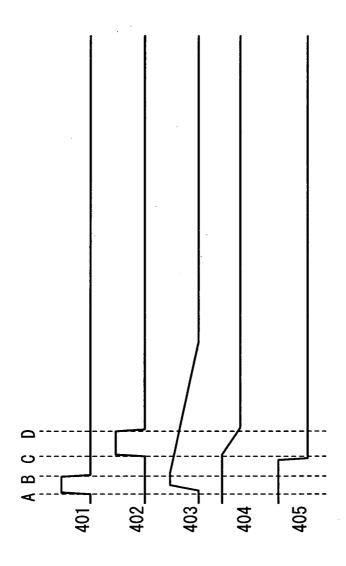

FIG. 4 is a timing chart.

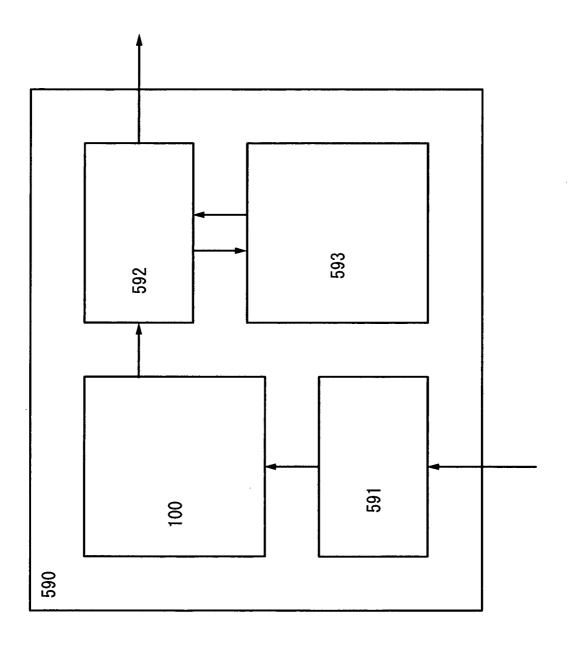

FIG. 5 illustrates a structure of a display panel.

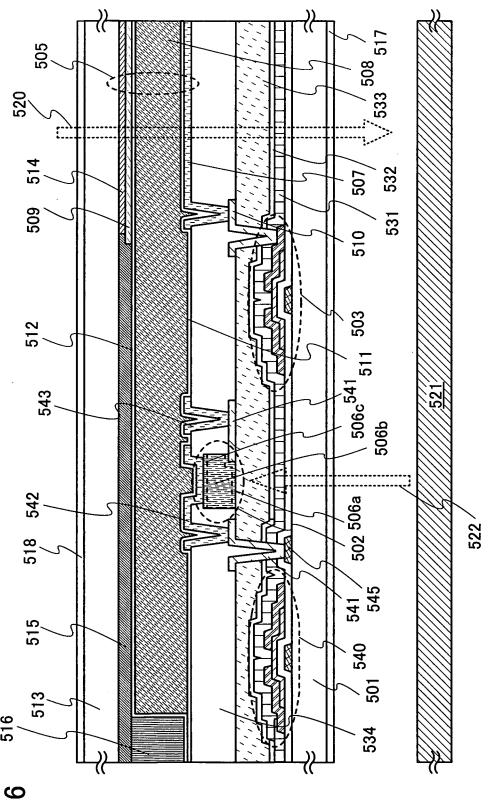

FIG. 6 is a cross-sectional view of a display panel.

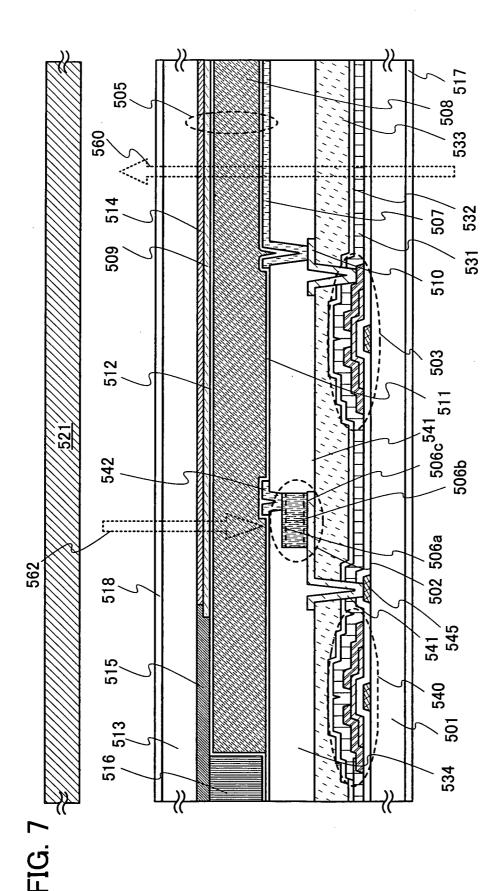

FIG. 7 is a cross-sectional view of a display panel.

FIG. 8 illustrates a structure of a display panel.

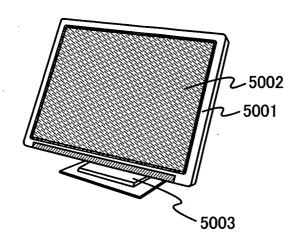

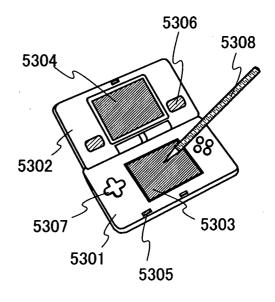

FIGS. 9A to 9D each illustrate an example of an electronic device having a display panel.

PCT/JP2010/068649

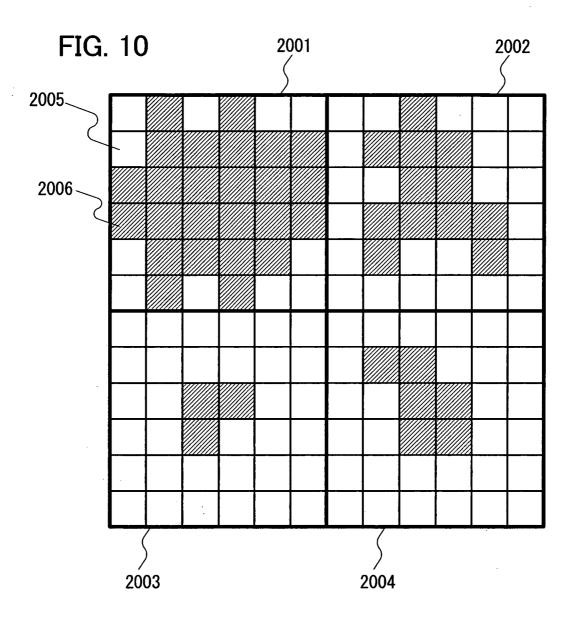

FIG. 10 illustrates an image processing.

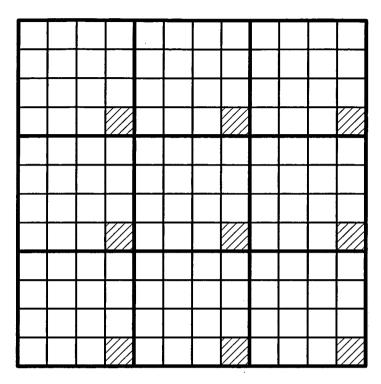

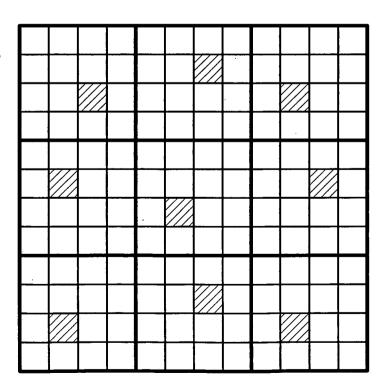

FIGS. 11A and 11B illustrate an image processing.

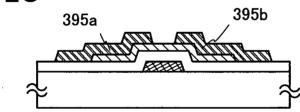

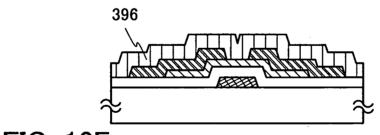

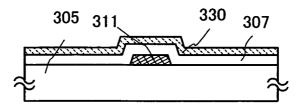

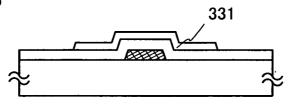

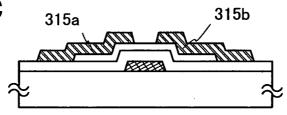

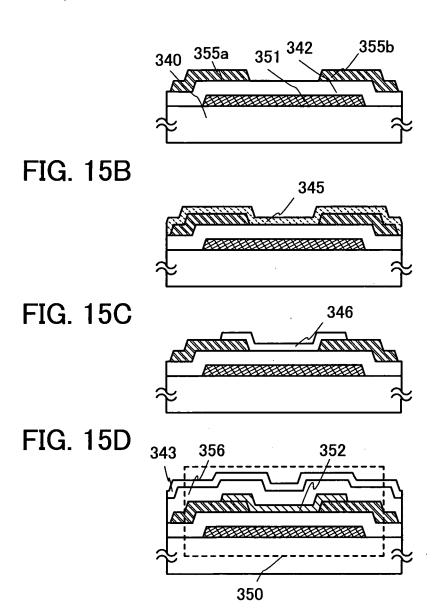

FIGS. 12A to 12E illustrate a thin film transistor and a method for manufacturing the thin film transistor.

FIGS. 13A to 13E illustrate a thin film transistor and a method for manufacturing the thin film transistor.

FIGS. 14A to 14D illustrate a thin film transistor and a method for manufacturing the thin film transistor.

FIGS. 15A to 15D illustrate a thin film transistor and a method for manufacturing the thin film transistor.

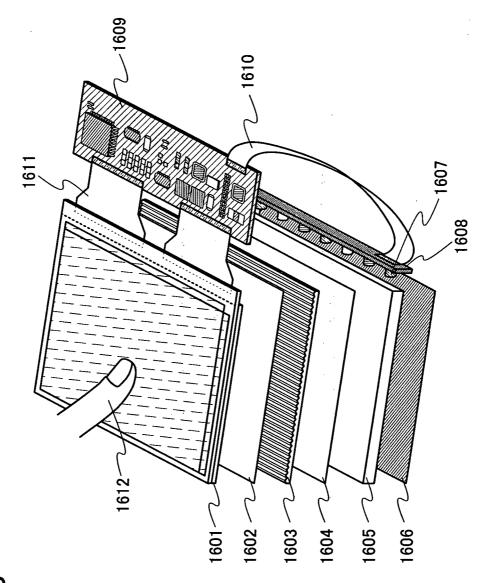

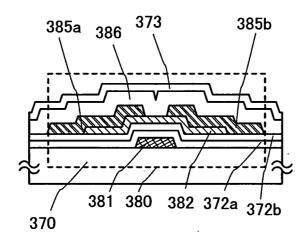

FIG. 16 illustrates a thin film transistor.

FIG. 17 illustrates a thin film transistor.

FIG. 18 is a longitudinal cross-sectional view of an inverted staggered thin film transistor including an oxide semiconductor.

FIG. 19A is an energy band diagram (schematic diagram) of a cross section along A-A' in FIG. 18, and FIG. 19B is an energy band diagram at the time when a voltage is applied.

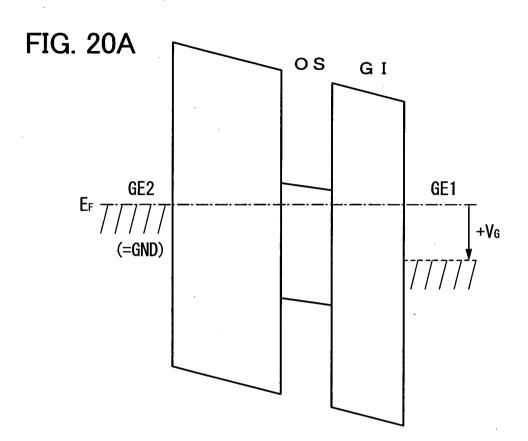

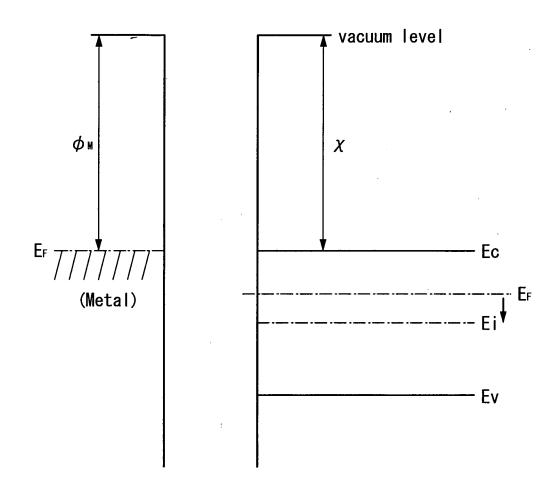

FIG. 20A is an energy band diagram illustrating a state in which positive potential  $(+V_G)$  is applied to a gate (G1), and FIG 20B is an energy band diagram illustrating a state in which negative potential  $(-V_G)$  is applied to a gate (G1).

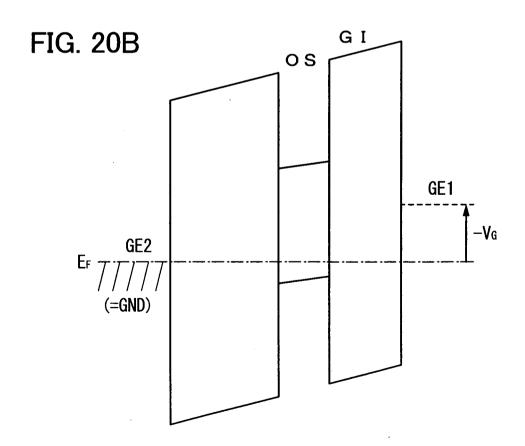

FIG. 21 is an energy band diagram illustrating relationships between a vacuum level and a work function of a metal  $(\phi M)$  and between the vacuum level and electron affinity  $(\chi)$  of an oxide semiconductor.

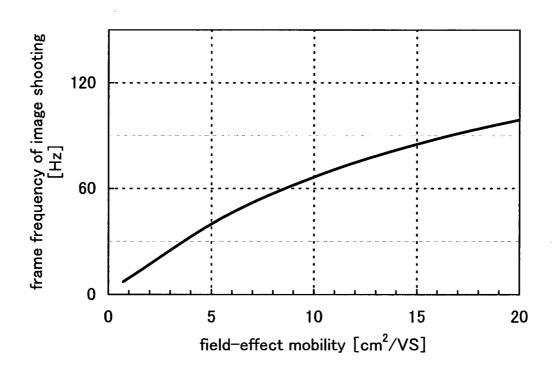

FIG. 22 is a graph showing a relationship between field-effect mobility of a transistor and a frame frequency of image shooting, which is obtained by calculation.

## BEST MODE FOR CARRYING OUT THE INVENTION

30 [0036]

5

10

15

20

25

Hereinafter, embodiments will be described in detail with reference to the

accompanying drawings. However, since embodiments described below can be embodied in many different modes, it is easily understood by those skilled in the art that the mode and the detail can be variously changed without departing from the scope of the present invention. Therefore, the disclosed invention should not be interpreted as being limited to the following description of the embodiments. In the drawings for describing the embodiments, the same parts or parts having a similar function are denoted by the same reference numerals, and description of such parts is not repeated. [0037]

(Embodiment 1)

In this embodiment, a display panel will be described with reference to FIG. 1, FIG. 2, FIG. 3, FIG. 4, and FIG. 5.

[0038]

5

10

15

20

25

30

A structure of the display panel will be described with reference to FIG. 1. A display panel 100 includes a pixel circuit 101, a display element control circuit 102, and a photosensor control circuit 103. The pixel circuit 101 includes a plurality of pixels 104 arranged in a matrix of rows and columns. Each of the pixels 104 includes a display element 105 and a photosensor 106.

[0039]

Each of the display elements 105 includes a thin film transistor (TFT), a storage capacitor, a liquid crystal element including a liquid crystal layer, and the like. The thin film transistor has a function of controlling injection or ejection of charge to/from the storage capacitor. The storage capacitor has a function of holding charge which corresponds to voltage applied to the liquid crystal layer. Taking advantage of the change in the direction of a polarization due to a voltage application to the liquid crystal layer, tone of light passing through the liquid crystal layer is made (gray scale display is performed), so that image display is realized. Light that a light source (a backlight) emits from the rear side of a liquid crystal display device is used as the light passing through the liquid crystal layer.

Note that the case where the display elements 105 include liquid crystal elements is described; however, other elements such as light-emitting elements may be included. The light-emitting element is an element in which the luminance is

controlled by current or voltage. Specifically, a light emitting diode, an EL element (organic EL element (organic light emitting diode (OLED) or an inorganic EL element), and the like are given.

[0041]

5

10

15

20

25

30

The photosensors 106 each include an element such as a photodiode, which has a function of generating an electrical signal when receiving light, and a thin film transistor. Note that as light which is received by the photosensors 106, ambient light is used in the case where image shooting data of a shadow of an object is detected, whereas reflected light obtained when light from a backlight is delivered to an object is used in the case where image shooting data of the object itself is detected.

[0042]

The display element control circuit 102 controls the display elements 105 and includes a display element driver circuit 107 and a display element driver circuit 108. The display element driver circuit 107 inputs a signal to the display elements 105 through signal lines (also referred to as "source signal lines") such as video data signal lines. The display element driver circuit 108 inputs a signal to the display elements 105 through scan lines (also referred to as "gate signal lines"). For example, the display element driver circuit 108 for driving the scan lines has a function of selecting display elements 105 included in the pixels placed in a particular row. Further, the display element driver circuit 107 for driving the signal lines has a function of giving a predetermined potential to the display elements 105 included in the pixels placed in the selected row. Note that in the display elements to which the display element driver circuit 108 for driving the scan lines gives a high potential, the thin film transistors are brought into conduction and charges given by the display element driver circuit 107 for driving the signal lines are supplied to the display elements.

[0043]

The photosensor control circuit 103 controls the photosensor 106 and includes a photosensor readout circuit 109 connected to a photosensor output signal line and a photosensor reference signal line, and a photosensor driver circuit 110. The photosensor driver circuit 110 has a function of performing reset operation and selecting operation on the photosensors 106 included in the pixels placed in a particular row, which are described below. Further, the photosensor readout circuit 109 has a function

of taking out output signals of the photosensors 106 included in the pixels in the selected row. Note that the photosensor readout circuit 109 may have a configuration in which an output, which is an analog signal, of the photosensor is extracted as an analog signal to the outside of the display panel by an OP amplifier; or a configuration in which the output is converted into a digital signal by an A/D converter circuit and then extracted to the outside of the display panel.

[0044]

[0046]

The display panel 100 including a photosensor is provided with a circuit having a transistor including an oxide semiconductor layer.

10 [0045]

5

15

20

25

30

In order to prevent variation in electric characteristics of the thin film transistor including an oxide semiconductor layer, which is included in the display panel 100 including a photosensor, impurities such as hydrogen, moisture, a hydroxyl group, or a hydride (also referred to as a hydrogen compound) which cause the variation are intentionally removed from the oxide semiconductor layer. Additionally, the oxide semiconductor layer is highly purified to become i-type (intrinsic) by supplying oxygen which is a major component of an oxide semiconductor, which is simultaneously reduced in a step of removing impurities.

Therefore, it is preferable that the oxide semiconductor contains hydrogen and carriers as little as possible. In the thin film transistor disclosed in this specification, a channel formation region is formed in the oxide semiconductor layer, in which hydrogen contained in the oxide semiconductor is set less than or equal to  $5 \times 10^{19} / \text{cm}^3$ , preferably, less than or equal to  $5 \times 10^{18} / \text{cm}^3$ , more preferably, less than or equal to  $5 \times 10^{17} / \text{cm}^3$  or less than  $5 \times 10^{16} / \text{cm}^3$ ; hydrogen contained in the oxide semiconductor is removed as much as possible to be close to 0; and the carrier concentration is less than  $5 \times 10^{14} / \text{cm}^3$ , preferably, less than or equal to  $5 \times 10^{12} / \text{cm}^3$ .

It is preferable that an off-state current be as small as possible in reverse characteristics of a thin film transistor. An off-state current is a current that flows between a source and a drain of a thin film transistor in the case where a given gate voltage between -1 V to -10 V is applied. A current value per 1  $\mu$ m in a channel width (w) of a thin film transistor including an oxide semiconductor, which is disclosed in this specification, is less than or equal to 100 aA/ $\mu$ m, preferably, less than or equal to 10 aA/ $\mu$ m. Further, since there is no pn junction and no hot carrier degradation, electric characteristics of the thin film transistor is not adversely affected.

[0048]

5

10

15

20

25

30

A circuit diagram of the pixel 104 will be described with reference to FIG. 2. The pixel 104 includes the display element 105 including a transistor 201, a storage capacitor 202, and a liquid crystal element 203; and the photosensor 106 including a photodiode 204, a transistor 205, and a transistor 206. In FIG. 2, the transistor 201, the transistor 205, and the transistor 206 are each a thin film transistor including an oxide semiconductor layer.

[0049]

A gate of the transistor 201 is electrically connected to a gate signal line 207, one of a source and a drain of the transistor 201 is electrically connected to a video data signal line 210, and the other of the source and the drain of the transistor 201 is electrically connected to one electrode of the storage capacitor 202 and one electrode of the liquid crystal element 203. The other electrode of the storage capacitor 202 and the other electrode of the liquid crystal element 203 are each held at a certain potential. The liquid crystal element 203 is an element including a pair of electrodes and a liquid crystal layer interposed between the pair of electrodes.

When a potential at a high level "H" is applied to the gate signal line 207, the transistor 201 applies the potential of the video data signal line 210 to the storage capacitor 202 and the liquid crystal element 203. The storage capacitor 202 holds the applied potential. The liquid crystal element 203 changes light transmittance in accordance with the applied potential.

[0051]

Since the off-state currents of the transistors 201, 205, and 206 which are each a thin film transistor including an oxide semiconductor layer are extremely small, a

storage capacitor can be extremely small or is not necessarily provided. [0052]

One electrode of the photodiode 204 is electrically connected to a photodiode reset signal line 208, and the other electrode of the photodiode 204 is electrically connected to a gate of the transistor 205. One of a source and a drain of the transistor 205 is electrically connected to a photosensor reference signal line 212, and the other of the source and the drain of the transistor 205 is electrically connected to one of a source and a drain of the transistor 206. A gate of the transistor 206 is electrically connected to a gate signal line 209, and the other of the source and the drain of the transistor 206 is electrically connected to a photosensor output signal line 211.

[0053]

5

10

15

20

25

30

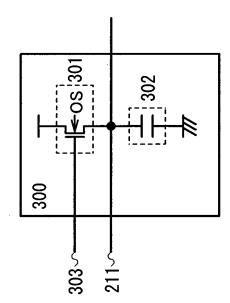

Next, a configuration of the photosensor readout circuit 109 will be described with reference to FIG. 3. In FIG. 3, a photosensor readout circuit 300 of one column of the pixels includes a transistor 301 and a storage capacitor 302. In addition, the photosensor output signal line 211 of the column of pixels and a precharge signal line 303 are provided.

[0054]

Note that in the circuit configurations in this specification, a thin film transistors including an oxide semiconductor layer are each denoted by a symbol "OS" so that they can be identified as a thin film transistors including an oxide semiconductor layer. In FIG. 2, the transistor 201, the transistor 205, and the transistor 206 are each a thin film transistor including an oxide semiconductor layer. In FIG. 3, the transistor 301 is a thin film transistor including an oxide semiconductor layer.

[0055]

In the circuit 300, the potential of the photosensor output signal line 211 is set to a reference potential before operation of the photosensor in the pixel. The reference potential set for the photosensor output signal line 211 may be a high potential or a low potential. In FIG. 3, by setting a potential of the precharge signal line 303 at a high level "H", the potential of the photosensor output signal line 211 can be set to a high potential which is a reference potential. Note that the storage capacitor 302 is not necessarily provided in the case where the parasitic capacitance of the photosensor output signal line 211 is large.

[0056]

Next, readout operation of the photosensor in the display panel is described with reference to a timing chart of FIG. 4. In FIG. 4, a signal 401, a signal 402, a signal 403, and a signal 404 respectively correspond to the potential of the photodiode reset signal line 208, the potential of the gate signal line 209 to which the gate of the transistor 206 is connected, the potential of the gate signal line 213 to which the gate of the transistor 205 is connected, and the potential of the photosensor output signal line 211 in FIG. 2. In addition, a signal 405 corresponds to the potential of the precharge signal line 303 in FIG. 3.

10 [0057]

5

15

25

30

In a time A, when the potential of the photodiode reset signal line 208 (the signal 401) is set at the potential "H", in other words, the potential of the photodiode reset signal line which is electrically connected to the photodiode is set so that a forward bias is applied to the photodiode (reset operation), the photodiode 204 is brought into conduction and the potential of the gate signal line 213 (the signal 403) to which the gate of the transistor 205 is connected is set at the potential "H". In addition, when the potential of the precharge signal line 303 (the signal 405) is set at the potential "H", the potential of the photosensor output signal line 211 (the signal 404) is precharged to the potential "H".

20 [0058]

In a time B, when the potential of the photodiode reset signal line 208 (the signal 401) is set at the potential "L" (accumulating operation), the potential of the gate signal line 213 to which the gate of the transistor 205 is connected (the signal 403) begins to be lowered due to an off current of the photodiode 204. The off current of the photodiode 204 increases when light is delivered; therefore, the potential of the gate signal line 213 to which the gate of the transistor 205 is connected (the signal 403) varies depending on the amount of delivered light. That is, a current between the source and the drain of the transistor 205 varies.

In a time C, when the potential of the gate signal line 209 (the signal 402) is set at the potential "H" (selecting operation), the transistor 206 is brought into conduction and the photosensor reference signal line 212 and the photosensor output signal line 211

are brought into conduction through the transistor 205 and the transistor 206. Then, the potential of the photosensor output signal line 211 (the signal 404) begins to be lowered. Note that before the time C, the potential of the precharge signal line 303 (the signal 405) is set at the potential "L" and precharge of the photosensor output signal line 211 is completed. Here, the rate at which the potential of the photosensor output signal line 211 (the signal 404) is lowered depends on the current between the source and the drain of the transistor 205. That is, the potential of the photosensor output signal line 211 (the signal 404) varies in accordance with the amount of light which is delivered to the photodiode 204.

10 [0060]

5

15

20

25

30

In a time D, when the potential of the gate signal line 209 (the signal 402) is set at the potential "L", the transistor 206 is turned off, whereby the potential of the photosensor output signal line 211 (the signal 404) is kept at a fixed value after the time D. Here, the value to be the fixed value varies in accordance with the amount of light which is delivered to the photodiode 204. Therefore, the amount of light which is delivered to the photodiode 204 can be found by obtaining the potential of the photosensor output signal line 211.

[0061]

Based on the amount of light emitted to the photodiode 204 as described above, it can be determined whether ambient light is incident on the photodiode 204 or a contactless object prevents ambient light from being incident on the photodiode 204, that is, the portion where ambient light is blocked is a shadow.

[0062]

The results of circuit calculation of a frequency of image shooting in the photosensor 106 of FIG. 2 are shown in FIG. 22. FIG. 22 shows a relationship between field-effect mobility of the transistor 205 and the transistor 206 which are included in the photosensor 106 and a frame frequency of image shooting which is calculated from a reading speed.

[0063]

The circuit calculation was performed with the following conditions assumed. In a touch panel, which has a 20-inch FHD standard (1920 horizontal RGB pixels and 1080 vertical pixels), each pixel is provided with a photosensor, the parasitic

capacitance of the photosensor output signal line 211 is 20 pF (corresponds to the capacitor 302), the transistor 205 and the transistor 206 each have a channel length of 5  $\mu$ m and a channel width of 16  $\mu$ m, and the transistor 301 has a channel length of 5  $\mu$ m and a channel width of 1000  $\mu$ m. Note that a circuit simulator, Smart Spice (manufactured by Silvaco Data Systems Inc.), is used for the calculation.

The circuit calculation was performed with the following operations assumed. First, an initial state is to be a state immediately after the accumulating operation. Specifically, the potential of the gate signal line 213 is set at 8 V, the potential of the gate signal line 209 is set at 0 V, the potential of the photosensor output signal line 211 is set at 8 V, the potential of the photosensor reference signal line 212 is set at 8 V, and the potential of the precharge signal line 303 is set at 0 V. After the potential of the precharge signal line 303 and the potential of the photosensor output signal line 211 are changed to 8 V and 0 V (precharged state) respectively, the potential of the precharge signal line 303 and the potential of the gate signal line 209 are changed to 0 V and 8 V, respectively. In other words, the selecting operation is started. Note that the reference voltage is set at 0 V. After that, a final state is to be the time when the potential of the photosensor output signal line 211 is changed to 2 V, that is, the potential is changed by 2 V from the potential at the precharge operation. The time from the initial state to the final state in the operations described above is to be time for image shooting per one row.

10

15

20

25

30

[0065]

The time needed for image shooting is to be 1080 times as much as the above time for image shooting per one row, and the inverse of the time for image shooting is to be a frequency of the image shooting. As an example, the frequency of image shooting of 60 Hz means that the above time for image shooting per one row corresponds to the following equation: 1/60 [Hz] / 1080 [columns] = 15.43 [µs]. [0066]

According to the results in FIG. 22, it is found that the frequency of image shooting is 70 Hz to 100 Hz in the case where the field-effect mobility of each of the transistor 205 and the transistor 206 is set at 10 cm<sup>2</sup>/Vs to 20 cm<sup>2</sup>/Vs on the assumption

that a transistor including an oxide semiconductor is used. On the other hand, in the case where the field-effect mobility of each of the transistor 205 and the transistor 206 is set at 0.5 cm<sup>2</sup>/Vs on the assumption that a transistor including amorphous silicon is used, the frequency of image shooting is only about 5 Hz. In other words, a transistor which is included in a photosensor is effectively formed with a transistor including an oxide semiconductor.

[0067]

5

10

15

20

25

30

FIG. 5 illustrates a display panel system 590 which detects motion of a contactless object, using a shadow of the object. Here, the display panel system 590 includes a display panel 100, a control circuit 591, an image processing circuit 592, a memory device 593 which stores image data. The control circuit 591 generates various timing signals for driving the display panel. The image processing circuit 592 performs arithmetic processing on the image data of the shadow of the contactless object, which is obtained by a photosensor, and detects motion of the shadow of the object. Furthermore, the image processing circuit 592 stores image data needed in the subsequent image processing in the memory device 593, and reads the data stored in the memory device 593 and performs arithmetic processing thereon if needed.

An example of a specific method of image processing performed by the image processing circuit 592 will be described with reference to FIG. 10. In FIG. 10, a display region including  $12 \times 12$  pixels is illustrated.

[0069]

The image processing is performed as follows: (1) a position of an object is extracted from the image data of the shadow of the object; (2) motion of the object is detected from positional data of the object which are successively captured; (3) generation of input data in response to the motion of the object is performed; and the like.

[0070]

As for (1) extraction of a position of an object from the image data of the shadow of the object, the display region is divided into four areas: an area 2001, an area 2002, an area 2003, and an area 2004, for example, as frames are marked with thick lines in FIG. 10. In each area, a ratio of portions recognized as a shadow of the object

to the area is calculated. More specifically, when the amount of light obtained by the photosensor in each pixel is lower than a given threshold value, the pixel detects a shadow of the object. Note that a pixel not detecting a shadow is denoted by a reference numeral 2005 and a pixel detecting a shadow is denoted by a reference numeral 2006.

[0071]

5

10

20

25

30

Then, an area in which a ratio of the pixels over which the shadow is cast to all of the pixels is the highest of the areas 2001 to 2004 is extracted as a position of the object. In FIG. 10, the pixels detecting the shadow are marked with diagonal lines. The ratio of the pixels detecting the shadow in each area is as follows: in the area 2001, the ratio is 25/36; the area 2002, 12/36; the area 2003, 3/36; and the area 2004, 6/36. The ratio of the pixels over which the shadow is cast is the highest in the area 2001; therefore, the area 2001 is extracted as a position of the object and the positional data thereof is obtained.

15 [0072]

Note that the display region is divided into more areas, whereby the position can be extracted more precisely.

[0073]

Next, (2) detection of motion of the object from positional data of the object which are successively captured will be described more specifically: the positional data are successively obtained as described above, and then the positional data is compared with the positional data captured before and after the positional data is captured, whereby the motion of the object can be known. For example, when the last positional data is the right and the positional data of this time is the left, the object can be detected to move from right to left. Moreover, in the case where the positional data is extracted more precisely, the more precise motion such as the motion speed in addition to the direction in which the object moves can be detected.

[0074]

As for (3) generation of input data in response to the motion of the object, it is effective to preliminarily set the input data in flexible response to the motion of the object depending on the usage of the display panel. For example, the following application is possible: given that an object is a finger, when the finger moves from left

to right, a moving image is reproduced and when the finger moves from top to bottom, a moving image is stopped. Moreover, it is also effective to suppose a letter from an elaborate motion of a finger to determine it as input data.

[0075]

5

10

15

20

25

It is also effective that the sensitivity of the photosensor with respect to the amount of light is variable. In a structure in FIG. 2, for example, the potential applied to the photosensor (the potential of the photosensor reference signal line 208, the potential of the gate signal line 209, the potential of the photosensor reference signal line 212, or the potential of the precharge signal line 303) varies, so that the sensitivity to the amount of light is variable. Thus, when the sensitivity of the photosensor with respect to the amount of light is variable, the sensitivity can be set at an optimal value as appropriate depending on the environment (the brightness or the like) where the display panel is used and a shadow of a contactless object can easily be recognized. Moreover, the display panel can be used not only for detecting a shadow of a contactless object but also as a contact area sensor. That is to say, a function of detecting a contactless object and a function of detecting a touch object can be used as appropriate depending on the usage.

[0076]

With the above structure, a display panel capable of detecting even a contactless object and inputting data can be provided.

[0077]

Furthermore, the above image processing can be applied to the case of detecting light reflected by an object in addition to the case of detecting a shadow of the object. In the case of detecting reflection light, photosensors placed at a position toward which an object moves receive stronger light than those at the other positions. That is, an area, in the display region, which receives stronger light, is specified using the above image processing, whereby the position, the motion, or the shape of the object can be detected. In this case, the pixels which are marked with diagonal lines in FIG. 10 receive stronger light reflected by the object.

30 [0078]

Additionally, it is effective that a first photosensor which detects a contactless object and a second photosensor which detects a touch object are provided in the

display panel. The second photosensor is used as the contact area sensor. With such a structure, a display panel capable of detecting a contactless object and capable of detecting also a touch object can be provided. That is, two types of detection functions can be used as appropriate depending on the usage of the display panel.

[0079]

5

10

15

20

25

30

Pixels each including the first photosensor and pixels each including the second photosensor are arranged in matrix on the display panel. It is desirable that the number of second photosensors is larger than the number of first photosensors. The second photosensor serving as a contact area sensor is required to shoot a high resolution image; therefore, a distance (pitch) between the second photosensors is short, whereby the resolution can be high. On the other hand, the first photosensor detecting a shadow only need to determine the position of the object; therefore, the first photosensor is not required to have as high resolution as the second photosensor used as a contact area sensor. That is, the distance between the arranged second photosensors may be shorter than the distance between the arranged first photosensors.

[0080]

Note that pixels in each of which the first photosensor detecting a shadow is provided are pixels in each of which the second photosensor used as a contact area sensor is not provided. Therefore, photosensors serving as contact area sensors are desirably provided in about one to three pixels around photosensor detecting a shadow so that a lost image in the pixels can be restored by image processing.

[0081]

FIG. 11A illustrates an example of pixels where the first photosensors detecting a shadow and the second photosensors used as a contact area sensor are arranged. In FIGS. 11A and 11B,  $12 \times 12$  pixels are used; however, the number of pixels is not limited to this.

[0082]

[0083]

In FIG. 11A, the first photosensors are provided in pixels marked with diagonal lines, and the second photosensors are provided in the other pixels. The first photosensors are arranged at intervals. For the above reason, the number of second photosensors is larger than that of first photosensors.

Note that the first photosensors are not necessarily arranged at regular intervals as illustrated in FIG. 11A, and may be arranged at irregular intervals as illustrated in FIG. 11B. In the case where  $640 \times 480$  pixels are used as a more practical example, when the pixels are divided into areas including hundred pixels of  $10 \times 10$  pixels, a pixel of the hundred pixels is provided with the first photosensor and the ninety-nine pixels are provided with the second photosensors, which is effective enough for the device to detect a shadow of the object and to serve as a contact area sensor. However, the structure is not limited to this. The ratio of the first photosensors to the second photosensors may be determined in accordance with the detection accuracy. The number of the first photosensors can be equal to each other, for example.

[0084]

5

10

15

Note that, in the photosensor detecting a shadow and the photosensor used as a contact area sensor, it is effective to individually set a potential to be applied to each of the photosensors (e.g., the potential of the photosensor reference signal line 208, the potential of the gate signal line 209, the potential of the photosensor reference signal line 212, or the potential of the precharge signal line 303 in FIG. 2 or FIG. 3). Moreover, it is effective that the sizes of photodiodes included in the photosensors or the circuit configurations of the photosensors vary from one photosensor to another.

20 [0085]

This embodiment can be implemented in appropriate combination with any of the other embodiments and examples.

[0086]

(Embodiment 2)

In this embodiment, a method for increasing detection accuracy of a photosensor in the case of using light reflected by an object will be described.

[0087]

For detection of a contactless object, slight light reflected by the object needs to be effectively detected. Specifically, the following method is given.

30 [0088]

A structure is employed in which a sensor which detects infrared light (an

infrared light sensor) is used as a photosensor and the infrared light sensor detects infrared light emitted from a touch panel and reflected by an object. The infrared light sensor can be formed, for example, by being provided with a stack of color filters of different colors (e.g., R (red) and B (blue), or R (red) and G (green)) on a photosensor so that light (infrared light) other than visible light can be incident on the photosensor. By using color filters provided on a display panel for color display also as filters of the infrared light sensor, the number of steps can be reduced. Moreover, for example, a light source emitting infrared light in addition to visible light (white) is added to a backlight, whereby the touch panel can emit infrared light. As for infrared light, the wavelength is longer and the amount of scattering is smaller than visible light; therefore, the detection accuracy can be easily increased. The structure of detecting infrared light is effective, particularly in the case where the object is a finger or a hand. [0089]

When an infrared light sensor and a visible light sensor are formed using different materials, the infrared light sensor may be formed using a material which absorbs light (infrared light) other than visible light. For example, a photosensor formed using InGaAs, PbS, PbSe, or the like absorbs infrared light efficiently.

[0090]

In the structure described in Embodiment 1 where the first photosensor detecting a contactless object and the second photosensor detecting a touch object are provided in the display panel, an infrared light sensor is used for the first photosensor and a visible light sensor is used for the second photosensor. Accordingly, the accuracy of both a function of detecting a contactless object and a function as a contact area sensor can be improved. The first photosensors (the infrared light sensors) and the second photosensors (the visible light sensors) can be arranged in a manner similar to that of Embodiment 1.

[0091]

5

10

15

20

25

30

Moreover, the image processing described in Embodiment 1 can be adopted. [0092]

This embodiment can be implemented in appropriate combination with any of the other embodiments and examples.

[0093]

#### (Embodiment 3)

5

10

15

20

30

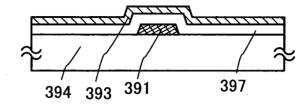

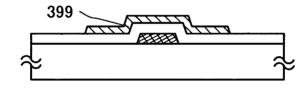

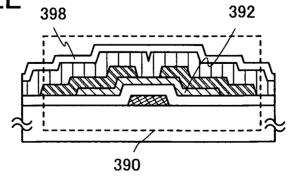

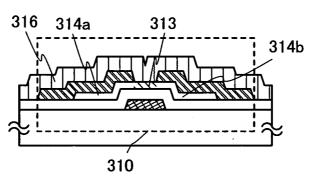

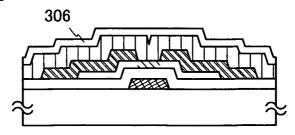

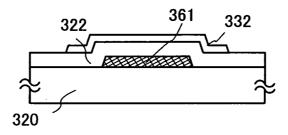

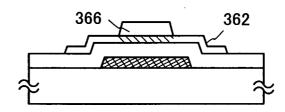

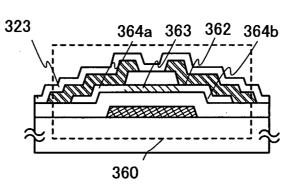

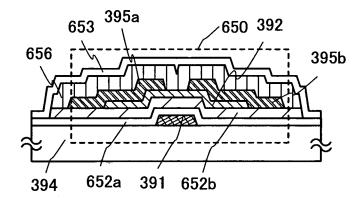

In this embodiment, a structure of a display device according to an embodiment of the present invention will be described with reference to FIG. 6.

[0094]

FIG. 6 illustrates an example of a cross-sectional view of the display device. In the display device illustrated in FIG. 6, a photodiode 502, a transistor 540, a transistor 503, and a liquid crystal element 505 are formed over a substrate 501 having an insulating surface (a TFT substrate).

[0095]

An oxide insulating layer 531, a protective insulating layer 532, an interlayer insulating layer 533, and an interlayer insulating layer 534 are provided over the transistor 503 and the transistor 540. The photodiode 502 is provided over the interlayer insulating layer 533. In the photodiode 502, a first semiconductor layer 506a, a second semiconductor layer 506b, and a third semiconductor layer 506c are sacked in that order over the interlayer insulating layer 533 between an electrode layer 541 formed over the interlayer insulating layer 533 and an electrode layer 542 formed over the interlayer insulating layer 534.

The electrode layer 541 is electrically connected to a conductive layer 543 which is formed in the interlayer insulating layer 534, and the electrode layer 542 is electrically connected to a gate electrode layer 545 through the electrode layer 541. The gate electrode layer 545 is electrically connected to a gate electrode layer of the transistor 540, and the photodiode 502 is electrically connected to the transistor 540. The transistor 540 corresponds to the transistor 205 in Embodiment 1.

# 25 [0097]

In order to prevent variation in electric characteristics of the transistor 503 and the transistor 540 each formed using an oxide semiconductor layer, which are included in a touch panel including a photosensor, impurities such as hydrogen, moisture, hydroxyl group, or a hydride (also referred to as a hydrogen compound) which cause the variation are intentionally removed from the oxide semiconductor layer. Additionally, the oxide semiconductor layer is highly purified to become i-type (intrinsic) by supplying oxygen which is a major component of the oxide semiconductor layer, which

is simultaneously reduced in a step of removing impurities. [0098]

Therefore, it is preferable that the oxide semiconductor layer contains hydrogen and carriers as little as possible. In the transistor 503 and the transistor 540, a channel formation region is formed in the oxide semiconductor layer, in which hydrogen contained therein is removed as much as possible to be close to 0 so that the hydrogen concentration is less than or equal to  $5 \times 10^{19}$  /cm<sup>3</sup>, preferably, less than or equal to  $5 \times 10^{18}$  /cm<sup>3</sup>, more preferably, less than or equal to  $5 \times 10^{17}$  /cm<sup>3</sup> or less than  $5 \times 10^{16}$  /cm<sup>3</sup>, and the carrier concentration is less than  $5 \times 10^{14}$  /cm<sup>3</sup>, preferably, less than or equal to  $5 \times 10^{12}$  /cm<sup>3</sup>.

[0099]

5

10

15

20

25

30

It is preferable that an off-state current be as small as possible in reverse characteristics of the transistor 503 and the transistor 540. An off-state current is a current that flows between a source and a drain of a thin film transistor in the case where a gate voltage between -1 V to -10 V is applied. A current value per 1  $\mu$ m in a channel width (w) of a thin film transistor formed using an oxide semiconductor, which is disclosed in this specification, is less than or equal to 100 aA/ $\mu$ m, preferably, less than or equal to 10 aA/ $\mu$ m. Further, since there is no pn junction and no hot carrier degradation, electric characteristics of the thin film transistor is not adversely affected.

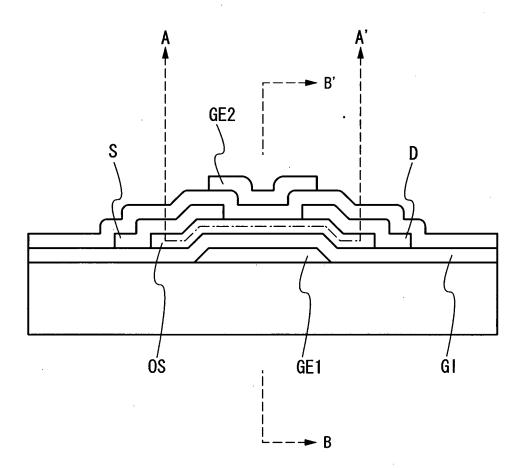

[0100]

FIG. 18 is a longitudinal cross-sectional view of an inverted staggered thin film transistor formed using an oxide semiconductor. An oxide semiconductor layer (OS) is provided over a gate electrode (GE1) with a gate insulating film (GI) interposed therebetween, and a source electrode (S) and a drain electrode (D) are provided thereover.

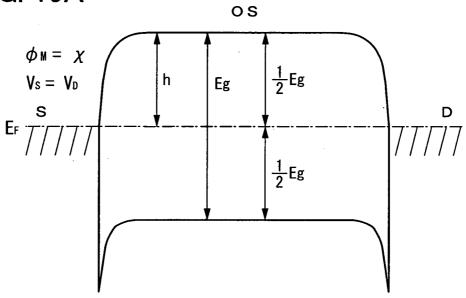

[0101]

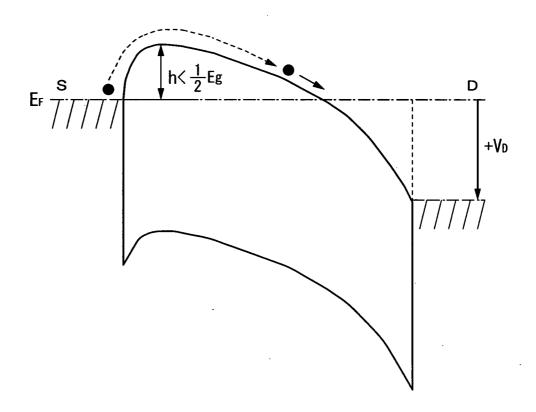

FIGS. 19A and 19B are energy band diagrams (schematic diagrams) of a cross section along A-A' in FIG. 18. FIG. 19A illustrates the case where the potential applied to the source is equal to the potential applied to the drain ( $V_D = 0 \text{ V}$ ), and FIG. 19B illustrates the case where a positive potential with respect to the source is applied to the

drain  $(V_D > 0 V)$ . [0102]

FIGS. 20A and 20B are energy band diagrams (schematic diagrams) of a cross section along B-B' in FIG. 18. FIG. 20A illustrates an on state in which a positive potential  $(+V_G)$  is applied to a gate electrode (GE1) and carriers (electrons) flow between the source and the drain. FIG. 20B illustrates an off state in which a negative potential  $(-V_G)$  is applied to the gate (GE1) and minority carriers do not flow. [0103]

FIG. 21 illustrates the relationships between the vacuum level and the work function of a metal  $(\phi M)$  and between the vacuum level and the electron affinity  $(\chi)$  of an oxide semiconductor.

[0104]

5

10

15

20

25

30

A conventional oxide semiconductor is typically an n-type semiconductor, and the Fermi level (E<sub>F</sub>) is away from the intrinsic Fermi level (Ei) located in the middle of a band gap and is located closer to the conduction band. Note that since hydrogen can serve as a donor, hydrogen is known as a factor to make the oxide semiconductor layer n-type.

[0105]

On the other hand, an oxide semiconductor according to the present invention is an intrinsic (i-type) or a substantially intrinsic oxide semiconductor which is obtained by removing hydrogen that is an n-type impurity from an oxide semiconductor and highly purifying the oxide semiconductor such that an impurity is prevented from being contained therein as much as possible. In other words, a feature is that a highly purified i-type (intrinsic) semiconductor or a semiconductor close thereto is obtained by removing an impurity such as hydrogen or water as much as possible. This enables the Fermi level (E<sub>F</sub>) to be at the same level as the intrinsic Fermi level (Ei).

The electron affinity  $(\chi)$  of an oxide semiconductor is said to be 4.3 eV. The work function of titanium (Ti) included in the source electrode and the drain electrode is substantially equal to the electron affinity  $(\chi)$  of the oxide semiconductor. In that case, a Schottky barrier to electrons is not formed at an interface between the metal and the

oxide semiconductor.

[0107]

In other words, in the case where the work function of the metal  $(\phi M)$  and the electron affinity  $(\chi)$  of the oxide semiconductor are equal to each other and the metal and the oxide semiconductor are in contact with each other, an energy band diagram (a schematic diagram) as illustrated in FIG. 19A is obtained.

[0108]

5

10

15

In FIG. 19B, a black circle (•) represents an electron, and when a positive potential is applied to the drain, the electron is injected into the oxide semiconductor layer over the barrier (h) and flows toward the drain. In that case, the height of the barrier (h) changes depends on the gate voltage and the drain voltage; in the case where a positive drain voltage is applied, the height of the barrier (h) is smaller than the height of the barrier in FIG. 19A where no voltage is applied, i.e., 1/2 of the band gap (Eg). [0109]

At this time, the electron injected into the oxide semiconductor layer flows through the oxide semiconductor layer as illustrated in FIG. 20A. In addition, in FIG. 20B, when a negative potential is applied to the gate electrode (GE1), the value of current is as close to zero as possible because holes that are minority carriers do not substantially exist.

20 [0110]

For example, even a thin film transistor has a channel width W of  $1 \times 10^4$  µm and a channel length of 3 µm, an off-state current is less than or equal to  $10^{-13}$  A and a subthreshold swing (S value) is 0.1 V/dec. (the thickness of the gate insulating film: 100 nm).

25 [0111]

In this manner, when the oxide semiconductor layer is highly purified so that impurities are contained as little as possible, the operation of the thin film transistor can be favorable.

[0112]

30

Therefore, the above transistors 503 and 540 formed using the oxide semiconductor layer are thin film transistors having stable electric characteristics and

high reliability.

[0113]

5

10

15

20

30

As the oxide semiconductor layer included in each of the transistor 503 and the transistor 540, any of a four-component metal oxide such as an In-Sn-Ga-Zn-O film, a three-component metal oxide such as an In-Ga-Zn-O film, an In-Sn-Zn-O film, an In-Al-Zn-O film, a Sn-Ga-Zn-O film, an Al-Ga-Zn-O film, and a Sn-Al-Zn-O film, or a two-component metal oxide such as an In-Zn-O film, a Sn-Zn-O film, an Al-Zn-O film, a Zn-Mg-O film, a Sn-Mg-O film, an In-Mg-O film, an In-O film, a Sn-O film, and a Zn-O film can be used. Further, SiO<sub>2</sub> may be contained in the above oxide semiconductor layer.

[0114]

Note that as the oxide semiconductor layer, a thin film expressed by  $InMO_3(ZnO)_m$  (m > 0) can be used. Here, M represents one or more metal elements selected from Ga, Al, Mn, and Co. For example, M can be Ga, Ga and Al, Ga and Mn, Ga and Co, or the like. An oxide semiconductor layer whose composition formula is represented by  $InMO_3$  ( $ZnO)_m$  (m > 0), which includes Ga as M, is referred to as the In-Ga-Zn-O oxide semiconductor described above, and a thin film of the In-Ga-Zn-O oxide semiconductor is also referred to as an In-Ga-Zn-O-based non-single-crystal film. [0115]

Here, a pin photodiode in which a semiconductor layer having p-type conductivity as the first semiconductor layer 506a, a high-resistance semiconductor layer (i-type semiconductor layer) as the second semiconductor layer 506b, and a semiconductor layer having n-type conductivity as the third semiconductor layer 506c are stacked is illustrated as an example.

25 [0116]

The first semiconductor layer 506a is a p-type semiconductor layer and can be formed using an amorphous silicon film containing an impurity element imparting p-type conductivity. The first semiconductor layer 506a is formed with a plasma CVD method with the use of a semiconductor source gas containing an impurity element belonging to Group 13 (such as boron (B)). As the semiconductor material gas, silane (SiH<sub>4</sub>) may be used. Alternatively, Si<sub>2</sub>H<sub>6</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, SiHCl<sub>3</sub>, SiCl<sub>4</sub>, SiF<sub>4</sub>, or the like may be used. Further alternatively, an amorphous silicon film which does not contain an

impurity element may be formed, and then, an impurity element may be introduced to the amorphous silicon film with the use of a diffusion method or an ion injecting method. Heating or the like may be performed after introducing the impurity element with an ion injecting method or the like in order to diffuse the impurity element. In this case, as a method of forming the amorphous silicon film, an LPCVD method, a chemical vapor deposition method, a sputtering method, or the like may be used. The first semiconductor layer 506a is preferably formed to have a thickness of greater than or equal to 10 nm and less than or equal to 50 nm.

The second semiconductor layer 506b is an i-type semiconductor layer (intrinsic semiconductor layer) and is formed with an amorphous silicon film. As for formation of the second semiconductor layer 506b, an amorphous silicon film is formed with a plasma CVD method using a semiconductor material gas. As the semiconductor material gas, silane (SiH<sub>4</sub>) may be used. Alternatively, Si<sub>2</sub>H<sub>6</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, SiHCl<sub>3</sub>, SiCl<sub>4</sub>, SiF<sub>4</sub>, or the like may be used. The second semiconductor layer 506b may be alternatively formed with an LPCVD method, a chemical vapor deposition method, a sputtering method, or the like. The second semiconductor layer 506b is preferably formed to have a thickness of greater than or equal to 200 nm and less than or equal to 1000 nm.

20 [0118]

5

10

15

25

30

[0117]

The third semiconductor layer 506c is an n-type semiconductor layer and is formed with an amorphous silicon film containing an impurity element imparting n-type conductivity. The third semiconductor layer 506c is formed with a plasma CVD method using a semiconductor material gas containing an impurity element belonging to Group 15 (such as phosphorus (P)). As the semiconductor material gas, silane (SiH<sub>4</sub>) may be used. Alternatively, Si<sub>2</sub>H<sub>6</sub>, SiH<sub>2</sub>Cl<sub>2</sub>, SiHCl<sub>3</sub>, SiCl<sub>4</sub>, SiF<sub>4</sub>, or the like may be used. Further alternatively, an amorphous silicon film which does not contain an impurity element may be formed, and then, an impurity element may be introduced to the amorphous silicon film with the use of a diffusion method or an ion injecting method. Heating or the like may be performed after the impurity element is introduced with an ion injecting method or the like in order to diffuse the impurity element. In this case, as a method of forming the amorphous silicon film, an LPCVD method, a

chemical vapor deposition method, a sputtering method, or the like may be used. The third semiconductor layer 506c is preferably formed to have a thickness of greater than or equal to 20 nm and less than or equal to 200 nm.

[0119]

5

10

15

20

30

The first semiconductor layer 506a, the second semiconductor layer 506b, and the third semiconductor layer 506c are not necessarily formed using an amorphous semiconductor, and they may be formed using a polycrystalline semiconductor or a microcrystalline semiconductor (a semi-amorphous semiconductor (SAS)).

[0120]

The microcrystalline semiconductor belongs to a metastable state of an intermediate between amorphous and single crystalline when Gibbs free energy is considered. That is, the microcrystalline semiconductor film is a semiconductor having a third state which is thermodynamically stable and has a short range order and lattice distortion. Columnar-like or needle-like crystals grow in a normal direction with respect to a substrate surface. The Raman spectrum of microcrystalline silicon, which is a typical example of a microcrystalline semiconductor, is shifted to a small wavenumber region below 520 cm<sup>-1</sup> which represents single-crystalline silicon. That is, the peak of the Raman spectrum of the microcrystalline silicon exists between 520 cm<sup>-1</sup> which represents single crystal silicon and 480 cm<sup>-1</sup> which represents amorphous silicon. In addition, microcrystalline silicon contains hydrogen or halogen of at least 1 atomic% or more in order to terminate a dangling bond. Moreover, microcrystalline silicon may contain a rare gas element such as helium, argon, krypton, or neon to further promote lattice distortion, so that a microcrystalline semiconductor film with high thermodynamic stability can be obtained.

25 [0121]

The microcrystalline semiconductor film can be formed with a high-frequency plasma CVD method with a frequency of several tens of MHz to several hundreds of MHz or with a microwave plasma CVD method with a frequency of greater than or equal to 1 GHz. Typically, the microcrystalline semiconductor film can be formed using a silicon hydride such as SiH<sub>4</sub>, Si<sub>2</sub>H<sub>6</sub>, SiH<sub>2</sub>Cl<sub>2</sub> or SiHCl<sub>3</sub>, or a silicon halide such as SiCl<sub>4</sub> or SiF<sub>4</sub>, which is diluted with hydrogen. With a dilution with one or a plural kinds of rare gas elements selected from helium, argon, krypton, or neon in addition to

silicon hydride and hydrogen, the microcrystalline semiconductor film can be formed. In that case, the flow ratio of hydrogen to the silicon hydride is 5:1 to 200:1, preferably, 50:1 to 150:1, more preferably, 100:1. Further, a hydrocarbon gas such as CH<sub>4</sub> or C<sub>2</sub>H<sub>6</sub>, a germanium gas such as GeH<sub>4</sub> or GeF<sub>4</sub>, F<sub>2</sub>, or the like may be mixed into the gas containing silicon.

[0122]

5

10

15

20

25

30

In addition, since the mobility of holes generated by the photoelectric effect is lower than that of electrons, a pin photodiode has better characteristics when a surface on the p-type semiconductor layer side is used as a light-receiving plane. Here, an example where light received by the photodiode 502 from a surface of the substrate 501, over which a pin photodiode is formed, is converted into electric signals will be described. Further, light from the semiconductor layer having a conductivity type opposite to that of the semiconductor layer on the light-receiving plane is disturbance light; therefore, the electrode layer is preferably formed using a light-blocking conductive film. Note that a surface on the n-type semiconductor layer side can alternatively be used as the light-receiving plane.

The liquid crystal element 505 includes a pixel electrode 507, liquid crystal 508, a counter electrode 509, an alignment film 511, and an alignment film 512. The pixel electrode 507 is formed over the substrate 501, and the alignment film 511 is formed over the pixel electrode 507. The pixel electrode 507 is electrically connected to the transistor 503 through a conductive film 510. A substrate 513 (a counter substrate) is provided with the counter electrode 509, the alignment film 512 is formed on the counter electrode 509, and the liquid crystal 508 is interposed between the alignment film 511 and the alignment film 512. The transistor 503 corresponds to the transistor 201 in Embodiment 1.

[0124]

[0123]

A cell gap between the pixel electrode 507 and the counter electrode 509 can be controlled by using a spacer 516. In FIG. 6, the cell gap is controlled by using the columnar spacer 516 selectively formed by photolithography. Alternatively, the cell gap can be controlled by dispersing spherical spacers between the pixel electrode 507 and the counter electrode 509.

[0125]

The liquid crystal 508 is surrounded by a sealing material between the substrate 501 and the substrate 513. The liquid crystal 508 may be injected with a dispenser method (droplet method) or a dipping method (pumping method).

5 [0126]

10

15

20

25

30

For the pixel electrode 507, a light-transmitting conductive material such as indium tin oxide (ITO), indium tin oxide containing silicon oxide (ITSO), organic indium, organic tin, indium zinc oxide (IZO) containing zinc oxide (ZnO), zinc oxide (ZnO), zinc oxide containing gallium (Ga), tin oxide (SnO<sub>2</sub>), indium oxide containing tungsten oxide, indium zinc oxide containing tungsten oxide, indium oxide containing titanium oxide, or the like can be used. A conductive composition containing a conductive macromolecule (also referred to as a conductive polymer) can be used to form the pixel electrode 507. As the conductive macromolecule, a so-called  $\pi$ -electron conjugated conductive polymer can be used. For example, polyaniline or a derivative thereof, polypyrrole or a derivative thereof, polythiophene or a derivative thereof, a copolymer of two or more kinds of them, and the like can be given.

[0127]

Since the transparent liquid crystal element 505 is given as an example in this embodiment, the light-transmitting conductive material described above can be used also for the counter electrode 509 as in the case of the pixel electrode 507.

[0128]

An alignment film 511 is provided between the pixel electrode 507 and the liquid crystal 508, and an alignment film 512 is provided between the counter electrode 509 and the liquid crystal 508. The alignment film 511 and the alignment film 512 can be formed using an organic resin such as a polyimide or poly(vinyl alcohol). Alignment treatment such as rubbing is performed on their surfaces in order to align liquid crystal molecules in certain direction. Rubbing can be performed by rolling a roller wrapped with cloth of nylon or the like while applying pressure on the alignment film so that the surface of the alignment film is rubbed in certain direction. Note that by using an inorganic material such as silicon oxide, the alignment film 511 and the alignment film 512 each having an alignment property can be directly formed with an

evaporation method without performing an alignment treatment. [0129]

Further, a color filter 514 through which light in a particular wavelength range can pass is formed over the substrate 513 so as to overlap with the liquid crystal element 505. The color filter 514 can be selectively formed by photolithography after application of an organic resin such as an acrylic-based resin in which colorant is dispersed on the substrate 513. Alternatively, the color filter 514 can be selectively formed by etching after application of a polyimide-based resin in which colorant is dispersed on the substrate 513. Alternatively, the color filter 514 can be selectively formed with a droplet discharge method such as an ink-jet method.

Furthermore, a shielding film 515 which can block light is formed over the substrate 513 so as to overlap with the photodiode 502. By providing the shielding film 515, light from a backlight that passes through the substrate 513 and enters the touch panel can be prevented from being directly delivered to the photodiode 502. Further, disclination due to disorder of alignment of the liquid crystal 508 among pixels can be prevented from being viewed. An organic resin containing black colorant such as carbon black or a low-valent titanium oxide can be used for the shielding film 515. Alternatively, a film formed using chromium can be used for the shielding film 515.

20 [0131]

5

10

15

Furthermore, a polarizing plate 517 is provided on a surface which is the opposite side of a surface of the substrate 501 over which the pixel electrode 507 is formed, and a polarizing plate 518 is provided on a surface which is the opposite side of a surface of the substrate 513 on which the counter electrode 509 is formed.

25 [0132]

30

With the use of an insulating material, the oxide insulating layer 531, the protective insulating layer 532, the interlayer insulating layer 533, and the interlayer insulating layer 534 can be formed, depending on the material, with a method such as a sputtering method, an SOG method, spin coating, dip coating, spray coating, or a droplet discharge method (e.g., an ink-jet method, screen printing, offset printing, or the like), or a tool (equipment) such as a doctor knife, a roll coater, a curtain coater, or a knife coater.

[0133]

As the oxide insulating layer 531, a single layer or a stacked layer of an oxide insulating layer such as a silicon oxide layer, a silicon oxynitride layer, an aluminum oxide layer, an aluminum oxynitride layer, or the like can be used.

5 [0134]

10

15

20

25

30

As an inorganic insulating material of the protective insulating layer 532, a single layer or a stacked layer of a nitride insulating layer such as a silicon nitride layer, a silicon nitride oxide layer, an aluminum nitride layer, an aluminum nitride oxide layer, or the like can be used. High-density plasma CVD with the use of microwaves (2.45 GHz) is preferably employed because formation of a dense and high-quality insulating layer having high withstand voltage is possible.

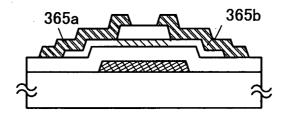

For reduction of the surface roughness, an insulating layer functioning as a planarization insulating film is preferably used as the interlayer insulating layers 533 and 534. The interlayer insulating layers 533 and 534 can be formed using an organic insulating material having heat resistance such as a polyimide, an acrylic resin, a benzocyclobutene-based resin, a polyamide, or an epoxy resin. Other than such organic insulating materials, it is possible to use a single layer or stacked layers of a low-dielectric constant material (a low-k material), a siloxane-based resin, phosphosilicate glass (PSG), borophosphosilicate glass (BPSG), or the like.